PIN到99.99%问题的解决办法

NPort 6150 6250 Series Quick Installation Guide

P/N: 1802061500016 *1802061500016*NPort 6150/6250 Series Quick Installation GuideEdition 9.0, November 2016Technical Support Contact Information/supportMoxa Americas:Toll-free: 1-888-669-2872 Tel: 1-714-528-6777 Fax: 1-714-528-6778 Moxa China (Shanghai office): Toll-free: 800-820-5036 Tel: +86-21-5258-9955 Fax: +86-21-5258-5505 Moxa Europe:Tel: +49-89-3 70 03 99-0 Fax: +49-89-3 70 03 99-99 Moxa Asia-Pacific:Tel: +886-2-8919-1230 Fax: +886-2-8919-1231 Moxa India:Tel: +91-80-4172-9088 Fax: +91-80-4132-10452016 Moxa Inc. All rights reserved.OverviewThe NPort 6150/6250 series secure serial device servers provide reliable serial-to-Ethernet connectivity for a wide range of serial devices. The NPort 6150/6250 support TCP Server, TCP Client, UDP, andPair-Connection operation modes to ensure the compatibility of network software. In addition, the NPort 6150/6250 also support Secure TCP Server, Secure TCP Client, Secure Pair-Connection, and Secure Real COM modes for security critical applications such as banking, telecom, access control, and remote site management.Package ChecklistBefore installing a NPort 6150/6250 secure device server, verify that the package contains the following items:• 1 NPort 6150 or NPort 6250•Power adapter (does not apply to -T models)• 2 wallmount ears•Documentation and software CD•Quick installation guide (this guide)•Warranty cardOptional Accessories•DK-35A: DIN-rail mounting kit (35 mm)•DIN-rail power supply•CBL-RJ45M9-150: 8-pin RJ45 to male DB9 cable•CBL-RJ45M25-150: 8-pin RJ45 to male DB25 cableNOTE: Please notify your sales representative if any of the above items are missing or damaged.Hardware IntroductionNPort 6150NPort 6250Reset Button—Press the Reset Button continuously for 5 sec to load factory defaults. Use a pointed object, such as a straightened paper clip or toothpick, to press the reset button. This will cause the Ready LED to blink on and off. The factory defaults will be loaded once the Ready LED stops blinking (after about 5 seconds). At this point, you should release the reset button.LED IndicatorsAdjustable pull high/low resistor for RS-422/485 (150 K Ω or 1 K Ω)Jumpers are used to set the pull high/low resistors. The default is 150 kΩ. Short the jumpers to set this value to 1 kΩ. Do not use the 1 kΩ setting with RS -232 mode, since doing so will degrade the RS-232 signals and shorten the communication distance.Hardware Installation ProcedureSTEP 1: Connect the 12-48 VDC power adaptor to the NPort 6150 andthen plug the power adaptor into a DC outlet.STEP 2: For first-time configuration, use a cross-over Ethernet cable toconnect the NPort 6150 directly to your computer’s Ethernet cable. For connecting to a network, use a standardstraight-through Ethernet cable to connect to a hub or switch.STEP 3: Connect the NPort 6150’s serial port to a serial device.Placement OptionsThe NPort 6150/6250 can be placed flat on a desktop or other horizontal surface. In addition, you may use the DIN-rail or wallmount options, as illustrated below.WallmountDin RailSoftware Installation InformationThe Documentation and software CD contains the user’s manual, NPort Search Utility, and the PComm Lite Suite. Insert the CD into yourcomputer’s CD-ROM drive and follow the on-screen instructions. Please refer to the user’s manual for additional details on using the NPort Search Utility and PComm Lite.Pin Assignments and Cable WiringTwo serial cables for connecting the NPort 6150 to a serial device can be purchased separately. The wiring diagrams for the two cables are shown below.。

1777099中文资料

Extract from the onlinecatalogMSTBV 2,5/ 4-GF-5,08Order No.: 1777099The figure shows a 10-position version of the producthttp://eshop.phoenixcontact.de/phoenix/treeViewClick.do?UID=1777099Header, nominal current: 12 A, rated voltage: 250 V, pitch: 5.08 mm, no. of positions: 4, mounting: Solderinghttp://Please note that the data givenhere has been taken from theonline catalog. For comprehensiveinformation and data, please referto the user documentation. TheGeneral Terms and Conditions ofUse apply to Internet downloads. Technical dataDimensions / positionsPitch 5.08 mmDimension a15.24 mmNumber of positions4Pin dimensions 1 x 1 mmHole diameter 1.4 mmTechnical dataInsulating material group IIIaRated surge voltage (III/3) 4 kVRated surge voltage (III/2) 4 kVRated surge voltage (II/2) 4 kVRated voltage (III/2)320 VRated voltage (II/2)400 VConnection in acc. with standard EN-VDENominal current I N12 ANominal voltage U N250 VMaximum load current12 AInsulating material PBTInflammability class acc. to UL 94V0Certificates / ApprovalsCSANominal voltage U N300 VNominal current I N10 ACULNominal voltage U N300 VNominal current I N10 AULNominal voltage U N300 VNominal current I N10 ACertification CB, CSA, CUL, GL, GOST, RS, UL, VDE-PZI AccessoriesItem Designation DescriptionAssembly1755477MSTB-BL Keying cap, for forming sections, plugs onto header pin, greeninsulating materialMarking1051993B-STIFT Marker pen, for manual labeling of unprinted Zack strips, smear-proof and waterproof, line thickness 0.5 mm0804293SK 5,08/3,8:FORTL.ZAHLEN Marker card, printed horizontally, self-adhesive, 12 identicaldecades marked 1-10, 11-20 etc. up to 91-(99)100, sufficient for120 terminal blocks0805085SK 5,08/3,8:SO Marker card, special printing, self-adhesive, labeled acc. tocustomer requirements, 12 identical marker strips per card, max.25-position labeling per strip, color: white0805412SK 5,08/3,8:UNBEDRUCKT Marker cards, unprinted, with pitch divisions, self-adhesive, 10-section marker strips, 12 strips per card, can be labeled with theM-PENPlug/Adapter1734401CR-MSTB Coding section, inserted into the recess in the header or theinverted plug, red insulating materialAdditional productsItem Designation DescriptionGeneral1873223FKC 2,5/ 4-STF-5,08Plug with screw flange, nominal current: 12 A, rated voltage: 250V, pitch: 5.08 mm, no. of positions: 4, type of connection: Spring-cage connection1902327FKCT 2,5/ 4-STF-5,08Plug component, nominal current: 12 A, rated voltage: 250 V,pitch: 5.08 mm, no. of positions: 4, type of connection: Spring-cage connection1874125FKCVR 2,5/ 4-STF-5,08Plug component, nominal current: 12 A, rated voltage: 250 V,pitch: 5.08 mm, no. of positions: 4, type of connection: Spring-cage connection1873825FKCVW 2,5/ 4-STF-5,08Plug component, nominal current: 12 A, rated voltage: 250 V,pitch: 5.08 mm, no. of positions: 4, type of connection: Spring-cage connection1777824FRONT-MSTB 2,5/ 4-STF-5,08Plug with screw flange, nominal current: 12 A, rated voltage: 250V, pitch: 5,08 mm, no. of positions: 4, type of connection: Screwconnection1778001MSTB 2,5/ 4-STF-5,08Plug component, nominal current: 12 A, rated voltage: 250 V,pitch: 5.08 mm, no. of positions: 4, type of connection: Screwconnection1809750MSTBC 2,5/ 4-STZF-5,08Plug component, nominal current: 12 A, rated voltage: 320 V,pitch: 5.08 mm, no. of positions: 4, type of connection: Crimpconnection1805327MSTBT 2,5/ 4-STF-5,08Plug with T-shape and screw flange, nominal current: 12 A,rated voltage: 250 V, pitch: 5,08 mm, no. of positions: 4, type ofconnection: Screw connection1835119MVSTBR 2,5/ 4-STF-5,08Plug with screw flange, nominal current: 12 A, rated voltage: 250V, pitch: 5,08 mm, no. of positions: 4, type of connection: Screwconnection1834929MVSTBW 2,5/ 4-STF-5,08Plug component, nominal current: 12 A, rated voltage: 250 V,pitch: 5.08 mm, no. of positions: 4, type of connection: Screwconnection1918117QC 0,75/ 4-STF-5,08Plug components, 5.08 mm pitch, color: green, no. of positions 4,dimension a 15.24 mm1883378QC 1/ 4-STF-5,08Plug, nominal current: 10 A, rated voltage: 500 V, pitch: 5.08mm, number of positions: 4, connection method: Insulationdisplacement connection QUICKON1853120TMSTBP 2,5/ 4-STF-5,08Plug component, nominal current: 12 A, rated voltage: 250 V,pitch: 5.08 mm, no. of positions: 4, type of connection: Screwconnection1873029ZFKK 1,5-ICV-5,08Modular terminal blocks with plug entry, cross section: 0.2 - 1.5mm², width: 5.1 mm, color: grayDrawingsDrilling diagramDimensioned drawingAddressPHOENIX CONTACT GmbH & Co. KGFlachsmarktstr. 832825 Blomberg,GermanyPhone +49 5235 3 00Fax +49 5235 3 41200http://www.phoenixcontact.de© 2008 Phoenix ContactTechnical modifications reserved;。

OPA549T中文资料

q HIGH OUTPUT CURRENT: 8A Continuous 10A Peak q WIDE POWER SUPPLY RANGE: Single Supply: +8V to +60V Dual Supply: ±4V to ±30V q WIDE OUTPUT VOLTAGE SWING q FULLY PROTECTED: Thermal Shutdown Adjustable Current Limit q OUTPUT DISABLE CONTROL q THERMAL SHUTDOWN INDICATOR q HIGH SLEW RATE: 9V/µs q CONTROL REFERENCE PIN q 11-LEAD POWER ZIP PACKAGE

±20

25 –100 ±0.5 ±5 70 1 (V+) – 2.3 (V–) – 0.2 95 107 || 6 109 || 4

INPUT VOLTAGE RANGE Common-Mode Voltage Range: Positive VCM Negative VCM Common-Mode Rejection Ratio CMRR INPUT IMPEDANCE Differential Common-Mode OPEN-LOOP GAIN Open-Loop Voltage Gain FREQUENCY RESPONSE Gain Bandwidth Product Slew Rate Full Power Bandwidth Settling Time: ±0.1% Total Harmonic Distortion + Noise(3) AOL

VO = ±25V, RL = 1kΩ VO = ±25V, RL = 4Ω

FAIRCHILD 5497 DM7497 数据手册

Recommended Operating Conditions

Symbol

VCC VIH VIL IOH IOL TA ts(L) th(H) th(L) tw(H) tw(L) tw(H)

Parameter

Supply Voltage High Level Input Voltage Low Level Input Voltage High Level Output Current Low Level Output Current Free Air Operating Temperature Setup Time LOW CE to CP Rising Hold Time HIGH CE to CP Rising Hold Time LOW CE to CP Falling CP Pulse Width HIGH CP Pulse Width LOW MR Pulse Width HIGH

VCC e Pin 16 GND e Pin 8

Pin Names

S0 – S5 EZ EY CE CP MR OZ Oy TC

Description

Rate Select Inputs OZ Enable Input (Active LOW) OY Enable Input Count Enable Input (Active LOW) Clock Pulse Input (Active Rising Edge) Asynchronous Master Reset Input (Active HIGH) Gated Clock Output (Active LOW) Complement Output (Active HIGH) Terminal Count Output (Active LOW)

NI cDAQ

SPECIFICA TIONSNI cDAQ™-91844-Slot, Ethernet CompactDAQ ChassisDefinitionsWarranted specifications describe the performance of a model under stated operating conditions and are covered by the model warranty.Characteristics describe values that are relevant to the use of the model under stated operating conditions but are not covered by the model warranty.•Typical specifications describe the expected performance met by a majority of the models.•Nominal specifications describe parameters and attributes that may be useful in operation. Specifications are Typical unless otherwise noted.ConditionsSpecifications are valid at 25 °C unless otherwise noted.Analog InputInput FIFO size127 samples per slotMaximum sample rate1Determined by the C Series module or modules Timing accuracy250 ppm of sample rateTiming resolution212.5 nsNumber of channels supported Determined by the C Series module or modules 1Performance dependent on type of installed C Series module and number of channels in the task.2Does not include group delay. For more information, refer to the documentation for each C Series module.Analog OutputNumber of channels supportedHardware-timed taskOnboard regeneration16Non-regeneration Determined by the C Series module or modules Non-hardware-timed task Determined by the C Series module or modules Maximum update rateOnboard regeneration 1.6 MS/s (multi-channel, aggregate)Non-regeneration Determined by the C Series module or modules Timing accuracy50 ppm of sample rateTiming resolution12.5 nsOutput FIFO sizeOnboard regeneration8,191 samples shared among channels used Non-regeneration127 samples per slotAO waveform modes Non-periodic waveform,periodic waveform regeneration mode fromonboard memory,periodic waveform regeneration from hostbuffer including dynamic updateDigital Waveform CharacteristicsWaveform acquisition (DI) FIFOParallel modules511 samples per slotSerial modules63 samples per slotWaveform generation (DO) FIFOParallel modules2,047 samples per slotSerial modules63 samples per slotDigital input sample clock frequencyStreaming to application memory System-dependentFinite0 MHz to 10 MHz2| | NI cDAQ-9184 SpecificationsDigital output sample clock frequencyStreaming from application memory System-dependentRegeneration from FIFO0 MHz to 10 MHzFinite0 MHz to 10 MHzTiming accuracy50 ppmGeneral-Purpose Counters/TimersNumber of counters/timers4Resolution32 bitsCounter measurements Edge counting, pulse, semi-period, period,two-edge separation, pulse widthPosition measurements X1, X2, X4 quadrature encoding withChannel Z reloading; two-pulse encoding Output applications Pulse, pulse train with dynamic updates,frequency division, equivalent time sampling Internal base clocks80 MHz, 20 MHz, 100 kHzExternal base clock frequency0 MHz to 20 MHzBase clock accuracy50 ppmOutput frequency0 MHz to 20 MHzInputs Gate, Source, HW_Arm, Aux, A, B, Z,Up_DownRouting options for inputs Any module PFI, analog trigger, many internalsignalsFIFO Dedicated 127-sample FIFOFrequency GeneratorNumber of channels1Base clocks20 MHz, 10 MHz, 100 kHzDivisors 1 to 16 (integers)Base clock accuracy50 ppmOutput Any module PFI terminalNI cDAQ-9184 Specifications| © National Instruments| 3Module PFI CharacteristicsFunctionality Static digital input, static digital output, timinginput, and timing outputTiming output sources3Many analog input, analog output, counter,digital input, and digital output timing signals Timing input frequency0 MHz to 20 MHzTiming output frequency0 MHz to 20 MHzDigital TriggersSource Any module PFI terminalPolarity Software-selectable for most signalsAnalog input function Start Trigger, Reference Trigger,Pause Trigger, Sample Clock,Sample Clock TimebaseAnalog output function Start Trigger, Pause Trigger, Sample Clock,Sample Clock TimebaseCounter/timer function Gate, Source, HW_Arm, Aux, A, B, Z,Up_DownModule I/O StatesAt power-on Module-dependent. Refer to the documentationfor each C Series module.Network InterfaceNetwork protocols TCP/IP, UDPNetwork ports used HTTP:80 (configuration only), TCP:3580;UDP:5353 (configuration only), TCP:5353(configuration only); TCP:31415; UDP:7865(configuration only), UDP:8473 (configurationonly)Network IP configuration DHCP + Link-Local, DHCP, Static,Link-Local3Actual available signals are dependent on type of installed C Series module.4| | NI cDAQ-9184 SpecificationsHigh-performance data streams7Data stream types available Analog input, analog output, digital input,digital output, counter/timer input,counter/timer output, NI-XNET4Default MTU size1500 bytesJumbo frame support Up to 9000 bytesEthernetNetwork interface1000 Base-TX, full-duplex; 1000 Base-TX,half-duplex; 100 Base-TX, full-duplex;100 Base-TX, half-duplex; 10 Base-T,full-duplex; 10 Base-T, half-duplex Communication rates10/100/1000 Mbps, auto-negotiated Maximum cabling distance100 m/segmentPower RequirementsCaution The protection provided by the NI cDAQ-9184 chassis can be impaired ifit is used in a manner not described in the NI cDAQ-9181/9184/9188/9191 UserManual.Note Some C Series modules have additional power requirements. For moreinformation about C Series module power requirements, refer to the documentationfor each C Series module.Note Sleep mode for C Series modules is not supported in the NI cDAQ-9184.V oltage input range9 V to 30 VMaximum power consumption515 W4When a session is active, CAN or LIN (NI-XNET) C Series modules use a total of two data streams regardless of the number of NI-XNET modules in the chassis.5Includes maximum 1 W module load per slot across rated temperature and product variations.NI cDAQ-9184 Specifications| © National Instruments| 5Note The maximum power consumption specification is based on a fully populatedsystem running a high-stress application at elevated ambient temperature and withall C Series modules consuming the maximum allowed power.Power input connector 2 positions 3.5 mm pitch mini-combicon screwterminal with screw flanges, SauroCTMH020F8-0N001Power input mating connector Sauro CTF020V8, Phoenix Contact 1714977,or equivalentPhysical CharacteristicsWeight (unloaded)Approximately 643 g (22.7 oz)Dimensions (unloaded)178.1 mm × 88.1 mm × 64.3 mm(7.01 in. × 3.47 in. × 2.53 in.) Refer to thefollowing figure.Screw-terminal wiringGauge0.5 mm 2 to 2.1 mm2 (20 AWG to 14 AWG)copper conductor wireWire strip length 6 mm (0.24 in.) of insulation stripped from theendTemperature rating85 °CTorque for screw terminals0.20 N · m to 0.25 N · m (1.8 lb · in. to2.2 lb · in.)Wires per screw terminal One wire per screw terminalConnector securementSecurement type Screw flanges providedTorque for screw flanges0.20 N · m to 0.25 N · m (1.8 lb · in. to2.2 lb · in.)If you need to clean the chassis, wipe it with a dry towel.6| | NI cDAQ-9184 SpecificationsFigure 1. NI cDAQ-9184 Dimensions30.6 mm 47.2 mm Safety VoltagesConnect only voltages that are within these limits.V terminal to C terminal30 V maximum, Measurement Category IMeasurement Category I is for measurements performed on circuits not directly connected to the electrical distribution system referred to as MAINS voltage. MAINS is a hazardous liveNI cDAQ-9184 Specifications | © National Instruments | 7electrical supply system that powers equipment. This category is for measurements of voltages from specially protected secondary circuits. Such voltage measurements include signal levels, special equipment, limited-energy parts of equipment, circuits powered by regulatedlow-voltage sources, and electronics.Caution Do not connect the system to signals or use for measurements withinMeasurement Categories II, III, or IV.Note Measurement Categories CAT I and CAT O (Other) are equivalent. These testand measurement circuits are not intended for direct connection to the MAINsbuilding installations of Measurement Categories CAT II, CAT III, or CAT IV.Environmental-20 °C to 55 °C6Operating temperature (IEC 60068-2-1and IEC 60068-2-2)Caution To maintain product performance and accuracy specifications when theambient temperature is between 45 and 55 °C, you must mount the chassishorizontally to a metal panel or surface using the screw holes or the panel mount kit.Measure the ambient temperature at each side of the CompactDAQ system 63.5 mm(2.5 in.) from the side and 25.4 mm (1.0 in.) from the rear cover of the system. Forfurther information about mounting configurations, go to /info and enterthe Info Code cdaqmounting.-40 °C to 85 °CStorage temperature (IEC 60068-2-1 andIEC 60068-2-2)Ingress protection IP 30Operating humidity (IEC 60068-2-56)10% to 90% RH, noncondensingStorage humidity (IEC 60068-2-56)5% to 95% RH, noncondensingPollution Degree (IEC 60664)2Maximum altitude5,000 mIndoor use only.6When operating the NI cDAQ-9184 in temperatures below 0 °C, you must use the PS-15 powersupply or another power supply rated for below 0 °C.8| | NI cDAQ-9184 SpecificationsHazardous LocationsU.S. (UL)Class I, Division 2, Groups A, B, C, D, T4;Class I, Zone 2, AEx nA IIC T4Canada (C-UL)Class I, Division 2, Groups A, B, C, D, T4;Class I, Zone 2, Ex nA IIC T4Europe (ATEX) and International (IECEx)Ex nA IIC T4 GcShock and VibrationTo meet these specifications, you must direct mount the NI cDAQ-9184 system and affix ferrules to the ends of the terminal lines.Operational shock30 g peak, half-sine, 11 ms pulse (Tested inaccordance with IEC 60068-2-27. Test profiledeveloped in accordance withMIL-PRF-28800F.)Random vibrationOperating 5 Hz to 500 Hz, 0.3 g rmsNon-operating 5 Hz to 500 Hz, 2.4 g rms (Tested in accordancewith IEC 60068-2-64. Non-operating testprofile exceeds the requirements ofMIL PRF-28800F, Class 3.)Safety and Hazardous Locations StandardsThis product is designed to meet the requirements of the following electrical equipment safety standards for measurement, control, and laboratory use:•IEC 61010-1, EN 61010-1•UL 61010-1, CSA C22.2 No. 61010-1•EN 60079-0:2012, EN 60079-15:2010•IEC 60079-0: Ed 6, IEC 60079-15; Ed 4•UL 60079-0; Ed 6, UL 60079-15; Ed 4•CSA 60079-0:2011, CSA 60079-15:2012Note For UL and other safety certifications, refer to the product label or the OnlineProduct Certification section.NI cDAQ-9184 Specifications| © National Instruments| 9Electromagnetic CompatibilityThis product meets the requirements of the following EMC standards for electrical equipment for measurement, control, and laboratory use:•EN 61326-1 (IEC 61326-1): Class A emissions; Basic immunity•EN 55011 (CISPR 11): Group 1, Class A emissions•EN 55022 (CISPR 22): Class A emissions•EN 55024 (CISPR 24): Immunity•AS/NZS CISPR 11: Group 1, Class A emissions•AS/NZS CISPR 22: Class A emissions•FCC 47 CFR Part 15B: Class A emissions•ICES-001: Class A emissionsNote In the United States (per FCC 47 CFR), Class A equipment is intended foruse in commercial, light-industrial, and heavy-industrial locations. In Europe,Canada, Australia and New Zealand (per CISPR 11) Class A equipment is intendedfor use only in heavy-industrial locations.Note Group 1 equipment (per CISPR 11) is any industrial, scientific, or medicalequipment that does not intentionally generate radio frequency energy for thetreatment of material or inspection/analysis purposes.Note For EMC declarations and certifications, and additional information, refer tothe Online Product Certification section.CE ComplianceThis product meets the essential requirements of applicable European Directives, as follows:•2014/35/EU; Low-V oltage Directive (safety)•2014/30/EU; Electromagnetic Compatibility Directive (EMC)•2014/34/EU; Potentially Explosive Atmospheres (ATEX)Online Product CertificationRefer to the product Declaration of Conformity (DoC) for additional regulatory compliance information. To obtain product certifications and the DoC for this product, visit / certification, search by model number or product line, and click the appropriate link in the Certification column.10| | NI cDAQ-9184 SpecificationsEnvironmental ManagementNI is committed to designing and manufacturing products in an environmentally responsible manner. NI recognizes that eliminating certain hazardous substances from our products is beneficial to the environment and to NI customers.For additional environmental information, refer to the Minimize Our Environmental Impact web page at /environment. This page contains the environmental regulations and directives with which NI complies, as well as other environmental information not included in this document.Waste Electrical and Electronic Equipment (WEEE) EU Customers At the end of the product life cycle, all NI products must bedisposed of according to local laws and regulations. For more information abouthow to recycle NI products in your region, visit /environment/weee.电子信息产品污染控制管理办法(中国RoHS)中国客户National Instruments符合中国电子信息产品中限制使用某些有害物质指令(RoHS)。

WNA1100 N150无线USB适配器安装指南说明书

Guide d'installation Adaptateur USB sans fil N150 modèle WNA1100Contenu de la boîteCD InstallationDurée approximative de l'installation : 10 minutes.1. Insérez le CD dans le lecteur de CD-ROM de votre ordinateur. Si l'écranprincipal du CD ne s'affiche pas, parcourez les fichiers du CD et double-cliquez sur Autorun.exe.2. Cliquez sur Setup (Installation).L'écran Software Update Check (Détection de mises à jour) s'affiche.3. Si vous êtes connecté à Internet, cliquez sur Check for Updates (Rechercherdes mises à jour). Dans le cas contraire, cliquez sur Install from CD (Installerà partir du CD).4. Cliquez sur I Agree (J'accepte) pour accepter les termes de la licence, puiscliquez sur Next (Suivant).pendant l'installation du logiciel.L'opération peut prendre quelquesinsérer votre adaptateur.5.câble USB fournis.Le câble USB et le support deUSB à l'ordinateur.Remarque : pour des résultatsà moins un mètre du routeur.6. Cliquez sur Next(Suivant).7. NETGEAR Genie affiche la liste des réseaux sans fil présents dans votre zone.Connexion à un réseau sans filVous pouvez vous connecter à un réseau sans fil à partir de l'écran NETGEARGenie. Vous pouvez également utiliser la fonctionnalité WPS (Wi-Fi ProtectedSetup) si votre réseau sans fil est compatible.• NETGEAR Genie : cliquez sur votre réseau sans fil pour le sélectionner dans laliste, puis cliquez sur Connect (Se connecter). Si le réseau est sécurisé,saisissez le mot de passe ou la clé réseau.• WPS : appuyez sur le bouton WPS situé sur le côté de l'adaptateur etmaintenez-le enfoncé 2 secondes.Dans un délai de 2 minutes, appuyez sur le bouton WPS situé sur votre routeurMai 2011Ce symbole a été apposé conformément à la directive européenne 2002/96 sur la mise au rebut des équipements électriques et électroniques (directive WEEE - Waste Electrical and ElectronicEquipment). En cas de mise au rebut de ce produit dans un Etat membre de l'Union européenne, il doit être traité et recyclé conformément à cette directive.©2011 par NETGEAR, Inc. Tous droits réservés. NETGEAR et le logo NETGEAR sont des marques déposées de NETGEAR, Inc. aux Etats-Unis et/ou dans d'autres pays. Les autres marques ou noms de produits sont des marques commerciales ou des marques déposées de leurs détenteurs respectifs. Ces informations sontsusceptibles d'être modifiées sans préavis.L'adaptateur se connecte au réseau (l'opération peut prendre plusieurs minutes). Vos paramètres sont enregistrés dans un profil.Icône NETGEAR GenieLorsque vous installez votre adaptateur, l'icône NETGEAR Genie s'affiche dans la zone de notification Windows et sur le bureau. Cliquez sur cette icône pour ouvrir NETGEAR Genie et apporter des modifications ou établir une connexion vers un autre réseau sans fil. La couleur de l'icône indique le niveau de puissance de votre connexion sans fil, de zéro à cinq barres.Vert : 3 à 5 barres Jaune : 1 ou 2 barresRouge : 0 (zéro) barre, aucune connexionSi vous retirez l'adaptateur, NETGEAR Genie n'est pas disponible et l'icône ne s'affiche pas. Elle s'affiche à nouveau si vous réinsérez l'adaptateur.Assistance techniqueNous vous remercions d'avoir choisi les produits NETGEAR.Après l'installation de votre périphérique, notez le numéro de série inscrit surl'étiquette de votre produit. Il vous sera nécessaire pour enregistrer votre produit à l'adresse gear.fr/support/. Vous devez être enregistré pour utiliser le service d'assistance téléphonique. Nous vous recommandons vivement de procéder à l'enregistrement sur le site Web NETGEAR.Visitez le site gear.fr/support/ pour obtenir des mises à jour de produits et consulter le support Web.Pour en savoir plus sur l'installation, la configuration et l'utilisation de votre adaptateur USB sans fil, reportez-vous au Manuel de l'utilisateur .Pour consulter la déclaration de conformité complète, rendez-vous sur le site Web NETGEAR des déclarations de conformité pour l'UE à l'adresse : /app/answers/detail/a_id/11621/.Pour obtenir des informations sur la licence publique générale GNU (GPL),rendez-vous à l'adresse : /app/answers/detail/a_id/2649.。

Omron G3VM-101HR MOS FET Relay 数据手册说明书

1Higher power, 1.4-A switching with a 100-V load voltage, SOP package. Low 100-m Ω ON Resistance.•Continuous load current of 1.4 A. (Connection C: 2.8 A)■Application Examples■Terminal Arrangement/Internal Connections■List of Models*The AC peak and DC value are given for the load voltage.RoHS compliantNote: The actual product is marked differently from theimage shown here.•Communication equipment •Test & Measurement equipment •Data loggers •Industrial equipmentOMRON logo Pin 1 markModel name LOT.No.932101HRNote:The actual product is marked differently from the image shown here.Package type Contact formTerminalsLoad voltage (peak value) *ModelMinimum package quantityNumber per tube Number per tape and reelSOP61a(SPST-NO)Surface-mounting Terminals100 VG3VM-101HR75-G3VM-101HR (TR)-2,5002G3VM-101HRMOS FET Relays■Recommended Operating ConditionsUse the G3VM under the following conditions so that the Relay will operate properly.■Engineering Data■Safety Precautions•Refer to "Common Precautions" for all G3VM models.ItemSymbol MinimumTypical Maximum Unit Load voltage (AC peak/DC)V DD -- 100V Operating LED forward current I F 57.520mAContinuous load current (AC peak/DC)I O - -1.1A Ambient operating temperatureTa−20- 65°CLED forward current vs. Ambient temperatureContinuous load current vs. Ambient temperatureLED forward current vs. LED forward voltageContinuous load current vs. On-state voltage On-state resistance vs. Ambient temperature Trigger LED forward current vs. Ambient temperatureTurn ON, Turn OFF time vs. LED forward current Turn ON, Turn OFF time vs. Ambient temperatureCurrent leakage vs. Load voltageOutput terminal capacitance vs. Load voltageI F - TaAmbient temperature Ta (°C)L E D f o r w a r d c u r r e n t I F (m A )01020304050-40-2020406080100O Ambient temperature Ta (°C)C o n t i n u o u s l o a d c u r r e n t I O (A )12345F FLED forward voltage V F (V)L E D f o r w a r d c u r r e n t I F (m A )0.60.8 1.0 1.2 1.4 1.61.80.1110100I O - V ONOn-state voltage V ON (V)C o n t i n u o u s l o a d c u r r e n t I O (A )-1.5-1-0.500.511.5R ON - TaAmbient temperature Ta (°C)O n -s t a t e r e s i s t a n c e R O N (m Ω)050100150200I FT - TaAmbient temperature Ta (°C)T r i g g e r L E D f o r w a r d c u r r e n t I F T (m A )0.00.51.01.52.0-40-20020406080100t ON , t OFF - I FLED forward current I F (mA)T u r nO N , T u r n O F F t i m e t O N , t O F F (m s )0.010.1110Ambient temperature Ta (°C)T u r n O N , T u r n O F F t i m e t O N , t O F F (m s )0.010.1110-40-20020406080100I LEAK - V OFFLoad voltage (V)C u r r e n t l e a k a g e I L E A K (n A )0.00.51.01.52.0020406080100C OFF - V OFFLoad voltage (V)O u t p u t t e r m i n a l c a p a c i t a n c e C O F F /C O F F (0V )0.20.40.60.811.2010203040■Dimensions(Unit: mm)Note:Actual Mounting PadDimensions(Recommended Value, TOP VIEW)Note: The actual product is marked differently from the image shown here.Surface-mounting TerminalsWeight: 0.13 g• Application examples provided in this document are for reference only. In actual applications, confirm equipment functions and safety before using the product.• Consult your OMRON representative before using the product under conditions which are not described in the manual or applying the product to nuclear control systems, railroad systems, aviation systems, vehicles, combustion systems, medical equipment, amusement machines, safety equipment, and other systems or equipment that may have a serious influence on lives and property if used improperly. Make sure that the ratings and performance characteristics of the product provide a margin of safety for the system or equipment, and be sure to provide the system or equipment with double safety mechanisms.Cat. No. K180-E1-010412(0412)(O)Note: Do not use this document to operate the Unit.OMRON CorporationELECTRONIC AND MECHANICAL COMPONENTS COMPANYContact: /ecb。

VG-99 连接指南说明书

How Do I Optimize the VG-99 for My Playing Style?

3

®ÂØÒňή VG-99 How Do I Select a Patch?

There are 200 Preset and 200 User Patches in the VG-99. Here’s how to select them: 1 Turn the PATCH/VALUE dial to select a patch.

Roland Backstage member, you become part of the online Roland community and gain access to helpful tools and services. 4 Once you’re logged in, click the large Knowledge Base button. 5 On the Knowledge Base screen, enter “VG-99” in the Product field. 6 Click the Find button in the middle of the screen to browse the available VG-99 Knowledge Base articles.

How Do I Find VG-99 Articles in the Knowledge Base?

7

of the display. 9 Adjust the sensitivity for each of the remaining strings using the F2-F6 knobs.

国家电子NI 9227 四通道、五臂、24位、同时、渠道间隔离模拟输入模块操作指南和规格说明书

Caution Ensure that hazardous voltage wiring is performed only by qualified personnel adhering to local electrical standards. Caution Do not mix hazardous voltage circuits and human-accessible circuits on the same module. Caution Make sure that devices and circuits connected to the module are properly insulated from human contact.

Services /services

2 | | NI 9227 Operating Instructions and Specifications

Safety Guidelines

Operate the NI 9227 only as described in these operating instructions.

Figure 5. Input Circuitry for One Channel of the NI 9227

AI+C

Amplifier Prefilter

NI 9227

NI 9227 Operating Instructions and Specifications | © National Instruments | 9

Related Information

Agilent N2795A 96A 97A单端活动探头数据手册说明书

N2795A/96A/97A Single-ended Active ProbesData SheetKey Features• High resistance (1MΩ) and low capacitance (1 pF) input for low loading• Wide input dynamic range (±8V) and offset range (±12V for N2796A/97A, ±8V for N2795A)• Built-in headlight for better visibility while probing • Includes various probe tip accessories• Direct connection to AutoProbe interface (no power supply required)• Provides full system bandwidth with InfiniiVision and Infiniium oscilloscopes with bandwidths up to 1 GHz• N2797A for extreme temperature environmentalchamber testing at –40 to +85 °CThe N2795A/96A are low-cost, 1 and 2 GHz single-ended active probes with the AutoProbe interface (compatible with Agilent’s InfiniVision and Infiniium family of oscilloscopes). These probes integrate many of the characteristics needed for today’s general-purpose, high-speed probing - especially in digital system design, component design/characteriza-tion, and educational research applications. Its 1MΩ input resistance and extremely low input capacitance (1 pF) provide ultra low loading of the DUT. This, accompanied with superior signal fidelity, makes these probes useful for most of today’s digital logic voltages. And with their wide dynamic range(±8 V) and offset range (±12 V for N2796A/97A, ±8 V forN2795A), these probes can be used in a wide variety of applications.For high signal integrity probing, the N2795A 1 GHz andN2796A 2 GHz active probes are perfect complements to Agilent’s 500 MHz – 600 MHz and 1 GHz bandwidth scopes, respectively. The N2796A 2 GHz probe can also be used with Agilent’s 2 GHz or higher bandwidth Infiniium scope as a low cost alternative to InfiniiMax probes.Testing devices over extreme temperature ranges is quite common these days. The N2797A single-ended active probe is the industry’s first low-cost high input impedance active probe with rugged probe tips for environmental chamber test-ing of ICs and devices. The probe gives the ability to probe signals at drastic temperature swings ranging from –40 to +85 °C. The probe provides 1.5 GHz of bandwidth and a 2 m long cable.The N2795A/96A/97A are equipped with a pleasant white LED headlight to illuminate the circuit under test. The probes are powered directly by the InfiniiVision and Infiniium Autoprobe interface, eliminating the need for an additional power supply. The probes also come with a number of accessories that allow for easy connections to the circuit under test.N2795A/96A active probewith standard accessoriesA White LED headlight can be turned on to illuminatethe circuit under test for better visibility while probingN2797A with standardaccessoriesN2795AN2796AN2797AProbe bandwidth* (–3 db) 1 GHz 2 GHz 1.5 GHz**Risetime (calculated, 10-90%)350 psec 175 psec 233 psec System bandwidth (with Agilent oscilloscope)500/600 MHz (with Agilent’s 500/600 MHz InfiniiVision/ Infiniium oscilloscope)1 GHz (with Agilent’s 1 GHz InfiniiVision/Infiniium oscilloscope) 1 GHz (with Agilent’s 1 GHz InfiniiVision/Infiniium oscilloscope)Attenuation ratio (@DC)10:1 ± 0.5%Input dynamic range–8 V to +8 V (DC or peak AC)Non-destructive max input voltage –20 V to +20 VOffset range ±8 V±12 V ±12 VDC offset error (Output zero)< ±1 mVFlatness (at 25 °C)Typical 0.4 dB(100 kHz - 100 MHz) Typical 0.6 dB(100 MHz - 500 MHz) Typical 0.8 dB (500 MHz - 1 GHz) Typical 1.3 dB (1 GHz - 2 GHz)Typical 0.3 dB (10 Hz – 100 MHz) Typical 0.8 dB (100 MHz – 1 GHz) Typical 2.0 dB (1 GHz – 1.5 GHz)Flatness over temperature (–40 to +85 °C)Typical 0.3 dB (10 Hz – 100 kHz) Typical 0.6 dB(100 kHz – 100 MHz) Typical 0.8 dB(100 MHz – 500 MHz) Typical 2.0 dB (500 MHz – 1 GHz) Typical 2.5 dB (1 GHz – 1.5 GHz)Input resistance* 1 MΩ +0 %, –2.5 %1 MΩ ±3%Inputcapacitance 1 pFProbe noise < 2.5 mVrms (referred to input)Output impedance50 ΩN2795AN2796A N2797AInternal power Agilent Autoprobe Interface from scope(InfiniiVision and Infiniium)Cable length 1.3 m 2 m Probe weight Approx. 100 g Approx. 108 g Ambient operating Temperature 0 to 50 °C –40 to +85 °C Ambientnon-operating temperature –40 to 70 °C–40 to +85 °COperating humidity95% RH @ 40 °C Non-operating humidity 90% RH @ 65 °COperating altitude 4000 mESD8 kV HBM Standard accessories- 2 each spring probe tip - 2 rigid probe tip- 1 each flex nose clip adapter (red and black)- 1 each copper pad, 10x - 1 each Y -lead adapter, 10 cm - 1 each right angle ground, 5 cm - 1 each right angle ground, 10 cm - 2 each ground blade - 1 each offset ground - 1 each flex ground- 4 color coded rings (each yellow, green, blue and purple)- 10 each solderable tip - 5 each rigid probe tip - 2 each flex nose clip adapter (red and black) - 1 each pico hook tip (red and black)- 2 each Y-lead adapter, 9 cm (800 MHz)- 2 each Y-lead adapter, 6 cm (1 GHz)- 2 each right angle ground, 5 cm- 2 each ground blade - 4 color coded rings (each yellow, green, blue and purple)Others (included)-1 each accessory configuration card Compatible Agilent scopes Agilent InfiniiVision 3000 X-, 4000 X-, 5000, 6000, 7000 (except 6000 100MHz) and Infiniium 9000, 90000, 90000 X-Series (with N5442A)Agilent InfiniiVision 3000 X-, 4000 X- andInfiniium 9000, 90000 and 90000 X-/Q-Series (with N5442A)* denotes warranted electrical specifications after 20 minute warm-up, all others are typical ** typical 2 GHz, when used with rigid probe tip, ground blade and handheldUse flex nose clip adapters with the dual lead adapter to obtainaccess to IC leads or head connectors.The dual lead adapter allows you to easily connect the probe to a popular 0.1” pin header with 0.025” square pins.Model numberDescriptionN2795A 1 GHz single-ended active probe N2796A 2 GHz single-ended active probeN2797A 1.5 GHz extreme temperature single-ended active probeN2798AAccessory kit for N2797ACharacteristics100.0 k 10.00 k 1.000 k 100.0Frequency (Hz)Impedance(Ohms)Frequency response of N2796A (Vout/Vin)Time domain step response of N2796A (with Agilent MSO9404A) Voltage derating over frequency (N2796A)Input impedance over frequency (Red = measured, Blue = model) Measurement PlotsN2797A measuring a step signal over –40 to +90 °C, oscilloscopein infinite persistence mode/find/N2795AFor more information on AgilentTechnologies’ products, applications or services, please contact your local Agilent office. The complete list is available at:/find/contactus Americas Canada (877) 894 4414 Brazil (11) 4197 3600Mexico 01800 5064 800 United States (800) 829 4444 Asia Pacific Australia 1 800 629 485China 800 810 0189Hong Kong 800 938 693India 1 800 112 929Japan 0120 (421) 345Korea 080 769 0800Malaysia 1 800 888 848Singapore 180****8100Taiwan 0800 047 866Other AP Countries (65) 375 8100 Europe & Middle East Belgium 32 (0) 2 404 93 40 Denmark 45 45 80 12 15Finland 358 (0) 10 855 2100France 0825 010 700* *0.125 €/minute Germany 49 (0) 7031 464 6333 Ireland 1890 924 204Israel 972-3-9288-504/544Italy 39 02 92 60 8484Netherlands 31 (0) 20 547 2111Spain 34 (91) 631 3300Sweden 0200-88 22 55United Kingdom 44 (0) 118 927 6201For other unlisted countries:/find/contactus(BP-3-1-13)Product specifications and descriptions in this document subject to change without notice.© Agilent Technologies, Inc. 2010, 2013Printed in USA, August 17, 20135990-6480ENLAN eXtensions for Instruments puts the power of Ethernet and the Web inside your test systems. Agilent is a founding member of the LXI consortium.Agilent Channel Partners/find/channelpartners Get the best of both worlds: Agilent’s measurement expertise and product breadth, combined with channel partner convenience./qualityAdvancedTCA ® Extensions forInstrumentation and Test (AXIe) is an open standard that extends theAdvancedTCA for general purpose and semiconductor test. Agilent is a founding member of the AXIe consortium.PCI eXtensions for Instrumentation (PXI) modular instrumentation delivers a rugged, PC-based high-performance measurement and automation system.Quality Management SystemQuality Management Sys ISO 9001:2008DEKRA Certified /find/myagilentA personalized view into the information most relevant to you.myAgilentmy /find/AdvantageServices Accurate measurements throughout the life of your instruments./find/ThreeYearWarranty Agilent’s combination of product reliability and three-year warranty coverage is another way we help you achieve your business goals: increased confidence in uptime, reduced cost of ownership and greater convenience.。

防错技术(防)

0.6063789 60.63789%

0.3676954 36.76954%

0.1353353 13.53353%

0.0067481 0.0000456

0.67481% 0.00456%

不良数ppm 1000.00000 19811.13517 48794.37180 95207.85289

181351.17052 393621.05514 632304.57523 864664.73934 993251.93625 999954.41805

我们的期望

我们期望,我们有能力: –减少所有的缺陷,避免所有的问题! –如果缺陷不能减少,问题不能避免,我们期 望对我们不良的影响最小,损失最小!

来自ISO/TS16949的要求

7.1 产品实现的策划 注:有些顾客将项目管理或产品质量先期策划

作为一种产品实现的方法,产品质量先期策划包含 着防错和持续改进的概念,与找出错误不同,而且 是基于多方论证的方法。

伤害 • 丢失业务

消除错误的意义

• Zero Defects——零缺陷目标

– 减少各种错误-缺陷-损失 – 减少浪费(Muda) ——增加正向收获 – 降低废品率,减少返工 – 向消除质量检验迈进,降低检验成本

• 提高工作质量、强化效率 • 将操作人员的时间和精力解放出来,以从事更具有创造性和附

加价值的活动,从而使员工通过更多的参与获得成就感与满足 感 • 增强安全性并适应环境保护的需要 • 降低质量风险、优化产品性能、提高顾客满意度,获取最大竞 争优势

0.9831570 0.9666010

98.31570% 96.66010%

不良数ppm 3.40000 67.99780

169.98584 339.94278 679.77001 1698.55870 3394.23231 6773.56683 16842.97291 33398.97364

APW7073

Applications

• Graphic Cards

Ordering and Marking Information

APW7073

Assembly Material Handling Code Temperature Range Package Code

Package Code K : SOP - 14

Unit V V V V V

V

V

VRT, VOCSET, VEN VFB,V COMP, VSS

V PGND TJ

TSTG TSDR

RT, OCSET, EN to GND FB, COMP, SS to GND PGND to GND Junction Temperature Range Storage Temperature Maximum Lead Soldering Temperature, 10 Seconds

APW7073 K :

APW7073 XXXXX

XXXXX - Date Code

Note : A NPEC lead- free products contain molding compounds /die attach materials and 100% matte tin plate termination finish;

1500ppm by w eight). ANP EC res erves the right to ma ke cha nges to imp rove relia bility or m anufac turab ility witho ut no tice, and advise customers to obtain the latest version of relevant information to verify before placing orders.

pin到99%解决办法

pin不动的时候 可以用-N,但是容易漏码,建议开始pin后再改回-n

到99%重复,不出MM,可以点击左下角的开始-系统-超级用户模式,启用命令行模式。

输入命令:reaver -i mon0 -b xx:xx:xx:xx:xx:xx -v -a -n 回车

当你看到PIN到一定程度,窗口里的PIN码不变、进度百分比也不走,那么恭喜你碰到死循环了。

其他的就不用了。还可以加一个 –c

如果前四位猜对了,那么进度会跳到90.96%,否则是90.00%。不知是否正确?

1.每次pin不动了,记下前面四位数字,pin是先pin出前四位,然后才是后四位。最后一位是确认的。

2.下次打开pin,pin上一到两分钟点击停止。看看文件系统--usr--local--etc--reaver--里面有没有以mac地址加.wpc结尾的文件,有的话进度文件就生成了,可以进行下一步。没有的话继续进行此步。

一般将-S改成-n 然后后面再加-d 0 这样快又不会怎么漏码

个人用-n -d 0

-d2 每PIN一次后等待2秒后继续PIN下一个 d0就是不等待

-n 对目标AP总是发送NACK

-N 不发送NACK信息(如果一直pin不动,可以尝试这个参数)

-S 使用小DH关键值提高速度

pin码99%循环了

-----

原因是漏码了

-S改-n 最后加上-p XXXX

XXXX为前4位

如果不行的话可以修改WPC再加-n来测试前四位是否正确

漏码了,把参数里的-S改成-n 前面四位应该是对的,就不需要动了,

可以用-p命令也可以改.wpc文件然后重新pin

5.如果90.9%进程后死机或停机,可以使用-p参数

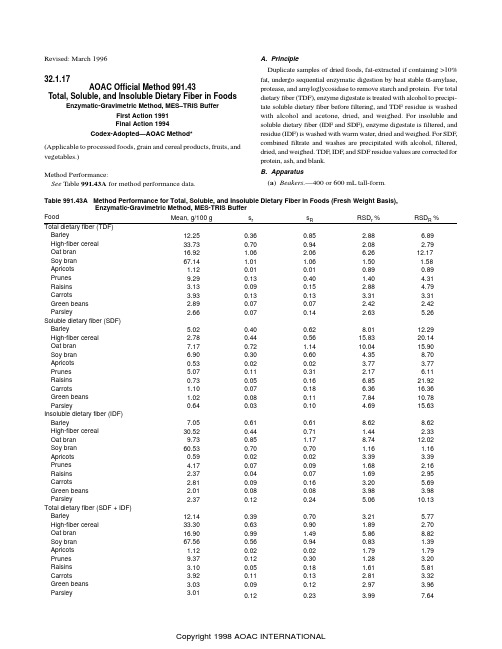

AOAC 991.43

Revised: March 1996 32.1.17AOAC Official Method 991.43Total, Soluble, and Insoluble Dietary Fiber in FoodsEnzymatic-Gravimetric Method, MES–TRIS BufferFirst Action 1991Final Action 1994Codex-Adopted—AOAC Method*(Applicable to processed foods, grain and cereal products, fruits, and vegetables.)Method Performance:See Table 991.43A for method performance data.A. PrincipleDuplicate samples of dried foods, fat-extracted if containing >10%fat, undergo sequential enzymatic digestion by heat stable α-amylase,protease, and amyloglycosidase to remove starch and protein. For total dietary fiber (TDF), enzyme digestate is treated with alcohol to precipi-tate soluble dietary fiber before filtering, and TDF residue is washed with alcohol and acetone, dried, and weighed. For insoluble and soluble dietary fiber (IDF and SDF), enzyme digestate is filtered, and residue (IDF) is washed with warm water, dried and weighed. For SDF,combined filtrate and washes are precipitated with alcohol, filtered,dried, and weighed. TDF, IDF, and SDF residue values are corrected for protein, ash, and blank.B. Apparatus(a ) Beakers.—400 or 600 mL tall-form.Table 991.43A Method Performance for Total, Soluble, and Insoluble Dietary Fiber in Foods (Fresh Weight Basis),Enzymatic-Gravimetric Method, MES-TRIS BufferFood Mean, g/100 g s r s R RSD r%RSD R % Barley 12.250.360.85 2.88 6.89High-fiber cereal 33.730.700.94 2.08 2.79 Oat bran 16.92 1.06 2.06 6.2612.17 Soy bran 67.14 1.01 1.06 1.50 1.58 Apricots 1.120.010.010.890.89 Prunes 9.290.130.40 1.404.31 Raisins 3.130.090.15 2.88 4.79 Carrots 3.930.130.13 3.31 3.31 Green beans 2.890.070.07 2.42 2.42 Parsley 2.660.070.14 2.635.26Soluble dietary fiber (SDF) Barley 5.020.400.628.0112.29 High-fiber cereal 2.780.440.5615.83 20.14 Oat bran 7.170.72 1.1410.04 15.90 Soy bran6.900.300.60 4.358.70 Apricots 0.530.020.02 3.77 3.77 Prunes 5.070.110.31 2.17 6.11 Raisins 0.730.050.16 6.8521.92 Carrots 1.100.070.18 6.3616.36 Green beans 1.020.080.117.8410.78 Parsley 0.640.030.10 4.6915.63 Insoluble dietary fiber (IDF) Barley 7.050.610.618.628.62 High-fiber cereal 30.520.440.71 1.44 2.33 Oat bran9.730.85 1.178.7412.02 Soy bran 60.530.700.70 1.16 1.16 Apricots 0.590.020.02 3.39 3.39 Prunes 4.170.070.09 1.68 2.16 Raisins 2.370.040.07 1.69 2.95 Carrots 2.810.090.16 3.20 5.69 Green beans 2.010.080.08 3.98 3.98 Parsley 2.370.120.24 5.0610.13 Total dietary fiber (SDF + IDF) Barley 12.140.390.70 3.21 5.77 High-fiber cereal 33.300.630.90 1.89 2.70 Oat bran 16.900.99 1.49 5.868.82 Soy bran 67.560.560.940.83 1.39 Apricots 1.120.020.02 1.79 1.79 Prunes 9.370.120.30 1.28 3.20 Raisins 3.100.050.18 1.61 5.81 Carrots 3.920.110.13 2.81 3.32 Green beans 3.030.090.12 2.97 3.96 Parsley 3.010.120.23 3.997.64(b ) Filtering crucible.—With fritted disk, coarse, ASTM 40–60µm pore size, Pyrex 60 mL (Corning No. 36060 Bchner, Corning,Inc., Science Products, Corning, NY 14831, USA, or equivalent).Prepare as follows. Ash overnight at 525° in muffle furnace. Let furnace temperature fall below 130° before removing crucibles.Soak crucibles 1 h in 2% cleaning solution at room temperature.Rinse crucibles with H 2O and then deionized H 2O; for final rinse,use 15 mL acetone and then air-dry. Add ca 1.0 g Celite to dry crucibles, and dry at 130° to constant weight. Cool crucible ca 1h in desiccator, and record weight, to nearest 0.1 mg, of crucible plus Celite.(c ) V acuum system.—V acuum pump or aspirator with regulating device. Heavy walled filtering flask, 1 L, with side arm. Rubber ring adaptors, for use with filtering flasks.(d ) Shaking water baths.—(1) Capable of maintaining 98 2°,with automatic on-and-off timer. (2) Constant temperature, adjust-able to 60°.(e ) Balance.—Analytical, sensitivity 0.1 mg.(f ) Muffle furnace.—Capable of maintaining 525 5°.(g ) Oven.—Capable of maintaining 105 and 130 3°.(h ) Desiccator .—With SiO 2 or equivalent desiccant. Biweekly,dry desiccant overnight at 130°.(i ) pH meter .—Temperature compensated, standardized with pH 4.0, 7.0, and 10.0 buffer solutions.(j ) Pipetters .—With disposable tips, 100–300 µL and 5 mL capacity.(k ) Dispensers.—Capable of dispensing 15 0.5 mL for 78%ethanol, 95% ethanol, and acetone; 40 0.5 mL for buffer.(l ) Magnetic stirrers and stir bars.C. ReagentsUse deionized water throughout.(a ) Ethanol solutions.—(1) 85%. Place 895 mL 95% ethanol into 1 L volumetric flask, dilute to volume with H 2O. (2) 78%. Place 821 mL 95% ethanol into 1 L volumetric flask, dilute to volume with H 2O.(b ) Heat-stable α-amylase solution.—Catalog Number A 3306,Sigma Chemical Co., St. Louis, MO 63178, USA, or Termamyl 300L, Catalog Number 361-6282, Novo-Nordisk, Bagsvaerd, Den-mark, or equivalent.(c ) Protease.—Catalog Number P 3910, Sigma Chemical Co, or equivalent. Prepare 50 mg/mL enzyme solution in MES/TRIS buff-er fresh daily.(d ) Amyloglucosidase solution .—Catalog Number AMG A9913,Sigma Chemical Co, or equivalent. Store at 0–5°.(e ) Diatomaceous earth.—Acid washed (Celite 545 AW, No.C8656, Sigma Chemical Co. or equivalent).(f ) Cleaning solution .—Liquid surfactant-type laboratory cleaner, designed for critical cleaning (Micro ®, International Prod-ucts Corp., Burlington, NJ 08601, USA, or equivalent). Prepare 2%solution in H 2O.(g ) MES .—2-(N -Morpholino)ethanesulfonic acid (No. M-8250,Sigma Chemical Co., or equivalent.)(h ) TRIS.—Tris(hydroxymethyl)aminomethane (No. T-1503,Sigma Chemical Co., or equivalent).(i ) MES–TRIS buffer solution.—0.05M MES, 0.05M TRIS, pH 8.2 at 24°. Dissolve 19.52 g MES and 12.2 g TRIS in 1.7 L H 2O.Adjust pH to 8.2 with 6N NaOH, and dilute to 2 L with H 2O.(Note: It is important to adjust pH to 8.2 at 24°. However, if buffer temperature is 20°, adjust pH to 8.3; if temperature is 28°,adjust pH to 8.1. For deviations between 20 and 28°, adjust by interpolation.)(j ) Hydrochloric acid solution.—0.561N . Add 93.5 mL 6N HCl to ca 700 mL H 2O in 1 L volumetric flask. Dilute to 1 L with H 2O.D. Enzyme PurityTo ensure absence of undesirable enzymatic activities and pres-ence of desirable enzymatic activities, run standards listed in Table 991.43B each time enzyme lot changes or at maximum interval of 6months.E. Sample Preparation and DigestionPrepare samples as in 985.29E (see 45.4.07) (if fat content of sample is unknown, defat before determining dietary fiber). For high sugar samples, desugar before determining dietary fiber by extract-ing 2–3 times with 85% ethanol, 10 mL/g, decanting, and then drying overnight at 40°.Run 2 blanks/assay with samples to measure any contribution from reagents to residue.Weigh duplicate 1.000 0.005 g samples (M 1 and M 2), accurate to 0.1 mg, into 400 mL (or 600 mL) tall-form beakers. Add 40 mL MES–TRIS buffer solution, pH 8.2, to each. Stir on magnetic stirrer until sample is completely dispersed (to prevent lump formation,which would make test material inaccessible to enzymes).Add 50 µL heat-stable α-amylase solution, stirring at low speed.Cover beakers with Al foil, and incubate in 95–100° H 2O bath 15min with continuous agitation. Start timing once bath temperature reaches 95° (total of 35 min is normally sufficient).Remove all beakers from bath, and cool to 60°. Remove foil.Scrape any ring from inside of beaker and disperse any gels in bottom of beaker with spatula. Rinse beaker walls and spatula with 10 mL H 2O.Add 100 µL protease solution to each beaker. Cover with Al foil,and incubate 30 min at 60 1° with continuous agitation. Start timing when bath temperature reaches 60°.Remove foil. Dispense 5 mL 0.561N HCl into beakers while stirring. Adjust pH to 4.0–4.7 at 60°, by adding 1N NaOH solution or 1N HCl solution. (Note: It is important to check and adjust pH while solutions are 60° because pH will increase at lower tempera-tures.) (Most cereal, grain, and vegetable products do not require pH adjustment. Once verified for each laboratory, pH checking procedure can be omitted. As a precaution, check pH of blank routinely; if outside desirable range, check samples also.)Add 300 µL amyloglucosidase solution while stirring. Cover with Al foil, and incubate 30 min at 60 1° with constant agitation. StartTable 991.43B Standards for Testing Enzyme Activity Standard Activity Tested Weight of Standard, gExpected Recovery, (%)Citrus pectin Pectinase 0.1–0.295–100 Arabinogalactan Hemicellulase 0.1–0.295–100β-Glucan β-Glucanase 0.1–0.295–100Wheat starch α-Amylase + AMG 1.0 0–1 Corn starch α-Amylase + AMG 1.00–1Casein Protease0.30–1timing once bath reaches 60°.F. Determination of Total Dietary FiberTo each digested sample, add 225 mL (measured after heating) 95% ethanol at 60°. Ratio of ethanol to sample volume should be 4:1. Remove from bath, and cover beakers with large sheets of Al foil. Let precipitate form 1 h at room temperature.Wet and redistribute Celite bed in previously tared crucible B(b), using 15 mL 78% ethanol from wash bottle. Apply suction to crucible to draw Celite onto fritted glass as even mat.Filter alcohol-treated enzyme digestate through crucible. Using wash bottle with 78% ethanol and rubber spatula, quantitatively transfer all remaining particles to crucible. (Note: If some samples form a gum, trapping the liquid, break film with spatula.)Using vacuum, wash residue 2 times each with 15 mL portions of 78% ethanol, 95% ethanol, and acetone. Dry crucible containing residue overnight in 105° oven. Cool crucible in desiccator ca 1 h. Weigh crucible, containing dietary fiber residue and Celite, to near-est 0.1 mg, and calculate residue weight by subtracting weight of dry crucible with Celite, B(b).Use one duplicate from each sample to determine protein, by method 960.52 (see 12.1.07), using N× 6.25 as conversion factor. For ash analysis, incinerate second duplicate 5 h at 525°. Cool in desiccator, and weigh to nearest 0.1 mg. Subtract weight of crucible and Celite, B(b), to determine ash weight.G. Determination of Insoluble Dietary FiberWet and redistribute Celite bed in previously tared crucible, B(b), using ca 3 mL H2O. Apply suction to crucible to draw Celite into even mat. Filter enzyme digestate, from E, through crucible into filtration flask. Rinse beaker, and then wash residue 2 times with 10 mL 70° H2O. Combine filtrate and water washings, transfer to pretared 600 mL tall-form beaker, and reserve for determination of soluble dietary fiber, H. Using vacuum, wash residue 2 times each with 15 mL portions of 78% ethanol, 95% ethanol, and acetone. (Note: Delay in washing IDF residues with 78% ethanol, 95% ethanol, and acetone may cause inflated IDF values.)Use duplicates to determine protein and ash as in F.H. Determination of Soluble Dietary FiberProceed as for insoluble dietary fiber determination through in-struction to combine the filtrate and water washings in pretared 600 mL tall-form beakers. Weigh beakers with combined solution of filtrate and water washings, and estimate volumes.Add 4 volumes of 95% ethanol preheated to 60°. Use portion of 60° ethanol to rinse filtering flask from IDF determination. Alterna-tively, adjust weight of combined solution of filtrate and water washings to 80 g by addition of H2O, and add 320 mL 60° 95% ethanol. Let precipitate form at room temperature 1 h.Follow TDF determination, F, from “Wet and redistribute Celite bed . . . .”I. CalculationsBlank (B, mg) determination:B = [(BR1 + BR2)/2] – P B – A Bwhere BR1 and BR2 = residue weights (mg) for duplicate blank determinations; and P B and A B = weights (mg) of protein and ash, respectively, determined on first and second blank residues. Dietary fiber (DF, g/100 g) determination:DF = {[(R1 + R2)/2] – P – A – B}/[(M1 + M2)/2] × 100 where R1 and R2 = residue weights (mg) for duplicate samples; P and A = weights (mg) of protein and ash, respectively, determined on first and second residues; B = blank weight (mg); and M1 and M2 = weights (mg) for samples.Total dietary fiber determination: Determine either by independent analysis, as in F, or by summing IDF and SDF, as in G and H. Reference: J. AOAC Int. 75, 395(1992).*Adopted as a Codex Defining Method for gravimetry/enzymatic di-gestion of total dietary fiber in infant formula and follow-up for-mula.。

Tektronix AFG31000系列高性能模拟函数生成器说明书

Arbitrary Function GeneratorsAFG31000 Series DatasheetThe Tektronix AFG31000 Series is a high-performance AFG with built-in arbitrary waveform generation, real-time waveform monitoring, and the largest touchscreen on the market. Providing advanced waveform generation and programming capabilities, waveform verification, and a modern touch-screen interface, the new AFG31000 is sure to delight and simplify the job of every researcher and engineer.Key performance specifications1 or2 channel modelsOutput amplitude range 1 mV P-P to 10 V P-Pinto 50 Ω loadsBasic (AFG) mode:25 MHz, 50 MHz, 100 MHz, 150 MHz, or 250 MHz sine waveforms250 MSa/s, 1 GSa/s or 2 GSa/s sample rates14-bit vertical resolutionBuilt-in waveforms include sine, square, ramp, pulse, noise, andother frequently used waveformsSweep, Burst, and Modulation modes (AM, FM, PM, FSK, andPWM)Advanced (Sequence) mode:Continuous mode (optional Sequence, Triggered and Gatedmodes)16 Mpts arbitrary waveform memory on each channel (128 Mptsoptional)Up to 256 steps in sequence mode with loop, jump and wait events Variable sampling clock 1 µSa/s to 2 GSa/sKey featuresPatented InstaView ™ technology enables engineers to see the actual waveform at the Device Under Test (DUT) in real time, without the need of an oscilloscope and probe, eliminating the uncertainty causedby mismatched impedanceSequencing option adds the ability to program long, complexwaveforms with up to 256 stepsThe 9-inch capacitive touch screen works like a smart phone and hasshort-cuts to frequently used settingsBuilt-in ArbBuilder lets you create and edit arbitrary waveforms on theinstrument, eliminating the need to connect to a PCOutputs are protected from over voltage and current to minimizepotential instrument damageCompatible with TekBench ™ software to help students set up, control,and analyze test results in the labApplicationsAdvanced researchClock and system synchronizationReplication of real world signalsComponent and circuit characterization and validationEmbedded circuit design and testGeneral purpose signal generationBasic and Advanced ModesThe AFG31000 series is the industry’s first arbitrary function generator with full function Basic (AFG) and Advanced (Sequence) modes.In Basic mode, the AFG31000 generates traditional functions and arbitrary waveforms. The touchscreen and front-panel controls make it simple to set up.Basic mode lets you change frequency without the need to worry about waveform length and sample rate. This feature is useful in analog designs that characterize filter/amplifier frequency responses or in digital designs where clock rates change frequently.Key settings are visible at a glance, and are easy to adjust using touch, numeric keypad, or rotary controlsNew with the AFG31000, Advanced mode provides the ability to generate multiple waveforms with complex timing. In this mode, you can compose a list (or a sequence) of 1 to 256 waveforms, with total waveform length up to 16 Mpts/ch (128 Mpts/ch optional) and define the ouput sequence of these waveforms. Repeat, go-to, wait, jump, and triggered events are all supported and the large memory provides space to store many waveforms or long waveforms.This feature is very useful in applications where many test cases need to be performed sequentially. Instead of loading the test cases one by one, you can put all of them in a sequence and load at one time, switching from one to another seamlessly to greatly improve the test efficiency.Advanced mode lets you build complex waveform sequences with flexible step controlsSequenced sine waveforms with different frequency and amplitude. Additionally, Advanced mode uses variable sample rate technology. Every sample in a waveform is output once and only once in each cycle, synchronized to the sample rate. Since there is no skipping or repetition, all details in the waveforms are kept. This feature is very useful for applications in which signal fidelity is extremely critical, such as IQ modulation and pulse train generation.InstaView™ technology shows the actual waveform at the DUTMost waveform generators assume they are driving a 50 Ω impedance. However, most devices under test do not have a 50 Ω impedance. This mismatch results in an inconsistency between the waveform as set on the AFG and the signal at the DUT.DatasheetWith InstaView turned off, the AFG31000 works like a traditional function generator. Due to an impedance mismatch, the AFG display shows a different waveform from the one observed at the DUT.With the patented InstaView ™technology, the AFG31000 Series can display the actual waveform at the DUT, instead of just the nominalwaveform as set on the AFG. The waveform displayed on the AFG instantly responds to changes in frequency, amplitude, waveform shape, andimpedance changes at the DUT. InstaView helps eliminate the uncertainty and measurement risk caused by impedance mismatches, without requiringadditional cables, instruments, or effort.With InstaView turned on, the AFG31000 shows the waveform as observed at the DUT.A large touch screen and smart user interfaceThe large 9-inch capacitive touch screen displays all related settings and parameters on a single screen. Similar to smart devices, you can tap or swipe to easily select, browse, locate and change settings and parameters.Frequently-used functions are immediately accessible. Familiar buttons and rotary knob controls are available for more traditional navigation.Frequently used settings are easy to access from the swipe-up menuAFG31000 SeriesBuilt-in ArbBuilder tool makes creating and editing arbitrary waveforms easier than ever In the past, you needed a PC with waveform editing software to create or edit your arbitrary waveforms. The waveform would then need to be downloaded to the AFG using either a USB stick or a data cable connection. The process was time-consuming, especially when waveforms required frequent changes.ArbBuilder is a built-in application on the AFG31000 series that lets you create and edit your arbitrary waveforms directly on the generator. You can create arbitrary waveforms with the Equation Editor tool or start from a library of standard templates. Thanks to the large capacitive touch screen, you can drag, pinch and zoom to get the detail you need.You can quickly replicate real-world waveforms captured with oscilloscopes or created by third-party software by loading CSV format data files directly into ArbBuilder from a USB memory stick.Creating an arbitrary waveform using the easy touch screen interfaceSimplified multi-unit synchronizationMost applications need one or two channels of output, but some applications require more channels. For example, in order to simulate 3-phase power signals, engineers often need to synchronize three 2-channel generators; one for the voltage and current on each phase. To do this used to be time-consuming, as it required many cable connections between the AFG units, and making changes in deep branches of the menu trees on all instruments.The AFG31000 simplifies this process with an onscreen wizard that leads you through the process of making cable connections and configuring settings to synchronize multiple generators.An on-screen wizard guides you through the process of multiple-unit synchronizationUpgradability protects your investmentThe AFG31000 provides upgrade options for bandwidth, memory extension, and sequence mode support. These options can be installed at the factory or at any time after purchase. This upgradability helps to reduce the product ownership threshold. And when your test requirements change, you can purchase and install upgrade software licenses to add higher performance features. Upgrades eliminate the concern about the return on investment during the instrument lifetime.DatasheetAFG31000 SeriesSpecificationsAll specifications are guaranteed unless noted otherwise. All specifications apply to all models unless noted otherwise.Model overviewOutput characteristicsAmplitudeOutput impedance50 ΩLoad impedance setting Selectable: 50 Ω, 1 Ω to 10.0 kΩ, High Z (Adjusts displayed amplitude according to selected load impedance)Isolation42 Vpk maximum to earth groundShort-circuit protection Signal outputs are robust against permanent shorts against floating groundOvercurrent protection When incoming current is greater than 250 mA, the output channels are protected with relays that disconnect the AFG from thedevice under test. Connection can be resumed by user after removing the incoming currentGeneral characteristics - Basic modeBasic (AFG)Run modes Continuous, Modulation, Sweep and BurstStandard waveforms Sine, Square, Pulse, Ramp, More (Noise, DC,Sin(x)/x, Gaussian, Lorentz, Exponential Rise, Exponential Decay, Haversine )Arbitrary waveformsSampling clock: 250 MSa/s, 1 GSa/s or 2 GSa/s (model and waveform length apply)Vertical resolution: 14 bitsWaveform length: 2 to 131,072 pointsSineFrequency rangeEffective maximum frequency outAmplitude flatness (1 V P-P ,relative to 1 kHz)Amplitude flatness (1 V P-P ,relative to 1 kHz), typicalHarmonic distortion (1 V P-P ),typicalDatasheetTHD, typical≤ 0.04%, 10 Hz to 20 kHz, 1 V P-PSpurious noise (1 V P-P ), typicalPhase noise, typical< -125 dBc/Hz at 20 MHz, 10 kHz offset, 1 V P-PResidual clock noise, all models -63 dBmSquareFrequency rangeRise/fall time, typicalOvershoot, typical< 3%Jitter (RMS), typical2.5 psRampFrequency rangeLinearity, typical (1 kHz, 1 V P-P ,100% symmetry)Symmetry0% to 100%AFG31000 SeriesGeneral characteristics - Basic modePulseFrequency rangePulse widthPulse width resolution 10 ps or 5 digitsPulse Duty 0.001% to 99.999% (limitations of pulse width apply)Edge transition timeEdge transition time resolution 10 ps or 4 digits Lead delay rangeLead delay resolution 10 ps or 8 digits Overshoot, typical < 2%Jitter (RMS), typical 2.5 psDCRange (into 50 Ω)Resolution (into 50 Ω) 1 mV or 4 digits Accuracy ± (1% of |setting | +1mV)NoiseBandwidth (-3 dB)Noise typeWhite GaussianInternal noiseDatasheetGeneral characteristics - Basic modeOther waveformsFrequency rangeArbitrary waveformsFrequency rangeEffective analog bandwidth (-3 dB)Waveform length2 to 131,072Sample rateVertical resolution14 bitRise/fall time, typicalJitter (RMS), typical2.5 psModulationAM, FM, PMAM modulation depth0.0 % to 120 %AM modulation resolution0.1%AFG31000 SeriesGeneral characteristics - Basic modeMinimum FM peak deviationDCMaximum FM peak deviationPM phase deviation range0° to 180°PM phase resolution0.1°FSKPWMSweepType Linear, Logarithmic Waveforms All, except Pulse, Noise, DC Sweep time 1 ms to 500 s Hold/return time0 s to 500 s Maximum total sweep time500 sAccuracy, typical: ≤ 0.4%Minimum start/stop frequency All except ARB: 1 μHzARB: 1 mHzMaximum start/stop frequencyDatasheetGeneral characteristics - Basic modeBurstWaveform All except Noise, DC Type Triggered, gatedBurst count 1 to 1,000,000 cycles or Infinite Intenal trigger rate 1 μs to 500.0 sGate and trigger sources Internal, external, remote interfaceInstaView ™Waveforms All except noise Cable (channel output to load)50 Ω BNC to BNCRun modeContinuous in Basic modeMaximum measurement range (DC + peak AC voltage)DC level measurementAmplitude measurementBandwidth (-3 dB)500 MHzFlatness, sine, 1 V P-P , into 50 ohm, relative to 1 kHz,typicalCable propagation delay measurement, typicalAFG31000 SeriesGeneral characteristics - Basic modeGeneral characteristics - Advanced modeWaveform memory size 16 Mpts (128 Mpts optional) each channel Run modeStandard: ContinuousOptional: Sequence, Triggered, GatedNumber of waveform entriesContinuous, Triggered, Gated: 1 Sequence: 1 to 256Minimum waveform length 168 pts Waveform granularity 1 pt Vertical resolution 14 bitsJump/trigger events External trigger (rising or falling edge), manual trigger, timer, SCPI commands Repeat count 1 to 1,000,000 or infinite Timer range 2 µS to 3600 S Timer resolution 4 ns or 8 digitsVariable sample rateRise/Fall time, typicalOvershoot, typical< 2%Level flatness, typical (sine, 1 V P-P ,relative to 1 kHz)Harmonic distortion, typical (sine with 64 pts/cycle, 1 V P-P )DatasheetSpurious, typical (sine with 64 pts/cycle, 1 V P-P )Spurious free dynamic range,typical (sine with 64 pts/cycle,1 V P-P )Phase noise, typical (sine with 64 pts/cycle, 1 V P-P , at 10 kHz offset)Skew controlRange -320 ns to 320 ns (channel 1 to channel 2 on dual channel models, at maximum sample rate)Resolution 100 ps or 4 digits Accuracy, typical ±(1% of |setting| + 500 ps)Initial skew, typical< 500 psSystem characteristicsOutput Frequency ResolutionFrequency accuracy±10-6 of setting (all except ARB), 0 °C to 50 °C (32 °F to 122 °F)±10-6 of setting ± 1 μHz (ARB), 0 °C to 50 °C (32 °F to 122 °F)Aging ±1.0 x 10-6 per yearPhaseRange -180° to +180°Resolution0.01° (sine)0.1° (other waveforms)Remote program interface GPIB, Ethernet 10BASE-T / 100BASE-TX / 1000BASE-T, USB 2.0Maximum configuration times,typicalPower sourceSource100-240 V, 47-63 Hz 115 V, 360-440 HzConsumption120 WAFG31000 SeriesGeneral characteristics - Advanced modeWarm up time, typical 20 minutes minimum Power on self diagnosis time < 24 s Acoustic noise < 50 dBADisplay9-inch capacitive touch screen with 800 * 480 resolutionUser interface and Help languages English, French, German, Japanese, Korean, Simplified and Traditional Chinese, Russian (user selectable)Auxiliary input characteristicsExternal modulation input, channel 1 and channel 2Input rangeInput impedance 5.2 kΩFrequency range 125 kHz (1 MSa/s)External Trigger inputLevel TTL compatible Impedance10 kΩMinimum pulse width 100 nsSlopePositive or negative selectable Trigger delay range 0 ns to 85 s Trigger delay resolution 100 ps or 5 digitsTrigger latency, typical 390 ns (trigger input to signal output)Jitter (RMS), typical 100 ps (signal output, with external trigger input in burst mode)10 MHz reference clock inputImpedance 1 kΩInput couplingACRequired input voltage swing 100 mV P-P to 5 V P-P Lock range10 MHz ±35 kHz Channel 1 external add inputImpedance 50 ΩInput range -1 V to +1 V (DC + peak AC)BandwidthDC to 10 MHz (-3 dB) at 1 V P-P DatasheetSystem characteristicsAFG31000 Series Auxiliary output characteristicsChannel 1 trigger outputLevel Positive TTL level pulse into 1 kΩImpedance50 ΩJitter, RMS, typical10 ps for all modelsOutput frequency10 MHz reference clock outImpedance50 Ω, AC coupledAmplitude 1.2 V P-P into 50 Ω loadPhysical characteristicsDimensionsHeight191.8 mm (7.55 in.)Width412.8 mm (16.25 in.)Depth143.3 mm (5.64 in.)WeightNet 4.7 kg (10.4 lb.)Shipping7.0 kg (15.4 lb.)EMC, environment, and safetyTemperatureOperating0 °C to +50 °C (32 °F to 122 °F)Nonoperating-30 °C to +70 °C (-22 °F to 158 °F)HumidityOperating≤ 80%, 0 °C to 40 °C (32 °F to104 °F)≤ 60%, > 40°C to 50°C (104 °F to 122 °F), noncondensingNonoperating5% to 90%, < 40 °C (< 104 °F), noncondensing5% to 80%, ≥ 40 °C to 60 °C (≥ 104 °F to 140 °F), noncondensing5% to 40%, > 60 °C to 70 °C (> 140 °F to 158 °F), noncondensingAltitudeOperating Up to 3,000 m (9,842 ft.)Nonoperating Up to 12,000 m (39,370 ft.)EMC compliance EN61326-1:2013, EN 61326-2-1:2013European Union EU Council Directive 2004/108/ECDatasheetEMC, environment, and safetySafety UL 61010-1:2004CAN/CSA C22.2 No. 61010-1:2004IEC 61010-1:2001Over-temperature protection Instrument is protected from over-temperature by turning off outputsAFG31000 Series Ordering InformationModelsAFG31021 1 μHz to 25 MHz sine wave, 1-channel arbitrary function generatorAFG31022 1 μHz to 25 MHz sine wave, 2-channel arbitrary function generatorAFG31051 1 μHz to 50 MHz sine wave, 1-channel arbitrary function generatorAFG31052 1 μHz to 50 MHz sine wave, 2-channel arbitrary function generatorAFG31101 1 μHz to 100 MHz sine wave, 1-channel arbitrary function generatorAFG31102 1 μHz to 100 MHz sine wave, 2-channel arbitrary function generatorAFG31151 1 μHz to 150 MHz sine wave, 1-channel arbitrary function generatorAFG31152 1 μHz to 150 MHz sine wave, 2-channel arbitrary function generatorAFG31251 1 μHz to 250 MHz sine wave, 1-channel arbitrary function generatorAFG31252 1 μHz to 250 MHz sine wave, 2-channel arbitrary function generatorOptionsFactory optionsMEM Extends arbitrary waveform memory to 128 Mpts/ch in Advanced modeSEQ Enables Sequence, Triggered and Gated modes in Advanced modeFeature upgrade after purchaseThe AFG31000 products offer several ways to easily add functionality after the initial purchase.DatasheetPower plug optionsOpt. A0North America power plug (115 V, 60 Hz)Opt. A1Universal Euro power plug (220 V, 50 Hz)Opt. A2United Kingdom power plug (240 V, 50 Hz)Opt. A3Australia power plug (240 V, 50 Hz)Opt. A5Switzerland power plug (220 V, 50 Hz)Opt. A6Japan power plug (100 V, 50/60 Hz)Opt. A10China power plug (50 Hz)Opt. A11India power plug (50 Hz)Opt. A12Brazil power plug (60 Hz)Opt. A99No power cordLanguage optionsOpt. L0English front panel overlay (default)Opt. L1French front panel overlayOpt. L2Italian front panel overlayOpt. L3German front panel overlayOpt. L4Spanish front panel overlayOpt. L5Japanese front panel overlayOpt. L6Portuguese front panel overlayOpt. L7Simplified Chinese front panel overlayOpt. L8Traditional Chinese front panel overlayOpt. L9Korean front panel overlayOpt. L10Russian front panel overlayOpt. L99No front panel overlayService optionsOpt. C3Calibration Service 3 YearsOpt. C5Calibration Service 5 YearsOpt. D1Calibration Data ReportOpt. D3Calibration Data Report 3 Years (with Opt. C3)Opt. D5Calibration Data Report 5 Years (with Opt. C5)Opt. R5Repair Service 5 Years (including warranty)Opt. T3Three Year Total Protection Plan, includes repair or replacement coverage from wear and tear, accidental damage, ESD or EOSplus preventative maintenance. Including a 5 day turnaround time and priority access to customer support Opt. T5Five Year Total Protection Plan, includes repair or replacement coverage from wear and tear, accidental damage, ESD or EOSplus preventative maintenance. Including a 5 day turnaround time and priority access to customer supportAccessories are not covered by the instrument warranty and Service Offerings.AccessoriesStandard accessories-----AFG31000 Series Arbitrary Function Generator Compliance, Installation, and Safety Instructions 012-1732-xx BNC cable shielded, 3 ft.174-4401-xx USB cable, A to B, 3 ft.-----Power cord-----NIST-traceable calibration certificate-----Three-year warranty on parts and laborRecommended accessories012-1732-xx BNC cable shielded, 3 ft.012-0991-xx GPIB cable, double shielded011-0049-02 50 Ω BNC terminatorACD4000B Soft transit caseHCTEK54Hard transit case (requires ACD4000B)WarrantyProduct warranty Three-year warranty on parts and laborTektronix is registered to ISO 9001 and ISO 14001 by SRI Quality System Registrar.Product(s) complies with IEEE Standard 488.1-1987, RS-232-C, and with Tektronix Standard Codes and Formats.Product Area Assessed: The planning, design/development and manufacture of electronic Test and Measurement instruments.AFG31000 SeriesDatasheetASEAN / Australasia (65) 6356 3900 Austria 00800 2255 4835*Balkans, Israel, South Africa and other ISE Countries +41 52 675 3777 Belgium 00800 2255 4835*Brazil +55 (11) 3759 7627 Canada180****9200Central East Europe and the Baltics +41 52 675 3777 Central Europe & Greece +41 52 675 3777 Denmark +45 80 88 1401Finland +41 52 675 3777 France 00800 2255 4835*Germany 00800 2255 4835*Hong Kong 400 820 5835 India 000 800 650 1835 Italy 00800 2255 4835*Japan 81 (3) 6714 3086 Luxembourg +41 52 675 3777 Mexico, Central/South America & Caribbean 52 (55) 56 04 50 90Middle East, Asia, and North Africa +41 52 675 3777 The Netherlands 00800 2255 4835*Norway 800 16098People's Republic of China 400 820 5835 Poland +41 52 675 3777 Portugal 80 08 12370Republic of Korea +822 6917 5084, 822 6917 5080 Russia & CIS +7 (495) 6647564 South Africa +41 52 675 3777Spain 00800 2255 4835*Sweden 00800 2255 4835*Switzerland 00800 2255 4835*Taiwan 886 (2) 2656 6688 United Kingdom & Ireland 00800 2255 4835*USA180****9200* European toll-free number. If not accessible, call: +41 52 675 3777For Further Information. Tektronix maintains a comprehensive, constantly expanding collection of application notes, technical briefs and other resources to help engineers working on the cutting edge of technology. Please visit . Copyright © Tektronix, Inc. All rights reserved. Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supersedes that in all previously published material. Specification andprice change privileges reserved. TEKTRONIX and TEK are registered trademarks of Tektronix, Inc. All other trade names referenced are the service marks, trademarks, or registered trademarks of their respective companies.13 Nov 2018 75W-61444-2 。

preug_9