德州仪器(TI)LM3S2948系列 规格书,Datasheet 资料

机器人接口部分

电源接口部分用8.4V镍氢电池组为其供电,通过两片LM7805稳压芯片进行分频,分别有两种电压值输出为5V,12V。

从而满足系统板供电要求。

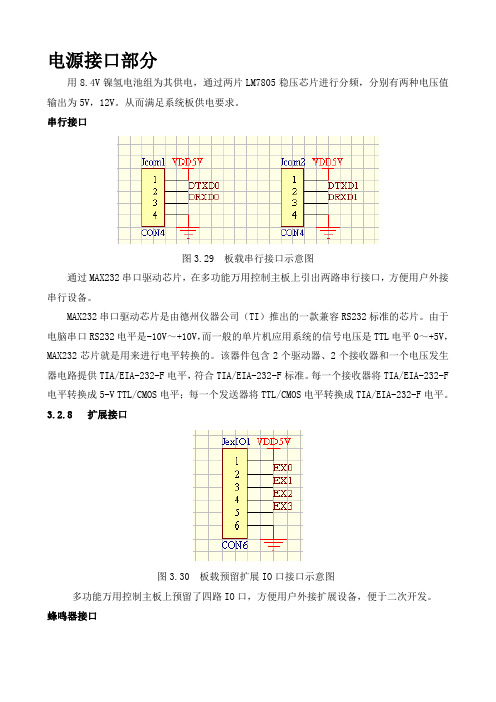

串行接口图3.29 板载串行接口示意图通过MAX232串口驱动芯片,在多功能万用控制主板上引出两路串行接口,方便用户外接串行设备。

MAX232串口驱动芯片是由德州仪器公司(TI)推出的一款兼容RS232标准的芯片。

由于电脑串口RS232电平是-10V~+10V,而一般的单片机应用系统的信号电压是TTL电平0~+5V,MAX232芯片就是用来进行电平转换的。

该器件包含2个驱动器、2个接收器和一个电压发生器电路提供TIA/EIA-232-F电平,符合TIA/EIA-232-F标准。

每一个接收器将TIA/EIA-232-F 电平转换成5-V TTL/CMOS电平;每一个发送器将TTL/CMOS电平转换成TIA/EIA-232-F电平。

3.2.8 扩展接口图3.30 板载预留扩展IO口接口示意图多功能万用控制主板上预留了四路IO口,方便用户外接扩展设备,便于二次开发。

蜂鸣器接口板载蜂鸣器接口示意图板载蜂鸣器,起到提示的作用,当传感器工作时有提示声音,下载程序时,蜂鸣器发声,提示下载成功。

直流电机接口电机驱动芯片(L298N)图3.33 四路电机接口板载四路直流电机接口,用于给小车提供足够的动力来源。

采用两片L298N电机驱动芯片,其中每一片L298N均可驱动两路直流电机。

L298N内部包含4通道逻辑驱动电路。

可以方便的驱动两个直流电机,或一个两相步进电机。

L298N芯片可以驱动两个二相电机,也可以驱动一个四相电机,输出电压最高可达50V,可以直接通过电源来调节输出电压;可以直接用单片机的IO口提供信号;而且电路简单,使用比较方便。

恒速电机接口板载恒速电机接口示意图板载两路恒速电机接口,可用于外接小型直流电机。

步进电机接口板载步进电机接口示意图主板预留步进电机接口,可外接两路步进电机,用于完成控制步进电机的正转、反转、转动角度以及转动速度。

第1章嵌入式系统概述

2、SiM3U1xx(80MHZ USB)系列(M3)

1.4 STM32系列微控制器简介 STM32为意法半导体(ST)公司生产的ARM处理器。

Flash Size (bytes)

512K

256 K

STM32 prod Q2/08 Samples Dec 07 Prod Q2/08

未来 发展方向

64 K 32 K

STM32 Samples NOW Prod Oct 07

72 MHz CORTEX- M3 CPU Wide offer

• 32KB-512KB Flash • 6Kb-64KB RAM

0K 48 pins 64 pins 100 pins

144 pins

LQFP

LQFP

LQFP

LQFP

(7x7) (10x10) (14x14)/BGA (20x20)/BG

machinery or plants”.

1.嵌入式系统简介

目前,对嵌入式系统的定义多种多样,但没有一种定义是全面的。下面给出两种 比较合理定义:

●从技术的角度定义:以应用为中心、以计算机技术为基础、软件硬件可裁剪、 适应应用系统对功能、可靠性、成本、体积、功耗严格要求的专用计算机系统。 ●从系统的角度定义:嵌入式系统是设计完成复杂功能的硬件和软件,并使其紧 密耦合在一起的计算机系统。术语嵌入式反映了这些系统通常是更大系统中的一 个完整的部分,称为嵌入的系统。嵌入的系统中可以共存多个嵌入式系统。

ADC

16 channels /

Tem1pMSsepns sor

Power Supply Reg 1.8V

POR/PDR/PV XTDAL

oscillators 3I2nKt.HRzC+ o4s~c1il6lMatoHrzs 32KHz +

德州仪器(TI)LM3S2793系列规格书,Datasheet资料

TEXAS INSTRUMENTS-PRODUCTION DATAStellaris®LM3S2793MicrocontrollerDATA SHEETCopyright©2007-2012 DS-LM3S2793-11425CopyrightCopyright©2007-2012Texas Instruments Incorporated All rights reserved.Stellaris and StellarisWare®are registered trademarks of Texas Instruments Incorporated.ARM and Thumb are registered trademarks and Cortex is a trademark of ARM Limited.Other names and brands may be claimed as the property of others.PRODUCTION DATA information is current as of publication date.Products conform to specifications per the terms of Texas Instruments standard warranty.Production processing does not necessarily include testing of all parameters.Please be aware that an important notice concerning availability,standard warranty,and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.Texas Instruments Incorporated108Wild Basin,Suite350Austin,TX78746/stellaris/sc/technical-support/product-information-centers.htmStellaris®LM3S2793MicrocontrollerTable of ContentsRevision History (32)About This Document (43)Audience (43)About This Manual (43)Related Documents (43)Documentation Conventions (44)1Architectural Overview (46)1.1Overview (46)1.2Target Applications (48)1.3Features (48)1.3.1ARM Cortex-M3Processor Core (48)1.3.2On-Chip Memory (50)1.3.3External Peripheral Interface (51)1.3.4Serial Communications Peripherals (53)1.3.5System Integration (57)1.3.6Advanced Motion Control (63)1.3.7Analog (65)1.3.8JTAG and ARM Serial Wire Debug (66)1.3.9Packaging and Temperature (67)1.4Hardware Details (67)2The Cortex-M3Processor (68)2.1Block Diagram (69)2.2Overview (70)2.2.1System-Level Interface (70)2.2.2Integrated Configurable Debug (70)2.2.3Trace Port Interface Unit(TPIU) (71)2.2.4Cortex-M3System Component Details (71)2.3Programming Model (72)2.3.1Processor Mode and Privilege Levels for Software Execution (72)2.3.2Stacks (72)2.3.3Register Map (73)2.3.4Register Descriptions (74)2.3.5Exceptions and Interrupts (87)2.3.6Data Types (87)2.4Memory Model (87)2.4.1Memory Regions,Types and Attributes (89)2.4.2Memory System Ordering of Memory Accesses (90)2.4.3Behavior of Memory Accesses (90)2.4.4Software Ordering of Memory Accesses (91)2.4.5Bit-Banding (92)2.4.6Data Storage (94)2.4.7Synchronization Primitives (95)2.5Exception Model (96)2.5.1Exception States (97)2.5.2Exception Types (97)Table of Contents2.5.3Exception Handlers (100)2.5.4Vector Table (100)2.5.5Exception Priorities (101)2.5.6Interrupt Priority Grouping (102)2.5.7Exception Entry and Return (102)2.6Fault Handling (104)2.6.1Fault Types (104)2.6.2Fault Escalation and Hard Faults (105)2.6.3Fault Status Registers and Fault Address Registers (106)2.6.4Lockup (106)2.7Power Management (106)2.7.1Entering Sleep Modes (106)2.7.2Wake Up from Sleep Mode (107)2.8Instruction Set Summary (108)3Cortex-M3Peripherals (111)3.1Functional Description (111)3.1.1System Timer(SysTick) (111)3.1.2Nested Vectored Interrupt Controller(NVIC) (112)3.1.3System Control Block(SCB) (114)3.1.4Memory Protection Unit(MPU) (114)3.2Register Map (119)3.3System Timer(SysTick)Register Descriptions (121)3.4NVIC Register Descriptions (125)3.5System Control Block(SCB)Register Descriptions (138)3.6Memory Protection Unit(MPU)Register Descriptions (167)4JTAG Interface (177)4.1Block Diagram (178)4.2Signal Description (178)4.3Functional Description (179)4.3.1JTAG Interface Pins (179)4.3.2JTAG TAP Controller (181)4.3.3Shift Registers (181)4.3.4Operational Considerations (182)4.4Initialization and Configuration (184)4.5Register Descriptions (185)4.5.1Instruction Register(IR) (185)4.5.2Data Registers (187)5System Control (189)5.1Signal Description (189)5.2Functional Description (189)5.2.1Device Identification (190)5.2.2Reset Control (190)5.2.3Non-Maskable Interrupt (195)5.2.4Power Control (195)5.2.5Clock Control (196)5.2.6System Control (203)5.3Initialization and Configuration (205)5.4Register Map (205)Stellaris®LM3S2793Microcontroller5.5Register Descriptions (207)6Hibernation Module (295)6.1Block Diagram (296)6.2Signal Description (296)6.3Functional Description (297)6.3.1Register Access Timing (297)6.3.2Hibernation Clock Source (298)6.3.3System Implementation (299)6.3.4Battery Management (300)6.3.5Real-Time Clock (300)6.3.6Battery-Backed Memory (301)6.3.7Power Control Using HIB (301)6.3.8Power Control Using VDD3ON Mode (301)6.3.9Initiating Hibernate (301)6.3.10Waking from Hibernate (301)6.3.11Interrupts and Status (302)6.4Initialization and Configuration (302)6.4.1Initialization (302)6.4.2RTC Match Functionality(No Hibernation) (303)6.4.3RTC Match/Wake-Up from Hibernation (303)6.4.4External Wake-Up from Hibernation (304)6.4.5RTC or External Wake-Up from Hibernation (304)6.5Register Map (304)6.6Register Descriptions (305)7Internal Memory (322)7.1Block Diagram (322)7.2Functional Description (322)7.2.1SRAM (323)7.2.2ROM (323)7.2.3Flash Memory (325)7.3Register Map (330)7.4Flash Memory Register Descriptions(Flash Control Offset) (331)7.5Memory Register Descriptions(System Control Offset) (343)8Micro Direct Memory Access(μDMA) (359)8.1Block Diagram (360)8.2Functional Description (360)8.2.1Channel Assignments (361)8.2.2Priority (362)8.2.3Arbitration Size (362)8.2.4Request Types (362)8.2.5Channel Configuration (363)8.2.6Transfer Modes (365)8.2.7Transfer Size and Increment (373)8.2.8Peripheral Interface (373)8.2.9Software Request (373)8.2.10Interrupts and Errors (374)8.3Initialization and Configuration (374)8.3.1Module Initialization (374)Table of Contents8.3.2Configuring a Memory-to-Memory Transfer (374)8.3.3Configuring a Peripheral for Simple Transmit (376)8.3.4Configuring a Peripheral for Ping-Pong Receive (377)8.3.5Configuring Channel Assignments (380)8.4Register Map (380)8.5μDMA Channel Control Structure (381)8.6μDMA Register Descriptions (388)9General-Purpose Input/Outputs(GPIOs) (417)9.1Signal Description (417)9.2Functional Description (422)9.2.1Data Control (423)9.2.2Interrupt Control (424)9.2.3Mode Control (425)9.2.4Commit Control (425)9.2.5Pad Control (426)9.2.6Identification (426)9.3Initialization and Configuration (426)9.4Register Map (427)9.5Register Descriptions (430)10External Peripheral Interface(EPI) (473)10.1EPI Block Diagram (474)10.2Signal Description (475)10.3Functional Description (477)10.3.1Non-Blocking Reads (478)10.3.2DMA Operation (479)10.4Initialization and Configuration (479)10.4.1SDRAM Mode (480)10.4.2Host Bus Mode (484)10.4.3General-Purpose Mode (495)10.5Register Map (503)10.6Register Descriptions (504)11General-Purpose Timers (546)11.1Block Diagram (547)11.2Signal Description (547)11.3Functional Description (550)11.3.1GPTM Reset Conditions (551)11.3.2Timer Modes (551)11.3.3DMA Operation (557)11.3.4Accessing Concatenated Register Values (558)11.4Initialization and Configuration (558)11.4.1One-Shot/Periodic Timer Mode (558)11.4.2Real-Time Clock(RTC)Mode (559)11.4.3Input Edge-Count Mode (559)11.4.4Input Edge Timing Mode (560)11.4.5PWM Mode (561)11.5Register Map (561)11.6Register Descriptions (562)Stellaris®LM3S2793Microcontroller 12Watchdog Timers (593)12.1Block Diagram (594)12.2Functional Description (594)12.2.1Register Access Timing (595)12.3Initialization and Configuration (595)12.4Register Map (595)12.5Register Descriptions (596)13Analog-to-Digital Converter(ADC) (618)13.1Block Diagram (619)13.2Signal Description (620)13.3Functional Description (622)13.3.1Sample Sequencers (622)13.3.2Module Control (623)13.3.3Hardware Sample Averaging Circuit (625)13.3.4Analog-to-Digital Converter (626)13.3.5Differential Sampling (629)13.3.6Internal Temperature Sensor (632)13.3.7Digital Comparator Unit (632)13.4Initialization and Configuration (637)13.4.1Module Initialization (637)13.4.2Sample Sequencer Configuration (638)13.5Register Map (638)13.6Register Descriptions (640)14Universal Asynchronous Receivers/Transmitters(UARTs) (698)14.1Block Diagram (699)14.2Signal Description (699)14.3Functional Description (701)14.3.1Transmit/Receive Logic (701)14.3.2Baud-Rate Generation (702)14.3.3Data Transmission (703)14.3.4Serial IR(SIR) (703)14.3.5ISO7816Support (704)14.3.6Modem Handshake Support (704)14.3.7LIN Support (706)14.3.8FIFO Operation (707)14.3.9Interrupts (708)14.3.10Loopback Operation (709)14.3.11DMA Operation (709)14.4Initialization and Configuration (709)14.5Register Map (710)14.6Register Descriptions (712)15Synchronous Serial Interface(SSI) (762)15.1Block Diagram (763)15.2Signal Description (763)15.3Functional Description (764)15.3.1Bit Rate Generation (765)15.3.2FIFO Operation (765)15.3.3Interrupts (765)Table of Contents15.3.4Frame Formats (766)15.3.5DMA Operation (773)15.4Initialization and Configuration (774)15.5Register Map (775)15.6Register Descriptions (776)16Inter-Integrated Circuit(I2C)Interface (804)16.1Block Diagram (805)16.2Signal Description (805)16.3Functional Description (806)16.3.1I2C Bus Functional Overview (806)16.3.2Available Speed Modes (808)16.3.3Interrupts (809)16.3.4Loopback Operation (810)16.3.5Command Sequence Flow Charts (811)16.4Initialization and Configuration (818)16.5Register Map (819)16.6Register Descriptions(I2C Master) (820)16.7Register Descriptions(I2C Slave) (833)17Inter-Integrated Circuit Sound(I2S)Interface (842)17.1Block Diagram (843)17.2Signal Description (843)17.3Functional Description (845)17.3.1Transmit (846)17.3.2Receive (850)17.4Initialization and Configuration (852)17.5Register Map (853)17.6Register Descriptions (854)18Controller Area Network(CAN)Module (879)18.1Block Diagram (880)18.2Signal Description (880)18.3Functional Description (881)18.3.1Initialization (882)18.3.2Operation (883)18.3.3Transmitting Message Objects (884)18.3.4Configuring a Transmit Message Object (884)18.3.5Updating a Transmit Message Object (885)18.3.6Accepting Received Message Objects (886)18.3.7Receiving a Data Frame (886)18.3.8Receiving a Remote Frame (886)18.3.9Receive/Transmit Priority (887)18.3.10Configuring a Receive Message Object (887)18.3.11Handling of Received Message Objects (888)18.3.12Handling of Interrupts (890)18.3.13Test Mode (891)18.3.14Bit Timing Configuration Error Considerations (893)18.3.15Bit Time and Bit Rate (893)18.3.16Calculating the Bit Timing Parameters (895)Stellaris®LM3S2793Microcontroller 18.4Register Map (898)18.5CAN Register Descriptions (899)19Analog Comparators (930)19.1Block Diagram (931)19.2Signal Description (931)19.3Functional Description (932)19.3.1Internal Reference Programming (933)19.4Initialization and Configuration (934)19.5Register Map (935)19.6Register Descriptions (936)20Pulse Width Modulator(PWM) (944)20.1Block Diagram (945)20.2Signal Description (946)20.3Functional Description (949)20.3.1PWM Timer (949)20.3.2PWM Comparators (950)20.3.3PWM Signal Generator (951)20.3.4Dead-Band Generator (952)20.3.5Interrupt/ADC-Trigger Selector (952)20.3.6Synchronization Methods (953)20.3.7Fault Conditions (954)20.3.8Output Control Block (954)20.4Initialization and Configuration (955)20.5Register Map (956)20.6Register Descriptions (959)21Quadrature Encoder Interface(QEI) (1022)21.1Block Diagram (1022)21.2Signal Description (1023)21.3Functional Description (1024)21.4Initialization and Configuration (1027)21.5Register Map (1027)21.6Register Descriptions (1028)22Pin Diagram (1045)23Signal Tables (1047)23.1100-Pin LQFP Package Pin Tables (1048)23.2108-Ball BGA Package Pin Tables (1084)23.3Connections for Unused Signals (1120)24Operating Characteristics (1122)25Electrical Characteristics (1123)25.1Maximum Ratings (1123)25.2Recommended Operating Conditions (1123)25.3Load Conditions (1124)25.4JTAG and Boundary Scan (1124)25.5Power and Brown-Out (1126)25.6Reset (1127)25.7On-Chip Low Drop-Out(LDO)Regulator (1128)25.8Clocks (1128)Table of Contents25.8.1PLL Specifications (1128)25.8.2PIOSC Specifications (1129)25.8.3Internal30-kHz Oscillator Specifications (1129)25.8.4Hibernation Clock Source Specifications (1130)25.8.5Main Oscillator Specifications (1130)25.8.6System Clock Specification with ADC Operation (1131)25.9Sleep Modes (1131)25.10Hibernation Module (1131)25.11Flash Memory (1133)25.12Input/Output Characteristics (1133)25.13External Peripheral Interface(EPI) (1134)25.14Analog-to-Digital Converter(ADC) (1139)25.15Synchronous Serial Interface(SSI) (1140)25.16Inter-Integrated Circuit(I2C)Interface (1142)25.17Inter-Integrated Circuit Sound(I2S)Interface (1143)25.18Analog Comparator (1144)25.19Current Consumption (1145)25.19.1Nominal Power Consumption (1145)25.19.2Maximum Current Consumption (1146)A Register Quick Reference (1148)B Ordering and Contact Information (1184)B.1Ordering Information (1184)B.2Part Markings (1184)B.3Kits (1185)B.4Support Information (1185)C Package Information (1186)C.1100-Pin LQFP Package (1186)C.1.1Package Dimensions (1186)C.1.2Tray Dimensions (1188)C.1.3Tape and Reel Dimensions (1188)C.2108-Ball BGA Package (1190)C.2.1Package Dimensions (1190)C.2.2Tray Dimensions (1192)C.2.3Tape and Reel Dimensions (1193)List of FiguresFigure1-1.Stellaris LM3S2793Microcontroller High-Level Block Diagram (47)Figure2-1.CPU Block Diagram (70)Figure2-2.TPIU Block Diagram (71)Figure2-3.Cortex-M3Register Set (73)Figure2-4.Bit-Band Mapping (94)Figure2-5.Data Storage (95)Figure2-6.Vector Table (101)Figure2-7.Exception Stack Frame (103)Figure3-1.SRD Use Example (117)Figure4-1.JTAG Module Block Diagram (178)Figure4-2.Test Access Port State Machine (181)Figure4-3.IDCODE Register Format (187)Figure4-4.BYPASS Register Format (187)Figure4-5.Boundary Scan Register Format (188)Figure5-1.Basic RST Configuration (192)Figure5-2.External Circuitry to Extend Power-On Reset (192)Figure5-3.Reset Circuit Controlled by Switch (193)Figure5-4.Power Architecture (196)Figure5-5.Main Clock Tree (199)Figure6-1.Hibernation Module Block Diagram (296)ing a Crystal as the Hibernation Clock Source (299)ing a Dedicated Oscillator as the Hibernation Clock Source with VDD3ONMode (299)Figure7-1.Internal Memory Block Diagram (322)Figure8-1.μDMA Block Diagram (360)Figure8-2.Example of Ping-PongμDMA Transaction (366)Figure8-3.Memory Scatter-Gather,Setup and Configuration (368)Figure8-4.Memory Scatter-Gather,μDMA Copy Sequence (369)Figure8-5.Peripheral Scatter-Gather,Setup and Configuration (371)Figure8-6.Peripheral Scatter-Gather,μDMA Copy Sequence (372)Figure9-1.Digital I/O Pads (422)Figure9-2.Analog/Digital I/O Pads (423)Figure9-3.GPIODATA Write Example (424)Figure9-4.GPIODATA Read Example (424)Figure10-1.EPI Block Diagram (475)Figure10-2.SDRAM Non-Blocking Read Cycle (483)Figure10-3.SDRAM Normal Read Cycle (483)Figure10-4.SDRAM Write Cycle (484)Figure10-5.Example Schematic for Muxed Host-Bus16Mode (490)Figure10-6.Host-Bus Read Cycle,MODE=0x1,WRHIGH=0,RDHIGH=0 (492)Figure10-7.Host-Bus Write Cycle,MODE=0x1,WRHIGH=0,RDHIGH=0 (493)Figure10-8.Host-Bus Write Cycle with Multiplexed Address and Data,MODE=0x0,WRHIGH=0,RDHIGH=0 (493)Figure10-9.Host-Bus Write Cycle with Multiplexed Address and Data and ALE with DualCSn (494)Figure10-10.Continuous Read Mode Accesses (494)Figure10-11.Write Followed by Read to External FIFO (495)Figure10-12.Two-Entry FIFO (495)Figure10-13.Single-Cycle Write Access,FRM50=0,FRMCNT=0,WRCYC=0 (499)Figure10-14.Two-Cycle Read,Write Accesses,FRM50=0,FRMCNT=0,RDCYC=1,WRCYC=1 (499)Figure10-15.Read Accesses,FRM50=0,FRMCNT=0,RDCYC=1 (500)Figure10-16.FRAME Signal Operation,FRM50=0and FRMCNT=0 (500)Figure10-17.FRAME Signal Operation,FRM50=0and FRMCNT=1 (500)Figure10-18.FRAME Signal Operation,FRM50=0and FRMCNT=2 (501)Figure10-19.FRAME Signal Operation,FRM50=1and FRMCNT=0 (501)Figure10-20.FRAME Signal Operation,FRM50=1and FRMCNT=1 (501)Figure10-21.FRAME Signal Operation,FRM50=1and FRMCNT=2 (501)Figure10-22.iRDY Signal Operation,FRM50=0,FRMCNT=0,and RD2CYC=1 (502)Figure10-23.EPI Clock Operation,CLKGATE=1,WR2CYC=0 (503)Figure10-24.EPI Clock Operation,CLKGATE=1,WR2CYC=1 (503)Figure11-1.GPTM Module Block Diagram (547)Figure11-2.Timer Daisy Chain (553)Figure11-3.Input Edge-Count Mode Example (555)Figure11-4.16-Bit Input Edge-Time Mode Example (556)Figure11-5.16-Bit PWM Mode Example (557)Figure12-1.WDT Module Block Diagram (594)Figure13-1.Implementation of Two ADC Blocks (619)Figure13-2.ADC Module Block Diagram (620)Figure13-3.ADC Sample Phases (624)Figure13-4.Doubling the ADC Sample Rate (625)Figure13-5.Skewed Sampling (625)Figure13-6.Sample Averaging Example (626)Figure13-7.ADC Input Equivalency Diagram (627)Figure13-8.Internal Voltage Conversion Result (628)Figure13-9.External Voltage Conversion Result (629)Figure13-10.Differential Sampling Range,V IN_ODD=1.5V (630)Figure13-11.Differential Sampling Range,V IN_ODD=0.75V (631)Figure13-12.Differential Sampling Range,V IN_ODD=2.25V (631)Figure13-13.Internal Temperature Sensor Characteristic (632)Figure13-14.Low-Band Operation(CIC=0x0and/or CTC=0x0) (635)Figure13-15.Mid-Band Operation(CIC=0x1and/or CTC=0x1) (636)Figure13-16.High-Band Operation(CIC=0x3and/or CTC=0x3) (637)Figure14-1.UART Module Block Diagram (699)Figure14-2.UART Character Frame (702)Figure14-3.IrDA Data Modulation (704)Figure14-4.LIN Message (706)Figure14-5.LIN Synchronization Field (707)Figure15-1.SSI Module Block Diagram (763)Figure15-2.TI Synchronous Serial Frame Format(Single Transfer) (767)Figure15-3.TI Synchronous Serial Frame Format(Continuous Transfer) (767)Figure15-4.Freescale SPI Format(Single Transfer)with SPO=0and SPH=0 (768)Figure15-5.Freescale SPI Format(Continuous Transfer)with SPO=0and SPH=0 (768)Figure15-6.Freescale SPI Frame Format with SPO=0and SPH=1 (769)Figure15-7.Freescale SPI Frame Format(Single Transfer)with SPO=1and SPH=0 (770)Figure15-8.Freescale SPI Frame Format(Continuous Transfer)with SPO=1and SPH=0 (770)Figure15-9.Freescale SPI Frame Format with SPO=1and SPH=1 (771)Figure15-10.MICROWIRE Frame Format(Single Frame) (772)Figure15-11.MICROWIRE Frame Format(Continuous Transfer) (773)Figure15-12.MICROWIRE Frame Format,SSIFss Input Setup and Hold Requirements (773)Figure16-1.I2C Block Diagram (805)Figure16-2.I2C Bus Configuration (806)Figure16-3.START and STOP Conditions (807)plete Data Transfer with a7-Bit Address (807)Figure16-5.R/S Bit in First Byte (808)Figure16-6.Data Validity During Bit Transfer on the I2C Bus (808)Figure16-7.Master Single TRANSMIT (812)Figure16-8.Master Single RECEIVE (813)Figure16-9.Master TRANSMIT with Repeated START (814)Figure16-10.Master RECEIVE with Repeated START (815)Figure16-11.Master RECEIVE with Repeated START after TRANSMIT with RepeatedSTART (816)Figure16-12.Master TRANSMIT with Repeated START after RECEIVE with RepeatedSTART (817)Figure16-13.Slave Command Sequence (818)Figure17-1.I2S Block Diagram (843)Figure17-2.I2S Data Transfer (846)Figure17-3.Left-Justified Data Transfer (846)Figure17-4.Right-Justified Data Transfer (846)Figure18-1.CAN Controller Block Diagram (880)Figure18-2.CAN Data/Remote Frame (882)Figure18-3.Message Objects in a FIFO Buffer (890)Figure18-4.CAN Bit Time (894)Figure19-1.Analog Comparator Module Block Diagram (931)Figure19-2.Structure of Comparator Unit (933)parator Internal Reference Structure (933)Figure20-1.PWM Module Diagram (946)Figure20-2.PWM Generator Block Diagram (946)Figure20-3.PWM Count-Down Mode (951)Figure20-4.PWM Count-Up/Down Mode (951)Figure20-5.PWM Generation Example In Count-Up/Down Mode (952)Figure20-6.PWM Dead-Band Generator (952)Figure21-1.QEI Block Diagram (1023)Figure21-2.Quadrature Encoder and Velocity Predivider Operation (1026)Figure22-1.100-Pin LQFP Package Pin Diagram (1045)Figure22-2.108-Ball BGA Package Pin Diagram(Top View) (1046)Figure25-1.Load Conditions (1124)Figure25-2.JTAG Test Clock Input Timing (1125)Figure25-3.JTAG Test Access Port(TAP)Timing (1125)Figure25-4.Power-On Reset Timing (1126)Figure25-5.Brown-Out Reset Timing (1126)Figure25-6.Power-On Reset and Voltage Parameters (1127)Figure25-7.External Reset Timing(RST) (1127)Figure25-8.Software Reset Timing (1127)Figure25-9.Watchdog Reset Timing (1128)Figure25-10.MOSC Failure Reset Timing (1128)Figure25-11.Hibernation Module Timing with Internal Oscillator Running in Hibernation (1132)Figure25-12.Hibernation Module Timing with Internal Oscillator Stopped in Hibernation (1133)Figure25-13.SDRAM Initialization and Load Mode Register Timing (1134)Figure25-14.SDRAM Read Timing (1135)Figure25-15.SDRAM Write Timing (1135)Figure25-16.Host-Bus8/16Mode Read Timing (1136)Figure25-17.Host-Bus8/16Mode Write Timing (1136)Figure25-18.Host-Bus8/16Mode Muxed Read Timing (1137)Figure25-19.Host-Bus8/16Mode Muxed Write Timing (1137)Figure25-20.General-Purpose Mode Read and Write Timing (1138)Figure25-21.General-Purpose Mode iRDY Timing (1138)Figure25-22.ADC Input Equivalency Diagram (1140)Figure25-23.SSI Timing for TI Frame Format(FRF=01),Single Transfer TimingMeasurement (1141)Figure25-24.SSI Timing for MICROWIRE Frame Format(FRF=10),Single Transfer (1141)Figure25-25.SSI Timing for SPI Frame Format(FRF=00),with SPH=1 (1142)Figure25-26.I2C Timing (1143)Figure25-27.I2S Master Mode Transmit Timing (1143)Figure25-28.I2S Master Mode Receive Timing (1144)Figure25-29.I2S Slave Mode Transmit Timing (1144)Figure25-30.I2S Slave Mode Receive Timing (1144)Figure C-1.Stellaris LM3S2793100-Pin LQFP Package Dimensions (1186)Figure C-2.100-Pin LQFP Tray Dimensions (1188)Figure C-3.100-Pin LQFP Tape and Reel Dimensions (1189)Figure C-4.Stellaris LM3S2793108-Ball BGA Package Dimensions (1190)Figure C-5.108-Ball BGA Tray Dimensions (1192)Figure C-6.108-Ball BGA Tape and Reel Dimensions (1193)List of TablesTable1.Revision History (32)Table2.Documentation Conventions (44)Table2-1.Summary of Processor Mode,Privilege Level,and Stack Use (73)Table2-2.Processor Register Map (74)Table2-3.PSR Register Combinations (79)Table2-4.Memory Map (87)Table2-5.Memory Access Behavior (90)Table2-6.SRAM Memory Bit-Banding Regions (92)Table2-7.Peripheral Memory Bit-Banding Regions (92)Table2-8.Exception Types (98)Table2-9.Interrupts (99)Table2-10.Exception Return Behavior (104)Table2-11.Faults (104)Table2-12.Fault Status and Fault Address Registers (106)Table2-13.Cortex-M3Instruction Summary (108)Table3-1.Core Peripheral Register Regions (111)Table3-2.Memory Attributes Summary (114)Table3-3.TEX,S,C,and B Bit Field Encoding (117)Table3-4.Cache Policy for Memory Attribute Encoding (118)Table3-5.AP Bit Field Encoding (118)Table3-6.Memory Region Attributes for Stellaris Microcontrollers (118)Table3-7.Peripherals Register Map (119)Table3-8.Interrupt Priority Levels (146)Table3-9.Example SIZE Field Values (174)Table4-1.JTAG_SWD_SWO Signals(100LQFP) (178)Table4-2.JTAG_SWD_SWO Signals(108BGA) (179)Table4-3.JTAG Port Pins State after Power-On Reset or RST assertion (180)Table4-4.JTAG Instruction Register Commands (185)Table5-1.System Control&Clocks Signals(100LQFP) (189)Table5-2.System Control&Clocks Signals(108BGA) (189)Table5-3.Reset Sources (190)Table5-4.Clock Source Options (197)Table5-5.Possible System Clock Frequencies Using the SYSDIV Field (200)Table5-6.Examples of Possible System Clock Frequencies Using the SYSDIV2Field (200)Table5-7.Examples of Possible System Clock Frequencies with DIV400=1 (201)Table5-8.System Control Register Map (205)Table5-9.RCC2Fields that Override RCC Fields (226)Table6-1.Hibernate Signals(100LQFP) (296)Table6-2.Hibernate Signals(108BGA) (297)Table6-3.Hibernation Module Clock Operation (303)Table6-4.Hibernation Module Register Map (305)Table7-1.Flash Memory Protection Policy Combinations (326)er-Programmable Flash Memory Resident Registers (330)Table7-3.Flash Register Map (330)Table8-1.μDMA Channel Assignments (361)Table8-2.Request Type Support (363)Table8-3.Control Structure Memory Map (364)Table8-4.Channel Control Structure (364)Table8-5.μDMA Read Example:8-Bit Peripheral (373)Table8-6.μDMA Interrupt Assignments (374)Table8-7.Channel Control Structure Offsets for Channel30 (375)Table8-8.Channel Control Word Configuration for Memory Transfer Example (375)Table8-9.Channel Control Structure Offsets for Channel7 (376)Table8-10.Channel Control Word Configuration for Peripheral Transmit Example (377)Table8-11.Primary and Alternate Channel Control Structure Offsets for Channel8 (378)Table8-12.Channel Control Word Configuration for Peripheral Ping-Pong ReceiveExample (379)Table8-13.μDMA Register Map (380)Table9-1.GPIO Pins With Non-Zero Reset Values (418)Table9-2.GPIO Pins and Alternate Functions(100LQFP) (418)Table9-3.GPIO Pins and Alternate Functions(108BGA) (420)Table9-4.GPIO Pad Configuration Examples (426)Table9-5.GPIO Interrupt Configuration Example (427)Table9-6.GPIO Pins With Non-Zero Reset Values (428)Table9-7.GPIO Register Map (428)Table9-8.GPIO Pins With Non-Zero Reset Values (441)Table9-9.GPIO Pins With Non-Zero Reset Values (447)Table9-10.GPIO Pins With Non-Zero Reset Values (449)Table9-11.GPIO Pins With Non-Zero Reset Values (452)Table9-12.GPIO Pins With Non-Zero Reset Values (459)Table10-1.External Peripheral Interface Signals(100LQFP) (475)Table10-2.External Peripheral Interface Signals(108BGA) (476)Table10-3.EPI SDRAM Signal Connections (481)Table10-4.Capabilities of Host Bus8and Host Bus16Modes (485)Table10-5.EPI Host-Bus8Signal Connections (486)Table10-6.EPI Host-Bus16Signal Connections (488)Table10-7.EPI General Purpose Signal Connections (497)Table10-8.External Peripheral Interface(EPI)Register Map (503)Table11-1.Available CCP Pins (547)Table11-2.General-Purpose Timers Signals(100LQFP) (548)Table11-3.General-Purpose Timers Signals(108BGA) (549)Table11-4.General-Purpose Timer Capabilities (550)Table11-5.Counter Values When the Timer is Enabled in Periodic or One-Shot Modes (551)Table11-6.16-Bit Timer With Prescaler Configurations (552)Table11-7.Counter Values When the Timer is Enabled in RTC Mode (553)Table11-8.Counter Values When the Timer is Enabled in Input Edge-Count Mode (554)Table11-9.Counter Values When the Timer is Enabled in Input Event-Count Mode (555)Table11-10.Counter Values When the Timer is Enabled in PWM Mode (556)Table11-11.Timers Register Map (561)Table12-1.Watchdog Timers Register Map (596)Table13-1.ADC Signals(100LQFP) (620)Table13-2.ADC Signals(108BGA) (621)Table13-3.Samples and FIFO Depth of Sequencers (622)Table13-4.Differential Sampling Pairs (629)。

SH366006 标准版用户手册_V1.0

MCU及常见MCU外围电路

电子系统设计与实践

28

2013/5/12

Cortex-M3

电子系统设计与实践

29

2013/5/12

Cortex-M4

电子系统设计与实践

30

2013/5/12

CMSIS

ARM Cortex 微控制器软件接口标准

(CMSIS) 是 Cortex-M 处理器系列的与 供应商无关的硬件抽象层。 使用 CMSIS,可以为接口外设、实时操作系 统和中间件实现一致且简单的软件接口, 从而简化软件的重用、缩短新微控制器 开发人员的学习过程,并缩短新产品的 上市时间。

电子系统设计与实践

15

2013/5/12

嵌入式处理器(常见)

ADI

ADSP-BF53x/56x (Blackfin 16bits) TI OMAP2、DM64x、达芬奇 (ARM+TI DSP) Intel Pentium-M C-M 、 Core-Duo (x86) Via C7 (x86) Altera NiosII (NiosII soft core) Xilinx PowerPC(硬核)/MicroBlaze 软核 Magiceyes MMSP2 MP25xx (Dual ARM9) ARM Cortex内核(Cortex-A8/Cortex-A9)

Cortex-M核芯片

意法半导体-- STM STM32 F0xx系列(M0 48MHZ) STM32 Lxxx系列(M3 32MHZ) STM32 F1xx系列(M3 72MHZ) STM32 F2xx系列(M3 120MHZ) STM32 F4xx系列(M4 168MHZ)

电子系统设计与实践

17

2013/5/12

SD2943W;中文规格书,Datasheet资料

August 2011Doc ID 11584 Rev 31/15SD2943HF/VHF/UHF RF power N-channel MOSFETsFeatures■High power capability■P OUT = 350 W min. with 22dB gain @ 30 MHz ■P SAT = 450 W ■Low R DS(on)■Thermally enhanced packaging for lower junction temperatures ■Gold metallization ■Excellent thermal stability ■Common source configurationDescriptionThe SD2943 is a gold metallized N-channel MOS field-effect RF power transistor. It is intended for use in 50 V dc large signal applications up to 150 MHz. The SD2943 offers a 20% higher power saturation than the SD2933, and is ideal for ISM applications where reliability and ruggedness are critical factors.Table 1.Device summaryOrder code Marking Base qty.Package Packaging (1)SD2943WSD2943(1)25 pcsM177Plastic tray1.For more details please refer to Chapter 7: Marking, packing and shipping specifications ..Contents SD2943 Contents1Electrical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 2Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 3Impedance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 4Typical performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 5Test Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 6Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 7Marking, packing and shipping specifications . . . . . . . . . . . . . . . . . . . 13 8Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142/15Doc ID 11584 Rev 3SD2943Electrical dataDoc ID 11584 Rev 33/151 Electrical data(T CASE = 25°C)Table 2.Absolute maximum ratingSymbol ParameterValue Unit V (BR)DSS (1)Drain source voltage130V V DGR Drain-gate voltage (R GS = 1MW)130V V GS Gate-source voltage ±20V I D Drain current 40A P DISS Power dissipation648W T j Max. operating junction temperature200°C E AS Avalanche energy, single pulse (I D = 53A, 800µH coil)1100mJ T STGStorage temperature-65 to +150°C1.T J = 150 °CTable 3.Thermal dataSymbol ParameterValue Unit R thJCJunction to case thermal resistance0.27°C/WElectrical characteristics SD29434/15Doc ID 11584 Rev 32 Electrical characteristics(T CASE = 25°C)Table 4.StaticSymbol Test conditionsMin.Typ.Max.Unit V (BR)DSS (1)V GS = 0 V I DS = 200 mA 130V I DSS V GS = 0 V V DS = 50 V 200µA I GSS V GS = 20 V V DS = 0 V 500nA V GS(Q)V DS = 10 V I D = 250 mA 24V V DS(ON)V GS = 10 V I D = 20 A 2V G FS (2)V DS = 10 V I D = 10 A 10mho C ISS V GS = 0 V V DS = 50 V f = 1 MHz 830pF C OSS V GS = 0 V V DS = 50 V f = 1 MHz 470pF C RSSV GS = 0 VV DS = 50 Vf = 1 MHz35pF1.T J = 150°C2.GFS sorts for each unit see Table .Table 5.DynamicSymbol Test conditionsMin.Typ.Max.Unit P OUT V DD = 50 V I DQ = 250 mAf = 30 MHz 350450W G PS V DD = 50 V I DQ = 250 mA P OUT = 350 W f = 30 MHz 2225dB h D V DD = 50 VI DQ = 250 mA P OUT = 350 Wf = 30 MHz 6065%Load MismatchV DD = 50 V I DQ = 250 mA P OUT = 350 W f = 30 MHzAll Phase Angles3:1VSWRTable 6.G FS sortsSymbolValue A 10 ÷ 10.99B 11 ÷ 11.99C 12 ÷ 12.99D 13 ÷ 13.99E 14 ÷ 14.99F 15 ÷ 15.99G 16 ÷ 16.99H17 ÷ 18SD2943Impedance 3 ImpedanceFigure 2.Impedance Data SchematicTable 7.Impedance dataf Z IN (Ω)Z DL (Ω)30 MHz 1.3 - j 2.9 3.1 + j 2.3108 MHz 1.4 - j 2.4 1.9 + j 1.4175 MHz 1.4 - j 2.2 1.7 +j 1.6Doc ID 11584 Rev 35/15Typical performance SD29436/15Doc ID 11584 Rev 34 Typical performanceFigure 5.Gate-source voltage vs caseFigure 6.Maximum thermal resistance vs.SD2943Typical performance Figure 7.Output power vs input power Figure 8.Output power vs input power (atDoc ID 11584 Rev 37/15Test Circuit SD29438/15Doc ID 11584 Rev 35 Test CircuitNote:1Dimension at component symbol are reference for component placement.2Gap between group and trasmission files are 0.056[1.42] typ.3Transmission lime are not 1:1 scale.4Input and output trasmission line are 50ΩTable 8.30 MHz test circuit component part listSymbol DescriptionC1,C90.01 µF / 500 V surface mount ceramic chip capacitor C2, C3750 pF A TC 700B surface mount ceramic chip capacitor C4300 pF A TC 700B surface mount ceramic chip capacitorC5,C10,C11,C14,C1610000 pF A TC 200B surface mount ceramic chip capacitorC6510 pF A TC 700B surface mount ceramic chip capacitor C7300 pF A TC 700B surface mount ceramic chip capacitor C8175-680 pF TYPE 46 standard trimmer capacitor C1247 µF / 63 V aluminum electrolytic radial lead capacitorSD2943Test CircuitDoc ID 11584 Rev 39/15C131200 pF A TC 700B surface mount ceramic chip capacitor C15100 µF / 63 V aluminum electrolytic radial lead capacitor R1,R3 1 K Ω 1 W surface mount chip resistor R2560Ω 2 W wire-wound axils lead resistor T1HF 2-30 MHz surface mount 9:1 transformerT2RG - 142B/U 50Ω coaxial cable OD = 0.165[4.18] L 15”[381.00] covered with 15”[381.00] tinned copper tubular brand 13/65” [5.1] widthL1 1 3/4 turn air-wound 16 AWG ID = 0.219 [5.56] poly-coated magnet wire L2 1 3/4 turn air-wound 12 AWG ID = 0.250 [6.34] bus bar wire RFC1,RFC23 turns 14 AWG wire through fair rite toroid FB1surface mount emi shield bead FB2toroidPCBULTRALAM 2000. 0.030” THK, εr = 2.55, 2 Oz ED CU both sidesTable 8.30 MHz test circuit component part list (continued)Symbol DescriptionTest Circuit SD294310/15Doc ID 11584 Rev 3分销商库存信息: STMSD2943W。

Nsiway NNSS44335588 超低EMI、无需滤波器、5W+3W×2的2.1声道 用户手

10.1

TQFN4×4-28 封装尺寸................................................................................................................... 18

10.2

SOP-28 封装尺寸............................................................................................................................ 19

7.3

NS4358 引脚功能描述 ..................................................................................................................... 9

7.4

芯片印章说明 ................................................................................................................................. 10

NS4358

超低EMI、无需滤波器、5W+3W×2的2.1声道+3D环绕立体声数字音频功放

NS4358 用户手册 V1.1

深圳市纳芯威科技有限公司 2011 年 10 月

Nsiway

1

日期

2011-3-11 2011-10-11

NS4358

超低EMI、无需滤波器、5W+3W×2的2.1声道+3D环绕立体声数字音频功放

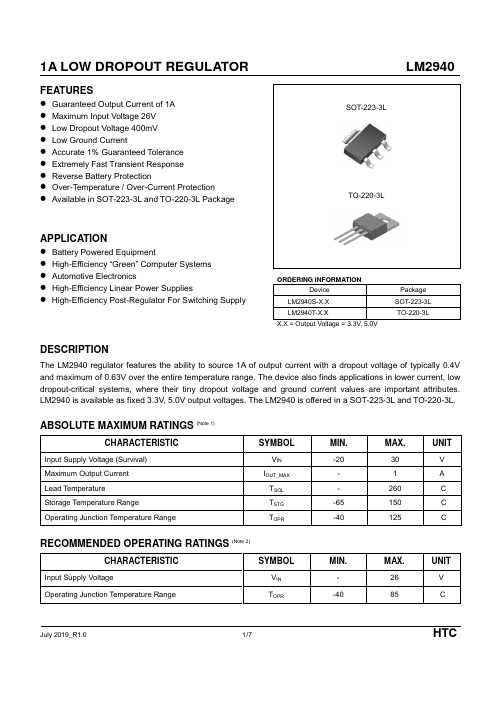

低掉电控制器LM2940说明书

FEATURES●Guaranteed Output Current of 1A ●Maximum Input Voltage 26V●Low Dropout Voltage 400mV●Low Ground Current●Accurate 1% Guaranteed Tolerance●Extremely Fast Transient Response●Reverse Battery Protection●Over-Temperature / Over-Current Protection●Available in SOT-223-3L and TO-220-3L PackageAPPLICATION●Battery Powered Equipment●High-Efficiency “Green” Computer Systems●Automotive Electronics●High-Efficiency Linear Power Supplies●High-Efficiency Post-Regulator For Switching SupplySOT-223-3LTO-220-3LORDERING INFORMATIONDevice Package LM2940S-X.X SOT-223-3L LM2940T-X.X TO-220-3L X.X = Output Voltage = 3.3V, 5.0VDESCRIPTIONThe LM2940 regulator features the ability to source 1A of output current with a dropout voltage of typically 0.4V and maximum of 0.63V over the entire temperature range. The device also finds applications in lower current, low dropout-critical systems, where their tiny dropout voltage and ground current values are important attributes. LM2940 is available as fixed 3.3V, 5.0V output voltages. The LM2940 is offered in a SOT-223-3L and TO-220-3L.ABSOLUTE MAXIMUM RATINGS (Note 1)CHARACTERISTIC SYMBOL MIN. MAX. UNIT Input Supply Voltage (Survival) V IN-20 30 V Maximum Output Current I OUT_MAX- 1 A Lead Temperature T SOL- 260 °C Storage Temperature Range T STG-65 150 °C Operating Junction Temperature Range T OPR-40 125 °CRECOMMENDED OPERATING RATINGS (Note 2)CHARACTERISTIC SYMBOL MIN. MAX. UNIT Input Supply Voltage V IN- 26 V Operating Junction Temperature Range T OPR-40 85 °CHTCORDERING INFORMATIONV OUT Package Order No. Supplied As Status3.3VSOT-223-3L LM2940S-3.3 ReelActiveTO-220-3L LM2940T-3.3 Tube Active5.0V SOT-223-3L LM2940S-5.0 Reel ActiveTO-220-3L LM2940T-5.0 Tube ActiveHTCPIN CONFIGURATIONSOT-223-3L TO-220-3LPIN DESCRIPTIONSOT-223-3L / TO-220-3LPin No.Name Function1 VIN Input Voltage2 GND Ground3 VOUT Output VoltageHTCTYPICAL CIRCUITV IN V OUT* LM2940 can deliver a continuous current of 1A over the full operating temperature. However, the output current is limited by the restriction of power dissipation which differs from packages. A heat sink may be required depending on the maximum power dissipation and maximum ambient temperature of application.With respect to the applied package, the maximum output current of 1A may be still undeliverable.** See Application Information.*** C IN : C IN must be at least 1uF or large to maintain stability.**** C OUT : C OUT must be at least 10uF or large to maintain stability.HTCELECTRICAL CHARACTERISTICS (Note 3)Limits in standard typeface are for T J = 25°C, and limits in boldface type apply over the full operating temperature range. Unless otherwise specified: V IN (Note 4) = V O(NOM) + 1V, I OUT = 5 mA, C IN = 10 μF, C OUT = 10 μFPARAMETER SYMBOL TEST CONDITION MIN. TYP. MAX. UNIT Output Voltage Tolerance V OI OUT = 5mA -1 - 1 %5 mA ≤ I OUT≤ 1A, (V OUT+1V) ≤ V IN≤ 26V -2 - 2 % Line Regulation ΔV LINE I OUT = 5mA, (V OUT+1V) ≤ V IN≤ 26V - 0.06 0.5 % Load Regulation ΔV LOAD V IN = V OUT +1V, 5 mA ≤ I OUT≤ 1A - 0.2 1 %Output VoltageTemperature Coefficient (Note 5)ΔV OUT /ΔT - - 100 ppm/°CDropout Voltage (Note 6)V DROP I OUT = 5mA - 60 180 mV I OUT = 100mA - 170 - mV I OUT = 1A - 400 630mVGround Pin Current (Note 7)I GNDI OUT = 5mA - 250 500 μAI OUT = 1A - 16 25 mA Ground Pin Current at Dropout I GNDDO V IN = 0.5V less than specified V OUT, I OUT = 5mA - 1 - mA Current Limit I CL V OUT = 0V - 1.5 - ANote 1. Exceeding the absolute maximum ratings may damage the device.Note 2. The device is not guaranteed to function outside its operating ratings.Note 3. Stresses listed as the absolute maximum ratings may cause permanent damage to the device. These are for stress ratings. Functional operating of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibly to affect device reliability.Note 4. The minimum operating value for input voltage is equal to either (V OUT,NOM + V DROP), whichever is greater.Note 5. Output voltage temperature coefficient is defined as the worst case voltage change divided by the total temperature range.Note 6. Dropout voltage is defined as the minimum input to output differential voltage at which the output drops 1% below the nominal value. Note 7. Ground current, or quiescent current, is the difference between input and output currents. It's defined by I GND = I IN - I OUT under the given loading condition. The total current drawn from the supply is the sum of the load current plus the ground pin current.HTCAPPLICATION INFORMATIONMaximum Output Current CapabilityThe LM2940 can deliver a continuous current of 1A over the full operating junction temperature range. However, the output current is limited by the restriction of power dissipation which differs from packages. A heat sink may be required depending on the maximum power dissipation and maximum ambient temperature of application. With respect to the applied package, the maximum output current of 1A may be still undeliverable due to the restriction of the power dissipation of LM2940. Under all possible conditions, the junction temperature must be within the range specified under operating conditions. The temperatures over the device are given by:T C = T A + P D X θCA / T J = T C + P D X θJC / T J = T A + P D X θJAwhere T J is the junction temperature, T C is the case temperature, T A is the ambient temperature, P D is the total power dissipation of the device, θCA is the thermal resistance of case-to-ambient, θJC is the thermal resistance of junction-to-case, and θJA is the thermal resistance of junction to ambient. The total power dissipation of the device is given by:P D = P IN – P OUT = (V IN X I IN)–(V OUT X I OUT)= (V IN X (I OUT+I GND)) – (V OUT X I OUT) = (V IN - V OUT) X I OUT + (V IN X I GND)where I GND is the operating ground current of the device which is specified at the Electrical Characteristics. The maximum allowable temperature rise (T Rmax) depends on the maximum ambient temperature (T Amax) of the application, and the maximum allowable junction temperature (T Jmax):T Rmax = T Jmax – T AmaxThe maximum allowable value for junction-to-ambient thermal resistance, θJA, can be calculated using the formula:θJA = T Rmax / P D = (T Jmax – T Amax) / P DLM2940 is available in SOT-223-3L package. The thermal resistance depends on amount of copper area or heat sink, and on air flow. If the maximum allowable value of θJA calculated above is over 137°C/W for SOT-223 -3L package, no heat sink is needed since the package can dissipate enough heat to satisfy these requirements. If the value for allowable θJA falls near or below these limits, a heat sink or proper area of copper plane is required. In summary, the absolute maximum ratings of thermal resistances are as follow:Absolute Maximum Ratings of Thermal ResistanceCharacteristic Symbol Rating Unit Thermal Resistance Junction-To-Ambient / SOT-223-3L θJA-SOT-223-3L137 °C/W Thermal Resistance Junction-To-Ambient / TO-220-3L θJA-TO-220-3L70 °C/WNo heat sink / No air flow / No adjacent heat source / T A=25°CHTCREVISION NOTICEThe description in this datasheet is subject to change without notice to describe its electrical characteristics properly.HTC。

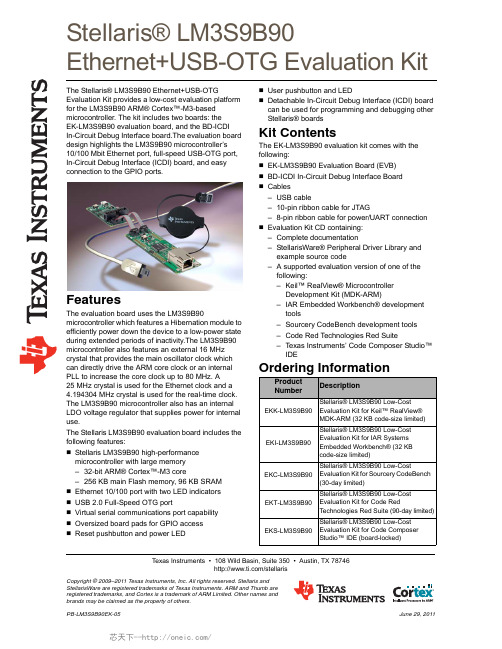

德州仪器,LM3S9B90-I系列, 规格书,Datasheet 资料

Texas Instruments •108 Wild Basin, Suite 350•Austin, TX 78746/stellarisCopyright © 2009–2011 Texas Instruments, Inc. All rights reserved. Stellaris andStellarisWare are registered trademarks of Texas Instruments. ARM and Thumb areregistered trademarks, and Cortex is a trademark of ARM Limited. Other names andbrands may be claimed as the property of others.PB-LM3S9B90EK-05June 29, 2011The Stellaris® LM3S9B90 Ethernet+USB-OTG Evaluation Kit provides a low-cost evaluation platform for the LM3S9B90 ARM® Cortex™-M3-based microcontroller. The kit includes two boards: the EK-LM3S9B90 evaluation board, and the BD-ICDI In-Circuit Debug Interface board.The evaluation board design highlights the LM3S9B90 microcontroller’s10/100 Mbit Ethernet port, full-speed USB-OTG port, In-Circuit Debug Interface (ICDI) board, and easy connection to the GPIO ports.Features The evaluation board uses the LM3S9B90 microcontroller which features a Hibernation module toefficiently power down the device to a low-power state during extended periods of inactivity.The LM3S9B90 microcontroller also features an external 16MHz crystal that provides the main oscillator clock which can directly drive the ARM core clock or an internalPLL to increase the core clock up to 80MHz. A 25MHz crystal is used for the Ethernet clock and a 4.194304MHz crystal is used for the real-time clock. The LM3S9B90 microcontroller also has an internal LDO voltage regulator that supplies power for internal use.The Stellaris LM3S9B90 evaluation board includes the following features: Stellaris LM3S9B90 high-performance microcontroller with large memory –32-bit ARM® Cortex™-M3 core –256KB main Flash memory, 96KB SRAM Ethernet 10/100 port with two LED indicators USB 2.0 Full-Speed OTG port Virtual serial communications port capability Oversized board pads for GPIO access Reset pushbutton and power LED User pushbutton and LEDDetachable In-Circuit Debug Interface (ICDI) board can be used for programming and debugging other Stellaris® boardsKit ContentsThe EK-LM3S9B90 evaluation kit comes with the following:EK-LM3S9B90 Evaluation Board (EVB)BD-ICDI In-Circuit Debug Interface BoardCables–USB cable–10-pin ribbon cable for JTAG–8-pin ribbon cable for power/UART connectionEvaluation Kit CD containing:–Complete documentation–StellarisWare® Peripheral Driver Library andexample source code– A supported evaluation version of one of thefollowing:–Keil™ RealView® MicrocontrollerDevelopment Kit (MDK-ARM)–IAR Embedded Workbench® developmenttools–Sourcery CodeBench development tools –Code Red Technologies Red Suite –Texas Instruments’ Code Composer Studio™ IDEOrdering InformationProductNumber Description EKK-LM3S9B90Stellaris® LM3S9B90 Low-Cost Evaluation Kit for Keil™ RealView® MDK-ARM (32 KB code-size limited)EKI-LM3S9B90Stellaris® LM3S9B90 Low-Cost Evaluation Kit for IAR Systems Embedded Workbench® (32 KB code-size limited)EKC-LM3S9B90Stellaris® LM3S9B90 Low-Cost Evaluation Kit for Sourcery CodeBench(30-day limited)EKT-LM3S9B90Stellaris® LM3S9B90 Low-Cost Evaluation Kit for Code Red Technologies Red Suite (90-day limited)EKS-LM3S9B90Stellaris® LM3S9B90 Low-Cost Evaluation Kit for Code ComposerStudio™ IDE (board-locked)Stellaris®LM3S9B90Ethernet+USB-OTG Evaluation Kit 芯天下--/IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAudio /audio Communications and Telecom /communicationsAmplifiers Computers and Peripherals /computersData Converters Consumer Electronics /consumer-appsDLP®Products Energy and Lighting /energyDSP Industrial /industrialClocks and Timers /clocks Medical /medicalInterface Security /securityLogic Space,Avionics and Defense /space-avionics-defense Power Mgmt Transportation and /automotiveAutomotiveMicrocontrollers Video and Imaging /videoRFID Wireless /wireless-appsRF/IF and ZigBee®Solutions /lprfTI E2E Community Home Page Mailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2011,Texas Instruments Incorporated芯天下--/。

德州仪器(TI)LM3S1968规格书,Datasheet 资料

Stellaris® Development and Evaluation Kits for Red SuiteThe Stellaris Development and Evaluation Kits provide a low-cost way to start designing with Stellaris microcontrollers using Code Red Technologies’ Red Suite development tools. The boards can function as either a complete evaluation target or as a debugger interface to any external Stellaris device.RequirementsYou have a PC with a USB interface, running Microsoft® Windows XP (SP2 or greater) or VistaYou have the Stellaris Evaluation Kit Documentation and Software CD or the standalone Code Red CD found in the Development KitCAUTION: There is a known electrical issue with the FT2232 device that is used in theon-board In Circuit Debug Interface (ICDI). Some USB hubs can cause the device to misbehave, with symptoms ranging from failed enumeration to corrupt data transfers. If you experience trouble when using the on-board ICDI, try connecting the USB cable directly to one of the USB ports on your PC or laptop.Red SuiteThis quickstart shows you how to install the Red Suite development tool and how to use it to build and run an example application on your Stellaris Evaluation Board.Step 1: Install Red Suite1.Insert the Evaluation Kit Documentation and Software CD or the standalone Code RedCD into the CD-ROM drive of your computer. If Autoplay is enabled on your PC, the index.htm file is opened automatically in your default web browser. If Autoplay is not enabled, use Windows Explorer to open the CD manually.2.With the Evaluation Kit CD, click the Tools button and then click the Code Red logoto start the setup program. If the setup program does not start, use Windows Explorer to view the files on the CD and double-click the red_suite_n.n.n.exe file located in the “Tools\Code Red\” directory.With the standalone CD, follow the installer dialog.3.Follow the instructions in the Red Suite installation program. When you get to theDebug Driver Selection window, deselect the “NXP LPC-Line drivers” by clicking the checkbox. After you have clicked the checkbox, the window should look like this:4.Click the Next button to continue with the installation.5.Red Suite continues to install into a single directory of your choice. Unlike manysoftware packages, Red Suite does not install or use any keys in the WindowsRegistry, or use or modify any environment variables (including PATH), which results in a clean installation that does not interfere with anything else on your PC.Step 2: Install the StellarisWare® PackageA full set of C-based peripheral drivers is provided, covering all peripherals and functionality of the Stellaris devices. The StellarisWare package includes various example applications with project files for all major tool vendors that support Stellaris, including Code Red. To install StellarisWare components, follow these steps:1.Navigate to the Tools tab on the Evaluation Kit Documentation and Software CD, orto the Software tab on the Development Kit Documentation and Software CD.NOTE: If you are navigating the CD using Windows Explorer (or a similarapplication), go to the Tools/StellarisWare or Software/StellarisWare directories.2.Click on the 'Install' link next in the StellarisWare section (under Tools or Software) ofthe CD and run the StellarisWare installer. If you prefer to manually installStellarisWare, the installer is a self-extracting zip file that is located in theTools/StellarisWare directory. You can use a zip file extraction utility such as WinZip to manually extract the contents.3.To view the StellarisWare documentation, navigate to the installation directory andclick on the Stellaris Software User’s Guide PDF.Step 3: Start Red Suite and Open a Workspace1.Start the Red Suite IDE by selecting it from the Windows Start menu or clicking theRed Suite 2 icon installed on your desktop. When the IDE loads, it will ask you where to open the workspace folder:red_suite\workspace|2.The Workspace launcher defaults to the following path:C:\Documents and Settings\<username>\My Documents\red_suite\workspaceClick OK to use this default workspace location.3.If this is the first time you have run the Red Suite IDE, a dialog box may appear likethe one shown below. If the dialog appears, click OK to continue.4.The Red Suite IDE now opens with an empty workspace. Go to “Help > Productactivation” to request and activate your evaluation license.5.Follow the instructions to obtain and activate your evaluation license.Important: For the most recent version of the StellarisWare workspaces, check the /stellaris web site for the latest software updates.Step 4: Import and Build Example Projects1.Select the “Import…” option from the File menu in Red Suite.2.Another dialog box appears to let you select what to import. Click “General” toexpand all of the options and then click “Import project(s) from XML description.”Click the Next button when you are finished.3.On the next screen, browse to locate an XML file. The XML description files arelocated in the StellarisWare installation from Step 2, which by default isC:/StellarisWare. From here, the XML file is located in:StellarisWare\boards\{board_name}Select the cr_workspace.xml file and click on “Open”. Then click “Finish”.4. A new window opens containing all of the available projects for your board. You canimport them all to your workspace or select only the examples that you want. If you choose to select only a few examples, the top items must also be imported. These are the StellarisWare library projects, third-party applications, and utilities directories that some projects have dependencies on. In this example, you will only import the “hello”project.With the projects selected, click “OK.” The projects are then imported to your workspace and built.5.You will now see the projects listed in the Project Explorer. The projects willautomatically start to build. Wait for the projects to finish building before continuing.6.To rebuild an individual project, select the project you want to build by clicking anitem in the Project Explorer list. From the “Build and Settings” section of theQuickstart Panel in the bottom left of the Red Suite window, click “Build project‘<name>’ for Debug.” If this option is not visible, expand the “Build and Settings”section by clicking on the downward pointing arrows to the right of the title.Step 5: Debugging a Project1.You will have several example projects from which to choose for your evaluationboard. For an example, start with the hello project. Select the “hello” project in theProject Explorer pane then click “Debug project ‘hello’” from the “Debug and Run” section of the Quickstart Panel.2.You will be asked to select the executable to debug. Choose “Debug/hello.axf” thenpress OK.3.You may get the Windows Security Alert pop-up shown below. Click the Unblockbutton to continue. This is necessary for proper operation of the debugging interface.4.If this is the first time you have used the debugger, Red Suite will also prompt you toconfirm your prospective switch. Click the Yes button to continue.5.The Red Suite debugger automatically connects to your evaluation board, programsthe flash, and runs to the beginning of the main() function. From here, you canexamine and modify memory, program variables and processor registers, setbreakpoints, step, and other typical debugging activities. To run the program, select“Resume” from the Run menu.6.The application starts running, and you should see the text “Hello World!” output tothe display of the evaluation board.Step 6: Build and Run Additional Example ProgramsThere are several additional example projects listed in workspace. If you would like to build another example project, follow the above instructions to import the different projects into the workspace. The quickstart application that came preloaded on the evaluation board is theqs_xxxxx project listed with the examples.Creating a New ProjectOnce you have gone through the StellarisWare example applications, you may want to create your own project to start development. While you can always start with an existing, simple project, sometimes you may want to start fresh.The Code Red tools have a very nice project wizard that lets you create a variety of different project types, with all of the necessary hooks to StellarisWare. It also completely sets up the debug interface so that all you need to do is start writing software, without worrying about setting up your project correctly.To add a new project to your workspace (assuming you’re still using the example described above), go to File > New > C Project.Red Suite will prompt you with a dialog box asking for the type of project you want to create. You’ll focus on the executable project types for this example. In this list, you have 6 options for Stellaris microcontrollers. The simplest one to start with is the “LMI StellarisWare Project” because it provides all of the necessary hooks to StellarisWare drivers.Here, let’s create a new project called “my_project”. If you click Next, the tool will give you the option to automatically set up the hooks into the StellarisWare Graphics Library and USB Library if you need them. The default configuration (if you were to just click Finish instead of Next) sets all of these up for you.supports it), and if you would like to use a buffered (FIFO enabled) UART.You can then select the name of your source directory and choose whether or not you’d like the tool to create a main.c file and startup code for you. We suggest letting the tool do it to make it easy for you. You can also choose to create both Debug and Release versions of your code.Lastly, you select the device you’re using.With your project created, all you really need to do is add your code. The main.c file created for you already sets up the system clock and includes the header files to use the System Control module of the DriverLib. From here, you’re ready to go!ConclusionYou have now installed the Red Suite development tools and used them to build and load an example application on your Stellaris Evaluation Board. From here, you can experiment with the debugger or start creating your own application using the projects as examples. Red Suite has many powerful features to help you develop embedded applications. For further information on Red Suite, start with the “Red Suite Quickstart Guide” installed with the RedSuite tools.Copyright © 2009-2010 Texas Instruments, Inc. All rights reserved. Stellaris and StellarisWare are registered trademarks of Texas Instruments. ARM and Thumb are registered trademarks, and Cortex is a trademark of ARM Limited. Other names and brands may be claimed as the property of others.Texas Instruments108 Wild Basin Rd., Suite 350Austin, TX 78746 /stellarisRev. 1.9 6/1/2010ReferencesThe following references are included on the Stellaris Evaluation Kit Documentation and Software CD and are also available for download at /stellaris :Stellaris Evaluation Kit User's ManualStellarisWare Software , Order Number SW-LM3SStellarisWare Peripheral Driver Library User’s Guide , Order Number SW-DRL-UG In addition, the following website may be useful:Code Red Technologies website at IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDLP®Products Communications and /communicationsTelecomDSP Computers and /computersPeripheralsClocks and Timers /clocks Consumer Electronics /consumer-appsInterface Energy /energyLogic Industrial /industrialPower Mgmt Medical /medicalMicrocontrollers Security /securityRFID Space,Avionics&/space-avionics-defenseDefenseRF/IF and ZigBee®Solutions /lprf Video and Imaging /videoWireless /wireless-appsMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2010,Texas Instruments Incorporated。

LM2940详细资料