实验一、Cadence软件操作步骤

cadence教程

cadence教程Cadence 是一款流行的电路设计和仿真工具。

它广泛应用于电子工程领域,可以帮助工程师进行电路设计、布局、仿真和验证。

以下是一个简单的 Cadence 教程,帮助你快速入门使用该软件。

第一步: 下载和安装 Cadence首先,你需要从 Cadence 官方网站下载适用于你操作系统的Cadence 软件安装包。

在下载完成后,双击安装包文件并按照安装向导的指示进行安装。

第二步: 创建新项目打开 Cadence 软件后,你将看到一个初始界面。

点击“File”菜单,然后选择“New”来创建一个新的项目。

第三步: 添加电路元件在新项目中,你可以开始添加电路元件。

点击菜单栏上的“Library”按钮,然后选择“Add Library”来添加一个元件库。

接下来,使用菜单栏上的“Place”按钮来添加所需的电路元件。

第四步: 连接电路元件一旦添加了电路元件,你需要使用连线工具来连接它们。

点击菜单栏上的“Place Wire”按钮,然后将鼠标指针移到一个元件的引脚上。

点击引脚,然后按照电路的设计布局开始连接其他元件。

第五步: 设置仿真参数在完成电路布局后,你需要设置仿真参数。

点击菜单栏上的“Simulate”按钮,然后选择“Configure”来设置仿真器类型、仿真时间等参数。

第六步: 运行仿真设置完成后,你可以点击菜单栏上的“Simulate”按钮,然后选择“Run”来运行仿真。

仿真过程会模拟电路的运行情况,并生成相应的结果。

总结通过这个简单的 Cadence 教程,你了解了如何下载安装Cadence 软件、创建新项目、添加电路元件、连接元件、设置仿真参数和运行仿真。

掌握了这些基本操作后,你可以进一步学习和探索 Cadence 的更多功能和高级技巧。

祝你在使用Cadence 中取得成功!。

CADENCE仿真流程

CADENCE仿真流程1.设计准备在进行仿真之前,需要准备好设计的原理图和布局图。

原理图是电路的逻辑结构图,布局图是电路的物理结构图。

此外,还需要准备好电路的模型、方程和参数等。

2.确定仿真类型根据设计需求,确定仿真类型,包括DC仿真、AC仿真、时域仿真和优化仿真等。

DC仿真用于分析直流电路参数,AC仿真用于分析交流电路参数,而时域仿真则用于分析电路的时间响应。

3.设置仿真参数根据仿真类型,设置仿真参数。

例如,在DC仿真中,需要设置电压和电流源的数值;在AC仿真中,需要设置信号源的频率和幅度;在时域仿真中,需要设置仿真的时间步长和仿真时间等。

4.模型库选择根据设计需求,选择合适的元件模型进行仿真。

CADENCE提供了大量的元件模型,如晶体管、二极管、电感、电容等。

5.确定分析类型根据仿真目标,确定分析类型,例如传输功能分析、噪声分析、频率响应分析等。

6.仿真运行在仿真运行之前,需要对电路进行布局和连线。

使用CADENCE提供的工具对电路进行布局和连线,并生成物理设计。

7.仿真结果分析仿真运行后,CADENCE会生成仿真结果。

利用CADENCE提供的分析工具对仿真结果进行分析,观察电路的性能指标。

8.优化和修改根据仿真结果,对电路进行优化和修改。

根据需要,可以调整电路的拓扑结构、参数和模型等,以改进电路的性能。

9.再次仿真和验证根据修改后的电路,再次进行仿真和验证,以确认电路的性能指标是否得到改善。

最后需要注意的是,CADENCE仿真流程并不是一成不变的,根据具体的设计需求和仿真目标,流程可能会有所调整和修改。

此外,CADENCE还提供了许多其他的工具和功能,如电路板设计、封装设计、时序分析等,可以根据需要进行使用。

cadence使用方法

cadence使用方法Cadence 是一种流行的电子设计自动化(EDA)工具,用于VLSI(Very Large Scale Integration)设计和仿真。

它由美国卡内基梅隆大学的Circuit Design Group开发,是IC设计工程师广泛使用的一种工具。

Cadence 提供了一整套的工具,包括电路设计、物理布局、封装设计以及信号完整性仿真等。

1.工程设置:在开始之前,你需要设置你的工程。

这包括指定设计库和工作目录。

你可以在Cadence的命令行界面输入"set"命令,设置Cadence工程的相关参数。

2.电路设计:在Cadence中,你可以使用Virtuoso Schematic Editor或者Silicon Ensemble Schematic Editor进行电路设计。

你可以从菜单中选择相应的元件,然后将它们拖放到画布上,并连接它们。

你还可以设置元件的参数和属性。

3.电路仿真:完成电路设计后,你可以使用Spectre或者HSPICE等仿真工具来验证你的设计。

你需要定义相应的仿真参数,如仿真器类型、仿真时间等。

Cadence还提供了仿真结果的分析和波形显示,以便你评估电路的性能和稳定性。

4.物理布局:5.物理验证:完成物理布局后,你需要进行物理验证,以确保设计的可制造性和可靠性。

Cadence提供了Innovus和Tempus等工具,用于进行电压引脚冲突检查、信号完整性分析和时序分析等。

这些工具可以帮助你发现潜在的物理问题,并提供相应的解决方案。

6.封装设计:在完成物理验证后,你需要设计封装。

Cadence提供了封装设计工具,如Allegro Package Designer。

你可以定义芯片的引脚布局和间距规则,并生成封装文件。

7.电路板设计:当你完成芯片设计后,你可能需要进行电路板设计。

Cadence提供了Allegro PCB Designer等工具,用于进行电路板布局和连线。

Cadence实验教程

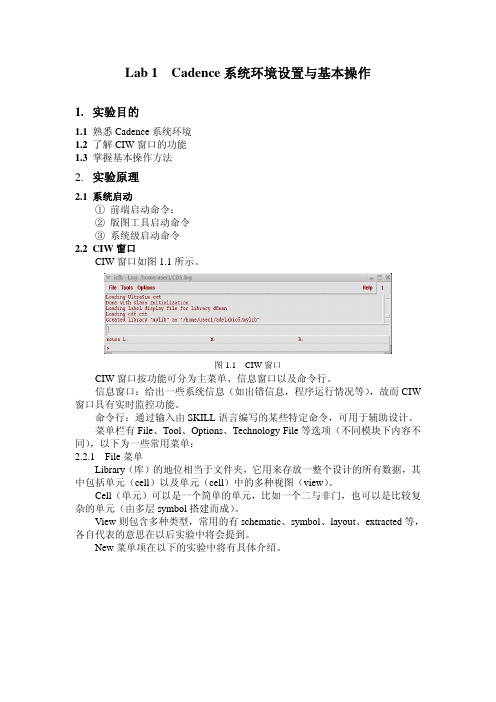

④ cd ~/VLE_5033/Diva ⑤ layoutPlus & 3.2 运行 Cadence 系统 3.2.1 电路原理图设计工具-Schematic Editor

图 1.7 New Library 窗口

图 1.8 Create New File 窗口

图 1.9 Schematic Editing 窗口 图 1.10 Layout Editor 窗口 图 1.11 LSW 窗口

Cadence 系统安装过程中已经设置了通用的盲键,但用户可以根据自己的需 要自行设置,在 CIW 窗口中,选择 Options→Bindkeys,可以对所有设置的盲键 自定义。常用盲键在 Edit 和 Add 等菜单中都有定义,点击选择 Edit,下拉菜单 中的 Stretch 选项的盲键为[m],而 Move 选项的盲键为[M],Select 选项中的 Filter 则为[^r]。用[ ]来表示盲键是 Cadence 系统自带的习惯,本实验系统中予以保留。 三种盲键分别表示为:

① 浏览 Schematic Editing 窗口,最顶部窗口栏显示为:Virtuoso Schematic Editing:mylib nand2,显示当前编辑的电路名称。

② 顶部第二行状态栏(Status Bar)以红色显示 x 与 y 的坐标,在编辑中, 常常需要位置的准确量度,坐标精度为 0.1um。

在设计过程中,除了可以使用图标快捷方式外,还有盲键(Bindkey)快捷 方式。比如添加元件,可以在 Add 菜单下选择 Instance 来弹出 Add Instance 窗口, 也可以点击图标 Add Instance 来弹出 Add Instance 窗口,盲键快捷方式则为直接 在键盘上按“i”键即可。对比三种方式,盲键最为方便快捷。

cadence 教程

cadence 教程Cadence 是一种电子设计自动化工具,常用于模拟、验证和布局设计。

它可以帮助工程师在各种电子系统中设计和验证电路,从而提高电路设计的效率和可靠性。

下面将介绍一些 Cadence 的基本使用方法和技巧。

1. 创建新项目要使用 Cadence,首先需要创建一个新项目。

可以通过菜单栏上的"File" -> "New"来创建新项目。

然后输入项目名称、路径等信息,并选择适当的项目类型。

2. 添加电路在 Cadence 中,可以通过绘制电路原理图来添加电路。

可以使用"Create Schematic"工具来创建新的电路原理图。

在绘制电路原理图时,注意使用正确的元件符号和连线方式。

3. 设置仿真参数在进行电路仿真之前,需要设置仿真参数。

可以通过菜单栏上的"Simulator" -> "Edit Simulation"来打开仿真设置窗口。

在仿真设置窗口中,可以设置仿真类型(如DC、AC、Transient 等)、仿真时间范围、仿真步长等参数。

4. 运行仿真设置好仿真参数后,可以通过菜单栏上的"Simulator" -> "Run Simulation"来运行仿真。

运行仿真后,可以查看仿真结果,如电压波形、电流波形等。

5. 进行验证在验证电路设计时,可以使用 Cadence 提供的调试工具和验证功能。

可以通过菜单栏上的"Debug" -> "Start Debugging"来启动调试。

在调试过程中,可以查看电路元件的属性、信号的波形等信息,以发现和解决问题。

6. 进行布局设计在电路设计完成后,可以进行布局设计。

可以使用 Cadence 提供的布局工具来布局电路版图。

布局时,要注意合理安排电路元件的位置和走线方式,以满足电路设计的要求。

cadence icadvm使用流程

cadence icadvm使用流程1.打开Cadence ICADV,并选择新建项目。

Open Cadence ICADV and choose new project.2.在弹出的对话框中输入项目名称和路径,并点击确定。

Enter the project name and path in the pop-up dialog box, and click OK.3.在项目管理器中右键单击设计库,选择新建设计库。

Right-click on the design library in the project manager and choose to create a new design library.4.输入设计库名称,并选择路径,然后点击确定。

Enter the design library name, choose the path, and click OK.5.在设计库中右键单击设计组,选择新建设计组。

Right-click on the design group in the design library and choose to create a new design group.6.输入设计组名称,并选择路径,然后点击确定。

Enter the design group name, choose the path, and click OK.7.在设计组中右键单击设计单元,选择新建设计单元。

Right-click on the design unit in the design group and choose to create a new design unit.8.输入设计单元名称,并选择路径,然后点击确定。

Enter the design unit name, choose the path, and click OK.9.在设计单元中设计电路原理图。

Design the circuit schematic in the design unit.10.完成设计后保存文件,关闭Cadence ICADV。

Cadence入门使用说明

• 1.确认服务器打开,将IP地址更改为 192.123.123.150,进入Xbrowser浏览器 • 2.单击CAD1500,输入用户名和密码,进入 Solaris系统

• 3打开终端,进入文件夹目录,输入icfb&启 动软件,主要中间有个空格。

启动后出现如下界面

· 4点击Tools-Library Manager进入Library Manager界面

上面显示的是文件管理窗口,可以看到文件存放的结构,其中Library就是文 件夹,Cell就是一个单元,View就是Cell的不同表现形式,比如一个mos管 是一个Cell,但是mos管有原理图模型,有版图模型,有hspice参数模型, 有spectre参数模型等,这就列举了Cell的4个View。他们之间是树状的关系, 即,Library里面有多个Cell,一个Cell里面有多个View。

• 5建立新的Library

• 6文件夹建好了后,我们要建立原理图

注意ViewName是填的schematic,Tool用的是这个。点 击OK之后发现Library Manager里面有如下变化:

• 7双击View中的schematic打开schematic editing窗口进行版图绘制

• Cadence绘制版图常用的快捷键 R 矩形 C 复制 Q 显示属性 DEL 删除 shift+O 旋转 shift+M 粘合 C+F3 镜像

Cadence基本操作、快捷键、基础知识

一、基本操作(一)电路图绘制1、登陆到UNIX系统。

在登陆界面,输入用户名***和密码***** 。

2、Cadence的启动。

登录进去之后,点击Terminal出现窗口,输入icfb命令,启动Cadence软件。

3、根据设计指标及电路结构,估算电路参数。

4、利用Candence原理图的输入。

(1)Composer的启动。

在CIW窗口新建一个单元的Schematic视图。

(2)添加器件。

在comparator schematic窗口点击Add-Instance或者直接点i,就可以选择所需的器件。

(3)添加连线。

执行Add-Wire,将需要连接的部分用线连接起来。

(4)添加管脚。

执行Add-Pin和直接点p,弹出添加管脚界面。

(5)添加线名。

为设计中某些连线添加有意义的名称有助于在波形显示窗口中显出该条线的信号名称,也可以帮助检查电路错误。

点击Add-Wire Name,弹出新窗口,为输入输出线添加名称。

为四端的MOS器件的衬底添加名称vdd!或gnd!,其中!表示全局变量。

(6)添加电源信号,根据不同的仿真电路设置不同的电源参数。

(7)保存并检查。

点击schematic窗口上的Check and Save按钮,察看是否有警告或者错误。

如果有,察看CIW窗口的提示。

4、利用Candence原理图的输入。

(二)电路图仿真(1)启动模拟仿真环境。

在comparator schematic窗口,选择Tools-Analog Environment,弹出模拟仿真环境界面。

(2)设置模型库。

(3)设置分析类型。

在仿真窗口,点击Choose Analyses按钮,弹出Choose Analyses窗口,该窗口中列出了各种仿真类型,依次进行各种仿真,如ac、dc、tran,进行交流仿真、直流仿真、瞬态仿真。

(4)设置波形显示工具。

Cadence中有两种波形显示工具:AWD和wavescane,在仿真窗口选择Session-assign,在弹出的窗口中可以选择波形显示工具为AWD或wavescane。

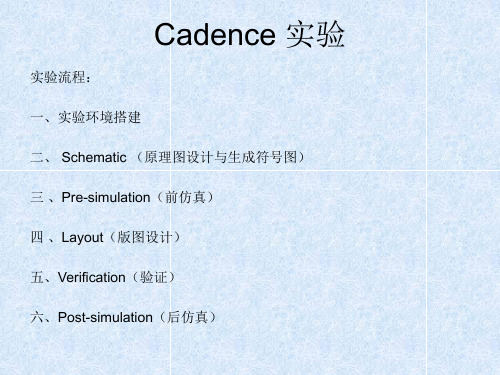

Cadence实验

实验报告要求:1、封面要求:集成电路设计技术实验报告专业、学号、姓名2、正文要求:要求有以下几项:A、实验名称B、实验目的C、实验步骤D、出现问题及解决方法E 时间试验1名称:Candence软件操作准备试验目的:了解熟悉虚拟机的概念、linux常用命令;熟练操作文件的挂载,虚拟机以及Candence 的启动。

试验步骤:熟悉相关概念,启动虚拟机,建立自己的文件夹,挂载库“csmc06lib_ver4”以及文件夹“models”并拷贝到自己建立的文件夹中;在自己建立文件夹的路径下启动Candence。

出现问题及解决:虚拟机:虚拟机(VM)是支持多操作系统并行运行在单个物理服务器上的一种系统,能够提供更加有效的底层硬件使用。

在虚拟机中,中央处理器芯片从系统其它部分划分出一段存储区域,操作系统和应用程序运行在“保护模式”环境下。

在一台电脑上将硬盘和内存的一部分拿出来虚拟出若干台机器,每台机器可以运行单独的操作系统而互不干扰,这些“新”机器各自拥有自己独立的CMOS、硬盘和操作系统,你可以像使用普通机器一样对它们进行分区、格式化、安装系统和应用软件等操作,还可以将这几个操作系统联成一个网络。

在虚拟系统崩溃之后可直接删除不影响本机系统,同样本机系统崩溃后也不影响虚拟系统,可以下次重装后再加入以前做的虚拟系统。

虚拟机以及Candence的启动见计算机中拷贝的相关资料。

文件的挂载:就是将windows操作系统下的文件共享到linux操作系统中,见计算机中拷贝的相关资料。

本实验将windows下的库“csmc06lib_ver4”共享到linux中,并拷贝到自己建立的目录中。

实验一虚拟机以及Candence的启动1、点击桌面“VMare Workstation”的图标,进入VMare Workstation工作界面。

2、点击菜单“file”中的子菜单“open”,找到虚拟机的安装路径。

3、路径找到后,点击文件名为“red hat linux”的虚拟机文件,然后点击“打开”。

CADENCE仿真步骤

CADENCE仿真步骤1.电路设计:首先,需要使用电路设计软件(例如OrCAD)绘制电路原理图。

在设计电路时,应该合理选择电路元件,确保其参数和规格满足设计要求。

2.创建电路网络:在CADENCE中创建电路网络是第一步。

通过将电路原理图导入到CADENCE中,可以建立电路的模型。

在建立电路网络时,应定义元件的参数值,并将其连接起来。

3.定义仿真设置:在进行仿真之前,需要设置仿真参数。

这些参数包括仿真类型(例如直流、交流、蒙特卡罗等)、仿真步长、仿真时间等。

此外,还可以设置其他参数,如故障分析、参数扫描等。

4. 运行仿真:设置好仿真参数后,可以开始运行仿真了。

CADENCE 提供了多种仿真工具,如PSpice、Spectre等,可以根据不同的需求选择适合的工具。

在仿真过程中,CADENCE会使用电路元件的模型计算电路参数,根据仿真设置提供的信息生成相应的结果。

5.分析仿真结果:一旦仿真完成,CADENCE会生成仿真结果文件。

通过分析仿真结果,可以评估电路设计的性能。

常见的仿真结果包括电流、电压、功耗、频率响应等。

可以将仿真结果与预期结果进行比较,找出设计中的问题并进行优化。

6.优化电路设计:根据仿真结果,可以对电路设计进行调整和优化。

优化可以包括选择不同的元件、调整元件参数、改变电路拓扑等。

通过不断迭代仿真和优化,可以逐步改进电路设计,使其达到预期的性能指标。

7.验证仿真结果:当设计经过一系列的优化后,需要验证仿真结果是否可靠。

一种常用的验证方法是进行物理验证,即将最终的电路设计制作出来并测量其实际性能。

通过比较实际测量结果与仿真结果,可以验证仿真的准确性,并进行必要的修正。

8. 导出设计文件:一旦电路设计完成并验证通过,就可以将设计文件导出,准备进一步的生产制造。

将设计文件导出为标准的格式(如Gerber文件),可以将其发送给制造商进行生产。

总结:CADENCE仿真步骤包括电路设计、创建电路网络、定义仿真设置、运行仿真、分析仿真结果、优化电路设计、验证仿真结果和导出设计文件。

cadence使用教程

cadence使用教程Cadence是一种电路设计和仿真软件,非常适合电子工程师用于电路设计和分析。

在本教程中,我们将介绍如何使用Cadence进行基本的电路设计和仿真。

首先,打开Cadence软件,并新建一个新项目。

请确保你已经安装了Cadence软件,并且拥有一个有效的许可证。

在新项目中,你需要定义电路的基本参数,如电源电压、电阻值等。

可以通过绘制原理图的方式来完成这些参数的定义。

在绘图界面中,你可以选择不同的元件,包括电源、电阻、电容、电感等。

你可以使用菜单栏中的工具来放置和连接这些元件。

一旦电路图绘制完成,你可以对电路进行仿真。

首先,需要选择合适的仿真器。

Cadence提供了多种仿真器,如Spectre和HSPICE。

选择一个适合你电路的仿真器,并设置仿真参数,如仿真时间、仿真步长等。

在仿真之前,你首先需要对电路进行布局。

布局涉及将电路中的元件放置在芯片上,并根据布线规则进行连接。

Cadence提供了强大的布局工具,可以帮助你完成这个过程。

完成布局后,你可以进行后仿真。

后仿真涉及将布局好的电路导入到仿真器中,并进行仿真分析。

你可以查看电路的性能指标,如电压、电流和功耗等。

除了基本的电路设计和仿真,Cadence还提供了其他功能,如噪声分析、温度分析和优化设计等。

你可以根据需要选择适合的功能。

总的来说,Cadence是一个功能强大的电路设计和仿真软件。

通过本教程,你可以学会如何使用Cadence进行基本的电路设计和仿真。

希望这对你的电子工程项目有所帮助。

CADENCE实验报告

收集相关电路设计资料,了解实验原理和电路设计要求。

实验操作流程制定

根据实验目的和要求,制定详细的实验操作流程,确保实验顺利 进行。

电路设计

01

02

03

电路原理图绘制

使用CADENCE软件绘制 电路原理图,确保电路设 计正确无误。

元器件选型与布局

根据电路设计需求,选择 合适的元器件,并进行合 理的布局,以提高电路性 能。

实验细节

在实验过程中,我对一些细节问题处理不够得当,影响了 实验结果。未来应更加注重实验细节,确保每一步操作的 准确性。

对未来实验的展望

拓展实验内容

01

希望未来能够进一步拓展实验内容,涵盖更多的CADENCE软件

功能和技术领域。

加强理论结合

02

希望能够加强理论与实践的结合,使实验内容更加丰富和有意

Cadence

Palladium

这是一个高保真度模拟器,用于 在数字和模拟混合信号IC设计中 进行精确仿真。

Cadence

Encounter

这是一个全面的IC物理验证解决 方案,用于确保设计的正确性和 可靠性。

电路设计基本流程

1. 需求分析

明确设计目标,理解系统需求。

2. 规格制定

定义电路性能参数,如功耗、速度和面积等 。

7. 导出GDSII

将版图导出为GDSII格式,供制造使用。

实验涉及的理论知识

电路分析

数字电路设计

理解电阻、电容、电感等基本元件的 工作原理。

理解逻辑门、触发器等数字电路的基 本设计方法。

模拟电路设计

了解放大器、滤波器等模拟电路的基 本设计方法。

03 实验步骤与操作

实验准备

cadence 实验手册

Virtuoso Analog Design Environment中文实验手册Version 5.1.41虚拟机:操作平台:Linux AS5 软件版本:IC 5141 实验模块:ADE编译:06级-程涛目录实验一、熟悉Virtuoso Analog Design Environment (1)实验二、Schematic Entry (5)实验三、模拟仿真 (12)实验四、显示仿真结果 (21)实验五、仿真结果分析 (30)实验六、参数分析 (42)实验七、使用OCEAN 和SKILL语言(略) (45)实验八、使用Corner分析工具 (46)实验九、Monte Carlo 分析 (49)实验十、优化分析 (58)实验十一、Component Description Format(CDF)参数 (63)实验十二、Macromodels、Subcircuits和Inline Subcircuits (67)实验十三、例化设计 (73)实验十四、继承连接 (76)实验一、熟悉Virtuoso Analog Design Environment实验步骤:一、登录Linux操作系统,用安装软件的用户登录,最好不要用root用户。

二、打开Linux的终端,进入软件所在文件夹,比如我的是/home/chengtao/adelabic5,输入cd /home/chengtao/adelabic5,即可进入,注意在安装时有一个lnx86.cshrc的文件,在每次进入Cadence之前都应该先运行以下命令:source lnx86.cshrc ,然后再终端中输入icms & ,稍等片刻,即可进入Cadence 图形界面CIW,如下图所示(会弹出一个Cadence的介绍窗口,关闭即可)。

三、打开一个尖峰检测电路。

1、选择Tool下的Library Manager ,即可弹出Library Manager对话框,总共有三栏分别为:Library、Cell、View,只有在Library下有目录,另外两个是空的,点traning,在Cell下便会显示很多目录,我们选择点击peakTestv,在View下会出现一个schematic,双击便会弹出一个对话框,如下图所示:2、选中peakDetectv ,peakDetectv会被白色的正方形线包围,然后依次执行Design—Hierarchy—Descend Edit (可以使用快捷键E),会蹦出一个小对话框,在View Name中选择schematic,点击Ok,则会弹出一个电路图,如下图所示:3、用鼠标选中一个Ampv,按下E键,将ViewName设置为Veriloga,点击OK,即可弹出这个器件的Verilog-a语言描述,可以仔细参考一下,先不要关闭。

cadence palladium使用流程

使用Cadence Palladium进行模拟是电子设计自动化(EDA)中的重要环节。

以下是使用Cadence Palladium的基本流程:

1. 启动软件:首先,打开Cadence Palladium软件。

2. 创建新项目:在软件中创建一个新的模拟项目。

3. 设置项目参数:在项目创建向导中,你需要为你的项目设置一些参数,例如项目名称、保存路径等。

4. 创建电路图:在项目中,你需要创建或导入电路图。

这可以通过使用库中的组件,或直接在画布上绘制来完成。

5. 配置模拟参数:在电路图设置完成后,你需要配置模拟参数,例如模拟的开始和结束时间、模拟精度等。

6. 运行模拟:配置完成后,你可以运行模拟。

在模拟过程中,你可以查看实时的波形、数据和统计信息。

7. 分析结果:模拟结束后,你可以分析结果。

Palladium提供了一系列的分析工具,帮助你理解和优化你的设计。

8. 保存和导出:最后,别忘了保存你的项目和结果。

你还可以将结果导出为报告或其他格式,以便于分享或进一步分析。

以上就是使用Cadence Palladium的基本流程。

需要注意的是,每个步骤都有许多子步骤和选项,你可能需要花一些时间来熟悉这些功能和设置。

同时,为了获得最佳的结果,你可能需要具备一定的电子设计和模拟背景知识。

实验一、Cadence软件操作步骤

实验一基本门电路设计——电路仿真一、实验内容:完成CMOS 反相器的电路设计完成CMOS 反相器的电路设计实验目的掌握基本门电路的设计方法掌握基本门电路的设计方法熟悉Cadence 的设计数据管理结构,以及定制设计的原理图输入、电路仿真、版图设计、版图验证工具的使用二、实验目的:基于csmc05工艺,完成一个具有逻辑反相功能的电路设计要求:设计要求:1.反相器的逻辑阈值在Vdd/2附近,即噪声容限最大2.反相器的版图高度限制为24微米,电源和地线宽度各为2微米3.反相器宽度限制为mos 器件不折栅4.为了给顶层设计留出更多的布线资源,版图中只能使用金属1和多晶硅作为互连线,输入,输出和电源、地线等pin脚必须使用金属15.版图满足设计规则要求,并通过LVS 检查三、设计过程:启动icfb1.建立自己的设计库2.用Virtuoso Schematic Composer 画电路图3. 在Analog Design Environment中进行电路仿真4. 用Virtuoso (XL)Layout Editer 画版图5. 利用diva 工具进行DRC检查,用dracula进行DRC和LVS验证。

四、实验步骤1.Cadence软件操作步骤:(1).点击桌面虚拟机快捷方式图标;(2).打开虚拟机(存放路径:F:\cadence);(3).启动虚拟机(4).单击右键,Open Teminal,弹出终端对话框,输入Cadence启动命令icfb&(&是后台运行的意思)。

2.. 新建一个库建立自己的Design Lib第一步:CIW-> Tools-Library manager第二步:File-New弹出“New Library ”对话框,在“Name”项填写要建的design lib的名字,这里是“lesson1”,选择“Attach to an existing techfile”第三步:弹出”Attach Design Library to Technology File”对话框,在“Technology Library”中选择st023.新建一个电路图(1)File->New->Cellview(2)弹出“Create New File”对话框,“Library Name”项选择“lesson1”“Cell Name”项填入”inv”,“Tool”项选择”Composer-Schematic”“Tool”项确定后, 相应的“View Name”项会出现内容因而无需输入”,点击“OK”后就进入Virtuso Schematic。

Cadence教程(D422)PDF.pdf

规定:本实验教材中红色为键入命令或字符,兰色为菜单项,紫色为键盘功能键;“单击”指鼠标左键按下一次。

实验一、Virtuoso Schematic Editor实验目的:掌握电原理图(schematic)设计输入方法。

[1]启动IC Design 软件:首先,登陆Linux,在username文件夹中建立一个你命名的文件夹,然后在Terminal窗口中进入这个文件夹,在该文件夹目录下输入:icfb&,(这样,你在cadence中做的一切工作都会自动保存在这个文件夹中,如果直接icfb&的话,会导致你的工作成果,例如:电路图、仿真结果等,会在/home中保存,影响其他人的使用)[2]建立新库、新单元以及新视图(view):首先,输入icfb&后,出现下图窗口在图中CIW窗口中依次打开:Tools->Library Manager,出现下图窗口:在图中窗口中依次打开:File->New->Library,出现下图窗口:输入Library Name:test,然后点OK。

(注意下面的保存路径就是你第一步建立的文件夹)出现下一个窗口:选中Attach to an existing techfile,然后OK。

出现下一个窗口:选中右下方Technology Library:chrt35dg_SiGe,然后OK。

下面我们来画一个nand2电路。

选中左侧的test,在Library Manager 窗口,File->New->Cellview,如下图:在弹出的“Create New File”窗口Cell Name栏中,nand2 Tool栏中,选Composer-SchematicOK,如下图[3]添加元件(实例instance)在弹出的“Virtuos o Schematic Editing:…”窗口中,左边为工具栏,选instance 图标(或i)单击“Add instance”窗口Library栏最右侧Browser,弹出“Library Browser-…”窗口,Library选chrt35dg_SiGe,Cell选nmos_3p3, View选symbol鼠标回到“Add instance”窗口,Model name栏:nmos_3p3, width(Total Width): 3.0u , Length: 0.5u,Hide 如下图在“Virtuoso Schematic Editing:…”窗口, 鼠标左键单击一次,间隔一定距离再单击一次,这样就增加了2个nmos元件,ESC(试一试:先选中一个元件,再q ,查看/改变属性)。

Cadence基本操作、快捷键、基础知识

一、基本操作(一)电路图绘制1、登陆到UNIX系统。

在登陆界面,输入用户名***和密码***** 。

2、Cadence的启动。

登录进去之后,点击Terminal出现窗口,输入icfb命令,启动Cadence软件。

3、根据设计指标及电路结构,估算电路参数。

4、利用Candence原理图的输入。

(1)Composer的启动。

在CIW窗口新建一个单元的Schematic视图。

(2)添加器件。

在comparator schematic窗口点击Add-Instance或者直接点i,就可以选择所需的器件。

(3)添加连线。

执行Add-Wire,将需要连接的部分用线连接起来。

(4)添加管脚。

执行Add-Pin和直接点p,弹出添加管脚界面。

(5)添加线名。

为设计中某些连线添加有意义的名称有助于在波形显示窗口中显出该条线的信号名称,也可以帮助检查电路错误。

点击Add-Wire Name,弹出新窗口,为输入输出线添加名称。

为四端的MOS器件的衬底添加名称vdd!或gnd!,其中!表示全局变量。

(6)添加电源信号,根据不同的仿真电路设置不同的电源参数。

(7)保存并检查。

点击schematic窗口上的Check and Save按钮,察看是否有警告或者错误。

如果有,察看CIW窗口的提示。

4、利用Candence原理图的输入。

(二)电路图仿真(1)启动模拟仿真环境。

在comparator schematic窗口,选择Tools-Analog Environment,弹出模拟仿真环境界面。

(2)设置模型库。

(3)设置分析类型。

在仿真窗口,点击Choose Analyses按钮,弹出Choose Analyses窗口,该窗口中列出了各种仿真类型,依次进行各种仿真,如ac、dc、tran,进行交流仿真、直流仿真、瞬态仿真。

(4)设置波形显示工具。

Cadence中有两种波形显示工具:AWD和wavescane,在仿真窗口选择Session-assign,在弹出的窗口中可以选择波形显示工具为AWD或wavescane。

cadence_实验

• 4、vi .cdsinit 在文件的最后一行的上面添加如下 内容(添加内容的前面没有分号) : • load(“/opt/mentor/caliber/lib/caliber.skl”) • load(“/opt/mentor/caliber/lib/caliber.4.3.skl”) • 主要用于版图的验证使用 • 如图所示:

• 接着添加vdd 与gnd

• 添加管脚,使用快捷键p,Pin Names 为in,Direction 为input, Usage 为schematic,然后在原理图编辑窗口空白处点击一下鼠标, 会出现输入管脚in 。

• 使用相同的方法,添加输出管脚out,此时Pin Names 为out, Direction 为output,Usage 为schematic 。

•

• 创建视图单元/原理图(cell view):在主 窗口中Tools->Library Manager,在 Library 中单击 wo(刚才建立的新库),在 Library Manager 窗口,然后选择File->New->Cell View,设置Cell Name为inv,View Name 为Schematic,Tool为ComposerSchematic,点击OK ,弹出Schematic Editing的空白窗口。

一、实验环境搭建

• 1、解压TSMC0.35.tgz 使用命令:tar –xzf TSMC0.35.tgz • 2、新建一个工作目录:mkdir jiang 将用到的工艺文件和 显示文件(在TSMC035/Virtuoso 下面)拷贝至工作目录 jiang下 。 • 工艺文件:035ms.tf 显示文件:display.drf • 3、拷贝IC工具自带的.cdsinit文件到工作目录jiang下面 3 IC .cdsinit jiang • cp /opt/asic_labs/apps/IC5141/tools.lnx86/dfII/cdsuser/.cdsi nit ./ • 这样,在原理图和版图界面中就可以使用快捷键了。

Cadence教程

规定:本实验教材中红色为键入命令或字符,兰色为菜单项,紫色为键盘功能键;“单击”指鼠标左键按下一次。

实验一、Virtuoso Schematic Editor实验目的:掌握电原理图(schematic)设计输入方法。

[1]启动IC Design 软件:首先,登陆Linux,在username文件夹中建立一个你命名的文件夹,然后在Terminal窗口中进入这个文件夹,在该文件夹目录下输入:icfb&,(这样,你在cadence中做的一切工作都会自动保存在这个文件夹中,如果直接icfb&的话,会导致你的工作成果,例如:电路图、仿真结果等,会在/home中保存,影响其他人的使用)[2]建立新库、新单元以及新视图(view):首先,输入icfb&后,出现下图窗口在图中CIW窗口中依次打开:Tools->Library Manager,出现下图窗口:在图中窗口中依次打开:File->New->Library,出现下图窗口:输入Library Name:test,然后点OK。

(注意下面的保存路径就是你第一步建立的文件夹)出现下一个窗口:选中Attach to an existing techfile,然后OK。

出现下一个窗口:选中右下方Technology Library:chrt35dg_SiGe,然后OK。

下面我们来画一个nand2电路。

选中左侧的test,在Library Manager 窗口,File->New->Cellview,如下图:在弹出的“Create New File”窗口Cell Name栏中,nand2Tool栏中,选Composer-SchematicOK,如下图[3]添加元件(实例instance)在弹出的“Virtuoso Schematic Editing:…”窗口中,左边为工具栏,选instance 图标(或i)单击“Add instance”窗口Library栏最右侧Browser,弹出“Library Browser-…”窗口,Library选chrt35dg_SiGe,Cell选nmos_3p3, View选symbol鼠标回到“Add instance”窗口,Model name栏:nmos_3p3, width(Total Width): , Length: ,Hide 如下图在“Virtuoso Schematic Editing:…”窗口, 鼠标左键单击一次,间隔一定距离再单击一次,这样就增加了2个nmos元件,ESC(试一试:先选中一个元件,再q ,查看/改变属性)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验一基本门电路设计——电路仿真

一、实验内容:

完成CMOS 反相器的电路设计完成CMOS 反相器的电路设计

实验目的

掌握基本门电路的设计方法掌握基本门电路的设计方法

熟悉Cadence 的设计数据管理结构,以及定制设计的原理图输入、电路仿真、版图设计、版图验证工具的使用

二、实验目的:基于csmc05工艺,完成一个具有逻辑反相功能的电路

设计要求:设计要求:

1.反相器的逻辑阈值在Vdd/2附近,即噪声容限最大

2.反相器的版图高度限制为24微米,电源和地线宽度各为2微米

3.反相器宽度限制为mos 器件不折栅

4.为了给顶层设计留出更多的布线资源,版图中只能使用金属1和多晶硅作为互连线,输入,输出和电源、地线等pin脚必须使用金属1

5.版图满足设计规则要求,并通过LVS 检查

三、设计过程:

启动icfb

1.建立自己的设计库

2.用Virtuoso Schematic Composer 画电路图

3. 在Analog Design Environment中进行电路仿真

4. 用Virtuoso (XL)Layout Editer 画版图

5. 利用diva 工具进行DRC检查,用dracula进行DRC和LVS验证。

四、实验步骤

1.Cadence软件操作步骤:

(1).点击桌面虚拟机快捷方式图标;

(2).打开虚拟机(存放路径:F:\cadence);

(3).启动虚拟机

(4).单击右键,Open Teminal,弹出终端对话框,输入Cadence启动命令icfb&(&是后台运行的意思)。

2.. 新建一个库

建立自己的Design Lib

第一步:

CIW-> Tools-Library manager

第二步:File-New

弹出“New Library ”对话框,在“Name”项填写要建的design lib的名字,这里是“lesson1”,选择“Attach to an existing techfile”

第三步:

弹出”Attach Design Library to Technology File”对话框,在“Technology Library”中选择st02

3.新建一个电路图

(1)File->New->Cellview

(2)弹出“Create New File”对话框,“Library Name”项选择“lesson1”“Cell Name”项填入”inv”,“Tool”项选择”Composer-Schematic”“Tool”项确定后, 相应的“View Name”项会出现内容因而无需输入”,点击“OK”后就进入Virtuso Schematic。

(3).添加元器件并修改属性(快捷键i)

Schematic 窗口:Add->Instance,在“Add Instance ”中,点击Browse 在“Add Instance 中,点击Browse,在“Library Browser”中,选择需要添加的Instance,选择需要添加的Library:st02 Cell: mp,Cellview: symbol,

编辑元件的属性:修改MOSFET的Length=550nm, Total Width=6um

再添加一个NMOS管st02 cell:mn,Cellview: symbol。

Length=550nm, Total Width=3um。

再从添加analogLib 库里添加电源vdd和地gnd

(4).画线

按快捷键w,画连线。

(4).添加输入输出管脚

按快捷键p,分别添加输入管脚in和输出管脚out,

(6).创建一个符号(Symbol)

Design->Creat Cellview->From Cellview。

弹出窗口OK。

最后生成一个符号,如下图。

(这个符号可以修改,这里先不修改)

4.重新建一个电路图用来仿真

(1)在lesson1下新建一个原理图文件,文件名为inv_test。

如下图。

(2).添加刚刚建好的lesson1里面的inv的symbol,analogLib里的vdd,gnd和vdc。

电源电压DC V oltage设置成5。

连接反相器输入端的vdc不用设置。

5.电路仿真

(1)原理图编辑窗口下,调出模拟仿真环境:Tools->Analog Environment,

(2).添加仿真模型(model):Setup-Model libraries,点Browse,找到CSMC05MMPDK的

模型文件S05mixdtssa0111.scs。

选中后OK,section(opt)填入tt。

然后点add,这样模型就添加上了,注意上面还有很多其他模型,需要去掉,选中上面其他的模型,然后Disable。

OK

(3).选择仿真类型,这里我们先做个直流扫描

Analyses->choose, 点dc,下面点component Parameter, Select Parameter,

点连接反相器的电压源,弹出Select Component Parmeter,选择dc,下图所示。

设置扫描电压范围从0V——5V。

如下图。

OK

这里我们点输入端的连线和输出端的连线(或输出端的管脚)

(5).跑仿真,点击下图右下角的Netlist and Run。

弹出扫描结果,如下图。

如果出错,根据网表描述修改错误。

五、退出系统

退出cadence时,弹出窗口,选择suspend。