Cadence软件介绍

(完整word版)cadence软件介绍

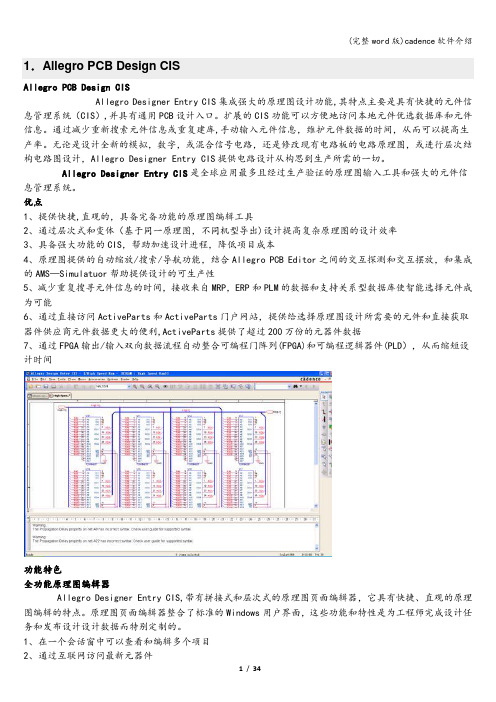

1.Allegro PCB Design CISAllegro PCB Design CISAllegro Designer Entry CIS集成强大的原理图设计功能,其特点主要是具有快捷的元件信息管理系统(CIS),并具有通用PCB设计入口。

扩展的CIS功能可以方便地访问本地元件优选数据库和元件信息。

通过减少重新搜索元件信息或重复建库,手动输入元件信息,维护元件数据的时间,从而可以提高生产率。

无论是设计全新的模拟,数字,或混合信号电路,还是修改现有电路板的电路原理图,或进行层次结构电路图设计,Allegro Designer Entry CIS提供电路设计从构思到生产所需的一切。

Allegro Designer Entry CIS是全球应用最多且经过生产验证的原理图输入工具和强大的元件信息管理系统。

优点1、提供快捷,直观的,具备完备功能的原理图编辑工具2、通过层次式和变体(基于同一原理图,不同机型导出)设计提高复杂原理图的设计效率3、具备强大功能的CIS,帮助加速设计进程,降低项目成本4、原理图提供的自动缩放/搜索/导航功能,结合Allegro PCB Editor之间的交互探测和交互摆放,和集成的AMS—Simulatuor帮助提供设计的可生产性5、减少重复搜寻元件信息的时间,接收来自MRP,ERP和PLM的数据和支持关系型数据库使智能选择元件成为可能6、通过直接访问ActiveParts和ActiveParts门户网站,提供给选择原理图设计所需要的元件和直接获取器件供应商元件数据更大的便利,ActiveParts提供了超过200万份的元器件数据7、通过FPGA输出/输入双向数据流程自动整合可编程门阵列(FPGA)和可编程逻辑器件(PLD),从而缩短设计时间功能特色全功能原理图编辑器Allegro Designer Entry CIS,带有拼接式和层次式的原理图页面编辑器,它具有快捷、直观的原理图编辑的特点。

cadence简介和使用基础

CMOS电路原理图设计

或者CIW窗口→File→Open(打开已有的 Cellview)。

CMOS电路原理图设计

也可以在Library Manager中直接打开。

Cadence的使用基础

双击Schematics,出现原理图编辑器

Cadence的使用基础

之后出现Symbol Generation Options窗口。

Cadence的使用基础

出现界面:

Cadence的使用基础

可将上图修改为惯用图形,以CMOS反相器为例。

CMOS电路原理图设计

电路仿真 仿真环境简介

Schematic图形窗口→Tools→Analog Environment。

Cadence的使用基础

Cadence的使用基础

基本工作环境

局域网资源

Cadence的使用基础

用户登陆 微机登陆后,点击桌面X-manager 图标,

Cadence的使用基础

打开X-manager图标后,点击xstart 图标,出现对话 框,进行如下设置:

Cadence的使用基础

登录时出现Linux-CDE (Common Desktop Environment) 界面

一、 cadence简介和使用

集成电路设计软件技术介绍

EDA技术的概念

EDA技术是在电子CAD技术基础上发展起来 的计算机软件系统,是指以计算机为工作平台, 融合了应用电子技术、计算机技术、信息处理 及智能化技术的最新成果,进行电子产品的自 动设计

EDA工具的功能

利用EDA工具,电子设计师可以从概念、算法、 协议等开始设计电子系统,大量工作可以通过 计算机完成,并可以将电子产品从电路设计、

CADENCE板级PCB设计常用软件

工具介绍1、Allegro PCB Editor用于创建修改设计文件(brd文件),是主要的设计工具。

可以单独启动,也可以在工程管理中启动。

有两种模式:layout mode(平时的布局布线)和symbol creation mode当我们进行手工布局布线时,就工作在layout mode模式下。

Symbol creation mode中可以创建及修改Package symbol(元件封装)、mechanical symbol(机械板形状,如PCB外框图形)、format symbol(公司logo及其它一些说明,类似AD的丝印层)、shape symbol、flash symbol。

2、Padstack Designer创建及修改焊盘padstacksAllegro在创建零件封装时,焊盘需要单独设计,必须使用此工具先创建焊盘。

3、DBDoctor(数据库检查工具)用语检查设计数据中的错误,在设计的每一个阶段执行,可以部分修复数据错误。

在省城光绘文件前必须进行DBDoctor检查。

4、Allegro ConstraintManagerAlegro约束管理器,布局布线约束规则的创建、管理评估、检查等,如各种物理间距,线长、线宽等。

可以与Allegro PCB Editor和Allegro PCB SI等完美集成。

5、Allegro PCB Router自动布线工具,对于有复杂设计规则的高密度电路板处理能力很强,可以在Allegro PCB Editor中用自动不限命令调出来。

6、Allegro PCB SI电路信号完整性仿真工具,反射、串扰等噪声分析。

布局前后都可以使用,布线前主要进行约束规则的开发。

7、Allegro PCB PI电源完整性仿真工具,不能仿真电源平面分割情况,可以使用其它工具替代。

cadence简介

现在需要设置元件参数,有三种方法,①菜单栏-> Edit-> Properties-> Objects,再点击要修改参数的元件,②先选中器件,再键入快捷键q,③选中器件,再点击工具栏Propertiy。

参数可以是以下三种形式的各种数学组合表达式,①变量,②常量,③skill语言函数。变量作参数会在仿真时用到。常量和skill语言函数作参数,在下面就会用到。

同样的方法继续设置NMOS参数,只是模型名为n18,栅长为固定值0.18u,栅宽设为pPar(“wn”)。设置好参数后的电路图如图3.9所示。

注意:①设置参数时不要自己输入单位,系统会自动加上。比如0.18uM是错误的写法。如果非要自己写单位,也要和数值之间留一个空格,否则系统会把M识别为变量。

2.

现在,我们可以启动Cadence了。在终端中输入命令

icfb&

出现Cadence初始界面,如图2.1所示。

然后就会打开Cadence的主控窗口CIW(Command Interpreter Window)。如图2.2所示:

这就是Cadence的集成设计环境,Cadence的大部分工具都可以从这里打开。其中最上方是标题栏,第二行是菜单栏。中间部分是输出区域,许多命令的结果在这里显示。一些出错信息也在这里显示,要学会从输出区域中获取相应的信息。接下来一行是命令输入行。Cadence的许多操作可以通过鼠标执行,也可以通过输入命令来执行。

进入连线命令后,于起点单击左键,再于终点单击左键。画完一段导线后,此时并没有退出画线命令,可以继续画连接线,直到画完所所有的连接线后,按ESC退出画线命令。连好线的电路图如图3.7所示。其中左右两条水平导线是后面连连接端口用的。

还可以对画好的线进行命名,键入快捷键l,在弹出的对话框中输入线名,比如a,点击Hide,然后将字母a移动到要命名的线附近点击左键放下,如果名字离线较远,则要求再单击所要命名的线。

cadence高亮一种孔径的过孔

cadence高亮一种孔径的过孔作为一名电子设计工程师,熟练运用Cadence软件是非常重要的技能。

Cadence是一款强大的电子设计自动化(EDA)工具,可以帮助工程师高效地完成电路设计、仿真和验证等工作。

在实际应用中,Cadence高亮功能能为工程师提供便利,尤其在优化过孔尺寸方面。

本文将详细介绍如何使用Cadence 高亮一种孔径的过孔,以提高电路性能。

首先,我们需要了解孔径的概念。

孔径是指电路板上两个相邻导线之间的开口,它在电路设计中具有举足轻重的地位。

合适的孔径尺寸可以降低信号传输的损耗,提高电路的性能。

因此,在设计过程中,如何选择合适的孔径至关重要。

Cadence软件提供了高亮功能,可以帮助工程师快速地识别和优化过孔。

以下是使用Cadence高亮一种孔径的过孔的步骤:1.打开Cadence软件,导入电路设计文件。

2.在菜单栏中选择“Analyze”→“Highlight”→“Vias”,激活高亮过孔功能。

3.在弹出的对话框中,选择要高亮的过孔类型,如“All Vias”、“SMD Vias”等。

4.设置高亮参数,如颜色、透明度等,以便在设计中更容易识别。

5.确认设置后,点击“Apply”按钮,即可高亮显示所选类型的过孔。

在高亮显示的过孔中,工程师可以逐一检查和分析,找出对电路性能影响较大的孔径。

针对这些关键过孔,可以采取以下措施进行优化:1.调整孔径尺寸:根据电路需求和传输特性,选择合适的孔径尺寸。

通常情况下,孔径越大,传输损耗越小,但制造难度也会增加。

2.更改过孔形状:除了圆形孔径外,还可以尝试使用其他形状,如六角形、方形等,以降低寄生效应。

3.采用埋孔技术:埋孔可以提高电路的电磁兼容性,降低外部干扰。

通过以上方法,工程师可以有针对性地优化过孔,提高电路性能。

在实际操作中,还需要注意以下几点:1.确保孔径尺寸的均匀性:避免在电路板上出现过大或过小的孔径,以免影响信号传输的一致性。

2.考虑孔径的布局:合理分布过孔,避免过于密集或疏松,以降低互相干扰的可能性。

cadence快速入门(物联网其实很简单-cadence简单使用过程)

cadence快速入门(物联网其实很简单-cadence简单使用过程)大家好我是will,这篇我会向大家介绍一下cadence的使用过程,我会和大家一起绘制一块常用的简单的串口工具来帮助大家来快速掌握。

我会把这个当作一个小项目来讲解,会分为多个部分,这是第一部分,简单介绍一下会涉及的软件。

Cadence是一款功能强大的EDA软件,主要用于电路涉及、绘制PCB 版图、仿真等使用。

国内使用较多的EDA软件有三款Altium Designer、PADS、Cadence。

其中AD使用量最大,原因是我们上大学学习的Protel 99se有关,AD为99se的升级版。

PADS在南方用的比较多,主要原因是智能手机大多数的解决方案都会提供PADS版本的原理图与核心布线。

但是我更喜欢Cadence原因是它更符合模块的思路,找功能非常方便,而且功能异常强大,方便,实乃利器啊!阿里狗破戒大师首页安装Cadence安装完成后我们会发现有很多软件图标,但是我们就用下面两个OrCAD Capture咱们用来绘制原理图和元件库的工具。

点击PCB Editor图标会让咱们选择Allegro产品版本,咱们选择Alloegro PCB Designer即可。

Allegro主要主要用于绘制PCB,功能非常强大方便。

最后生成光绘文件(PCB生产文件)提交给板厂生产。

ps:这里说明一下很多用AD的同学经常会提交源文件给板厂生产,will认为这样非常不规范,经常会因为板厂软件版本问题造成生产的差异,所以在这里建议发板尽量使用光绘文件进行。

以上Cadence就简单说完了,通过使用OrCAD和Allegro我们就可以完成原理图和PCB的绘制,接下来我再向大家介绍一款非常牛的软件CAM350,这是一款光绘软件,我经常用来查看光绘文件的可用性。

CAM350所有PCB层级PCB顶层经过CAM350检查完光绘文件的可用性后,就可以找板厂制板了。

我这里使用的是深圳嘉立创进行制板,在打样和小批量制板他家可以称为国内的老大。

Cadence基础仿真分析与电路控制描述

Cadence基础仿真分析与电路控制描述Cadence是一款主要用于集成电路设计和仿真分析的软件工具。

本文档将介绍Cadence的基础仿真分析功能以及电路控制描述的方法。

Cadence基础仿真分析Cadence提供了多种仿真分析工具,包括电路级仿真、时钟级仿真和系统级仿真等。

这些工具可用于验证电路设计的正确性,并进行性能评估。

在进行仿真分析之前,需要进行以下步骤:1. 设计:使用Cadence的设计工具创建电路图和原理图,定义电路的结构和功能。

2. 参数设置:对电路器件进行参数设置,包括电阻、电容、电感等元件的数值设定。

3. 仿真配置:选择适当的仿真工具和仿真设置,如仿真类型、仿真时间和仿真模型等。

接下来,执行仿真分析:1. 电路级仿真:通过电路级仿真工具,如Spectre,对电路进行验证和性能评估。

参数设置和仿真配置完成后,运行仿真并分析仿真结果。

2. 时钟级仿真:通过时钟级仿真工具,如Virtuoso AMS Designer,对电路中时序相关的功能进行验证。

设置时钟源和时钟周期等参数,并运行仿真以验证电路的时序性能。

3. 系统级仿真:通过系统级仿真工具,如Virtuoso System Design Platform,对整个电路系统进行仿真。

设置系统级的参数和信号源,并进行仿真分析。

电路控制描述在Cadence中,可以使用Verilog-A或Verilog-AMS等硬件描述语言来描述电路的行为和控制。

1. Verilog-A:主要用于模拟连续时间的电路。

可以使用Verilog-A描述电路的行为和相互之间的连接关系。

通过编写Verilog-A代码,可以实现电路的仿真和性能分析。

2. Verilog-AMS:结合了连续时间和离散时间的特性,可用于描述混合信号电路。

除了模拟电路行为之外,还可以描述数字电路部分。

通过编写Verilog-AMS代码,可以实现电路的混合仿真和性能分析。

使用这些硬件描述语言时,需要了解其语法和规范,并根据实际需求编写相应的代码。

Cadence软件介绍

Cadence软件介绍Cadence 是一个大型的EDA 软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA 设计和PCB 板设计。

Cadence 在仿真、电路图设计、自动布局布线、版图设计及验证等方面有着绝对的优势。

Cadence 包含的工具较多几乎包括了EDA 设计的方方面面。

下面主要介绍其产品线的范围。

1、板级电路设计系统包括原理图输入、生成、模拟数字/混合电路仿真,fpga设计,pcb编辑和自动布局布线mcm电路设计、高速pcb版图的设计仿真等等。

包括:A、Concept HDL原理图设计输入工具, 有for NT和for Unix的产品。

B、Check Plus HDL原理图设计规则检查工具。

(NT & Unix)D、Allegro Expert专家级PCB版图编辑工具(NT & Unix)E、SPECTRA Expert AutoRouter 专家级pcb自动布线工具F、SigNoise信噪分析工具G、EMControl 电磁兼容性检查工具H、Synplify FPGA / CPLD综合工具I、HDL Analyst HDL分析器J、Advanced Package Designer先进的MCM封装设计工具2、Alta系统级无线设计这部分包括:A、SPW (Cierto Signal Processing Work System)信号处理系统。

可以说,spw包括了matlab的很多功能,连demo都有点象。

它是面向电子系统的模块化设计、仿真和实现的环境。

它的通常的应用领域包括无线和有线载波通信、多媒体和网络设备。

在进行算法设计、滤波器设计、c Code生成、软/硬件结构联合设计和硬件综合的理想环境。

它里面非常有意思的就是信号计算器。

B、HDS (Hardware Design System)硬件系统设计系统它现在是SPW的集成组件之一。

包括仿真、库和分析扩展部分。

Cadenceallegro菜单使用说明

Cadenceallegro菜单使用说明Cadence Allegro菜单使用说明1. 简介本文档旨在向使用Cadence Allegro软件的用户提供菜单使用说明。

Cadence Allegro是一款常用的电子设计自动化(EDA)软件,有助于进行电路设计和 PCB 布局。

2. 界面概述Cadence Allegro的界面主要由工具栏、菜单栏和主编辑区组成。

菜单栏包含了软件的各种功能和工具,方便用户进行设计和布局操作。

3. 菜单使用Cadence Allegro的菜单栏提供了丰富的功能和工具,方便用户进行电路设计和布局。

以下是一些常用菜单和其功能的介绍:3.1 文件菜单文件菜单可以用于新建、打开和保存设计文件,以及进行打印和导出等操作。

- 新建设计文件: `文件` -> `新建`- 打开设计文件: `文件` -> `打开`- 保存设计文件: `文件` -> `保存`- 打印设计文件: `文件` -> `打印`- 导出设计文件: `文件` -> `导出`3.2 编辑菜单编辑菜单提供了一系列用于编辑和处理设计文件的功能和工具。

- 撤销上一步操作: `编辑` -> `撤销`- 复制选定的元件或图形: `编辑` -> `复制`- 粘贴剪贴板的内容: `编辑` -> `粘贴`- 删除选定的元件或图形: `编辑` -> `删除`- 查找和替换元件或图形: `编辑` -> `查找和替换`3.3 视图菜单视图菜单用于控制设计的可见性和显示方式。

- 放大或缩小设计: `视图` -> `放大` / `视图` -> `缩小`- 移动设计视图: `视图` -> `移动`- 显示或隐藏参考层: `视图` -> `参考层`- 显示或隐藏网络标签: `视图` -> `网络标签`3.4 工具菜单工具菜单提供了一些实用的辅助工具和功能。

- 进行电路仿真: `工具` -> `电路仿真`- 进行电路布局和线路连接: `工具` -> `布局和线路连接`- 进行信号完整性分析: `工具` -> `信号完整性分析`- 进行功率完整性分析: `工具` -> `功率完整性分析`4. 其他说明以上仅是一些常用菜单和功能的介绍,Cadence Allegro软件还提供了许多其他有用的功能和工具,用户可以根据自己的需求进行探索和使用。

Cadence和Hspice详细介绍

Cadence 和Hspice 详细介绍

本文为大家带来两款EDA 软件:Cadence 和Hspice 的介绍。

Cadence 介绍

Cadence 是一个大型的EDA 软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA 设计和PCB 板设计。

Cadence 在仿真、电路图设计、自动布局布线、版图设计及验证等方面有着绝对的优势。

Cadence

包含的工具较多几乎包括了EDA 设计的方方面面。

Cadence 的底层软件

Cadence 的底层软件有下面这些:

逻辑设计规划器

这是用于设计早期的规划工具。

其主要用途是延时预测、生成供综合工具使用的线路负载模型。

这个工具是用来在物理设计的早期象逻辑设计者提供

设计的物理信息。

cadence几种模式的用法

cadence几种模式的用法

摘要:

1.介绍Cadence

2.Cadence 的几种模式

3.各种模式的用法详解

4.总结

正文:

Cadence 是一种常用的电路设计软件,它能够帮助工程师进行电路原理图设计、PCB 布局以及电路仿真等工作。

在Cadence 中,有几种不同的模式,工程师可以根据不同的需求选择合适的模式进行操作。

下面我们就来详细介绍一下Cadence 的几种模式以及它们的用法。

首先,我们要介绍的是Cadence 的基本模式,也就是我们平常最常用到的模式。

在这个模式下,我们可以进行原理图的设计、编辑、修改以及查看等操作。

通过这个模式,我们可以轻松地绘制出复杂的电路图,并且可以进行实时的仿真和测试。

其次,Cadence 还提供了一种叫做“布局”的模式。

在这个模式下,我们可以进行PCB 的布局设计。

这个模式下,我们可以选择不同的布局方式,例如自动布局、手动布局等,以满足不同的设计需求。

除此之外,Cadence 还有一种叫做“原理图仿真”的模式。

在这个模式下,我们可以对原理图进行仿真,以测试电路的性能。

这个模式下,我们可以选择不同的仿真工具,例如模拟仿真、数字仿真等,以满足不同的仿真需求。

最后,Cadence 还有一种叫做“库”的模式。

在这个模式下,我们可以

管理和维护电路元件库。

这个模式下,我们可以添加、删除、修改元件的属性,以满足不同的设计需求。

总的来说,Cadence 的不同模式各有各的用途,工程师需要根据实际的设计需求选择合适的模式进行操作。

cadence使用教程

cadence使用教程Cadence是一种电路设计和仿真软件,非常适合电子工程师用于电路设计和分析。

在本教程中,我们将介绍如何使用Cadence进行基本的电路设计和仿真。

首先,打开Cadence软件,并新建一个新项目。

请确保你已经安装了Cadence软件,并且拥有一个有效的许可证。

在新项目中,你需要定义电路的基本参数,如电源电压、电阻值等。

可以通过绘制原理图的方式来完成这些参数的定义。

在绘图界面中,你可以选择不同的元件,包括电源、电阻、电容、电感等。

你可以使用菜单栏中的工具来放置和连接这些元件。

一旦电路图绘制完成,你可以对电路进行仿真。

首先,需要选择合适的仿真器。

Cadence提供了多种仿真器,如Spectre和HSPICE。

选择一个适合你电路的仿真器,并设置仿真参数,如仿真时间、仿真步长等。

在仿真之前,你首先需要对电路进行布局。

布局涉及将电路中的元件放置在芯片上,并根据布线规则进行连接。

Cadence提供了强大的布局工具,可以帮助你完成这个过程。

完成布局后,你可以进行后仿真。

后仿真涉及将布局好的电路导入到仿真器中,并进行仿真分析。

你可以查看电路的性能指标,如电压、电流和功耗等。

除了基本的电路设计和仿真,Cadence还提供了其他功能,如噪声分析、温度分析和优化设计等。

你可以根据需要选择适合的功能。

总的来说,Cadence是一个功能强大的电路设计和仿真软件。

通过本教程,你可以学会如何使用Cadence进行基本的电路设计和仿真。

希望这对你的电子工程项目有所帮助。

EDA工具-Cadence

Cadence[编辑本段]Cadence 公司Cadence Design Systems Inc.是全球最大的电子设计技术(Electronic Design Technologies)、程序方案服务和设计服务供应商。

其解决方案旨在提升和监控半导体、计算机系统、网络工程和电信设备、消费电子产品以及其它各类型电子产品的设计。

其总部位于美国加州圣何塞(San Jose),在全球各地设有销售办事处、设计及研发中心,现拥有员工约4800名,2003年收入约11亿美元。

Cadence公司的电子设计自动化(Electronic Design Automation)产品涵盖了电子设计的整个流程,包括系统级设计,功能验证,IC综合及布局布线,模拟、混合信号及射频IC设计,全定制集成电路设计,IC物理验证,PCB设计和硬件仿真建模等。

同时,Cadence公司还提供设计方法学服务,帮助客户优化其设计流程;提供设计外包服务,协助客户进入新的市场领域。

自1991年以来,该公司已连续在国际EDA市场中销售业绩稳居第一。

全球知名半导体与电子系统公司均将Cadence软件作为其全球设计的标准。

Cadence 中国现拥有员工110人,拥有北京和上海两个研究开发中心,销售网络遍布全国。

Cadence在上海先后建立了高速系统技术中心和企业服务中心,为用户提供高质量、有效的专业设计和外包服务。

Cadenc e北京研发中心主要承担与美国总部EDA软件研发任务,力争提供给用户更加完美的设计工具和全流程服务。

Cadence 公司2003年斥5000万美元巨资在北京投资建立的中关村-Cadence软件学院,立志为中国电子行业培养更多面向集成电路和电子系统的高级设计人才。

Allegro系统互连设计平台Cadence Allegro系统互连平台能够跨集成电路、封装和PCB协同设计高性能互连。

应用平台的协同设计方法,工程师可以迅速优化I/O缓冲器之间和跨集成电路、封装和PCB的系统互联。

Cadence软件介绍

Cadence软件介绍Cadence 就是一个大型得EDA 软件,它几乎可以完成电子设计得方方面面,包括ASIC 设计、FPGA 设计与PCB 板设计。

Cadence 在仿真、电路图设计、自动布局布线、版图设计及验证等方面有着绝对得优势。

Cadence 包含得工具较多几乎包括了EDA 设计得方方面面。

下面主要介绍其产品线得范围。

1、板级电路设计系统包括原理图输入、生成、模拟数字/混合电路仿真,fpga设计,pcb编辑与自动布局布线mcm电路设计、高速pcb版图得设计仿真等等。

包括:A、Concept HDL原理图设计输入工具, 有for NT与for Unix得产品。

B、Check Plus HDL原理图设计规则检查工具。

(NT & Unix)D、Allegro Expert专家级PCB版图编辑工具(NT & Unix)E、SPECTRA Expert AutoRouter 专家级pcb自动布线工具F、SigNoise信噪分析工具G、EMControl 电磁兼容性检查工具H、Synplify FPGA / CPLD综合工具I、HDL Analyst HDL分析器J、Advanced Package Designer先进得MCM封装设计工具2、Alta系统级无线设计这部分包括:A、SPW (Cierto Signal Processing Work System)信号处理系统。

可以说,spw包括了matlab得很多功能,连demo都有点象。

它就是面向电子系统得模块化设计、仿真与实现得环境。

它得通常得应用领域包括无线与有线载波通信、多媒体与网络设备。

在进行算法设计、滤波器设计、c Code生成、软/硬件结构联合设计与硬件综合得理想环境。

它里面非常有意思得就就是信号计算器。

B、HDS (Hardware Design System)硬件系统设计系统它现在就是SPW得集成组件之一。

包括仿真、库与分析扩展部分。

cadence相关软件介绍.

公司概述Cadence是全球电子设计自动化(EDA领先企业,从事软件与硬件设计工具、芯片知识产权与设计服务,目前正致力于EDA产业的转型。

Cadence把此次转型构想命名为EDA360,因为它将包含设计过程中的所有方面,并关注最终产品的可盈利性。

这种应用驱动型方法,能在创建、集成与优化电子设计方面帮助我们的客户以更低的成本和更高的质量完成硅芯片、片上系统设备、以及完整的系统实现。

Cadence Design System, Inc.公司成立于1988年,总部位于美国加州圣荷塞,其设计中心、研发中心和销售部门分布于世界各地。

CADENCE中国1992年Cadence 公司进入中国大陆市场,迄今已拥有大量的集成电路 (IC 及系统设计客户群体。

在过去的二十年里,Cadence公司在中国不断发展壮大,建立了北京、上海、深圳分公司以及北京研发中心、上海研发中心,并于2008年将亚太总部设立在上海,Cadence中国现拥有员工400余人。

北京研发中心和上海研发中心主要承担美国公司总部EDA软件研发任务,力争提供给用户更加完美的设计工具和全流程服务。

Cadence在中国拥有强大的技术支持团队,提供从系统软硬件仿真验证、数字前端和后端及低功耗设计、数模混合RF 前端仿真与DFM以及后端物理验证、SiP封装以及PCB设计等技术支持。

我们的销售方案中还包括提供专业设计服务,VCAD团队为用户提供高质量、有效的设计和外包服务。

把世界顶尖的产品技术和服务融入中国,成为中国电子行业最亲密合作伙伴,和中国电子高科技产业共同腾飞是Cadence 在中国的坚定信念。

市场与趋势Cadence服务于产值达2万亿美元的全球电子市场,其中包括产值超过3000亿美元的半导体市场。

我们的主要垂直市场领域包括:有线与无线通讯;工业、医疗与汽车电子;计算机与消费电子,比如多媒体和个人娱乐设备。

这些领域占全球电子设备营收和半导体营收的90%以上。

Cadence软件介绍

Cadence软件介绍Cadence 是一个大型的EDA 软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA 设计和PCB 板设计。

Cadence 在仿真、电路图设计、自动布局布线、版图设计及验证等方面有着绝对的优势。

Cadence 包含的工具较多几乎包括了EDA 设计的方方面面。

下面主要介绍其产品线的范围。

1、板级电路设计系统包括原理图输入、生成、模拟数字/混合电路仿真,fpga设计,pcb编辑和自动布局布线mcm电路设计、高速pcb版图的设计仿真等等。

包括:A、Concept HDL原理图设计输入工具, 有for NT和for Unix的产品。

B、Check Plus HDL原理图设计规则检查工具。

(NT & Unix)D、Allegro Expert专家级PCB版图编辑工具(NT & Unix)E、SPECTRA Expert AutoRouter 专家级pcb自动布线工具F、SigNoise信噪分析工具G、EMControl 电磁兼容性检查工具H、Synplify FPGA / CPLD综合工具I、HDL Analyst HDL分析器J、Advanced Package Designer先进的MCM封装设计工具2、Alta系统级无线设计这部分包括:A、SPW (Cierto Signal Processing Work System)信号处理系统。

可以说,spw包括了matlab的很多功能,连demo都有点象。

它是面向电子系统的模块化设计、仿真和实现的环境。

它的通常的应用领域包括无线和有线载波通信、多媒体和网络设备。

在进行算法设计、滤波器设计、c Code生成、软/硬件结构联合设计和硬件综合的理想环境。

它里面非常有意思的就是信号计算器。

B、HDS (Hardware Design System)硬件系统设计系统它现在是SPW的集成组件之一。

包括仿真、库和分析扩展部分。

Cadence软件介绍

Cadence软件介绍Cadence 公司旗下有两个产品链,⼀个是IC产品,⼀个是PCB产品。

PCB产品⼜分成PO系列和PS系列,PO就是Orcad系列,PS是⾼端系列,有的⼈称其为Allegro系列,其实并不准确。

Cadence公司在收购Orcad之前,它的原理图⼯具叫Concept HDL,PCB⼯具就是Allegro,也就是PCB Editor,另外还有SI⼯具(做信号完整性分析的)。

Orcad旗下有三个⼯具,原理图⼯具Caputre CIS,原理图仿真⼯具Pspice AD和PSpice AA,还有⼀款PCB布局布线⼯具Layout(PLUs)。

Cadence收购了Orcad之后,就完全将Orcad的Capture CIS和Pspice与⾃⾝的产品做了⽆缝整合⽽摒弃了Orcad以前的Layout(Plus)。

⽬前Cadence的Allegro已经完全作为PCB布线⼯具整合到Orcad系列中。

(到这⾥,你可以明⽩,为什么PS系列不能简单的叫做Allegro了吧)。

那么,Orcad系列和PS系列到底区别在哪⾥呢?1、核⼼产品是⼀样的。

Orcad的原理图是Capture CIS,PS⾥⾯的原理图有两个,⼀个就是Cadence以前的concept HDL,还有,就是Capture CIS,不过在PS⾥⾯,名称改为Design Entry CIS;Orcad的PCB布局布线器是PCB Edior,PS系列⾥⾯的也是两者核⼼是完全⼀样的;Orcad的原理图仿真⼯具是PSpice AD和Pspice AA,PS系列也是,不过在PS系列⾥,把Pspice AD和PspiceAA整合成⼀个产品包,并改名为AMS simulator.2、PS系列⾥⾯分成三个等级,L,XL和GXL,就像⾐服的⼤⼩号⼀样,号越⼤,功能越强,当然价格肯定也越贵了。

L也好,XL也好,Gxl也好,原理图⼯具Capture CIS是没有任何区别的,⽽Pspice 功能不分等级,都是⼀样的。

cadence测量边到边的举例

cadence测量边到边的举例(原创实用版)目录1.引言2.cadence 的含义和作用3.边到边的概念和测量方法4.cadence 测量边到边的举例5.结论正文【引言】在电子设计自动化(EDA)领域,Cadence(凯德尼斯)是一家全球领先的软件公司,它提供各种工具和服务,帮助客户设计、验证和实现电子系统。

Cadence 的工具被广泛应用于印刷电路板(PCB)设计、半导体器件设计、信号完整性分析等领域。

本文将介绍 Cadence 测量边到边的方法及其应用举例。

【cadence 的含义和作用】Cadence(凯德尼斯)这个名字来源于英语中的“节奏、韵律”之意,寓意着其软件工具能够帮助电子设计工程师高效、精准地进行设计,使设计工作像音乐一样富有节奏感。

Cadence 提供了一整套电子设计自动化解决方案,可以帮助工程师从设计概念到产品上市的全过程,提高设计效率和质量。

【边到边的概念和测量方法】边到边(Edge-to-Edge)是指在 PCB 设计中,两个相邻元件的边缘之间的距离。

这个距离对于保证 PCB 的稳定性和信号完整性至关重要。

Cadence 提供了多种测量边到边的方法,包括:1.手动测量:通过视觉观察和手动测量工具进行测量。

这种方法较为耗时,容易出错,但对于简单的设计可行。

2.自动测量:利用 Cadence 的自动布局和布线工具进行测量。

这种方法可以大大提高测量效率和准确性,适用于复杂的设计。

【cadence 测量边到边的举例】假设我们要设计一个 PCB,其中有两个相邻的元件 A 和 B,我们需要测量它们之间的边到边距离。

我们可以按照以下步骤使用 Cadence 进行测量:1.打开 Cadence 软件,导入 PCB 设计文件。

2.在设计文件中选择元件 A 和 B,然后使用 Cadence 的布局工具将这两个元件摆放在 PCB 上。

3.使用 Cadence 的布线工具,为元件 A 和 B 之间的信号线进行布线。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Cadence软件介绍

Cadence 是一个大型的EDA 软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA 设计和PCB 板设计。

Cadence 在仿真、电路图设计、自动布局布线、版图设计及验证等方面有着绝对的优势。

Cadence 包含的工具较多几乎包括了EDA 设计的方方面面。

下面主要介绍其产品线的范围。

1、板级电路设计系统

包括原理图输入、生成、模拟数字/混合电路仿真,fpga设计,pcb编辑和自动布局布线mcm电路设计、高速pcb版图的设计仿真等等。

包括:

A、Concept HDL原理图设计输入工具, 有for NT和for Unix的产品。

B、Check Plus HDL原理图设计规则检查工具。

(NT & Unix)

D、Allegro Expert专家级PCB版图编辑工具(NT & Unix)

E、SPECTRA Expert AutoRouter 专家级pcb自动布线工具

F、SigNoise信噪分析工具

G、EMControl 电磁兼容性检查工具

H、Synplify FPGA / CPLD综合工具

I、HDL Analyst HDL分析器

J、Advanced Package Designer先进的MCM封装设计工具

2、Alta系统级无线设计

这部分包括:

A、SPW (Cierto Signal Processing Work System)信号处理系统。

可以说,spw包括了matlab的很多功能,连demo都有点象。

它是面向

电子系统的模块化设计、仿真和实现的环境。

它的通常的应用领域包括无线和有线载波通信、多媒体和网络设备。

在进行算法设计、滤波器设计、c Code生成、软/硬件结构联合设计和硬件综合的理想环境。

它里面非常有意思的就是信号计算器。

B、HDS (Hardware Design System)硬件系统设计系统

它现在是SPW的集成组件之一。

包括仿真、库和分析扩展部分。

可以进行spw的定点分析行为级和rtl级的代码生成。

C、Mutimedia多媒体(Multimedia Design Kit)

它可以进行多媒体应用的设计,包括电视会议系统、数字电视等等以及任何种类的图象处理系统的设计。

D、无线技术Wireless(IS-136 Verification Environment)

无线电技术标准系统级验证工具,可以在系统级的抽象层上生成、开发和改进遵守IS-54/136 标准的信号处理算法。

在完成硬件结构设计后,就可以使用hds直接生成可综合的hdl描述和相应的标准检测程序(testbench)。

E、IS-95无线标准系统级验证

同上。

F、BONeS网络协议分析和验证的设计工具。

它是一套软件系统,专门用来做多媒体网络结构和协议的设计的。

可以用来快速的生成和分析结构单元之间的信息流的抽象模型,并建立一个完整的无线网络的运作模型。

例如,用户可以改进atm转换器的算法,并建立其基于微处理器包括高速缓存和内存和总线、通信处理方法的应用模型。

G、VCC 虚拟协同设计工具包

它是用来进行基于可重用的ip核的系统级设计环境。

3、逻辑设计与验证(LDV)

LDV包括的模块有:

A、verilog-xl仿真器

B、Leapfrog VHDL仿真器

支持混合语言的仿真,其vhdl语言的仿真是通过编译后仿真,加快了速度。

C、Affirma NC Verilog仿真器

其主要的特点是适合于大系统的仿真。

D、Affirma NC VHDL仿真器

适用于VHDL语言的仿真。

E、Affirema 形式验证工具--等价检验器

F、Verifault-XL 故障仿真器

用来测试芯片的可测性设计的。

G、VeriSure代码覆盖率检查工具

H、Envisia Build Gates 综合工具

4、时序驱动的深亚微米设计

Cadence 的底层软件有:

A、逻辑设计规划器。

这是用于设计早期的规划工具。

其主要用途是延时预测、生成供综合工具使用的线路负载模型。

这个工具是用来在物理设计的早期象逻辑设计者提供设计的物理信息。

B、物理设计规划器。

物理设计的前期规划。

对于大型设计而言,物理设计的前期规划非常重要。

很多流程中,在前期的物理规划(floorplan)结束后,就需要一次反标验证设计的时序。

C、SE (Silicon Ensemble)布局布线器

se是一个布局布线的平台,它可以提供多个布局布线及后期处理软件的接口。

D、PBO Optimization基于布局的优化工具

E、CT-GEN 时钟树生成工具

F、RC参数提取 HyperRules规生成,HyperExtract RC提取,RC简化,和delay计算

G、Pearl静态时序分析

Pearl 除了界面友好的特点外,还有就是可以和spice仿真器交换数据来进行关键路径的仿真。

H、Vampire验证工具

5、全定制ic设计工具

这部分的工具包括:

A、Virtuos Schematic Composer : IC Design Entry

它是可以进行混合输入的原理图输入方式。

支持 vhdl/hdl语言的文本输入。

B、Affirma Analog DEsign Environment

这是一个很好的混合信号设计环境

C、Virtuos Layout Editor版图编辑

它支持参数化单元,应该是一个很好的特性。

D、Affirma Spectra

高级电路仿真器和hspice一类的仿真器。

E、Virtuoso Layout Synthesizer

直接的layout生成工具,小规模设计环境

F、Assura验证环境,包括diva

G、dracula验证和参数提取包

H、ICCragtsman 布局设计的环境。

在面向ip的设计中比较合适。