IC datasheet pdf-CD74AC540,pdf(Octal Buffer_Line Drivers, 3-State)

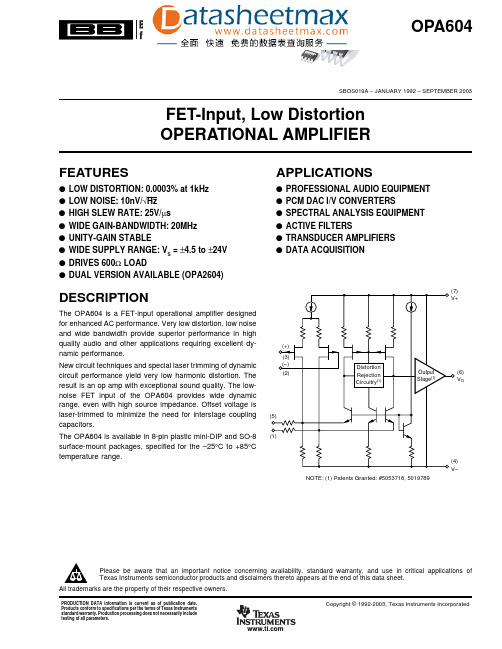

IC datasheet pdf-OPA604,pdf(FET-Input, Low Distortion Operational Amplifier)

fA/√Hz

V dB

Ω || pF Ω || pF

dB

MHz V/µs µs µs

%

V mA mA Ω

V V mA

°C °C °C/W

OPA604

3

SBOS019A

THD + N (%)

Current Noise (fA/ Hz)

TYPICAL CHARACTERISTICS

Copyright © 1992-2003, Texas Instruments Incorporated

ABSOLUTE MAXIMUM RATINGS

Power Supply Voltage ....................................................................... ±25V Input Voltage ............................................................... (V–)–1V to (V+)+1V Output Short Circuit to Ground ................................................ Continuous Operating Temperature .................................................. –40°C to +100°C Storage Temperature ...................................................... –40°C to +125°C Junction Temperature .................................................................... +150°C Lead Temperature (soldering, 10s) AP .......................................... +300°C Lead Temperature (soldering, 3s) AU ............................................ +260°C

IC datasheet pdf-REF1004,pdf(Micropower Voltage Reference)

The REF1004 is offered in an 8-lead Plastic SOIC package and shipped in anti-static rails or tape and reel.

Typical Operating Circuit

NC 1 NC 2 NC 3 Anode 4

IR = 100µA

10Hz ≤ IR ≤ 10kHz

60

120

µV

LONG TERM STABILITY

IR = 100µA

TA = 25°C ± 0.1°C

20

2 (1) This specification applies over the full operating temperature range of 0°C ≤ TA ≤ 70°C. (2) This specification applies over the full operating temperature range of 40°C ≤ TA ≤ +85°C. (3) Denotes the specifications which apply over the full operating temperature range.

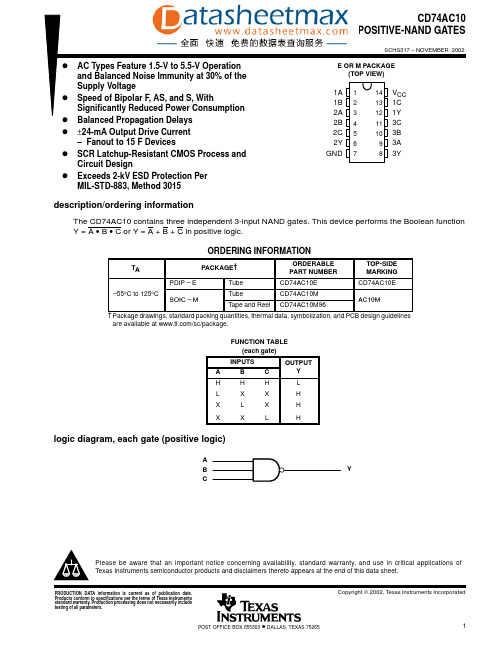

IC datasheet pdf-CD74ACT10,pdf(QUADRUPLE 2-INPUT POSITIVE-NAND GATES)

TRIPLE 3-INPUT POSITIVE-NAND GATESTRIPLE 3-INPUT POSITIVE-NAND GATESIMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements, improvements,and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right,or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI. Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use anynon-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers AudioData Converters AutomotiveDSP BroadbandInterface Digital ControlLogic MilitaryPower Mgmt Optical NetworkingMicrocontrollers SecurityLow Power TelephonyWirelessVideo&ImagingWirelessMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2007,Texas Instruments IncorporatedPACKAGING INFORMATION Orderable DeviceStatus (1)Package Type Package Drawing Pins Package Qty Eco Plan (2)Lead/Ball Finish MSL Peak Temp (3)CD74ACT10EACTIVE PDIP N 1425Pb-Free (RoHS)CU NIPDAU N /A for Pkg Type CD74ACT10EE4ACTIVE PDIP N 1425Pb-Free (RoHS)CU NIPDAU N /A for Pkg Type CD74ACT10MACTIVE SOIC D 1450Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM CD74ACT10M96ACTIVE SOIC D 142500Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM CD74ACT10M96E4ACTIVE SOIC D 142500Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM CD74ACT10M96G4ACTIVE SOIC D 142500Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM CD74ACT10ME4ACTIVE SOIC D 1450Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM CD74ACT10MG4ACTIVE SOIC D 1450Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM (1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan -The planned eco-friendly classification:Pb-Free (RoHS),Pb-Free (RoHS Exempt),or Green (RoHS &no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS):TI's terms "Lead-Free"or "Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all 6substances,including the requirement that lead not exceed 0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free (RoHS Exempt):This component has a RoHS exemption for either 1)lead-based flip-chip solder bumps used between the die and package,or 2)lead-based die adhesive used between the die andleadframe.The component is otherwise considered Pb-Free (RoHS compatible)as defined above.Green (RoHS &no Sb/Br):TI defines "Green"to mean Pb-Free (RoHS compatible),and free of Bromine (Br)and Antimony (Sb)based flame retardants (Br or Sb do not exceed 0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.PACKAGE OPTION ADDENDUM 23-Apr-2007TAPE AND REEL INFORMATION*All dimensions are nominal Device Package Type Package DrawingPinsSPQ Reel Diameter (mm)Reel Width W1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W (mm)Pin1Quadrant CD74ACT10M96SOIC D 142500330.016.4 6.59.0 2.18.016.0Q1*All dimensions are nominalDevice Package Type Package Drawing Pins SPQ Length(mm)Width(mm)Height(mm) CD74ACT10M96SOIC D142500346.0346.033.0。

CD74ACT541中文资料

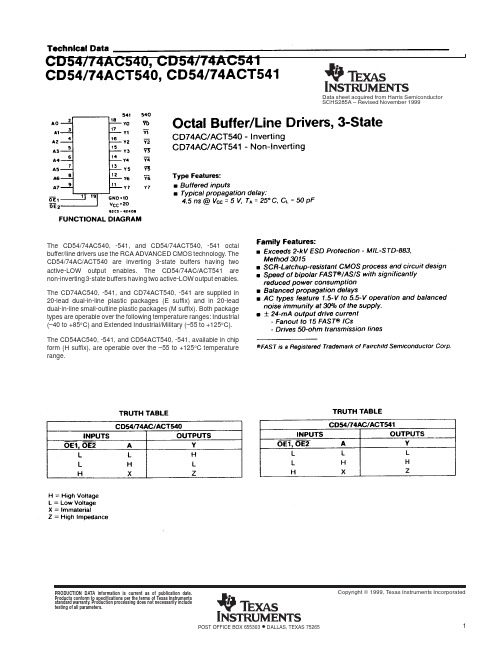

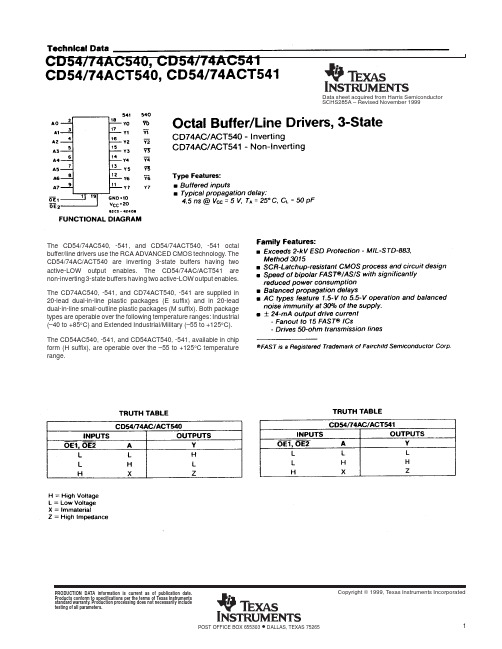

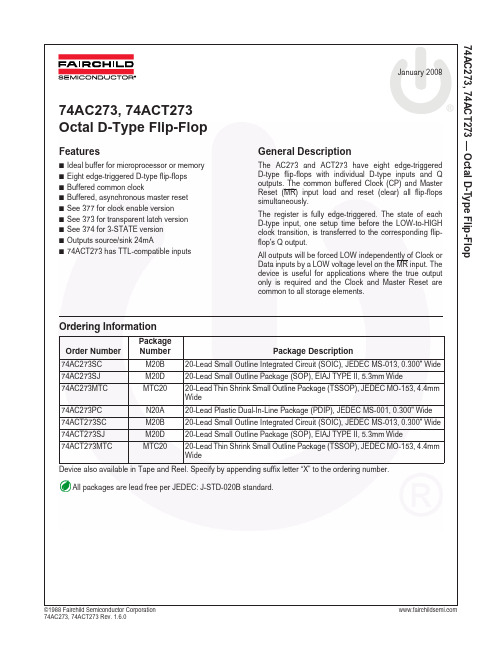

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265Copyright © 1999, Texas Instruments IncorporatedPRODUCTION DATA information is current as of publication date.Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.The CD54/74AC540, -541, and CD54/74ACT540, -541 octal buffer/line drivers use the RCA ADVANCED CMOS technology. The CD54/74AC/ACT540 are inverting 3-state buffers having two active-LOW output enables. The CD54/74AC/ACT541 are non-inverting 3-state buffers having two active-LOW output enables.The CD74AC540, -541, and CD74ACT540, -541 are supplied in 20-lead dual-in-line plastic packages (E suffix) and in 20-lead dual-in-line small-outline plastic packages (M suffix). Both package types are operable over the following temperature ranges: Industrial (–40 to +85°C) and Extended Industrial/Military (–55 to +125°C).The CD54AC540, -541, and CD54ACT540, -541, available in chip form (H suffix), are operable over the –55 to +125°C temperature range.L H ZData sheet acquired from Harris Semiconductor SCHS285A – Revised November 1999MAXIMUM RATINGS,Absolute-Maximum Values:. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .DC SUPPLY-VOLTAGE (V CC)–0.5 to 6 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .DC INPUT DIODE CURRENT, I IK (for V I < –0.5 or V I > V CC + 0.5 V)±20 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .DC OUTPUT DIODE CURRENT, I OK (for V O < –0.5 or V O > V CC + 0.5 V)±50 mA DC OUTPUT SOURCE OR SINK CURRENT per Output Pin, I O (for V O > –0.5 or V O < V CC + 0.5 V)±50 mA. . . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .DC V CC OR GROUND CURRENT (I CC or I GND)±100 mA*. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .PACKAGE THERMAL IMPEDANCE, θJA (see Note 1):E package69°C/W. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .M package58°C/W. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .STORAGE TEMPERATURE (T stg)–65 to +150°C LEAD TEMPERATURE (DURING SOLDERING):. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .At distance 1/16 ± 1/32 in. (1.59 ± 0.79 mm) from case for 10 s maximum+265°C. . . . . . . . . . . . . . . . . . . . . . . .Unit inserted into PC board min. thickness 1/16 in. (1.59 mm) with solder contacting lead tips only+300°C * For up to 4 outputs per device: add ±25 mA for each additional output.NOTE 1:The package thermal impedance is calculated in accordance with JESD 51.2POST OFFICE BOX 655303 • DALLAS, TEXAS 752653 POST OFFICE BOX 655303 • DALLAS, TEXAS 752654POST OFFICE BOX 655303 • DALLAS, TEXAS 75265ns5 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265POST OFFICE BOX 655303 • DALLAS, TEXAS 75265元器件交易网IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinueany product or service without notice, and advise customers to obtain the latest version of relevant informationto verify, before placing orders, that information being relied on is current and complete. All products are soldsubject to the terms and conditions of sale supplied at the time of order acknowledgement, including thosepertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extentTI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarilyperformed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OFDEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICALAPPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, ORWARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHERCRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TOBE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operatingsafeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or representthat any license, either express or implied, is granted under any patent right, copyright, mask work right, or otherintellectual property right of TI covering or relating to any combination, machine, or process in which suchsemiconductor products or services might be or are used. TI’s publication of information regarding any thirdparty’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1999, Texas Instruments Incorporated。

IC datasheet pdf-TL1431,pdf(Precision Programmable Reference)

(5) Maximum power dissipation is a function of TJ(max), θJC, and TC. The maximum allowable power dissipation at any allowable case temperature is PD = (TJ(max) – TC)/θJC. Operating at the absolute maximum TJ of 150°C can affect reliability.

2

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

FEATURES

1

•2 0.4% Initial Voltage Tolerance • 0.2-Ω Typical Output Impedance • Fast Turnon…500 ns

D PACKAGE (TOP VIEW)

CATHODE 1 ANODE 2 ANODE 3 NC 4

II(ref)

Reference input current range

θJA

CD74ACT540中文资料

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265Copyright © 1999, Texas Instruments IncorporatedPRODUCTION DATA information is current as of publication date.Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.The CD54/74AC540, -541, and CD54/74ACT540, -541 octal buffer/line drivers use the RCA ADVANCED CMOS technology. The CD54/74AC/ACT540 are inverting 3-state buffers having two active-LOW output enables. The CD54/74AC/ACT541 are non-inverting 3-state buffers having two active-LOW output enables.The CD74AC540, -541, and CD74ACT540, -541 are supplied in 20-lead dual-in-line plastic packages (E suffix) and in 20-lead dual-in-line small-outline plastic packages (M suffix). Both package types are operable over the following temperature ranges: Industrial (–40 to +85°C) and Extended Industrial/Military (–55 to +125°C).The CD54AC540, -541, and CD54ACT540, -541, available in chip form (H suffix), are operable over the –55 to +125°C temperature range.L H ZData sheet acquired from Harris Semiconductor SCHS285A – Revised November 1999MAXIMUM RATINGS,Absolute-Maximum Values:. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .DC SUPPLY-VOLTAGE (V CC)–0.5 to 6 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .DC INPUT DIODE CURRENT, I IK (for V I < –0.5 or V I > V CC + 0.5 V)±20 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .DC OUTPUT DIODE CURRENT, I OK (for V O < –0.5 or V O > V CC + 0.5 V)±50 mA DC OUTPUT SOURCE OR SINK CURRENT per Output Pin, I O (for V O > –0.5 or V O < V CC + 0.5 V)±50 mA. . . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .DC V CC OR GROUND CURRENT (I CC or I GND)±100 mA*. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .PACKAGE THERMAL IMPEDANCE, θJA (see Note 1):E package69°C/W. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .M package58°C/W. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .STORAGE TEMPERATURE (T stg)–65 to +150°C LEAD TEMPERATURE (DURING SOLDERING):. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .At distance 1/16 ± 1/32 in. (1.59 ± 0.79 mm) from case for 10 s maximum+265°C. . . . . . . . . . . . . . . . . . . . . . . .Unit inserted into PC board min. thickness 1/16 in. (1.59 mm) with solder contacting lead tips only+300°C * For up to 4 outputs per device: add ±25 mA for each additional output.NOTE 1:The package thermal impedance is calculated in accordance with JESD 51.2POST OFFICE BOX 655303 • DALLAS, TEXAS 752653 POST OFFICE BOX 655303 • DALLAS, TEXAS 752654POST OFFICE BOX 655303 • DALLAS, TEXAS 75265ns5 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265POST OFFICE BOX 655303 • DALLAS, TEXAS 75265元器件交易网IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinueany product or service without notice, and advise customers to obtain the latest version of relevant informationto verify, before placing orders, that information being relied on is current and complete. All products are soldsubject to the terms and conditions of sale supplied at the time of order acknowledgement, including thosepertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extentTI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarilyperformed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OFDEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICALAPPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, ORWARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHERCRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TOBE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operatingsafeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or representthat any license, either express or implied, is granted under any patent right, copyright, mask work right, or otherintellectual property right of TI covering or relating to any combination, machine, or process in which suchsemiconductor products or services might be or are used. TI’s publication of information regarding any thirdparty’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1999, Texas Instruments Incorporated。

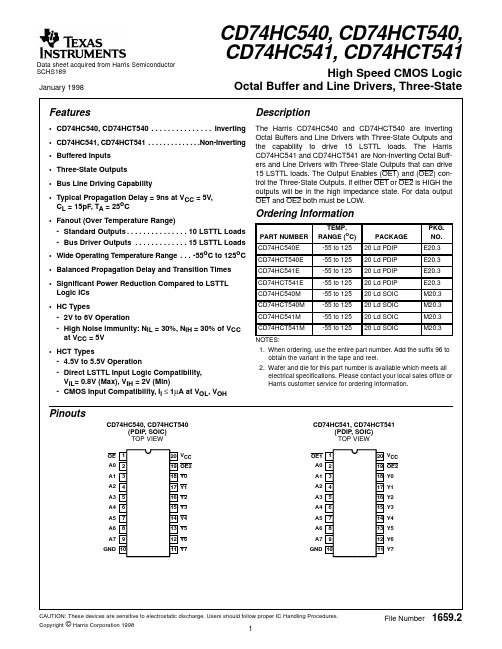

CD74HCT540资料

Data sheet acquired from Harris Semiconductor SCHS189Features•CD74HC540, CD74HCT540 . . . . . . . . . . . . . . .Inverting•CD74HC541, CD74HCT541 . . . . . . . . . . . . . .Non-Inverting •Buffered Inputs •Three-State Outputs •Bus Line Driving Capability•Typical Propagation Delay = 9ns at V CC = 5V ,C L = 15pF, T A = 25o C•Fanout (Over Temperature Range)-Standard Outputs. . . . . . . . . . . . . . .10 LSTTL Loads -Bus Driver Outputs . . . . . . . . . . . . .15 LSTTL Loads •Wide Operating Temperature Range . . .-55o C to 125o C •Balanced Propagation Delay and Transition Times •Significant Power Reduction Compared to LSTTL Logic ICs •HC Types-2V to 6V Operation-High Noise Immunity: N IL = 30%, N IH = 30% of V CC at V CC = 5V •HCT Types- 4.5V to 5.5V Operation-Direct LSTTL Input Logic Compatibility,V IL = 0.8V (Max), V IH = 2V (Min)-CMOS Input Compatibility, I l ≤1µA at V OL , V OHDescriptionThe Harris CD74HC540and CD74HCT540are Inverting Octal Buffers and Line Drivers with Three-State Outputs and the capability to drive 15LSTTL loads.The Harris CD74HC541and CD74HCT541are Non-Inverting Octal Buff-ers and Line Drivers with Three-State Outputs that can drive 15LSTTL loads.The Output Enables (OE1)and (OE2)con-trol the Three-State Outputs.If either OE1or OE2is HIGH the outputs will be in the high impedance state.For data output OE1 and OE2 both must be LOW.Ordering InformationPART NUMBER TEMP.RANGE (o C)PACKAGE PKG.NO.CD74HC540E -55 to 12520 Ld PDIP E20.3CD74HCT540E -55 to 12520 Ld PDIP E20.3CD74HC541E -55 to 12520 Ld PDIP E20.3CD74HCT541E -55 to 12520 Ld PDIP E20.3CD74HC540M -55 to 12520 Ld SOIC M20.3CD74HCT540M -55 to 12520 Ld SOIC M20.3CD74HC541M -55 to 12520 Ld SOIC M20.3CD74HCT541M-55 to 12520 Ld SOICM20.3NOTES:1.When ordering,use the entire part number.Add the suffix 96to obtain the variant in the tape and reel.2.Wafer and die for this part number is available which meets all electrical specifications.Please contact your local sales office or Harris customer service for ordering information.PinoutsCD74HC540, CD74HCT540(PDIP , SOIC)TOP VIEWCD74HC541, CD74HCT541(PDIP , SOIC)TOP VIEW1112131415161718201910987654321OE A0A1A2A3A4A6A5A7GND V CC Y0Y1Y2OE2Y3Y4Y5Y6Y71112131415161718201910987654321OE1A0A1A2A3A4A6A5A7GND V CC Y0Y1Y2OE2Y3Y4Y5Y6Y7January 1998CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.File Number1659.2CD74HC540, CD74HCT540,CD74HC541, CD74HCT541High Speed CMOS LogicOctal Buffer and Line Drivers, Three-State[ /Title (CD74HC540,CD74HCT540,CD74HC541,CD74HCT54Functional DiagramTRUTH TABLEINPUTSOUTPUTSOE1OE2An 540541L L H L H H X X Z Z X H X Z Z LLLHLNOTE:H = HIGH Voltage Level L = LOW Voltage Level X = Don’t CareZ = High ImpedanceD 0Y 0D 2D 4D 6Y 2Y 4Y 6D 1D 3D 5D 7Y 1Y 3Y 5Y 7OE AOE B540541Y 0Y 2Y 4Y 6Y 1Y 3Y 5Y 7Absolute Maximum Ratings Thermal InformationDC Supply Voltage, V CC. . . . . . . . . . . . . . . . . . . . . . . .-0.5V to 7V DC Input Diode Current, I IKFor V I < -0.5V or V I > V CC + 0.5V. . . . . . . . . . . . . . . . . . . . . .±20mA DC Output Diode Current, I OKFor V O < -0.5V or V O > V CC + 0.5V . . . . . . . . . . . . . . . . . . . .±20mA DC Drain Current, per Output, I OFor -0.5V < V O < V CC + 0.5V. . . . . . . . . . . . . . . . . . . . . . . . . .±35mA DC Output Source or Sink Current per Output Pin, I OFor V O > -0.5V or V O < V CC + 0.5V . . . . . . . . . . . . . . . . . . . .±25mA DC V CC or Ground Current, I CC . . . . . . . . . . . . . . . . . . . . . . . . .±50mA Operating ConditionsTemperature Range, T A . . . . . . . . . . . . . . . . . . . . . .-55o C to 125o C Supply Voltage Range, V CCHC Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2V to 6V HCT Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4.5V to 5.5V DC Input or Output Voltage, V I, V O . . . . . . . . . . . . . . . . .0V to V CC Input Rise and Fall Time2V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1000ns (Max) 4.5V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .500ns (Max) 6V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .400ns (Max)Thermal Resistance (T ypical, Note 3)θJA (o C/W) PDIP Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . .125 SOIC Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . .120 Maximum Junction T emperature. . . . . . . . . . . . . . . . . . . . . . .150o C Maximum Storage Temperature Range . . . . . . . . . .-65o C to 150o C Maximum Lead Temperature (Soldering 10s). . . . . . . . . . . . .300o C (SOIC - Lead Tips Only)CAUTION:Stresses above those listed in“Absolute Maximum Ratings”may cause permanent damage to the device.This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.NOTE:3.θJA is measured with the component mounted on an evaluation PC board in free air.DC Electrical SpecificationsPARAMETER SYMBOLTESTCONDITIONS VCC(V)25o C-40o C TO 85o C-55o C TO125o CUNITS V I(V)I O(mA)MIN TYP MAX MIN MAX MIN MAXHC TYPESHigh Level Input Voltage V IH--2 1.5-- 1.5- 1.5-V4.5 3.15-- 3.15 - 3.15-V6 4.2-- 4.2- 4.2-VLow Level Input Voltage V IL--2--0.5-0.5-0.5V4.5-- 1.35- 1.35- 1.35V6-- 1.8- 1.8- 1.8VHigh Level Output VoltageCMOS Loads V OH V IH or V IL-0.022 1.9-- 1.9- 1.9-V -0.02 4.5 4.4-- 4.4 - 4.4-V-0.026 5.9-- 5.9- 5.9-VHigh Level Output VoltageTTL Loads---------V -6 4.5 3.98-- 3.84- 3.7-V -7.86 5.48-- 5.34- 5.2-VLow Level Output VoltageCMOS Loads V OL V IH or V IL0.022--0.1-0.1-0.1V0.02 4.5--0.1-0.1-0.1V0.026--0.1-0.1-0.1VLow Level Output VoltageTTL Loads---------V6 4.5--0.26-0.33-0.4V7.86--0.26-0.33-0.4VInput Leakage Current I I V CC orGND-6--±0.1-±1-±1µAQuiescent Device CurrentI CC V CC or GND 06--8-80-160µA Three-State Leakage Current I OZV IL or V IHV O =V CC or GND6--±0.5-±5.0-±10µAHCT TYPES High Level Input Voltage V IH -- 4.5 to 5.52--2-2-V Low Level Input VoltageV IL -- 4.5 to 5.5--0.8-0.8-0.8V High Level Output VoltageCMOS Loads V OHV IH or V IL-0.024.54.4-- 4.4- 4.4-VHigh Level Output Voltage TTL Loads -6 4.5 3.98-- 3.84- 3.7-VLow Level Output VoltageCMOS Loads V OLV IH or V IL0.02 4.5--0.1-0.1-0.1VLow Level Output Voltage TTL Loads 6 4.5--0.26-0.33-0.4VInput Leakage CurrentI I V CC and GND 0 5.5-±0.1-±1-±1µA Quiescent Device CurrentI CC V CC or GND 0 5.5--8-80-160µA Three-State Leakage CurrentI OZV IL or V IHV O =V CC or GND 5.5--±0.5-±5.0-±10µAAdditional Quiescent Device Current Per Input Pin: 1 Unit Load∆I CCV CC -2.1-4.5 to5.5-100360-450-490µANOTE:For dual-supply systems theoretical worst case (V I = 2.4V , V CC = 5.5V) specification is 1.8mA.DC Electrical Specifications(Continued)PARAMETER SYMBOL TEST CONDITIONSV CC (V)25o C-40o C TO 85o C -55o C TO 125o C UNITS V I (V)I O (mA)MIN TYP MAX MIN MAX MIN MAX HCT Input Loading TableINPUT UNIT LOADSHCT540HCT541A0 - A710.4OE20.750.75OE11.151.15NOTE:Unit load is ∆I CC limit specific in DC Electrical Specifications Table, e.g., 360µA max. at 25o C.Switching Specifications C L = 50pF, Input t r, t f= 6nsPARAMETER SYMBOLTESTCONDITIONS V CC(V)25o C-40o C TO85o C-55o C TO125o CUNITSMIN TYP MAX MIN MAX MIN MAXHC TYPESPropagation Delay t PLH, t PHL C L = 50pFData to Outputs (540)2--110-140-165ns4.5--22-28-33nsC L = 15pF5-9-----nsC L = 50pF6--19-24-28nsData to Outputs (541)t PLZ,t PHZ C L = 50pF2--115-145-175ns4.5--23-29-35nsC L = 15pF5-9-----nsC L = 50pF6--20-25-30nsOutput Enable and Disable to Outputs (540)t PLZ,t PHZ C L = 50pF2--160-200-240ns4.5--32-40-48nsC L = 15pF5-13-----nsC L = 50pF6--27-34-41nsOutput Enable and Disable to Outputs (541)t PLZ,t PHZ C L = 50pF2--160-200-240ns4.5--32-40-48nsC L = 15pF5-14-----nsC L = 50pF6--23-29-35nsOutput Transition Time t THL, t TLH C L = 50pF2--60-75-90ns4.5--12-15-18ns6--10-13-15ns Input Capacitance C I C L = 50pF-10-10-10-10pF Three-State OutputCapacitanceC O--20-20-20-20pFPower Dissipation Capacitance(Notes 4, 5) (540)C PD C L = 15pF5-50-----pFPower Dissipation Capacitance(Notes 4, 5) (541)C PD C L = 15pF5-48-----pF HCT TYPESPropagation Delay t PHL,t PLHData to Outputs (540)C L = 50pF 4.5--24-30-36nsC L = 15pF5-9-----nsData to Outputs (541)t PHL,t PLH C L = 50pF 4.5--28-35-42nsC L = 15pF5-11-----nsOutput Enable and Disable to Outputs (540, 541)t PLZ,t PHZ C L = 50pF 4.5--35-44-53nsC L = 15pF5-14-----nsOutput Transition Time t TLH, t THL C L = 50pF 4.5--12-15-18ns Input Capacitance C I C L = 50pF-10-10-10-10pFThree-State Output CapacitanceC O --20-20-20-20pF Power Dissipation Capacitance (Notes 4, 5) (540, 541)C PDC L = 15pF5-55-----pFNOTES:4.C PD is used to determine the dynamic power consumption, per channel.5.P D = V CC 2 f i (C PD + C L ) where f i =Input Frequency, C L = Output Load Capacitance, V CC = Supply Voltage.Switching SpecificationsC L = 50pF, Input t r , t f = 6ns (Continued)PARAMETERSYMBOL TEST CONDITIONSV CC (V)25o C-40o C TO 85o C -55o C TO 125o C UNITS MIN TYP MAX MIN MAX MIN MAX Test Circuits and WaveformsFIGURE 1.HC TRANSITION TIMES AND PROPAGATIONDELAY TIMES, COMBINATION LOGICFIGURE 2.HCT TRANSITION TIMES AND PROPAGATIONDELAY TIMES, COMBINATION LOGICFIGURE 3.HC THREE-STATE PROPAGATION DELAYWAVEFORM FIGURE 4.HCT THREE-STATE PROPAGATION DELAYWAVEFORMt PHLt PLHt THLt TLH 90%50%10%50%10%INVERTING OUTPUTINPUTGNDV CCt r = 6nst f = 6ns90%t PHLt PLHt THLt TLH 2.7V 1.3V 0.3V1.3V 10%INVERTING OUTPUTINPUTGND3Vt r = 6nst f = 6ns90%50%10%90%GNDV CC 10%90%50%50%OUTPUT DISABLEOUTPUT LOWTO OFFOUTPUT HIGHTO OFFOUTPUTS ENABLEDOUTPUTS DISABLEDOUTPUTS ENABLED6ns 6nst PZH t PHZt PZLt PLZ0.32.7GND3V10%90%1.3V1.3VOUTPUT DISABLEOUTPUT LOWTO OFFOUTPUT HIGHTO OFFOUTPUTS ENABLEDOUTPUTS DISABLEDOUTPUTS ENABLEDt r6nst PZHt PHZt PZLt PLZ6nst f 1.3CD74HC540, CD74HCT540, CD74HC541, CD74HCT541NOTE:Open drain waveforms t PLZ and t PZL are the same as those for three-state shown on the left.The test circuit is Output R L =1k Ωto V CC , C L = 50pF .FIGURE 5.HC AND HCT THREE-STATE PROPAGATION DELAY TEST CIRCUITTest Circuits and Waveforms (Continued)IC WITH THREE-STATE OUTPUT OTHER INPUTS TIED HIGH OR LOW OUTPUT DISABLEV CC FOR t PLZ AND t PZL GND FOR t PHZ AND t PZHOUTPUTR L = 1k ΩC L 50pFIMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI’s publication of information regarding any third party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1999, Texas Instruments Incorporated。

CD74AC540中文资料

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265Copyright © 1999, Texas Instruments IncorporatedPRODUCTION DATA information is current as of publication date.Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.The CD54/74AC540, -541, and CD54/74ACT540, -541 octal buffer/line drivers use the RCA ADVANCED CMOS technology. The CD54/74AC/ACT540 are inverting 3-state buffers having two active-LOW output enables. The CD54/74AC/ACT541 are non-inverting 3-state buffers having two active-LOW output enables.The CD74AC540, -541, and CD74ACT540, -541 are supplied in 20-lead dual-in-line plastic packages (E suffix) and in 20-lead dual-in-line small-outline plastic packages (M suffix). Both package types are operable over the following temperature ranges: Industrial (–40 to +85°C) and Extended Industrial/Military (–55 to +125°C).The CD54AC540, -541, and CD54ACT540, -541, available in chip form (H suffix), are operable over the –55 to +125°C temperature range.L H ZData sheet acquired from Harris Semiconductor SCHS285A – Revised November 1999MAXIMUM RATINGS,Absolute-Maximum Values:. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .DC SUPPLY-VOLTAGE (V CC)–0.5 to 6 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .DC INPUT DIODE CURRENT, I IK (for V I < –0.5 or V I > V CC + 0.5 V)±20 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .DC OUTPUT DIODE CURRENT, I OK (for V O < –0.5 or V O > V CC + 0.5 V)±50 mA DC OUTPUT SOURCE OR SINK CURRENT per Output Pin, I O (for V O > –0.5 or V O < V CC + 0.5 V)±50 mA. . . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .DC V CC OR GROUND CURRENT (I CC or I GND)±100 mA*. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .PACKAGE THERMAL IMPEDANCE, θJA (see Note 1):E package69°C/W. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .M package58°C/W. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .STORAGE TEMPERATURE (T stg)–65 to +150°C LEAD TEMPERATURE (DURING SOLDERING):. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .At distance 1/16 ± 1/32 in. (1.59 ± 0.79 mm) from case for 10 s maximum+265°C. . . . . . . . . . . . . . . . . . . . . . . .Unit inserted into PC board min. thickness 1/16 in. (1.59 mm) with solder contacting lead tips only+300°C * For up to 4 outputs per device: add ±25 mA for each additional output.NOTE 1:The package thermal impedance is calculated in accordance with JESD 51.2POST OFFICE BOX 655303 • DALLAS, TEXAS 752653 POST OFFICE BOX 655303 • DALLAS, TEXAS 752654POST OFFICE BOX 655303 • DALLAS, TEXAS 75265ns5 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265POST OFFICE BOX 655303 • DALLAS, TEXAS 75265元器件交易网IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinueany product or service without notice, and advise customers to obtain the latest version of relevant informationto verify, before placing orders, that information being relied on is current and complete. All products are soldsubject to the terms and conditions of sale supplied at the time of order acknowledgement, including thosepertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extentTI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarilyperformed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OFDEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICALAPPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, ORWARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHERCRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TOBE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operatingsafeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or representthat any license, either express or implied, is granted under any patent right, copyright, mask work right, or otherintellectual property right of TI covering or relating to any combination, machine, or process in which suchsemiconductor products or services might be or are used. TI’s publication of information regarding any thirdparty’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1999, Texas Instruments Incorporated。

74AC540中文资料

2

元器件交易网

74AC540

AC Electrical Characteristics

VCC Symbol tPLH tPHL tPZH tPZL tPHZ tPLZ Parameter Propagation Delay Data to Output Propagation Delay Data to Output Output Enable Time Output Enable Time Output Disable Time Output Disable Time (V) (Note 5) 3.3 5.0 3.3 5.0 3.3 5.0 3.3 5.0 3.3 5.0 3.3 5.0

元器件交易网

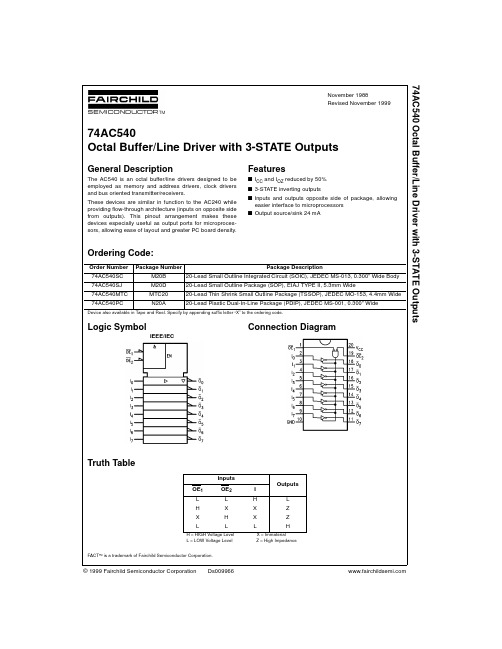

74AC540 Octal Buffer/Line Driver with 3-STATE Outputs

November 1988 Revised November 1999

74AC540 Octal Buffer/Line Driver with 3-STATE Outputs

TA = −40°C to +85°C CL = 50 pF Min 1.0 1.0 1.0 1.0 2.5 2.0 2.0 1.5 1.5 1.0 2.0 1.5 Max 8.0 6.5 7.5 6.0 12.0 9.5 11.0 8.5 14.0 11.0 11.0 9.0 ns ns ns ns ns ns Units

Ds009966

元器件交易网

74AC540

Absolute Maximum Ratings(Note 1)

Supply Voltage (VCC) DC Input Diode Current (IIK) VI = −0.5V VI = VCC + 0.5V DC Input Voltage (VI) DC Output Diode Current (IOK) VO = −0.5V VO = VCC + 0.5V DC Output Voltage (VO) DC Output Source or Sink Current (IO) DC VCC or Ground Current per Output Pin (ICC or IGND) Storage Temperature (TSTG) Junction Temperature (TJ) PDIP 140°C ±50 mA −65°C to +150°C ±50 mA −20 mA +20 mA −0.5V to VCC + 0.5V −20 mA +20 mA −0.5V to VCC + 0.5V −0.5V to +7.0V

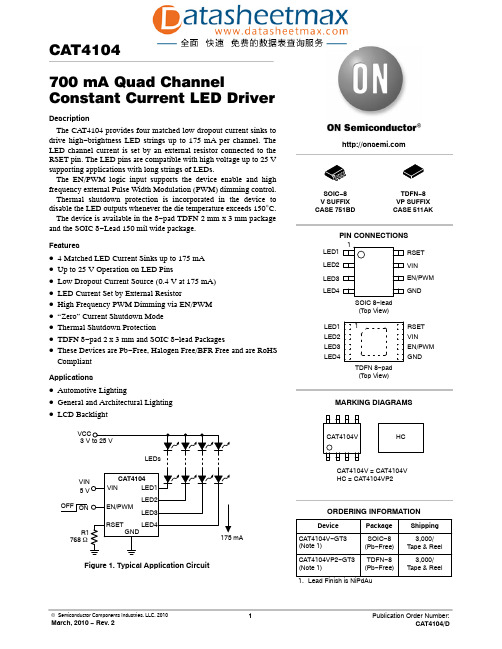

IC datasheet pdf-CAT4104 pdf,datasheet

CAT4104700 mA Quad ChannelConstant Current LED DriverDescriptionThe CAT4104 provides four matched low dropout current sinks to drive high −brightness LED strings up to 175 mA per channel. The LED channel current is set by an external resistor connected to the RSET pin. The LED pins are compatible with high voltage up to 25 V supporting applications with long strings of LEDs.The EN/PWM logic input supports the device enable and high frequency external Pulse Width Modulation (PWM) dimming control.Thermal shutdown protection is incorporated in the device to disable the LED outputs whenever the die temperature exceeds 150°C.The device is available in the 8−pad TDFN 2 mm x 3 mm package and the SOIC 8−Lead 150 mil wide package.Features•4 Matched LED Current Sinks up to 175 mA •Up to 25 V Operation on LED Pins•Low Dropout Current Source (0.4 V at 175 mA)•LED Current Set by External Resistor•High Frequency PWM Dimming via EN/PWM •“Zero” Current Shutdown Mode •Thermal Shutdown Protection•TDFN 8−pad 2 x 3 mm and SOIC 8−lead Packages•These Devices are Pb −Free, Halogen Free/BFR Free and are RoHS CompliantApplications•Automotive Lighting•General and Architectural Lighting •LCD BacklightFigure 1. Typical Application Circuit768 WONOFFSOIC −8V SUFFIX CASE 751BD PIN CONNECTIONSMARKING DIAGRAMSCAT4104V = CAT4104VHC = CAT4104VP2SOIC 8−lead (Top View)Device Package Shipping ORDERING INFORMATIONCAT4104V −GT3(Note 1)SOIC −8(Pb −Free)3,000/Tape & Reel 1.Lead Finish is NiPdAuCAT4104V TDFN −8VP SUFFIX CASE 511AKCAT4104VP2−GT3(Note 1)TDFN −8(Pb −Free)3,000/Tape & ReelGNDVIN RSET LED4LED3LED2LED11EN/PWM GNDVINRSET LED4LED3LED2LED1EN/PWM TDFN 8−pad (Top View)HC1Table 1. ABSOLUTE MAXIMUM RATINGSParameter Rating Unit VIN, RSET, EN/PWM Voltages−0.3 to 6V LED1, LED2, LED3, LED4 Voltages−0.3 to 25V Storage Temperature Range−65 to +160_C Junction Temperature Range−40 to +150_C Lead Temperature300_C Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.Table 2. RECOMMENDED OPERATING CONDITIONSParameter Rating Unit VIN 3.0 to 5.5V Voltage applied to LED1 to LED4, outputs off up to 25V Voltage applied to LED1 to LED4, outputs on up to 6 (Note 2)V Ambient Temperature Range−40 to +85_CI LED per LED pin10 to 175mA2.Keeping LEDx pin voltage below 6 V in operation is recommended to minimize thermal dissipation in the package.NOTE:Typical application circuit with external components is shown on page 1.Table 3. ELECTRICAL OPERATING CHARACTERISTICS (Min and Max values are over the recommended operating conditions= 25°C.)unless specified otherwise. Typical values are at VIN = 5.0 V, TTable 4. RECOMMENDED EN/PWM TIMING (Min and Max values are over the recommended operating conditions unless specified otherwise. Typical values are at VIN = 5.0 V, T AMB = 25°C.)Symbol NameConditions MinTyp MaxUnits T PS Turn −On time, EN/PWM rising to I LED from shutdownI LED = 175 mA I LED = 80 mA 1.51.3m s T P1Turn −On time, EN/PWM rising to I LED I LED = 175 mA 600ns T P2Turn −Off time, EN/PWM falling to I LED I LED= 175 mA I LED = 80 mA 400300ns T R LED rise time I LED = 175 mA I LED = 80 mA 700440ns T F LED fall time I LED = 175 mA I LED = 80 mA360320ns T LO EN/PWM low time 1m s T HI EN/PWM high time5m s T PWRDWNEN/PWM low time to shutdown delay48msFigure 2. CAT4104 EN/PWM TimingEN/PWM OperationThe EN/PWM pin has two primary functions. One function enables and disables the device. The other function turns the LED channels on and off for PWM dimming control. The device has a very fast turn −on time (from EN/PWM rising to LED on) and allows “instant on” when dimming LED using a PWM signal.Accurate linear dimming is compatible with PWM frequencies from 100 Hz to 5 kHz for PWM duty cycle down to 1%. PWM frequencies up to 50 kHz can be supported for duty cycles greater than 10%.When performing a combination of low frequencies and small duty cycles, the device may enter shutdown mode.This has no effect on the dimming accuracy, because the turn −on time T PS is very short, in the range of 1 m s.To ensure that PWM pulses are recognized, pulse width low time T LO should be longer than 1 m s. The CAT4104enters a “zero current” shutdown mode after a 4 ms delay (typical) when EN/PWM is held low.Figure 3. Quiescent Current vs. Input Voltage(RSET Open)Figure 4. Quiescent Current vs. RSET CurrentINPUT VOLTAGE (V)RSET CURRENT (mA)5.55.04.54.03.53.00.40.60.81.01.22.01.51.00.5002468Figure 5. Quiescent Current vs. Input Voltage(Full Load)Figure 6. LED Dropout vs. LED Pin VoltageINPUT VOLTAGE (V)LED PIN VOLTAGE (V)5.55.04.54.03.53.05.05.56.06.57.0 1.00.80.60.40.2004080120160200Figure 7. LED Line RegulationFigure 8. LED Current Change vs.TemperatureVIN (V)TEMPERATURE (°C)5.55.04.54.03.53.00408012016020012080400−4004080120160200Q U I E S C E N T C U R R E N T (m A )Q U I E S C E N T C U R R E N T (m A )Q U I E S C E N T C U R R E N T (m A )L E D C U R R E N T (m A )L E D C U R R E N T (m A )L E D C U R R E N T (m A )No LoadFull LoadFigure 9. LED Current vs. RSET ResistorFigure 10. LED Current vs. LED Pin VoltageRSET (k W )LED PIN VOLTAGE (V)1010.1101001000654321004080120160200Figure 11. RSET Pin Voltage vs. Input VoltageFigure 12. RSET Pin Voltage vs. TemperatureINPUT VOLTAGE (V)TEMPERATURE (°C)5.55.04.54.03.53.01.101.151.201.251.3012080400−401.101.151.201.251.30Figure 13. LED Off Current vs. LED PinVoltageLED PIN VOLTAGE (V)0.20.40.60.81.0L E D C U R R E N T (m A )L E D C U R R E N T (m A )R S E T V O L T A G E (V )R S E T V O L T A G E (V )L E D O F F C U R R E N T (m A )Figure 14. EN/PWM Pull −down Current vs.V EN/PWMFigure 15. EN/PWM Threshold vs. VINENABLE VOLTAGE (V)INPUT VOLTAGE (V)54321005101520250.40.60.81.01.21.4Figure 16. Power Up from Shutdown Figure 17. Power DownFigure 18. PWM 200 Hz, 1% Duty CycleE N A B L E C U R R E N T (m A )E N A B L E T H R E S H O L D (V )Table 5. PIN DESCRIPTIONSNamePinSOIC 8−LeadPinTDFN 8−Lead FunctionLED111LED1 cathode terminalLED222LED2 cathode terminalLED333LED3 cathode terminalLED444LED4 cathode terminalGND5 5 and TAB Ground referenceEN/PWM66Device enable input and PWM control VIN77Device supply pinRSET88LED current set pin for the LED channels Pin FunctionVIN is the supply pin for the device. A small 0.1 m F ceramic bypass capacitor is optional for noisy environments. Whenever the input supply falls below the under−voltage threshold, all LED channels are automatically disabled. EN/PWM is the enable and one wire dimming input for all LED channels. Guaranteed levels of logic high and logic low are set at 1.3 V and 0.4 V respectively. When EN/PWM is initially taken high, the device becomes enabled and all LED currents are set at a gain of 100 times the current in RSET. To place the device into zero current shutdown mode, the EN/PWM pin must be held low for 4 ms typical.LED1 to LED4 provide individual regulated currents for each of the LED cathodes. There pins enter a high impedance zero current state whenver the device is placed in shutdown mode.RSET pin is connected to an external resistor to set the LED channel current. The ground side of the external resistor should be star connected to the GND of the PCB. The pin source current mirrors the current to the LED sinks. The voltage at this pin is regulated to 1.2 V.GND is the ground reference for the device. The pin must be connected to the ground plane on the PCB.TAB (TDFN 8−Lead Only) is the exposed pad underneath the package. For best thermal performance, the tab should be soldered to the PCB and connected to the ground plane.Block DiagramFigure 19. CAT4104 Functional Block Diagram4 Current Sink RegulatorsVINBasic OperationThe CAT4104 has four tightly matched current sinks to regulate LED current in each channel. The LED current in the four channels is mirrored from the current flowing through the RSET pin according to the following formula:I LED ^1001.2V R SETTable 6 shows standard resistor values for RSET and the corresponding LED current.Table 6. RSET RESISTOR SETTINGSLED Current [mA]RSET [k W ]20 6.3460 2.10100 1.271750.768Tight current regulation for all channels is possible over a wide range of input voltages and LED voltages due to independent current sensing circuitry on each channel.Each LED channel needs a minimum of 400 mV headroom to sink constant regulated current up to 175 mA.If the input supply falls below 2 V , the under −voltage lockout circuit disables all LED channels. Any unused LED channels should be left open.For applications requiring more than 175 mA current,LED channels can be tied together to sink up to a total of 700 mA from the one device.The LED channels can withstand voltages up to 25 V . This makes the device ideal for driving long strings of high power LEDs from a high voltage source.Application InformationSingle 12 V SupplyThe circuit shown in Figure 20 shows how to power the LEDs from a single 12 V supply using the CA T4104. Three external components are needed to create a lower voltage necessary for the VIN pin (below 5.5 V). The resistor R2 and zener diode Z provide a regulated voltage while the quiescent current runs through the N −Channel transistor M.The recommended parts are ON Semiconductor MM3Z6V2zener diode (in SOD −323 package), and 2N7002L N −Channel transistor (in SOT23).Figure 20. Single Supply Driving 12 LEDsDaylight DetectionThe circuit in Figure 21 shows how to use CA T4104 in an automatic light sensor application. The light sensor allows the CAT4104 to be enabled during the day and disabled during the night. Two external components are required to configure the part for ambient light detection and conserve power. Resistor R1 sets the bias for the light sensor. The recommended part is Microsemi LX1972 light sensor. For best performance, the LED light should not interfere with the light sensor.Figure 21. Daylight DetectionNightlight DetectionThe circuit shown in Figure 22 illustrates how to use the CAT4104 in an automatic night light application. The light sensor allows the CA T4104 to be disabled during the day and enabled during the night. Five external components are needed to properly configure the part for night detection.Resistor R3 limits the quiescent current through the N −Channel transistor M. Resistors R1 and R2 act as avoltage divider to create the required voltage to turn on transistor M, which disables the CAT4104. The recommended parts are ON Semiconductor 2N7002L N −Channel transistor (in SOT23) and the Microsemi LX1972 light sensor. For best performance, the LED light should not interfere with the light sensor.Figure 22. Nightlight DetectionLED Current DeratingThe circuit shown in Figure 23 provides LED temperature derating to avoid over −driving the LED under high ambient temperatures, by reducing the LED current to protect the LED from over −heating. The positive thermo coefficient (PTC) thermistor RPTC is used for temperature sensing and should be located near the LED. As the temperature of RPTC increases, the gate voltage of the MOSFET M1decreases. This causes the transistor M1 on −resistance to increase which results in a reduction of the LED current. The circuit is powered from a single VCC voltage of 5 V . The recommended parts are Vishay 70°C thermistor PTCSS12T071DTE and ON Semiconductor 2N7002L N −Channel transistor (in SOT23).The PCB and heatsink for the LED should be designed such that the LED current is constant within the normal temperature range. But as soon as the ambient temperature exceeds a max threshold, the LED current drops to protect the LEDs from overheating.Figure 23. LED Current DeratingPower DissipationThe power dissipation (P D) of the CAT4104 can be calculated as follows:P D+(V IN I IN))S(V LEDN I LEDN)where V LEDN is the voltage at the LED pin, and I LEDN is theLED current. Combinations of high V LEDN voltage and high ambient temperature can cause the CAT4104 to enter thermal shutdown. In applications where V LEDN is high, a resistor can be inserted in series with the LED string to lower the power dissipation P D.Thermal dissipation of the junction heat consists primarily of two paths in series. The first path is the junction to the case (q JC) thermal resistance which is defined by the package style, and the second path is the case to ambient (q CA) thermal resistance, which is dependent on board layout. The overall junction to ambient (q JA) thermal resistance is equal to:q JA+q JC)q CAFor a given package style and board layout, the operating junction temperature T J is a function of the power dissipation P D, and the ambient temperature, resulting in the following equation:T J+T AMB)P D(q JC)q CA)+T AMB)P D q JA When mounted on a double−sided printed circuit board with two square inches of copper allocated for “heat spreading”, the resulting q JA is about 90°C/W for the TDFN−8 package, and 160°C/W for the SOIC−8 package. For example, at 60°C ambient temperature, the maximum power dissipation for the TDFN−8 is calculated as follow: P Dmax+T Jmax*T AMBq JA+150*6090+1WRecommended LayoutA small ceramic capacitor should be placed as close as possible to the driver VIN pin. The RSET resistor should have a Kelvin connection to the GND pin of the CAT4104. The board layout should provide good thermal dissipation through the PCB. In the case of the CAT4104VP2 in the TDFN package, a via can be used to connect the center tab to a large ground plane underneath as shown on Figure 24.Figure 24. CAT4104 Recommended LayoutSOIC 8, 150 mils CASE 751BD −01ISSUE OIDENTIFICATIONTOP VIEWSIDE VIEWEND VIEWNotes:(1) All dimensions are in millimeters. Angles in degrees.(2) Complies with JEDEC MS-012.SYMBOLMIN NOMMAX θA A1b cD E E1e h 0º8º0.100.330.190.254.805.803.801.27 BSC1.750.250.510.250.505.006.204.00L0.40 1.271.35TDFN8, 2x3CASE 511AK −01ISSUE ATOP VIEW SIDE VIEW BOTTOM VIEWFRONT VIEWA1Notes:(1) All dimensions are in millimeters.(2) Complies with JEDEC MO-229.SYMBOLMIN NOM MAX A 0.700.750.80A10.000.020.05A30.20 REF b 0.200.250.30D 1.90 2.00 2.10D2 1.30 1.40 1.50E 3.00E2 1.20 1.30 1.40e 2.900.50 TYP 3.10L0.200.300.40A20.450.550.65Example of Ordering Information (Note 6)Prefix Device #Suffix 4.All packages are RoHS −compliant (Lead −free, Halogen −free).5.The standard plated finish is NiPdAu.6.The device used in the above example is a CAT4104V −GT3 (SOIC, NiPdAu, Tape & Reel, 3,000/Reel).7.For additional temperature options, please contact your nearest ON Semiconductor Sales office.8.For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

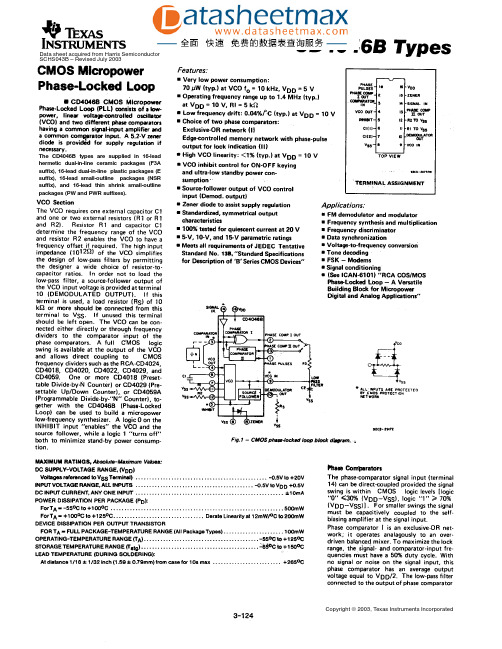

IC datasheet pdf-CD4046B,pdf(TYPES)

The CD4046B types are supplied in 16-lead hermetic dual-in-line ceramic packages (F3A suffix), 16-lead dual-in-line plastic packages (E suffix), 16-lead small-outline packages (NSR suffix), and 16-lead thin shrink small-outline packages (PW and PWR suffixes).PACKAGING INFORMATIONOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)5962-9466401MEA ACTIVE CDIP J161TBD A42N/A for Pkg Type CD4046BE ACTIVE PDIP N1625Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeCD4046BEE4ACTIVE PDIP N1625Pb-Free(RoHS)CU NIPDAU N/A for Pkg Type CD4046BF ACTIVE CDIP J161TBD A42N/A for Pkg Type CD4046BF3A ACTIVE CDIP J161TBD A42N/A for Pkg Type CD4046BNSR ACTIVE SO NS162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4046BNSRE4ACTIVE SO NS162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4046BNSRG4ACTIVE SO NS162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4046BPW ACTIVE TSSOP PW1690Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4046BPWE4ACTIVE TSSOP PW1690Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4046BPWG4ACTIVE TSSOP PW1690Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4046BPWR ACTIVE TSSOP PW162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4046BPWRE4ACTIVE TSSOP PW162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4046BPWRG4ACTIVE TSSOP PW162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS),Pb-Free(RoHS Exempt),or Green(RoHS&no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free(RoHS Exempt):This component has a RoHS exemption for either1)lead-based flip-chip solder bumps used between the die and package,or2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free(RoHS compatible)as defined above.Green(RoHS&no Sb/Br):TI defines"Green"to mean Pb-Free(RoHS compatible),and free of Bromine(Br)and Antimony(Sb)based flame retardants(Br or Sb do not exceed0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis onincoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.TAPE AND REEL INFORMATION*All dimensions are nominal Device Package Type Package DrawingPinsSPQ Reel Diameter (mm)Reel Width W1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W (mm)Pin1Quadrant CD4046BNSR SONS 162000330.016.48.210.5 2.512.016.0Q1CD4046BPWR TSSOP PW 162000330.012.4 6.9 5.6 1.68.012.0Q1*All dimensions are nominalDevice Package Type Package Drawing Pins SPQ Length(mm)Width(mm)Height(mm) CD4046BNSR SO NS162000346.0346.033.0CD4046BPWR TSSOP PW162000346.0346.029.0IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDLP®Products Communications and /communicationsTelecomDSP Computers and /computersPeripheralsClocks and Timers /clocks Consumer Electronics /consumer-appsInterface Energy /energyLogic Industrial /industrialPower Mgmt Medical /medicalMicrocontrollers Security /securityRFID Space,Avionics&/space-avionics-defenseDefenseRF/IF and ZigBee®Solutions /lprf Video and Imaging /videoWireless /wireless-appsMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2010,Texas Instruments Incorporated。

MC74AC541资料

IOL

24 mA

24 mA

VI = VCC, GND

VI (OE) = VIL, VIH VI = VCC, GND VO = VCC, GND VOLD = 1.65 V Max VOHD = 3.85 V Min

VIN = VCC or GND

3

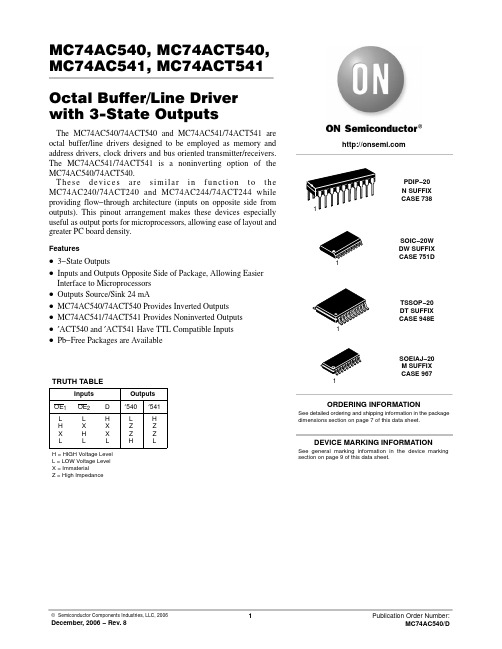

MC74AC540, MC74ACT540, MC74AC541, MC74ACT541

tr, tf

′ACT Devices except Schmitt Inputs

VCC @ 4.5 V

−

10

−

VCC @ 5.5 V

−

8.0

−

TJ

Junction Temperature (PDIP)

−

−

140

TA

Operating Ambient Temperature RangCHARACTERISTICS (For Figures and Waveforms − See AND8277/D at )

74AC

74AC

Symbol

Parameter

TA = +25°C

TA = −40°C to +85°C

VCC*

CL = 50 pF

CL = 50 pF

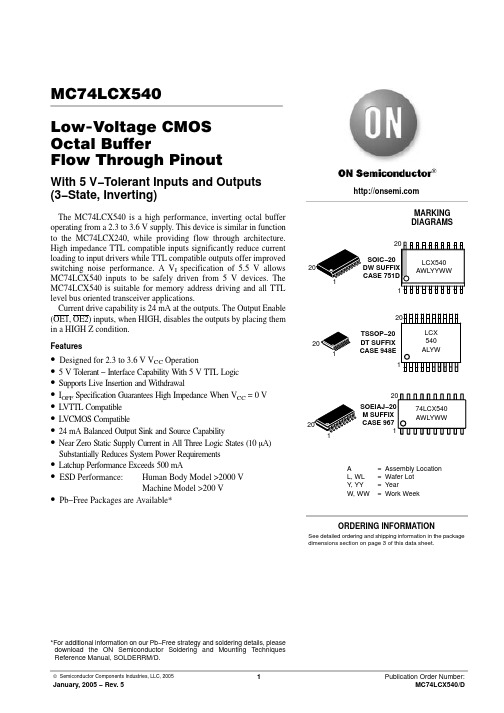

These devices are similar in function to the MC74AC240/74ACT240 and MC74AC244/74ACT244 while providing flow−through architecture (inputs on opposite side from outputs). This pinout arrangement makes these devices especially useful as output ports for microprocessors, allowing ease of layout and greater PC board density.

IC datasheet pdf-CD54AC245,CD74AC245,CD54ACT245,CD74ACT245,pdf(Octal-Bus Transceiver,Three-State, No

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.

FAST™ is a Trademark of Fairchild Semiconductor.

For VI < -0.5V or VI > VCC + 0.5V . . . . . . . . . . . . . . . . . . . . . .±20mA DC Output Diode Current, IOK

For VO < -0.5V or VO > VCC + 0.5V . . . . . . . . . . . . . . . . . . . .±50mA DC Output Source or Sink Current per Output Pin, IO

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . . 300oC

Operating Conditions

Temperature Range, TA . . . . . . . . . . . . . . . . . . . . . . -55oC to 125oC Supply Voltage Range, VCC (Note 4)

AC Types. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1.5V to 5.5V ACT Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4.5V to 5.5V DC Input or Output Voltage, VI, VO . . . . . . . . . . . . . . . . . 0V to VCC Input Rise and Fall Slew Rate, dt/dv AC Types, 1.5V to 3V . . . . . . . . . . . . . . . . . . . . . . . . . 50ns (Max) AC Types, 3.6V to 5.5V . . . . . . . . . . . . . . . . . . . . . . . . 20ns (Max) ACT Types, 4.5V to 5.5V. . . . . . . . . . . . . . . . . . . . . . . 10ns (Max)

74HC540中文资料

(1) HC : VM = 50%; VI = GND to VCC. HCT: VM = 1.3 V; VI = GND to 3 V.

Fig.7 Waveforms showing the 3-state enable and disable times.

PACKAGE OUTLINES See “74HC/HCT/HCU/HCMOS Logic Package Outlines”.

元器件交易网

INTEGRATED CIRCUITS

DATA SHEET

For a complete data sheet, please also download:

• The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications • The IC06 74HC/HCT/HCU/HCMOS Logic Package Information • The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

QUICK REFERENCE DATA GND = 0 V; Tamb = 25 °C; tr = tf = 6 ns

SYMBOL

PARAMETER

CONDITIONS

tPHL/ tPLH CI CPD

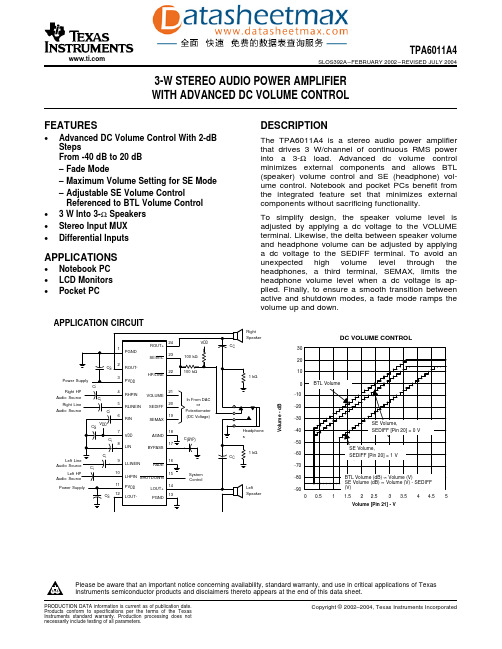

IC datasheet pdf-TPA6011A4,pdf(3-W Stereo Audio Power Amplifier)