AD401M94VSA-5中文资料

四門控制器 RC5401 快速安裝指南说明书

面板LED 燈號 PCB 接點及Jumper跳線LED 燈號 顯示說明Jumper 跳線說明出廠設定 PWR 正常情況持續閃爍表CPU 有在正常運作 JP5 DI 外部或控制器內部供電切換 控制器內部供電 COM 未接卡機約每秒閃爍一次,接卡機閃爍速度變快JP6 設定繼電器(RELAY)是否由控制器供電控制器不供電 10M 當網路(LAN)通訊速率為10Mbps 時會亮燈 閉路(Close)表示由控制器供12VDC 電源100M 當網路(LAN)通訊速率為100Mbps 時會亮燈 JP7~JP12 繼電器(RELAY) NC 或NO 切換Normal Open DI1~DI8 當燈亮時表示該輸入接點導通JP15 韌體AP 是否啟用,開路(Open)表示啟用 韌體AP 啟用 RY1~RY6當燈亮時表示其對應之輸出接點繼電器作動後側板接點 接線說明接點及按鈕 接線說明C+ DI 外部電源輸入 (注意事項8) RESET 長按10秒控制器重置回出廠設定 DI1~DI4 出門按鈕接點對應1~4門點 預設IP 位址:10.0.50.100 DI5~DI8 火災發報接點對應1~4門點 COM RS485(2線/4線)串接讀卡機使用 G控制器共地接點 (注意事項8) LAN RJ45網路接線RY1+~RY4+ 外部電源輸入接點對應1~4門的電鎖使用DC JACK 控制器電源輸入(12VDC) RY1-~RY4-電源輸出至1~4門的電鎖使用PWR控制器電源輸入(12VDC)注意事項1. 控制器請使用12VDC 供電,允許的輸入電壓為9VDC~13VDC;控制器輸入電源,DC JACK 與端子接點(PWR)兩者擇一2. 控制器若斷電超過24小時,系統時鐘需重新設定3. 控制器韌體版本必須與讀卡機相符方可正常使用;版本ATOP 4Door ATT 是Atop 讀卡機使用,ATOP 4Door SOYAL 是Soyal 讀卡機使用4. 讀卡機RS-485 ID1~ID4為進入卡機,ID5~ID8為出門卡機5. 讀卡機的通訊線路建議使用22AWG 具Shielding 防護之雙絞線材;以一進一出方式串接卡機6. 電鎖的電源與控制器的電源分開供電,避免電鎖作動瞬間影響控制器7. 訊號傳輸線與電源線建議分開配管,避免訊號干擾8.當JP5切換使用"C+"外部電源時,勿使用"G"接點作為共地接點,應使用DI 外部電源之地電壓當迴路地控制器與HID卡機、AR1200韋根轉換器、電鎖建議接線圖控制器與卡機、電鎖建議接線圖電鎖由卡機控制接線圖控制器進出管制接線圖注意事項1. 電鎖及出門按鈕由控制器直接控制,安全性較高2. 若為節省佈線,可將電鎖及出門按鈕由轉換器控制3. 電鎖繼電器的NC/NO依電鎖型式決定,一般的陽極鎖或磁力鎖為NC4. 電鎖的電源建議獨立供電5. 電鎖建議外加一個反向二級體(1N4001)保護電路注意事項1. 進讀卡機的RS-485 ID為1~4,出讀卡機的RS-485 ID為5~82. 電鎖及出門按鈕由控制器直接控制,安全性較高3. 若為節省佈線,可將電鎖及出門按鈕由進讀卡機控制4. 電鎖繼電器的NC/NO依電鎖型式決定,一般的陽極鎖或磁力鎖為NC5. NC/NO使用控制器PCB之JUMPER JP7~JP10跳線6. 電鎖的電源建議獨立供電7. 電鎖建議外加一個反向二級體(1N4001)保護電路RS485 D+RS485 D-出門按鈕V+DI1DI COMVIN+NC1COM1To Vout+To Vout-控制器Wiegand注意事項1. 電鎖及出門按鈕由卡機控制,可節省佈線,但安全性較低2. 電鎖繼電器的NC/NO依電鎖型式決定,一般的陽極鎖或磁力鎖為NC3. 電鎖的電源建議獨立供電4. 電鎖建議外加一個反向二級體(1N4001)保護電路注意事項1. 電鎖及出門按鈕由控制器直接控制,安全性較高2. 電鎖繼電器的NC/NO依電鎖型式決定,一般的陽極鎖或磁力鎖為NC3. NC/NO使用控制器PCB之JUMPER JP7~JP10跳線4. 電鎖的電源建議獨立供電5. 電鎖建議外加一個反向二級體(1N4001)保護電路磁簧DI_GDIPCB跳線控制器出門按鈕警報器V+外部電源V-Pin6PCB跳線參見注意事項Pin7Pin8Pin1Pin2GND控制器電源供應器(For 控制器&卡機)出門按鈕V-RS485 D+DI_GDIGND V+(12V)電源供應器(For 電鎖)GNDID=1控制器警報器磁簧外部電源V+V+Pin5Pin6Pin9Pin7。

Shure AD4Q Axient 数字四接收机说明书

AD4Q Axient 数字四接收机AD4Q Axient 数字四接收机在透明数字音频和最大化频谱效率方面树立了新标准。

突破性的性能特点包括宽调谐、低延迟、高密度(HD)模式和四分集™,确保在最具挑战性的射频环境中发挥稳定性能。

联网控制、AES3+Dante 输出和信号路由选项为您的整个工作流程带来了全新的管理和灵活性水平。

兼容所有Axient 数字发射机。

特点音频•60dB 的增益调节提供与各种输入源的兼容性•Dante™联网功能可实现快速且轻松的频道管理•Dante 浏览功能可使耳机监听所有Dante 频道,包括第三方组件•通过AES 256加密保护音频通道•自动限幅器功能可防止信号削波、实现更高增益设置,并防止意外信号峰值•前面板连接耳机以实现可调节音量I/O•四个变压器平衡XLR 输出(输出3个和4个可切换的AES3数字信号)•四个变压器平衡1/4''输出•两个启用Dante 功能的以太网端口,两个具备PoE 功能的网络控制以太网端口⁃分支冗余模式:两个以太网端口、两个Dante 端口⁃切换模式:四个以太网端口、四个Dante 端口•锁定交流电源链接•交流电源级联至其他组件•提供可选的交流模块以支持冗余电源射频•每个频道提供真正的数字分集式接收•四分集模式可提供增强的覆盖范围•最高210MHz 调谐范围•频道质量计显示射频信号的信噪比•适用于发射机的选择或合并模式的频率分集•用于额外一台接收机的天线级联•预编程组和频道地图,具有创建自定义组的选项•使用组和频道扫描通过接收机搜索开放频率•通过Wireless Workbench 执行全频段扫描以实现频率协调•将多达八个发射机注册到一个接收机频道•如果采用高密度传输模式,最多可在6MHz 电视频道中容纳47台同时工作的发射机(一个8MHz 电视频道中可容纳63台发射机)网络控制•Wireless Workbench ®控制软件•ShurePlus™Channels 移动设备控制•控制台集成•控制系统支持附带组件接收机附带以下组件:90XN1371硬件套件95A8994隔板转接器,BNC 视不同地区而有所区别1/2波长宽频天线(2)95B9023适用于隔板安装的BNC-BNC 同轴射频线缆(短)95C9023适用于隔板安装的BNC-BNC 同轴射频线缆(长)95N2035同轴射频级联线缆视不同地区而有所区别交流电源线,VLock 视不同地区而有所区别交流电源跨接线缆95A33402以太网线缆3英尺95B33402以太网跨接线缆1/20©2017Shure Incorporated AD4Q硬件接收机前面板2/202017/10/25⑮控制轮•按下以进入菜单•按下可选择频道或菜单项•旋转可在菜单项之间滚动,或编辑参数值⑯电源开关打开或关闭设备电源。

AD4001 AD4005 数据手册说明书

16位、2 MSPS/1 MSPS 、精密差分SAR ADC数据手册AD4001/AD4005Rev. ADocument FeedbackInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks andregistered trademarks are the property of their respective owners.One Technology Way, P .O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 781.329.4700 ©2017 Analog Devices, Inc. All rights reserved. Technical Support /cnADI 中文版数据手册是英文版数据手册的译文,敬请谅解翻译中可能存在的语言组织或翻译错误,ADI 不对翻译中存在的差异或由此产生的错误负责。

如需确认任何词语的准确性,请参考ADI 提供的最产品特性吞吐速率:2 MSPS/1 MSPS 可选INL :±0.4 LSB (最大值) 保证16位无失码 低功耗9.5 mW (2 MSPS),4.9 mW (1 MSPS)(仅VDD ) 80 μW (10 kSPS),16 mW (2 MSPS)(总计)SNR :典型值96.2 dB (1 kHz, V REF = 5 V);典型值95.5 dB (100 kHz) THD :典型值−123 dB (1 kHz, V REF = 5 V);典型值−99 dB (100 kHz) 易用特性可降低系统功耗和复杂性 输入过压箝位电路减少了非线性输入电荷反冲 高阻态模式 长采集阶段 输入范围压缩快速转换时间支持很低的SPI 时钟速率 SPI 可编程模式、读/写能力、状态字 差分模拟输入范围:±V REF0 V 至V REF (V REF 在2.4 V 至5.1 V 之间)单电源工作:1.8 V ,逻辑接口电压:1.71 V 至5.5 V SAR 架构:无延迟/流水线延迟,首次转换有效 精确的首次转换保证工作:−40°C 至+125°CSPI/QSPI/MICROWIRE/DSP 兼容串行接口以菊花链形式连接多个ADC ,并能提供繁忙指示10引脚封装:3 mm × 3 mm LFCSP 、3 mm × 4.90 mm MSOP 封装应用自动测试设备 机器自动化 医疗设备 电池供电设备 精密数据采集系统概述AD4001/AD4005是低噪声、低功耗、高速、16位精密逐次逼近型寄存器(SAR)模数转换器(ADC)。

特殊功能模块讲解

六、模拟量输入/输出单元

• 模拟量输入输出单元功能模块既可用于Fl、 F2系列PLC,也适用于FX2和FX2C系列PLC。 F2-6A是8位2通道输入、1通道输出的模拟 量输人输出模块。有关性能及应用如下:

• 1.输人类型的选择 输入类型选为(0~5)V、 (0~10)V和(O~20)mA时,各个通道可混 合选择,若某一通道选择(4~20)mA,则所 有的通道都需设置为(4~20)mA。

四、热电偶温度传感器模拟量 输入模块FX-4AD-TCFX

• FX-4AD-TC是4通道热电偶温度传感器模拟 量输入模块。瞬时值及设定值等数据的读 出、写入用FROM/TO指令进行。FX4AD-TC的指术指标如表8-4所示。table 模拟量输入输出模块常在温度控制、流量 控制、速度控制、张力控制、压力控制、 风力控制、电流、电压的监控中应用。

• 通常在PLC由STOP转为RUN状态时将数据 写入这些BFM中。当FX-2DA上电时,BFM 的值被复位,恢复到其缺省设定值。

• ①BFM#0中的两位十六进制数是分别用来

控制两通道的输出模式的,最低位控制 CH1,最高位控制CH2。H00中: 0=0 时,电压输出(-10V~+10V) 0=1时,电 流输出(+4mA~+20mA) 例如,H1O表示 CH1为电压输出,CH2为电流输出。

三、模拟量输出模块FX-2DA

• FX-2DA为2通道12位D/A转换模块,每个 通道可独立设置电压或电流输出。FX-2DA 是一种具有高精确度的输出模块。通过简 易的调整或根据PLC的指令可改变模拟量输 出的范围。瞬时值和设定值等数据的读出 和写入用FROM/TO指令进行。FX-2DA的 技术指标如表8-3表示。

• ②输出数据写在BFM#1和BFM#2 BFM#1为 CH1数据(缺省值=0) BFM#2为CH2数据(缺省 值=0)

AD404M94VTB-5中文资料

ASCEND Semiconductor 4Mx4 EDO Data sheetDescriptionThe device CMOS Dynamic RAM organized as 4,194,304 words x 4 bits with extended data out access mode. It is fabricated with an advanced submicron CMOS technology and designed to operate from a single 3.3V oniy power supply. Low voltage operation is more suitable to be used on battery backup, portable elec-tronic application. lt is packaged in JEDEC standard 26/24-pin plastic SOJ or TSOP(II).Features• Single 3.3V(%) only power supply • High speed t RAC acess time: 50/60ns • Low power dissipation- Active mode : 432/396 mW (Mas) - Standby mode: 0.54 mW (Mas)• Extended - data - out(EDO) page mode access • I/O level: CMOS level (Vcc = 3.3V)• 2048 refresh cycle in 32 ms(Std.) or 128 ms(S-version)• 4 refresh modesh: - RAS only refresh- CAS - before - RAS refresh - Hidden refresh - Self-refresh(S-version)10±Pin Name FunctionA0-A10Address inputs- Row address - Column address - Refresh address DQ1~DQ4Data-in / data-out RAS Row address strobe CAS Column address strobe WE Write enable OE Output enable Vcc Power (+ 3.3V)VssGroundVCC 1DQ12DQ23DQ34DQ45VCC6891011 NC 12 WE 13A0 A117 A218 A319VSS RAS CAS OE A8A7A6A5A4VSSAD404M42VSPin Description Pin Configuration21222324 2526151416 A1026/24-PIN 300mil Plastic SOJA9VCC 1DQ12DQ23DQ34DQ45VCC6891011 NC 12 WE 13A0 A117 A218 A319VSS RAS CAS OE A8A7 A6A5 A4VSSAD404M42VT212223242526151416 A1026/24-PIN 300mil Plastic TSOP (ll)A9A0-A10A0-A10A0-A10WECASNO. 2 CLOCK GENERATORCOLUMN ADDRESS BUFFERS (11)REFRESH CONTROLLERREFRESH COUNTERBUFFERS (11)ADDRESS ROW NO. 1 CLOCK GENERATORA0RASA1A2A3A4A5A6A7A8CONTROLLOGICDATA-IN BUFFERDATA-OUT BUFFEROEDQ1.DQ4.COLUMN DECODER2048SENSE AMPLIFIERSI/O GATING2048x42048x2048x4MEMORY ARRAY2048R O W D E C O D E RVcc VssBlock DiagramA9A10TRUTH TABLENotes: 1. EARLY WRITE only.FUNCTIONRASCAS WE OE ADDRESSESDQ SNotesROW COL STANDBY H X X X X High-Z READL L H L ROW COL Data-Out WRITE: (EARLY WRITE )L L L X ROW COL Data-lnREAD WRITE L L ROW COL Data-Out,Data-ln EDO-PAGE-MODE READ1st Cycle L H L ROW COL Data-Out 2nd CycleL H L n/a COL Data-Out EDO-PAGE MODE WRITE1st CycleL L X ROW COL Data-In 2nd Cycle L L Xn/a COL Data-InEDO-PAGE-MODEREAD-WRITE 1st Cycle L ROW COL Data-Out, Data-In 2nd Cycle L n/a COL Data-Out, Data-In HIDDEN REFRESHREAD L H L ROW COL Data-Out WRITEL L X ROW COL Data-In 1RAS-ONLY REFRESH L H X X ROW n/a High-Z CBR REFRESHLHXXXHigh-ZH X →H L →L H →H L →H L →H L →H L →H L →H L →L H →H L →H L →L H→L H L →→L H L→→H L→Absolute Maximum RatingsRecommended DC Operating ConditionsCapacitanceTa = 25°C, V CC = 3.3V%, f = 1MHz Note: 1. Capacitance measured with effective capacitance measuring method. 2. RAS, CAS = V IH to disable Dout.ParameterSymbol Value Unit Voltage on any pin relative to Vss V T -0.5 to + 4.6V Supply voltage relative to Vss V CC -0.5 to + 4.6V Short circuit output current I OUT 50mA Power dissipation P D 1.0WOperating temperature T OPT 0 to + 70°C Storage temperatureT STG-55 to + 125°CParameter/Condition Symbol3.3 Volt VersionUnitMinTyp MaxSupply VoltageV CC 3.0 3.33.6V Input High Voltage, all inputs V IH 2.0-V CC + 0.3V Input Low Voltage, all inputsV IL-0.3-0.8VParameterSymbol Typ Max Unit Note Input capacitance (Address)C I1 -5pF 1Input capacitance (RAS, CAS, OE, WE)C I2-7pF 1Output capacitance(Data-in, Data-out)C I/O-7pF1, 210±DC Characteristics :(T a = 0 to 70°C, V CC = + 3.3V%, V SS = 0V)Parameter Symbol Test Conditions AD404M42V Unit Notes-5-6Min Max Min MaxOperating current I CC1RAS cyclingCAS, cyclingt RC = min-120-110mA1, 2Standby Current LowpowerS-versionI CC2LVTTL interfaceRAS, CAS = V IHDout = High-Z-0.5-0.5mACMOS interfaceRAS, -0.2VDout = High-Z-0.15-0.15mAStandardpowerversionLVTTL interfaceRAS, CAS = V IHDout = High-Z-2-2mACMOS interfaceRAS,-0.2VDout = High-Z-0.5-0.5mARAS- only refresh current I CC3RAS cycling, CAS = V IHt RC = min-120-110mA1, 2 EDO page mode current I CC4t PC = min-90-80mA1, 3CAS- before- RAS refresh current I CC5t RC = minRAS, CAS cycling-120-110mA1, 2Self- refresh current (S-Version)I CC8 - 550 - 55010±CAS V CC≥CAS V CC≥t RASS100µs≥µADC Characteristics :(T a = 0 to 70°C , V CC = +3.3V %, V SS = 0V)Notes:1. I CC is specified as an average current. It depends on output loading condition and cycle rate when the device is selected. I CC max is specified at the output open condition.2. Address can be changed once or less while RAS = V IL .3. For I CC4, address can be changed once or less within one EDO page mode cycle time.Parameter Symbol Test Conditions AD404M42VUnitNotes-5-6Min MaxMin MaxInput leakage current I LI + 0.3V -55-55Output leakage current I LO + 0.3V Dout = Disable -55-55Output high Voltage V OH I OH = -2mA 2.4- 2.4-V Output low voltage V OLI OL = +2mA-0.4-0.4V10±0V Vin V CC ≤≤µA 0V Vout V CC ≤≤µAAC Characteristics(T a = 0 to + 70°C , V cc = 3.3V %, V ss = 0V) *1, *2, *3, *4Test conditions• Output load: one TTL Load and 100pF (V CC = 3.3V %)• Input timing reference levels:V IH = 2.0V, V IL = 0.8V (V CC = 3.3V %)• Output timing reference levels:V OH = 2.0V, V OL = 0.8V10±10±10±Read, Write, Read- Modify- Write and Refresh Cycles (Common Parameters)ParameterSymbol AD404M42V UnitNotes-5-6Min MaxMin MaxRandom read or write cycle time t RC 84-104-ns RAS precharge timet RP 30-40-ns CAS precharge time in normal mode t CPN 10-10-ns RAS pulse width t RAS 50100006010000ns 5CAS pulse width t CAS 8100001010000ns 6Row address setup time t ASR 0-0-ns Row address hold time t RAH 8-10-ns Column address setup time t ASC 0-0-ns 7Column address hold time t CAH 8-10-ns RAS to CAS delay timet RCD 12371445ns 8RAS to column address delay time t RAD 10251230ns 9Column address to RAS lead time t RAL 25-30-ns RAS hold time t RSH 8-10-ns CAS hold timet CSH 38-40-ns CAS to RAS precharge time t CRP 5-5-ns 10OE to Din delay time t OED 12-15-ns Transition time (rise and fall)t T 150150ns 11Refresh periodt REF -32-32ms Refresh period (S- Version)t REF -128-128ms CAS to output in Low- Z t CLZ 0-0-ns CAS delay time from Din t DZC 0-0-ns OE delay time from Dint DZO-0-nsRead CycleWrite Cycle Parameter SymbolAD404M42V Unit Notes-5-6Min Max Min MaxAccess time from RAS t RAC-50-60ns12 Access time from CAS t CAC-14-15ns13, 14 Access time from column address t AA-25-30ns14, 15 Access time from OE t OEA-12-15nsRead command setup time t RCS0-0-ns7 Read command hold time to CAS t RCH0-0-ns10, 16 Read command hold time to RAS t RRH0-0-ns16 Output buffer turn-off time t OFF012015ns17 Output buffer turn-off time from OE t OEZ012015ns17Parameter SymbolAD404M42V Unit Notes -5-6Min Max Min MaxWrite command setup time t WCS0-0-ns7, 18 Write command hold time t WCH8-10-nsWrite command pulse width t WP8-10-nsWrite command to RAS lead time t RWL13-15-nsWrite command to CAS lead time t CWL8-10-nsData-in setup time t DS0-0-ns19 Data-in hold time t DH8-10-ns19 WE to Data-in delay t WED10-10-nsRead- Modify- Write CycleRefresh Cycle Parameter SymbolAD404M42V Unit Notes-5-6Min Max Min MaxRead-modify- write cycle time t RWC108-133-nsRAS to WE delay time t RWD64-77-ns18 CAS to WE dealy time t CWD26-32-ns18 Column address to WE delay time t AWD39-47-ns18 OE hold time from WE t OEH8-10-nsParameter SymbolAD404M42VUnit Notes -5-6Min Max Min MaxCAS setup time (CBR refresh) t CSR5-5-nsCAS hold time (CBR refresh)t CHR8-10-ns10 RAS precharge to CAS hold time t RPC5-5-ns7 RAS pulse width (self refresh)t RASS100-100-RAS precharge time (self refresh)t RPS90-110-nsCAS hold time (CBR self refresh)t CHS-50--50-nsWE setup time t WSR0-0-nsWE hold time t WHR10-10-nsµsEDO Page Mode CycleEDO Page Mode Read Modify Write CycleParameterSymbol AD404M42VUnit Notes-5-6Min MaxMin MaxEDO page mode cycle timet PC 20-25-ns EDO page mode CAS precharge time t CP 10-10-ns EDO page mode RAS pulse width t RASP 5010560105ns 20Access time from CAS precharge t CPA -30-35ns 10, 14RAS hold time from CAS precharge t CPRH 30-35-ns OE high hold time from CAS high t OEHC 5-5-ns OE high pulse widtht OEP 10-10-ns Data output hold time after CAS low t COH 5-5-ns Output disable delay from WEt WHZ 310310ns WE pulse width for output disable whenCAS hight WPZ7-7-nsParameterSymbol AD404M42V Unit Notes -5-6Min MaxMin MaxEDO page mode read- modify- write cycle CAS precharge to WE delay timet CPW 45-55-ns 10EDO page mode read- modify- write cycle timet PRWC56-68-nsNotes :1. AC measurements assume t T = 2ns.2. An initial pause of 100 is required after power up, and it followed by a minimum of eightinitialization cycles (RAS - only refresh cycle or CAS - before - RAS refresh cycle). If the internal refresh counter is used, a minimun of eight CAS - before - RAS refresh cycles are required.3. In delayed write or read-modify-write cycles, OE must disable output buffer prior to applying data to the device.4. All the V CC and V SS pins shall be supplied with the same voltages.5. t RAS (min) = t RWD (min)+t RWL (min)+t T in read-modify-write cycle.6. t CAS (min) = t CWD (min)+t CWL (min)+t T in read-modify-write cycle.7. t ASC (min), t RCS (min), t WCS (min), and t RPC are determined by the falling edge of CAS .8. t RCD (max) is specified as a reference point only, and t RAC (max) can be met with the t RCD (max) limit.Otherwise, t RAC is controlled exclusively by t CAC if t RCD is greater than the specified t RCD (max) limit. 9. t RAD (max) is specified as a reference point only, and t RAC (max) can be met with the t RAD (max) limit.Otherwise, t RAC is controlled exclusively by t AA if t RAD is greater than the specified t RAD (max) limit. 10. t CRP , t CHR , t RCH , t CPA and t CPW are determined by the rising edge of CAS .11. V IH (min) and V IL (max) are reference levels for measuring timing or input signals. Therefore, transitiontime is measured between V IH and V IL .12. Assumes that t RCD tRCD (max) and t RAD t RAD (max). If t RCD or t RAD is greater than the maximum recommended value shown in this table, t RAC exceeds the value shown. 13. Assumes that (max) and (max).14. Access time is determined by the maximum of t AA , t CAC , t CPA . 15. Assumes that (max) and (max). 16. Either t RCH or t RRH must be satisfied for a read cycle.17. t OFF (max) and t OEZ (max) define the time at which the output achieves the open circuit condition (highimpedance). t OFF is determined by the later rising edge of RAS or CAS.18. t WCS , t RWD , t CWD , and t AWD are not restrictive operating parameters. They are included in the datasheet as electrical characteristics only. If (min), the cycle is an early write cycle and the data out will remain open circuit (high impedance) throughout the entire cycle. If (min),(min), (min) and (min), the cycle is a read-modify-write and the data output will contain data read from the selected cell. If neither of the above sets of conditions is satisfied, the condition of the data output (at access time) is indeterminate.19. These parameters are referenced to CAS separately in an early write cycle and to WE edge in adelayed write or a read-modify-write cycle.20. t RASP defines RAS pulse width in EDO page mode cycles.µs ≤≤t RCD t RCD ≥t RADt RAD ≤t RCD t RCD ≤t RAD t RAD ≥t WCS t WCS ≥t RWD t RWD ≥t CWDt CWD ≥t AWD t AWD ≥t CPW t CPW≥Timing Waveforms• Read Cyclet RC t RASt RPtCRPtCPNtRRHtRCHt OEZ t OFF tOEA tCACt AAtRACt CLZD OUTtRCS t ASR tRAH tASC tCAH tRAD t RALtCAStRSH tRCDt TtCSHRASCASADDRESSWEDQ1~DQ4Note : = don’t care OEt OFFRowColumn= Invalid Dout•Early Write CycletRC t RASt RPt WCHt DSt DHt WCS t RALtCAStRSH tRCDt TtCSHRASCASWEDQ1~DQ4tCRPtASRtRAH tASCtCAH ADDRESSColumnRowtCPND INtRADt RAL• Delayed Write CycletRC t RASt RPt RWL t RCSt CAStRSH tRCDt TtCSHRASCAStASR tRAH tCAHADDRESSColumnRow tASC D INDQ1~DQ4WEtCRPtCPNt DHt DSt OEHt OEDOEt DSOPENt WPt CWL• Read - Modify - Write CycletRWC t RASt RPtRWDt WPtRADtRWL tCAStCWL tRCDt TtCPNRASCASWEtCRP t ASRtRAHtASCtCAHADDRESS Column RowDQ1~DQ4t DHt DSOEtRCStAWD tCWD D INt OEDt OEHt OEZt OEA t CAC t RACt AADQ1~DQ4D OUTOPENtDZCtDZO• EDO Page Mode Read CycletRASPtCPRHt RCStCAStRSH tRCDt OEAtCSHRASCAStASRtRAHtCAHADDRESStCASWEtCRPt CPOEDQ1~DQ4OPENtOEPD OUT 1t PCt CPtCAStCPNtCRPtRADtCAHtASCt ASCtCAHt ASCt RAL Row Column 1t OEAt OEHCtRRH tRCHt RACt AAt AAt AA t CPA t CPA t OEZt OFFt OFFt CACt OEZt CAC t CACt COHD OUT NWE OE Column 2Column N Rowt RPD OUT 2• EDO Page Mode Early Write CycletRASPtRPt WCSt CAStRSH tRCDRASCAStASRtRAHtCAHADDRESStCASWEt CPDQ1~DQ4t PCt CPt CAStCPNtCRP tCAH tASCtASC tCAH tASC Row Column 1t DS WE Column 2Column Nt WCH t WCS t WCH t WCS t WCHt DH t DS t DH t DS t DHD IN 1D IN 2D IN Nt TtCSH• EDO Page Mode Read-Early-Write Cyclet RASPtCPRHt RCStCAStRSH tRCDt OEAtCSHRASCAStASRtRAHtCAHADDRESStCASWEtCRPt CPOEDQ1~DQ4OPENtWEDt PCt CPtCAStCPNtCRPtRADtRAHtASCt ASCtCAHt ASCt RAL Row Column 1tWCStRCHt RACt AAt AAt CPA t DHt WHZt CACt CACt COHWE OE Column 2Column N Rowt RPt CAL tWCHDataDoutput 2Data Input NDataDoutput 1t DStCSH• EDO Page Mode Read-Modify-Write Cyclet RASPt CPRHt RCStCASt WP RASCASt ASRtRAHtCAHADDRESSt CASWEtRCDCPDQ1~DQ4tPRWCt CPtCAStCRPtRADtCAHtASCt ASCtCAH tASC Row Column 1tRWLtRCSt OEDt DZOt CAC WE OEt RPt RAL D OUT 2D OUT ND OUT 1tTt Column NColumn 2Column 1tRWD tAWD tCWDtCWLtRCStCWDtAWD tCPW tCWL tCPW tAWD tCWDtCWL t OEDt OEDt OEHt OEHt OEHt CAC t CAC t OEA t AAt RACt OEZt OEAt AA t CPAt OEZt OEAt AA t CPAt OEZ t DSt DHt WP t DSt DHt WP t DSt DHOPENOPENOPEN D IN 1D IN ND IN 2DQ1~DQ4t DZCt DZOt DZCt DZCt DZO• Read Cycle with WE Controlled Disablet WPZt RCStCAStRCDt TtCSHRASCASt ASRtRAHtCAHADDRESSColumnRow tASCD DQ1~DQ4WEt OEZt DSt WHZOEt RCH t OEA t CACt AAt RACt CLZOUTtRADRASADDRESSt RC t CRPt ASRt RAHt Tt RPCROWt OFFCAS t RASt RPOPENt CRPDQ1~DQ4RASt CSRt WSRt RPt T t RPCt OFFCAS t RASt RPOPENt CRPDQ1~DQ4t RPCt CHRt RASt RPt RCt RCt CHRt CSRt WHRt WSRt WHRWECAS-Before-RAS Refresh CycleRASWEt RPCt OFFt CSRt CHSt WSRCASt RASS t RPSOPENDQ1~DQ4t WHRHigh lmpedance• Hidden Refresh Cyclet RPt RASRASt RCDt CRPADDRESSWEt CHRt CASt RSHt RAHt ASRt ASCt CAHt RAL ROW t RCHt OEZCASDQ1~DQ4t Tt RCSD t RASt RASt RPt RPt RC t RCt RCt RADt RRHt OFF t OFFt OEA t CACt AAt RACCOlumnOUTOE(READ)(REFRESH)(REFRESH)Ordering informationAD404M42VSA-5• AD• Ascend Memory Product • 40 • Device Type• 4M4 • Density and Organization • 2• Refresh Rate, 2: 2K Refresh • V• T: 5V, V: 3.3V• S • Package Type (S : SOJ, T : TSOP II)• A• Version• 5• Speed (5: 50 ns, 6: 60 ns)Part Number Access time PackageAD404M42VSA-5AD404M42VSA-6AD404M42VTA-5AD404M42VTA-650 ns 60 ns 50 ns 60 ns300mil 26/24-Pin Plastic SOJTSOP IIPackaging information • 300 mil, 26/24-Pin Plastic SOJ• 300 mil, 26/24-Pin TSOP II。

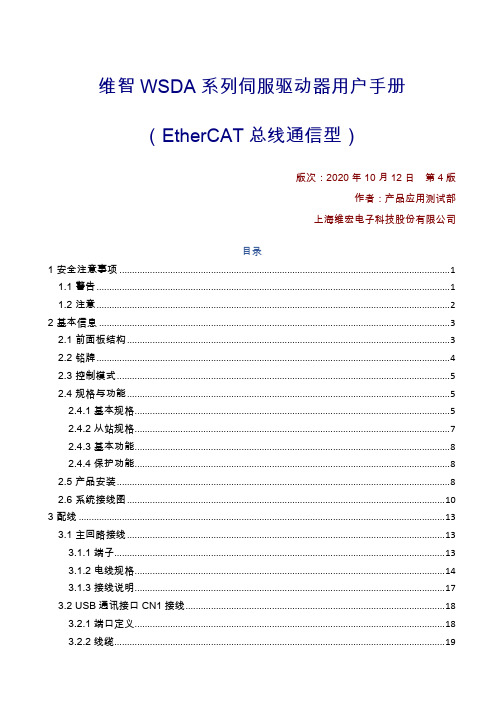

维智WSDA系列伺服驱动器用户手册(EtherCAT总线通信型)-R4

维智WSDA系列伺服驱动器用户手册(EtherCAT总线通信型)版次:2020年10月12日第4版作者:产品应用测试部上海维宏电子科技股份有限公司目录1 安全注意事项 (1)1.1 警告 (1)1.2 注意 (2)2 基本信息 (3)2.1 前面板结构 (3)2.2 铭牌 (4)2.3 控制模式 (5)2.4 规格与功能 (5)2.4.1 基本规格 (5)2.4.2 从站规格 (7)2.4.3 基本功能 (8)2.4.4 保护功能 (8)2.5 产品安装 (8)2.6 系统接线图 (10)3 配线 (13)3.1 主回路接线 (13)3.1.1 端子 (13)3.1.2 电线规格 (14)3.1.3 接线说明 (17)3.2 USB通讯接口CN1接线 (18)3.2.1 端口定义 (18)3.2.2 线缆 (19)3.3 总线接口 CN2A/B 接线 (20)3.3.1 接线图 (20)3.3.2 线缆 (20)3.4 电机编码器线接口CN4接线 (21)3.4.1 端口定义 (21)3.4.2 说明 (22)3.4.3 线缆 (23)3.5 外置再生制动电阻器连接 (24)4 驱动器面板 (29)4.1 概述 (29)4.2 监视器模式 (31)4.3 参数设定模式 (41)4.4 EEPROM 写入模式 (41)4.5 辅助功能模式 (42)4.5.1 概述 (42)4.5.2 设置站别名 (44)4.5.3 解除报警 (44)4.5.4 试运行电机 (45)4.5.5 清零绝对值编码器 (45)4.5.6 初始化参数 (46)4.5.7 解除前面板锁定 (46)4.5.8 注册驱动器 (46)4.5.9 初始化对象字典 (47)4.6 驱动器面板锁定 (48)5 电机试运行 (48)5.1 准备工作 (48)5.2 进行基本设定 (48)5.2.1 打开伺服 (49)5.2.2 选择电机旋转方向 (49)5.2.3 启用超程防止功能 (49)5.2.4 设定电机过载率 (50)5.2.5 启用制动器 (50)5.2.6 伺服断开及报警时停止电机 (50)5.3.1 使用 iMotion 软件 (51)5.3.2 使用驱动器面板 (51)5.4 故障排查 (51)6 控制系统连接 (54)6.1 选择系统类型 (54)6.2 设置关联参数 (54)6.2.1 设置控制系统参数 (54)6.2.2 设置维智伺服驱动器参数 (55)6.3 设置站别名 (55)6.4 设定基准或回机械原点 (55)6.4.1 设定基准 (55)6.4.2 回机械原点 (56)6.5 运行电机 (56)7 绝对式系统 (56)7.1 安装与更换电池 (56)7.2 自制绝对式编码器电缆 (58)7.3 启用绝对值功能 (58)7.4 启用无限旋转绝对式功能 (58)8 增益调整 (58)8.1 准备工作 (58)8.1.1 设定驱动禁止输入 (59)8.1.2 设定转矩限制 (59)8.1.3 设定过速度保护 (59)8.1.4 设定位置偏差过大保护 (59)8.1.5 设定电机可动范围 (60)8.2 推定惯量比 (60)8.3 设置自适应滤波器 (61)8.3.1 操作步骤 (62)8.3.2 故障排查 (62)8.3.3 相关信息 (63)8.4 自动调整增益 (63)8.4.1 操作步骤 (64)8.4.3 相关信息 (65)8.5 手动调整增益 (67)8.5.1 执行基本调整 (68)8.5.2 切换增益 (69)8.5.3 抑制机械共振 (75)8.5.4 设置 2 段转矩滤波器 (76)8.6 总线控制系统调整增益 (77)9 驱动器注册 (77)9.1 获取序列号 (77)9.1.1 通过 iMotion 软件 (78)9.1.2 通过驱动器面板 (79)9.2 获取注册码 (80)9.3 注册驱动器 (81)10 异常与对策 (82)10.1 异常时应对思路 (82)10.2 警告 (83)10.2.1 查找警告 (83)10.2.2 警告码 (83)10.3 SDO传输中止码 (84)10.4 错误码一览表 (85)10.5 错误码详情 (90)10.5.1 Err10系列 (90)10.5.2 Err20系列 (97)10.5.3 Err30系列 (101)10.5.4 Err40系列 (105)10.5.5 Err50系列 (108)10.5.6 Err70系列 (112)10.5.7 Err80系列 (115)10.5.8 Err90系列 (124)10.5.9 其他错误码 (125)10.5.10 解除错误 (125)11 参数 (126)11.2 [分类 0]基本设定 (126)11.2.1 Pr001 (126)11.2.2 Pr002 (127)11.2.3 Pr003 (127)11.2.4 Pr004 (128)11.2.5 Pr011 (128)11.2.6 Pr012 (129)11.2.7 Pr013 (130)11.2.8 Pr014 (131)11.2.9 Pr015 (131)11.2.10 Pr016 (132)11.2.11 Pr017 (132)11.2.12 Pr018~Pr019 (133)11.2.13 Pr024 (134)11.3 [分类 1]增益调整 (134)11.3.1 Pr100~Pr104 (134)11.3.2 Pr105~Pr109 (136)11.3.3 Pr110 (137)11.3.4 Pr111 (138)11.3.5 Pr112 (138)11.3.6 Pr113 (138)11.3.7 Pr114 (139)11.3.8 Pr115 (140)11.3.9 Pr116 (142)11.3.10 Pr117 (142)11.3.11 Pr118 (142)11.3.12 Pr119 (143)11.3.13 Pr120 (143)11.3.14 Pr121 (144)11.3.15 Pr122 (144)11.3.16 Pr123 (144)11.3.17 Pr124 (145)11.3.19 Pr126 (145)11.3.20 Pr127 (146)11.4 [分类 2]控制抑制功能 (146)11.4.1 Pr200 (146)11.4.2 Pr201~Pr203 (146)11.4.3 Pr204~Pr206 (147)11.4.4 Pr207~Pr209 (149)11.4.5 Pr210~Pr212 (150)11.4.6 Pr214~Pr215 (151)11.4.7 Pr216~Pr217 (151)11.4.8 Pr218~Pr219 (152)11.4.9 Pr220~Pr221 (152)11.4.10 Pr222 (153)11.4.11 Pr223 (154)11.5 [分类 3]速度/转矩控制 (155)11.5.1 Pr300 (155)11.5.2 Pr302 (156)11.5.3 Pr304 (156)11.5.4 Pr312~Pr313 (157)11.5.5 Pr314 (158)11.5.6 Pr317、Pr318、Pr321、Pr322 (158)11.5.7 Pr323 (160)11.5.8 Pr326 (160)11.5.9 Pr327 (161)11.5.10 Pr343 (161)11.5.11 Pr344 (161)11.5.12 Pr345 (162)11.5.13 Pr346 (162)11.6 [分类 4] I / F 监视器设定 (162)11.6.1 Pr400~Pr406 (162)11.6.2 Pr408~Pr411 (165)11.6.3 Pr430 (167)11.6.5 Pr432 (168)11.6.6 Pr433 (168)11.6.7 Pr434 (169)11.6.8 Pr435 (169)11.6.9 Pr436 (170)11.6.10 Pr437 (171)11.6.11 Pr438 (171)11.6.12 Pr439~Pr440 (172)11.6.13 Pr441 (173)11.6.14 Pr449 (173)11.6.15 Pr450 (174)11.7 [分类 5]扩展设定 (174)11.7.1 Pr503 (174)11.7.2 Pr504 (174)11.7.3 Pr505 (175)11.7.4 Pr506 (176)11.7.5 Pr507 (177)11.7.6 Pr508 (177)11.7.7 Pr509 (177)11.7.8 Pr510 (178)11.7.9 Pr511 (179)11.7.10 Pr512 (179)11.7.11 Pr513 (179)11.7.12 Pr514 (180)11.7.13 Pr516 (180)11.7.14 Pr520 (180)11.7.15 Pr521 (181)11.7.16 Pr522 (181)11.7.17 Pr523 (181)11.7.18 Pr524 (181)11.7.19 Pr525 (182)11.7.20 Pr526 (182)11.7.22 Pr533 (184)11.7.23 Pr535 (184)11.7.24 Pr540 (184)11.7.25 Pr541 (185)11.8 [分类 6]特殊设定 (185)11.8.1 Pr601 (185)11.8.2 Pr602 (185)11.8.3 Pr604 (185)11.8.4 Pr607 (186)11.8.5 Pr608 (186)11.8.6 Pr609 (186)11.8.7 Pr611 (187)11.8.8 Pr612 (187)11.8.9 Pr615 (187)11.8.10 Pr617 (188)11.8.11 Pr623 (188)11.8.12 Pr624 (189)11.8.13 Pr627 (189)11.8.14 Pr628 (189)11.8.15 Pr629 (189)11.8.16 Pr630 (190)11.8.17 Pr632 (190)11.8.18 Pr633 (192)11.8.19 Pr638 (192)11.8.20 Pr640 (193)11.8.21 Pr642 (193)11.8.22 Pr643 (194)11.8.23 Pr647 (194)11.8.24 Pr650 (194)11.8.25 Pr651 (195)11.8.26 Pr660 (195)12 EtherCat通信规格 (195)12.2 帧结构 (196)12.3 ESC地址空间 (197)12.4 通信状态 (197)12.5 SDO (198)12.6 PDO (198)12.6.1 PDO映射 (199)12.6.2 分配对象 (200)12.6.3 映射配置 (200)12.7 DC通信同步模式 (201)12.8 SII EEPROM (201)12.9 寻址模式 (201)13 对象字典 (202)13.1 概述 (202)13.1.1 分类 (202)13.1.2 数据类型 (203)13.1.3 相关用语 (203)13.2 通信对象 (204)13.2.1 设备信息 (204)13.2.2 同步管理器通讯类型 (208)13.2.3 PDO通讯 (210)13.2.4 同步管理器 2 和 3 同步对象 (240)13.2.5 对象写入 EEPROM (250)13.2.6 对象恢复出厂 (251)13.2.7 故障履历 (252)13.3 驱动器参数对象 (259)13.3.1 2100h (259)13.3.2 2101h (260)13.3.3 2102h (262)13.3.4 2103h (263)13.3.5 2200h (264)13.4 厂商定义对象 (265)13.5 辅助功能对象 (266)13.5.1 信息监视器对象 (266)13.5.2 多圈绝对式编码器清零 (277)13.6 驱动协议对象 (277)13.6.1 功率驱动系统状态机 (277)13.6.2 控制模式设置 (283)13.6.3 位置控制模式 (287)13.6.4 速度控制模式 (325)13.6.5 转矩控制模式 (335)13.6.6 模式共通功能 (343)14 对象字典一览表 (370)14.1 1000h~1FFFh (370)14.2 2000h~2FFFh (378)14.3 3000h~30FFh (379)14.4 3100h~37FFh (392)14.5 6000h~6FFFh (394)1安全注意事项注意事项根据不遵守可能会造成危害的程度,分为警告和注意类型:警告:特别需要提示的内容,如果不遵守此类信息,可能会造成人身伤害甚至是死亡、机器损坏、或者其他财产损失。

MOXA EDS-4014系列14端口managed Fast Ethernet交换机说明书

EDS-4014Series8+4G+22.5GbE-port managed Ethernet switchesFeatures and Benefits•Developed according to the IEC62443-4-1and compliant with the IEC62443-4-2industrial cybersecurity standards•Increased bandwidth capabilities with fiber SFP slots supporting up to2.5Gbps•Turbo Ring and Turbo Chain(recovery time<20ms@250switches)1,andRSTP/STP for network redundancy•Wide range of power input options for flexible deployment•Compact and flexible housing design to fit into confined spaces•Supports MXstudio for easy,visualized industrial network managementCertificationsIntroductionThe EDS-4014Series is a range of14-port managed Fast Ethernet switches with four1Gbps and two2.5Gbps fiber-optic ports.Redundant Ethernet technologies such as Turbo Ring,Turbo Chain,and RSTP/STP increase the reliability of your system and improve the availability of your network backbone.The EDS-4014Series is designed specifically for demanding applications such as video and process monitoring,ITS,and DCS systems,all of which can benefit from a scalable backbone.The EDS-4014Series is compliant with the IEC62443-4-2and IEC62443-4-1Industrial Cybersecurity certifications,which cover both product security and secure development life-cycle requirements,helping our customers meet the compliance requirements of secure industrial network design.SpecificationsEthernet Interface10/100BaseT(X)Ports(RJ45connector)8Auto MDI/MDI-X connectionAuto negotiation speedFull/Half duplex mode100/1000BaseSFP Slots41000/2500BaseSFP Ports2Standards IEEE802.3for10BaseTIEEE802.3u for100BaseT(X)and100BaseFXIEEE802.3ab for1000BaseT(X)IEEE802.3z for1000BaseXIEEE802.3bz for2.5GBaseXIEEE802.3x for flow controlIEEE802.3ad for Port Trunk with LACPIEEE802.1Q for VLAN TaggingIEEE802.1D-2004for Spanning Tree ProtocolIEEE802.1w for Rapid Spanning Tree ProtocolIEEE802.1p for Class of ServiceIEEE802.1X for authentication1.If the port link speed is1Gigabit or higher,the recovery time is<50ms.Ethernet Software FeaturesFilter GMRP,GVRP,GARP,802.1Q VLAN,IGMP Snooping v1/v2/v3,IGMP Querier Management IPv4/IPv6,Flow control,Back Pressure Flow Control,DHCP Server/Client,ARP,RARP,LLDP,Port Mirror,Linkup Delay,SMTP,SNMP Trap,SNMP Inform,SNMPv1/v2c/v3,RMON,TFTP,SFTP,HTTP,HTTPS,Telnet,Syslog,Private MIBMIB P-BRIDGE MIB,Q-BRIDGE MIB,IEEE8021-SPANNING-TREE-MIB,IEEE8021-PAE-MIB,IEEE8023-LAG-MIB,LLDP-EXT-DOT1-MIB,LLDP-EXT-DOT3-MIB,SNMPv2-MIB,RMON MIB Groups1,2,3,9Redundancy Protocols STP,RSTP,Turbo Ring v2,Turbo Chain,Ring Coupling,Dual-Homing,LinkAggregation,MSTPSecurity Broadcast storm protection,Rate Limit,Trust access control,Static Port Lock,MACSticky,HTTPS/SSL,SSH,RADIUS,TACACS+,Access control list,Login and PasswordPolicyTime Management SNTP,NTP Server/Client,NTP AuthenticationProtocols IPv4/IPv6,TCP/IP,UDP,ICMP,ARP,RARP,TFTP,DNS,NTP Client,DHCP Server,DHCP Client,802.1X,QoS,HTTPS,HTTP,Telnet,SMTP,SNMPv1/v2c/v3,RMON,SyslogSwitch PropertiesMAC Table Size16KJumbo Frame Size9.216KBMax.No.of VLANs256VLAN ID Range VID1to4094IGMP Groups512Priority Queues4Packet Buffer Size1MBLED InterfaceLED Indicators PWR1,PWR2,STATE,FAULT,MSTR/HEAD,CPLR/TAIL,SYNCSerial InterfaceConsole Port RS-232(TxD,RxD,GND),8-pin RJ45(115200,n,8,1)USB InterfaceUSB Connector USB Type A(Reserved)Input/Output InterfaceAlarm Contact Channels1,Relay output with current carrying capacity of1A@24VDCDigital Input Channels1Digital Inputs+13to+30V for state1-30to+3V for state0Max.input current:8mAButtons Reset buttonDIP Switch ConfigurationDIP Switches Turbo Ring,Master,Coupler,ReservePower ParametersConnection2removable4-contact terminal block(s)Pre-installed Power Module-LV/-LV-T models:PWR-100–LV-HV/-HV-T models:PWR-105-HV-INote The EDS-4014Series supports modular power supplies.The model names and powerparameters are determined by the installed power module.For example:EDS-4014-4GS-2QGS-T+PWR-100-LV=EDS-4014-4GS-2QGS-LV-TEDS-4014-4GS-2QGS-T+PWR-105-HV-I=EDS-4014-4GS-2QGS-HV-TIf you install a different power module,refer to the specifications of the correspondingmodel.For example,if you replace the power module of the EDS-4014-4GS-2QGS-LV-Twith the PWR-105-HV-I,refer to the specifications of the EDS-4014-4GS-2QGS-HV-T. Input Voltage-LV/-LV-T models:12/24/48VDC,Redundant dual inputs-HV/-HV-T models:110/220VDC/VAC,Single inputOperating Voltage-LV/-LV-T models:9.6to60VDC-HV/-HV-T models:88to300VDC,85to264VACInput Current-LV/-LV-T models:12-48VDC,1.50-0.40A or24VDC,0.70A-HV/-HV-T models:110-220VAC,50-60Hz,0.30-0.20A or110-220VDC,0.30-0.20A Power Consumption(Max.)EDS-4014-4GS-2QGS-LV(-T)models:12.15WEDS-4014-4GS-2QGS-HV(-T)models:14.44WOverload Current Protection SupportedReverse Polarity Protection SupportedPhysical CharacteristicsIP Rating IP40Dimensions55x140x122.5mm(2.17x5.51x4.82in)Weight846g(1.87lb)Installation DIN-rail mounting,Wall mounting(with optional kit)Housing MetalEnvironmental LimitsOperating Temperature Standard Models:-10to60°C(14to140°F)Wide Temp.Models:-40to75°C(-40to167°F)Standards and CertificationsIndustrial Cybersecurity IEC62443-4-1IEC62443-4-2Safety UL61010-2-201,EN62368-1(LVD)EMC EN55032/35,EN61000-6-2/-6-4EMI CISPR32,FCC Part15B Class AEMS IEC61000-4-2ESD:Contact:8kV;Air:15kVIEC61000-4-3RS:80MHz to1GHz:20V/mIEC61000-4-4EFT:Power:4kV;Signal:4kVIEC61000-4-5Surge:Power:4kV;Signal:4kVIEC61000-4-6CS:10VIEC61000-4-8PFMFMaritime-LV/-LV-T models:DNV,ABS,NK,LRVibration IEC60068-2-6Shock IEC60068-2-27Freefall IEC60068-2-32Railway EN50121-4Traffic Control NEMA TS2Power Substation IEC61850-3,IEEE1613Class1Hazardous Locations Class I Division2,ATEX,IECExMTBFTime EDS-4014-4GS-2QGS-LV/LV-T:1,003,814hrsEDS-4014-4GS-2QGS-HV/HV-T:489,769hrsWarrantyWarranty Period5yearsDetails See /warrantyPackage ContentsDevice1x EDS-4014Series switchDocumentation1x quick installation guide1x product notice,Simplified Chinese1x product certificates of quality inspection,Simplified Chinese1x warranty cardDimensionsOrdering InformationModel Name 10/100BaseT(X)Ports(RJ45Connector)100/1000BaseSFPPorts1000/2500BaseSFPPortsOperating VoltagePre-installedPower ModuleOperating Temp.EDS-4014-4GS-2QGS-LV8429.6to60VDC PWR-100-LV-10to60°C EDS-4014-4GS-2QGS-LV-T8429.6to60VDC PWR-100-LV-40to75°CEDS-4014-4GS-2QGS-HV84288to300VDC,85to264VACPWR-105-HV-I-10to60°CEDS-4014-4GS-2QGS-HV-T 84288to300VDC,85to264VACPWR-105-HV-I-40to75°CAccessories(sold separately)SFP ModulesSFP-1GEZXLC SFP module with11000BaseEZX port with LC connector for110km transmission,0to60°C operatingtemperatureSFP-1GEZXLC-120SFP module with11000BaseEZX port with LC connector for120km transmission,0to60°C operatingtemperatureSFP-1GLHLC SFP module with11000BaseLH port with LC connector for30km transmission,0to60°C operatingtemperatureSFP-1GLHXLC SFP module with11000BaseLHX port with LC connector for40km transmission,0to60°C operatingtemperatureSFP-1GLSXLC SFP module with11000BaseLSX port with LC connector for1km/2km transmission,0to60°Coperating temperatureSFP-1GLXLC SFP module with11000BaseLX port with LC connector for10km transmission,0to60°C operatingtemperatureSFP-1GSXLC SFP module with11000BaseSX port with LC connector for300m/550m transmission,0to60°Coperating temperatureSFP-1GZXLC SFP module with11000BaseZX port with LC connector for80km transmission,0to60°C operatingtemperatureSFP-1GLHLC-T SFP module with11000BaseLH port with LC connector for30km transmission,-40to85°C operatingtemperatureSFP-1GLHXLC-T SFP module with11000BaseLHX port with LC connector for40km transmission,-40to85°Coperating temperatureSFP-1GLSXLC-T SFP module with11000BaseLSX port with LC connector for1km/2km transmission,-40to85°Coperating temperatureSFP-1GLXLC-T SFP module with11000BaseLX port with LC connector for10km transmission,-40to85°C operatingtemperatureSFP-1GSXLC-T SFP module with11000BaseSX port with LC connector for300m/550m transmission,-40to85°Coperating temperatureSFP-1GZXLC-T SFP module with11000BaseZX port with LC connector for80km transmission,-40to85°C operatingtemperatureSFP-1G10ALC WDM-type(BiDi)SFP module with11000BaseSFP port with LC connector for10km transmission;TX1310nm,RX1550nm,0to60°C operating temperatureSFP-1G10BLC WDM-type(BiDi)SFP module with11000BaseSFP port with LC connector for10km transmission;TX1550nm,RX1310nm,0to60°C operating temperatureSFP-1G20ALC WDM-type(BiDi)SFP module with11000BaseSFP port with LC connector for20km transmission;TX1310nm,RX1550nm,0to60°C operating temperatureSFP-1G20BLC WDM-type(BiDi)SFP module with11000BaseSFP port with LC connector for20km transmission;TX1550nm,RX1310nm,0to60°C operating temperatureSFP-1G40ALC WDM-type(BiDi)SFP module with11000BaseSFP port with LC connector for40km transmission;TX1310nm,RX1550nm,0to60°C operating temperatureSFP-1G40BLC WDM-type(BiDi)SFP module with11000BaseSFP port with LC connector for40km transmission;TX1550nm,RX1310nm,0to60°C operating temperatureSFP-1G10ALC-T WDM-type(BiDi)SFP module with11000BaseSFP port with LC connector for10km transmission;TX1310nm,RX1550nm,-40to85°C operating temperatureSFP-1G10BLC-T WDM-type(BiDi)SFP module with11000BaseSFP port with LC connector for10km transmission;TX1550nm,RX1310nm,-40to85°C operating temperatureSFP-1G20ALC-T WDM-type(BiDi)SFP module with11000BaseSFP port with LC connector for20km transmission;TX1310nm,RX1550nm,-40to85°C operating temperatureSFP-1G20BLC-T WDM-type(BiDi)SFP module with11000BaseSFP port with LC connector for20km transmission;TX1550nm,RX1310nm,-40to85°C operating temperatureSFP-1G40ALC-T WDM-type(BiDi)SFP module with11000BaseSFP port with LC connector for40km transmission;TX1310nm,RX1550nm,-40to85°C operating temperatureSFP-1G40BLC-T WDM-type(BiDi)SFP module with11000BaseSFP port with LC connector for40km transmission;TX1550nm,RX1310nm,-40to85°C operating temperatureSFP-1FELLC-T SFP module with1100Base single-mode with LC connector for80km transmission,-40to85°Coperating temperatureSFP-1FEMLC-T SFP module with1100Base multi-mode,LC connector for2/4km transmission,-40to85°C operatingtemperatureSFP-1FESLC-T SFP module with1100Base single-mode with LC connector for40km transmission,-40to85°Coperating temperatureSFP-2.5GSLC-T SFP module with12.5GBaseFX port with LC connector,single-mode,for5km transmission,-40to85°C operating temperatureSFP-2.5GLSLC-T SFP module with12.5GBaseFX port with LC connector,single-mode,for20km transmission,-40to85°C operating temperatureSFP-2.5GMLC-T SFP module with12.5GBaseFX port with LC connector,multi-mode,for170,200,550,600mtransmission,-40to85°C operating temperatureSFP-2.5GSLHLC-T SFP module with12.5GBaseFX port with LC connector,single-mode,for45km transmission,-40to85°C operating temperaturePower SuppliesHDR-60-2460W/2.5A DIN-rail24VDC power supply,universal85to264VAC or120to370VDC input voltage,-30to70°C operating temperatureNDR-120-24120W/5.0A DIN-rail24VDC power supply,universal90to264VAC or127to370VDC input voltage,-20to70°C operating temperatureNDR-120-48120W/2.5A DIN-rail48VDC power supply,universal90to264VAC or127to370VDC input voltage,-20to70°C operating temperatureNDR-240-48240W/5.0A DIN-rail48VDC power supply,universal90to264VAC or127to370VDC input voltage,-20to70°C operating temperatureMDR-40-24DIN-rail24VDC power supply with40W/1.7A,85to264VAC,or120to370VDC input,-20to70°Coperating temperatureMDR-60-24DIN-rail24VDC power supply with60W/2.5A,85to264VAC,or120to370VDC input,-20to70°Coperating temperature©Moxa Inc.All rights reserved.Updated Oct27,2022.This document and any portion thereof may not be reproduced or used in any manner whatsoever without the express written permission of Moxa Inc.Product specifications subject to change without notice.Visit our website for the most up-to-date product information.。

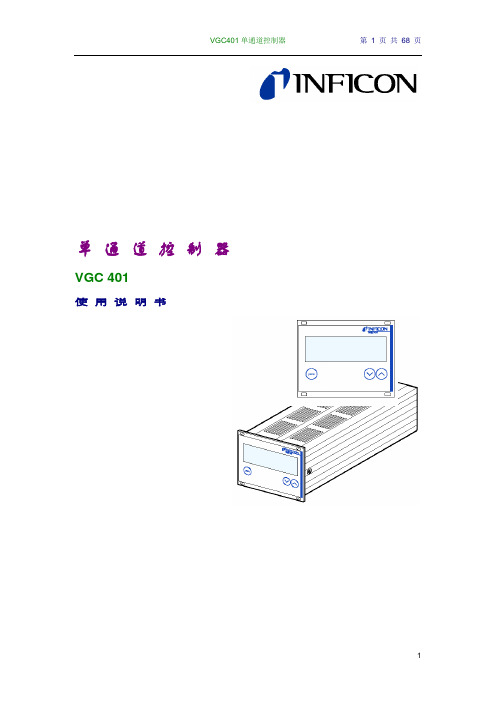

VGC401 中文手册

单通道控制器VGC 401使用说明书产品标识与INFICON联系时,请告知产品名牌上的信息。

为便于参考,现将名牌上的信息表示如下:有效性本说明书用于件号为398-010的产品。

件号(PN)可从产品名牌上看到。

本说明书件基于固件版号302-519-A。

如你的仪器工作与本文件的说明不符,请检查是否与上述固件版号(48)相符。

我们保留本说明书不事先通知的技术修改权。

全部尺寸均用毫米表示。

用途V GC401与INFICON生产的规管同时使用,用于真空系统的总压强测量。

全部产品必须按产品说明书使用。

供货范围1件单通道控制器1根电源电缆1根橡皮条2个橡皮脚4个凹槽螺丝4个塑料套管产品标识有效性用途供货范围1 安全1.1 使用符号1.2 人员要求1.3 一般安全规则1.4 责任与保修2 技术参数3 安装3.1 人员3.2 安装,设置3.2.1 机架安装3.2.2 安装在控制屏内3.2.3 用作桌上式仪器3.3 电源连接3.4 传感器连接3.5 控制器连接3.6 RS232接口连接4 运行4.1 面板4.2 VGC401的On和Off 4.3 工作模式4.4 测量模式4.5 参数模式4.5.1 参数4.6 测试模式4.6.1 参数4.6.2 测试程序5 维护6 故障查找7 检修8 附件9 储存10 废物处理附录A. 转换表提供的压强传感器B. 缺省参数C. 软件升级D. 文献E. 索引质量保证书参考在本说明书内的内容使用符号(XY)。

参考“文献”中的内容使用符号([Z])。

1.1 使用符号其它符号灯亮灯闪灯黑按此键(例:’para’键)不要按任何键.1.2 人员要求1.3 一般安全规则对于全部要进行的工作,必须遵守规章制度和采取必要的预防措施和考虑本说明书中的安全规则。

向所有其他用户通报安全信息。

1.4 责任与保修如最终用户或第三方发生以下情况,INFICON将不承担赔偿责任和保修将不再有效。

●不顾本说明书中的信息。

工控机技术资料

串 口 … … … … … … … … … … … … … … … … … … … … … … … … … … … … … … … … … … … 9

并 口 … … … … … … … … … … … … … … … … … … … … … … … … … … … … … … … … … … … 10

接 口 功 能 介 绍 … … … … … … … … … … … … … … … … … … … … … … … … … … … … … … … 5

功 能 示 意 图 … … … … … … … … … … … … … … … … … … … … … … … … … … … … … … 5

技术支持

用户可通过以下途径获得思泰基电脑的相关技术支持:

表 1.思泰基技术支持信息

网址 http://www.seatech.sh.cn

E-mail seatech@seatech.sh.cn

电话 021-61450355/6/7/8

通讯地址 上海宜山路 1618 号综合楼四楼

CPU

采用低功耗 486CPU,并可通过跳线调节 CPU 的频率。

CRT 接口/ LCD 接口

DX-440C 同时提供 CRT/LCD 显示接口,可支持各种液晶屏。

DOC 插座

DX-440C 提供一个在板 DOC (Disk On Chip) 插座,可支持 8M~144M 的 DOC。

软驱接口

DX-440C 主板已集成标准的软驱接口于主板上。

-4-

SEATECH 产品特征

研发部

本章介绍

本章主要包括 DX-440C 详细的一些安装和配置的相关信息,主要内容有: l 接口功能介绍 l 电源 l 内存 l 串口 l 并口 l IDE 硬盘接口 l 软驱 l DOC 插座 l Utility 接口 l 总线接口;

AD9954芯片中文数据表(部分)

AD9954芯片中文数据表(部分)操作模式单音信号模式在单音信号模式下,DDS核使用了一个单独的调谐字(tuningword)。

存储在FTW0中的任何值可被用来做相位累加。

这个值仅能手动改变,通过向FTW0写一个新值并更新I/O来实现。

相位调整可通过相位偏置寄存器实现。

RAM可控制操作模式直接转换模式直接转换模式使能FSK调制或PSK调制。

AD9954在直接转换模式可以编程,其通过写RAM使能位为真并将每个期望的profile的RAM片段模式控制位编程成逻辑000(b)实现。

对于当前profile,该模式仅读取了RAM片段起始地址的内容。

直接转换模式下,没有地址ramping可用。

为了执行4-toneFSK,对于直接转换模式及一个唯一的起始地址值,使用者对每一个RAM片段控制字编程。

另外,RAM使能位被写为真,这使得RAM、RAM目的文件位被写成fale,设置RAM输出为频率调谐字。

Profile〈1:0〉输入为4-toneFSK数据输入。

当profile被改变时,存储在新的profile中的频率调谐字被加载到相位累加器中并且被用做相位连续型式中的当前存储值的增量。

相位-偏置字驱使相位偏置加法器。

对于数据而言,2-toneFSK可通过仅使用一个profilepin来完成。

对于为了PSK调制将AD9954编程和FSK是相似的,除了RAM目的文件位设置为逻辑“1”外,使RAM输出驱动相位偏置加法器。

FTW0驱动输入至相位累加器。

Togglingtheprofilepin改变(调制)当前相位值。

RAM的upper14位驱动相位加法器(〈31:18〉)。

当RAM目的文件位被设置时,RAM输出的Bit〈17:0〉未被使用。

直接转换模式下,无停留位(no-dwell)是一项禁忌注意事项。

Ramp-Up模式Ramp-Up模式,结合分割的RAM容量,允许多达4种不同的“weepprofile”在AD9954中编程。

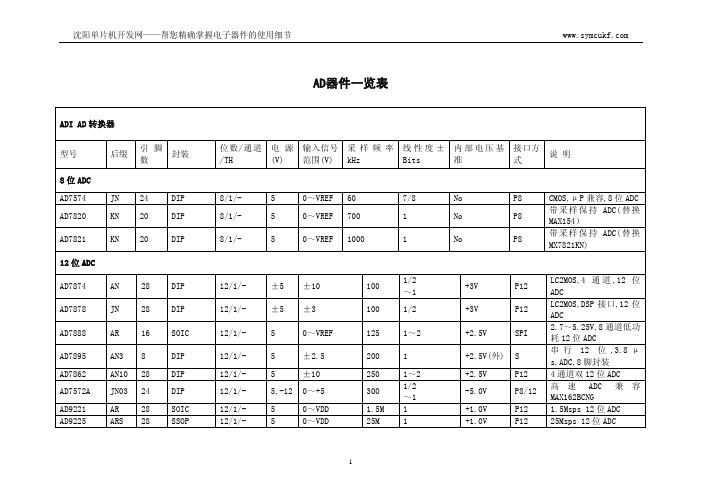

AD器件一览表

AD器件一览表

ADI AD 转换器

型号

8 位 ADC AD7574 AD7820

后缀

引脚 数

封装

JN 24

DIP

KN 20

DIP

AD7821

KN 20

DIP

12 位 ADC

AD7874

AN 28 DIP

AD7878

JN 28 DIP

三相电量测量 IC

3

沈阳单片机开发网——帮您精确掌握电子器件的使用细节

TI AD 转换器

器件

后缀

并行输出 AD 转换器

TLC0820A CN

THS1206 THS1408

CDA CPFB

串行输出 AD 转换器

TLC0838 TLV0838 TLC549 TLC549 TLV1544 TLC1549

20 8

8

8

8

8

16 10

8

10

16 10

20 10

16 10

20 10

20 12 20 12

±1.0 20

8

5

12.5 8 位 A/D 转换器

±1.0 37.9 8

3.3

50

低电压

±0.5 40

1

5

Y

12

8 位 A/D 转换器

±0.5 40

1

5

Y

12

8 位 A/D 转换器

±1.0 66

4

3.3

Y

Y

AD7777

AN

28 DIP

AD7861

AP

44 PLCC

AD7853L AN

NRF9E5中文资料

表 3 SFR 存储器映射表 1.2 PWM

nRF9E5 有一个可编程脉宽调制输出,它是 P0.7 的复用脚。PWM 可通过编程设置成 6,7,8 位脉宽 调制。占空比通过设置一个 8 位寄存器可设置在 0%和 100%间。 1.3 SPI

nRF9E5 以 SPI 接口控制为特点。SPI 的 3 根数据线(MISO,SCK 和 MOSI)具有多种复用功能。SPI 硬件不产生片选择信号。设计人员可以通过 GPIO 来设置一个或多个外部 SPI 的片选。EECSN 引脚是通用 I/O 接口,它在这里作为导入 EEPROM 的片选端。

应用领域:

无线数据通讯 报警和安全系统 自动测试系统 家庭自动化控制 遥控装置 监测 车辆安全系统 工业控制 无线通信 电信终端

适合高频应用

载波检测功能

低供电电流,发射时的典型值为 11mA@-10dBm,接收的典型值为 12.5mA

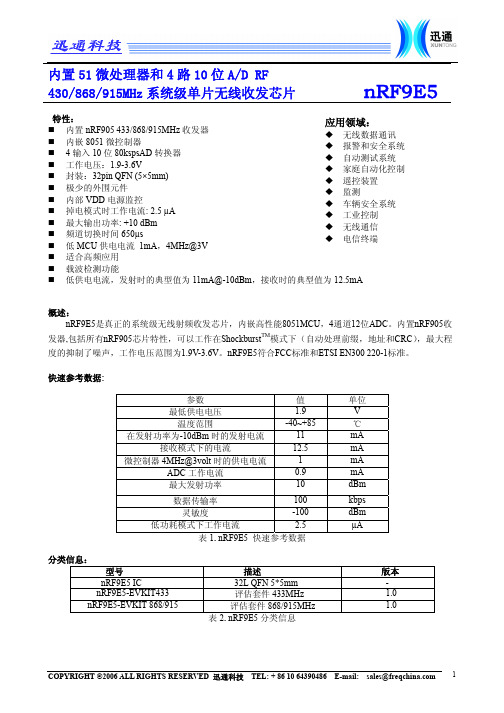

概述: nRF9E5是真正的系统级无线射频收发芯片,内嵌高性能8051MCU,4通道12位ADC。内置nRF905收

片内微控制器的指令周期为 4 到 20 个时钟周期,8051 为 12 到 48 个时钟周期。中断控制器支持 5 个扩展 中断源:ADC 中断, SPI 中断, 两个无线收发中断、一个唤醒中断。微控制器内有 3 个与 8052 相同的 定时器。一个与 8051 相同的串行通讯端口 UART。 CPU 备有两个数据指针,使得片外 RAM 存取数据变 得更为方便。系统时钟频率由晶体振荡器提供。 1.1. 1 存储器结构

AD9959数据手册部分内容中文翻译

精心整理AD9959数据手册(部分)GENERALDESCRIPTION概述TheAD9959consistsoffourdirectdigitalsynthesizer(DDS)coresthatprovideindependentfrequency ,phase,andamplitudecontroloneachchannel.Thisflexibilitycanbeusedtocorrectimbalancesbetweensig nalsduetoanalogprocessing,suchasfiltering,amplification,orPCBlayout-relatedmismatches.Becauseal lchannelsshareacommonsystemclock,theyareinherentlysynchronized.Synchronizationofmultipledevi cesissupported.TheAD9959canperformuptoa16-levelmodulationoffrequency,phase,oramplitude(FS或PCB 同步。

SPI 脚(DAC具10VDDce lyorusedincombinationwithanintegratedREFCLKmultiplier(PLL)uptoamaximumof500MSPS.The PLLmultiplicationfactorisprogrammablefrom4to20,inintegersteps.TheREFCLKinputalsofeaturesa noscillatorcircuittosupportanexternalcrystalastheREFCLKsource.Thecrystalmustbebetween20MH zand30MHz.ThecrystalcanbeusedincombinationwiththeREFCLKmultiplier.DAC的输出供给参考必须通过电阻接到A VDD或接到A VDD中心抽头变压器。

AD 芯片资料中文版

AD9954- Direct Digital Synthesizer400 MSPS 14-Bit, 1.8 V CMOS功能: (2)应用 (2)概述 (2)AD9954电气特性 (3)最大操作范围 (4)Table 2. (4)管脚定义 (4)管脚功能描述 (4)典型的性能特性 (6)原理 (7)器件块 (7)控制寄存器位描述 (10)Other Register Descriptions 其他寄存器描述 (14)Programming AD9954 Features-- AD9954编程特性 (18)SERIAL PORT OPERATION串口操作 (19)INSTRUCTION BYTE指令字节 (20)SERIAL INTERFACE PORT PIN DESCRIPTION串行接口管脚描述 (20)MSB/LSB TRANSFERS (20)RAM I/O VIA SERIAL PORT (21)Power-Down Functions of the AD9954 AD9954省电功能 (21)功能:400MSPS 内部时钟 集成14位DAC可编程相位/幅度抖动 32位控制字相位噪声小于等于-120dbc/Hz@1kHz(DAC 输出)出色的动态性能>80db SFDR@160MHz (偏离100KHz ) 串行I/O 口控制 超高速模拟比较器 自动线性和非线性扫频能力 4种频率/相位偏移坡面 1.8v 电压供电软件或者硬件控制休眠内部集成1024字节*32位RAM 大多数输入口支持5v 电平PLL REFCLK 乘法器(4倍-20倍) 单晶振驱动内部时钟 相位调制能力 多芯片同步 应用敏捷LO 频率输出 可编程的时钟发生器雷达和扫频系统中的FM 啁啾源自动雷达测试和测量设备 声光设备驱动概述AD9954具有一个14位DAC 最高达400 MSPS 的DDS 。

AD9954使用了先进的DDS 技术,内部集成高速,高性能的DAC 形成数字可编程,完整的高频合成器,能产生高达200MHz 模拟正弦波的能力。

AD420中文资料

AD420中文资料摘要:AD420是具有灵活串行数字接口的16住数模转换器,它带有SPI和Microwire总线接口,使用方便、性价比高。

介绍了AD420的引脚功能、电气特性,阐述了AD420与MSP430的接口技术,并给出了在MSP430控制下的实际应用电路及程序。

关键词:AD420;D/A转换;MSP430;电流环1 概述AD420是ADI公司生产的高精度、低功耗全数字电流环输出转换器。

AD420的输出信号可以是电流信号,也可以是电压信号。

其中电流信号的输出范围为4mA~20mA,0mA~20mA或0mA~24mA,具体可通过引脚RANGE SELECTl,RANGE SELECT2进行配置。

当需要输出电压信号时,它也能从一个隔离引脚提供电压输出,这时需外接一个缓冲放大器,可输出0V~5V,0V~10V,±5V 或±10V电压。

AD420具有灵活的串行数字接口(最大速率可达3.3 Mb/s),使用方便、性价比高、抑制干扰能力强,非常适合用于高精度远程控制系统。

AD420与单片机的接口方式有2种:3线制和异步制。

单片机系统通过AD420可实现连续的模拟量输出。

其主要特点如下:宽泛的电源电压范围为12 V~32 V,输出电压范围为0V~-2.5 V;带有3线模式的SPI或Microwire接口,可采集连续的模拟输入信号,采用异步模式时仅需少量的信号线;数据输出引脚可将多个AD420器件连接成菊链型;上电初始化时,其输出最小值为0 mA,4 mA或O V;具有异步清零引脚,可将输出复位至最小值(0mA、4 mA或0V);BOOST引脚可连接一个外部晶体管来吸收回路电流,降低功耗;只需外接少量的外部器件,就能达到较高的精度。

AD420采用24引脚SOIC和PDIP封装,表1是其引脚功能说明。

2 工作原理在AD420中,二阶调节器用于保持最小死区。

从调节器发出的单字节流控制开关电流源,两个连续的电阻电容装置进行过滤。

AD9445资料

14-Bit, 105/125 MSPS, IF Sampling ADCAD9445 Rev. 0Information furnished by Analog Devices is believed to be accurate and reliable. However, noresponsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners. One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 Fax: 781.461.3113 © 2005 Analog Devices, Inc. All rights reserved.FEATURES125 MSPS guaranteed sampling rate (AD9445BSV-125) 78.3 dBFS SNR/92 dBFS SFDR with 30 MHz input (3.2 V p-p) 74.8 dBFS SNR/95 dBFS SFDR with 30 MHz input (2.0 V p-p) 77.0 dBFS SNR/87 dBFS SFDR with 170 MHz input (3.2 V p-p) 74.6 dBFS SNR/95 dBFS SFDR with 170 MHz input (2.0 V p-p) 73.0 dBFS SNR/88 dBFS SFDR with 300 MHz input (2.0 V p-p) 102 dBFS 2-tone SFDR with 30 MHz and 31 MHz92 dBFS 2-tone SFDR with 170 MHz and 171 MHz60 fsec rms jitterExcellent linearityDNL = ±0.25 LSB typicalINL = ±0.8 LSB typical2.0 V p-p to 4.0 V p-p differential full-scale inputBuffered analog inputsLVDS outputs (ANSI-644 compatible) or CMOS outputs Data format select (offset binary or twos complement) Output clock available3.3 V and 5 V supply operationAPPLICATIONSMulticarrier, multimode cellular receiversAntenna array positioningPower amplifier linearizationBroadband wirelessRadarInfrared imagingMedical imagingCommunications instrumentationGENERAL DESCRIPTIONThe AD9445 is a 14-bit, monolithic, sampling analog-to-digital converter (ADC) with an on-chip IF sampling track-and-hold circuit. It is optimized for performance, small size, and ease of use. The product operates at up to a 125 MSPS conversion rate and is designed for multicarrier, multimode receivers, such as those found in cellular infrastructure equipment.The ADC requires 3.3 V and 5.0 V power supplies and a low voltage differential input clock for full performance operation. No external reference or driver components are required for many applications. Data outputs are CMOS or LVDS compatible (ANSI-644 compatible) and include the means to reduce the overall current needed for short trace distances.FUNCTIONAL BLOCK DIAGRAMVREF05489-1REFBSENSE REFTFigure 1.Optional features allow users to implement various selectable operating conditions, including input range, data format select, high IF sampling mode, and output data mode.The AD9445 is available in a Pb-free, 100-lead, surface-mount, plastic package (100-lead TQFP/EP) specified over the industrial temperature range −40°C to +85°C.PRODUCT HIGHLIGHTS1.High performance: outstanding SFDR performance for IFsampling applications such as multicarrier, multimode 3G, and 4G cellular base station receivers.2.Ease of use: on-chip reference and high input impedancetrack-and-hold with adjustable analog input range and an output clock simplifies data capture.3.Packaged in a Pb-free, 100-lead TQFP/EP package.4.Clock duty cycle stabilizer (DCS) maintains overall ADCperformance over a wide range of clock pulse widths.5.OR (out-of-range) outputs indicate when the signal isbeyond the selected input range.6.RF enable pin allows users to configure the device foroptimum SFDR when sampling frequencies above 210 MHz (AD9445-125) or 240 MHz (AD9445-105).AD9445Rev. 0 | Page 2 of 40TABLE OF CONTENTSFeatures..............................................................................................1 Applications.......................................................................................1 General Description.........................................................................1 Functional Block Diagram..............................................................1 Product Highlights...........................................................................1 Revision History...............................................................................2 Specifications.....................................................................................3 DC Specifications.........................................................................3 AC Specifications..........................................................................4 Digital Specifications...................................................................6 Switching Specifications..............................................................6 Timing Diagrams..........................................................................7 Absolute Maximum Ratings............................................................8 Thermal Resistance......................................................................8 ESD Caution..................................................................................8 Terminology.......................................................................................9 Pin Configurations and Function Descriptions.........................10 Equivalent Circuits.........................................................................15 Typical Performance Characteristics...........................................16 Theory of Operation......................................................................24 Analog Input and Reference Overview...................................24 Clock Input Considerations......................................................26 Power Considerations................................................................27 Digital Outputs...........................................................................27 Timing.........................................................................................27 Operational Mode Selection.....................................................28 Evaluation Board............................................................................29 Outline Dimensions.......................................................................37 Ordering Guide.. (37)REVISION HISTORY10/05—Revision 0: Initial VersionAD9445Rev. 0 | Page 3 of 40SPECIFICATIONSDC SPECIFICATIONSAVDD1 = 3.3 V , AVDD2 = 5.0 V , DRVDD = 3.3 V , LVDS mode, specified minimum sampling rate, 2.0 V p-p differential input, internal trimmed reference (1.0 V mode), AIN = −1.0 dBFS, DCS on, unless otherwise noted. RF ENABLE = AGND. Table 1.AD9445BSVZ-105 AD9445BSVZ-125 Parameter Temp Min Typ Max Min Typ Max Unit RESOLUTION Full 14 14 Bits ACCURACY No Missing Codes Full Guaranteed Guaranteed Offset Error Full −7 +7 −7 +7 mV 25°C ±3 ±3 mV Gain Error Full −3 +3 −3 +3 % FSR 25°C −2 +2 −2 +2 % FSRDifferential Nonlinearity (DNL)1Full −0.6 ±0.25 +0.65 −0.6 ±0.25 +0.65 LSB 5 5Integral Nonlinearity (INL)125°C ±0.65 ±0.8 LSB Full −1.6 +1.6 −2 +2 LSBVOLTAGE REFERENCEOutput Voltage VREF = 1.0 V Full 0.9 1.0 1.1 0.9 1.0 1.1 V Load Regulation @ 1.0 mA Full ±2 ±2 mV Reference Input Current (External VREF = 1.6 V) Full μA INPUT REFERRED NOISE 25°C 1.0 1.0 LSB rms ANALOG INPUT Input Span VREF = 1.6 V Full 3.2 3.2 V p-p VREF = 1.0 V Full 2.0 2.0 V p-p Internal Input Common-Mode Voltage Full 3.5 3.5 VExternal Input Common-Mode Voltage Full 3.1 3.9 3.1 3.9 VInput Resistance 2Full 1 1 kΩ Input Capacitance 2Full 6 6 pF POWER SUPPLIES Supply Voltage AVDD1 Full 3.14 3.3 3.46 3.14 3.3 3.46 V AVDD2 Full 4.75 5.0 5.25 4.75 5.0 5.25 VDRVDD—LVDS Outputs Full 3.0 3.6 3.0 3.6 VDRVDD—CMOS Outputs Full 3.0 3.3 3.6 3.0 3.3 3.6 VSupply Current 1AVDD1 Full 335 364 384 424 mAAVDD21, 3Full 169 196 172 199 mA I DRVDD 1—LVDS Outputs Full 63 78 63 78 mAI DRVDD 1—CMOS Outputs Full 14 14 mAPSRROffset Full 1 1 mV/V Gain Full 0.2 0.2 %/VPOWER CONSUMPTIONLVDS Outputs Full 2.2 2.4 2.3 2.6 W CMOS Outputs (DC Input) Full 2.0 2.1 W1Measured at the maximum clock rate, f IN = 15 MHz, full-scale sine wave, with a 100 Ω differential termination on each pair of output bits for LVDS output mode and approximately 5 pF loading on each output bit for CMOS output mode. 2Input capacitance or resistance refers to the effective impedance between one differential input pin and AGND. Refer to Figure 6 for the equivalent analog input structure. 3For RF ENABLE = AVDD1, I AVDD2 increases by ~30 mA, which increases power dissipation.AD9445Rev. 0 | Page 4 of 40AC SPECIFICATIONSAVDD1 = 3.3 V , AVDD2 = 5.0 V , DRVDD = 3.3 V , LVDS mode, specified minimum sample rate, 2.0 V p-p differential input, internal trimmed reference (1.0 V mode), A IN = −1.0 dBFS, DCS on, RF ENABLE = ground, unless otherwise noted. Table 2.AD9445BSVZ-105 AD9445BSVZ-125Parameter Temp Min Typ Max Min Typ Max Unit SIGNAL-TO-NOISE RATIO (SNR) f IN = 10 MHz 25°C 74.3 74.1 dB f IN = 30 MHz 25°C 73.3 74.3 72.9 73.8 dB Full 73 72.5 dB f IN = 170 MHz 25°C 72.9 73.6 72.3 73.2 dBf IN = 225 MHz 125°C 72.2 73 72 72.9 dB Full 72.2 71.4 dBf IN = 300 MHz 225°C 71.4 72.1 71.3 72 dB f IN = 400 MHz 225°C 71 71 dBf IN = 450 MHz 225°C 70.5 70.5 dB f IN = 10 MHz (3.2 V p-p Input) 25°C 77.6 77.3 dB f IN = 30 MHz (3.2 V p-p Input) 25°C 77.5 77.3 dB f IN = 170 MHz (3.2 V p-p Input) 25°C 76 76 dBf IN = 225 MHz (3.2 V p-p Input)125°C 75.3 75.4 dB f IN = 300 MHz (3.2 V p-p Input)225°C 73.7 73.5 dB SIGNAL-TO-NOISE AND DISTORTION (SINAD) f IN = 10 MHz 25°C 74.2 73.9 dB f IN = 30 MHz 25°C 73.2 74.2 72.8 73.7 dB Full 72.8 72.3 dB f IN = 170 MHz 25°C 72.3 73.3 72.4 73.0 dBf IN = 225 MHz 125°C 71.4 72.5 71.9 72.5 dB Full 71.3 70.7 dB f IN = 300 MHz 225°C 70.2 71.7 69.3 71.5 dBf IN = 400 MHz 225°C 67.2 66.3 dB f IN = 450 MHz 225°C 65.2 64.3 dB f IN = 10 MHz (3.2 V p-p Input) 25°C 77.4 76.9 dB f IN = 30 MHz (3.2 V p-p Input) 25°C 77.3 76.8 dB f IN = 170 MHz (3.2 V p-p Input) 25°C 75.7 75.4 dBf IN = 225 MHz (3.2 V p-p Input)125°C 75.1 75.2 dBf IN = 300 MHz (3.2 V p-p Input)225°C 72.5 71.8 dB EFFECTIVE NUMBER OF BITS (ENOB) f IN = 10 MHz 25°C 12.2 12.2 Bits f IN = 30 MHz 25°C 12.2 12.1 Bits f IN = 170 MHz 25°C 12.1 12.0 Bitsf IN = 225 MHz 125°C 12.0 12.0 Bits f IN = 300 MHz 225°C 11.8 11.8 Bitsf IN = 400 MHz 225°C 11.7 11.7 Bits f IN = 450 MHz 225°C 11.6 11.6 BitsAD9445Rev. 0 | Page 5 of 40AD9445BSVZ-105 AD9445BSVZ-125Parameter Temp Min Typ Max Min Typ Max UnitSPURIOUS-FREE DYNAMIC RANGE(SFDR, Second or Third Harmonic) f IN = 10 MHz 25°C 95 95 dBc f IN = 30 MHz 25°C 84 92 85 94 dBc Full 83 82 dBc f IN = 170 MHz 25°C 82 94 80 91 dBc f IN = 225 MHz 125°C 76 87 83 88 dBc Full 75 75 dBc f IN = 300 MHz 225°C 76 87 75 87 dBcf IN = 400 MHz 225°C 75 73 dBc f IN = 450 MHz 225°C 70 69 dBc f IN = 10 MHz (3.2 V p-p Input) 25°C 92 92 dBc f IN = 30 MHz (3.2 V p-p Input) 25°C 88 91 dBc f IN = 170 MHz (3.2 V p-p Input) 25°C 86 86 dBc f IN = 225 MHz (3.2 V p-p Input)125°C 81 80 dBcf IN = 300 MHz (3.2 V p-p Input)225°C 77 76 dBcWORST SPUR EXCLUDING SECOND ORTHIRD HARMONICS f IN = 10 MHz 25°C −97 −97 dBc f IN = 30 MHz 25°C −99 −90 −98 −89 dBc Full −90 −88 dBc f IN = 170 MHz 25°C −99 −92 −93 −85 dBc f IN = 225 MHz 125°C −94 −88 −94 −84 dBc Full −86 −80 dBc f IN = 300 MHz 225°C −97 −90 −92 −82 dBcf IN = 400 MHz 225°C −93 −93 dBc f IN = 450 MHz 225°C −82 −87 dBc f IN = 10 MHz (3.2 V p-p Input) 25°C −97 −95 dBc f IN = 30 MHz (3.2 V p-p Input) 25°C −97 −95 dBc f IN = 170 MHz (3.2 V p-p Input) 25°C −97 −95 dBc f IN = 225 MHz (3.2 V p-p Input)125°C −95 −94 dBcf IN = 300 MHz (3.2 V p-p Input)225°C −93 −91 dBc TWO-TONE SFDRf IN = 30.3 MHz @ −7 dBFS,31.3 MHz @ −7 dBFS25°C 102 102 dBFS f IN = 170.3 MHz @ −7 dBFS,171.3 MHz @ −7 dBFS 25°C 92 91 dBFS ANALOG BANDWIDT H Full 615 615 M H z1 RF ENABLE = low (AGND ) for AD9445-105; RF ENABLE = high (AVDD1) for AD9445-125. 2RF ENABLE = high (AVDD1).AD9445Rev. 0 | Page 6 of 40DIGITAL SPECIFICATIONSAVDD1 = 3.3 V , AVDD2 = 5.0 V , DRVDD = 3.3 V , R LVDS_BIAS = 3.74 kΩ, unless otherwise noted. Table 3.AD9445BSVZ-105 AD9445BSVZ-125 Parameter Temp Min Typ Max Min Typ Max Unit CMOS LOGIC INPUTS (DFS, DCS MODE, OUTPUT MODE) High Level Input Voltage Full 2.0 2.0 V Low Level Input Voltage Full 0.8 0.8 VHigh Level Input Current Full 200 200 μALow Level Input Current Full −10 +10 −10 +10 μAInput Capacitance Full 2 2 pFDIGITAL OUTPUT BITS—CMOS MODE (D0 to D13, OTR)1DRVDD = 3.3 VHigh Level Output Voltage Full 3.25 3.25 VLow Level Output Voltage Full 0.2 0.2 V DIGITAL OUTPUT BITS—LVDS MODE (D0 to D13, OTR)V OD Differential Output Voltage 2Full 247 545 247 545 mVV OS Output Offset Voltage Full 1.125 1.375 1.125 1.375 VCLOCK INPUTS (CLK+, CLK−)Differential Input Voltage Full 0.2 0.2 VCommon-Mode Voltage Full 1.3 1.5 1.6 1.3 1.5 1.6 V Differential Input Resistance Full 1.1 1.4 1.7 1.1 1.4 1.7 kΩDifferential Input Capacitance Full 2 2 pF1 Output voltage levels measured with 5 pF load on each output.2LVDS R TERM = 100 Ω.SWITCHING SPECIFICATIONSAVDD1 = 3.3 V , AVDD2 = 5.0 V , DRVDD = 3.3 V , unless otherwise noted. Table 4.AD9445BSVZ-105 AD9445BSVZ-125 Parameter Temp Min Typ Max Min Typ Max Unit CLOCK INPUT PARAMETERS Maximum Conversion Rate Full 105 125 MSPS Minimum Conversion Rate Full 10 10 MSPS CLK Period Full 9.5 8.0 nsCLK Pulse Width High 1(t CLKH ) Full 3.8 3.2 nsCLK Pulse Width Low 1 (t CLKL ) Full 3.8 3.2 ns DATA OUTPUT PARAMETERSOutput Propagation Delay—CMOS (t PD )2(Dx, DCO+) Full 3.35 3.35 ns Output Propagation Delay—LVDS (t PD )3 (Dx+), (t CPD )3 (DCO+) Full 2.1 3.6 4.8 2.3 3.6 4.8 ns Pipeline Delay (Latency) Full 13 13 CyclesAperture Delay (t A ) Full nsAperture Uncertainty (Jitter, t J ) Full 60 60 fsecrms1 With duty cycle stabilizer (DCS) enabled.2Output propagation delay is measured from clock 50% transition to data 50% transition with 5 pF load. 3LVDS R TERM = 100 Ω. Measured from the 50% point of the rising edge of CLK+ to the 50% point of the data transition.AD9445Rev. 0 | Page 7 of 40TIMING DIAGRAMSA INCLK+CLK–DATA OUTDCO+DCO–CPD05489-002Figure 2. LVDS Mode Timing Diagram05489-003VINCLK+CLK–DX DCO+DCO–Figure 3. CMOS Timing DiagramAD9445Rev. 0 | Page 8 of 40ABSOLUTE MAXIMUM RATINGSTable 5.Stresses above those listed under Absolute Maximum Ratingsmay cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operationalsection of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.With Respect To Parameter RatingELECTRICAL AVDD1 AGND −0.3 V to +4 V AVDD2 AGND −0.3 V to +6 V DRVDD DGND −0.3 V to +4 V AGND DGND −0.3 V to +0.3 V THERMAL RESISTANCEAVDD1 DRVDD −4 V to +4 V The heat sink of the AD9445 package must be soldered to ground. AVDD2 DRVDD −4 V to +6 V AVDD2 AVDD1 −4 V to +6 V Table 6.D0± to D13± DGND –0.3 V to DRVDD + 0.3 V Package Type θJA θJB θJCUnit CLK+/CLK− AGND –0.3 V to AVDD1 + 0.3 V100-lead TQFP/EP19.88.3 2 °C/WAGND –0.3 V to AVDD1 + 0.3 V OUTPUT MODE, DCSMODE, DFS, SFDR, RF ENABLETypical θJA = 19.8°C/W (heat sink soldered) for multilayerboard in still air.VIN+, VIN− AGND –0.3 V to AVDD2 + 0.3 V VREF AGND –0.3 V to AVDD1 + 0.3 V Typical θJB = 8.3°C/W (heat sink soldered) for multilayer board in still air.SENSE AGND –0.3 V to AVDD1 + 0.3 V REFT, REFB AGND –0.3 V to AVDD1 + 0.3 V Typical θJC = 2°C/W (junction to exposed heat sink) represents the thermal resistance through heat sink path.ENVIRONMENTAL–65°C to +125°C Storage TemperatureRangeAirflow increases heat dissipation, effectively reducing θJA . Also, more metal directly in contact with the package leads from metal traces through holes, ground, and power planes reduces the θJA . It is required that the exposed heat sink be soldered to the ground plane.–40°C to +85°C Operating Temperature Range300°C Lead Temperature(Soldering 10 sec) Junction Temperature 150°CESD CAUTIONESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.AD9445Rev. 0 | Page 9 of 40TERMINOLOGYAnalog Bandwidth (Full Power Bandwidth)Minimum Conversion RateThe clock rate at which the SNR of the lowest analog signal frequency drops by no more than 3 dB below the guaranteed limit.The analog input frequency at which the spectral power of the fundamental frequency (as determined by the FFT analysis) is reduced by 3 dB.Aperture Delay (t A )Offset ErrorThe major carry transition should occur for an analog value of ½ LSB below VIN+ = VIN−. Offset error is defined as the deviation of the actual transition from that point.The delay between the 50% point of the rising edge of the clock and the instant at which the analog input is sampled. Aperture Uncertainty (Jitter, t J )Out-of-Range Recovery TimeThe sample-to-sample variation in aperture delay.The time it takes for the ADC to reacquire the analog input after a transition from 10% above positive full scale to 10% above negative full scale, or from 10% below negative full scale to 10% below positive full scale.Clock Pulse Width and Duty CyclePulse width high is the minimum amount of time that the clock pulse should be left in the Logic 1 state to achieve rated performance. Pulse width low is the minimum time the clock pulse should be left in the low state. At a given clock rate, these specifications define an acceptable clock duty cycle. Output Propagation Delay (t PD )The delay between the clock rising edge and the time when all bits are within valid logic levels.Differential Nonlinearity (DNL, No Missing Codes)Power-Supply Rejection RatioAn ideal ADC exhibits code transitions that are exactly 1 LSB apart. DNL is the deviation from this ideal value. Guaranteed no missing codes to 14-bit resolution indicates that all 16,384 codes must be present over all operating ranges.The change in full scale from the value with the supply at the minimum limit to the value with the supply at the maximum limit.Signal-to-Noise and Distortion (SINAD)Effective Number of Bits (ENOB)The ratio of the rms input signal amplitude to the rms value of the sum of all other spectral components below the Nyquist frequency, including harmonics but excluding dc.The effective number of bits for a sine wave input at a given input frequency can be calculated directly from its measured SINAD using the following formula:()6.021.76−=SINAD ENOB Signal-to-Noise Ratio (SNR)The ratio of the rms input signal amplitude to the rms value of the sum of all other spectral components below the Nyquist frequency, excluding the first six harmonics and dc.Gain ErrorThe first code transition should occur at an analog value of½ LSB above negative full scale. The last transition should occur at an analog value of 1½ LSB below the positive full scale. Gain error is the deviation of the actual difference between first and last code transitions and the ideal difference between first and last code transitions.Spurious-Free Dynamic Range (SFDR)The ratio of the rms signal amplitude to the rms value of the peak spurious spectral component. The peak spurious component may be a harmonic. SFDR can be reported in dBc (that is, degrades as signal level is lowered) or dBFS (always related back to converter full scale).Integral Nonlinearity (INL)The deviation of each individual code from a line drawn from negative full scale through positive full scale. The point used as negative full scale occurs ½ LSB before the first code transition. Positive full scale is defined as a level 1½ LSB beyond the last code transition. The deviation is measured from the middle of each particular code to the true straight line.Temperature DriftThe temperature drift for offset error and gain error specifies the maximum change from the initial (25°C) value to the value at T MIN or T MAX .Total Harmonic Distortion (THD)The ratio of the rms input signal amplitude to the rms value of the sum of the first six harmonic components.Maximum Conversion RateThe clock rate at which parametric testing is performed.Two-Tone SFDRThe ratio of the rms value of either input tone to the rms value of the peak spurious component. The peak spurious component may or may not be an IMD product.AD9445Rev. 0 | Page 10 of 40PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONSD8+D8–D7+D6–D6+D7–DRGND DCO+DCO–D5+DRVDD DRGND D4+D4–D3+D3–D2+D2–D1+D1–D0+D0– (LSB)DNC DNCD5–F E N A B L EG N DG N DV D D 1V D D 1V D D 1V D D 1V D D 1V D D 1G N DR +R –R V D DR G N D 13+ (M S B )13–12+12–11+11–10+10–9+9–R V D DA V D D 2A V D D 2A V D D 2A V D D 2A V D D 2A V D D 2A V D D 1A V D D 1A V D D 1A V D D 2A V D D 1A V D D 2A V D D 1A G N DC L K +C L K –A G N DA V D D 1A V D D 1A V D D 1A G N DD R G N DD R V D DD N CD N CDNCOUTPUT MODEDFSSENSE AVDD1LVDS_BIASDCS MODE VREF AGNDREFT AVDD2AVDD2AVDD2AVDD2AVDD2AVDD2AVDD1AVDD1AVDD1AGNDVIN+VIN–AGND AVDD2REFB 05489-004Figure 4. 100-Lead TQFP/EP Pin Configuration in LVDS ModeTable 7. Pin Function Descriptions—100-Lead TQFP/EP in LVDS ModePin No. Mnemonic Description1 DCSMODEClock Duty Cycle Stabilizer (DCS) Control Pin. CMOS compatible. DCS = low (AGND) toenable DCS (recommended); DCS = high (AVDD1) to disable DCS.2, 49 to 52 DNC Do Not Connect. These pins should float.3 OUTPUTMODECMOS-Compatible Output Logic Mode Control Pin. OUTPUT MODE = 0 for CMOS mode;OUTPUT MODE = 1 (AVDD1) for LVDS outputs.4 DFSData Format Select Pin. CMOS control pin that determines the format of the output data.DFS = high (AVDD1) for twos complement; DFS = low (ground) for offset binary format.5 LVDS_BIAS Set Pin for LVDS Output Current. Place 3.7 kΩ resistor terminated to DRGND.6, 18 to 20, 32 to 34, 36, 38,43 to 45, 92 to 97AVDD1 3.3 V (±5%) Analog Supply.7 SENSEReference Mode Selection. Connect to AGND for internal 1 V reference; connect toAVDD1 for external reference.8 VREF1.0 V Reference I/O. Function dependent on SENSE and external programming resistors.Decouple to ground with 0.1 μF and 10 μF capacitors.9, 21, 24, 39, 42, 46, 91, 98, 99, Exposed Heat Sink AGND Analog Ground. The exposed heat sink on the bottom of the package must be connected to AGND.10 REFTDifferential Reference Output. Decoupled to ground with 0.1 μF capacitor and to REFB(Pin 14) with 0.1 μF and 10 μF capacitors.11 REFBDifferential Reference Output. Decoupled to ground with a 0.1 μF capacitor and to REFT(Pin 13) with 0.1 μF and 10 μF capacitors.12 to 17, 25 to 31, 35, 37 AVDD2 5.0 V Analog Supply (±5%).22 VIN+AnalogInput—True.23 VIN−AnalogInput—Complement.40 CLK+ClockInput—True.41 CLK−ClockInput—Complement.47, 63, 75, 87 DRGND Digital Output Ground.48, 64, 76, 88 DRVDD 3.3 V Digital Output Supply (3.0 V to 3.6 V).53 D0− (LSB) D0 Complement Output Bit (LVDS Levels).54D0+ D0 True Output Bit.55D1− D1 Complement Output Bit.56D1+ D1TrueOutputBit.57D2− D2 Complement Output Bit.58D2+ D2TrueOutputBit.59D3− D3 Complement Output Bit.60D3+ D3TrueOutputBit.61D4− D4 Complement Output Bit.62D4+ D4TrueOutputBit.65 D5− D5 Complement Output Bit.66 D5+D5TrueOutputBit.67 DCO− Data Clock Output—Complement.68 DCO+ Data Clock Output—True.69 D6− D6 Complement Output Bit.70 D6+D6TrueOutputBit.71 D7− D7 Complement Output Bit.72 D7+D7TrueOutputBit.73 D8− D8 Complement Output Bit.74 D8+D8TrueOutputBit.77 D9− D9 Complement Output Bit.78 D9+D9TrueOutputBit.79D10− D10 Complement Output Bit.80D10+ D10 True Output Bit.81D11− D11 Complement Output Bit.82D11+ D11 True Output Bit.Rev. 0 | Page 11 of 40Pin No. Mnemonic Description83 D12− D12 Complement Output Bit.84 D12+ D12 True Output Bit.85 D13− D13 Complement Output Bit.86 D13+ (MSB) D13 True Output Bit.89 OR− Out-of-Range Complement Output Bit.90 OR+ Out-of-Range True Output Bit.ENABLE100 RFRF ENABLE Control Pin. CMOS-compatible control pin to optimize the configuration ofthe AD9445 analog front end. Connecting RF ENABLE to AGND optimizes SFDRperformance for applications with analog input frequencies <210 MHz for 125 MSPSspeed grade and <230 MHz for the 105 MSPS speed grade. For applications with analoginputs >225 MHz for the 125 MSPS speed grade and >230 MHz for the 105 MSPS speedgrade, this pin should be connected to AVDD1 for optimum SFDR performance. Powerdissipation from AVDD2 increases by 150 mW to 200 mW.Rev. 0 | Page 12 of 40Rev. 0 | Page 13 of 40D2D1D0 (LSB)DNC DNC DNC DRGND DCO+DCO–DNC DRVDD DRGND DNC DNC DNC DNC DNC DNC DNC DNC DNC DNC DNC DNCDNC F E N A B L EG N DG N DV D D 1V D D 1V D D 1V D D 1V D D 1V D D 1G N DR13 (M S B )R V D DR G N D 1211109876543R V D DA V D D 2A V D D 2A V D D 2A V D D 2A V D D 2A V D D 2A V D D 1A V D D 1A V D D 1A V D D 2A V D D 1A V D D 2A V D D 1A G N DC L K +C L K –A G N DA V D D 1A V D D 1A V D D 1A G N DD R G N DD R V D DD N CD N CDNCOUTPUT MODEDFSSENSE AVDD1LVDS_BIASDCS MODE VREF AGNDREFT AVDD2AVDD2AVDD2AVDD2AVDD2AVDD2AVDD1AVDD1AVDD1AGNDVIN+VIN–AGNDAVDD2REFB 05489-005Figure 5. 100-Lead TQFP/EP Pin Configuration in CMOS ModeTable 8. Pin Function Descriptions—100-Lead TQFP/EP in CMOS ModePin No. Mnemonic Description1 DCSMODEClock Duty Cycle Stabilizer (DCS) Control Pin. CMOS compatible. DCS = low (AGND) to enableDCS (recommended); DCS = high (AVDD1) to disable DCS.2, 49 to 62, 65 to 66, 69 to 71 DNC Do Not Connect. These pins should float.3 OUTPUTMODE CMOS-Compatible Output Logic Mode Control Pin. OUTPUT MODE = 0 for CMOS mode; OUTPUT MODE = 1 (AVDD1) for LVDS outputs.4 DFSData Format Select Pin. CMOS control pin that determines the format of the output data.DFS = high (AVDD1) for twos complement; DFS = low (ground) for offset binary format.5 LVDS_BIAS Set Pin for LVDS Output Current. Place 3.7 kΩ resistor terminated to DRGND.6, 18 to 20, 32 to 34, 36, 38,43 to 45, 92 to 97AVDD1 3.3 V (±5%) Analog Supply.7 SENSEReference Mode Selection. Connect to AGND for internal 1 V reference; connect to AVDD1 forexternal reference.8 VREF1.0 V Reference I/O. Function dependent on SENSE and external programming resistors.Decouple to ground with 0.1 μF and 10 μF capacitors.9, 21, 24, 39, 42, 46, 91, 98, 99, Exposed Heat Sink AGND Analog Ground. The exposed heat sink on the bottom of the package must be connected to AGND.10 REFTDifferential Reference Output. Decoupled to ground with 0.1 μF capacitor and to REFB(Pin 14) with 0.1 μF and 10 μF capacitors.11 REFBDifferential Reference Output. Decoupled to ground with a 0.1 μF capacitor and to REFT(Pin 13) with 0.1 μF and 10 μF capacitors.12 to 17, 25 to 31, 35, 37 AVDD2 5.0 V Analog Supply (±5%).22 VIN+AnalogInput—True.23 VIN−AnalogInput—Complement.40 CLK+ClockInput—True.41 CLK−ClockInput—Complement.47, 63, 75, 87 DRGND Digital Output Ground.48, 64, 76, 88 DRVDD 3.3 V Digital Output Supply (3.0 V to 3.6 V).67 DCO− Data Clock Output—Complement.68 DCO+ Data Clock Output—True.72 D0 (LSB) D0 True Output Bit (CMOS levels).73 D1D1TrueOutputBit.74 D2D2TrueOutputBit.77 D3D3TrueOutputBit.78 D4D4TrueOutputBit.79 D5D5TrueOutputBit.80 D6D6TrueOutputBit.81 D7D7TrueOutputBit.82 D8D8TrueOutputBit.83 D9D9TrueOutputBit.84 D10 D10 True Output Bit.85 D11 D11 True Output Bit.86 D12 D12 True Output Bit.89 D13 (MSB) D13 True Output Bit.90 OR Out-of-Range True Output Bit.100 RFENABLERF ENABLE CMOS-compatible Control Pin. Optimizes the configuration of the analog front end.Connecting RF ENABLE to AGND optimizes SFDR performance for applications with analog inputfrequencies <210 MHz for 125 MSPS speed grade and <230 MHz for the 105 MSPS speed grade.For applications with analog inputs >225 MHz for the 125 MSPS speed grade and >230 MHzfor the 105 MSPS speed grade, this pin should be connected to AVDD1 for optimum SFDR.Power dissipation from AVDD2 increases by 150 mW to 200 mW.Rev. 0 | Page 14 of 40。

ADG409中文资料