李玉山信号完整性分析3~483页PPT

信号完整性分析PPT课件

Olica

4

SI简介

• 学习SI的目的 a.什么是典型的信号完整性问题? b.这些问题来自哪里? c.为什么有必要去理解SI问题? d.如何去分析和解决SI问题? e.如何去做SI测试?

30.11.2020

Olica

5

• SI的内容 SI简介

信号完整性它包含两方面的内容,一是 独立信号的质量,另一个是时序。我们 在电子设计的过程中不得不考虑两个问 题:信号有没有按时到达目的地?信号 达到目的地后它的质量如何?所以我们 做信号完整性分析的目的就是确认高频 数字传输的可靠性。

30.11.2020

Olica

10

SI简介

• 数据采样及时序例子

30.11.2020

Olica

11

SI简介

• 数据采样及时序例子 从这个图里面我们可以清楚地看到数据 必须准时到达逻辑门而且在接收端期间 开始锁存前必须确定它们的逻辑状态。 任何数据的延迟或者失真都会导致数据 传输的失败。失败有两种可能:一个是 因为接收端根本就无法识别数据;另一 个是接收端虽然识别了数据,但数据因 为失真而导致错误。

30.11.2020

Olica

3

SI简介

• SI的重要性

随着高频数字电路的不断发展,SI问题变得越来越引 人注目,数字电路的频率越高,出现SI问题的可能性 就越大,对设计工程师来说,他的挑战也就越大。很 多SI问题实际上都是自然界中的电磁现象,所以SI问 题跟EMI/EMC是息息相关的。

30.11.2020

30.11.2020

Olica

7

SI简介

• 理想逻辑电压波形

30.11.2020

Olica

8

SI简介

信号完整性分析 ppt课件

图0-0 五种PCB及系统级中的互连线条形式

信号完整性分析

• 点到点

• 近、远端簇

• 菊花链

• 周期性加载

图0-1 单个网络的各种互连拓扑情况

图0-2 高速IEEE-1394视频采集系统

物理互连本身的电阻、电容、电感和传输线效应 影响了系统性能。SI分析一书的作者Eric将后果归结

为信四类号SI完问整题:性分析

• 反射(reflection);

• 串扰(crosstalk);

• 电源轨道塌陷(rail collapse);

• 电磁干扰(EMI)。

此种划分系一家之言!该书属入门读物,后两种 涉及不深。

图0-3 四种信号完整性问题图解

图0-4 实际互连的阻抗不匹配示例,多分支更是如此

图0-5 振铃曲线,是由于阻抗不匹配造成的反射所致

• Ansoft: HFSS(高频结构仿真器)、SI2D

信号完整性分析

• 阻抗分析仪; • 矢量网络分析仪(VNA); • 时域反射仪(TDR)。

1. 阻抗分析仪:频域, 正弦电流源+电压表 (直接测); 2. 矢量网络分析仪(VNA):频域, 电压源+ 电压表(间接测); 3. 时域反射仪(TDR):时域, 信号源+示波器 (间接测)。

升边将增加到100ps。

图0-10 由于有损线造成的上升边退化

信号完整性分析

• 经验法则; • 解析近似; • 数值仿真 (有场和路两种途径); • 实际测量。

信号完整性分析

• SPICE(侧重IC的仿真程序) • Mentor公司:Hyperlynx • Candence公司:SigXP(SigXplorer) • Agilent公司:ADS

物理互连(Interconnect )包括四个层次:芯片内连线、芯片 封装、PCB及系统互连。它们决定高速信号、数据和电源质量。 三个高密度载体为:芯片系统SOC、板级系统SOB、封装系统 SOP。

信号完整性分析培训课件

当电路中的信号能够以正确的时序、持续的时间 和电压的幅度进行传送,并到达输出端时,说明 该电路具有良好的信号完整性;而当信号不能正 常响应,就出现了信号完整性问题。精文档信号完整性分析概念

一个数字系统能否正确工作,其关键在于信号定 时是否准确。

印制电路板层的参数、信号线的距离、驱动端和接 收端的电器特性,以及信号线的端接收方式等,都 对串扰有一定的影响。

精品文档

常见的信号完整性问题

3、反射(Reflection)

反射就是传输线上的回波。信号功率的一部分经传输线 传给负载,另一部分则向源端反射。在高速设计中,可 以把导线等效为传输线,而不再是集总参数电路中的导 线。如果阻抗匹配(源端阻抗、传输线阻抗和负载阻抗 等),则反射不会发生;反之,若负载阻抗与传输线阻 抗失配就会导致接收端反射。

高速电路设计的重点将与低速电路设计时截然不同, 不再仅仅是元件的合理放置与导线的正确连接,还 应该对信号的完整性(Signal Integrity,SI)问题给与 充分的考虑。

否则,即使原理图正确,系统可能也无法正常工作。

精品文档

信号完整性分析概述

信号完整性分析是重要的高速PCB板极 和系统极分析和设计的手段,在硬件电路设 计中发挥着越来越重要的作用。Protel 99SE 提供了具有较强功能的信号完整性分析器, 以及实用的SI专用工具,使Protel 99SE用户 在软件上就能模拟出整个电路板各个网络的 工作情况,同时还提供了多种补偿方案,帮 助用户进一步优化自己的电路设计。

在高频电路设计中,信号的传输延时是一个完全无法避 免的问题。为此引入了一个延迟容限的概念,即在保证 电路能够正常工作的前提下,所允许的信号最大时序变 化量。

信号完整性ppt课件

导电平面就像一个镜子,镜像电路与原电

路电流方向相反,并以平面对称。这样由

于互感影响,该涡流 会较大的减小原电路

的回路自感。

23

电感的物理基础

•

悬空平面越靠近回路,回路的电感就

越小,如下图:

24

传输线的物理基础

• 一、信号 信号总是指信号路径和返回路径之间相

邻两点的电压差,该原则适用于所有传输 线,无论是单端还是差分传输线。

信号完整性分析

通常设计过程是极富直觉和创造性的,要想尽快 完成合格设计,激发关于信号完整性的设计 直觉至关 重要。设计产品的设计师应了解信号完整性如何影响整 个产品的性能。该文档主要介绍 理解和解决信号完整 性问题所需的基本原理,直观定量地给出信号完整性问 题的工程背景知识。

主要参考: 信号完整性分析

• 四、传输线的瞬态阻抗及特征阻抗 传输线的瞬态阻抗并不是PCB上导线的电阻。如

果我们在一根导线上加一个电压,该电压信号从一 端传输到另一端的过程中所受到的阻抗即为瞬态阻 抗,当一定时间后,整根导线上的电源稳定后,导 线表现出的阻抗与瞬态阻抗肯定不一样,稳定后的 电阻才是我们平时所指的电阻。瞬态阻抗仅由传输 线 的两个固定参数决定,即传输线的横截面积和材 料特性共同决定,与传输线的长度无关。计算公式 为(只考虑电容效应的近似计算):

3

概论

c、返回路径平面上的间隙; d、接插件; e、分支线、T型线或桩线; f、网络末端。 B、网络间的串扰; C、轨道塌陷噪声;

当通过电源和地路径的电流发生变化时,在电 源路径和地路径间的阻抗上将产生一个压降。设计 电源和地分配的目标是使电源分配系统(PDS)的 阻抗 最小 D、来自整个系统的电磁干扰和辐射。

11

信号完整性分析 ppt课件

波形外观变差,出现了非正常形状的变形,称为信号完整性

被破坏。信号完整性问题是物理互连在高速情况下的直接结

果。

信号完整性强调信号在电路中产生正确响应的能力。

7

广义信号完整性(SI)泛指由各种信号、数据、电源 互连线引起的所有电压、电流不正常现象,包括: 噪声、干扰、时序抖动、数据传输等。

当频率大于1GHz时,介质损耗的增长与频率成正 比,而导线损耗与频率的平方根成正比(注意此处的自 变量为频率)。

FR4的介质损耗危害程度示例:当传输10inch后,上

升边将增加到100ps。

23

图0-10 由于有损线造成的上升边退化

24

信号完整性分析

• 经验法则; • 解析近似; • 数值仿真 (有场和路两种途径); • 实际测量。

狭义的信号完整性,是指信号电压(电流)波形的形 状及质量,主要包括反射和串扰。物理互连将其上面 的信号波形变差(退化),出现了非正常形变,称为信 号完整性被破坏。噪声可以转化为抖动,见DSI2.65式。

信号完整性退化是物理互连设计不当又工作在高 速环境下的直接后果。

8

0.2 互连的范畴

所有电子产品都可以解释为元器件及其互连。说到底,都可以 看作是靠不同层次下互连“编织”成的作品。

31

同层屏蔽线

Gnd

VDD

屏蔽层

Gnd

衬底层(Gnd) 图0-12 芯片内对抗线间串扰的屏蔽措施剖面说明

32

图0-13 为了减小电感,实际PCB去耦电容过孔的安装情况

33

VDD

板线

键合线 芯片内核

李玉山信号完整性分析34 83页PPT文档

正弦波,而在频域中只表示为一个点

用以下三项就可以充分描述正弦波: 频率; 幅度; 相位。 频率,通常用 f 来表示,是指每秒中包含的完整正弦波 周期数,单位是赫兹。角频率以每秒弧度来度量。弧度像 度数一样,描述了周期的一小部分,一个完整周期的弧度 为 2π。希腊字母ω通常用来表示角频率,以每秒弧度来度 量。正弦波的频率与角频率的关系如下:

仪器信噪比(SNR)高意味着测量质量高。矢量网络分析 仪 (VNA) 的 信 噪 比 在 其 整 个 频 率 范 围 内 应 是 恒 定 的 , 从 10MHz 到 50GHz 或更高频率,信噪比均为-130dB。

时域反射计(TDR),有效带宽可高达 10GHz,但信噪比从 低频处的+60dB 降至 10GHz 处的+5dB。

提示 毕竟,时域是客观存在的,我们不能脱离这个基础,除非频域中有求解答 案的捷径。

描述互连电路,常常包括电阻、电感和电容的组合。电 路中这些元件可用二阶线性微分方程描述,这类微分方程 的解就是正弦波。

这类电路中,实际产生的波形就是由上述微分方程的解 所对应的波形组合而成。

实际的电路模型含电阻、电感、电容、传输线。输入信 号是任意波形。电路不同,对输入加工处理的结果也不同。

其中: ω:角频率,弧度/秒 π:常量,为 3.14159... f: 正弦波频率,赫兹

(2.2)

例如,若正弦波的频率是 100MHz,那么它的角频率就等 于 2×3.14159×100MHz~6.3×108 弧度/秒。

幅度是中间值之上的波峰高度的最大值。水平方向之下 和水平方向之上的峰值相等。

相位较复杂些,它给出的是从时间轴起点波的起始位置。 相位以圆周、弧度或度为单位。

此时,在频域中绘制一个正弦波,仅需一个数据点。这 就是要在频域中研究问题的关键原因。

信号完整性分析实验报告_西电李玉山,路建民老师剖析

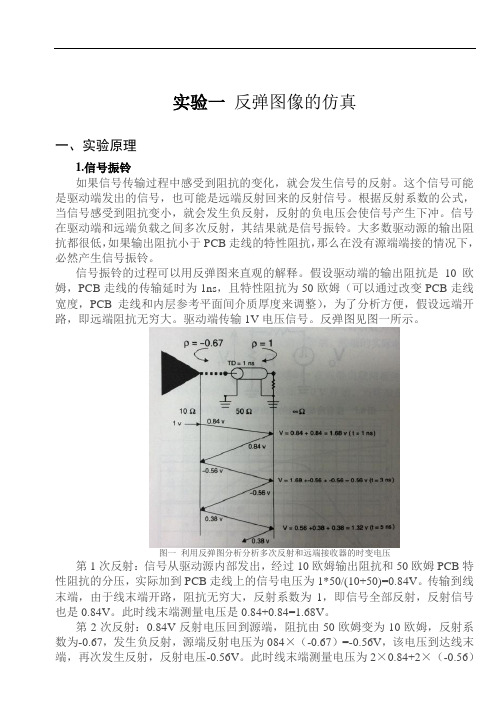

实验一反弹图像的仿真一、实验原理1.信号振铃如果信号传输过程中感受到阻抗的变化,就会发生信号的反射。

这个信号可能是驱动端发出的信号,也可能是远端反射回来的反射信号。

根据反射系数的公式,当信号感受到阻抗变小,就会发生负反射,反射的负电压会使信号产生下冲。

信号在驱动端和远端负载之间多次反射,其结果就是信号振铃。

大多数驱动源的输出阻抗都很低,如果输出阻抗小于PCB走线的特性阻抗,那么在没有源端端接的情况下,必然产生信号振铃。

信号振铃的过程可以用反弹图来直观的解释。

假设驱动端的输出阻抗是10欧姆,PCB走线的传输延时为1ns,且特性阻抗为50欧姆(可以通过改变PCB走线宽度,PCB走线和内层参考平面间介质厚度来调整),为了分析方便,假设远端开路,即远端阻抗无穷大。

驱动端传输1V电压信号。

反弹图见图一所示。

图一利用反弹图分析分析多次反射和远端接收器的时变电压第1次反射:信号从驱动源内部发出,经过10欧姆输出阻抗和50欧姆PCB特性阻抗的分压,实际加到PCB走线上的信号电压为1*50/(10+50)=0.84V。

传输到线末端,由于线末端开路,阻抗无穷大,反射系数为1,即信号全部反射,反射信号也是0.84V。

此时线末端测量电压是0.84+0.84=1.68V。

第2次反射:0.84V反射电压回到源端,阻抗由50欧姆变为10欧姆,反射系数为-0.67,发生负反射,源端反射电压为084×(-0.67)=-0.56V,该电压到达线末端,再次发生反射,反射电压-0.56V。

此时线末端测量电压为2×0.84+2×(-0.56)=0.56V。

第3次反射:从线末端反射回的-0.56V电压到达源端,再次发生负反射,反射电压为0.38V。

该电压到达线末端再次发生正反射,反射电压0.38V。

此时线末端测量电压为0.56+0.38+0.38=1.32V。

同样会发生第四次反射,第五次反射……如此循环,反射电压在源端和远端之间来回反弹,而引起线末端电压不稳定。

信号与电源完整性分拆与设计-李玉山第9讲

信号及电源完整性分析与设计[Chapter9]第九讲有损线带宽、抖动与数据完整性西安电子科技大学电路CAD研究所李玉山19.0高频损耗引起数据误码单纯传输,数据信号经过长线后,上升边退化。

图9.1 是上升边 RT=50ps 信号在 FR4 上经过 36in 、 50Ω线后的波 形。

除延迟外,上升边几乎拉长到2ns。

这种退化将引起 数据 0/1 符号间干扰 (Intersymbol Interference , ISI) 和误码 。

图9.1RT=50ps的信号入经50Ω、36in长线后为RT=1ns的信号出2当时钟频率高于1GHz、传输长度超过10in时,例 如高速链路(Serial Link)和千兆以太网,数据误码 主要是传输线损耗引起(机载、星载设备中同类问题很多)。

误码的主要原因是:数据信号幅度的塌陷退化直 接影响0/1的阈值判决;时序上的交叠抖动妨碍0/1的 判决时刻(其实,前一讲的时延ΔTD不仅有时延,也有上升边的退化含义,只是未单独讨论)。

3一般,频域中分析高频损耗比较简单。

例如:频域 中上升边退化变长等价于:信号高频分量的衰减比低 频分量衰减大得多。

下面分析传输线损耗的思路是:首先,在频域中理 解损耗机理;然后,再到时域中估计它对信号完整性 的影响 (本讲主要考察两种损耗:导线损、介质损及其对退化的影响分析)。

49.1有损线的退化作用若信号损耗与频率无关,即低频、高频时相同。

整个信 号的幅度会统一降低,波形形状则继续保真。

图9.2指出: 这种常量型衰减不会造成信号上升边退化和时序抖动。

图9.2当损耗与频率无关时,上升边为100ps的信号传播后波形形状不变5实际上,信号在有损传输线传播,高频分量的选 择性衰减使得信号带宽降低、上升边拉长。

上升边拉 长是退化的主要形式。

如果上升边退化与数据0/1位周期相比很小,位模 式(样式)将比较稳定,并与0/1数据流中前面位是0是 1的经历无关。

第9章-信号完整性分析

Page 11

清华大学出版社

2018/12/5

9.4.1 信号完整性规则设置

•在PCB编辑环境下进行信号完整性规则的设置 在PCB编辑环境下,执行菜单命令【设计】/【规则】, 弹出【PCB规则和约束编辑器】对话框,并从该对话框中打 开【Signal Intergity】选项,如图9-13所示。在该【 Signal Intergity】选项中用户可以选择设置信号完整分 析所需要的规则。

图9-13 【PCB规则和约束编辑器】对话框

Page 12 清华大学出版社 2018/12/5

Page 7 清华大学出版社 2018/12/5

为了更好地进行信号完整性分析,设计者在电路板系 统设计过程中,应当特别注意以下几点: 1. 将对噪声敏感的元器件进行物理隔离; 2. 尽量使线路阻抗匹配以及对信号进行反射控制; 3. 采用独立的电源及地电平层; 4. PCB布线避免走直角; 5. 同一组信号线尽量保持在走线上等长; 6. 在高速电路设计中,相邻的两条信号线的间距应符合 3W规则,即间距为信号线宽度W的三倍; 7. 选择容值足够大、阻抗低的旁路电容,对电源进行退 耦处理; 8. 将PCB板中的元器件进行合理布局。

9.3 添加信号完整性模型

Protel DXP提供了两种添加信号完整性模型的方法: 通过【Model Assignments】(模型配置)对话框进行 添加,该方法是向设计中添加信号完整性模型最简单 的方法; 手动方式进行添加,该方法利用【元件属性】对话框 来完成信号完整性模型的添加。 【实例9-1】 利用【Model Assignments】(模型配置)对 话框添加信号完整性模型。

传输时间过长 传输线距离过长, 替换或重新布线, 使用阻抗匹配的 没有开关动作 检查串行端接 驱动源,变更布 线策略

课件:李玉山1(研究生)修改

改良巴氏染色 Shorr染色 Diff-Quik法

观察方法

26

精子活力分析可接受误 差的应用

• 例2:

重复计数200个精子评估精子的活力结果如下: – PR精子分别占37%和28% – NP精子分别占3%和6% – IM精子分别占60%和66% – 最常见活力级别是IM型,均值为63%,差值是6% – 在均值为63%时,随机误差上限是10%,结果是可接

受的

精子活力分析可接受误

• 例1:

差的应用

重复计数200个精子评估精子的活力结果如下:

– PR型精子分别是30%和50%

– NP型精子是5%和15%

– IM型精子是65%和35%

– 最常见活力级别是IM型,均值为50%,差值是30%

– 在均值为50%的情况下,随机误差的上限是10%, 得出的差异超出10%,应需重新制作两份标本进行 评估

• 精液分析:

– 标准程序:精液采集和初步肉眼观察、精子浓度和精子总

数的测定、精子活力分级、精子形态学评估、非精子成分

– 可供选择的试验:多重精子缺陷指数、WBC免疫细胞化

学染色、精子宫颈粘液相互作用、精浆生化、CASA

– 研究实验:活性氧、顶体反应、精子卵细胞相互作用、精

子透明带结合、去透明带仓鼠卵穿透试验、精子染色质检测

可接受范围内,如果不可接受,重新读片) • 取平均值,报告结果

精液涂片的制备

• 充分混匀精液样本。 • 快速取样,避免精子从混悬的精液样本

中沉降。 • 重复取样前,再次混匀精液样本。 • 根据精液样本具体不同情况,采用不同

的涂片方式。

(a) 对于未稀释的精液,采用拉薄技术,将一滴精液(S) 沿成角的载玻片背侧边缘展开,向前拖拉制成涂片。

信号完整性分析培训课件

当电路中的信号能够以正确的时序、持续的时间 和电压的幅度进行传送,并到达输出端时,说明 该电路具有良好的信号完整性;而当信号不能正 常响应,就出现了信号完整性问题。

精品文档

信号完整性分析概念

一个数字系统能否正确工作,其关键在于信号定 时是否准确。

精品文档

信号完整性分析规则设置

1、激励信号规则(Signal Stimulus)规则

设置激励信号的种类,包括3种选项:“Constant Level”表示激励信号 为某个常数电平;“Single Pulse”表示激励信号为单脉冲信号; “Periodic Pulse”表示激励信号为周期性脉冲信号

设置激励信号高电平 脉宽的起始时间

信号定时与信号在传输线上的传输延迟,以及信 号波形的损坏程度都有密切关系。

差的信号完整性不是由某一单一因素导致的,而 是由板极设计中的多种因素共同引起的。

仿真证实,集成电路的切换速度过高,端接元件 的布设不正确,电路的互连不合理等,都会引发 信号完整性问题。

精品文档

பைடு நூலகம்

常见的信号完整性问题

Protel 99SE提供了一个高级的信号完整性分析器。 它能精确地模拟分析已步好线的PCB,可以测试 网络阻抗、下冲、过冲和信号斜率。

精品文档

信号完整性分析器

精品文档

信号完整性分析规则设置

5、信号下冲的上升沿(Undershoot-Rising Edge)规则:信号 下冲的上升沿与信号下冲的下降沿是相对应的。它定义了信 号上升边沿允许的最大下冲值,也即信号上升沿上低于信号 上位置的阻尼振荡,系统默认单位是伏特。

精品文档

信号完整性分析规则设置