AKD4368-B中文资料

CD14538B中文手册资料讲解

C D14538B中文手册CMOS双精度单稳态多谐振荡器功能:➢可再触发性能。

➢依靠Rx和Cx延迟作用触发和复位。

➢前边沿触发和后边沿触发可选。

➢Q和Q/缓冲输出可有效利用。

➢独立的复位功能。

➢可替换CD4538型号。

图1 功能框图CD14538B双精度单稳态多谐振荡器可以为任何固定电压定时应用提供稳定的可再触发的单次的操作。

一个外部电阻和一个外部电容控制电路的定时和精度。

调节Rx和Cx可以从Q和Q/终端输出一个宽范围的脉宽。

触发信号和复位信号的延时是通过调整Rx和Cx的参数值来实现的。

通过线性CMOS技术来完成输出脉宽的精度控制。

前边沿触发输入(+TR)和后边沿触发输入(-TR)是为任何一个输入脉冲边沿提供触发。

如果+TR引脚没有被使用,就应该将它跟Vss引脚连接。

如果-TR引脚没有被使用,就应该将它跟Vdd引脚连接。

复位信号(低电平)会使输出脉冲立即停止,当工作电源提供时,恢复输出脉冲。

RESET引脚正常应该连接到Vdd引脚。

如果,CD14538B的一个完整部分没有被使用,它的输入端必须连接到Vdd或Vss。

(见表1)正常操作电路重复触发(延长一个周期的输出脉冲)关于每个新触发脉冲。

在不可重复触发的模式下操作时,当前边沿触发接口(+TR)被使用时,Q/引脚和-TR引脚相连,当后边沿触发接口(-TR)被使用,Q引脚和+TR引脚相连。

这个多谐振荡器的时钟周期计算公式:T=Rx*Cx。

外部电阻的最小值Rx是4K欧姆,外部电容的最小值和最大值分别是0pF 和100uF。

CD14538B型号是有16脚密封双列直插式陶瓷封装(D和F后缀)、16脚双列直插式塑料封装(E后缀)和贴片形式(H后缀)提供。

CD14538B与MC14538相似,并且可以互换,与CD4098B*和CD4538B引脚兼容,它可以代替在新设计中不被推荐的CD4538B。

*T=0.5RxCx;Cx>=1000pF#T=RxCx;Cxmin=5000pF➢宽范围输出脉冲宽度。

6lb184中文资料

6lb184中文资料6lb184中文资料【用途】RS485/422电平转换电路【性能参数】双列贴片8脚封装。

TTL-RS485/422电平转换。

工作电压4.75-5.25V,典型5V。

【互换兼容】SN65LBC184D【6LB184的原厂(中文)资料数据手册脚功能参数封装】摘要:电子镇流器(Electrical ballast)是镇流器的一种,是指采用电子技术驱动电光源,使之产生所需照明的电子设备。

电子镇流器自身功耗低,有更佳的照明效果,消除了闪频现象,发光更稳定,而且可以调光。

文章采用AVR单片机作为控制芯片,通过电子镇流器进行调光和相关功能的控制,最大限度地发挥智能型镇流器的特点。

实际应用表明,文中的方法有效。

0 引言电子镇流器是新型节能产品,不仅能带动一些照明灯具,还可以和一些紫外灯结合在一起,对于空气净化和水源净化都有着非常大的作用。

当前,全世界都在大力提倡环境保护,电子镇流器间接地为环保提供了原动力。

AVR单片机是一款性价比较高的单片机,用这种单片机来对电子镇流器进行调光和时间采样非常合适,首先是AVR单片机本身较稳定,抗干扰能力比较强,其次是其本身的Harvard结构使得运行速度比较快,数据回读时间较快,可以实现实时在线控制。

1 AVR单片机介绍1.1 AVR单片机的特点与以往的8位单片机相比,AVR单片机采用Harvard结构,也就是程序总线和数据总线分开,并采用两级流水线,具备1MIPS/MHz的高速运行处理能力。

片内集成多种频率的RC振荡器、上电自动复位、看门狗、启动延时等功能模块,外围电路简单,系统更加稳定可靠。

大部分AVR片上资源丰富:带E2PROM、PWM、RTC、SPI、UART、TWI、ISP、AD、Analog Comparator、WDT等单元模块。

1.2 AVR单片机的PWM功能AVR单片机的定时器功能强大,以Atmega48为例,它有两个8位定时器和一个16位定时器,都具有硬件PWM功能。

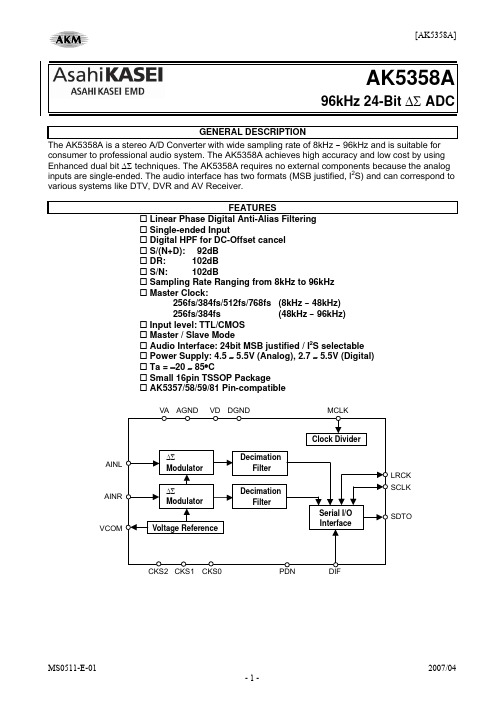

AK5358AET中文资料

FEATURES

Linear Phase Digital Anti-Alias Filtering

Single-ended Input

Digital HPF for DC-Offset cancel

S/(N+D): 92dB

DR:

102dB

S/N:

102dB

Sampling Rate Ranging from 8kHz to 96kHz

- Digital Power Supply Pin, 2.7 ∼ 5.5V

- Digital Ground Pin

Audio Serial Data Output Pin O

“L” Output at Power-down mode.

Output Channel Clock Pin I/O

“L” Output in Master Mode at Power-down mode.

Classification Analog

AINL AINR

Pin Name

Setting This pin should be open. This pin should be open.

MS0511-E-01 -3-

2007/04

元器件交易网

[AK5358A]

ABSOLUTE MAXIMUM RATINGS

-

Analog Input Voltage (AINL, AINR, CKS1 pins)

VINA

−0.3

Digital Input Voltage

(Note 3)

VIND

−0.3

Ambient Temperature (powered applied)

DF8B机车总体

3680kW

气缸直径:

280mm

活塞行程:

285mm

标定转速:

1000r/min

最低空载稳定转速: 400r/min

起动方式:

电机起动

燃油消耗率: 208(1+3%)g/(kW·h)机

油消耗率:

2.04g/(kW·h)

Page 17

四 机车主要部件概述—主发电机

主要参数 ⑴ 型号 ⑵ 额定容量 ⑶ 额定电压 ⑷ 额定电流 ⑸ 最大电流 ⑹ 额定转速 ⑺ 励磁方式 ⑻ 冷却方式 ⑼ 额定效率 ⑽ 额定频率 ⑾ 工作制

三 DF8B机车总体方案

辅助室

控制柜下方设有灭火器

复轨器

Page 16

通往车顶扶梯 手制动装置

风源净化装置

四 机车主要部件概述—柴油发电机组

柴油发电机组

型号:

16V280ZJA

型式四冲程、直接喷射燃烧室、废气 涡轮增压、增压空气中间冷却

缸数及排列型式: 16缸、V型排列、 50°夹角

运用功率:

JF204D

3700kVA

540 / 770V

3955 / 2775A

5610A

1000r/min 他励

强迫通风(风量290m3 /min) ≥96.5%

116.7 Hz 连续

四 机车主要部件概述—牵引电动机

主要参数 ⑴ 型号 ⑵ 额定功率 ⑶ 额定电压 ⑷ 额定电流 ⑸ 最大电流 ⑹ 额定转速 ⑺ 最大转速 ⑻ 励磁方式 ⑼ 工作制 ⑽ 磁场削弱

5 工作环境 6 相关成本

干式轮缘润滑装置 结构简单,零部件少

简单直接

安装调试简便

直接可视润滑剂状态,调 试简单 无污染 前期投入低,碳棒价格高

AKD4343-B中文资料

GENERAL DESCRIPTIONThe AKD4343-B is an evaluation board for the AK4343, Stereo DAC with built-in HP/RCV/SPK amplifier. The AKD4343-B has the interface with AKM’s ADC evaluation boards. Therefore, it’s easy to evaluate the AK4343. The AKD4343-B also has the digital audio interface and can achieve the interface with digital audio systems via opt-connector.Ordering guideAKD4343-B --- Evaluation board for AK4343(Cable for connecting with printer port of IBM-AT compatible PC and controlsoftware are packed with this. This control software does not operate on Windows NT.)FUNCTION• 10pin Header for Direct Interface with AKM’s ADC evaluation boards • DIR with optical input• 10pin Header for serial control mode • Mini-jack for external Stereo Speaker• On-board Stereo Class-D Speaker Amplifier (AK7830)Opt InFigure 1. AKD4343-B Block Diagram* Circuit diagram and PCB layout are attached at the end of this manualAK4343 Evaluation board Rev.0AKD4343-BEvaluation Board ManualOperation sequence1) Set up the power supply lines. [VCC] (red) = 5.0V (or 3.3V)[AGND] (black) = 0V [DGND] (black) = 0VEach supply line should be distributed from the power supply unit.When the power is supplied to the AK4343 via the regulator, JP21 should be set to “REG” side and VCC should be 5.0V.<default> (When the power is supplied from VCC jack to the AK4343 directly, JP21 should be set to “VCC” side and VCC should be 3.3V.)2) Set up the evaluation mode, jumper pins. (See the followings.)3) Power on.The AK4343 and AK4114 should be reset once bringing SW1 “L” upon power-up.And the AK7830 should be reset once bringing SW2(SPK_PDN) “L” upon power-up.Evaluation mode(1) Slave mode(1-1) Evaluation of Playback block (HP, SPK, LOUT) using DIR of AK4114 <Default> (1-2) All interface signals including master clock are fed externally.The AK4114’s audio interface format is fixed to LJ compatible.(1-1) Evaluation of Playback block using DIR of AK4114PORT1 (DIR) is used. Nothing should be connected to PORT3 (DSP).JP6BICK2JP7 LRCK2JP11SDTIADCDIRJP8LRCKJP9MCLKJP10BICKThe AK4114 operates at fs of 32kHz or more. If the fs is slower than 32kHz, any other evaluation mode without using DIR should be used.(1-2) All interface signals including master clock are fed externally. PORT3 (DSP) is used. Nothing should be connected to PORT1 (DIR).JP6BICK2JP7 LRCK2JP11SDTIADCDIRJP8LRCKJP9MCLKJP10BICK(2) Master mode(2-1) Master clock is fed externally(2-1) Master clock is fed externallyPORT3 (DSP) is used and MCLK is fed from PORT3. Nothing should be connected to PORT1 (DIR). It is possible to evaluate at various sampling frequencies using built-in AK4343’s PLL.JP6BICK2JP7 LRCK2JP11SDTIADCDIRJP8LRCKJP9MCLKJP10BICKOther jumper pins set up1. JP1 (GND) : Connection between AGND and DGND.OPEN : Both grounds are separated on board.SHORT : Both grounds are connected on board. <Default>2. JP4,JP5,JP12 : Select speaker type.Speaker Type JP4 JP5 JP12<Default>Dynamic, 400mW Short Short DynamicDynamic,1.2W ShortShortPiezoPiezoPizeo OpenOpen3. JP16,JP17: Select Pin #5,28Pin #5 Pin #28 JP16 JP17 AIN3 bitVCOC MIN VCOC Open 0 <Default>RIN3 LIN3 RIN3 Short 14. JP18,JP19,JP20 : Select the input from MIN/LIN3/RIN3.Pin #26 Pin #27 JP18 JP19 JP20 RCV bitROUT LOUT Open Open Short 0 <Default>RCN RCP Short Short Open 15. JP22 : Select the Power Booster of AK7830.VCC : Power Booster ONGND: Power Booster Off<Default>The function of the toggle SW[SW1] (PDN): Power down of AK4343 and AK4114. Keep “H” during normal operation.[SW2] (SPK_PDN): Power down of AK7830. Keep “H” during normal operation.Indication for LED[LED1] (ERF): Monitor INT0 pin of the AK4114. LED turns on when some error has occurred to AK4114.Serial ControlThe AK4343 can be controlled via the printer port (parallel port) of IBM-AT compatible PC. Connect PORT4 (CTRL) with PC by 10 wire flat cable packed with the AKD4343. When I 2C bus mode is used, PORT4 should be directly connected to the I 2C bus on the system. JP13,14 and 15 should be set to I 2C bus mode to control the AK7830.CSNSCL/CCLK SDA/CDTI 10pin Header10pinConnector10 wire flat cable PCAKD4343-BFigure 2. Connect of 10 wire flat cable(1) 3-wire Serial Control Mode <Default>The jumper pins should be set to the following.(2) I 2C-bus Control ModeThe jumper pins should be set to the following.(2-1) In case of using CAD0=0 (device address bits).(2-2) In case of using CAD0=1 (device address bits).JP13I2C_SELJP15SDAI2C 3-wireJP14CAD0JP13I2C_SELJP15SDAI2C3-wireJP14CAD0JP13I2C_SELJP15SDAI2C 3-wireJP14CAD0Analog Input/Output Circuits(1) Input Circuits1. MIN/LIN3/RIN3 Input CircuitMIN/LIN3RIN3JP17Figure 3. MIN/LIN3/RIN3 Input Circuit2. LINE1 Input CircuitLIN1RIN1C3J5Figure 4. LIN1/RIN1 Input Circuit3. LINE2 Input CircuitC18LIN2RIN2Figure 5. LIN2/RIN2 Input Circuit(2) Output Circuits1. Headphone-amp Output CircuitR14 C13J1 HPHPRHPLFigure 6. Headphone-amp Output Circuit2. STEREO LINE Output CircuitROUT LOUTJP19 JP18RCNFigure 7. STEREO LINE Output Circuit3. SPEAKER Output CircuitSPPR19R2010SPNFigure 8. SPEAKER Output Circuit4. External SPEAKER-Amp(AK7830) Output CircuitFigure 9. External SPEAKER-Amp(AK7830) Output Circuit∗ AKM assumes no responsibility for the trouble when using the above circuit examples.Control Software ManualSet-up of evaluation board and control software1. Set up the AKD4343-B according to previous term.2. Connect IBM-AT compatible PC with AKD4343-B by 10-line type flat cable (packed with AKD4343-B). Take careof the direction of 10pin header. (Please install the driver in the CD-ROM when this control software is used on Windows 2000/XP. Please refer “Installation Manual of Control Software Driver by AKM device control software”.In case of Windows95/98/ME, this installation is not needed. This control software does not operate on Windows NT.)3. Insert the CD-ROM labeled “AKD4343-B Evaluation Kit” into the CD-ROM drive.4. Access the CD-ROM drive and double-click the icon of “AKD4343.exe” to set up the control program. Whencontrol the AK7830 with the serial mode, double-click the icon of “akd7830.exe” to set up the control program.5. Then please evaluate according to the follows.Operation flowKeep the following flow.1. Set up the control program according to explanation above.2. Click “Port Reset” button.3. Click “Write default” buttonExplanation of each buttons1. [Port Reset] : Set up the USB interface board (AKDUSBIF-A) when using the board.2. [Write default] : Initialize the register of the AK4343.3. [All Write] : Write all registers that is currently displayed.4. [Function1] : Dialog to write data by keyboard operation.5. [Function2] : Dialog to write data by keyboard operation.6. [Function3] : The sequence of register setting can be set and executed.7. [Function4] : The sequence that is created on [Function3] can be assigned to buttons and executed.8. [Function5]: The register setting that is created by [SAVE] function on main window can be assigned tobuttons and executed.9. [SAVE] : Save the current register setting.10. [OPEN] : Write the saved values to all register.11. [Write] : Dialog to write data by mouse operation.Indication of dataInput data is indicated on the register map. Red letter indicates “H” or “1” and blue one indicates “L” or “0”. Blank is the part that is not defined in the datasheet.Explanation of each dialog1. [Write Dialog]: Dialog to write data by mouse operationThere are dialogs corresponding to each register.Click the [Write] button corresponding to each register to set up the dialog. If you check the check box, data becomes “H” or “1”. If not, “L” or “0”.If you want to write the input data to the AK4343, click [OK] button. If not, click [Cancel] button.2. [Function1 Dialog] : Dialog to write data by keyboard operationAddress Box: Input registers address in 2 figures of hexadecimal.Data Box: Input registers data in 2 figures of hexadecimal.If you want to write the input data to the AK4343, click [OK] button. If not, click [Cancel] button.3. [Function2 Dialog]: Dialog to evaluate DATTThere are dialogs corresponding to register of 09h, 0Ah, 0Ch, and 0Dh.Address Box: Input registers address in 2 figures of hexadecimal.Start Data Box: Input starts data in 2 figures of hexadecimal.End Data Box: Input end data in 2 figures of hexadecimal.Interval Box: Data is written to the AK4343 by this interval.Step Box: Data changes by this step.Mode Select Box:If you check this check box, data reaches end data, and returns to start data.[Example] Start Data = 00, End Data = 09Data flow: 00 01 02 03 04 05 06 07 08 09 09 08 07 06 05 04 03 02 01 00If you do not check this check box, data reaches end data, but does not return to start data.[Example] Start Data = 00, End Data = 09Data flow: 00 01 02 03 04 05 06 07 08 09If you want to write the input data to the AK4343, click [OK] button. If not, click [Cancel] button.4. [SAVE] and [OPEN]4-1. [SAVE]All of current register setting values displayed on the main window are saved to the file. The extension of file name is “akr”.<Operation flow>(1) Click [SAVE] Button.(2) Set the file name and click [SAVE] Button. The extension of file name is “akr”.4-2. [OPEN]The register setting values saved by [SAVE] are written to the AK4343. The file type is the same as [SAVE].<Operation flow>(1) Click [OPEN] Button.(2) Select the file (*.akr) and Click [OPEN] Button.The sequence of register setting can be set and executed.(1) Click [F3] Button.(2) Set the control sequence.Set the address, Data and Interval time. Set “-1” to the address of the step where the sequence should be paused. (3) Click [START] button. Then this sequence is executed.The sequence is paused at the step of Interval="-1". Click [START] button, the sequence restarts from the paused step. This sequence can be saved and opened by [SA VE] and [OPEN] button on the Function3 window. The extension of file name is “aks”.Figure 10. Window of [F3]The sequence file (*.aks) saved by [Function3] can be listed up to 10 files, assigned to buttons and then executed. When [F4] button is clicked, the window as shown in Figure 10 opens.Figure 11. [F4] window6-1. [OPEN] buttons on left side and [START] buttons(1) Click [OPEN] button and select the sequence file (*.aks) saved by [Function3].The sequence file name is displayed as shown in Figure 11. ( In case that the selected sequence file name is“DAC_Stereo_ON.aks”)Figure 12. [F4] window(2)(2) Click [START] button, then the sequence is executed.6-2. [SAVE] and [OPEN] buttons on right side[SAVE] : The name assign of sequence file displayed on [Function4] window can be saved to the file. The file name is “*.ak4”.[OPEN] : The name assign of sequence file(*.ak4) saved by [SAVE] is loaded.6-3. Note(1) This function doesn't support the pause function of sequence function.(2) All files used by [SAVE] and [OPEN] function on right side need to be in the same folder.(3) When the sequence is changed in [Function3], the sequence file (*.aks) should be loaded again in order to reflect the change.7. [Function5 Dialog]The register setting file(*.akr) saved by [SAVE] function on main window can be listed up to 10 files, assigned to buttons and then executed.When [F5] button is clicked, the window as shown in Figure 12 opens.Figure 13. [F5] window7-1. [OPEN] buttons on left side and [WRITE] button(1) Click [OPEN] button and select the register setting file (*.akr).The register setting file name is displayed as shown in Figure 13. (In case that the selected file name is“DAC_Output.akr”)(2) Click [WRITE] button, then the register setting is executed.Figure 14. [F5] windows(2)7-2. [SAVE] and [OPEN] buttons on right side[SAVE] : The name assign of register setting file displayed on [Function5] window can be saved to the file. The file name is “*.ak5”.[OPEN] : The name assign of register setting file(*.ak5) saved by [SAVE] is loaded.7-3. Note(1) All files used by [SAVE] and [OPEN] function on right side need to be in the same folder.(2) When the register setting is changed by [SAVE] Button on the main window, the register setting file (*.akr) should beloaded again in order to reflect the change.MEASUREMENT RESULTS1. EXT mode (slave mode)[Measurement condition]● Measurement unit: Audio Precision, System two Cascade● EXT Slave Mode● BICK: 64fs● Bit: 16bit● Measurement Frequency: 20Hz ∼ 20kH● Power Supply: AVDD=DVDD=HVDD=3.3V● Temperature: Room● Input Frequency: 1kHz● Sampling Frequency: 44.1kHz[Measurement Results]DAC (LOUT/ROUT) characteristics (R L=10kΩ, DAC Æ LOUT/ROUT)L[dB]R[dB] S/(N+D) 20kHzLPF (−3dB) 89.7 89.7S/N 20kHzLPF + A-weighted 94.6 94.62. PLOT DATA2-1 DAC (DAC Æ LOUT/ROUT)Figure 15. THD+N vs. Input LevelFigure 16.THD+N vs. Input FrequencyAKMAK4643 DAC -> LINEOUT THD+N vs Input Levelfs=44.1kHz , fin=1kHzd B r AdBFSAKMAK4643 DAC -> LINEOUT THD+N vs Input Frequencyfs=44.1kHz , fin=1kHzd B r AHzFigure 17. LinearityFigure 18. Frequency ResponseAKMAK4643 DAC -> LINEOUT Linearityfs=44.1kHz , fin=1kHzd B r AdBFSAKMAK4643 DAC -> LINEOUT Freqency Responsefs=44.1kHz , fin=1kHzd B r AHzFigure 19. FFT Plot (Input level= 0dBFs)Figure 20. FFT Plot (Input level = -60dBFs)AKMAK4643 DAC --> Lineout FFT fs=44.1kHz , fin=1kHz , 0dB InputHzd B r AAKMAK4643 DAC --> Lineout FFT fs=44.1kHz , fin=1kHz , -60dB InputHzd B r AFigure 21. FFT Plot (No signal)Figure 22. Crosstalk PlotAKMAK4643 DAC --> Lineout FFT fs=44.1kHz , fin=1kHz , No SignalHzd B r AAKMAK4643 DAC -> LINEOUT Crosstalkfs=44.1kHz , fin=1kHz , 0dB Inputad.at2cd B 2020k501002005001k2k5k10kHzRevision HistoryDate (YY/MM/DD) ManualRevisionBoardRevisionReason Contents06/04/12 KM083800 0 FirstEditionIMPORTANT NOTICE• These products and their specifications are subject to change without notice. Before considering any use or application, consult the Asahi Kasei Microsystems Co., Ltd. (AKM) sales office or authorized distributor concerning their current status.• AKM assumes no liability for infringement of any patent, intellectual property, or other right in the application or use of any information contained herein.• Any export of these products, or devices or systems containing them, may require an export license or other official approval under the law and regulations of the country of export pertaining to customs and tariffs, currency exchange, or strategic materials.• AKM products are neither intended nor authorized for use as critical components in any safety, life support, or other hazard related device or system, and AKM assumes no responsibility relating to any such use, except with the express written consent of the Representative Director of AKM. As used here:(a) A hazard related device or system is one designed or intended for life support or maintenance ofsafety or for applications in medicine, aerospace, nuclear energy, or other fields, in which its failure to function or perform may reasonably be expected to result in loss of life or in significant injury or damage to person or property.(b) A critical component is one whose failure to function or perform may reasonably be expected toresult, whether directly or indirectly, in the loss of the safety or effectiveness of the device or system containing it, and which must therefore meet very high standards of performance and reliability.• It is the responsibility of the buyer or distributor of an AKM product who distributes, disposes of, or otherwise places the product with a third party to notify that party in advance of the above content and conditions, and the buyer or distributor agrees to assume any and all responsibility and liability for and hold AKM harmless from any and all claims arising from the use of said product in the absence of such notification.。

1SMA5918BT3G中文资料

1SMA5913BT3 Series1.5 Watt PlasticSurface MountZener Voltage RegulatorsThis complete new line of 1.5 Watt Zener Diodes offers the following advantages.Features•Standard Zener Breakdown V oltage Range − 3.3 V to 68 V •ESD Rating of Class 3 (>16 kV) per Human Body Model •Flat Handling Surface for Accurate Placement •Package Design for Top Slide or Bottom Circuit Board Mounting •Low Profile Package•Ideal Replacement for MELF Packages•Pb−Free Packages are AvailableMechanical Characteristics:CASE:V oid-free, transfer-molded plasticFINISH:All external surfaces are corrosion resistant with readily solderable leadsMAXIMUM CASE TEMPERATURE FOR SOLDERING PURPOSES: 260°C for 10 secondsPOLARITY:Cathode indicated by molded polarity notch or cathode bandFLAMMABILITY RATING:UL 94 V−0 @ 0.125 inMAXIMUM RATINGSRating Symbol Value UnitDC Power Dissipation @ T L = 75°C, Measured Zero Lead Length (Note 1) Derate above 75°CThermal Resistance, Junction−to−LeadP DR q JL1.52050WmW/°C°C/WDC Power Dissipation @ T A = 25°C (Note 2) Derate above 25°CThermal Resistance, Junction−to−AmbientP DR q JA0.54.0250WmW/°C°C/WOperating and Storage Temperature Range T J, T stg−65 to+150°CStresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.1. 1 in square copper pad, FR−4 board.2.FR−4 Board, using ON Semiconductor minimum recommended footprint.Device Package Shipping†ORDERING INFORMATION1SMA59xxBT3SMA5000/Tape & Reel1SMA59xxBT3G SMA(Pb−Free)5000/Tape & Reel†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our T ape and Reel Packaging Specifications Brochure, BRD8011/D.See specific marking information in the device marking column of the Electrical Characteristics table on page 2 of this data sheet.DEVICE MARKING INFORMATIONELECTRICAL CHARACTERISTICS (T A = 25°C unlessotherwise noted, V F = 1.5 V Max. @ I F = 200 mA for all types)Symbol ParameterV Z Reverse Zener Voltage @ I ZT I ZT Reverse CurrentZ ZT Maximum Zener Impedance @ I ZT I ZK Reverse CurrentZ ZK Maximum Zener Impedance @ I ZK I R Reverse Leakage Current @ V R V R Reverse Voltage I F Forward Current V F Forward Voltage @ I F I ZMMaximum DC Zener CurrentELECTRICAL CHARACTERISTICS (T A = 25°C unless otherwise noted, V F = 1.5 V Max. @ I F = 200 mA for all types)Device* (Note 3)Device Marking Zener Voltage (Note 4)Zener Impedance Leakage CurrentI ZM V Z (Volts)@ I ZT Z ZT @ I ZTZ ZK @ I ZK I R @ V R Min Nom Max mA W W mA m A Volts mA(dc)1SMA5913BT3, G 813B 3.13 3.3 3.47113.610500 1.050 1.04551SMA5914BT3, G 814B 3.42 3.6 3.78104.29.0500 1.035.5 1.04171SMA5915BT3, G 815B 3.70 3.9 4.1096.17.5500 1.012.5 1.03851SMA5916BT3, G 816B 4.08 4.3 4.5287.2 6.0500 1.0 2.5 1.03491SMA5917BT3, G 817B 4.46 4.7 4.9479.8 5.0500 1.0 2.5 1.53191SMA5918BT3, G 818B 4.84 5.1 5.3673.5 4.0350 1.0 2.5 2.02941SMA5919BT3, G 819B 5.32 5.6 5.8866.9 2.0250 1.0 2.5 3.02681SMA5920BT3, G 820B 5.89 6.2 6.5160.5 2.0200 1.0 2.5 4.02421SMA5921BT3, G 821B 6.46 6.87.1455.1 2.5200 1.0 2.5 5.22211SMA5922BT3, G 822B 7.127.57.8850 3.04000.5 2.5 6.02001SMA5923BT3, G 823B 7.798.28.6145.7 3.54000.5 2.5 6.51831SMA5924BT3, G 824B 8.649.19.5641.2 4.05000.5 2.57.01651SMA5925BT3, G 825B 9.51010.537.5 4.55000.25 2.58.01501SMA5926BT3, G 826B 10.451111.5534.1 5.55500.250.58.41361SMA5927BT3, G 827B 11.41212.631.2 6.55500.250.59.11251SMA5928BT3, G 828B 12.351313.6528.87.05500.250.59.91151SMA5929BT3, G 829B 14.251515.75259.06000.250.511.41001SMA5930BT3, G 830B 15.21616.823.4106000.250.512.2941SMA5931BT3, G 831B 17.11818.920.8126500.250.513.7831SMA5932BT3, G 832B 19202118.7146500.250.515.2751SMA5933BT3, G 833B 20.92223.11717.56500.250.516.7681SMA5934BT3, G 834B 22.82425.215.6197000.250.518.2631SMA5935BT3, G 835B 25.652728.3513.9237000.250.520.6561SMA5936BT3, G 836B 28.53031.512.5267500.250.522.8501SMA5937BT3, G 837B 31.353334.6511.4338000.250.525.1451SMA5938BT3, G 838B 34.23637.810.4388500.250.527.4421SMA5939BT3, G 839B 37.053940.959.6459000.250.529.7381SMA5940BT3, G840B40.854345.158.7539500.250.532.7351SMA5941BT3, G 841B 44.654749.358.06710000.250.535.8321SMA5942BT3, G 842B 48.455153.557.37011000.250.538.8291SMA5943BT3, G 843B 53.25658.8 6.78613000.250.542.6271SMA5944BT3, G 844B 58.96265.1 6.010015000.250.547.1241SMA5945BT3, G 845B 64.66871.4 5.512017000.250.551.7223.Tolerance and Voltage Regulation Designation − The type number listed indicates a tolerance of ±5%.4.V Z limits are to be guaranteed at thermal equilibrium.*The “G” suffix indicates Pb−Free package available.Figure 1. Steady State Power DeratingFigure 2. V Z − 3.3 thru 10 VoltsT, TEMPERATURE (°C)Figure 3. V Z = 12 thru 68 VoltsP D , M A X I M U MP O W E R D I S S I P A T I O N (W A T T S )I Z , Z E N E R C U R R E N T (m A )Z Z , D Y N A M I C I M P ED A N CE (O H M S )1002468101010.1V Z , ZENER VOLTAGE (VOLTS)1001010.1010203040V Z , ZENER VOLTAGE (VOLTS)V Z , ZENER VOLTAGE (VOLTS)1001050Figure 4. Zener Voltage − 3.3 to 12 VoltsFigure 5. Zener Voltage − 12 to 68 Volts Figure 6. Effect of Zener VoltageI Z , Z E N E R C U R R E N T (m A )6070801086420−2−4V Z , ZENER VOLTAGE (VOLTS), T E M P E R A T U R E C O E F F I C I E N T (m V / C )°θV Z 10070503020101020305070100V Z , ZENER VOLTAGE (VOLTS), T E M P E R A T U R E C O E F F I C I E N T (m V / C )°θV ZPACKAGE DIMENSIONSSMACASE 403D−02ISSUE Cǒmm inchesǓSCALE 8:1*For additional information on our Pb−Free strategy and solderingdetails, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*DIM A MIN NOM MAX MINMILLIMETERS1.912.16 2.410.075INCHES A10.050.100.150.002b 1.27 1.45 1.630.050c 0.150.280.410.006D 2.29 2.60 2.920.090E 4.06 4.32 4.570.160L0.761.14 1.520.0300.0850.0950.0040.0060.0570.0640.0110.0160.1030.1150.1700.1800.0450.060NOM MAX 4.83 5.21 5.590.1900.2050.220H E STYLE 1:PIN 1.CATHODE (POLARITY BAND)2.ANODENOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: INCH.3.403D−01 OBSOLETE, NEW STANDARD IS 403D−02.ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

AK4312B-VF中文资料

AK4312BA T API 16bit DAC with Headphone AmpGeneral DescriptionThe AK4312B is a 1bit stereo DAC with channel separated volume and channel mixing functions corresponding to A T API CD-ROM specification. A 1bit DAC can achieve monotonicity and low distortion with no adjustment and is superior to traditional R-2R ladder based DACs. In the AK4312B, the loss of accuracy from clock jitter is also improved by using SCF techniques for on-chip post filter. The AK4312B includes continuos time filter with single end output and does not need any external parts. The AK4312B includes headphone amps in addition to line amps and is suitable for multimedia application, CD/DVD-ROM.FeaturesSampling Rate Ranging from 30kHz to 50kHzOn chip Perfect filtering•8 times FIR Interpolator•2nd order SCF, CTFOn chip Line Out Amps with Single End OutputOn chip Headphone Out AmpsDigital de-emphasis for 44.1kHz samplingOn chip Channel Separated Volume & Mixing ControlSoft MuteMaster Clock: 384fsHigh T olerance to Clock JitterTHD+N: -84dBDynamic Range: 90dBPower Supply: 5V±10%Small Package: 24pin VSOPAK4312B compatibleOrdering GuideAK4312B-VF -10∼+70°C 24pin VSOP(0.65mm pitch)AKD4312BEvaluation BoardPin LayoutDifferent Points from AK4312ParameterAK4312AK4312B I/F level CMOS TTL Line Output THD+N DR S/N-85dB 91dB 91dB-84dB 90dB 90dBPIN/FUNCTIONNote: All input pins except internal pull-down pins should not be left floating.ABSOLUTE MAXIMUM RATINGS(AVSS,DVSS=0V; Note 1 )Parameter Symbol min max UnitsPower Supplies: AnalogDigitalDVDD-AVDD AVDDDVDDVDA-0.3-0.3-6.06.00.3VVVInput Current, Any Pin Except Supplies IIN-±10mAInput Voltage VIND-0.3AVDD+0.3VAmbient Operating T emperature T a-1070°CStorage T emperature Tstg-65150°CNote: 1 . All voltages with respect to ground.WARNING: Operation at or beyond these limits may result in permanent damage to the device.Normal operation is not guaranteed at these extremes.RECOMMENDED OPERATING CONDITIONS(AVSS,DVSS=0V; Note 1 )Parameter Symbol min typ max UnitsPower Supplies: Analog (Note 2 )Digital AVDDDVDD4.54.55.05.05.5AVDDVVVoltage Reference (Note 3 )VREF 2.5-AVDD VNotes:2 . AVDD and DVDD should be powered at the same time or AVDD should be powered earlier than DVDD.3 . Analog output voltage scales with the voltage of VREF.AOUT(typ.@0dB)=2.83Vpp*VREF/5.* AKM assumes no responsibility for the usage beyond the conditions in this data sheet.Line Output(AOUT0,AOUT1)(T a=25°C; AVDD,DVDD=5.0V; VREF=AVDD; fs=44.1kHz; Signal Frequency=1kHz; Note 4Measurement Bandwidth=10Hz∼20kHz; R L=5kΩ; HOUT0,HOUT1 are unloaded. unless otherwise specified)Parameter min typ max UnitsResolution16BitsTHD+N (0dB Output)-84-78dBDynamic Range (-60dB Output, A weight)8490dBS/N (A weight)8490dBInterchannel Isolation(1kHz) (Note 5 )8090dBInterchannel Gain Mismatch0.10.3dBGain Drift (Note 6 )60-ppm/°COutput Voltage (Note 7 ) 2.69 2.83 2.97VppLoad Resistance5kΩNotes: 4 . Measured by AD725C(SHIBASOKU). Averaging mode. Refer to the eva board manual.5 . R L≥20kΩ6 . The voltage on VREF pin is held +5V externally.7 . Full-scale voltage(0dB). Output voltage scales with the voltage of VREF.AOUT(typ.@0dB)=2.83Vpp*VREF/5.Headphone Output(HOUT0,HOUT1)(T a=25°C; AVDD,DVDD=5.0V; VREF=AVDD; fs=44.1kHz; Signal Frequency=1kHz;0dB=2.83Vpp; Measurement Bandwidth=10Hz∼20kHz; R L=47Ω; C L=100pF;HOUT is measured by inputting from HIN. unless otherwise specified. Note 8 )Parameter min typ max UnitsTHD+N (-3dB) HOUT-HCOM (-3dB) HOUT-AVSS -75-75-60-60dBdBDynamic Range (-60dB output,A weight)94100dB S/N (A weight)94100dBInterchannel Isolation(1kHz) HOUT-HCOM HOUT-AVSS 50806090dBdBNote: 8 . HOUT-HCOM is measured by DC coupling. HOUT-AVSS is measured by DC cut. Power Supply(T a=25°C; AVDD,DVDD=5.0V; VREF=AVDD; fs=44.1kHz; Signal Frequency=1kHz;Note:9 . Power Dissipation in the power-down mode is applied with no external clocks(MCLK,BICK,LRCK held "H" or "L").(T a=25°C; AVDD,DVDD=4.5V∼5.5V; fs=44.1kHz; DEM="0")Parameter Symbol min typ max Units Digital FilterPassband ±0.1dB (Note 10 ) -6.0dB PB0-22.0520.0-kHzkHzStopband (Note 10 )SB24.1kHz Passband Ripple PR±0.06dB Stopband Attenuation SA43dB Group Delay (Note 11 )GD-14.7-1/fs Digital Filter + SCF + CTFFrequency Response 0∼20.0kHz-±0.5-dB Note: 10 . The passband and stopband frequencies scale with fs.For example, PB=0.4535*fs(@±0.1dB), SB=0.546*fs.11 . The calculating delay time which occurred by digital filtering. This time is from setting the 16bitdata of both channels to input register to the output of analog signal.DIGITAL CHARACTERISTICS(T a=25°C; AVDD,DVDD=4.5∼5.5V)Parameter Symbol min typ max UnitsHigh-Level Input Voltage (MCLK pin) (All pins except MCLK pin) Low-Level Input Voltage (MCLK pin) (All pins except MCLK pin) Input Voltage at AC coupling (MCLK pin)VIH1VIH2VIL1VIL2VAC70%DVDD2.2--1-------30%DVDD0.8AVDDVVVVVppHigh-Level Output Voltage (Iout=-100uA) Low-Level Output Voltage (Iout=100uA)VOHVOLDVDD-0.5---0.5VVInput Leakage Current (Note 12 )Iin--±10uA Notes: 12 . DEM,TST1 pins have internal pull-down devices, nominally 90kΩ.SWITCHING CHARACTERISTICSTiming DiagramOPERATION OVERVIEWSystem Clock InputThe external clocks which are required to operate the AK4312B are MCLK(384fs), LRCK(fs), BICK(32fs ∼). The master clock (MCLK) should be synchronized with LRCK but the phase is free of care. The MCLK is used to operate the digital interpolation filter and the delta-sigma modulator. The fs is audio sampling rate.Not only CMOS clock but sine wave signal with 1Vpp can be input to the MCLK pin by AC coupling. T able 1illustrates standard audio word rates and corresponding frequencies used in the DAC.As the AK4312B includes the phase detect circuit for LRCK, the AK4312B is reset automatically when the synchronization is out of phase by changing the clock frequencies.All external clocks(MCLK,BICK,LRCK) should always be present whenever the AK4312B is in normal operation mode(PD ="H"). If these clocks are not provided, the AK4312B may draw excess current. The AK4312B should be reset by PD ="L" after these clocks are provided. After exiting reset at power-up etc., the AK4312B is in power-down mode until MCLK and LRCK are input.Figure 1 . Internal Clock CircuitLRCK(fs)(kHz)MCLK (MHz)32.012.288044.116.934448.018.4320T able 1 . Examples of System ClockAudio Serial Interface FormatData is shifted in via the SDA T A pin using BICK and LRCK inputs. The serial data is MSB-first, 2's compliment format and is latched on the rising edge of BICK.Figure 2 . Audio Data Input FormatDe-emphasis filterThe AK4317 includes the digital de-emphasis filter(tc=50/15us) by IIR filter. This filter corresponds to three sampling frequencies(32kHz,44.1kHz,48kHz). De-emphasis is enabled by the following two ways.1. DEM pinOnly one de-emphasis(fs=44.1kHz) set initially can be controlled by DEM pin at resetting. The de-emphasis is enabled by setting DEM pin "H". When the frequency of de-emphasis is set by FS0,FS1 of serial mode control bits, the corresponding de-emphasis can be enabled. In this case, DEM bit in the serial mode control should be "0".2. DEM bit in the serial mode controlDEM pin should be open or "L". In this case, The de-emphasis corresponding to fs=32kHz, 44.1kHz,48kHz can be controlled by DEM, FS0 and FS1 in the serial mode control bits.Zero detectionWhen the input data at both channels are continuously zeros for 8192 LRCK cycles, DZF goes to "H". DZF immediately goes "L" if input data are not zero after going DZF "H".Soft mute operationSoft mute operation is performed at digital domain. When SMUTE pin goes "H" or the output mode is set to "MUTE", the output signal is attenuated by -∞ during 1024 LRCK cycles. When SMUTE pin is returned to "L" or exiting "MUTE", the mute is cancelled and the output attenuation gradually changes to 0dB during 1024 LRCK cycles. If the soft mute is cancelled within 1024 LRCK cycles after starting the operation, the attenuation is discontinued and returned to 0dB. The soft mute is effective for changing the signal source without stopping the signal transmission.Notes:1{The output signal is attenuated by -∞ during 1024 LRCK cycles(1024/fs).2{Analog output corresponding to digital input have the group delay(GD).3{If the soft mute is cancelled within 1024 LRCK cycles, the attenuation is discontinued and returned to 0dB. 4{As the input data at both channels are continuously zeros for 8192 LRCK cycles, DZF goes to "H".DZF immediately go to "L" if input data are not zero after DZF "H".Figure 3 . Soft mute and zero detectionSerial Mode ControlThe AK4312B can control output attenuation level, output mode, de-emphasis type and attenuation mode via the serial interface. The serial data consists of two 8 bits for setting the attenuation level of each channel and 8 bits for the mode control. This mode is compatible with the AK4311A.Figure 4 . Configuration of attenuator and mixerNote 1: CCLK should be held "H" or "L" except writing to A TT & mode registers in order to avoid the performancedegradation.Note 2: If the above serial mode control is not used, CS should be held "H".Figure 5 . Serial mode control timing1. Attenuator OperationThe AK4312B has individually controllable attenuator with linear scale and 256 levels for each channel. Equation of attenuation level: A TT=20×Log 10(Binary level/255)FFH: 0dB:01H: -48.1dB00H: Mute(Infinity zero:- ∞)The transition between A TT values is same as soft mute operation. When current value is A TT1 and new value is set as A TT2, A TT1 gradually becomes A TT2 with same operation as soft mute. If new value is set as A TT3 before reaching A TT2, A TT value gradually becomes A TT3 from the way of transition. Cycle time of soft mute: Ts=1024/fsWhen resetting, A TT value is set 00H(Infinity zero). A TT value gradually changes from 00H to FFH(0dB) during Tsafter exiting reset.L0-L7:Lch ATT data, L0=LSB, L7=MSB :FFH at RESET R0-R7:Rch ATT data, R0=LSB, R7=MSB :FFH at RESET S0-S3:Output mode Control :1001 at RESET DEM:De-Emphasis Control :0 at RESET ATC:ATT mode Control:0 at RESET FS0,FS1:fs Control for de-emphasis Filter :00 at RESET2. Output modeThe AK4312B supports the following output modes.•Normal stereo output•L/R Reverse output•Monaural output: L/L, R/R, (L+R)/2•Output muting with soft mute operationWhen resetting, A TT values of both channels are FFH and the attenuation levels are set 0dB. The output mode is also set normal stereo output.S0S1S2S3AOUT0AOUT1Mode0000MUTE MUTE MUTE0001MUTE R0010MUTE L0011MUTE(L+R)/20100R MUTE0101R R0110R L Reverse0111R(L+R)/21000L MUTE1001L R Stereo*at RESET1010L L1011L(L+R)/21100(L+R)/2MUTE1101(L+R)/2R1110(L+R)/2L1111(L+R)/2(L+R)/2MONOT able 2 . Output mode3. De-emphasis controlDEM bit and DEM pin are ORed internally. The de-emphasis(tc=50/15us) corresponding to fs(sampling frequency) selected by FS0 and FS1 is enabled by setting DEM bit "1" or DEM pin "H". When DEM bit is "0" and DEM pin is "L", the de-emphasis is disabled and the setting of FS0 and FS1 is invalid. The de-emphasis is also disabled atFS0="1" and FS1="0". When resetting, DEM bit is set "0". For example, when the de-emphasis is controlled by only DEM pin at fs=44.1kHz, DEM,FS0,FS1 bits should be "0". This condition is also set at resetting.FS0FS1mode0044.1kHz10OFF0148kHz1132kHzT able 3 . De-emphasis filter setting(Valid at DEM bit="1" or DEM pin="H")4. Attenuation controlA TT values of both channels are set Lch A TT data by setting A TC bit "1". In this case, Rch A TT data is ignored. When resetting, A TC bit is set "0" (individually control).Power-DownA1Analog output corresponding to digital input have the group delay(GD).2Analog outputs are floating(Hi-Z) at the power-down mode.3Click noise about -50dB occurs at the edges("↑↓") of PD signal.This noise is output even if "0" data is input.4{When the external clocks(MCLK,BICK,LRCK) are stopped, the AK4312B should be in the power-down mode.5{Please mute the analog output externally if the click noise(3{) influences system application.The timing example is shown in this figure.Figure 6 . Power-down/up sequence exampleSystem ResetThe AK4312B should be reset once by bringing PD "L" upon power-up. The internal timing starts clocking by LRCK "↑" upon exiting reset. If the phase difference between LRCK and internal control signals is larger than +1/16∼-1/16 of word period(1/fs), the synchronization of internal control signals with LRCK is done automatically at the first rising edge of LRCK.1. Internal State at resetting by out-of-synchronizationWhen the AK4312B is reset automatically by out-of-synchronization, the contents of the serial mode control register are kept at this procedure. Therefore, it is not necessary to reset the serial mode control register. After returning to normal operation, A TT value gradually changes from 00H to the kept value (Figure 7 ).Figure 7 .A TT operation at out-of-synchronizationWhen enabling MUTE bit in the serial mode control register by the timing of Figure 7 , the analog output is corresponding to the input data outputs for an instant because the A TT initial transition and the soft muting operate at the same time. This can be avoided by not using the soft muting or setting the input audio data to "0" or settingA TT register to 00H when the out-of-synchronization occurs.Figure 8 . Out-of-synchronization timing with soft muting(@A TT=FFH)(The solid line shows the actual attenuation level.)2. Out-of-synchronization will occur in following cases•L/R clock more than 2 times speed is input to AK4312B in CD-ROM application.•The clock frequency is not changed smoothly between VCO and X'tal in the digitalrecording application.SYSTEM DESIGNFigure 9 shows the system connection diagram. An evaluation board[AKD4312B] is available which demonstrates the optimum layout, power supply arrangements and measurement results.Figure 9 . T ypical Connection DiagramNotes:-LRCK=fs, MCLK=384fs.-If the above serial mode control is not used, CS should be held "H".-When AOUT drives some capacitive load, some resistor should be addedin series between AOUT and capacitive load.- The capacitor value on VCOM depends on low frequency noise level of power supply.- All input pins except internal pull-down pins should not be left floating.1. Grounding and Power Supply DecouplingT o minimize coupling by digital noise, decoupling capacitors should be connected to AVDD and DVDD, respectively. AVDD is supplied from analog supply in system and DVDD is supplied from AVDD via 10Ω resistor as shown in Figure 9. Alternatively if AVDD and DVDD are supplied separately, AVDD and DVDD should be powered at the same time or AVDD should be powered earlier than DVDD. Analog ground and digital ground should be connected together near to where the supplies are brought onto the printed circuit board. Decoupling capacitors for high frequency should be placed as near as possible.2. Voltage referenceThe differential Voltage between VREF and AVSS set the analog output range. VREF pin is normally connected to AVDD with a 0.1uF ceramic capacitor. VCOM is a signal ground of this chip. An electrolytic capacitor of around 10uF in parallel with a 0.1uF ceramic capacitor attached to these pins eliminates the effects of high frequency noise. No load current may be drawn from VCOM pin. All signals, especially clocks, should be kept away from the VREF and VCOM pins in order to avoid unwanted coupling into the AK4312B.3. Line OutputsThe analog outputs are also single-ended and centered around the VCOM voltage. The output signal range is typically 2.83Vpp. The internal switched-capacitor filter and continuous-time filter attenuate the noise generated by the delta-sigma modulator beyond the audio passband. Therefore, no external filters are required for typical application. The output voltage is a positive full scale for 7FFFH(@16bit) and a negative full scale for 8000H(@16bit). The ideal output is VCOM voltage for 0000H(@16bit).DC offsets on analog outputs are eliminated by AC coupling since analog outputs have DC offsets of a few mV.4. Headphone Outputs1)DC CoupleIf the bold lines has some impedance, the interchannel separation degrades. When the ripple on AVDD is big, RC filtering between AVDD-VREF is recommended. Figure 11 shows THD+N vs load of headphone amp.Figure 10 . Headphone Circuit Example(DC Couple)Figure 11 . THD+N vs Input Level(DC couple)2)DC CutIf the bold lines has some impedance, the interchannel separation degrades. When the ripple on AVDD is big, RC filtering between AVDD-VREF is recommended. When 100uF for DC cut is used on HOUT, the cut-off frequency at low band is fc=1/(2πRC)=1/(2*3.14*32*100u)=50Hz.Figure 12 . Headphone Circuit Example(DC Cut)Figure 13 . THD+N vs Input Level(DC cut)z 24pin VSOP (Unit: mm)NOTE: Dimension “*” does not include mold flash.Package & Lead frame materialPackage molding compound:EpoxyLead frame material:CuLead frame surface treatment:Solder plateContents of AAXXXXAA: Lot#XXXX: Date Code元器件交易网。

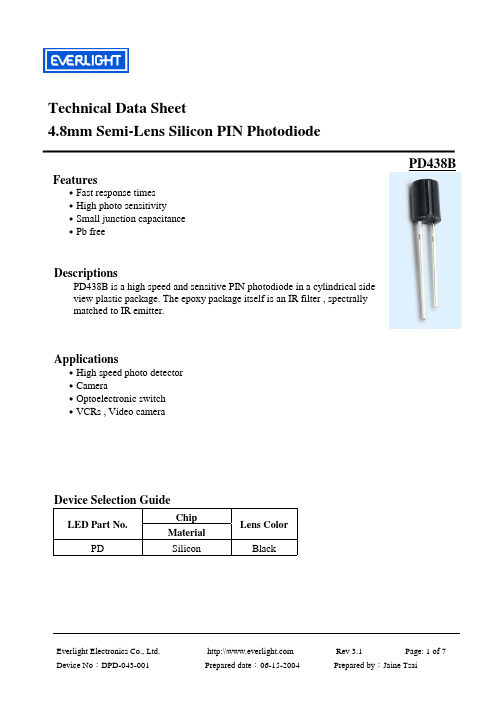

PD438B中文资料

Storage Temperature Tstg Notes: *1:Soldering time≦5 seconds.

Everlight Electronics Co., Ltd. Device No:DPD-043-001

http:\\ Prepared date:06-15-2004

10

2

1

80 60

f=1MHZ VR=3V

VR=10V O Ta=25 C

10

0

t

40

10

-1

20

10 10

-2

-3

0 0.1 1 10 100

10

1

10

2

10

3

10

4

10

5

Everlight Electronics Co., Ltd. Device No:DPD-043-001

http:\\ Prepared date:06-15-2004

Applications

․High speed photo detector ․Camera ․Optoelectronic switch ․VCRs , Video camera

Device Selection Guide

LED Part No. PD Chip Material Silicon Lens Color Black

Package Dimensions

Color Mark

Sensitive Surface

Hale Waihona Puke 4.8±0.20.5± 0.1

1.5Max

1 2

2.54

1.0Min

14.5Min

6.60±0.3

3.8±0.2

2020年弹簧的选材及参数

作者:非成败

作品编号:92032155GZ5702241547853215475102

时间:2020.12.13

弹簧的选材

2010-06-16 10:45:19| 分类:相关知识| 标签:成都碟形弹簧|字号大中小订阅

现阶段,我国碟形弹簧采用的材料有高质量的弹簧钢60Si2MnA、50CrVA或特殊材料,如不锈钢、铬镍铁合金等。

其中特殊材料、不锈钢、铬镍铁合金等适用于高温和腐蚀性环境。

然而,我们发现想找到一种材质,同时满足高强度、耐高温、耐腐蚀、抗磁场,是不可能的,只能寻求某种性能的最大化,比如高强度或耐高温、腐蚀。

因此用户在订购碟簧时,一定要写清楚工况要求,我们的技术人员会充分考虑那些最不利的因素,择其一种合适材质,推荐使用。

下面我们列出国外比较典型的碟簧材料,供参考:

特殊应用

作者:非成败

作品编号:92032155GZ5702241547853215475102 时间:2020.12.13。

AK4365中文资料

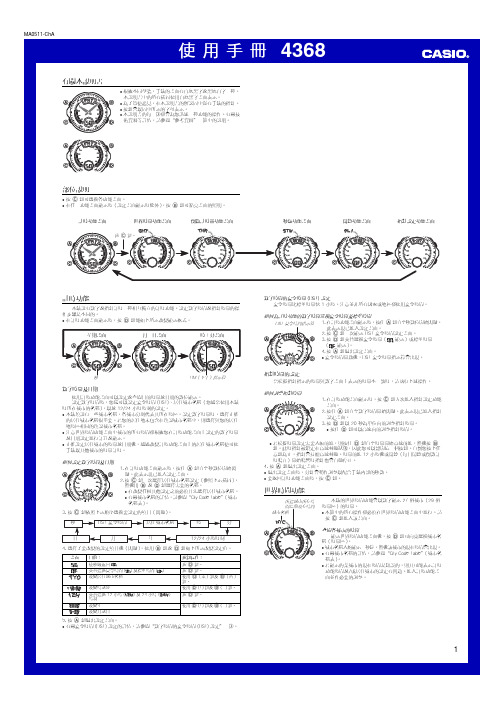

ASAHI KASEI[AK4368]AK4368PLL & HP-AMP DACAK4368 PLL & I/F 1624bit D/A AK4368 3D Stereo Enhancement ON/OFF 41pin BGAPLL50mW∆ΣDAC- 8kHz, 11.025kHz, 12kHz, 16kHz, 22.05kHz, 24kHz, 32kHz, 44.1kHz, 48kHz FIR : 20kHz : ±0.02dB : 54dB : 32kHz, 44.1kHz, 48kHz PLL: : 27MHz, 26MHz, 19.8MHz, 19.68MHz, 19.2MHz, 15.36MHz, 14.4MHz, 13MHz, 12MHz, 11.2896MHz AC I/F : MSB First, 2’s Compliment 2 - I S, 24bit , 24bit/20bit/16bit : LR, LL, RR, (L+R)/2 ALC 83D Stereo Enhancement :3 /I2C: 50mW x 2ch @16Ω, 3.3V - S/N: 92dB@3.3V ON/OFF : 1.6V ∼ 3.6V : 4.0mA @2.4V (HP-AMP ) Ta: −30 ∼ 85°C : 41pin BGA (4mm x 4mm, 0.5mm pitch)MS0409-J-01 -1-2005/08ASAHI KASEI[AK4368]PVDDPVSSMCKOMCLKVCOCLINMINBICK LRCK SDATA DVDD DVSSAVDD Audio Interface PLL VCOM AVSS VCOMDAC(Lch)HDP AmpMUTEHPLALC DEM ATT Bass Boost Digital Filter 3D Stereo Enhancement LOUT 3DCAP1 3DCAP2 3DCAP3 ROUT HDP AmpPDN I2C CAD0/CSN SCL/CCLK SDA/CDTI Serial I/FDAC(Rch)MUTEHPRHVDD HVSS MUTET RINFigure 1.MS0409-J-01 -2-2005/08ASAHI KASEI[AK4368]AK4368VG AKD4368−30 ∼ +85°C AK436841pin BGA (0.5mm pitch)7 6 5AK4368VG4 3 2 1 Top ViewABCDEFG7 6 5 4 3 2 1NC HPL MIN RIN VCOC PVDD NC AHPR HVSS NC NC LIN PVSS MCKO BHVDD AVSSAVDD MUTETVCOM ROUTLOUTNC3DCAP2 3DCAP3 NC 3DCAP1 NC CAD0/ CSN SCL/ CCLK NC GTop View NC DVSS DVDD C I2C MCKI D LRCK BICK EPDN NC SDATA SDA/ CDTI FMS0409-J-01 -3-2005/08ASAHI KASEI[AK4368]AK4365, AK4367AK4365 PLL PLL I/F 19.8/19.68/19.2/15.36/ 14.4/13/12/11.2896MHz 8/11.025/16/22.05/24/32/ 44.1/48kHz 20bit 16/20bit I2S Available N/A N/A Mono 3-wire +6dB (L+R)/2 10mW 2.7 ∼ 3.3V 28QFN(5.2mm x 5.2mm) AK4367 N/A N/A 24bit 16/20/24bit I2S N/A N/A N/A Mono 3-wire/I2C +16dB (L+R)/2 50mW 2.2 ∼ 3.6V 20QFN(4.2mm x 4.2mm) AK4368 27/26/19.8/19.68/19.2/ 15.36/14.4/13/12/11.2896 MHz 8/11.025/12/16/22.05/24/ 32/44.1/48kHzALC 3D Stereo EnhancementAvailable Available Available StereoLL, RR, (L+R)/2 50mW 1.6 ∼ 3.6V 41BGA(4mm x 4mm)MS0409-J-01 -4-2005/08ASAHI KASEI[AK4368]No. B1 C2 C1 D2 D1 E2 E1 F2 F1 G2 G3 MCKO DVSS DVDD I2C MCKI LRCK BICK SDATA SDA CDTI SCL CCLK CAD0 CSN PDN 3DCAP1 3DCAP2 3DCAP3 LOUT ROUT VCOM AVDD AVSS MUTET HVDD HVSS HPR HPL MIN RIN LIN VCOC PVSS PVDDI/O O I I I/O I/O I I/O I I I I I I O O O O O O O O O I I I O HVSS pin L/R “H”: I2C , “L”: 30 & “L”(I2C pin = “H”) (I2C pin = “L”) (I2C pin = “H”) (I2C pin = “L”) (I2C pin = “H”) (I2C pin = “L”)F4 G5 F6 G6 F7 E6 E7 D7 C6 D6 C7 B6 B7 A6 A5 A4 B3 A3 B2 A2“L” 3D Stereo Enhancement 3DCAP2 pin 4.7nF 3D Stereo Enhancement 3DCAP1 pin 4.7nF 470nF 3D Stereo Enhancement 3DCAP3 pin 470nF Lch Rch AVSS pin 2.2µF1 2 3DCAP3 pin 3Rch HP-Amp Lch HP-Amp Rch Lch PLL PVSS PLL PLLAVSS AVDDMS0409-J-01 -5-2005/08ASAHI KASEI[AK4368]No. A1 A7 B4 B5 C3 F3 F5 G1 G4 G7 Note:NCI/O -No Connect Pin No internal bonding. These pins should be connected to ground(I2C, SDA/CDTI, SCL/CCLK, CAD0/CSN, SDATA, LRCK, BICK, MCKI, PDN) PDN pin = “L”Note: MCKI pinAnalog DigitalLOUT, ROUT, MUTET, HPR, HPL, MIN, RIN, LIN CAD0 MCKODVSSMS0409-J-01 -6-2005/08ASAHI KASEI[AK4368](AVSS, DVSS, HVSS, PVSS=0V; Note 1) Parameter Symbol min max Power Supplies Analog AVDD 4.6 −0.3 Digital DVDD 4.6 −0.3 PLL PVDD 4.6 −0.3 HP-Amp HVDD 4.6 −0.3 |AVSS – DVSS| (Note 2) 0.3 ∆GND1 |AVSS – HVSS| (Note 2) 0.3 ∆GND2 |AVSS – PVSS| (Note 2) 0.3 ∆GND3 Input Current (any pins except for supplies) IIN ±10 Analog Input Voltage (Note 3) VINA AVDD+0.3 or 4.6 −0.3 Digital Input Voltage (Note 4) VIND DVDD+0.3 or 4.6 −0.3 Ambient Temperature Ta 85 −30 Storage Temperature Tstg 150 −65 Note 1. Note 2. AVSS, DVSS, HVSS PVSS Note 3. MIN, LIN, RIN pins. Note 4. SDA/CDTI, SCL/CCLK, CAD0/CSN, SDATA, LRCK, BICK, MCLK, PDN, I2C pins.Units V V V V V V V mA V V °C °C:(AVSS, DVSS, HVSS, PVSS=0V; Note 1) Parameter Symbol Power Supplies Analog AVDD Digital DVDD PLL PVDD HP-Amp HVDD Difference1 AVDD−PVDD Difference2 AVDD−HVDD Note 1.min 1.6 1.6 1.6 1.6 −0.3 −0.3typ 2.4 2.4 2.4 2.4 0 0Max 3.6 AVDD 3.6 3.6 +0.3 +0.3Units V V V V V V:MS0409-J-01 -7-2005/08ASAHI KASEI[AK4368]( Ta=25°C; AVDD=PVDD=DVDD=HVDD=2.4V, AVSS=PVSS=DVSS=HVSS=0V; fs=44.1kHz; EXT mode; BOOST OFF; Slave Mode; Signal Frequency =1kHz; Measurement band width=20Hz ∼ 20kHz; Headphone-Amp: RL =16Ω, CL=220µF (Figure 45 )) Parameter min typ Max Units 24 bit DAC Resolution Headphone-Amp: (HPL/HPR pins) (Note 5) Analog Output Characteristics THD+N dB −3dBFS Output, 2.4V, Po=10mW@16Ω −50 −40 −4.8dBFS Output, 3.3V, dB −20 Po=50mW@16Ω HPG bit= “1” 82 90 dB D-Range −60dBFS Output, A-weighted, 2.4V 92 dB −60dBFS Output, A-weighted, 3.3V S/N A-weighted, 2.4V 82 90 dB A-weighted, 3.3V 92 dB Interchannel Isolation 60 80 dB DC Accuracy Interchannel Gain Mismatch Gain Drift Load Resistance (Note 6) Load Capacitance Output Voltage −3dBFS Output (Note 7) −4.8dBFS Output, 3.3V, Po=50mW@16Ω HPG bit= “1” Stereo Line Output: (LOUT/ROUT pins, RL=10kΩ) (Note 8) Analog Output Characteristics: THD+N 0dBFS Output S/N A-weighted DC Accuracy Gain Drift Load Resistance (Note 6) Load Capacitance Output Voltage 0dBFS Output (Note 9) Output Volume: (LOUT/ROUT pins) Step Size Gain Control Range 16 1.01 0.3 200 1.13 0.89 0.5 300 1.25 dB ppm/°C Ω pF Vpp Vrms80 10 1.32 1 −30−60 87 200 1.47 2 -−50 25 1.61 3 0dB dB ppm/°C kΩ pF Vpp dB dBNote 5. DACHL=DACHR bits = “1”, MINHL=MINHR=LINHL=RINHR bits = “0” Note 6. AC Note 7. AVDD Vout = 0.47 x AVDD(typ)@−3dBFS. Note 8. DACL=DACR bits = “1”, MINL=MINR=LINL=RINR bits = “0” Note 9. AVDD Vout = 0.61 x AVDD(typ)@0dBFS.MS0409-J-01 -8-2005/08ASAHI KASEI[AK4368]Parameter LINEIN: (LIN/RIN/MIN pins) Analog Input Characteristics Input Resistance (Figure 23, Figure 24 ) LIN pin LINHL bit = “1”, LINL bit = “1” LINHL bit = “1”, LINL bit = “0” LINHL bit = “0”, LINL bit = “1” RIN pin RINHR bit = “1”, RINR bit = “1” RINHR bit = “1”, RINR bit = “0” RINHR bit = “0”, RINR bit = “1” MIN pin MINHL=MINHR=MINL=MINR bits = “1” MINHL bit = “1”, MINHR=MINL=MINR bits = “0” MINHR bit = “1”, MINHL=MINL=MINR bits = “0” MINL bit = “1”, MINHL=MINHR=MINR bits = “0” MINR bit = “1”, MINHL=MINHR=MINL bits = “0” Gain LIN/MIN→LOUT, RIN/MIN ROUT LIN/MIN→HPL, RIN/MIN HPR Power Supplies Power Supply Current Normal Operation (PDN pin = “H”) (Note 10) AVDD+PVDD+DVDD HVDD Power-Down Mode (PDN pin = “L”) (Note 11)mintypmaxUnits35 35 17 −1 −0.2450 100 100 50 100 100 25 100 100 100 100 0 +0.76+1 +1.76kΩ kΩ kΩ kΩ kΩ kΩ kΩ kΩ kΩ kΩ kΩ dB dB-3.8 1.2 15.5 2.5 100mA mA µANote 10. PMDAC=PMHPL=PMHPR=PMLO bits = “1”, MUTEN bit = “1”, MCKO bit = “0”, HP-Amp PMDAC=PMHPL=PMHPR= “1”,PMLO bit= “0” , AVDD+PVDD+DVDD+HVDD= 4.0mA. Note 11. (MCKI, BICK, LRCK) DVSSMS0409-J-01 -9-2005/08ASAHI KASEI[AK4368](Ta=25°C; AVDD, DVDD, PVDD, HVDD=1.6 ∼ 3.6V; fs=44.1kHz; De-emphasis = “OFF”) Parameter Symbol min typ DAC Digital Filter: (Note 12) Passband (Note 13) PB 0 −0.05dB 22.05 −6.0dB Stopband (Note 13) SB 24.1 Passband Ripple PR Stopband Attenuation SA 54 Group Delay (Note 14) GD 22 Group Delay Distortion 0 ∆GD DAC Digital Filter + Analog Filter: (Note 12) (Note 15) Frequency Response FR 0 ∼ 20.0kHz ±0.5 Analog Filter: (Note 16) Frequency Response FR 0 ∼ 20.0kHz ±1.0 BOOST Filter: (Note 15) (Note 17) Frequency Response 20Hz FR 5.76 MIN 100Hz 2.92 1kHz 0.02 20Hz FR 10.80 MID 100Hz 6.84 1kHz 0.13 20Hz FR 16.06 MAX 100Hz 10.54 1kHz 0.37 Note 12. BOOST OFF (BST1-0 bit = “00”) Note 13. fs ( ) PB=0.4535fs(@−0.05dB) SB=0.546fs(@−54dB) Note 14. Note 15. DAC Note 16. MIN Note 17. HPL, HPR, LOUT, ROUT HPL/HPR/LOUT/ROUT, LIN fsmax 20.0 ±0.02 -Units kHz kHz kHz dB dB 1/fs µs dB dB dB dB dB dB dB dB dB dB dBHPL/LOUT, RINHPR/ROUTBoost Filter (fs=44.1kHz) 20 15 Level [dB] MID 10 MIN 5 0 -5 10 100 Frequency [Hz] 1000 10000MAXFigure 2. Boost Frequency (fs=44.1kHz)MS0409-J-01 - 10 -2005/08DC(Ta=25°C; AVDD, DVDD, PVDD, HVDD=1.6 ∼ 3.6V)UnitsmaxtypParameter Symbol minVHigh-Level Input Voltage 2.2V≤DVDD≤3.6V VIH 70%DVDD- -V1.6V≤DVDD<2.2V VIH 80%DVDD- -Low-Level Input Voltage 2.2V≤DVDD≤3.6V VIL - - 30%DVDD V1.6V≤DVDD<2.2V VIL - - 20%DVDD VInput Voltage at AC Coupling (Note 18) VAC 0.4 - - VppVHigh-Level Output Voltage (Iout=−200µA)VOH DVDD−0.2- -Low-Level Output VoltageV (Except SDA pin: Iout=200µA)VOL - - 0.2(SDA pin: Iout=3mA)VOL - - 0.4 VInput Leakage Current Iin - - ±10 µANote 18. MCKI pin (Figure 45 )(Ta=25°C; AVDD, DVDD, PVDD, HVDD=1.6 ∼ 3.6V; C L = 20pF)maxtypUnitsminParameter SymbolMaster Clock Input TimingFrequency (PLL mode)fCLK 11.2896 - 27 MHz(EXT mode) fCLK 2.048 - 12.288 MHzPulse Width Low (Note 19) tCLKL 0.4/fCLK- - nsPulse Width High (Note 19) tCLKH 0.4/fCLK- - nsAC Pulse Width (Note 20) tACW 18.5 - - nsLRCK TimingkHz Frequency fs 8 44.1 48Duty Cycle: Slave Mode Duty 45 - 55 %MasterMode Duty - 50 - %MCKO Output Timing (PLL mode)Frequency fCLKO 0.256 - 12.288 MHzDuty Cycle (Except fs=32kHz, PS1-0= “00”) dMCK 40 - 60 %(fs=32kHz, PS1-0= “00”) dMCK - 33 - %Serial Interface Timing (Note 21)Slave Mode (M/S bit = “0”):Period tBCK 312.5 - - nsBICKBICK Pulse Width Low tBCKL 100 - - nsPulse Width High tBCKH 100 - - nsLRCK Edge to BICK “↑” (Note 22) tLRB 50 - - nsBICK “↑” to LRCK Edge (Note 22) tBLR 50 - - nsSDATA Hold Time tSDH 50 - - nsSDATA Setup Time tSDS 50 - - nsMaster Mode (M/S bit = “1”):BICK Frequency (BF bit = “1”)fBCK - 64fs - Hz(BF bit = “0”) fBCK - 32fs - HzDuty dBCK - 50 - %BICKBICK “↓” to LRCK tMBLR −50 - 50 nsSDATA Hold Time tSDH 50 - - nsSDATA Setup Time tSDS 50 - - nsControl Interface Timing (3-wire Serial mode)CCLK Period tCCK 200 - - nsCCLK Pulse Width Low tCCKL 80 - - nsPulse Width High tCCKH 80 - - nsCDTI Setup Time tCDS 40 - - nsCDTI Hold Time tCDH 40 - - nsCSN “H” Time tCSW 150 - - nsCSN “↑” to CCLK “↑” tCSS 50 - - nsCCLK “↑” to CSN “↑” tCSH 50 - - nsNote 19. ACNote 20. MCKI(Figure 3 )Note 21.Note 22. LRCK BICK “↑”UnitsmaxtypminParameter SymbolControl Interface Timing (I2C Bus mode): (Note 23)SCL Clock Frequency fSCL - - 400 kHzBus Free Time Between Transmissions tBUF 1.3 - - µsStart Condition Hold Time (prior to first clock pulse) tHD:STA0.6 - - µsClock Low Time tLOW 1.3 - - µsClock High Time tHIGH 0.6 - - µsSetup Time for Repeated Start Condition tSU:STA0.6 - - µsSDA Hold Time from SCL Falling (Note 24) tHD:DAT0 - - µsSDA Setup Time from SCL Rising tSU:DAT0.1 - - µsRise Time of Both SDA and SCL Lines tR - - 0.3 µsFall Time of Both SDA and SCL Lines tF - - 0.3 µsSetup Time for Stop Condition tSU:STO0.6 - - µsPulse Width of Spike Noise Suppressed by Input Filter tSP 0 - 50 nsPower-down & Reset TimingPDN Pulse Width(Note 25)tPD 150 - - nsNote 23. I2C Philips SemiconductorsNote 24. 300ns (SCL )Note 25. PDN pin “L” “H”MeasurementPointDVSS1000pFFigure 3. MCKI AC Coupling TimingVIHMCKIVILVIH LRCKVILVIHBICKVIL50%DVDD MCKOFigure 4. Clock TimingLRCKVIH BICKVILVIHSDATAVILVIH VILFigure 5. Serial Interface Timing (Slave Mode)LRCK50%DVDDBICKVIH SDATAVIL50%DVDDFigure 6. Serial Interface Timing (Master mode)CSNVIH CCLKVILVIH CDTI VILVIHVILFigure 7. WRITE Command Input TimingCSNVIH CCLKVILVIH CDTI VILVIHVILD3D2D1D0Figure 8. WRITE Data Input TimingVIHVILVIHVILFigure 9. I 2C Bus Mode TimingVILPDNFigure 10. Power-down & Reset Timing1) PLL (PMPLL bit = “1”)PLL PLL3-0 bits, FS3-0 bits (Table 1, Table 2) MCKO PS1-0 bits (Table 3) MCKO bit ON/OFF PLL Table 1 (PMDAC bit = “1”) 0”M/S bit “1” “0” AK4368 (PDN pin = “L”) M/S bit “1”11.2896MHz, 12MHz, 13MHz, 14.4MHz, 15.36MHz, 19.2MHz, 19.68MHz, 19.8MHz, 26MHz, 27MHz PLL MCKO, BICK, LRCK (Figure 11)Figure 11. PLL Master ModeM/S bit “1” AK4368 LRCK, BICK pin AK4368 LRCK, BICK pin 100kΩ(M/S bit = “1”) PMPLL bit = “0” Æ “1” PMDAC bit = “0” Æ “1” PLL LRCK BICK “L” MCKO bit = “1” MCKO pin MCKO bit = “0” MCKO pin “L” PLL LRCK BICK AK4368 (Table 4)BICK, LRCK pin PLL AK4368 MCKO BICK, LRCKFigure 12. PLL Slave Mode(M/S bit = “0”) PMPLL bit = “0” Æ “1” PMDAC bit = “0” Æ “1” PLL MCKO bit = “1” MCKO pin PLL MCKO pin Table 3 (PMDAC bit = “1”) LRCK BICK (PMDAC bit = “0”)VCOC R,CMode PLL3 PLL2 PLL1 PLL0 MCKI fs[kHz] R[Ω]C[F] PLL (typ 0 0 0 0 0 11.2896MHz 44.1, 48 10k 22n 20ms Default 1 0 0 0 1 14.4MHz 44.1, 48 10k 22n 20ms 2 0 0 1 0 12MHz 44.1, 48 10k 47n 20ms 3 0 0 1 1 19.2MHz 44.1, 48 10k 22n 20ms 4 0 1 0 0 15.36MHz 44.1, 48 10k 22n 20ms 5 0 1 0 1 13MHz 44.1, 48 15k 330n 100ms 6 0 1 1 0 19.68MHz 44.1, 48 10k 47n 20ms 7 0 1 1 1 19.8MHz 44.1, 48 10k 47n 20ms 8 1 0 0 0 26MHz 44.1, 48 15k 330n 100ms 9 1 0 0 1 27MHz 44.1, 48 10k 47n 20ms 10 1 0 1 0 13MHz 44.0995 48.000710k 22n 20ms11 1 0 1 1 26MHz 44.0995 48.000710k 22n 20ms12 1 1 0 0 19.8MHz 44.0995 47.999210k 22n 20ms13 1 1 0 1 27MHz 44.0995 47.999710k 22n 20ms14-15 Others N/A N/A N/A N/A -Table 1. MCKI (PLL mode)Mode FS3 FS2 FS1 FS0 fs0 0 0 0 0 48kHz1 0 0 0 1 24kHz2 0 0 1 0 12kHz4 0 1 0 0 32kHz5 0 1 0 1 16kHz6 0 1 1 0 8kHz8 1 0 0 0 44.1kHz Default9 1 0 0 1 22.05kHz10 1 0 1 0 11.025kHz3, 7,11-15Others N/ATable 2. (PLL mode)PS1 PS0 MCKO0 0 256fsDefault0 1 128fs1 0 64fs1 1 32fsTable 3. MCKO (PLL mode, MCKO bit = “1”)Master Mode (M/S bit = “1”)Power Up(PMDAC bit= PMPLL bit= “1”) Power Down(PMDAC bit= PMPLL bit= “0”)PLL UnlockMCKI pin Refer to Table 1. Input orfixed to “L” or “H”Refer to Table 1.MCKO pin MCKO bit = “0”: “L”MCKO bit = “1”: Output “L” MCKO bit = “0”: “L”MCKO bit = “1”: UnsettlingBICK pin BF bit = “1”: 64fs outputBF bit = “0”: 32fs output“L” “L” LRCK pin Output “L” “L”Table 4. Clock Operation in Master mode (PLL mode)Slave Mode (M/S bit = “0”)Power Up(PMDAC bit= PMPLL bit= “1”) Power Down(PMDAC bit= PMPLL bit= “0”)PLL UnlockMCKI pin Refer to Table 1. Input orfixed to “L” or “H”Refer to Table 1.MCKO pin MCKO bit = “0”: “L”MCKO bit = “1”: Output “L” MCKO bit = “0”: “L”MCKO bit = “1”: UnsettlingBICK pin Input Fixed to “L” or “H” externally Input orFixed to “L” or “H”externallyLRCK pin Input Fixed to “L” or “H” externally Input orFixed to “L” or “H”externallyTable 5. Clock Operation in Slave mode (PLL mode)2) (PMPLL bit = “0”: Default)PMPLL bit “0” (EXT mode) MCKI pin PLL DAC FS3-0 bits Table 6 PLL3-0 bits MCKO MCKO bit ON/OFF PS1-0 bit DAC (PMDAC bit = “1”) “0”(M/S bit = “1”) LRCK BICK AK4368 (Figure 13) (PMDAC bit = “1”) MCKI pin DAC (PMDAC bit = “0”)AK4368Figure 13. EXT Master Mode(M/S bit = “0”) MCKI, BICK, LRCK (Figure 14) MCKI LRCK DAC (PMDAC bit = “1”) (MCKI, BICK, LRCK) DAC (PMDAC bit = “0”)AK4368Figure 14. EXT Slave ModeMode FS3 FS2 FS1 FS0 fs MCKI0 0 0 0 0 8kHz ∼ 48kHz 256fs1 0 0 0 1 8kHz ∼ 24kHz 512fs2 0 0 1 0 8kHz ∼ 12kHz 1024fs4 0 1 0 0 8kHz ∼ 48kHz 256fs5 0 1 0 1 8kHz ∼ 24kHz 512fs6 0 1 1 0 8kHz ∼ 12kHz 1024fs8 1 0 0 0 8kHz ∼ 48kHz 256fs Default9 1 0 0 1 8kHz ∼ 24kHz 512fs10 1 0 1 0 8kHz ∼ 12kHz 1024fs3, 7,Others N/A N/A 11-15Table 6. MCKI (EXT mode)PS1 PS0 MCKODefault0 0 256fs0 1 128fs1 0 64fs1 1 32fsTable 7. MCKO (EXT mode, MCKO bit = “1”)Master Mode (M/S bit = “1”)Power Up (PMDAC bit = “1”) Power Down (PMDAC bit = “0”)MCKI pin Refer to Table 6. Input orfixed to “L” or “H”“L”MCKO pin MCKO bit = “0”: “L”MCKO bit = “1”: OutputBICK pin BF bit = “1”: 64fs output“L”BF bit = “0”: 32fs outputLRCK pin Output “L”Table 8. Clock Operation in Master mode (EXT mode)Slave Mode (M/S bit = “0”)Power Up (PMDAC bit = “1”) Power Down (PMDAC bit = “0”)MCKI pin Refer to Table 6. Input orfixed to “L” or “H”MCKO pin MCKO bit = “0”: “L”“L”MCKO bit = “1”: OutputBICK pin Input Fixed to “L” or “H” externallyLRCK pin Input Fixed to “L” or “H” externallyTable 9. Clock Operation in Slave mode (EXT mode)DR, S/N MCKIDR, S/N Table 10 DAC DR,S/NDR, S/N (BW=20kHz, A-weight)MCKIfs=8kHz fs=16kHz256fs 56dB 75dB512fs 75dB 90dB1024fs 90dB N/ATable 10. MCKI DR, S/N (2.4V)SDATA, BICK, LRCK 3pin 5 (Table 11) DIF2-0 bits Mode 0 16bitDAC Mode 1 Mode 0 20bit Mode 4 Mode 0 24bit Mode 2 ADC DSP Mode 3 I 2S BICK ≥48fs Mode 2 3 16bit LSB 17∼24bit 8 “0” 20bit LSB 21∼24bit 4 “0”BICK=32fs(BF bit = “0”) Mode 1, 2Mode DIF2 DIF1 DIF0 BICK0 0 0 0 0: 16bit, 32fs ≤ BICK ≤ 64fsFigure 15 1 0 0 1 1: 20bit, 40fs ≤ BICK ≤ 64fsFigure 16 2 0 1 0 2: 24bit, 48fs ≤ BICK ≤ 64fsFigure 17Default 3 0 1 1 3: I 2SBICK=32fs or 48fs ≤ BICK ≤ 64fs Figure 18 4 1 0 0 4: 24bit, 48fs ≤ BICK ≤ 64fsFigure 16 Table 11.SDATABICKLRCKSDATABICK(32fs)Mode 0Mode 0Figure 15. Mode 0 (LRP = BCKP bits = “0”)SDATALRCKBICKMode 1SDATAMode 4Figure 16. Mode 1, 4 (LRP = BCKP bits = “0”)LRCK BICKSDATA16bitSDATA20bitSDATA24bitFigure 17. Mode 2 (LRP = BCKP bits = “0”)LRCKBICKSDATA16bitSDATA20bitSDATA24bitBICKSDATA16bit (32fs)Figure 18. Mode 3 (LRP = BCKP bits = “0”)ALCALC bit = “1” ALC ALC bit = “0” ALC 0dB[1] ALCALC DAC L/R ALC (−6.0dBFS) ALC ATT (LMAT1-0 bits, Table 13) ALC L/R ROTM1-0 bits (Table 12)ALC ,ROTM1 ROTM0fs=16kHzfs=22.05kHz fs=24kHzfs=32kHz fs=44.1kHz fs=48kHz0 0 1024/fs 64ms 46ms 43ms 32ms 23ms 21ms0 1 2048/fs128ms 93ms 85ms 64ms 46ms 43msDefault1 0 4096/fs 256ms 186ms 171ms 128ms 93ms 85ms11Reserved- - - - - - Table 12. ALC ,ALC ATTLMAT1 LMAT0 ALC Output ≥−6.0dBFS ALC Output ≥0dBFSALC Output ≥+6dBFSALC Output ≥+12dBFS0 1 1 1 1Default 01 2 2 2 210 2 2 4 411 2 4 4 8Table 13. ALC ATT[2] ALCALC ALC ROTM1-0 bits DAC (−8.5dBFS) ALC ALC ROTM1-0 bits (Table 12) (L/R ) (REF7-0 bits, Table 15) RATT bit (Table 14) ALC ROTM1-0 bits ROTM1-0 bits ROTM1-0 bitsALC DAC L/R ALC (−6.0dBFS) ALCALC(ALC ) ≤ (DAC ) < (ALC )(ALC ) > (DAC )ROTM1-0 bitsSTEPRATT GAINDefault0 11 2Table 14. ALCREF7-0GAIN(dB)FFH: ReservedC2HC1H +18.0C0H +17.625BFH +17.25: :92H +0.375Default91H 090H −0.375: :73H −11.2572H −11.62571H −12.070H: Reserved00HTable 15. ALC[3] ALCfs=16kHz fs=44.1kHzRegister Name CommentData Operation Data Operation ROTM1-0 Zero crossing timeout period 00 64ms 01 46msREF7-0 Maximum gain at recovery operation C1H +18dB C1H+18dBLMAT1-0Limiter ATT step 00 1 step 001 stepRATT Recovery GAIN step 0 1 step 0 1 stepALC ALC enable 1 Enable 1 EnableTable 16. ALCALC ALC (ALC bit = “0” PMDAC bit = “0”)LMAT1-0, ROTM1-0, RATT, REF7-0Note: WR: WriteFigure 19. ALCAK4368 MUTE 0.5dB 256 (DATT) DAC 0dB −127dB (Table 17) DATTC bit “1” ATTL7-0 bit Lch, Rch DATTC bit “0” Lch, RchATTL7-0AttenuationATTR7-0FFH 0dBFEH −0.5dBFDH −1.0dBFCH −1.5dB: :: :02H −126.5dB01H −127.0dB00H MUTE (−∞) DefaultTable 17. Digital Volume ATTATT7-0 ATS bit 1061/fs 7424/fs (Table 18) ATS bit = “0” ATT 1062 FFH(0dB) 00H(MUTE) 1061/fs (24ms @fs=44.1kHz) PDN pin “L” ATT7-0 00H ATT7-0 PMDAC bit “0” 00H PMDAC bit “1”ATT speedATS0dB to MUTE 1 stepDefault0 1061/fs 4/fs1 7424/fs 29/fsTable 18. ATT7-0SMUTE bit “1” ATT ATT ×ATT (Table 18) −∞ (“0”) SMUTE bit “0” −∞ ATT ×ATT ATT −∞ ATTAttenuation-Analog OutputFigure 20.Notes:(1) ATT ×ATT (Table 18) ATS bit = “1” ATT “128”(−63.5dB)3712/fs(2) (GD)(3) −∞ATTIIR 3 (32kHz, 44.1kHz, 48kHz) (50/15µs ) DEM1-0 bit (Table 19)DEM1 bit DEM0 bit De-emphasis44.1kHz0 0Default0 1 OFF48kHz1 032kHz1 1Table 19.BST1-0 bit DAC (Table 20)BST1 bit BST0 bit BOOSTDefault0 0 OFF0 1 MIN1 0 MID1 1 MAXTable 20.MONO1-0 bit DAC Lch/Rch (Table 21)MONO1 bit MONO0 bit Lch RchDefault0 0 L R0 1 L L1 0 R R(L+R)/2(L+R)/21 1Table 21.PDN pin “L” VCOM, DAC, HPL, HPR, LOUT, ROUT PDN pinDAC PMDAC bit “1” MCKI MCKI(HPL, HPR pins)HVDD MUTET pin 16Ω PMHPL=PMHPR bits = “1” MUTEN bit “1” VCOM(=0.475 x AVDD) MUTEN bit “0” HVSS t r : (VCOM/2 )70k x C (typ) t f : (VCOM/2 )60k x C (typ) Table 22.: MUTET pin C=1µF(VCOM/2 ): t r = 70k x 1µ = 70ms(typ)(VCOM/2 ): t f = 60k x 1µ = 60ms(typ)PMHPL, PMHPR bits “0” HPL, HPR pins HVSSMUTEN bitPMHPL/R bitHPL/R pin (1) (2)(4) (3)t r t fVCOM/2VCOMFigure 21.(1) (PMHPL, PMHPR bits = “1”) HVSS(2) (MUTEN bit = “1”) MUTET MUTET pin “C” VCOM/2 (t r ) 70k x C(typ)(3) (MUTEN bit = “0”) MUTET HVSS MUTET pin “C” VCOM/2 (t f ) 60k x C(typ)(4) (PMHPL, PMHPR bits = “1”) HVSS(fc) Table 23 (fc) R L 16Ω AVDD=2.4, 3.0, 3.3V 0.47 x AVDD (Vpp) @−3dBFSFigure 22.Output Power [mW]HPG=0, 0dBHPG=1,4.8dBR [Ω] C [µF]fc [Hz] BOOST=OFFfc [Hz] BOOST=MIN2.4V3.0V 3.3V 3.3V220 45 170 100 100 43 20 31 38 50100 70286.8 47 149 78 10 15 18 25100 50 191647 106 475 8 9 13Table 23. , fON/OFF DACHL, LINHL, MINHL, DACHR, RINHR, MINHR bits HPG bit = “0” (R 1=100k) +0.76dB(typ) HPG bit = “1” (R 1= 50k) DAC +6.76dB(typ)Figure 23. (HPG bit = “0” )(LOUT, ROUT pins)0.475 x AVDD 10kΩ PMLO bit = “1” ON/OFF DACL, LINL, MINL, DACR, RINR, MINR bits LOG bit = “0”(R1=100k), ATTS3-0 bits = “0FH”(0dB) 0dB(typ) LOG bit = “1” (R1= 50k) DAC +6dBFigure 24. LOUT/ROUT (LOG bit = “0” )LOUT/ROUT LMUTE bit = “0” ATTS3-0 bit (0dB ∼−30dB, 2dB step, Table 24) LOUT/ROUTLMUTE ATTS3-0 Attenuation0FH 0dB0EH −2dB0DH −4dB0CH −6dB: :: :01H −28dB00H −30dBDefault1 x MUTETable 24. LOUT/ROUT Volume ATT (x: Don’t care)3D Stereo EnhancementAK4368 3D (3D Stereo Enhancement) 3D1-0 bits 3D (Table 25) 3D DP1-0 bits (Table 26) 3D1-0 bits 50ms 3D1-0 bits MUTEN bit3DCAP1, 3DCAP2, 3DCAP3 pins Figure 25 4.7nF 470nF ±20% 3DCAP1, 3DCAP2, 3DCAP3 pins 20pFDefaultDP1 bit DP0 bit 3D Depth 0 0 0% Default 0 1 50% 1 0 70% 1 1 100%Table 26. 3D4.7nF470nFFigure 25. 3D(EXT mode)1) DAC → HP-AmpPower Supply PDN pinPMVCM bitClock InputSDTI pin PMDAC bit DAC Internal State HPL/R pinPMHPL, PMHPR bits ATTL7-0 ATTR7-0 bitsMUTEN bitDACHL, DACHR bits3D1-0 bitsFigure 26. DAC HP-amp (Don’t care: Hi-Z )(1) 150ns PDN pin “H” (2) PDN pin “H” PMVCM, PMDAC bit “1” (3) DAC (MCKI, BICK, LRCK) PMDAC bit = “0”(4) PMVCM, PMDAC bits “1” DACHL, DACHR bits “1”(5) 3D DACHL, DACHR bits “1” 3D1-0 bits “10”(6) 3D DACHL, DACHR bits “1” 2ms (VCOM pin2.2µF ) PMHPL, PMHPR, MUTEN bits “1” 3D 3D1-0bits “10” 50ms PMHPL, PMHPR, MUTEN bits “1”(7) MUTET pin (C) VCOM/2(t r ) 70k x C(typ) C=1µF t r 70ms(typ)(8) MUTET pin (C) VCOM/2(t f ) 60k x C(typ) C=1µF t f 60ms(typ)PMHPL, PMHPR “0” DACL, DACR bits “0” 3D1-0bits “00”(9) 22/fs(=499µs@fs=44.1kHz) (GD)(10) ATS bit 1061/fs(=24ms@fs=44.1kHz) (11) OFF2) DAC → LineoutPower SupplyPDN pinPMVCM bitClock InputSDTI pin PMDAC bit DAC Internal State PMLO bit ATTL/R7-0 bits LMUTE,ATTS3-0 bitsDACL, DACR bits3D1-0 bitsFigure 27. DAC Lineout (Don’t care: Hi-Z )(1) 150ns PDN pin “H” (2) PDN pin “H” PMVCM bit “1” (3) PMVCM bit “1” DACL, DACR bits “1”(4) 3D DACL, DACR bits “1” 3D1-0 bits “01”(5) 3D DACL, DACR bits “1” PMDAC, PMLO bits “1”3D 3D1-0bits “01” PMDAC, PMLO bits “1”(6) DAC (MCKI, BICK, LRCK) PMDAC bit = “0”LOUT/ROUT (7) PMLO bit LOUT, ROUT pins(8) 22/fs(=499µs@fs=44.1kHz) (GD)(9) ATS bit 1061/fs(=24ms@fs=44.1kHz)3) LIN/RIN/MIN → HP-Amp, LineoutPower SupplyPDN pinPMVCM bitHPL/R pinsMOUT pinLMUTE,ATTM3-0 bitsLIN/RIN/MIN pinsPMHPL/R bitsMUTEN bitPMLO bit3D1-0 bitsFigure 28. LIN/RIN/MIN, HP-amp LOUT/ROUT(Don’t care: Hi-Z )(1) 150ns PDN pin “H” DAC(MCLK, BICK, LRCK) (2) PDN pin “H” PMVCM bit “1” (3) PMVCM bit “1” LINHL, MINHL, RINHR, MINHR, LINL, MINL, RINR, MINR bits “1”(4) LINHL, MINHL, RINHR, MINHR, LINL, MINL, RINR, MINR bits “1” LIN, RIN, MIN pin0.475 x AVDD(5) 3D LINHL, MINHL, RINHR, MINHR, LINL, MINL, RINR, MINR bits “1”3D1-0bits “01”, “10” “11” (Refer to Table 25)(6) 3D LINHL, MINHL, RINHR, MINHR, LINL, MINL, RINR, MINR bits “1”2ms (VCOM pin 2.2µF ) PMHPL, PMHPR, MUTEN, PMLO bits “1” 3D 3D1-0bits “01”, “10” “11” 50ms PMHPL, PMHPR, MUTEN, PMLO bits “1”(7) MUTET pin (C) VCOM/2(t r ) 70k x C(typ) C=1µF t r 70ms(typ)(8) MUTET pin (C) VCOM/2(t f ) 60k x C(typ) C=1µF t f 60ms(typ)PMHPL, PMHPR bits “0” LINHL, MINHL, RINHR, MINHR, LINL, MINL, RINR, MINR bits “0” (9) PMLO bit LOUT, ROUT pins(PLL Slave mode)1) DAC → HP-AmpPower Supply PDN pinMCKI pinSDTI pin DAC Internal State HPL/R pinPMHPL, PMHPR bits ATTL7-0 ATTR7-0 bitsMUTEN bitDACHL, DACHR bits3D1-0 bits MCKO pinBICK,LRCK pinsFigure 29. DAC HP-amp (Don’t care: Hi-Z )(1) 150ns PDN pin “H” (2) PDN pin “H” PMVCM, PMPLL, PMDAC, MCKO bits “1” (3) MCKI pin PLL(4) PLL Table 1 PLL MCKO pin (5) DAC MCKO (BICK, LRCK) PMDAC bit = “0”(6) PLL DACHL, DACHR bits “1”(7) 3D DACHL, DACHR bits “1” 3D1-0 bits “10”(8) 3D DACHL, DACHR bits “1” 2ms (VCOM pin2.2µF ) PMHPL, PMHPR, MUTEN bits “1” 3D 3D1-0bits “10” 50ms PMHPL, PMHPR, MUTEN bits “1”(9) MUTET pin (C) VCOM/2(t r ) 70k x C(typ) C=1µF t r 70ms(typ)(10) MUTET pin (C) VCOM/2(t f ) 60k x C(typ) C=1µF t f 60ms(typ)PMHPL, PMHPR “0” DACL, DACR bits “0” 3D1-0bits “00”(11) 22/fs(=499µs@fs=44.1kHz) (GD)(12) ATS bit 1061/fs(=24ms@fs=44.1kHz) (13) OFF2) DAC → LineoutMCKO pinBICK, LRCK pinsPower SupplyPDN pinMCKI pinSDTI pin DAC Internal State PMLO bit ATTL/R7-0 bits LMUTE,ATTS3-0 bitsDACL, DACR bits3D1-0 bitsFigure 30. DAC Lineout (Don’t care: Hi-Z )(1) 150ns PDN pin “H” (2) PDN pin “H” PMVCM, PMPLL, PMDAC, MCKO bits “1” (3) MCKI pin PLL(4) PLL Table 1 PLL MCKO pin (5) DAC MCKO (BICK, LRCK) PMDAC bit = “0”LOUT/ROUT (6) PLL DACL, DACR bits “1”(7) 3D DACL, DACR bits “1” 3D1-0 bits “01”(8) PMLO bit “1” (9) PMLO bit LOUT, ROUT pins(10) 22/fs(=499µs@fs=44.1kHz) (GD)(11) ATS bit 1061/fs(=24ms@fs=44.1kHz)3) LIN/RIN/MIN → HP-Amp, LineoutPower SupplyPDN pinPMVCM bitHPL/R pinsMOUT pinLMUTE,ATTM3-0 bitsLIN/RIN/MIN pinsPMHPL/R bitsMUTEN bitPMLO bit3D1-0 bitsFigure 31. LIN/RIN/MIN, HP-amp LOUT/ROUT(Don’t care: Hi-Z )(1) 150ns PDN pin “H” DAC(MCLK, BICK, LRCK) (2) PDN pin “H” PMVCM bit “1” (3) PMVCM bit “1” LINHL, MINHL, RINHR, MINHR, LINL, MINL, RINR, MINR bits “1”(4) LINHL, MINHL, RINHR, MINHR, LINL, MINL, RINR, MINR bits “1” LIN, RIN, MIN pin0.475 x AVDD(5) 3D LINHL, MINHL, RINHR, MINHR, LINL, MINL, RINR, MINR bits “1”3D1-0bits “01”, “10” “11” (Refer to Table 25)(6) 3D LINHL, MINHL, RINHR, MINHR, LINL, MINL, RINR, MINR bits “1”2ms (VCOM pin 2.2µF ) PMHPL, PMHPR, MUTEN, PMLO bits “1” 3D 3D1-0bits “01”, “10” “11” 50ms PMHPL, PMHPR, MUTEN, PMLO bits “1”(7) MUTET pin (C) VCOM/2(t r ) 70k x C(typ) C=1µF t r 70ms(typ)(8) MUTET pin (C) VCOM/2(t f ) 60k x C(typ) C=1µF t f 60ms(typ)PMHPL, PMHPR bits “0” LINHL, MINHL, RINHR, MINHR, LINL, MINL, RINR, MINR bits “0” (9) PMLO bit LOUT, ROUT pins。

兵子脉冲变资料

变压器・KCB 系列可控硅触发变压器62.KCB2410G“BingZi 兵字”/传递品质安全典范31PS5 2 4 脚悬空Vp (kV) 8 8 8 fp (Hz) 100 100 100 ∫udt (µVs) 3200 6000 9600 V1 (V) 8 15 24 tn (µs) 400 400 400 V2 (V) 6 6 6 RL (Ω) 7 7 7型号 KCB2410G-1 KCB2410G-2 KCB2410G-3u 1:1 2:1 3:1触发方式 单脉冲触发 单脉冲触发 单脉冲触发63.KCB4916G-01 73.7 63.8 53.8 55.5 47.51234876510 3041.8Ф4.2×4 M4×4 1 553.8413 8 2,4,6,7 不用型号 KCB4916G-1 KCB4916G-2 KCB4916G-3 u 1:1 2:1 3:1 Vp (kV) 20 20 20 触发方式 脉冲串触发 脉冲串触发 脉冲串触发 fp (kHz) 1 3 3 ∫udt (µVs) 2000 3000 3600 V1 (V) 10 15 24 tn (µs) 200 200 150 V2 (V) 8 6.8 7.2 RL (Ω) 7 7 785“BingZi 兵字”/传递品质 安全典范 59.KCB2810G变压器・KCB 系列可控硅触发变压器153 48 2,6,7 不用型号 KCB2810G-1 KCB2810G-2 KCB2810G-3u 1:1 2:1 3:1Vp (kV) 15 15 15触发方式 脉冲串触 发 脉冲串触 发 脉冲串触 发fp (kHz) 3 10 7∫udt (µVs) 1000 1080 1200V1 (V) 10 15 24tn (µs) 100 72 50V2 (V) 9 7 7RL (Ω) 7 7 760.KCB1607G 18 3 4 5 20 2 9 1 14 P S 20° Φ0.8 1 318.52 5 4 脚悬空fp (Hz) 100 100 100 ∫udt (µVs) 1200 1800 2880 V1 (V) 10 15 24 tn (µs) 120 120 120 V2 (V) 8 6.8 7.2 RL (Ω) 27 27 27型号 KCB1607G-1 KCB1607G-2 KCB1607G-3u 1:1 2:1 3:1Vp (kV) 5 5 5触发方式 单脉冲触发 单脉冲触发 单脉冲触发61.KCB1908G 21 3 4 5 21.6 2 10 1 7.5 2 5 4 脚悬空fp (Hz) 100 100 100 ∫udt (μVs) 1600 2250 3600 V1 (V) 10 15 24 tn (μs) 150 150 150 V2 (V) 8 6.8 7.2 RL (Ω) 27 27 2720°Φ1.01315PS18.5型号 KCB1908G-1 KCB1908G-2 KCB1908G-3u 1:1 2:1 3:1Vp (kV) 6 6 6触发方式 单脉冲触发 单脉冲触发 单脉冲触发84变压器・KCB 系列可控硅触发变压器56.SD-112AP“BingZi 兵字”/传递品质安全典范248ⅠⅡⅢ3 6 9 1,5,7,10 不用型号 SD-112AP u 1:1:1 Vp (kV) 2.0 触发方式 单脉冲触发 fp (Hz) 100 ∫udt (µVs) ≥800 V1 (V) 8 tn (µs) ≥100 V2 (V) 6 RL (Ω) 7 备注 线圈电感:≥10mH 线圈电阻:≤1.6Ω57.JPC50/20483 17 1 为屏蔽 2,5,6 不用tn (µs) 40 V2 (V) 9 RL (Ω) 7型号 JPC50/20u 2.5:1Vp (kV) 6触发方式 单脉冲触发fp (Hz) 300∫udt (µVs) 960V1 (V) 2458.NPC450/105947 121 为屏蔽 3,5,68,10 不用型号 NPC450/105u 4.5:1Vp (kV) 6触发方式 单脉冲触发fp (Hz) 300∫udt (µVs) 24000V1 (V) 24tn (µs) 1000V2 (V) 3.8RL (Ω) 5083“BingZi 兵字”/传递品质 安全典范 51.KCB01/K202A 52.KCB01/K201D变压器・KCB 系列可控硅触发变压器17ⅠⅡ5 9 2,3,4,5,810 不用型号 KCB01/K202A KCB01/K201D u 1:1 2:1 Vp (kV) 3.5 5 触发方式 单脉冲触发 单脉冲触发 fp (Hz) 100 100 ∫udt (µVs) 22500 8000 V1 (V) 15 20 tn (µs) 1500 400 V2 (V) 10 10 RL (Ω) 100 5053.KCB015/K201B 2 9ⅠⅡ4 7 8 号脚为空脚 1,3,5,6,8,10 不用Vp (kV) 8 fp (Hz) 300 ∫udt (µVs) 19200 V1 (V) 24 tn (µs) 800 V2 (V) 11 RL (Ω) 50型号 KCB015/K201Bu 2:1触发方式 单脉冲触发54.KCB05/K101A 55.KCB05/K201A17ⅠⅡ5 9 2,3,4,6,8 不用型号 KCB05/K101A KCB05/K201Au 1:1 2:1Vp (kV) 8.3 8.3触发方式 单脉冲触发 单脉冲触发fp (Hz) 100 100∫udt (µVs) 25000 50000V1 (V) 8 8tn (µs) 3300 6670V2 (V) 3.5 2.4RL (Ω) 7 782变压器・KCB 系列可控硅触发变压器47.KCB-06A 48.KCB-06B 49.KCB-06C“BingZi 兵字”/传递品质安全典范KCB-06A 8 5KCB-06B 8 6 58KCB-06C 7 65Ⅰ ⅡⅠ ⅡⅢⅠⅡⅢⅣ1 4 2,7 不用 3,6 悬空13 4 2,7 不用1234型号 KCB-06A KCB-06B KCB-06Cu 1:1 1:1:1 1:1:1:1Vp (kV) 3.1触发方式 单脉冲触发 脉冲串触发fp (Hz) 50 100 500∫udt (µVs) 6800 6480 6080V1 (V) 8 8tn (µs) 850 810 760V2 (V) 6 5.8 5.8RL (Ω) 750.KCB0025/K101A 1 6ⅠⅡ4 7 2,3,5,8 不用型号 KCB0025/K101A u 1:1 Vp (kV) 2 触发方式 单脉冲触发 fp (Hz) 200 ∫udt (µVs) 8500 V1 (V) 10 tn (µs) 850 V2 (V) 9.5 RL (Ω) 10081“BingZi 兵字”/传递品质 安全典范Vp (kV) 4.5 fp (HZ) 100 3000 7000 10000变压器・KCB 系列可控硅触发变压器∫udt (µVs) 300 240 200 200 V1 (V) 8 8 tn (µs) 37.50 30 25 25 V2 (V) 6.4 6.2 5.9 5.6 RL (Ω) 7型号 KCB-02A1 KCB-02B1 KCB-02Cu 1:1 1:1:1 1:1:1:1触发方式 单脉冲触发 脉冲串触发40.KCB-04A141.KCB-04B142.KCB-04CKCB-04A1 1 3KCB-04B1 1 4 59KCB-04C 10 3 6ⅠⅡⅠⅡⅢⅠⅡⅢⅣ8 6 4,5,9,10 不用型号 KCB-04A1 KCB-04B1KC B-04C u 1:1 1:1:1 1:1:1:1 Vp (kV) 4.5 触发方式 单脉冲触发 脉冲串触发 fp (Hz) 100 3000 7000 10000 ∫udt (µVs) 1600 1200 800 40083 6 9,10 不用V1 (V) 8 8 tn (µs) 200 150 100 508V2 (V) 6.2 6 6 5.81RL (Ω) 74543.KCB-05A 44.KCB-05B45.KCB-05C46.KCB-05A3KCB-05A KCB-05A3 1 31KCB-05B 4 59KCB-05C 10 36Ⅰ ⅡⅠ ⅡⅢⅠⅡⅢⅣ8 6 2,7 不用 3,6 悬空83 6 2,7 不用8145型号 KCB-05A KCB-05B KCB-05C KCB-05A3u 1:1 1:1:1 1:1:1:1 3:1Vp (kV) 4.5 8.0触发方式 单脉冲触发 脉冲串触发 脉冲串触发fp (Hz) 50 100 500 9400∫udt (µVs) 2500 2400 2000 1200V1 (V) 8 8 24tn (µs) 312.50 300 250 50V2 (V) 6 5.8 5.8 6RL (Ω) 7 780变压器・KCB 系列可控硅触发变压器“BingZi 兵字”/传递品质安全典范33.KCB418/317A 34.KCB418/503A 35.KCB04/301AM113ⅠⅡ24型号uVp (kV) 7.0 10 10触发方式 单脉冲触发KCB418/317A KCB418/503A KCB04/301AM11.5:1 1.5:1 3:1脉冲串触发 脉冲串触发 脉冲串触发fp (Hz) 100 3000 7000 10000 7000 7000∫udt (µVs) 560 500 400 320 450 1680V1 (V) 8 8 15 24tn (µs) 70 62.50 50 40 30 70V2 (V) 5.3 5.2 5 5 4 8RL (Ω) 7 7 10 036.KCB418/56928ⅠⅡ59型号 KCB418/56 9u 5:1Vp (kV) 6触发方式 脉冲串触发fp (kHz) 50∫udt (µVs) 240V1 (V) 24tn (µs) 10V2 (V) 4RL (Ω) 737.KCB-02A138.KCB-02B139.KCB-02C KCB-02A1 1 2 KCB-02B1 1 3 4 KCB-02C 8 2 57ⅠⅡⅠⅡⅢⅠⅡⅢⅣ6 5 3,4,7,8 不用 62 5 7,8 不用613479“BingZi 兵字”/传递品质 安全典范Vp (kV) 5.0 fp (Hz) 100 3000 7000 1000 0 100 3000 7000 1000 0 ∫udt (µVs) 1600 1000 400 300 1600 1000 400 300变压器・KCB 系列可控硅触发变压器V1 (V) 8 8 8 8 tn (µs) 200 125 50 37.50 200 125 50 37.50 V2 (V) 3.2 3.2 3 2.9 5.6 5.2 4.6 4.4 RL (Ω) 7型号u触发方式 单脉冲触发KCB674/864A2:1脉冲串触发 单脉冲触发KCB6743A1:16.0脉冲串触发729.KCB674/211B30.KCB674/211B1 1 3 5ⅠⅡⅢ2型号 KCB674/211B KCB674/211B1 u Vp (kV) 3.0 触发方式 单脉冲触发 2:1:1 脉冲串触发 fp (HZ) 100 3000 7000 10000 ∫udt (µVs) 3000 2100 1500 900 V1 (V) 15 154tn (µs) 200 140 100 606V2 (V) 6.6 6.4 6 5.8 RL (Ω) 2731.KCB418/311B32.KCB418/422B145ⅠⅡⅢ83 6 9,10 不用型号uVp (kV) 3.1 5触发方式 单脉冲触发KCB418/311B KCB418/422B3:1:1 2:1:1脉冲串触发 脉冲串触发fp (Hz) 100 3000 7000 10000 3000∫udt (µVs) 4000 2400 1500 1200 1200V1 (V) 24 24 24tn (µs) 166 100 62.50 50 50V2 (V) 7 6.8 6.4 6.2 10RL (Ω) 7 778变压器・KCB 系列可控硅触发变压器型号 KCB419/101S KCB419/111S KCB419/201S KCB419/211S KCB419/301S KCB419/311S u 1:1 1:1:1 2:1 2:1:1 3:1 3:1:1 Vp (kV) 5 5 5 5 5 5 触发方式 脉冲串触发 脉冲串触发 脉冲串触发 脉冲串触发 脉冲串触发 脉冲串触发“BingZi 兵字”/传递品质fp (kHz) 1 1 1 1 1 1 ∫udt (µVs) 1200 1200 2250 2250 3600 3600 V1 (V) 8 8 15 15 24 24 tn (µs) 150 150 150 150 150 150安全典范V2 (V) 6 5.8 6 5.8 6 5.8 RL (Ω) 7 7 7 7 7 7KCB420/101A KCB420/201A KCB420/301A KCB420/111BKCB420/211BKCB420/311B KCB420/111B KCB420/211B KCB420/311B 1 4 5KCB420/101A KCB420/201A KCB420/301A 2 8ⅠⅡⅠⅡⅢ4 5 1,3,6,7,不用型号 u Vp (kV) 5.0 触发方式 单脉冲触发 KCB420/101A 1:1 脉冲串触发 单脉冲触发 KCB420/111B 1:1:1 5.0 脉冲串触发 单脉冲触发 KCB420/201A 2:1 5.0 脉冲串触发 单脉冲触发 KCB420/211B 2:1:1 5.0 脉冲串触发 单脉冲触发 KCB420/301A 3:1 5.0 脉冲串触发 单脉冲触发 KCB420/311B 3:1:1 5.0 脉冲串触发 fp (HZ) 100 3000 7000 10000 100 3000 7000 10000 100 3000 7000 10000 100 3000 7000 10000 100 3000 7000 10000 100 3000 7000 10000 ∫udt (µVs) 1440 960 580 464 750 500 300 240 1280 850 500 400 1000 625 420 336 3000 2000 1200 960 2000 1300 780 620 V1 (V) 8 8 8 8 15 15 15 15 24 24 24 24 tn (µs) 180 120 72.5 58 93.75 62.5 37.5 30 85.3 56.6 33.3 26.6 66.6 41.6 28 22.4 125 83.3 50 40 133.3 86.6 52 41.383 6 2,7 不用RL (Ω) 100V2 (V) 7.3 7.2 7 6.8 6.5 6.2 6 5.8 6 5.8 5.7 5.6 5.8 5.6 5.5 5.4 6.5 6.4 6.2 6 6 5.8 5.7 5.67777727.KCB674/864A 28.KCB6743A 2 3ⅠⅡ1 4 77“BingZi 兵字”/传递品质 安全典范Vp (kV) 3.1 3.1 3.1 3.1 3.1 3.1 3.1 fp (kHz) 3 3 3 3 3 3 3变压器・KCB 系列可控硅触发变压器∫udt (µVs) 750 480 1200 400 400 750 1200 V1 (V) 15 8 24 8 8 15 24 tn (µs) 50 60 50 50 50 50 50 V2 (V) 5 3.8 5 5 5.8 5 5 RL (Ω) 50 50 50 50 50 50 50型号 KCB473/065B KCB473/951A KCB473/301A KCB473/101A KCB473/104B KCB473/211B KCB473/311Bu 2.3:1 2:1 3:1 1:1 1:1:1 2:1:1 3:1:1触发方式 脉冲串触发 脉冲串触发 脉冲串触发 脉冲串触发 脉冲串触发 脉冲串触发 脉冲串触发13.KCB419/301A Φ0.8 1 3ⅠⅡ24型号uVp (kV) 5触发方式 单脉冲触发KCB419/301A3:1脉冲串触发fp (Hz) 100 3000 7000 10000∫udt (µVs) 3000 2000 1200 960V1 (V) 24 24tn (µs) 125 83.30 50 40V2 (V) 6.5 6.4 6.2 6RL (Ω) 714.KCB419/201ATM Φ0.8 1 510Ω Ⅰ Ⅱ 3 68Ω24型号 KCB419/201ATMu 2:1Vp (kV) 3.5触发方式 脉冲串触发fp (Hz) 23000∫udt (µVs) 375V1 (V) 15tn (µs) 25V2 (V) 6.5RL (Ω) 7KCB419/101SKCB419/111SKCB419/201SKCB419/211SKCB419/301SKCB419/311S KCB419/111S KCB419/211S KCB419/311S 1 5 6KCB419/101S KCB419/201S KCB419/301S 2 10ⅠⅡⅠⅡⅢ5 6 1,3,4,7,8,9 不用 76 10 4 7 2,3,8,9 不用变压器・KCB 系列可控硅触发变压器1.KCB472/104B 2.KCB472/065B“BingZi 兵字”/传递品质 3.KCB472/951A KCB472/104B 5 3 6 KCB472/065B 1 6安全典范KCB472/951A 1 4ⅠⅡⅢⅠⅡⅠⅡ4212 5 3,4 悬空V1 (V) 8 8 10 10 8 8 tn (µs) 50 40 35 25 70 65 45 30 60 50 45 35 V2 (V) 5.6 5.4 5 4.8 4.2 4.2 4 3.8 4 3.8 3.7 3.66 3 2,5 不用RL (Ω) 7型号uVp (kV) 3.1触发方式 单脉冲触发KCB472/104B1:1:1脉冲串触发 单脉冲触发KCB472/065B2.3:13.1脉冲串触发 单脉冲触发KCB472/951A2:13.1脉冲串触发fp (Hz) 100 3000 7000 10000 100 3000 7000 10000 100 3000 7000 10000∫udt (µVs) 400 320 280 200 700 650 450 300 480 400 360 280774.KCB421/097B5.KCB421/301A KCB421/097B 1 4 6 KCB421/301A 1 5ⅠⅡⅢⅠⅡ2型号 KCB421/097B KCB421/301A u 1:1:1 3:1 Vp (kV) 3.1 3.1 触发方式 脉冲串触发 脉冲串触发 fp (Hz) 3000 3000 ∫udt (µVs) 500 1440 V1 (V) 8 2435tn (µs) 62.5 602 4 3,6 脚不用V2 (V) 6.8 6.5 RL (Ω) 50 7KCB473/065B KCB473/951A KCB473/301A KCB473/101A KCB473/104B KCB473/211B KCB473/311B KCB473/951A KCB473/301A KCB473/101A 1 4 KCB473/104B KCB472/211B KCB473/311B 5 3 6KCB473/065B 1 6ⅠⅡⅠⅡⅠⅡⅢ2 5 3,4 悬空 6 3 2,5 悬空42 751“BingZi 兵字”/传递品质 安全典范变压器・KCB 系列可控硅触发变压器2. 根据伏微秒积(∫udt)及触发脉冲的频率(fp),按已知触发脉冲的伏微秒积应小于等于该频率范围 内 KCB 触发变压器的额定伏微秒积的原则选型。

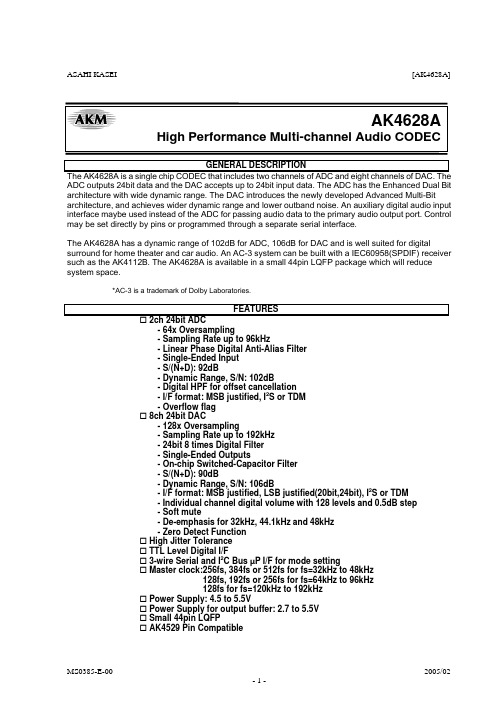

AK4628AVQ中文资料

“L”: Internal ADC output, “H”: DAUX input

SDOS pin should be set to “L” when TDM= “1”.

I Control Mode Select Pin “L”: 3-wire Serial, “H”: I2C Bus

I Soft Mute Pin

(Note 1)

When this pin goes to “H”, soft mute cycle is initialized.