帧格式头数据检测_VerilogHDL有限状态机

状态机verilog实际工程应用

状态机verilog实际工程应用

Verilog状态机在实际工程中有着广泛的应用。

状态机是一种能够根据输入信号和当前状态自动转移的逻辑电路,它可以用来描述系统的行为和控制逻辑。

在Verilog中,状态机通常使用有限状态机(FSM)来描述,可以分为Moore状态机和Mealy状态机两种类型。

在实际工程中,Verilog状态机可以应用于各种数字系统的设计,包括但不限于通信系统、控制系统、图形处理器、计算机处理器等。

下面我将从不同的角度来介绍Verilog状态机在实际工程中的应用。

1. 控制逻辑,Verilog状态机可以用于实现控制逻辑,例如在数字系统中根据特定的输入信号来控制输出信号的状态转移,比如在通信系统中根据接收到的数据来执行特定的操作。

2. 时序逻辑,状态机可以用于描述时序逻辑,例如在时序电路中根据时钟信号来执行特定的操作,比如在处理器中根据时钟信号来执行指令的译码和执行。

3. 状态转移,Verilog状态机可以描述系统中不同状态之间的

转移关系,比如在控制系统中描述不同的控制状态和状态之间的转

移条件,从而实现系统的自动控制。

4. 状态检测,状态机可以用于检测系统的状态,例如在通信系

统中可以用状态机来检测数据的传输状态,从而实现数据的接收和

发送控制。

总的来说,Verilog状态机在实际工程中有着广泛的应用,可

以用于描述系统的控制逻辑、时序逻辑、状态转移和状态检测等方面,是数字系统设计中非常重要的一部分。

通过合理的设计和实现,Verilog状态机可以帮助工程师们实现复杂的数字系统功能,提高

系统的可靠性和性能。

有限状态机的verilog例子

有限状态机的verilog例子有限状态机(Finite State Machine, FSM)是数字电路设计中的一种基本构件,它可以用来实现各种复杂的控制逻辑。

在Verilog中,可以用模块(module)来描述一个有限状态机,使用参数(parameters)来定义状态数量和状态转移逻辑。

以下是一个简单的有限状态机的Verilog例子,该FSM有3个状态(S0, S1, S2)和两个输入(clk, rst_n)以及一个输出(next_state, out):```verilogmodule fsm(input wire clk, // 时钟信号input wire rst_n, // 低电平复位信号input wire [1:0] in, // 输入信号,这里位宽为2,可以扩展output reg next_state, // 下一状态输出output reg out // 输出信号);// 状态参数parameter S0 = 2'b00;parameter S1 = 2'b01;parameter S2 = 2'b10;// 状态寄存器reg [1:0] state;// 状态转移逻辑always @(posedge clk or negedge rst_n) beginif (!rst_n) begin// 当处于复位状态时,状态寄存器和输出都初始化为0state <= S0;out <= 1'b0;end else begin// 根据当前状态和输入信号,更新下一状态和输出case (state)S0: beginnext_state <= S1;out <= 1'b1;endS1: beginnext_state <= S2;out <= 1'b0;endS2: beginnext_state <= S0;out <= 1'b1;enddefault: beginnext_state <= S0;out <= 1'b0;endendcaseendendendmodule```在这个例子中:- `clk` 是时钟信号。

基于Verilog HDL的有限状态机的优化设计

第二个进程组合逻辑 a as l y 模块的设计和二段式 的 w 设计相似 , 但是其只进行输入判断和状态转移规律描述 , 而不进行组合逻辑输出 ; 第三个进程也设计成 同步时序 a as l y 模块 ,采用同 w

步时序逻辑寄存 F M 的输出。 S

4三种状态机的逻辑、 电路 、 仿真分析

mp _t a e — ” jgi u uc O 一 / jg u— i s em r i / p / p t v. ” O” p/ t g r m n _ S m o

)

警

图 1 频 采集 图像 0视

图 8内核启动前加载摄 像头驱 动信息

不管你在何时插入 , 以上信息之一都表明 , 出现 摄像

头驱动加载成功 。驱动加载成功后 同时会在 /e dv目录下 产生一个 v eO i o 的设备节点 。 l命令可 以查看 , 图 9 d 用 s 如

所示 。

一

检验所设计 的 F M 的完备性 ,如果所设 计 的 F M不完 S S 备, 则会进入任意状态 , 仿真时很容易发现。

33三段式(h e — l y ) - T re awa s状态机 三段式状态机的设计 即使用三个进程对状态机进行 描述。第一个 a as l y 模块使用 同步时序描述状态之间的 w 转移 ; 第二个 a as l y 模块使用组合逻辑判 断状 态转移条 w 件, 描述状态转移规律 ; 第三个 a as l y 模块采用同步时序 w

成了远程视频数据 的采集 ,为整个 网络智能家居监控 系

统的实现打下了基础 。

摄像头被驱动后 ,需要编写一个对视频流采集 的应

用程序。 系统 中采用的是 m pg s em, 本 je—t a 这是一个视频 r 流服务器 , 里面有对整个视频采集及处理发送 的过程 。 首 先要 将其移植 到 目标板 上 , 也就 是 ¥ C 4 0平 台 , 3 24 并在 目标板上运行此视频流服务器 , 命令如下 :

verilog有限状态机的设计

习

题

8

8.5 设计一个汽车尾灯控制电路。已知汽车左右两侧各 有3个尾灯,要求控制尾灯按如下规则亮灭。 (1)汽车沿直线行驶时,两侧的指示灯全灭; (2)右转弯时,左侧的指示灯全灭,右侧的指示灯按 000,100,010,001,000循环顺序点亮; (3)左转弯时,右侧的指示灯全灭,左侧的指示灯按与 右侧同样的循环顺序点亮; (4)如果在直行时刹车,两侧的指示灯全亮;如果在转 弯时刹车,转弯这一侧的指示灯按上述的循环顺序点 亮,另一侧的指示灯全亮。

always @(state) /*该过程产生输出逻辑*/ begin case(state) S3: z=1'b1; default:z=1'b0; endcase end endmodule

“101”序列检测器(单过程描述)

module fsm4_seq101(clk,clr,x,z); input clk,clr,x; output reg z; reg[1:0] state; parameter S0=2'b00,S1=2'b01,S2=2'b11,S3=2'b10; /*状态编码,采用格雷(Gray)编码方式*/ always @(posedge clk or posedge clr) Begin if(clr) state<=S0; //异步复位,s0为起始状态 else case(state) S0:begin if(x) begin state<=S1; z=1'b0;end else begin state<=S0; z=1'b0;end end S1:begin if(x) begin state<=S1; z=1'b0;end else begin state<=S2; z=1'b0;end end S2:begin if(x) begin state<=S3; z=1'b0;end else begin state<=S0; z=1'b0;end end S3:begin if(x) begin state<=S1; z=1'b1;end else begin state<=S2; z=1'b1;end end default:begin state<=S0; z=1'b0;end /*default语句*/ endcase end endmodule

FPGA Verilog HDL 设计实例系列连载--------有限状态机设计

数字系统有两大类有限状态机(Finite State Machine,FSM):Moore状态机和Mealy 状态机。

Moore状态机其最大特点是输出只由当前状态确定,与输入无关。

Moore状态机的状态图中的每一个状态都包含一个输出信号。

这是一个典型的Moore状态机的状态跳转图,x、y、z是输入,a、b、c是输出。

Mealy状态机它的输出不仅与当前状态有关系,而且与它的输入也有关系,因而在状态图中每条转移边需要包含输入和输出的信息。

状态编码数字逻辑系统状态机设计中常见的编码方式有:二进制码(Binary码)、格雷码(Gray 码)、独热码(One-hot码)以及二一十进制码(BCD码)。

格雷码的特点:相邻的两个码组之间仅有一位不同。

普通二进制码与格雷码之间可以相互转换。

二进制码转换为格雷码:从最右边一位起,一次与左边一位“异或”,作为对应格雷码该位的值,最左边的一位不变(相当于最左边是0)。

格雷码转换为二进制码:从左边第二位起,将每一位与左边一位解码后的值“异或”,作为该解码后的值(最左边的一位依然不变)。

独热码又分为独热1码和独热0码,是一种特殊的二进制编码方式。

当任何一种状态有且仅有一个1时,就是独热1码,相反任何一种状态有且仅有一个0时,就是独热0码。

状态机的描述状态机有三种描述方式:一段式状态机、两段式状态机、三段式状态机。

下面就用一个小例子来看看三种方式是如何实现的。

(各种图片,各种坑爹啊 - -!)一段式状态机当把整个状态机卸载一个always模块中,并且这个模块既包含状态转移,又含有组合逻辑输入/输出时,称为一段式状态机。

不推荐采用这种状态机,因为从代码风格方面来讲,一般都会要求把组合逻辑和时序逻辑分开;从代码维护和升级来说,组合逻辑和书序逻辑混合在一起不利于代码维护和修改,也不利于约束。

1.//一段式状态机来实现:在异步复位信号的控制下,一段式状态机进入IDLE2.//状态,q_sig4被复位,一旦sig1或者sig2有效,状态机进入WAIT状态,如果3.//sig1和sig2同时有效,那么状态机进入DONE状态,4.//如果sig4还有效,那么q_sig4置位,同时状态机进入IDLE状态。

Verilog HDL代码描述对状态机综合的研究

1 引 言 V ro D elg L作为当今 国际主流的 H L语 言, 芭片的前 i H D 在 =

端 设计 中有着 广 泛 的应 用 。它 的 语 法 丰 富 , 功 地 应 用 于设 成

第 一 , 态 机要 安全 , 指 F M 不 会 进 入 死 循 环 , 别 是 状 是 S 特

应该是 : 在满足设计 时序 要求( 含对设计最 高频 率的要求) 包 的前提下 , 占用最小的芯 片面积 , 或者 在所规定 的面积下 , 使

设计 的时序余量更大 , 频率更高。另外 , 如果要求 F M安全 , S

则很多时候 需要使用“u ae 的编码 方式 , fls ” lc 即将状态转 移变 量的所有向量组合情况都在 F M 中有相应 的处理 , S 这经常势

计的各个 阶段 : 建模 、 真 、 仿 验证 和综合等 。可综 合是指综 合 工具能将 V ro D e l H L代码转换成标 准的门级结构 网表 , ig 因此 代码的描述必须符合一定的规则 。大部分数字系统都可以分 为控制单元和数据单元两个 部分 , 控制单 元的主体是 一个状

态机 , 它接收外部信号 以及数据单元 产生的状态信 息, 产生控

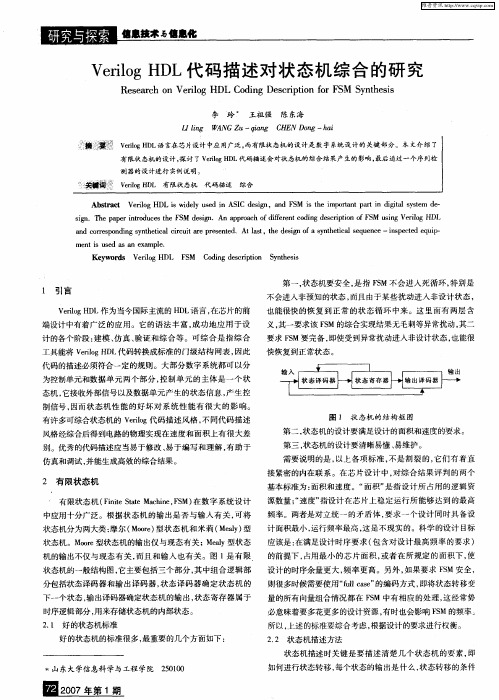

分包括状态译码器 和输 出译码器 , 状态译码器 确定状态机 的 下一个状态 , 输出译码器确定状态机 的输 出, 状态 寄存 器属于

时序逻辑部分 , 用来存储状态机 的内部状态 。

计 面积 最 小 , 行频 率 最 高

状态机 。M r 型状态机 的输出仅与现态 有关 ;M a oe e y型状态 l 机的输 出不仅 与现态有关 , 而且和输入 也有关。图 1 是有 限 状态机 的一般结构 图, 它主要包括三个部分 , 中组合 逻辑部 其

Verilog-HDL入门基础之时序状态机的设计精选全文完整版

可编辑修改精选全文完整版时序状态机的设计入门与提高计算机及具有存储器或按照所存储信息执行一系列操作的其他数字系统统称为“时序状态机”,其电路可以通过时序逻辑进行建模。

时序状态机的性能与组合逻辑不同,因为时序状态机的输出不仅仅取决于当前的输入值,而且取决于历史的输入值。

时序状态机被广泛应用于需要指定顺序操作的应用中。

所有的时序状态机都具有如图的通用反馈结构,在这种结构中时序状态机的下一状态是由当前状态和当前输入一起形成的:时序状态机可以按是否受一个公共的时钟控制(钟控)分为同步状态机和异步状态机;根据状态数目是否有限分为有限状态机和无限状态机。

此处只讨论有限状态机。

有限状态机的(FSM)分类有限状态机有米利(Mealy)机和摩尔(Moore)机:米利(Mealy)机:米利(Mealy)机的下一状态和输出都取决于当前状态和当前输入。

摩尔(Moore)机:摩尔(Moore)机的下一状态取决于当前状态和当前输入,而输出仅仅取决于当前状态。

有限状态机常用的描述、开发方法有限状态机可以借助时序图、状态表、状态图以及ASM图进行系统的描述与设计。

•时序图可以用于说明系统中及系统与周围环境的接口中信号的有效输入与状态转移之间的关系。

•状态表与状态转移表以表格的形式表示在当前状态和输入的各种组合下状态机的下一状态和输出•状态转移图(STG)是一种有向图,图中带有标记的节点或顶点与时序状态机的状态一一对应。

当系统处于弧线起点的状态时,用有向边或弧线表示在输入信号的作用下可能发生的状态转移。

米利机STG的顶点用状态进行标记,状态转移图的有向边有下面两种标记方法:(1)用能够导致状态向指定的下一状态转移的输入信号来标记(2)在当前状态下,用输入信号的输出来进行标记摩尔机的状态转移图与米利机相类似,但它的输出是由各状态的顶点来表示的,而不是在弧线上表示•算法状态机(ASM)图是时序状态机功能的一种抽象,是模拟其行为特性的关键工具。

基于Verilog HDL的有限状态机设计与描述

不会 进 入 死 循 环 , 使 由于 某 些 扰 动 进 入 非 法 状 态 , 能 很 快 即 也

的恢 复 到 正 常 的 状 态 循 环 中来 。

能 力 , 系统 在 系 统 级 或 寄 存 器 传 输 级 进 行 描 述 。 对

限状 态 机 已经 成 为关 键 。 传 统 的 有 限 状 态 机 的 描 述 方 式 有 状 态 转 移 图 , 态 转 移 状

图 1 有 限状 态机 结 构

() 限状 态 机 要 安 全 , 定 性 高 。这 就 要求 有 限 状 态 机 1有 稳

列 表 两 种 。随着 E A 技 术 的发 展 , 们 开 始 用 硬 件 描 述 语 言 D 人

sye n ei gHDL d srpin f S r to u e , s bl , ra a it, s e da dae fh s ls ed srb d Fn l , tls dV rl a o ecit s F M fei rd c d t it o o i n a i y e d bl i y p e rao tees e e c e . ial n y t r a i y

维普资讯

第 2 卷 第 4 9 期

VO . 9 12 N O. 4

计 算机 工 程 与设 计

Co mp t rE g n e n n sg u e n i e r g a d De in i

20 年 2 08 月

F b.2 0 e 0 8

文章编号 :0 072 20 ) 40 5 —3 10 —04(0 8 0 —9 80

De in a dd s rp in o n t tt c i eb s d o e i gHDL sg n e c t f i saema h n a e nv r o i o i f e l

使用Verilog进行硬件描述

使用Verilog进行硬件描述硬件描述语言(Hardware Description Language,简称HDL)是专门用于描述数字电路的语言,其中Verilog是一种常用的HDL。

本文将介绍如何使用Verilog进行硬件描述。

一、Verilog简介Verilog是一种硬件描述语言,用于描述和设计数字电路。

它具有丰富的语法和功能,可以灵活地描述各种类型的电路。

Verilog分为Verilog HDL和Verilog-A两种,本文主要介绍Verilog HDL。

二、Verilog的基本语法1. 模块声明Verilog中,通过使用`module`关键字进行模块声明。

模块由输入(Input)、输出(Output)和内部信号(Wire)组成。

例如:```module adder(input a, input b, output sum);// 模块的具体实现endmodule```2. 信号赋值Verilog中,使用`assign`关键字进行信号赋值。

例如:```assign sum = a + b;```3. 运算符Verilog支持各种运算符,包括算术运算符(+、-、*、/)、比较运算符(>、<、==、!=)和逻辑运算符(&&、||、!)。

例如:```assign c = a & b;```4. 时钟信号在Verilog中,时钟信号通常使用`always`关键字进行描述。

例如:```always @(posedge clk)begin// 在时钟上升沿执行的操作end```三、Verilog的应用1. 组合逻辑电路Verilog可以用于描述各种组合逻辑电路,如加法器、多路选择器等。

例如,下面的代码描述了一个4位全加器:```module full_adder(input a, input b, input c_in, output sum, output c_out);assign sum = a ^ b ^ c_in;assign c_out = (a & b) | (b & c_in) | (a & c_in);endmodule```2. 时序逻辑电路Verilog还可以描述时序逻辑电路,如触发器、时钟分频器等。

verilog 状态机写法

verilog 状态机写法Verilog是一种硬件描述语言,常用于设计和开发数字电路和系统。

在Verilog中,状态机是一种常用的建模方法,用于描述系统的状态和状态转移。

Verilog的状态机可以使用不同的写法来实现,通常有两种主要的方法:行为级描述和结构级描述。

行为级描述是一种以状态转移的逻辑和状态转移的条件为基础的写法。

在行为级描述中,我们需要定义状态变量和状态转移条件,然后使用if-else语句来实现状态转移逻辑。

以下是一个简单的例子,使用行为级描述写法实现一个简单的二进制计数器状态机:```verilogmodule binary_counter(input clk,input reset,output reg [3:0] count);reg [3:0] next_count;always @(posedge clk or posedge reset) beginif (reset) begincount <= 4'b0000;end else begincase (count)4'b0000: next_count = 4'b0001;4'b0001: next_count = 4'b0010;4'b0010: next_count = 4'b0011;4'b0011: next_count = 4'b0100;4'b0100: next_count = 4'b0101;4'b0101: next_count = 4'b0110;4'b0110: next_count = 4'b0111;4'b0111: next_count = 4'b1000;4'b1000: next_count = 4'b1001;4'b1001: next_count = 4'b0000;default: next_count = 4'b0000;endcasecount <= next_count;endendendmodule```在上面的例子中,我们定义了一个4位的计数器变量`count`,并在always块中定义了状态转移逻辑。

verilog状态机

基于Verilog应用2007-09-18 16:25:19 来源:电子技术应用关键字:可编程逻辑器件Verilog HDL FIFO FSM随着数字时代的到来,数字技术的应用已经渗透到了人类生活的各个方面。

数字系统的发展在很大程度上得益于器件和集成技术的发展,著名的摩尔定律(Moore's Law)的预言也在集成电路的发展过程中被印证了,数字系统的设计理念和设计方法在这过程中发生了深刻的变化。

从电子CAD、电子CAE到电子设计自动化(EDA),随着设计复杂程度的不断增加,设计的自动化程度越来越高。

目前,EDA技术作为电子设计的通用平台,逐渐向支持系统级的设计发展;数字系统的设计也从图形设计方案向硬件描述语言设计方案发展。

可编程器件在数字系统设计领域得到广泛应用,不仅缩短了系统开发周期,而且利用器件的现场可编程特性,可根据应用的要求对器件进行动态配置或编程,简单易行地完成功能的添加和修改。

在现代工业的发展中,实时测控系统得到广泛应用,这就对高速数字信号处理系统提出了更高的要求。

因为要涉及大量的设计,为了提高运算速度,应用了大量DSP器件。

数字采集系统是整个系统的核心部分之一,传统方法是应用MCU或DSP通过软件控制数据采集的模/数转换,这样必将频繁中断系统的运行从而减弱系统的数据运算,数据采集的速度也将受到限制。

因此,DSP+CPLD的方案被认为是数字信号处理系统的最优方案之一,由硬件控制模/数转换和数据存储,从而最大限度地提高系统的信号采集和处理能力。

1 系统总体方案数据采集系统是基于DSP的信号处理系统中的一部分。

框图如图1所示。

该数字信号处理系统用于随机共振理论在弱信号检测中的应用研究中。

整个系统由信号放大、信号滤波、信号采样、高速数字信号处理、与主计算机的高速数据传输接口等部分组成。

其中,信号放大是对输入信号进行调理以满足采样的要求;信号滤波是防止信号产生“混叠现象”;信号采样是完成模拟信号的数字化;高速数字信号处理是在建立随机共振模型的基础上完成各种算法;与主计算机的高速数据传输接口是满足信号检测的实时性,将DSP处理的数据传给计算机以进行进一步的处理。

有限状态机的Verilog设计与研究

谢谢观看

end

endcase

end

end

endmodule

该有限状态机使用三个寄存器来存储当前的状态,并在每个时钟周期检查输入 信号和当前状态来确定下一个状态。如果接收到读取信号,它将输出与输入相 同的数据,并在下一个时钟周期回到空闲状态。如果接收到写入信号,它也会 输出与输入相同的数据,并在下一个时钟周期回到空闲状态。该有限状态机的 设计是可综合的,因为它只包含基本的逻辑门和触发器,并且它的输出只依赖 于当前的状态和输入信号。

end else begin state <= STANDBY;

end

end

endcase

end

end

assign led = state;

endmodule

有限状态机的测试

为了确保有限状态机的正确性,需要对Verilog设计的有限状态机进行测试。 以下是测试过程中需要注意的几点:

end else begin state <= IDLE;

end

end

FLASH: begin

if (flash_timeout) begin state <= STANDBY;

end else begin state <= FLASH;

end

end

STANDBY: begin

if (activate) begin state <= FLASH;

有限状态机的Verilog设计与研究

01 引言

目录

02 有限状态机的设计

03 reg [1:0] state;

05

end else begin

04

if (rst) begin

06

Verilog 的有限状态机

基于Verilog HDL的有限状态机1.有限状态机1.1 概述有限状态机是指输出取决于过去输入部分和当前输入部分的时序逻辑电路。

有限状态机又可以认为是组合逻辑和寄存器逻辑的一种组合。

状态机特别适合描述那些发生有先后顺序或者有逻辑规律的事情,其实这就是状态机的本质。

状态机就是对具有逻辑顺序或时序规律的事件进行描述的一种方法在实际的应用中根据状态机的输出是否与输入条件相关,可将状态机分为两大类,即摩尔 (Moore)型状态机和米勒 (Mealy) 型状态机。

图 1Mealy型状态转移图1.2 状态机的描述方法状态机的描述方法多种多样,将整个状态机写到1个always 模块里,在该模块中既描述状态转移,又描述状态的输入和输出,这种写法一般被称为一段式FSM 描述方法;还有一种写法是使用两个always模块,其中一个always 模块采用同步时序的方式描述状态转移,而另一个模块采用组合逻辑的方式判断状态转移条件,描述状态转移规律,这种写法被称为两段式FSM 描述方法;还有一种写法是在两段式描述方法的基础上发展而来的,这种写法使用3 个always模块,一个always 模块采用同步时序的方式描述状态转移,一个采用组合逻辑的方式判断状态转移条件,描述状态转移规律,第三个always 模块使用同步时序电路描述每个状态的输出,这种写法称为三段式写法。

1.3 FSM的状态编码二进制码(Binary)和格雷码(Gray)属于压缩状态编码,这种编码的优点是使用的状态向量最少,但是需要较多的逻辑资源用来状态译码。

二进制码从一个状态转换到相邻状态时,可能有多个比特位发生变化,易产生中间状态转移问题,状态机的速度也要比采用其它编码方式慢。

格雷码两个相邻的码值仅有一位就可区分,这将会减少电路中相邻物理信号线同时变化的情况,因而可以减少电路中的电噪声。

Johnson码也有同样的特点,但是要用较多的位数。

独热码(One-hot)指对任意给定的状态,状态寄存器中只有l位为1,其余位都为0。

verilog 解析协议

verilog 解析协议Verilog是一种硬件描述语言(HDL),用于描述数字电路的行为和结构。

它通常用于设计和验证集成电路(IC)和系统级芯片(SoC)。

在Verilog中解析协议可以有多种方式,以下是几个常见的方法:1. 状态机,使用Verilog的状态机来解析协议是一种常见的方法。

通过定义不同的状态和状态转移条件,可以实现对协议的解析和处理。

状态机可以根据接收到的数据和协议规范进行状态转移,从而实现协议解析。

2. 位操作,Verilog提供了位操作的功能,可以对数据进行位级操作。

通过定义位字段和位掩码,可以提取和比较特定的位,从而解析协议。

位操作可以用于解析协议中的标志位、地址位、数据位等。

3. 有限状态机(FSM),有限状态机是一种常见的协议解析方法,可以使用Verilog来实现。

FSM通过定义不同的状态和状态转移条件来解析协议。

每个状态表示协议解析的不同阶段,状态之间的转移表示协议解析的流程。

4. 串行通信协议解析器,对于串行通信协议(如UART、SPI、I2C等),可以使用Verilog实现专门的解析器。

解析器可以根据协议规范对串行数据进行解析,提取有效信息并进行处理。

5. 高级协议解析器,对于复杂的高级协议(如以太网、USB、PCIe等),Verilog可能不是最合适的选择。

这种情况下,可以使用其他工具或语言(如C/C++、Python等)来实现协议解析器,并与Verilog进行接口交互。

总结起来,Verilog可以通过状态机、位操作、有限状态机等方式来解析协议。

具体的解析方法取决于协议的复杂性和Verilog 的功能。

在设计和实现协议解析时,需要仔细分析协议规范,并根据需要选择合适的解析方法。

帧格式头数据检测_VerilogHDL有限状态机

题目1:串行通讯中,经常要检测数据包的开始标志,例如:USB 数据包的起始数据是8‘b00101010设计一个电路,能够检测串行数据流中的特殊数据串,并在数据串有效时,给出相应的指示信号;(1)RTL Code/*信号定义与说明Clk:同步时钟rstb: 异步复位信号,低电平复位up_down: 加/减计数方向控制信号,1为加计数Din:串行数据输入pat_det: 检测结果输出*/`timescale 1ns/1nsmodule serialdata(din,clk,rstb,pat_det);input clk,rstb;input din;output pat_det;parameter S0='d0,S1='d1,S2='d2,S3='d3,S4='d4,S5='d5,S6='d6,IDLE='d7;reg[2:0] state;assign pat_det=(state= =S6&&din= =0)?1:0;always@(posedge clk or negedge rstb)beginif(!rstb) state<=IDLE;elsebegincase(state)IDLE:beginif(din==0) state<=S0;else state<=IDLE;endS0:beginif(din==0) state<=S1;else state<=IDLE;endS1:beginif(din==1) state<=S2;else state<=S1;endS2:beginif(din==0) state<=S3;else state<=IDLE;endS3:beginif(din==1) state<=S4;else state<=S1;endS4:beginif(din==0) state<=S5;else state<=IDLE;endS5:beginif(din==1) state<=S6;else state<=S1;endS6: state<=IDLE;default: state<=IDLE;endcaseendendendmodule(2)Test File`timescale 1ns/1ns`include "serialdata.v"module tb_serialdata;reg clk,rstb;wire din;wire pat_det;reg[31:0] data;assign din=data[31];serialdata t1(din,clk,rstb,pat_det);initial beginclk=1'b0;rstb=1'b0;data=32'b1001_0010_1010_1100_1010_1000_1010_1010;#10 rstb=1'b1;#640 $stop;endalways@(posedge clk)begindata <={data[30:0],data[31]};endalways #5 clk=~clk;endmodule(3)波形与说明图示标注地方每个上升沿取得数据din,当检测到00101010之后输出pat_det 置为高电平。

利用veriloghdl设计状态机

利用V e r i l o g H D L设计状态机(共4页)--本页仅作为文档封面,使用时请直接删除即可----内页可以根据需求调整合适字体及大小--利用Verilog HDL设计状态机1.设计要求利用Verilog HDL设计一个电路,对输入的一串二进制数,用于检测序列中连续3个或者3个以上的1,状态转换如图所示:2.设计步骤第一步:安装Quartus II软件并破解第二步:根据设计要求编写程序代码第三步:生成仿真电路图和波形如图3.程序代码module moore(clk,din,op);input clk,din;output op;reg[1:0] current_state,next_state;reg op;parameter S0=2'b00,S1=2'b01,S2=2'b10,S3=2'b11;always@(posedge clk)begincurrent_state<=next_state; endalways@(current_state or din) begincase(current_state)S0:beginop=0;if(din==0)next_state=S0;elsenext_state=S1; endS1:beginop=0;if(din==0)next_state=S0;elsenext_state=S2; endS2:beginop=0;if(din==0)next_state=S0;elsenext_state=S3; endS3:beginop=1;if(din==0)next_state=S0;elsenext_state=S3; enddefault:beginop=0;next_state=S0;endendcaseendendmodule4.仿真电路图和波形图电路图如下图:图一电路原理图图二转换关系图波形图如下图:波形图5.实验结论与心得体会实验结果:由仿真波形可以看出,利用该状态机,可以实现输入一串二进制数然后检测序列中连续3个或者3个以上的1,实现上面转换图要求的功能,符合实验要求。

fpga 有限状态机例子

fpga 有限状态机例子有限状态机(Finite State Machine,FSM)是一种常见的设计模式,用于描述和实现具有有限数量状态的对象的行为。

在硬件设计中,有限状态机常常用于描述数字逻辑电路的行为。

以下是一个使用Verilog语言编写的简单有限状态机的例子:verilog复制代码module counter(input clk, reset, output reg [3:0] count);// 定义状态机的状态parameter IDLE = 4'b0000; // 初始状态parameter COUNTER = 4'b0001; // 计数状态// 状态机的当前状态reg [3:0] current_state;// 状态转移逻辑always @(posedge clk or posedge reset) begin if (reset) begincurrent_state <= IDLE; // 如果reset信号为高,则进入IDLE状态end else begincase (current_state)IDLE: beginif (count == 4'b1000) current_state <= COUNTE R; // 如果计数达到8,则进入COUNTER状态endCOUNTER: begincurrent_state <= IDLE; // 在COUNTER状态下,计数完成后回到IDLE状态enddefault: begincurrent_state <= IDLE; // 如果状态机处于未知状态,则强制回到IDLE状态endendcaseendend// 计数逻辑always @(posedge clk) beginif (current_state == COUNTER) count <= count + 1; // 在COUNTER状态下,计数器递增endendmodule在这个例子中,我们定义了一个简单的4位计数器。

基于Verilog HDL的有限状态机设计与描述

基于Verilog HDL的有限状态机设计与描述

刘小平;何云斌;董怀国

【期刊名称】《计算机工程与设计》

【年(卷),期】2008(029)004

【摘要】有限状态机(FSM)是逻辑设计的重要内容,稍大一点的逻辑设计都存在FSM.介绍了采用Verilog HDL实现有限状态机的几种不同编码方式和描述风格,并从稳定性、可读性、速度和面积等方面比较了不同实现方式的利弊.最后,以简单序列检测器为例实现了可综合的FSM描述,并分析了其采用不同描述风格所得的综合结果.

【总页数】3页(P958-960)

【作者】刘小平;何云斌;董怀国

【作者单位】哈尔滨理工大学计算机学院,黑龙江,哈尔滨,150080;哈尔滨理工大学计算机学院,黑龙江,哈尔滨,150080;哈尔滨理工大学计算机学院,黑龙江,哈尔

滨,150080

【正文语种】中文

【中图分类】TP302

【相关文献】

1.基于Verilog HDL的有限状态机的优化设计 [J], 罗翔;李娇龙;田正凯

2.基于Verilog HDL的MTM总线主模块有限状态机设计 [J], 陈星;黄考利;连先耀;王振生

3.基于Verilog HDL的有限状态机设计 [J], 方洪浩;雷蕾;常何民

4.基于Verilog HDL的可综合有限状态机设计 [J], 魏芳;刘志军;王立华

5.基于Verilog HDL描述的10M/100Mbps以太网卡设计模块的测试方案 [J], 赵江华;吴建军;邹雪城;邹连英;何莹

因版权原因,仅展示原文概要,查看原文内容请购买。

verilog帧差法 -回复

verilog帧差法-回复什么是Verilog帧差法,它在图像处理中的应用有哪些?Verilog帧差法(Verilog Frame Difference Method)是一种常见的视频帧处理方法,主要用于图像中运动目标的检测与跟踪。

它通过比较连续视频帧之间的像素差异来确定图像中发生的运动。

Verilog帧差法在实时视频监控、视频分析、智能交通系统等领域中得到了广泛的应用。

首先,Verilog帧差法需要明确输入源。

输入源可以是摄像机捕获的实时视频数据、图像序列或者预先存储的视频文件。

这些输入源必须包含连续的视频帧,以便进行比较和处理。

其次,Verilog帧差法使用了基于2D图像的运动目标检测算法。

它的核心思想是通过计算相邻帧之间的差异,来确定像素中的运动。

算法首先将输入源的连续帧转化为灰度图像,并将其存储在内存中。

然后,通过比较相邻帧的像素值,可以计算出像素之间的差异。

这些差异将用于检测和跟踪图像中的运动目标。

Verilog帧差法的关键步骤包括:1. 将连续帧转化为灰度图像:为了降低计算复杂度,通常会将连续的彩色帧转化为灰度图像。

这可以通过简单地计算每个像素的加权平均值来实现。

灰度图像存储在内存中,以便后续的比较和处理。

2. 计算相邻帧之间的像素差异:对于每个像素,通过减去前一帧的像素值,可以计算出其与前一帧的差异。

这些差异将用于检测和跟踪图像中的运动目标。

差异可以通过计算每个差异像素的绝对值、平方值或其他形式的计算来表示。

3. 运动目标检测与跟踪:根据计算得到的差异,可以采用阈值处理方法来确定图像中发生的运动。

通过设置合适的阈值,可以筛选出差异较大的像素,代表图像中的运动目标。

这些像素可以形成连通区域或包围框,用于指示目标物体的位置和形状。

通过跟踪连续帧之间差异的变化,可以实现运动目标的跟踪。

Verilog帧差法的优点是简单、易于实现,并且在实时视频处理应用中具有较高的效率。

它可以用于实时监控、运动检测、行人跟踪、目标跟踪、车辆计数、智能交通流量统计等领域。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

题目1:串行通讯中,经常要检测数据包的开始标志,例如:USB 数据包的起

始数据是8‘b00101010设计一个电路,能够检测串行数据流中的特殊数据串,并在数据串有效时,给出相应的指示信号;

(1)RTL Code

/*信号定义与说明

Clk:同步时钟

rstb: 异步复位信号,低电平复位

up_down: 加/减计数方向控制信号,1为加计数

Din:串行数据输入

pat_det: 检测结果输出

*/

`timescale 1ns/1ns

module serialdata(din,clk,rstb,pat_det);

input clk,rstb;

input din;

output pat_det;

parameter S0='d0,S1='d1,S2='d2,S3='d3,S4='d4,S5='d5,S6='d6,IDLE='d7;

reg[2:0] state;

assign pat_det=(state= =S6&&din= =0)?1:0;

always@(posedge clk or negedge rstb)

begin

if(!rstb) state<=IDLE;

else

begin

case(state)

IDLE:

begin

if(din==0) state<=S0;

else state<=IDLE;

end

S0:

begin

if(din==0) state<=S1;

else state<=IDLE;

end

S1:

begin

if(din==1) state<=S2;

else state<=S1;

end

S2:

begin

if(din==0) state<=S3;

else state<=IDLE;

end

S3:

begin

if(din==1) state<=S4;

else state<=S1;

end

S4:

begin

if(din==0) state<=S5;

else state<=IDLE;

end

S5:

begin

if(din==1) state<=S6;

else state<=S1;

end

S6: state<=IDLE;

default: state<=IDLE;

endcase

end

end

endmodule

(2)Test File

`timescale 1ns/1ns

`include "serialdata.v"

module tb_serialdata;

reg clk,rstb;

wire din;

wire pat_det;

reg[31:0] data;

assign din=data[31];

serialdata t1(din,clk,rstb,pat_det);

initial begin

clk=1'b0;

rstb=1'b0;

data=32'b1001_0010_1010_1100_1010_1000_1010_1010;

#10 rstb=1'b1;

#640 $stop;

end

always@(posedge clk)

begin

data <={data[30:0],data[31]};

end

always #5 clk=~clk;

endmodule

(3)波形与说明

图示标注地方每个上升沿取得数据din,当检测到00101010之后输出pat_det 置为高电平。

整个32位串行输入数据1001_0010_1010_1100_1010_1000_1010_1010,总共640个时间单位stop,即32位输入数据跑两遍,共输出6个高电平脉冲,符合设计!

题目2:设计一个串行数据检测器,输入数据与时钟同步。

要求是:输入连续5

个或5 个以上的1 时输出为1,其他输入情况下输出为0

(1)RTL Code

/*信号定义与说明

clk: 同步输入时钟

nreset: 复位信号,低电平有效

din: 串行数据输入

out:检测结果输出

*/

`timescale 1ns/1ns

module serialfive1(out,din,clk,nreset);

input din;

input clk,nreset;

output out;

parameter M0='d0,M1='d1,M2='d2,M3='d3,M4='d4,IDLE='d5;

reg[2:0] state;

assign out=(state==M4&&din==1)?1:0;

always @(posedge clk)

begin

if(!nreset) state<=IDLE;

else

case(state)

IDLE:

begin

if(din==1) state <= M0;

else state <= IDLE;

end

M0:

begin

if(din==1) state <= M1;

else state <= IDLE;

end

M1:

begin

if(din==1) state <= M2;

else state <= IDLE;

end

M2:

begin

if(din==1) state <= M3;

else state <= IDLE;

end

M3:

begin

if(din==1) state <= M4;

else state <= IDLE;

end

M4:

begin

if(din==1) state <= M4;

else state <= IDLE;

end

default: state <= IDLE;

endcase

end

endmodule

(2)Test File

`include "serialfive1.v"

`timescale 1ns/1ns

module tb_serialfive1;

reg clk,nreset;

wire din,out;

reg[15:0] data;

assign din=data[15];

serialfive1 t1(out,din,clk,nreset);

initial

begin

clk = 1'b0;

nreset = 1'b0;

data = 'b0111_1110_0101_1111;

#8 nreset = 1'b1;

#320 $stop;

end

always #5 clk=~clk;

always @(posedge clk)

data = {data[14:0],data[15]};

endmodule

(3)波形与说明

如图所示,输入16位串行数据0111_1110_0101_1111。

在320个时间单位跑两遍,一共输出4个高电平脉冲输出,其中一个是连续6个1,所以其维持2个clk,如图示,满足设计要求!。