ADM6711MAKS-REEL-7中文资料

MEMORY存储芯片ADM3202ARUZ-REEL7中文规格书

READ OperationREAD bursts are initiated with a READ command. The starting column and bank ad-dresses are provided with the READ command and auto precharge is either enabled or disabled for that burst access. If auto precharge is enabled, the row being accessed is automatically precharged at the completion of the burst. If auto precharge is disabled,the row will be left open after the completion of the burst.During READ bursts, the valid data-out element from the starting column address is available READ latency (RL) clocks later. RL is defined as the sum of posted CAS additive latency (AL) and CAS latency (CL) (RL = AL + CL). The value of AL and CL is programma-ble in the mode register via the MRS command. Each subsequent data-out element is valid nominally at the next positive or negative clock edge (that is, at the next crossing of CK and CK#). Figure 69 shows an example of RL based on a CL setting of 8 and an AL setting of 0.Figure 69: READ LatencyCKCK#CommandAddressDQDQS, DQS#Don’t CareTransitioning Data Indicates break in time scaleNotes:1.DO n = data-out from column n .2.Subsequent elements of data-out appear in the programmed order following DO n .DQS, DQS# is driven by the DRAM along with the output data. The initial LOW state on DQS and HIGH state on DQS# is known as the READ preamble (t RPRE). The LOW state on DQS and the HIGH state on DQS#, coincident with the last data-out element, isknown as the READ postamble (t RPST). Upon completion of a burst, assuming no other commands have been initiated, the DQ goes High-Z. A detailed explanation of t DQSQ (valid data-out skew), t QH (data-out window hold), and the valid data window are de-picted in Figure 80 (page 171). A detailed explanation of t DQSCK (DQS transition skew to CK) is also depicted in Figure 80 (page 171).Data from any READ burst may be concatenated with data from a subsequent READ command to provide a continuous flow of data. The first data element from the new burst follows the last element of a completed burst. The new READ command should be issued t CCD cycles after the first READ command. This is shown for BL8 in Figure 70(page 165). If BC4 is enabled, t CCD must still be met, which will cause a gap in the data output, as shown in Figure 71 (page 165). Nonconsecutive READ data is reflected in Figure 72 (page 166). DDR3 SDRAM does not allow interrupting or truncating any READ burst.Figure 100: Precharge Power-Down (Slow-Exit Mode) Entry and ExitCKCK#CommandCKEEnter power-downmode Exit power-downmodeDon’t CareIndicates break in time scaleNotes:1.Any valid command not requiring a locked DLL.2.Any valid command requiring a locked DLL.Figure 101: Power-Down Entry After READ or READ with Auto Precharge (RDAP)Don’t CareTransitioning Data CKCK#Command DQ BL8DQ BC4DQS, DQS#Address CKEPower-down or self refresh entryIndicates break in time scaleFigure 102: Power-Down Entry After WRITECKCK#Command DQ BL8DQ BC4DQS, DQS#AddressCKEself refresh entry1Don’t CareTransitioning Data Indicates break in time scaleNote:1.CKE can go LOW 2t CK earlier if BC4MRS.Figure 103: Power-Down Entry After WRITE with Auto Precharge (WRAP)Don’t CareTransitioning Data CKCK#CommandDQ BL8DQ BC4DQS, DQS#Address A10CKEPower-down or self refresh entry 2Start internal precharge Indicates break in time scaleNotes:1.t WR is programmed through MR0[11:9] and represents t WRmin (ns)/t CK rounded up tothe next integer t CK.2.CKE can go LOW 2t CK earlier if BC4MRS.Figure 104: REFRESH to Power-Down EntryCKCK#CommandCKET0T1T2T3Ta0Ta1Ta2Tb0Don’t CareIndicates break in time scaleNote:1.After CKE goes HIGH during t RFC, CKE must remain HIGH until t RFC is satisfied.Figure 105: ACTIVATE to Power-Down EntryCKCK#Command Address CKET0T1T2T3T4T5T6T7Figure 108: Power-Down Exit to Refresh to Power-Down EntryCKCK#CKET0T1T2T3T4Ta0Ta1Tb0Command。

FPGA可编程逻辑器件芯片AD8130ARZ-REEL7中文规格书

MAXIMUM POWER DISSIPATION (W)

02464-005

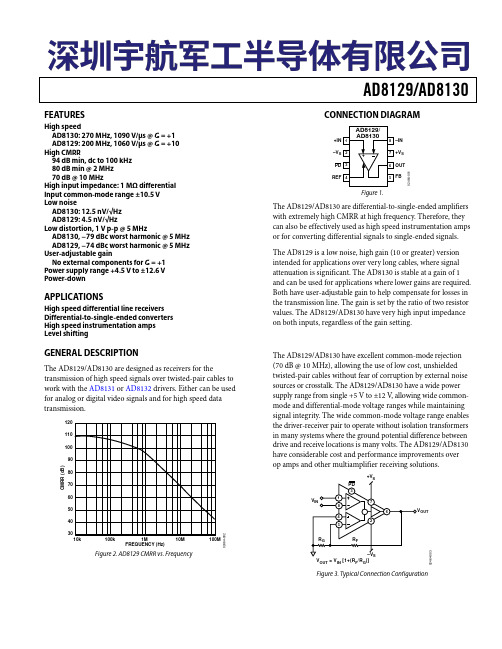

AD8129/AD8130

The power dissipated in the package (PD) is the sum of the quiescent power dissipation and the power dissipated in the package due to the load drive. The quiescent power is the voltage between the supply pins (VS) times the quiescent current (IS). The power dissipated due to the load drive depends upon the particular application. The power due to load drive is calculated by multiplying the load current by the associated voltage drop across the device. RMS voltages and currents must be used in these calculations.

+VS PD

3

1

VIN

7

8

6

4 2

5

VOUT

RG

RF

–VS VOUT = VIN [1+(RF/RG)]

Figure 3. Typical Connection Configuration

ABSOLUTE MAXIMUM RATINGS

Table 4. Parameter Supply Voltage Power Dissipation Input Voltage (Any Input) Differential Input Voltage (AD8129)

FPGA可编程逻辑器件芯片ADM202EARNZ-REEL中文规格书

ADM202E/ADM1181AFEATURESComplies with 89/336/EEC EMC directive ESD protection to IEC1000-4-2 (801.2) ±8 kV: contact discharge ±15 kV: air-gap discharge ±15 kV: human body modelEFT fast transient/burst immunity (IEC1000-4-4) Low EMI emissions (EN55022) 230 kbits/s data rate guaranteed TSSOP package optionUpgrade for MAX202E, 232E, LT1181AAPPLICATIONSGeneral-purpose RS-232 data link Portable instruments PDAsGENERAL DESCRIPTIONThe ADM202E and ADM1181A are robust, high speed, 2-channel RS-232/V .28 interface devices that operate from a single 5 V power supply. Both products are suitable for operation in harsh electrical environments and are compliant with the EU directive on EMC (89/336/EEC). Both the level of electromagnetic emissions and immunity are in compliance. EM immunity includes ESD protection in excess of ±15 kV on all I/O lines, fast transient/burst protection (1000-4-4), and radiated immunity (1000-4-3). EM emissions include radiated and conducted emissions as required by Information Technology Equipment EN55022, CISPR22.The ADM202E and ADM1181A conform to the EIA-232E and CCITT V .28 specifications and operate at data rates up to 230 kbps.Four external 0.1 µF charge-pump capacitors are used for the voltage doubler/inverter, permitting operation from a single 5 V supply.FUNCTIONAL BLOCK DIAGRAMS*INTERNAL 5k ΩPULL-DOWN RESISTOR ON EACH RS-232 INPUT10V T1T2R1R2*0.1µF 0.1µµF00066-001Figure 1.0.1µ 10V 10VT1µF T2R1R2*0.1µF 00066-002*INTERNAL 5k Ω PULL-DOWN RESISTOR ON EACH RS-232 INPUTFigure 2.The ADM202E provides a robust pin-compatible upgrade for existing ADM202, ADM232L, or MAX202E/MAX232E sockets. It is available in a 16-lead PDIP , a wide SOIC, a narrow SOIC, and a space-saving TSSOP package that is 44% smaller than the SOIC package.The ADM1181A provides a robust pin-compatible upgrade for the LTC1181A, and it is available in a 16-lead PDIP package and a wide 16-lead SOIC package.ADM202E/ADM1181A Rev. C | Page 6 of 16GENERAL DESCRIPTIONThe ADM202E/ADM1181E are rugged RS-232 linedrivers/receivers. Step-up voltage converters coupled with level-shifting transmitters and receivers allow RS-232 levels to be developed while operating from a single 5 V supply.Features include low power consumption, high transmission rates, and compliance with the EU directive on electromagnetic compatibility. EM compatibility includes protection against radiated and conducted interference, including high levels of electrostatic discharge.All inputs and outputs contain protection against electrostatic discharges of up to ±15 kV and electrical fast transients of up to ±2 kV . This ensures compliance to IEC1000-4-2 and IEC1000-4-4 requirements.The devices are ideally suited for operation in electrically harsh environments or where RS-232 cables are frequently being plugged/unplugged. They are also immune to high RF field strengths without special shielding precautions.CMOS technology is used to minimize the power dissipation, allowing maximum battery life in portable applications. The ADM202E/ADM1181A serve as a modification,enhancement, and improvement to the ADM230–ADM241 family and its derivatives. It is essentially plug-in compatible and do not have materially different applications.CIRCUIT DESCRIPTIONThe internal circuitry consists of four main sections: • A charge-pump voltage converter • 5 V logic to EIA-232 transmitters •EIA-232 to 5 V logic receivers.•Transient protection circuit on all I/O linesCharge-Pump DC-to-DC Voltage ConverterThe charge-pump voltage converter consists of a 200 kHz oscillator and a switching matrix. The converter generates a ±10 V supply from the input 5 V level. This is done in two stages, using a switched capacitor technique, as illustrated in Figure 6 and Figure 7. First, the 5 V input supply is doubled to 10 V , using Capacitor C1 as the charge storage element. The 10 V level is then inverted to generate −10 V , using C2 as the storage element. Capacitor C3 and Capacitor C4 are used to reduce the output ripple. Their values are not critical and can be increased if desired. On the ADM202E, Capacitor C3 is shown connected between V+ and V CC , whereas it is connected between V+ and GND on the ADM1181A. It is acceptable to use eitherconfiguration with both the ADM202E and ADM1181A. Ifdesired, larger capacitors (up to 47 µF) can be used forCapacitor C1 to Capacitor C4. This facilitates direct substitution with older generation charge-pump RS-232 transceivers.CCCCNOTE: C3 CONNECTS BETWEEN V+ AND GND ON THE ADM1181A00066-006Figure 6. Charge-Pump Voltage DoublerFigure 7. Charge-Pump Voltage InverterTransmitter (Driver) SectionThe drivers convert 5 V logic input levels into RS-232 output levels. When driving an RS-232 load with V CC = 5 V , the output voltage swing is typically ±9 V .Receiver SectionThe receivers are inverting level shifters that accept RS-232 input levels and translate them into 5 V logic output levels. The inputs have internal 5 kΩ pull-down resistors to ground and are also protected against overvoltages of up to ±30 V . Unconnected inputs are pulled to 0 V by the internal 5 kΩ pull-down resistor. Therefore, unconnected inputs and those connected to GND have a Logic 1 output level.The receivers have Schmitt-trigger inputs with a hysteresis level of 0.65 V . This ensures error-free reception for both noisy inputs and inputs with slow transition times.HIGH BAUD RATEThe ADM202E/ADM1181A feature high slew rates, permitting data transmission at rates well in excess of the EIA/RS-232-E specifications. RS-232 voltage levels are maintained at data rates of up to 230 kbps, even under worst case loading conditions. This allows for high speed data links between two terminals and is also suitable for the new generation ISDN modem standards, which require data rates of 230 kbps. The slew rate is internally controlled to less than 30 V/µs to minimize EMI interference.ADM202E/ADM1181ARev. C | Page 7 of 16ADM202E/ADM1181ARev. C | Page 10 of 16ESD TESTING (IEC1000-4-2)IEC1000-4-2 (previously 801-2) specifies compliance testing using two coupling methods, contact discharge and air-gap discharge. Contact discharge calls for a direct connection to the unit being tested. Air-gap discharge uses a higher test voltage, but does not make direct contact with the unit being tested. With air-gap discharge, the discharge gun is moved toward the unit being tested, developing an arc across the air gap. This method is influenced by humidity, temperature, barometric pressure, distance, and rate of closure of the discharge gun. Although less realistic, the contact-discharge method is more repeatable and is gaining preference to the air-gap method. Although very little energy is contained within an ESD pulse, the extremely fast rise time coupled with high voltages can cause failures in unprotected semiconductors. Catastrophic destruction can occur immediately as a result of arcing orheating. Even if catastrophic failure does not occur immediately, the device might suffer from parametric degradation, which can result in degraded performance. The cumulative effects of continuous exposure can eventually lead to complete failure. I/O lines are particularly vulnerable to ESD damage. Simply touching or plugging in an I/O cable can result in a static discharge, which can damage or completely destroy theinterface product connected to the I/O port. Traditional ESD test methods, such as the MIL-STD-883B method 3015.7, do not fully test a product’s susceptibility to this type of discharge. This test was intended to test a product’s susceptibility to ESD damage during handling. Each pin is tested with respect to all other pins. There are some important differences between the traditional test and the IEC test: •The IEC test is much more stringent in terms of discharge energy. The injected peak current is over four times greater. •The current rise time is significantly faster in the IEC test.•The IEC test is carried out while power is applied to the device.It is possible that the ESD discharge could induce latch-up in the device being tested. Therefore, this test is more representative of a real-world I/O discharge where the equipment is operating normally with power applied. For peace of mind, however, both tests should be performed to ensure maximum protection during both handling and field service.ESD TEST METHOD R2C1H.BODY MIL-STD883B 1.5k Ω100pF IEC1000-4-2330Ω150pF00066-018Figure 18. ESD Test StandardsI P E A K (%)00066-019Figure 19. Human Body Model ESD Current WaveformFigure 20. IEC1000-4-2 ESD Current WaveformThe ADM202E/ADM1181E products are tested using both of the previously mentioned test methods. Pins are tested with respect to all other pins as per the MIL-STD-883B specification. In addition, I/O pins are tested as per the IEC test specification. The products were tested under the following conditions: •Power-On •Power-OffThere are four levels of compliance defined by IEC1000-4-2. The ADM202E/ADM1181A products meet the most stringent level of compliance both for contact and for air-gap discharge. This means that the products are able to withstand contact discharges in excess of 8 kV and air-gap discharges in excess of 15 kV .ADM202E/ADM1181ARev. C | Page 11 of 16Table 4. IEC1000-4-2 Compliance LevelsLevel Contact Discharge Air Discharge 1 2 kV 2 kV 2 4 kV 4 kV 3 6 kV 8 kV 48 kV15 kVTable 5. ADM202E/ADM1181A ESD Test ResultsESD Test Method I/O Pins MIL-STD-883B ±15 kV IEC1000-4-2 Contact ±8 kV Air±15 kVFAST TRANSIENT/BURST TESTING (IEC1000-4-4)IEC1000-4-4 (previously 801-4) covers electrical fast transient (EFT)/burst immunity. Electrical fast transients occur as a result of arcing contacts in switches and relays. The tests simulate the interference generated when, for example, a power relaydisconnects an inductive load. A spark is generated due to the well-known back EMF effect. In fact, the spark consists of a burst of sparks as the relay contacts separate. The voltageappearing on the line, therefore, consists of a burst of extremely fast transient impulses. A similar effect occurs when switching on fluorescent lights.The fast transient/burst test defined in IEC1000-4-4 simulates this arcing, and its waveform is illustrated in Figure 17. It consists of a burst of 2.5 kHz to 5 kHz transients repeating at300 ms intervals. It is specified for both power and data lines.00066-021Figure 21. IEC1000-4-4 Fast Transient WaveformA simplified circuit diagram of the actual EFT generator is illustrated in Figure 22.The transients are coupled onto the signal lines using an EFT coupling clamp. The clamp, which is 1 m long, completelysurrounds the cable, providing maximum coupling capacitance (50 pF to 200 pF typ) between the clamp and the cable. High energy transients are capacitively coupled to the signal lines. Fast rise times (5 ns), as specified by the standard, result in very effective coupling. This test is very strenuous because high voltages are coupled onto the signal lines. The repetitive transients often cause problems where single pulses do not. Destructive latch-up can be induced due to the high energy content of the transients. Note that this stress is applied while the interface products are powered up and transmitting data. The EFT test applieshundreds of pulses with higher energy than ESD. Worst-case transient current on an I/O line can be as high as 40 A.00066-022Figure 22. IEC1000-4-4 Fast Transient GeneratorTest results are classified according to the following: •Classification 1: Normal performance within specifi- cation limits•Classification 2: Temporary degradation or loss of performance that is self-recoverable•Classification 3: Temporary degradation or loss of function or performance that requires operator intervention or system reset•Classification 4: Degradation or loss of function that is not recoverable due to damageThe ADM202E/ADM1181A meet Classification 2 and have been tested under worst-case conditions using unshielded cables. Data transmission during the transient condition iscorrupted, but can resume immediately following the EFT event without user intervention.。

ADM6713ZAKS中文资料

VCC < 3.6 V, ADM671_R/S/T/Z, TA = –40°C to +85°C VCC < 5.5 V, ADM671_L/M, TA = 85°C to 125°C

VCC < 3.6 V, ADM671_R/S/T/Z, TA = 85°C to 125°C

VCC, MR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 mA Output Current

RESET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 mA Rate of Rise, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100 V/µs JA Thermal Impedance, SC70 . . . . . . . . . . . . . . . . . 146°C/W Operating Temperature Range . . . . . . . . . . –40°C to +125°C Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C Lead Temperature (Soldering, 10 sec) . . . . . . . . . . . . . 300°C

Input Threshold

Pull-Up Resistance Minimum Pulsewidth Glitch Immunity Reset Delay

AD8310ARM-REEL7资料

Fast, Voltage-Out DC–440 MHz,95 dB Logarithmic AmplifierAD8310 Rev.EInformation furnished by Analog Devices is believed to be accurate and reliable.However, no responsibility is assumed by Analog Devices for its use, nor for anyinfringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: Fax: 781.461.3113© 2005 Analog Devices, Inc. All rights reserved.FEATURESMultistage demodulating logarithmic amplifierVoltage output, rise time <15 nsHigh current capacity: 25 mA into grounded R L95 dB dynamic range: −91 dBV to +4 dBVSingle supply of 2.7 V min at 8 mA typDC–440 MHz operation, ±0.4 dB linearitySlope of +24 mV/dB, intercept of −108 dBVHighly stable scaling over temperatureFully differential dc-coupled signal path100 ns power-up time, 1 mA sleep current APPLICATIONSConversion of signal level to decibel formTransmitter antenna power measurementReceiver signal strength indication (RSSI)Low cost radar and sonar signal processingNetwork and spectrum analyzersSignal-level determination down to 20 HzTrue-decibel ac mode for multimetersGENERAL DESCRIPTIONThe AD8310 is a complete, dc−440 MHz demodulating logarithmic amplifier (log amp) with a very fast voltage mode output, capable of driving up to 25 mA into a grounded load in under 15 ns. It uses the progressive compression (successive detection) technique to provide a dynamic range of up to 95 dB to ±3 dB law conformance or 90 dB to a ±1 dB error bound up to 100 MHz. It is extremely stable and easy to use, requiring no significant external components. A single-supply voltage of 2.7 V to 5.5 V at 8 mA is needed, corresponding to a power consumption of only 24 mW at 3 V. A fast-acting CMOS-compatible enable pin is provided.Each of the six cascaded amplifier/limiter cells has a small-signal gain of 14.3 dB, with a −3 dB bandwidth of 900 MHz.A total of nine detector cells are used to provide a dynamic range that extends from −91 dBV (where 0 dBV is defined as the amplitude of a 1 V rms sine wave), an amplitude of about ±40 μV, up to +4 dBV (or ±2.2 V). The demodulated outputis accurately scaled, with a log slope of 24 mV/dB and an intercept of −108 dBV. The scaling parameters are supply-and temperature-independent.FUNCTIONAL BLOCK DIAGRAMSUPPLY+INPUT–INPUTCOMMON184-1Figure 1.The fully differential input offers a moderately high impedance (1 kΩ in parallel with about 1 pF). A simple network can match the input to 50 Ω and provide a power sensitivity of −78 dBm to+17 dBm. The logarithmic linearity is typically within ±0.4 dBup to 100 MHz over the central portion of the range, but it is somewhat greater at 440 MHz. There is no minimum frequency limit; the AD8310 can be used down to low audio frequencies. Special filtering features are provided to support this wide range.The output voltage runs from a noise-limited lower boundary of 400 mV to an upper limit within 200 mV of the supply voltagefor light loads. The slope and intercept can be readily altered using external resistors. The output is tolerant of a wide varietyof load conditions and is stable with capacitive loads of 100 pF. The AD8310 provides a unique combination of low cost, small size, low power consumption, high accuracy and stability, high dynamic range, a frequency range encompassing audio to UHF, fast response time, and good load-driving capabilities, making this product useful in numerous applications that require the reduction of a signal to its decibel equivalent.The AD8310 is available in the industrial temperature range of−40°C to +85°C in an 8-lead MSOP package.AD8310Rev. E | Page 2 of 24TABLE OF CONTENTSSpecifications.....................................................................................3 Absolute Maximum Ratings............................................................4 ESD Caution..................................................................................4 Pin Configuration and Function Descriptions.............................5 Typical Performance Characteristics.............................................6 Theory of Operation........................................................................9 Progressive Compression............................................................9 Slope and Intercept Calibration................................................10 Offset Control.............................................................................10 Product Overview...........................................................................11 Enable Interface..........................................................................11 Input Interface............................................................................11 Offset Interface...........................................................................12 Output Interface.........................................................................12 Using the AD8310..........................................................................14 Basic Connections......................................................................14 Transfer Function in Terms of Slope and Intercept...............15 dBV vs. dBm...............................................................................15 Input Matching...........................................................................15 Narrow-Band Matching............................................................16 General Matching Procedure....................................................16 Slope and Intercept Adjustments.............................................17 Increasing the Slope to a Fixed Value......................................17 Output Filtering..........................................................................18 Lowering the High-Pass Corner Frequency of the OffsetCompensation Loop..................................................................18 Applications.....................................................................................19 Cable-Driving.............................................................................19 DC-Coupled Input.....................................................................19 Evaluation Board............................................................................20 Outline Dimensions.......................................................................22 Ordering Guide.. (22)REVISION HISTORY6/05—Rev. D to Rev. EChanges to Figure 6..........................................................................6 Change to Basic Connections Section.........................................14 Changes to Equation 10.................................................................17 Changes to Ordering Guide..........................................................22 10/04—Rev. C to Rev. DFormat Updated..................................................................Universal Typical Performance Characteristics Reordered..........................6 Changes to Figures 41 and 42.......................................................20 7/03—Rev. B to Rev. CReplaced TPC 12...............................................................................5 Change to DC-Coupled Input Section........................................14 Replaced Figure 20.........................................................................15 Updated Outline Dimensions.......................................................16 2/03—Rev. A to Rev. BChange to Evaluation Board Section...........................................15 Change to Table III.........................................................................16 Updated Outline Dimensions.......................................................16 1/00—Rev. 0 to Rev. A10/99—Revision 0: Initial VersionAD8310SPECIFICATIONST A = 25°C, V S = 5 V, unless otherwise noted.Table 1.Parameter Conditions Min Typ Max Unit INPUT STAGE Inputs INHI, INLOMaximum Input1Single-ended, p-p ±2.0 ±2.2 V4 dBV Equivalent Power in 50 Ω Termination resistor of 52.3 Ω 17 dBmDifferential drive, p-p 20 dBmNoise Floor Terminated 50 Ω source 1.28 nV/√Hz Equivalent Power in 50 Ω 440 MHz bandwidth −78 dBm Input Resistance From INHI to INLO 800 1000 1200 ΩInput Capacitance From INHI to INLO 1.4 pFDC Bias Voltage Either input 3.2 V LOGARITHMIC AMPLIFIER Output VOUT±3 dB Error Dynamic Range From noise floor to maximum input 95 dB Transfer Slope 10 MHz ≤ f ≤ 200 MHz 22 24 26 mV/dBOvertemperature, –40°C < T A < +85°C 20 26 mV/dB Intercept (Log Offset)210 MHz ≤ f ≤ 200 MHz −115 −108 −99 dBVEquivalent dBm (re 50 Ω) −102 −95 −86 dBmOvertemperature, −40°C ≤ T A ≤ +85°C −120 −96 dBVEquivalent dBm (re 50 Ω) −107 −83 dBmTemperature sensitivity −0.04 dB/°C Linearity Error (Ripple) Input from –88 dBV (–75 dBm) to +2 dBV (+15 dBm) ±0.4 dBOutput Voltage Input = –91 dBV (–78 dBm) 0.4 VInput = 9 dBV (22 dBm) 2.6 V Minimum Load Resistance, R L100 Ω Maximum Sink Current 0.5 mAOutput Resistance 0.05 ΩVideo Bandwidth 25 MHzRise Time (10% to 90%) Input Level = −43 dBV (−30 dBm), R L ≥ 402 Ω, C L ≤ 68 pF 15 nsInput Level = −3 dBV (+10 dBm), R L ≥ 402 Ω, C L ≤ 68 pF 20 nsFall Time (90% to 10%) Input Level = −43 dBV (−30 dBm), R L ≥ 402 Ω, C L ≤ 68 pF 30 nsInput Level = −3 dBV (+10 dBm), R L ≥ 402 Ω, C L ≤ 68 pF 40 nsOutput Settling Time to 1% Input Level = −13 dBV (0 dBm), R L ≥ 402 Ω, C L ≤ 68 pF 40 ns POWER INTERFACESSupply Voltage, VPOS 2.7 5.5 V Quiescent Current Zero-signal 6.5 8.0 9.5 mA Overtemperature −40°C < T A < +85°C 5.5 8.5 10 mA Disable Current 0.05 μALogic Level to Enable Power High condition, −40°C < T A < +85°C 2.3 VInput Current when High 3 V at ENBL 35 μALogic Level to Disable Power Low condition, −40°C < T A < +85°C 0.8 V1 The input level is specified in dBV, because logarithmic amplifiers respond strictly to voltage, not power. 0 dBV corresponds to a sinusoidal single-frequency input of1 V rms. A power level of 0 dBm (1 mW) in a 50 Ω termination corresponds to an input of 0.2236 V rms. Therefore, the relationship between dBV and dBm is a fixedoffset of 13 dBm in the special case of a 50 Ω termination.2 Guaranteed but not tested; limits are specified at six sigma levels.Rev. E | Page 3 of 24AD8310Rev. E | Page 4 of 24ABSOLUTE MAXIMUM RATINGSTable 2.Parameter Value Supply Voltage, V S 7.5 V Input Power (re 50 Ω), Single-Ended 18 dBm Differential Drive 22 dBm Internal Power Dissipation 200 mW θJA 200°C/W Maximum Junction Temperature 125°COperating Temperature Range −40°C to +85°C Storage Temperature Range−65°C to +150°C Lead Temperature (Soldering 60 sec)300°CStresses above those listed under Absolute Maximum Ratingsmay cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.ESD CAUTIONESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performancedegradation or loss of functionality.AD8310Rev. E | Page 5 of 24PIN CONFIGURATION AND FUNCTION DESCRIPTIONS01084-002INLOCOMM OFLT VOUTFigure 2. Pin ConfigurationTable 3. Pin Function DescriptionsPin No. Mnemonic Function1 INLO One of Two Balanced Inputs. Biased roughly to VPOS/2.2 COMM Common Pin. Usually grounded.3 OFLT Offset Filter Access. Nominally at about 1.75 V.4 VOUT Low Impedance Output Voltage. Carries a 25 mA maximum load. 5 VPOS Positive Supply. 2.7 V to 5.5 V at 8 mA quiescent current.6 BFIN Buffer Input. Used to lower post-detection bandwidth.7 ENBL CMOS Compatible Chip Enable. Active when high. 8INHISecond of Two Balanced Inputs.AD8310Rev. E | Page 6 of 24TYPICAL PERFORMANCE CHARACTERISTICSINPUT LEVEL (dBV)3.00–12020–100(–87dBm)R S S I O U T P U T (V )–80–60–40–200(+13dBm)2.52.01.51.00.501084-011Figure 3. RSSI Output vs. Input Level, 100 MHz Sine Input at T A = −40°C,+25°C, and +85°C, Single-Ended InputINPUT LEVEL (dBV)3.0–120–100(–87dBm)R S S I O U T P U T (V )–80–60–40–20(+13dBm)202.52.01.51.00.5001084-012Figure 4. RSSI Output vs. Input Level at T A = 25°C for Frequencies of 10 MHz, 50 MHz, and 100 MHzINPUT LEVEL (dBV)3.00–12020–100(–87dBm)R S S I O U T P U T (V )–80–60–40–200(+13dBm)2.52.01.51.00.501084-013Figure 5. RSSI Output vs. Input Level at T A = 25°C for Frequencies of 200 MHz, 300 MHz, and 440 MHz01084-043P IN (dBm)R S S I O U T P U T (V )E R R O R (d B )Figure 6. Log Linearity of RSSI Output vs. Input Level, 100 MHz Sine Input at T A = −40°C, +25°C, and +85°CINPUT LEVEL (dBV)–12020–100(–87dBm)E R R O R (d B )–80–60–40–20(+13dBm)01084-015Figure 7. Log Linearity of RSSI Output vs. Input Level, at T A = 25°C, for Frequencies of 10 MHz, 50 MHz, and 100 MHzINPUT LEVEL (dBV)–12020–100(–87dBm)E R R O R (d B )–80–60–40–20(+13dBm)01084-016Figure 8. Log Linearity of RSSI Output vs. Input Level at T A = 25°Cfor Frequencies of 200 MHz, 300 MHz, and 440 MHzAD8310Rev. E | Page 7 of 2401084-009Figure 9. Small-Signal AC Response of RSSI Output with External BFINCapacitance of 100 pF, 3300 pF, and 0.01 μFFigure 10. Large-Signal RSSI Pulse Response with C L = 100 pFand RL = 100 Ω, 154 Ω, and 200 Ω01084-006Figure 11. RSSI Pulse Response with R L = 402 Ω and C L = 68 pF,for Inputs Stepped from 0 dBV to −33 dBV, −23 dBV, −13 dBV, and −3 dBV 01084-010Figure 12. Small-Signal RSSI Pulse Responsewith R L = 402 Ω and C L = 68 pF01084-007Figure 13. Large-Signal RSSI Pulse Response with R L = 100 Ωand C L = 33 pF, 68 pF, and 100 pF01084-008Figure 14. Small-Signal RSSI Pulse Response with R L = 50 Ω and Back Termination of 50 Ω (Total Load = 100 Ω)AD8310Rev. E | Page 8 of 24ENABLE VOLTAGE (V)1000.000010.52.50.7S U P P L Y C U R R E N T (m A )0.9 1.1 1.3 1.5 1.7 1.9 2.1 2.31010.10.010.0010.000101084-003Figure 15. Supply Current vs. Enable Voltage at T A = −40°C, +25°C, and +85°CFREQUENCY (MHz)3029201100010R S S I S L O P E(m V /d B )100242322212625282701084-017Figure 16. RSSI Slope vs. FrequencySLOPE (mV/dB)21.522.0C O U N T22.523.023.524.024.501084-019Figure 17. Transfer Slope Distribution, V S= 5 V, Frequency = 100 MHz, 25°C01084-004Figure 18. Power-On/Off Response Time with RF Input of −83 dBV to −3 dBVFREQUENCY (MHz)–99–101–1191100010R S S I I N T E R C E P T (d B V )100–111–113–115–117–107–109–103–10501084-018Figure 19. RSSI Intercept vs. FrequencyINTERCEPT (dBV)1240–115–113C O U N T210861416–111–109–107–105–103–101–99–971820222401084-020Figure 20. Intercept Distribution V S = 5 V, Frequency = 100 MHz, 25°CAD8310Rev. E | Page 9 of 24THEORY OF OPERATIONLogarithmic amplifiers perform a more complex operation than classical linear amplifiers, and their circuitry is significantlydifferent. A good grasp of what log amps do and how they do itcan help users avoid many pitfalls in their applications. For a complete discussion of the theory, see the AD8307 data sheet. The essential purpose of a log amp is not to amplify (though amplification is needed internally), but to compress a signal of wide dynamic range to its decibel equivalent. It is, therefore, a measurement device. An even better term might be logarithmic converter, because the function is to convert a signal from one domain of representation to another via a precise nonlinear transformation:⎟⎟⎠⎞⎜⎜⎝⎛=X IN Y OUT V V V V log (1) where:V OUT is the output voltage. V Y is the slope voltage. The logarithm is usually taken to base ten, in which case V Y is also the volts-per-decade. V IN is the input voltage. V X is the intercept voltage. Log amps implicitly require two references (here V X and V Y )that determine the scaling of the circuit. The accuracy of a log amp cannot be any better than the accuracy of its scaling reference s . In the AD8310, these are provided by a band gapreference.VFigure 21. General Form of the Logarithmic FunctionWhile Equation 1, plotted in Figure 21, is fundamentally correct, a different formula is appropriate for specifying the calibration attributes or demodulating log amps like theAD8310, operating in RF applications with a sine wave input.()O IN SLOPE OUT P P V V −= (2)where:V OUT is the demodulated and filtered baseband (video or RSSI) output.V SLOPE is the logarithmic slope, now expressed in V/dB (25 mV/dB for the AD8310).P IN is the input power, expressed in dB relative to some reference power level.P O is the logarithmic intercept, expressed in dB relative to the same reference level.A widely used reference in RF systems is dB above 1 mW in 50 Ω, a level of 0 dBm. Note that the quantity (P IN – P O ) is dB. The logarithmic function disappears from the formula, because the conversion has already been implicitly performed in stating the input in decibels. This is strictly a concession to popular convention. Log amps manifestly do not respond to power(tacitly, power absorbed at the input), but rather to input voltage. The input is specified in dBV (decibels with respect to 1 V rms) throughout this data sheet. This is more precise, although still incomplete, because the signal waveform is also involved. Many users specify RF signals in terms of power(usually in dBm/50 Ω), and this convention is used in this datasheet when specifying the performance of the AD8310.PROGRESSIVE COMPRESSION High speed, high dynamic-range log amps use a cascade ofnonlinear amplifier cells to generate the logarithmic functionas a series of contiguous segments, a type of piecewise linear technique. The AD8310 employs six cells in its main signal path, each having a small-signal gain of 14.3 dB (×5.2) and a −3 dB bandwidth of about 900 MHz. The overall gain is about 20,000 (86 dB), and the overall bandwidth of the chain is approximately 500 MHz, resulting in a gain-bandwidth product(GBW) of 10,000 GHz, about a million times that of a typical op amp. This very high GBW is essential to accurate operationunder small-signal conditions and at high frequencies. The AD8310 exhibits a logarithmic response down to inputs as small as 40 μV at 440 MHz.Progressive compression log amps either provide a baseband video response or accept an RF input and demodulate thissignal to develop an output that is essentially the envelope of the input represented on a logarithmic or decibel scale. TheAD8310 is the latter kind. Demodulation is performed in a total of nine detector cells. Six are associated with the amplifier stages, and three are passive detectors that receive a progres-sively attenuated fraction of the full input. The maximum signal frequency can be 440 MHz, but, because all the gain stages are dc-coupled, operation at very low frequencies is possible.AD8310Rev. E | Page 10 of 24SLOPE AND INTERCEPT CALIBRATIONAll monolithic log amps from Analog Devices use precision design techniques to control the logarithmic slope and intercept. The primary source of this calibration is a pair of accurate voltage references that provide supply- andtemperature-independent scaling. The slope is set to 24 mV/dB by the bias chosen for the detector cells and the subsequent gain of the postdetector output interface. With this slope, the full 95 dB dynamic range can be easily accommodated within the output swing capacity, when operating from a 2.7 V supply. Intercept positioning at −108 dBV (−95 dBm re 50 Ω) has likewise been chosen to provide an output centered in the available voltage range.Precise control of the slope and intercept results in a log amp with stable scaling parameters, making it a true measurement device as, for example, a calibrated received signal strength indicator (RSSI). In this application, the input waveform is invariably sinusoidal. The input level is correctly specified in dBV . It can alternatively be stated as an equivalent power, in dBm, but in this case, it is necessary to specify the impedance in which this power is presumed to be measured. In RF practice, it is common to assume a reference impedance of 50 Ω, in which 0 dBm (1 mW) corresponds to a sinusoidal amplitude of 316.2 mV (223.6 mV rms). However, the power metric is correct only when the input impedance is lowered to 50 Ω, either by a termination resistor added across INHI and INLO, or by the use of a narrow-band matching network.Note that log amps do not inherently respond to power, but to the voltage applied to their input. The AD8310 presents a nominal input impedance much higher than 50 Ω (typically 1 kΩ at low frequencies). A simple input matching network can considerably improve the power sensitivity of this type of log amp. This increases the voltage applied to the input and, therefore, alters the intercept. For a 50 Ω reactive match, the voltage gain is about 4.8, and the whole dynamic range moves down by 13.6 dB. The effective intercept is a function of wave-form. For example, a square-wave input reads 6 dB higher than a sine wave of the same amplitude, and a Gaussian noise input reads 0.5 dB higher than a sine wave of the same rms value. OFFSET CONTROLIn a monolithic log amp, direct coupling is used between the stages for several reasons. First, it avoids the need for coupling capacitors, which typically have a chip area at least as large as that of a basic gain cell, considerably increasing die size. Second, the capacitor values predetermine the lowest frequency at which the log amp can operate. For moderate values, this can be as high as 30 MHz, limiting the application range. Third, the parasitic back-plate capacitance lowers the bandwidth of the cell, further limiting the scope of applications.However, the very high dc gain of a direct-coupled amplifier raises a practical issue. An offset voltage in the early stages of the chain is indistinguishable from a real signal. If it were as high as 400 μV , it would be 18 dB larger than the smallest ac signal (50 μV), potentially reducing the dynamic range by this amount. This problem can be averted by using a global feedback path from the last stage to the first, which corrects this offset in a similar fashion to the dc negative feedback applied around an op amp. The high frequency components of the feedback signal must, of course, be removed to prevent a reduction of the HF gain in the forward path.An on-chip filter capacitor of 33 pF provides sufficient suppres-sion of HF feedback to allow operation above 1 MHz. The −3 dB point in the high-pass response is at 2 MHz, but theusable range extends well below this frequency. To further lower the frequency range, an external capacitor can be added at OFLT (Pin 3). For example, 300 pF lowers it by a factor of 10. Operation at low audio frequencies requires a capacitor of about 1 μF. Note that this filter has no effect for input levels well above the offset voltage, where the frequency range would extend down to dc (for a signal applied directly to the input pins). The dc offset can optionally be nulled by adjusting the voltage on the OFLT pin (see the Applications section).PRODUCT OVERVIEWThe AD8310 has six main amplifier/limiter stages. These six cells and their and associated g m styled full-wave detectors handle the lower two-thirds of the dynamic range. Three top-end detectors, placed at 14.3 dB taps on a passive attenuator, handle the upper third of the 95 dB range. The first amplifier stage provides a low noise spectral density (1.28 nV/√Hz). Biasing for these cells is provided by two references: onedetermines their gain, and the other is a band gap circuit that determines the logarithmic slope and stabilizes it against supply and temperature variations. The AD8310 can be enabled or disabled by a CMOS-compatible level at ENBL (Pin 7). The differential current-mode outputs of the nine detectors are summed and then converted to single-sided form, nominally scaled 2 μA/dB. The output voltage is developed by applying this current to a 3 kΩ load resistor followed by a high speed gain-of-four buffer amplifier, resulting in a logarithmic slope of 24 mV/dB (480 mV/decade) at VOUT (Pin 4). The unbuffered voltage can be accessed at BFIN (Pin 6), allowing certain functional modifications such as the addition of an external postdemodulation filter capacitor and the alteration or adjustment of slope and intercept.–INPUT01084-022Figure 22. Main Features of the AD8310The last gain stage also includes an offset-sensing cell. This generates a bipolarity output current, if the main signal path exhibits an imbalance due to accumulated dc offsets. This current is integrated by an on-chip capacitor that can beincreased in value by an off-chip component at OFLT (Pin 3). The resulting voltage is used to null the offset at the output of the first stage. Because it does not involve the signal inputconnections, whose ac-coupling capacitors otherwise introduce a second pole into the feedback path, the stability of the offset correction loop is assured.The AD8310 is built on an advanced, dielectrically isolated, complementary bipolar process. In the following interface diagrams shown in Figure 23 to Figure 26, resistors labeled as R are thin-film resistors that have a low temperature coefficient of resistance (TCR) and high linearity under large-signal conditions. Their absolute tolerance is typically within ±20%.Similarly, capacitors labeled as C have a typical tolerance of ±15% and essentially zero temperature or voltage sensitivity. Most interfaces have additional small junction capacitances associated with them, due to active devices or ESD protection, which might not be accurate or stable. Component numbering in these interface diagrams is local.ENABLE INTERFACEThe chip-enable interface is shown in Figure 23. The currents in the diode-connected transistors control the turn-on and turn-off states of the band gap reference and the bias generator. They are a maximum of 100 μA when ENBL is taken to 5 V under worst-case conditions. For voltages below 1 V , the AD8310 is disabled and consumes a sleep current of less than 1 μA. When tied to the supply or a voltage above 2 V , it is fully enabled. The internal bias circuitry is very fast (typically <100 ns for either off or on). In practice, however, the latency period before the log amp exhibits its full dynamic range is more likely to be limited by factors relating to the use of ac-coupling at the input or the settling of the offset-control loop (see the following sections).01084-023Figure 23. Enable InterfaceINPUT INTERFACEFigure 24 shows the essentials of the input interface. C P and C M are parasitic capacitances, and C D is the differential input capacitance, largely due to Q1 and Q2. In most applications, both input pins are ac-coupled. The S switches close whenenable is asserted. When disabled, bias current I E is shut off and the inputs float; therefore, the coupling capacitors remain charged. If the log amp is disabled for long periods, small leakage currents discharge these capacitors. Then, if they are poorly matched, charging currents at power-up can generate a transient input voltage that can block the lower reaches of the dynamic range until it becomes much less than the signal. A single-sided signal can be applied via a blocking capacitor to either Pin 1 or Pin 8, with the other pin ac-coupled to ground. Under these conditions, the largest input signal that can be handled is 0 dBV (a sine amplitude of 1.4 V) when using a 3 V supply; a 5 dBV input (2.5 V amplitude) can be handled with a 5 V supply. When using a fully balanced drive, this maximum input level is permissible for supply voltages as low as 2.7 V . Above 10 MHz, this is easily achieved using an LC matching network. Such a network, having an inductor at the input, usefully eliminates the input transient noted above.。

ADUM1201ARZ-RL7中文资料

3 ns maximum channel-to-channel matching High common-mode transient immunity: > 25 kV/µs Safety and regulatory approvals

UL recognition 2500 V rms for 1 minute per UL 1577

APPLICATIONS

The ADuM120x isolators provide two independent isolation channels in a variety of channel configurations and data rates (see the Ordering Guide). Both parts operate with the supply voltage on either side ranging from 2.7 V to 5.5 V, providing compatibility with lower voltage systems as well as enabling a voltage translation functionality across the isolation barrier. In addition, the ADuM120x provide low pulse-width distortion (< 3 ns for CR grade) and tight channel-to-channel matching (< 3 ns for CR grade). Unlike other optocoupler alternatives, the ADuM120x isolators have a patented refresh feature that ensures dc correctness in the absence of input logic transitions

Mark VIe控制系统中文版第1册

GE EnergyMark VIe®控制系统指南 第一册 系统手册目录第1章综述1-1 介绍…………………………………………………………………………………….1-1 应用…………………………………………………………………………………….1-2 控制器………………………………………………………………………………….1-3 I/O网络(IONet)…………………………………………………………………….1-3 I/O模块…………………………………………………………………………………1-4 相关文献………………………………………………………………………………..1-5 如何获取帮助…………………………………………………………………………..1-5 缩写词和缩略语………………………………………………………………………..1-6第2章系统体系结构2-1 介绍……………………………………………………………………………………..2-1 系统部件………………………………………………………………………………..2-1 控制器……………………………………………………………………………..2-2控制器外罩………………………………………………………………………..2-4电源………………………………………………………………………………..2-4I/O包………………………………………………………………………………2-5终端块……………………………………………………………………………..2-6I/O类型……………………………………………………………………………2-7功率源……………………………………………………………………………..2-9 通信……………………………………………………………………………………..2-11 设备数据公路(UDH)……………………………………………………….....2-11工厂数据公路(PDH)…………………………………………………………..2-11IONet………………………………………………………………………………2-12人机接口(HMI)………………………………………………………………..2-12服务器……………………………………………………………………………..2-13计算机操作者接口(COI)………………………………………………………2-13与分布式控制系统(DCS)的连接……………………………………………….2-14EX2100励磁器……………………………………………………………………2-15发电机保护………………………………………………………………………..2-15LS2100静态启动器……………………………………………………………….2-15 控制和保护……………………………………………………………………………..2-16 平均故障间隔时间(MTBF)……………………………………………………2-16平均强制断电间隔时间(MTBFO)…………………………………………….2-17故障检测…………………………………………………………………………..2-18联机维修…………………………………………………………………………..2-19指定的控制器……………………………………………………………………..2-20UDH通信器……………………………………………………………………….2-21输出处理…………………………………………………………………………..2-22输入处理…………………………………………………………………………..2-24状态交换…………………………………………………………………………..2-29表决………………………………………………………………………………..2-29强制赋值…………………………………………………………………………..2-30对等I/O……………………………………………………………………………2-30命令操作…………………………………………………………………………..2-30响应速度…………………………………………………………………………..2-31涡轮保护…………………………………………………………………………..2-32 冗余选项………………………………………………………………………………..2-33 单工控制器………………………………………………………………………..2-34第3章网络3-1 介绍……………………………………………………………………………………...3-1 网络综述…………………………………………………………………………………3-1 网络层次……………………………………………………………………………3-2 数据公路…………………………………………………………………………………3-5 工厂数据公路(PDH)………………………………………………………….…3-5设备数据公路(UDH)……………………………………………………………3-7数据公路以太网交换机……………………………………………………………3-8为UDH和PDH选择IP地址…………………………………………………….3-9IONet………………………………………………………………………………3-10寻址……………………………………………………………………………….3-10以太网全局数据(EGD)……………………………………………………….3-12 光纤电缆……………………………………………………………………………….3-14 部件……………………………………………………………………………….3-14 单模光纤连线………………………………………………………………………….3-18 IONet部件………………………………………………………………………..3-19UDH/PDH部件…………………………………………………………………..3-20拓扑结构实例…………………………………………………………………….3-21以太网交换机故障检修………………………………………………………….3-21部件来源………………………………………………………………………….3-22 第4章法规、标准和环境4-1 介绍………………………………………………………………………………………4-1 安全标准…………………………………………………………………………………4-1 电气………………………………………………………………………………………4-1 印刷电路板部件……………………………………………………………………4-1电磁兼容性(EMC)………………………………………………………………4-2低压电指令…………………………………………………………………………4-2ATEX指令94/9/EC………………………………………………………………..4-2电源电压……………………………………………………………………………4-2 环境………………………………………………………………………………………4-4 温度…………………………………………………………………………………4-4运输和存储温度……………………………………………………………………4-6湿度…………………………………………………………………………………4-6海拔高度……………………………………………………………………………4-6污染物………………………………………………………………………………4-7振动…………………………………………………………………………………4-7 第5章安装和配置5-1 介绍………………………………………………………………………………………5-1 安装支持…………………………………………………………………………………5-1 前期规划……………………………………………………………………………5-1GE安装文献……………………………………………………………………….5-2技术咨询选项………………………………………………………………………5-2 设备接收和处理…………………………………………………………………………5-4 存储…………………………………………………………………………………5-5操作环境……………………………………………………………………………5-6 电源要求…………………………………………………………………………………5-7 安装支持图纸……………………………………………………………………………5-8 接地……………………………………………………………………………………..5-13设备接地…………………………………………………………………………..5-13电缆分级和排布………………………………………………………………………5-21 信号和电源等级的定义…………………………………………………………5-21电缆通道间距准则………………………………………………………………5-23布线准则…………………………………………………………………………5-26 电缆技术规格…………………………………………………………………………5-27 电缆的尺寸………………………………………………………………………5-27常规技术规格……………………………………………………………………5-28低压电屏蔽电缆…………………………………………………………………5-29 连接系统………………………………………………………………………………5-31 I/O布线………………………………………………………………………….5-31终端块特征………………………………………………………………………5-32电源系统…………………………………………………………………………5-33安装以太网………………………………………………………………………5-33 启动检查………………………………………………………………………………5-34 布线和电路检查…………………………………………………………………5-34 第6章工具和系统接口6-1 介绍………………………………………………………………………………………6-1 ToolboxST………………………………………………………………………………..6-1 人机接口(HMI)………………………………………………………………………6-2 基本说明……………………………………………………………………………6-2产品功能……………………………………………………………………………6-2 涡轮历史分析程序………………………………………………………………………6-4 系统配置……………………………………………………………………………6-4系统性能……………………………………………………………………………6-5数据流………………………………………………………………………………6-5涡轮历史分析程序工具……………………………………………………………6-6 uOSM…………………………………………………………………………………….6-8 OPC服务器……………………………………………………………………………..6-9 Modbus…………………………………………………………………………………6-10 以太网Modbus从机……………………………………………………………..6-11串行Modbus………………………………………………………………………6-12 以太网GSM……………………………………………………………………………6-16 时间同步化…………………………………………………………………………….6-17 冗余时间源……………………………………………………………………….6-17时间源的选择…………………………………………………………………….6-18 第7章维护和诊断7-1 介绍………………………………………………………………………………………7-1 维护………………………………………………………………………………………7-1 以太网交换机……………………………………………………………………………7-2 警告综述…………………………………………………………………………………7-3 进程警报…………………………………………………………………………………7-4 进程和保持警报数据流……………………………………………………………7-4 诊断警报…………………………………………………………………………………7-5 通过ToolboxST来浏览控制器诊断………………………………………………7-5针对表决器给出相异情况的诊断…………………………………………………7-6 总额计算器………………………………………………………………………………7-7 发光二极管快速参考……………………………………………………………………7-8 I/O包状态………………………………………………………………………….7-9IONet状态…………………………………………………………………………7-9第1章综述应用 ……………………………………………………..1-2控制器 ……………………………………………………..1-3I/O网络(IONet) ……………………………………..1-3I/O模块………………………………………………………1-4相关文献……………………………………………………..1-5如何获取帮助………………………………………………..1-5缩写词和缩略语……………………………………………..1-6介绍Mark VIe控制设备适用于多种控制和保护的应用场合,其中包括蒸汽和燃气涡轮以及电厂配套设施(BOP)等。

M7 1 用户手册说明书

USER MANUALM7Table of Contents1.GENERAL INFORMATION (2)1.1W ARNINGS AND RECOMMENDATIONS (2)1.2F UNCTION AND F EATURE (2)1.3F RONT VIEW (2)1.4R EAR VIEW (2)1.5D IMENSIONAL DATA AND INSTALLATION HEIGHTS (3)1.6W ALL-MOUNTED INSTALLATION (4)2.SYSTEM APPLICATION (5)2.1V ILLA OR SINGLE-FAMILY CONTEXT (5)2.2A PARTMENT BLOCK OR MULTI-FAMILY CONTEXT (5)3.OPERATION DESCRIPTION (7)3.1M AIN P AGE (7)3.2S HORTCUT PAGE (7)3.3A DJUSTING PAGE (8)3.4BASIC OPERATIONS (8)3.5SETUP INSTRUCTIONS (11)3.6U PLOAD PICTURE AS WALLPAPER (20)3.7U PLOAD MUSIC AS RINGTONE (20)4.SPECIFICATIONS (20)1. General information1.1 Warnings and recommendationsIt is important to read this manual carefully before proceeding with the installation. The guarantee automatically expires for negligence, misuse, tampering by unauthorizedpersonnel.The Video internal unit must only be installed indoors; it must not be exposed to water drops orsplashes.1.2 Function and Feature⚫ 7” capacitive touch screen monitor ⚫ Based on Android system ⚫ IP over 2-wire non-polarity ⚫ 1024(RGB)x600 pix resolution ⚫ Picture in Picture function⚫ Indicator: Power, mute, message, WIFI ⚫ Picture and video save⚫ Support the secondary door bell and ringer extension ⚫ Support WIFI for cloud intercom⚫Flexible power way: support remote and local power1.3 Front view+-1234567891. 7” touch screen display (16: 9)2. SD card slot3. 24v DC input4. Reset button5. Indicate lights for power, mute, message, WIFI6. Increase the volume7. Volume indicate lights8. Reduce the volume1.4 Rear view123456781. Mic2. Loudspeaker3. Interface for 2nd door bell and extension ring4. Interface for additional power supply, non-polarity5. Interface for 2-wire IP interface, non-polarity6. Configurator J1: remove for additional power supply7. Configurator J2: Master/Slave, remove for Slave8. SD card slot1.5 Dimensional data and installation heightshttps:///1201207-power_icon.html+-HOME232mm133m m15mmGround160 ~ 165m m135 ~ 140m mRecommended height, unless otherwise required by the law1.6 Wall-mounted installation12345671 - Mark the location of the bracket holes2 - Drill3 – Install expandable screw4 - Fix the wall bracket5 - Connect the wires with the interface according to the wiring diagrams.6 – Insert the connector into the monitor, using index finger, middle finger, ring finger and littlefinger is easy to insert7 - Put the monitor on its wall bracket2.System Application2.1Villa or single-family contextMonitor 3 PowerDoor StationSmartPhone APP INTERNETMonitor 2Monitor 1In villa(single-family) systems all of the unit can be connected with the power.2.2Apartment block or multi-family contextHome 1DistributorDoor StationSmartPhoneAPPINTERNETHome 2Home 3PowerIn multi-family systems (apartment blocks), you need the distributor to connect all of the monitor and door station.The distributor can be connected with each other via CAT-5 cable.Distributor1PowerPowerDistributor NPowerDistributor 2CAT-53.Operation Description3.1Main PageThe Main Page is your starting point for using all the applications on your monitor.Touch anywhere of the screen on monitor in standby mode, the Main Page will appear as follows:Icon description:System status icons: from left to right-Connection-Mute-Wi-FiDoor Connection to the outdoor panel to show imageCamera Connection to the IP cameraRecord Pictures and video reviewIntercom Call to other monitors in the house (if any).Setting Enter setting menuScreen off Shut the screen. The screen will automatically switch off after 30” if no activity is done.. Sliding the main page to the left will show shortcut page.. Sliding the main page to the right will show adjusting brightness and volume page 3.2Shortcut pageIcon description:WIFI Deactivate / activate WIFI (master monitor only)Silence Activate / deactivate do not disturb modeLeaving Deactivate / activate leaving mode,when leaving mode is active, the silence and transfer function will be onTransfer Deactivate / activate call transfer functionwhen transfer function is activate, the call from door panel will be transfer to APP.3.3Adjusting pageIcon description:Speaker Volume Adjust the volume from door stationRing Volume Adjust the ring/video volumeBrightness Adjust the screen brightness3.4BASIC OPERATIONSEnter Door ListP ush “Door” button Push door panel you want to see Then the monitor page will be shown as follows:1 23 4 5 6 7 8Icon description:1.The additional IP camera window2.Button for adjusting video quality3.Take picture4.Take video5.Open the first door6.Open the second door7.Start to talk with visitor8.Return home pageNote: The name of door panels can be set by user, Door1, Door2, Door3 and Door4 in default.The instruction to set name can be found from ‘Setting-Door’ in the Setting.Enter Camera ListP ush “Camera” button Push camera you want to seeThen the monitor page will be shown as follows:12 3Icon description:1.Button for adjusting video quality2.Take picture3.Return home pageNote: The name of camera can be set by user, Camera1, Camera2, Camera3 and Camera4 in default.The instruction to set name can be found from ‘Setting-Camera’ in the Setting.Enter Intercom ListP ush “Intercom” button Push the monitor you want to dial Then the dialing page will be shown as follows:12Icon description:1.Adjust volume2.Cancel the callThe called page is as follows:123Icon description:1.Adjusting volume2.Answer the call3.Hung up3.5SETUP INSTRUCTIONSAll settings should enter the setting page by touching the icon ’Setting’ from main page:Setting-Door Panel1From door list page above, choose the door you want to set, it will show the following page:123456Icon description:1.Set door panel name2.Set auto record mode. (None, Photo, Video)3.Set door panel ring tone4.Set door lock open time. (1s,2s,3s,4s,5s,6s,7s,8s,9s)5.Select IP camera for picture in picture function. To activate this function, please add IPcamera first. See “Setting-Camera”6.Turn on/off fish eye lensCloud intercomPress cloud menu, the following page will be shown:1Use App to scan the QR code, and add it to device list.The App link for smartphone:Android APP IOS APPNote: Users should turn on [Leaving] mode or [Transfer] mode to enable cloud intercom function Setting-Memory12345Parameter description:1.The usage of the memorya)Red means the volume of images storedb)Green means the volume of videos storedc)Grey means the available volume2.The number of pictures record3.The number of videos record4.The video time when take video5.Format MemorySetting-WIFI12Parameter description:1.WIFI switcher2.Select a WIFI network to joinSetting-Motion Detection1234Setting description:1.Turn on/off motion detection2.Set the lock to open when motion happen3.Set the time schedule for motion detection function4.Take picture when motion happenSetting-Mute123Setting description:1.Deactivate / activate “manual” for mute functionW hen activate “Manual” for mute function, there will no ring when visitor call from door panel.2.Deactivate / activate “schedule” for mute function3.Set schedule mute periodW hen setting “Schedule” mute function, there will no ring in the setting time. Setting-Time&Date12345Setting description:1.Turn on/off synchronization time automatedly2.Set time zone3.Set Date4.Set Time5.Deactivate / activate 12-hour or 24-hour formatSetting-Language1Setting description:1.Set languageSetting-Wallpaper12Setting description:1.Push to choose a new picture as wall paper2.The existing wallpaperSetting-SetupTo set monitor address, add RFID card, add IP camera, and upgrade system, user needs input password in the following page:1Note: default password: 12345Setting-Room-Address1234Parameter description:1.Set room number, the value can be 01 ~ 322.Set room name3.Set extension room number, the value can be 1-44.Confirm and restart the deviceSetting-RFID Card1234Setting description:1.Add new RFID card2.Delete all RFID card3.The number of existing RFID card4.The lock to open when swiping RFID cardSetting- Add RFID Card1For example: If apartment 01 wants to add RFID card, the procedure:1.P ush “Setting” →“RFID card” →“Add card”,2.Swipe the card on door station one by one, then push the 01 call button to finish it3.Sound prompt: add card - Beep 1 time, add card success: Beep 2 timesNote: When swipe card on the door station, the limited time is 90SThe indoor monitor can talk with door station when adding RFID card.Setting- swipe short time to open lock1, long time to open lock21Description:Time for short time swipe:1sTime for long time swipe: 3sSetting-Camera123Icon description:1.Modify IP camera setting2.Delete IP camera3.Add new IP cameraWhen push icon1 and icon 3, the following page will be shown:12345Parameter description:1.Type: Choose the brand of IP camera2.IP address name: set the name for IP camera.3.IPC address: Set IP address of IP cameraNote: the suggestion IP address for IP camera: from 192.168.137.134 to192.168.137.254ername: Fill in username of IP camera5.Password: Fill in password of IP cameraSetting-System12345678Setting description:1.Show hardware version2.Show software version3.Show model name4.Show Room number5.Show IP address6.Push to upgrade system7.Push to restore setting8.Push to change [setting] passwordAfter pushing upgrade button, the following page will be shown:1Setting description:1.Upgrade via SD carda.Create a new folder named “u pgrade”Note: please use lowercase lettersb.Put the system software in itc.P ush “Setting” →“System” →”System upgrade” →”SD upgrade” to start3.6Upload picture as wallpaperYou can use your own picture as the system wallpaper, the operation procedure:1.Prepare a Micro-SD card2.C reate a new folder named “w allpaper”, and copy your picture in itNote: please use lowercase letters3.P ush “Setting” →“Wallpaper” →”Choose a new wallpaper” to set3.7Upload music as ringtoneYou can use your own music as the ring tone, the operation procedure:1.Prepare a Micro-SD card2.Create a new folder named “ringtones”, and copy your music in itNote: please use lowercase letters3.P ush “Setting” →“Door” →”Ringtone” to set4.SpecificationsCategory SpecificationInput power DC: 24v, 50Hz/60HzPower Consumption Max: 6W, standby: 3WTFT LCD 7-inch digital TFT LCDLCD resolution 1024(RGB) x 600Connection with door station Support four 2-wire door stations (Maximum)Connection with CCTV Support 16 IP camera input (Maximum) Connection with extension monitor Support 3 extension monitorsMemory capacity TF card: 1024 pictures, 128 videos Dimensions (mm) 232mm*133mm*15mmWeight(kg) 0.43kg。

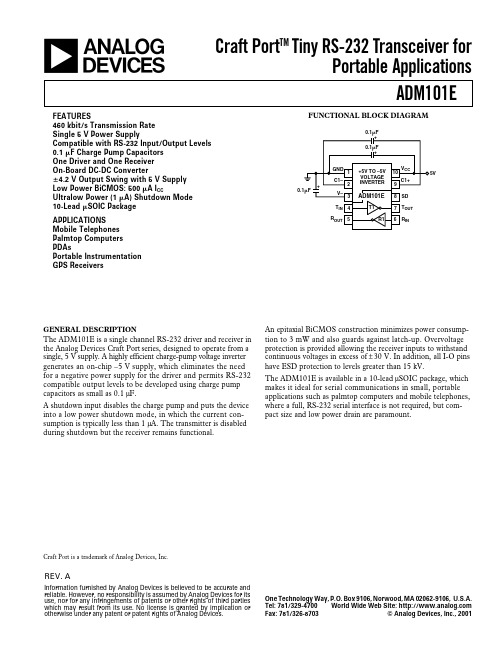

ADM101EARMZ-REEL7资料

REV.AInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.aADM101EOne Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 781/329-4700World Wide Web Site: Fax: 781/326-8703© Analog Devices, Inc., 2001Craft Port TMTiny RS-232 Transceiver forPortable ApplicationsFUNCTIONAL BLOCK DIAGRAM0.1FFEATURES460 kbit/s Transmission Rate Single 5 V Power SupplyCompatible with RS-232 Input/Output Levels 0.1 F Charge Pump Capacitors One Driver and One Receiver On-Board DC-DC Converter؎4.2 V Output Swing with 5 V Supply Low Power BiCMOS: 500A I CCUltralow Power (1 A) Shutdown Mode 10-Lead SOIC Package APPLICATIONS Mobile Telephones Palmtop Computers PDAsPortable Instrumentation GPS ReceiversGENERAL DESCRIPTIONThe ADM101E is a single channel RS-232 driver and receiver in the Analog Devices Craft Port series, designed to operate from a single, 5 V supply. A highly efficient charge-pump voltage inverter generates an on-chip –5 V supply, which eliminates the need for a negative power supply for the driver and permits RS-232compatible output levels to be developed using charge pump capacitors as small as 0.1 µF.A shutdown input disables the charge pump and puts the device into a low power shutdown mode, in which the current con-sumption is typically less than 1 µA. The transmitter is disabled during shutdown but the receiver remains functional.Craft Port is a trademark of Analog Devices, Inc.An epitaxial BiCMOS construction minimizes power consump-tion to 3 mW and also guards against latch-up. Overvoltage protection is provided allowing the receiver inputs to withstand continuous voltages in excess of ±30 V. In addition, all I-O pins have ESD protection to levels greater than 15 kV.The ADM101E is available in a 10-lead µSOIC package, which makes it ideal for serial communications in small, portable applications such as palmtop computers and mobile telephones,where a full, RS-232 serial interface is not required, but com-pact size and low power drain are paramount.ADM101E–SPECIFICATIONS(V CC = 5 V ؎ 10%, C1 = C2 = 0.1 F. All specifications T MIN to T MAX unlessotherwise noted.)Parameter Min Typ Max Unit Test Conditions/CommentsOutput Voltage Swing±3.5±4.2V V CC = 5 V ±5%, T OUT Loaded with 3 kΩ to GND±3.25±4.2V V CC = 5 V ±10%, T OUT Loaded with 3 kΩ toGNDV CC Power Supply Current (Unloaded)0.51mA No Load, T IN = V CC or GNDV CC Power Supply Current (Loaded) 1.85 2.5mA T OUT Loaded with 3 kΩ to GNDV CC Power Supply Current (Shutdown)1µA SD Input = V CCInput Logic Threshold Low, V INL0.8VInput Logic Threshold High, V INH 2.4VInput Leakage Current±1µARS-232 Input Voltage Range–15+15VRS-232 Input Threshold Low0.8 2.2VRS-232 Input Threshold High 2.4 2.6VRS-232 Input Hysteresis0.2VRS-232 Input Resistance357kΩTTL/CMOS Output Voltage Low, V OL0.4V I OUT = 1.6 mATTL/CMOS Output Voltage High, V OH 3.5V I OUT = –1.0 mAPropagation Delay0.25µs RS-232 to TTLInstantaneous Slew Rate125V/µs C L = 10 pF, R L = 3 kΩ–7 kΩ, T A = 25°C Transition Region Slew Rate11V/µs R L = 3 kΩ, C L = 1000 pFMeasured from +3 V to –3 V or Vice VersaBaud Rate460kB R L = 3 kΩ, C L = 1 nFOutput Resistance300ΩV CC = 0 V, V OUT = ±2 VRS-232 Output Short Circuit Current±25±60mANOTES1Sample tested to ensure compliance.Specifications subject to change without notice.ABSOLUTE MAXIMUM RATINGS*(T A = 25°C unless otherwise noted)V CC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 V V– . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +0.3 V to –6 V Input VoltagesDriver Input T IN . . . . . . . . . . . . . . –0.3 V to (V CC, +0.3 V) Receiver Input R IN . . . . . . . . . . . . . . . . . . . . . . . . . .±30 V Output VoltagesDriver Output T OUT . . . . . . . (V CC, +0.3 V) to (V–, –0.3 V) Receiver Output R OUT . . . . . . . . . . –0.3 V to (V CC +0.3 V) Short Circuit DurationT OUT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Continuous Power DissipationRM-10(Derate 12 mW/°C above 70°C) . . . . . . . . . 1488mW Thermal Impedance . . . . . . . . . . . . . . . . . . . . . . . . 135°C/W Operating Temperature RangeIndustrial (A Version) . . . . . . . . . . . . . . . –40°C to +85°C Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C Lead Temperature SolderingVapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . . . . 215°C Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220°C ESD Rating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . >2000 V ESD Rating (I-O Pins) . . . . . . . . . . . . . . . . . . . . . . . . .15 kV *This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.ORDERING GUIDETemperature Package Package Model Range Description Option ADM101EARM–40°C to +85°CµSOIC RM-10REV. A –2–REV. A ADM101E–3–PIN FUNCTION DESCRIPTIONSPin No.Mnemonic Function1GND Ground Pin. Must be connected to 0 V.2C1–Negative Terminal of C1 (if C1 is Polarized Capacitor).3V–Internally Generated Negative Supply Voltage.4T IN Driver Input (3 V to 5 V TTL/CMOS Logic Levels).5R OUT Receiver Output (3 V to 5 V TTL/CMOSLogic Levels).6R IN Receiver Input (EIA-232 Signal Levels).7T OUT Driver Output (EIA-232 Signal Levels).8SD Shutdown Input. Logic 1 on this input puts the ADM101E into low power shutdown mode.9C1+Positive Terminal of Charge Pump Capacitor (if C1 is Polarized Capacitor).10V CCPositive Power Supply, Nominally 5 V.PIN CONFIGURATIONV –SD T C1–C1+T OUTR OUTR INV CC Typical Performance CharacteristicsCURRENT – mA–1–6255C H A R G E P U M P V O L T A G E –V o l t s101520–2–3–4–5TPC 1.Charge Pump Voltage vs. Current LOAD CAPACITANCE – pF1412003500500I D D – m A10001500200010864250030002TPC 2.I DD vs. Load Capacitance @ 460 kbpsREV. AADM101E–4–LOAD CAPACITANCE – pF65–50500T X O /P – V o l t s100015002000432125000–1–2–3–4T X HIT X LOTPC 3.Transmitter Output Voltage vs. Load Capacitance @460 kbpsV CC – Volts6–601T X O /P H I & L O234425–2–4T X HIT X LO67TPC 4.Tx Output Voltage vs. SupplyDATA RATE – kbps40–400100S L E W RA T E – V o l t s /s2003004003020100–10500600–20–30TPC 5.Slew Rate vs. Data RateLOAD CURRENT – mA5–502T X O U T P U T V OL T A G E468432101012–1–2–3–414TPC 6.Transmitter Output Voltage vs. Load CurrentREV. A ADM101E–5–GENERAL DESCRIPTIONThe ADM101E is an RS-232 compatible line driver/receiver in the Analog Devices Craft Port series, containing one driver (trans-mitter) and one receiver. It is ideal for serial communication in small portable devices such as mobile telephones, palmtop per-sonal computers and personal digital assistants, where a full,RS-232 serial interface is not required, and only Tx and Rx lines are required for low speed communication between devices. The ADM101E operates from a single, 5 V supply, and generates its own, on-chip, –5 V power supply, thus removing the need for a negative power supply for the driver.CIRCUIT DESCRIPTIONThe internal circuitry consists of three main sections. These are:1.A charge pump dc-to-dc converter.2.5V logic to EIA-232 driver.3.EIA-232 to 5V logic receiver.Charge Pump DC-DC ConverterThe dc-dc converter generates a negative supply voltage from the 5 V supply, thus removing the need for a separate –5 V rail.It consists of an on-chip 200 kHz oscillator, switching matrix and two external capacitors, as shown in Figure 1.GND V – = –V CCFigure 1.Charge Pump DC–DC ConverterWhen S1 and S2 are closed, S3 and S4 are open, and C1charges to +V CC . S1 and S2 are then opened, while S3 and S4are closed to connect C1 across C2, dumping charge into C2.Since the positive terminal of C2 is at ground, a negative voltage will be built up on its negative terminal with each cycle of the oscillator. This voltage depends on the current drawn from C2.If the current is small, the voltage will be close to –V CC , but will fall as the current drawn increases.Charge Pump Capacitors And Supply DecouplingFor proper operation of the charge pump, the capacitors should have an equivalent series resistance (ESR) less than 1 Ω. As the charge pump draws current pulses from V CC , the V CC decou-pling capacitor should also have low ESR. The V CC decoupling capacitor and V– reservoir capacitor should also have low ESR because they determine how effectively ESD pulses are clamped to V CC or V– by the on-chip clamp diodes. Tantalum or mono-lithic ceramic capacitors are suitable for these components. If using tantalum capacitors, do not forget to observe polarity.Transmitter (Driver) SectionThe driver converts 5V logic input levels into RS-232 compat-ible output levels. With V CC = 5 V and driving an EIA-232 load,the output voltage swing is typically ±4.2 V.Receiver SectionThe receivers are inverting level-shifters that accept EIA-232input levels and translate them into 5 V logic output levels.The inputs have internal 5 k Ω pull-down resistors to ground and are also protected against overvoltages of up to ±25 V. The guaranteed switching thresholds are 0.8 V minimum and 2.8 V maximum. An unconnected receiver input is pulled to 0 V by the internal 5 k Ω pull-down resistor. This, therefore, results in a Logic 1 output level for unconnected inputs or for inputs con-nected to GND.The receivers have Schmitt trigger input with a hysteresis level of 0.25 V. This ensures error-free reception for both noisy inputs and for inputs with slow transition times.SHUTDOWN INPUTThe shutdown input allows the ADM101E to be put into an ultralow power mode where the dc-dc converter is switched off and the transmitter is disabled. The receiver remains active during shutdown. Logic 0 at this input enables the ADM101E,while a Logic 1 at this input shuts down the ADM101E.REV. AADM101E–6–OUTLINE DIMENSIONSDimensions shown in inches and (mm).C 00053–0–2/01 (r e v . A )P R I N T E D I N U .S .A .10-Lead SOIC(RM-10)0.006 (0.15)0.002 (0.05)ADM101E–Revision HistoryLocationPageData sheet changed from REV. 0 to REV. A.Changes made to Outline Dimensions (RM-10) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6。

MAX1978中文数据手册

用于Peltier模块的集成温度控制器概论MAX1978 / MAX1979是用于Peltier热电冷却器(TEC)模块的最小, 最安全, 最精确完整的单芯片温度控制器。

片上功率FET和热控制环路电路可最大限度地减少外部元件, 同时保持高效率。

可选择的500kHz / 1MHz开关频率和独特的纹波消除方案可优化元件尺寸和效率, 同时降低噪声。

内部MOSFET的开关速度经过优化, 可降低噪声和EMI。

超低漂移斩波放大器可保持±0.001°C的温度稳定性。

直接控制输出电流而不是电压, 以消除电流浪涌。

独立的加热和冷却电流和电压限制提供最高水平的TEC保护。

MAX1978采用单电源供电, 通过在两个同步降压调节器的输出之间偏置TEC, 提供双极性±3A输出。

真正的双极性操作控制温度, 在低负载电流下没有“死区”或其他非线性。

当设定点非常接近自然操作点时, 控制系统不会捕获, 其中仅需要少量的加热或冷却。

模拟控制信号精确设置TEC 电流。

MAX1979提供高达6A的单极性输出。

提供斩波稳定的仪表放大器和高精度积分放大器, 以创建比例积分(PI)或比例积分微分(PID)控制器。

仪表放大器可以连接外部NTC或PTC热敏电阻, 热电偶或半导体温度传感器。

提供模拟输出以监控TEC温度和电流。

此外, 单独的过热和欠温输出表明当TEC温度超出范围时。

片上电压基准为热敏电阻桥提供偏置。

MAX1978 / MAX1979采用薄型48引脚薄型QFN-EP 封装, 工作在-40°C至+ 85°C温度范围。

采用外露金属焊盘的耐热增强型QFN-EP封装可最大限度地降低工作结温。

评估套件可用于加速设计。

应用光纤激光模块典型工作电路出现在数据手册的最后。

WDM, DWDM激光二极管温度控制光纤网络设备EDFA光放大器电信光纤接口ATE特征♦尺寸最小, 最安全, 最精确完整的单芯片控制器♦片上功率MOSFET-无外部FET♦电路占用面积<0.93in2♦回路高度<3mm♦温度稳定性为0.001°C♦集成精密积分器和斩波稳定运算放大器♦精确, 独立的加热和冷却电流限制♦通过直接控制TEC电流消除浪涌♦可调节差分TEC电压限制♦低纹波和低噪声设计♦TEC电流监视器♦温度监控器♦过温和欠温警报♦双极性±3A输出电流(MAX1978)♦单极性+ 6A输出电流(MAX1979)订购信息* EP =裸焊盘。

MEMORY存储芯片ADM3075EARZ-REEL中文规格书

1

Disable

1 0 Mode register set 2 (MR2)

1 Disabled 1 Enabled

M5 M1 Output Drive St rength

1 1 Mode register set 3 (MR3)

M9 M6 M2

RTT,nom (ODT) 2 Non- Writes

0 0 0 RTT,nom disabled 0 0 1 RZQ/4 (60ȍ [NOM])

satisfied, the updated features are to be assumed unavailable.

09005aef85af8fa8 4Gb_DDR3L.pdf - Rev. R 09/18 EN

Figure 53: MRS to nonMRS Command Timing (tMOD)

The MR1 register must be loaded when all banks are idle and no bursts are in progress. The controller must satisfy the specified timing parameters tMRD and tMOD before initiating a subsequent operation.

RTT,nom (ODT) 3 Writes

RTT,nom disabled RZQ/4 (60ȍ [NOM])

M7 Write Levelization

0 Disable (normal)

1

Enable

00 01 10 11

RZQ/6 (40ȍ [NOM]) RZQ/7 (34ȍ [NOM])

IC-R71操作说明书(中文版)

应用 ICOM 开发的毫瓦分贝 J-FET IC-R71 具有 105dB 的动态范围 70.4515MHz 的第一中频实际上 消除了寄生噪声影响 加上使用了 ICOM 通带调谐技术 PBT 的高增益 9.0115MHz 第二中频 一个深度 的中频陷波器 可调的自动增益和噪音消隐 可用于调节消除脉冲噪音 音频音调调节控制 即使在 存在强干扰或高噪声水平情况下都可清晰接收

6 电源开关 这是一个带锁的按压开关 它控制整机的交

流电源输入 当开关按下并锁定时 电源供给接 收机 开关再次按下并松开 全部电路的电源都 被切断

-5 -

广播爱好者 m222 翻译 有建议请联系 邮件地址 m_fanqiang@

第四章 操作控制装置

7 功能键 按下此键时扩展了 AM 模式选择键和存储

注意 若需使用直流电源时 请联系您最近 的 ICOM 维修中心或授权的 ICOM 代理商

-3 -

广播爱好者 m222 翻译 有建议请联系 邮件地址 m_fanqiang@

第四章 操作控制装置 3-4 天线

天线在无线电通讯中担负着非常重要的作 用 如果天线质量很差 您的接收机就不能给您 最好的性能表现 使用一副良好的天线和 50 欧姆 阻抗的馈线电缆 您会很容易地得到期望的匹配 和良好的性能表现 细心地安装一副适合您要操 作的频段的高性能的天线 并且将它架设到最大 可能的高度 尤其要注意接头的状况 接头连接 不牢靠将使天线性能变差

第一章技术规格广播爱好者m2翻译有建议请联系邮件地址整机半导体数量晶体三极管集成电路包括cpumhz澳大利亚版本mhz德国版本mhz频段频率调节控制基于中央处理器cpu的有两个可变频率调节器vfhz步进数字频率锁相环系统频率示值读数hz示值读数频率稳定性开机1hz输入电源要求使用要求的内置变换器天线阻抗欧姆不平衡式单根导线可用于0nhz重量接收机接收系统具有连续带宽控制的四重变换超外差三重变换超外差接收模式a1a3输出fsk音频信号a3中频频率第一中频mhz第二中频mhz第三中频khz第四中频除外连续带宽调节控制除外第二中频中心频率ssba3ama3mhzcwa1mhz灵敏度当前置放大器打开时ssbcwrtam小于0sinad选择性ssbcwrtkhzcwkhzamkhz镜像抑制比大于6音频输出大于3选配件已安装时技术规格为近似值并可能在不做任何通告的情况下更改第二章功能特性广播爱好者m2翻译有建议请联系邮件地址mhz之间有3mhz频段的通用频率覆盖范围接收机除此之外通过从bandupdown键给出的一个电信号指令可选的低通和带通滤波器造就了一个不需调整的系统双重1hz步进数字可变频震荡器双重数字可变频震荡器具有微机控制调节系统它们拥有两个环路的频率锁相环并且用逻辑单元来控制调节频率锁相环正常的调谐比率为1hz增量步进增加旋转主调谐轮的速度时自动转换调谐增量步进到5下调谐速度按钮提供1khz调谐步进可获得数字输出为可选来用计算机控制接收机频率和功能并且可用于合成音频输出键键盘用于简捷地设置期望的频率通过按下所期望的频率数字的数字键操作频率将无需改变波段和旋转调谐轮而被改变个可调的存储信道提供模式和频率存储内置随机存储器由一个内置锂电池后备供电可维持存储长达7年之久通过此单元可实现频率存储信道和波段的扫描在mo模式只有那些具有特定接收模式的存储信道被扫描其它的被略过数据可以在可变频震荡器vf之间可变频震荡至记忆信道或记忆信道至可变频震荡器vf之间被传递优异的接收性能应用icom开发的毫瓦分贝jmhz的第一中频实际上消除了寄生噪声影响加上使用了icom通带调谐技术pbt的高增益9mhz第二中频一个深度的中频陷波器可调的自动增益和噪音消隐可用于调节消除脉冲噪音音频音调调节控制即使在存在强干扰或高噪声水平情况下都可清晰接收通带调谐具有一个内置的由icom公司开发的通带调谐系统它允许用户连续地调节中频带通通过旋转控制钮您可

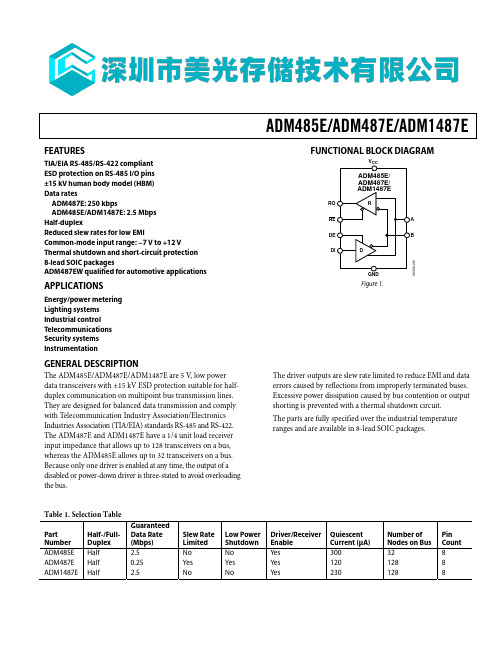

MEMORY存储芯片ADM487EARZ-REEL7中文规格书