91A1AF24A20R51中文资料

FlexiForce标准型号A201传感器说明书

DS Rev I 062821ISO 9001:2008 Compliant & 13485:2016 RegisteredThe FlexiForce A201 is our standard sensor and meets the requirements of most customers. The A201 is a thin and flexible piezoresistive force sensor that is available off-the-shelf in a variety of lengths for easy proof of concept. These ultra-thin sensors are ideal for non-intrusive force and pressure measurement in a variety of applications. The A201 can be used with our test & measurement, prototyping, and embedding electronics, including the FlexiForce Sensor Characterization Kit, FlexiForcePrototyping Kit, FlexiForce Quickstart Board, and the ELF™ System*. You can also use your own electronics, or multimeter.FlexiForce™Standard Model A201BenefitsPhysical PropertiesThickness 0.203 mm (0.008 in.)Length 191 mm (7.5 in.)** (optional trimmed lengths: 152 mm (6 in.), 102 mm (4 in.), 51 mm (2 in.))Width14 mm (0.55 in.)Sensing Area 9.53 mm (0.375 in.) diameterConnector3-pin Male Square Pin (center pin is inactive)Substrate Polyester Pin Spacing 2.54 mm (0.1 in.)✓ROHS COMPLIANT• Thin and flexible • E asy to use• C onvenient and affordable* Sensor will require an adapter/extender to connect to the ELF System. Contact yourTekscan representative for assistance.** Length does not include pins. Please add approximately 6 mm (0.25 in.) for pin length for a total length of approximately 197 mm (7.75 in).Typical PerformanceEvaluation ConditionsLinearity (Error)< ±3% of full scaleLine drawn from 0 to 50% loadRepeatability < ±2.5%Conditioned sensor, 80% of full force applied Hysteresis < 4.5% of full scaleConditioned sensor, 80% of full force appliedDrift< 5% per logarithmic time scaleConstant load of 111 N (25 lb)Response Time < 5µsecImpact load, output recorded on oscilloscope Operating Temperature -40°C - 60°C (-40°F - 140°F)Convection and conduction heat sources Durability≥ 3 million actuations Perpendicular load, room temperature, 22 N (5 lb)Temperature Sensitivity0.36%/°C (± 0.2%/°F)Conductive heating***All data above was collected utilizing an Op Amp Circuit (shown on the next page). If your application cannot allow an Op Amp Circuit, visit/flexiforce-integration-guides, or contact a FlexiForce Applications Engineer.***©Tekscan Inc., 2021. All rights reserved. Tekscan, the Tekscan logo, and FlexiForce are trademarks or registered trademarks of Tekscan, Inc.+1.617.464.4283|1.800.248.3669|****************|/flexiforceP urchase T oday o nline aT www .Tekscan .com /sToreVOLUMEDISCOUNTSA s k U sAb o u t Ou rSensing Area14 mm (.55 in.)191 mm (7.5 in.)6 mm (.25 in.)Actual size of sensorTrim LinesV OUT = -V REF * (R F / R S )• Polarity of V REF must be opposite the polarity of V SUPPLY • Sensor Resistance R S at no load is typically >1MΩ• Max recommended current is 2.5mAV OUTC 1R F V SS = GroundV DD = V SUPPLYC 1 = 47 pFR FEEDBACK (R F ) = 100kΩ POTENTIOMETER V REF OptionsSquare Wave Up to 5V , 50% Max Duty CycleDC0.25V - 1.25VMCP6004-V REF100K potentiometer and 47 pF are general recommendations; your specific sensor may be best suited with a different potentiometer andcapacitor. Testing should be performed to determine this.R SRecommended Circuit†This sensor can measure up to 4,448 N (1,000 lb). In order to measure higher forces, apply a lower drive voltage (-0.5 V, -0.25 V, etc.) and reduce the resistance of the feedback resistor (1kΩ min.). To measure lower forces, apply a higher drive voltage and increase the resistance of the feedback resistor.Sensor output is a function of many variables, including interface materials.Therefore, Tekscan recommends the user calibrate each sensor for the application.Standard Force Rangesas Tested with Circuit Shown4.4 N (0 - 1 lb)111 N (0 - 25 lb) 445 N (0 - 100 lb) †。

国产ds1991L-F5 参数说明书

SELOCKEY.SOA§ 1,152-bit secure read/write, nonvolatilememory§ Secure memory cannot be decipheredwithout matching 64-bit password§ Memory is partitioned into 3 blocks of 384bits each§ 64-bit password and ID fields for eachmemory block§ 512-bit scratchpad ensures data transferintegrity§ Operating temperature range: -40°C to+70°C§ Over 10 years of data retentionCOMMON Button FEATURES§ Unique, factory-lasered and tested 64-bitregistration number (8-bit family code + 48-bit serial number + 8-bit CRC tester) assures absolute traceability because no two parts are alike§ Multidrop controller for MicroBUS§ Digital identification and information bymomentary contact§ Chip-based data carrier compactly storesinformation§ Data can be accessed while affixed to object § Economically communicates to bus masterwith a single digital signal at 16.3k bits per second§ Standard 16 mm diameter and 1-Busprotocol ensure compatibility with Button family§ Button shape is self-aligning with cup-shaped probes§ Durable stainless steel case engraved withregistration number withstands harsh environments§ Easily affixed with self-stick adhesivebacking, latched by its flange, or locked with a ring pressed onto its rim§ Presence detector acknowledges when readerfirst applies voltageF5 MICROCAN TMAll dimensions shown in millimetersORDERING INFORMATIONTM1991L-F5F5 MicroCanTM1991MultiKey Button TMTM1991 Button DESCRIPTIONThe TM1991 MultiKey Button is a rugged read/write data carrier that acts as three separate electronic keys, offering 1,152 bits of secure, nonvolatile memory. Each key is 384 bits long with distinct 64-bit password and public ID fields (Figure 1). The password field must be matched in order to access the secure memory. Data is transferred serially via the 1-Bus protocol, which requires only a single data lead and a ground return. The 512-bit scratchpad serves to ensure integrity of data transfers to secure memory. Data should first be written to the scratchpad where it can be read back. After the data has been verified, a copy scratchpad command will transfer the data to the secure memory. This process ensures data integrity when modifying the memory. A 48-bit serial number is factory lasered into each TM1991 to provide a guaranteed unique identity which allows for absolute traceability. The family code for the TM1991 is 02h. The durable MicroCan package is highly resistant to environmental hazards such as dirt, moisture and shock. Its compact button-shaped profile is self-aligning with mating receptacles, allowing the TM1991 to be easily used by human operators. Accessories permit the TM1991 to be mounted on plastic key fobs, photo-ID badges, printed-circuit boards or any smooth surface of an object. Applications include secure access control, debit tokens, work-in-progress tracking, electronic travelers and proprietary data.OPERATIONThe TM1991 is accessed via a single data line using the 1-Bus protocol. The bus master must first provide one of the four ROM Function Commands, 1) Read ROM, 2) Match ROM, 3) Search ROM, 4) Skip ROM. These commands operate on the 64-bit lasered ROM portion of each device and can singulate a specific device if many are present on the 1-Bus line as well as indicate to the bus master how many and what types of devices are present. The protocol required for these ROM Function Commands is described in Figure 9. After a ROM Function Command is successfully executed, the memory functions that operate on the secure memory and the scratchpad become accessible and the bus master may issue any one of the six Memory Function Commands specific to the TM1991. The protocol for these Memory Function Commands is described in Figure 5. All data is read and written least significant bit first.64-BIT LASERED ROMEach TM1991 contains a unique ROM code that is 64 bits long. The first eight bits are a 1-Bus family code. The next 48 bits are a unique serial number. The last eight bits are a CRC of the first 56 bits. (Figure 2.) The 1-Bus CRC is generated using a polynomial generator consisting of a shift register and XOR gates as shown in Figure 3. The polynomial is X8 + X5 + X4 + 1. Additional information about the Dallas 1-Bus Cyclic Redundancy Check is available in the Book of TM19xx Button Standards. The shift register bits are initialized to zero. Then starting with the least significant bit of the family code, one bit at a time is shifted in. After the 8th bit of the family code has been entered, then the serial number is entered. After the 48th bit of the serial number has been entered, the shift register contains the CRC value. Shifting in the eight bits of CRC should return the shift register to all zeros.MEMORY FUNCTION COMMANDSThe TM1991 has six device-specific commands. Three scratchpad commands: Write Scratchpad, Read Scratchpad and Copy Scratchpad and three subkey commands: Write Password, Write Subkey and Read Subkey. After the device is selected, the memory function command is written to the TM1991. The command is comprised of three fields, each one byte long. The first byte is the function code field. This field defines the six commands that can be executed. The second byte is the address field. The first six bits of this field define the starting address of the command. The last two bits of this field are the subkey address code. The third byte of the command is a complement of the second byte (Figure 4).TM1991 For the first use, since the passwords actually stored in the device are unknown, the TM1991 needs to be initialized. This is done by directly writing (i. e., not through the scratchpad) the new identifier and password for the selected subkey using the Write Password command. As soon as the new identifier and password are stored in the device, further updates should be done through the scratchpad.MEMORY MAP Figure 1* Each subkey or the scratchpad has its own unique address.64-BIT LASERED ROM Figure 28-Bit CRC Code48-Bit Serial Number8-Bit Family Code (02H) MSB LSB MSB LSB MSB LSB1-BUS CRC GENERATOR Figure 3TM1991 COMMAND STRUCTURE Figure 42nd byte3rd byte Command1st byteB7 B6B5 B4 B3 B2 B1 B0writescratchpad96H readscratchpad69H 1 1any value00H to 3FHcopyscratchpad3CH0 0 0 0 0 0readSubKey66H writeSubKey99Hany value 10H to 3FHwritepassword5AH Sub-KeyNr.:00or01or100 0 0 0 0 0ones complementof 2nd byteSCRATCHPAD COMMANDSThe 64-byte read/write scratchpad of the TM1991 is not password-protected. Its normal use is to build up a data structure to be verified and then copied to a secure subkey.Write Scratchpad [96H]The Write Scratchpad command is used to enter data into the scratchpad. The starting address for the write sequence is specified in the command. Data can be continuously written until the end of the scratchpad is reached or until the TM1991 is reset. The command sequence is shown in Figure 5, first page, left column.Read Scratchpad [69H]The Read Scratchpad command is used to retrieve data from the scratchpad. The starting address is specified in the command word. Data can be continuously read until the end of the scratchpad is reached or until the TM1991 is reset. The command sequence is shown in Figure 5, first page, center column.Copy Scratchpad [3CH]The Copy Scratchpad command is used to transfer specified data blocks from the scratchpad to a selected subkey. This command should be used when data verification is required before storage in a secure subkey. Data can be transferred in single 8-byte blocks or in one large 64-byte block. There are nine valid block selector codes that are used to specify which block is to be transferred (Figure 6). As a further precaution against accidental erasure of secure data, the 8-byte password of the destination subkey must be entered. If the password does not match, the operation is terminated. After the block of data is transferred to the secure subkey, the original data in the corresponding block of the scratchpad is erased. The command sequence is shown in Figure 5, first page, right column.SUBKEY COMMANDSEach of the subkeys within the TM1991 is accessed individually. Transactions to read and write data to a secured subkey start at the address defined in the command and proceed until the device is reset or the end of the subkey is reached.Write Password [5AH]The Write Password command is used to enter the ID and password of the selected subkey. This command will erase all of the data stored in the secure area as well as overwriting the ID and password fields with the new data. The TM1991 has a built-in check to ensure that the proper subkey was selected. The sequence begins by reading the ID field of the selected subkey; the ID of the subkey to be changed is then written into the part. If the IDs do not match, the sequence is terminated. Otherwise, the subkey contents are erased and 64 bits of new ID data are written followed by a new 64-bit password. The command sequence is shown in Figure 5, 2nd page, right column.MEMORY FUNCTIONS FLOW CHART Figure 5TMTMTMTMMEMORY FUNCTIONS FLOW CHART (cont’d) Figure 5 TMTMTM TMBLOCK SELECTOR CODES OF THE TM1991 Figure 6Block Nr.Address Range LS Byte Codes MS Byte0 to 700 to 3FH56567F51575D5A7F0identifier9A9A B39D646E694C1password9A9A4C629B91694C210H to 17H9A65B3629B6E964C318H to 1FH6A6A436D6B616643420H to 27H9595BC92949E99BC528H to 2FH659A4C9D649169B3630H to 37H6565B39D646E96B3738H to 3FH65654C629B9196B3Write SubKey [99H]The Write Subkey command is used to enter data into the selected subkey. Since the subkeys are secure, the correct password is required to access them. The sequence begins by reading the ID field; the password is then written back. If the password is incorrect, the transaction is terminated. Otherwise, the data following is written into the secure area. The starting address for the write sequence is specified in the command word. Data can be continuously written until the end of the secure subkey is reached or until the TM1991 is reset. The command sequence is shown in Figure 5, 2nd page, center column. Read SubKey [66H]The Read Subkey command is used to retrieve data from the selected subkey. Since the subkeys are secure, the correct password is required to access them. The sequence begins by reading the ID field; the password is then written back. If the password is incorrect, the TM1991 will transmit random data. Otherwise the data can be read from the subkey. The starting address is specified in the command. Data can be continuously read until the end of the subkey is reached or until the TM1991 is reset. The command sequence is shown in Figure 5, 2nd page, left column.1-Bus BUS SYSTEMThe 1-Bus bus is a system which has a single bus master and one or more slaves. In all instances, the TM1991 is a slave device. The bus master is typically a micro-controller. The discussion of this bus system is broken down into three topics: hardware configuration, transaction sequence, and 1-Bus signaling (signal types and timing). A 1-Bus protocol defines bus transactions in terms of the bus state during specified time slots that are initiated on the falling edge of sync pulses from the bus master. For a more detailed protocol description, refer to Chapter 4 of the Book of TM19xx Button Standards.HARDWARE CONFIGURATIONThe 1- bus has only a single line by definition; it is important that each device on the bus be able to drive it at the appropriate time. To facilitate this, each device attached to the 1-Bus bus must have an open drain connections or 3-state outputs. The TM1991 is an open drain part with an internal circuit equivalent to that shown in Figure 7. The bus master can be the same equivalent circuit. If a bidirectional pin is not available, separate output and input pins can be tied together.The bus master requires a pullup resistor at the master end of the bus, with the bus master circuit equivalent to the one shown in Figures 8a and 8b. The value of the pullup resistor should be approximately 5 k W for short line lengths.A multidrop bus consists of a 1-Bus bus with multiple slaves attached. The 1-Bus bus has a maximum data rate of 16.3k bits per second. The idle state for the 1-Bus bus is high. If, for any reason a transactionTM1991needs to be suspended, the bus MUST be left in the idle state if the transaction is to resume. If this does not occur, and the bus is left low for more than 120 m s, one or more of the devices on the bus may be reset.EQUIVALENT CIRCUIT Figure 7BUS MASTER CIRCUIT Figure 8TMTMTMTRANSACTION SEQUENCEThe protocol for accessing the TM1991 via the 1-Bus port is as follows:§Initialization§ROM Function Command§Memory Function Command§Transaction/DataINITIALIZATIONAll transactions on the 1-Bus bus begin with an initialization sequence. The initialization sequence consists of a reset pulse transmitted by the bus master followed by presence pulse(s) transmitted by the slave(s). The presence pulse lets the bus master know that the TM1991 is on the bus and is ready to operate. For more details, see the “1-Bus Signaling” sectionROM FUNCTION COMMANDSOnce the bus master has detected a presence pulse, it can issue one of the four ROM function commands. All ROM function commands are eight bits long. A list of these commands follows (refer to flowchart in Figure 9).Read ROM [33H]This command allows the bus master to read the TM1991’s 8-bit family code, unique 48-bit serial number and 8-bit CRC. This command can be used only if there is a single TM1991 on the bus. If more than one slave is present on the bus, a data collision will occur when all slaves try to transmit at the same time (open drain will produce a wired-AND result).Match ROM [55H]The match ROM command, followed by a 64-bit ROM sequence, allows the bus master to address a specific TM1991 on a multidrop bus. Only the TM1991 that exactly matches the 64-bit ROM sequence will respond to the subsequent memory function command. All slaves that do not match the 64-bit ROM sequence will wait for a reset pulse. This command can be used with a single or multiple devices on the bus.Skip ROM [CCH]This command can save time in a single drop bus system by allowing the bus master to access the memory functions without providing the 64-bit ROM code. If more than one slave is present on the bus and a read command is issued following the Skip ROM command, data collision will occur on the bus as multiple slaves transmit simultaneously (open drain will produce a wired-AND result).Search ROM [F0H]When a system is initially brought up, the bus master might not know the number of devices on the 1-Wire bus or their 64-bit ROM codes. The Search ROM command allows the bus master to use a process of elimination to identify the 64-bit ROM codes of all slave devices on the bus. The ROM search process is the repetition of a simple 3-step routine: read a bit, read the complement of the bit, then write the desired value of that bit. The bus master performs this simple 3-step routine on each bit of the ROM. After one complete pass, the bus master knows the contents of the ROM in one device. The remaining number of devices and their ROM codes may be identified by additional passes. See Chapter 5 of the Book of TM19xx Button Standards for a comprehensive discussion of a search ROM, including an actual example.1-BUS SIGNALINGThe TM1991 requires strict protocols to ensure data integrity. The protocol consists of four types of signaling on one line: Reset Sequence with Reset Pulse and Presence Pulse, Write 0, Write 1 and Read Data. All these signals except presence pulse are initiated by the bus master. The initialization sequence required to begin any communication with the TM1991 is shown in Figure 10. A reset pulse followed by a presence pulse indicates the TM1991 is ready to send or receive data given the correct ROM command and memory function command. The bus master transmits (TX) a reset pulse (t RSTL , minimum 480 m s).The bus master then releases the line and goes into receive mode (RX). The 1-Bus bus is pulled to a high state via the pullup resistor. After detecting the rising edge on the data pin, the TM1991 waits (t PDH , 15-60m s) and then transmits the presence pulse (t PDL , 60-240 m s).ROM FUNCTIONS FLOW CHART Figure 9TMTMTMTM TMTM TMTMTMTMINITIALIZATION PROCEDURE “RESET AND PRESENCE PULSES” Figure 10480 m s £ t RSTL < ¥ *480 m s £ t RSTH < ¥(includes recovery time)15 m s £ t PDH < 60 m s 60 m s £ t PDL < 240 m s* In order not to mask interrupt signaling by other devices on the 1-Bus bus, tRSTL + t R should alwaysbe less than 960 m s.READ/WRITE TIME SLOTSThe definitions of write and read time slots are illustrated in Figure 11. All time slots are initiated by the master driving the data line low. The falling edge of the data line synchronizes the TM1991 to the master by triggering a delay circuit in the TM1991. During write time slots, the delay circuit determines when the TM1991 will sample the data line. For a read data time slot, if a “0” is to be transmitted, the delay circuit determines how long the TM1991 will hold the data line low overriding the 1 generated by the master. If the data bit is a “1”, the Button will leave the read data time slot unchanged.READ/WRITE TIMING DIAGRAM Figure 11Write-One Time Slot60 m s £ t SLOT < 120 m s1 m s £ t LOW1< 15 m s 1 m s £ t REC < ¥TMREAD/WRITE TIMING DIAGRAM (cont’d) Figure 11Write-Zero Time Slot60 m s < t LOW0 < t SLOT < 120 m s 1 m s < t REC < ¥Read-Data Time Slot60 m s £ t SLOT < 120 m s 1 m s £ t LOWR < 15 m s 0 £ t RELEASE < 45 m s 1 m s £ t REC < ¥t RDV = 15 m s t SU < 1 m sTMPHYSICAL SPECIFICATIONSSize See mechanical drawingWeight 3.3 gramsHumidity 90% RH at 50°CAltitude 10,000 feetExpected Service Life 10 years at 25°C (150 million transactions, see note 4) Safety Meets UL#913 (4th Edit.); Intrinsically Safe Apparatus,Approved under Entity Concept for use in Class I, Division1, Group A, B, C and D LocationsABSOLUTE MAXIMUM RATINGS*Voltage on any Pin Relative to Ground -0.5V to +7.0VOperating Temperature -40°C to +70°CStorage Temperature -40°C to +70°C*This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.DC ELECTRICAL CHARACTERISTICS (V PUP *=2.8V to 6.0V; -40°C to +70°C) PARAMETER SYMBOL MIN TYP MAX UNITS NOTES Input Logic Low V IL-0.30.8V1 Input Logic High V IH 2.2 6.0VOutput Logic Low @ 4 mA V OL0.4VOutput Logic High V OH V PUP 6.0V1,2 Input Resistance V IL500k W3* V PUP = external pullup voltageAC ELECTRICAL CHARACTERISTICS (-40°C to 70°C) PARAMETER SYMBOL MIN TYP MAX UNITS NOTES Time Slot Period t SLOT60120m sWrite 1 Low Time t LOW1115m sWrite 0 Low Time t LOW060120m sRead Data Valid t RDV exactly 15m sRelease Time t RELEASE01545m sRead Data Setup t SU1m s5 Recovery Time t REC1m sReset Low Time t RSTL480m sReset High Time t RSTH480m s4 Presence Detect High t PDH1560m sPresence Detect Low t PDL60240m sNOTES:1.All voltages are referenced to ground.2.V PUP= external pullup voltage to system supply.3.Input pulldown resistance to ground.4.An additional reset or communication sequence cannot begin until the reset high time has expired.5.Read data setup time refers to the time the host must pull the 1-Bus bus low to read a bit. Data isguaranteed to be valid within 1 m s of this falling edge and will remain valid for 14 m s minimum.。

目前市场可破解的部分瑞萨RENESAS R5F21系列解密型号

目前市场可破解的部分瑞萨RENESAS R5F21系列解密型号三菱单片机现属于瑞萨所有,因此很多公司在解密服务供应上会把三菱和瑞萨相混淆,作为全球半导体行业领导品牌之一,瑞萨科技的MCU市场占有率始终处于领跑水平,为了进一步开拓中国这个庞大的新兴市场,瑞萨科技正在以一种更加积极的态度来利用其日益进步的本土科技力量,公司内部采用中国本土化研发人员,并积极同许多高等院校、科研机构、整机厂家以及第三方合作伙伴开展合作。

瑞萨RENESAS芯片解密R5F212系列解密R5F21206JFP R5F21206KFP R5F21207JFP R5F21207KFPR5F21208JFP R5F21208KFP R5F2120AJFP R5F2120AKFPR5F2120CJFP R5F2120CKFP R5F21216JFP R5F21216KFPR5F21216JFP R5F21217KFP R5F21218JFP R5F21218KFPR5F2121AJFP R5F2121AKFP R5F2121CJFP R5F2121CKFPR5F21226JFP R5F21226KFP R5F21227JFP R5F21227KFPR5F212228JFP R5F21228KFP R5F2122AJFP R5F2122AKFPR5F2122CJFP R5F2122CKFP R5F21236JFP R5F21236KFPR5F21237JFP R5F21237KFP R5F21238JFP R5F21238KFPR5F2123AJFP R5F2123AKFP R5F2123CJFP R5F2123CKFPR5F21244SDFP R5F21244SNFP R5F21245SDFP R5F21245SNFPR5F21246SDFP R5F21246SNFP R5F21247SDFP R5F21247SNFPR5F21248SDFP R5F21248SNFP R5F21254SDFP R5F21254SNFPR5F21256SDFP R5F21256SNFP R5F21257SDFP R5F21257SNFPR5F21258SDFP R5F21258SNFP R5F21262DFP R5F21262JFPR5F21262KFP R5F21262NFP R5F21262SDFP R5F21262SJFPR5F21262SKFP R5F21262SNFP R5F21264DFP R5F21264JFPR5F21264KFP R5F21264NFP R5F21264SDFP R5F21264SJFPR5F21264SKFP R5F21264SNFP R5F21265DFP R5F21265JFPR5F21265KFP R5F21265NPF R5F21265SDFP R5F21265SJFPR5F21265SKFP R5F21265SNFP R5F21266DFP R5F21266JFPR5F21266KFP R5F21266NFP R5F21266SDFP R5F21266SJFPR5F21266SKFP R5F21266SNFP R5F21272DFP R5F21272JFPR5F21272KFP R5F21272NFP R5F21272SDFP R5F21272SJFPR5F21272SKFP R5F21272SNFP R5F21274DFP R5F21274JFPR5F21274KFP R5F21274NFP R5F21274SDFP R5F21274SJFPSRF21274SKFP R5F21274SNFP R5F21275DFP R5F21275JFPR5F21275KFP R5F21275NFP R5F21275SDFP R5F21275SJFPR5F21275SKFP R5F21276DFP R5F21276JFP R5F21276KFPR5F21276NFP R5F21276SDFP R5F21276SJFP R5F21276SKFPR5F21276SNFP R5F21282DSP R5F21282JSP R5F21282KSPR5F21282NSP R5F21282SDSP R5F21282SJSP R5F21282SKSPR5F21282SNSP R5F21284DSP R5F21284JSP R5F21284KSPR5F21284NSP R5F21284SDSP R5F21284SJSP R5F21284SKSP R5F21284SNSP R5F21292DSP R5F21292JSP R5F21292KSPR5F21292NSP R5F21292SDSP R5F21292SJSP R5F21292SKSP R5F21292SNSP R5F21294DSP R5F21294JSP R5F21294KSPR5F21294NSP R5F21294SDSP R5F21294SJSP R5F21291SJSPR5F21294SKSP R5F21294SNSP R5F212A7SDFA R5F212A7SDFP R5F212A7SNFP R5F212A7SNFP R5F212A8SDFA R5F212A8SDFP R5F212A8SNFA R5F212A8SNFP R5F212AASDFP R5F212AASDFP R5F212AASNFA R5F212AASNFP R5F212ACSDFA R5F212ACSDFP R5F212ACSNFA R5F212ACSNFP R5F212B7SDFA R5F212B7SDFP R5F212B7SNFP R5F212B7SNFP R5F212B8SDFA R5F212B8SDFP R5F212B8SNFA R5F212B8SNFP R5F212BASDFA R5F212BASDFP R5F212BASNFA R5F212BASNFP R5F212BCSDFA R5F212BCSDFP R5F212BCSNFP R5F212C7SDFP R5F212C7SNFP R5F212C8SDFP R5F212C8SNFP R5F212CASDFP R5F212CASNFP R5F212CCSDFP R5F212CCSNFP R5F212D7SDFP R5F212D7SNFP R5F212D8SDFP R5F212D8SNFP R5F212DASDFP R5F212DASNFP R5F212DCSDFP R5F212DCSNFP R5F212G4SDFP R5F212G4SNFP R5F212G5SDFP R5F212G5SNFP R5F212G6SDFP R5F212G6SNFP R5F212H1SDSP R5F212H1SNSP R5F212H2SDSP R5F212H2SNSP R5F212J0SDSP R5F212J0SNSP R5F212J1SDSP R5F212J1SNSP R5F212K2SDFPR5F212K2SNFP R5F212K4SDFP R5F212K4SNFP R5F212L2SDFP R5F212L2SNFP R5F212L4SDFP R5F212L4SNFP ……。

EC11B152420G中文资料(alps)中文数据手册「EasyDatasheet - 矽搜」

Size (mm)

11mm 11mm 11mm 11mm 11mm 11mm 11mm 11mm 11mm 11mm 11mm 11mm

数 豆类

15 15 15 15 15 15 15 15 20 20 20 20

掣

30 30 30 30 30 30 30 30 20 20 20 20

详细信息

卧式 卧式

立式 立式 卧式 卧式 立式 立式 卧式 卧式 立式 立式

Shaft lenght (mm)

25 mm 25 mm 25 mm 25 mm 20 mm 20 mm 20 mm 20 mm 20 mm 20 mm 20 mm 20 mm

Shaft Style

开槽 开槽 开槽 开槽

Flat Flat Flat Flat Flat Flat Flat Flat

芯片中文手册,看全文,戳

40

旋转编码器

Order

数

STEC11B01 STEC11B02 STEC11B03 STEC11B04 STEC11B05 STEC11B06 STEC11B07 STEC11B08 STEC11B09 STEC11B10 STEC11B13 STEC11B12

标准规格: 评分:

最大.工作电流:

绝缘电阻: 耐压 生命周期

10mA5 VDC 10mA 300V DC 10MΩ分钟. 300V AC 15.000 周期

轴数: 终端:

Attachement:

1

印刷线路板

No

附件

推进开关

No

推进开关

No

推进开关

No

推进开关

No

推进开关

No

推进开关

No

X9119TV14Z中文资料

Copyright Intersil Americas Inc. 2005, 2008. All Rights Reserved

All other trademarks mentioned are the property of their respective owners

X9119

Ordering Information

• Vary the frequency and duty cycle of timer ICs

• Vary the DC biasing of a pin diode attenuator in RF circuits

• Provide a control variable (I, V, or R) in feedback circuits

Functional Diagram

VCC

Features

• 1024 Resistor Taps – 10-Bit Resolution • 2-Wire Serial Interface for Write, Read, and

Transfer Operations of the Potentiometer • Wiper Resistance, 40Ω Typical @ VCC = 5V • Four Non-Volatile Data Registers • Non-Volatile Storage of Multiple Wiper Positions • Power-on Recall. Loads Saved Wiper Position on

NOTE: These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

BFR91A中文资料

13623

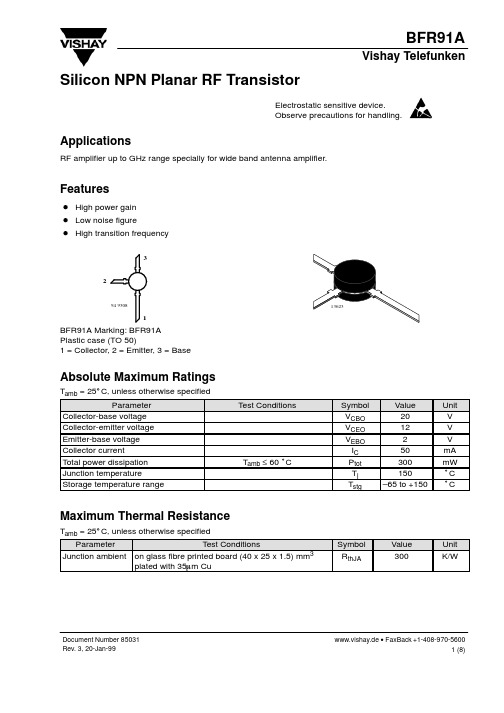

1

BFR91A Marking: BFR91A Plastic case (TO 50) 1 = Collector, 2 = Emitter, 3 = Base

Absolute Maximum Ratings

Tamb = 25_C, unless otherwise specified Parameter Collector-base voltage Collector-emitter voltage Emitter-base voltage Collector current Total power dissipation Junction temperature Storage temperature range Test Conditions Symbol VCBO VCEO VEBO IC Ptot Tj Tstg Value 20 12 2 50 300 150 –65 to +150 Unit V V V mA mW °C °C

Document Number 85031 Rev. 3, 20-Jan-99

www.vishay.de • FaxBack +1-408-970-5600 1 (8)

元器件交易网ຫໍສະໝຸດ BFR91AVishay Telefunken Electrical DC Characteristics

Tamb = 25_C, unless otherwise specified Parameter Collector cut-off current Collector-base cut-off current Emitter-base cut-off current Collector-emitter breakdown voltage Collector-emitter saturation voltage DC forward current transfer ratio Test Conditions VCE = 20 V, VBE = 0 VCB = 20 V, IE = 0 VEB = 2 V, IC = 0 IC = 1 mA, IB = 0 IC = 50 mA, IB = 5 mA VCE = 5 V, IC = 30 mA Symbol Min Typ Max Unit ICES 100 mA ICBO 100 nA IEBO 10 mA V(BR)CEO 12 V VCEsat 0.1 0.4 V hFE 40 90 150

AU9254A21中文资料

AU9254A21中⽂资料AU9254 A21USB Hub Controller Technical Reference ManualRevision 1.11997-2003 Alcor Micro Corp.All Rights ReservedCopyright NoticeCopyright 1997 - 2003Alcor Micro Corp.All Rights Reserved.Trademark AcknowledgementsThe company and product names mentioned in this document may be the trademarks or registered trademarks of their manufacturers.DisclaimerAlcor Micro Corp. reserves the right to change this product without notice.Alcor Micro Corp. makes no warranty for the use of its products and bears no responsibility for any errors that appear in this document. Specifications are subject to change without notice.Contact Information:Web site: /doc/8810114908.html/TaiwanAlcor Micro Corp.4F-1, No 200, Kang Chien Rd., Nei Hu,Taipei, Taiwan, R.O.C.Phone: 886-2-8751-1984Fax: 886-2-2659-7723San Clara Office Los Angeles Office2901 Tasman Drive, Suite 206 9400 Seventh St., Bldg. A2Santa Clara, CA 95054 Rancho Cucamonga, CA 91730Phone: (408) 845-9300 Phone: (909) 989-3060Fax: (408) 845-9086 Fax: (909) 944-0464Table of Contents1.0 Introduction (1)1.1. Description (1)1.2. Features (1)2.0 Application Block Diagram (3)3.0 Pin Assignment (5)4.0 System Architecture and Reference Design (10)4.1. AU9254 Block Diagram (10)4.2. Sample Schematics11 (11)5.0 Electrical Characteristics (15)5.1. Absolute Maximum Ratings (15)5.2. Recommended Operating Conditions (15)5.3. General DC Characteristics (15)5.4. DC Electrical Characteristics for 5 volts operation (16)5.5. DC Electrical Characteristics for 3.3 volts operation (16)5.6. Crystal Oscillator Circuit Setup for Characterization (17)5.7. USB Transceiver Characteristics (17)5.8. ESD Test Results (22)5.9. Latch-Up Test Results (23)6.0 Mechanical Information (25)6.1 Normal Size Package (Body Size 209 mil) (25)6.2 Small Size Package (Body Size 150 mil) (27)TABLE OF CONTENTS iTABLE OF CONTENTS i1.0 Introduction1.1. DescriptionThe AU9254A21 is an integrated single chip USB hub controller designed for the emerging industry-standard Universal Serial Bus (USB). The AU9254A21 supports four USB downstream ports. Each downstream port has power switch control, and over-current sensing.Single chip integration makes the AU9254A21 the most cost effective stand-alone USBhub solution available in the market. Downstream ports can be used to connect variousUSB peripheral devices, such as USB printers, modems, scanners, cameras, mice, or joysticks to the system without adding external glue logic.1.2. FeaturesFully compliant with the Universal Serial Bus Specification, version 1.1.USB hub design is compliant with Universal Serial Bus Hub Specification, revision1.1.Single chip integrated USB hub controller with embedded proprietary processor. Supports four bus-powered/self-powered downstream ports.Built-in 3.3v voltage regulator allows single +5V operating voltage, resulting in reduced overall system cost.Runs at 12Mhz frequency.28-pin SSOP package, both normal size (body size 209 mil) and smaller size (body size 150 mil) are available. INTRODUCTION 1This Page Intentionally Left BlankINTRODUCTION 22.0 Application Block DiagramThe AU9254A21 is a single chip 4-port USB hub controller. The upstream port is connected to the USB system. The downstream ports can be used for a mouse, joystick, scanner, printer or other device.KeyboardDIAGRAM 3APPLICATIONBLOCKThis Page Intentionally Left BlankDIAGRAM 4APPLICATIONBLOCKAPPLICATION BLOCK DIAGRAM 53.0 Pin AssignmentThe AU9254A21 is packaged as a 28-pin shrink small outline plastic package (SSOP). The figure on the following page shows the signal names for each of the pins on the chip. Accompanying the figure is the table that describes each of the pin signals.USB1_DP USB1_DM USB_DP USB_DM DP3_OVRCUR DP4_OVRCUR DP3_PWRUP XTAL2XTAL1AGND/GNDO NC DP2_OVRCUR SUSPEND DP1_OVRCURUSB2_DM USB2_DP USB3_DM USB3_DP USB4_DM USB4_DP DP4_PWRUP DP2_PWRUP BUS_PWREDVCC5O/VCC5IK GND5O/GND5IKVCC3V DP1_PWRUP GANGPOWERTable 3-1. Pin Descriptions of Au9254A21, 28-pin SSOPPin Name Input/Output DescriptionPinNo1 USB_DM Input/OutputUSB D- for downstream port 2; add 15K? pull-downto ground.2 USB2_DP Input/OutputUSB D+ for downstream port 2; add 15K? pull-down to ground.3 USB3_DM Input/OutputUSB D- for downstream port 3; add 15K? pull-downto ground.4 USB3_DP Input/OutputUSB D+ for downstream port 3; add 15K? pull-down to ground.5 USB4_DM Input/OutputUSB D- for downstream port 4; add 15K? pull-downto ground.6 USB4_DP Input/OutputUSB D+ for downstream port 4; add 15K? pull-down to ground.7 DP4_PWRUP Output Downstream port 4 power switch control. Active low.8 DP2_PWRUP Output Downstream port 2 power switch control. Active low.9 BUS_PWRED Input Bus power. Low indicates bus-powered.10 VCC5O/VCC5IK Power +5 V power supply.11 GND5O/GND5IK Power Ground.12 VCC3V Power 3.3V output for upstream D+ pull-up.13 DP1_PWRUP Output Downstream port 1 power switch control. Active low.14 GANGPOWER Input Ganged or individual port power selection. Add a 10k pull down for ganged power. 10k pull up forindividual power.15 DP1_OVRCUR Input Downstream port 1 over-current indicator. Active low.SYSTEM ARCHITECTURE AND REFERENCE DESIGN 6SYSTEM ARCHITECTURE AND REFERENCE DESIGN 716 SUSPEND Output Device is in suspended state: Active high. 17DP2_OVRCURInputDownstream port 2 over-current indicator. Active low.18 NC 19 AGND/GNDOPower+5 V power supply.20 XTAL_1 Input Crystal in. 21 XTAL_2 Output Crystal out. 22DP3_PWRUPOutputDownstream port 3 power switch control. Activelow.23 DP4_OVRCUR InputDownstream port 4 over-current indicator. Active low.24 DP3_OVRCUR InputDownstream port 3 over-current indicator. Active low.25 USB_DM Input/OutputUSB D- for upstream.26USB_DP Input/Output USB D+ for upstream port. Need external 1.5K ?pull-up to 3.3V. 27USB1_DM Input/Output USB D- for downstream port 1; add 15K ? pull-downto ground. 28USB1_DP Input/Output USB D+ for downstream port 1; add 15K ? pull-down to ground. This Page Intentionally Left BlankSYSTEM ARCHITECTURE AND REFERENCE DESIGN 84.0 System Architecture andReference Design4.1. AU9254A21 Block DiagramSYSTEM ARCHITECTURE AND REFERENCE DESIGN 94.2 Sample SchematicsSYSTEM ARCHITECTURE AND REFERENCE DESIGN 10SYSTEM ARCHITECTURE AND REFERENCE DESIGN 11SYSTEM ARCHITECTURE AND REFERENCE DESIGN 12SYSTEM ARCHITECTURE AND REFERENCE DESIGN 13This Page Intentionally Left BlankSYSTEM ARCHITECTURE AND REFERENCE DESIGN 14 5.0 Electrical Characteristics5.1. Absolute Maximum RatingsSYMBOL PARAMETER RATING UNITSV CC Power Supply -0.3 to 6.0 VV IN Input Voltage -0.3 to VCC+0.3 VV OUT Output Voltage -0.3 to VCC+0.3 VT STG Storage Temperature -40 to 125 ?C5.2. Recommended Operating ConditionsSYMBOL PARAMETER MIN TYP MAX UNITS5.5V5.0Supply 4.5V CC PowerVoltage 0 V CC V V IN InputTemperature -5 85 O CT OPR Operating5.3. General DC CharacteristicsSYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS I IL Input low current no pull-up or pull-down-1 1 µAI IH Input high current no pull-up or pull-down-1 1 µAI OZ Tri-state leakage current -10 10 µAcapacitance 4 ρFC IN Inputcapacitance 4 ρFC OUT OutputC BID Bi-directional buffer capacitance 4 ρF CHARACTERISTICS 15ELECTRICAL。

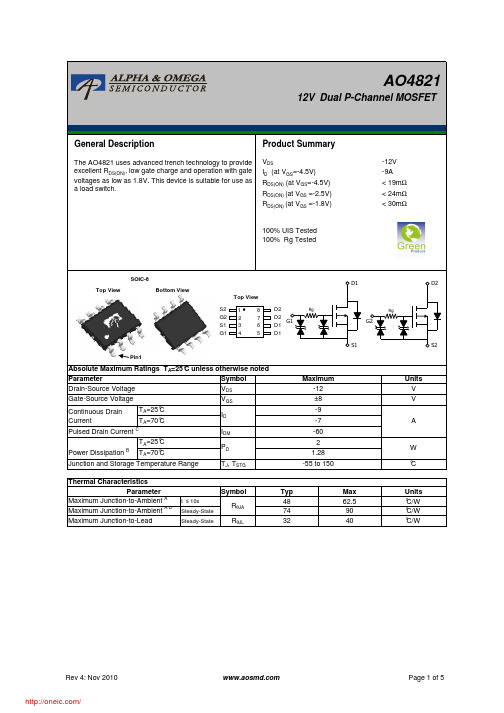

AO4821;中文规格书,Datasheet资料

100% UIS Tested 100% Rg TestedSymbol V DS V GSI DM T J , T STGSymbolt ≤ 10s Steady-State Steady-StateR θJLW 2Maximum Junction-to-Lead°C/W°C/W Maximum Junction-to-Ambient A D 329040Maximum Junction-to-Ambient A T A =25°C T A =70°C Power DissipationBP D Pulsed Drain Current CContinuous Drain CurrentT A =25°C AI D -9-7-60V MaximumUnits Parameter Absolute Maximum Ratings T A =25°C unless otherwise noted V ±8Gate-Source Voltage Drain-Source Voltage -12°C/W R θJA 487462.5°CThermal Characteristics Units ParameterTyp Max 1.28T A =70°CJunction and Storage Temperature Range -55 to 150G1S1G2S2D1D1D2D224513867 Top ViewSOIC-8Top View Bottom ViewPin1G1D11S1RgG2D2S2RgSymbolMin Typ Max Units BV DSS -12VV DS =-12V, V GS =0V-1T J =55°C-5I GSS ±10µA V GS(th)Gate Threshold Voltage -0.35-0.53-0.85V I D(ON)-60A 1619T J =125°C22271924m Ω2330m Ωg FS 45S V SD -0.56-1V I S-3A C iss 139017402100pF C oss 230334435pF C rss 120200280pF R g0.9 1.3 1.7k ΩQ g (4.5V)151923nC Q gs 3.6 4.5 5.4nC Q gd 35.37.4nC t D(on)240ns t r 580ns t D(off)7µs t f 4.2µst rr 182226ns Q rr141720nCTHIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. AOS DOES NOT ASSUME ANY LIABILITY ARISING OUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. AOS RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN,FUNCTIONS AND RELIABILITY WITHOUT NOTICE.Body Diode Reverse Recovery TimeDrain-Source Breakdown Voltage On state drain currentI D =-250µA, V GS =0V V GS =-4.5V, V DS =-5V V GS =-4.5V, I D =-9AReverse Transfer Capacitance I F =-9A, dI/dt=500A/µsV GS =0V, V DS =-6V, f=1MHz SWITCHING PARAMETERS Electrical Characteristics (T J =25°C unless otherwise noted)STATIC PARAMETERS ParameterConditions I DSS µA V DS =V GS I D =-250µA V DS =0V, V GS = ±8V Zero Gate Voltage Drain Current Gate-Body leakage current Forward Transconductance Diode Forward VoltageR DS(ON)Static Drain-Source On-Resistancem ΩI S =-1A,V GS =0VV DS =-5V, I D =-9A V GS =-1.8V, I D =-6AV GS =-2.5V, I D =-8A Gate resistanceV GS =0V, V DS =0V, f=1MHzTurn-Off Fall TimeTotal Gate Charge V GS =-4.5V, V DS =-6V, I D =-9AGate Source Charge Gate Drain Charge Body Diode Reverse Recovery Charge I F =-9A, dI/dt=500A/µsMaximum Body-Diode Continuous CurrentInput Capacitance Output CapacitanceTurn-On DelayTime DYNAMIC PARAMETERS Turn-On Rise Time Turn-Off DelayTime V GS =-4.5V, V DS =-6V, R L =0.67Ω,R GEN =3ΩA. The value of R θJA is measured with the device mounted on 1in 2FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The value in any given application depends on the user's specific board design.B. The power dissipation P D is based on T J(MAX)=150°C, using ≤ 10s junction-to-ambient thermal resistance.C. Repetitive rating, pulse width limited by junction temperature T J(MAX)=150°C. Ratings are based on low frequency and duty cycles to keep initialT J =25°C.D. The R θJA is the sum of the thermal impedence from junction to lead R θJL and lead to ambient.E. The static characteristics in Figures 1 to 6 are obtained using <300µs pulses, duty cycle 0.5% max.F. These curves are based on the junction-to-ambient thermal impedence which is measured with the device mounted on 1in 2 FR-4 board with 2oz. Copper, assuming a maximum junction temperature of T J(MAX)=150°C. The SOA curve provides a single pulse ratin g.TYPICAL ELECTRICAL AND THERMAL CHARACTERISTICS5101520Q g (nC)Figure 7: Gate-Charge Characteristics-V G S (V o l t s )24681012-V DS (Volts)Figure 8: Capacitance Characteristics C a p a c i t a n c e (p F )VdsCharge Gate Charge Test Circuit & WaveformD iode RVVddVddVR esistive S w itching Test C ircuit & W aveform s分销商库存信息: AOSAO4821。

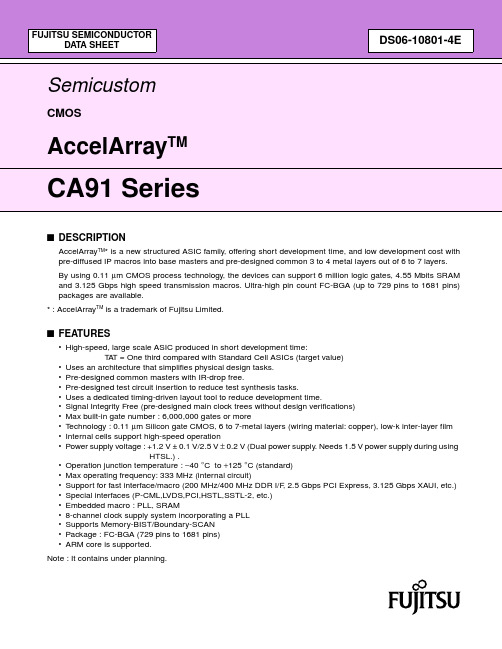

CA91中文资料

DS06-10801-4EFUJITSU SEMICONDUCTORDATA SHEETSemicustomCMOSAccelArray TMCA91 Series■DESCRIPTIONAccelArray TM * is a new structured ASIC family, offering short development time, and low development cost with pre-diffused IP macros into base masters and pre-designed common 3 to 4 metal layers out of 6 to 7 layers.By using 0.11 µm CMOS process technology, the devices can support 6 million logic gates, 4.55 Mbits SRAM and 3.125 Gbps high speed transmission macros. Ultra-high pin count FC-BGA (up to 729 pins to 1681 pins)packages are available.* : AccelArray TM is a trademark of Fujitsu Limited.■FEATURES•High-speed, large scale ASIC produced in short development time:T A T = One third compared with Standard Cell ASICs (target value)•Uses an architecture that simplifies physical design tasks.•Pre-designed common masters with IR-drop free.•Pre-designed test circuit insertion to reduce test synthesis tasks.•Uses a dedicated timing-driven layout tool to reduce development time.•Signal Integrity Free (pre-designed main clock trees without design verifications)•Max built-in gate number : 6,000,000 gates or more•T echnology : 0.11 µm Silicon gate CMOS, 6 to 7-metal layers (wiring material: copper), low-k inter-layer film •Internal cells support high-speed operation•Power supply voltage : +1.2 V ± 0.1 V/2.5 V ± 0.2 V (Dual power supply. Needs 1.5 V power supply during usingHTSL.) .•Operation junction temperature : −40 °C to +125 °C (standard) •Max operating frequency: 333 MHz (internal circuit)•Support for fast interface/macro (200 MHz/400 MHz DDR I/F , 2.5 Gbps PCI Express, 3.125 Gbps XAUI, etc.) •Special interfaces (P-CML,L VDS,PCI,HSTL,SSTL-2, etc.)•Embedded macro : PLL, SRAM•8-channel clock supply system incorporating a PLL •Supports Memory-BIST/Boundary-SCAN •Package : FC-BGA (729 pins to 1681 pins)•ARM core is supported.Note : It contains under planning.CA91 Series2■MACRO LIBRARY1.Unit cell•Flip Flop, with clear/preset (support for Mux-D Scan, with Lock up latch)•Clock Buffer•Other combination circuits (approximately 50 different types)2.APLL•Input frequency : 25 MHz to 800 MHz•Output frequency : 400 MHz to 800 MHz•User frequency : 25 MHz to 800 MHz•Phase shift : 0/90/180/270 deg.3.SRAM•1R1W-SRAM : 32 words × 40 bits•2RW-SRAM : 512 words × 40 bitsBit Select 1 : 1, 2 : 1, 4 : 1, 8 : 11 RW operation accesses specified port bit-width4.I/O•HSTL*1(250 MHz)•2.5 V L VCMOS(200 MHz (input buffer), 75 MHz to 100 MHz (output buffer))•PCML(250 MHz)•L VDS(311 MHz)•SSTL2(250 MHz)•PCI-66 *2(66 MHz)•PCI-X*2(133 MHz)•3.3 V tolerant(200 MHz (input buffer), 75 MHz to 100 MHz (output buffer)) *1 : Needs 1.5 V power supply*2 : As the I/F is 3.3V tolerant, it does not satisfy the PCI standard in some cases. Dedicated for Giga Frame•SPI-4P2 (622 Mbps to 800 Mbps)•XAUI (3.125 Gbps)•Fibre Channel (1.0 Gbps, 2.0 Gbps)•Serial Rapid IO (1.25 Gbps, 2.5 Gbps, 3.125 Gbps)•PCI Express (2.5 Gbps)5.Memory interface•DDR-SDRAM (400 Mbps)•QDR-SDRAM (400 Mbps)•Peer to Peer SDR (200 Mbps)•Peer to Peer DDR (200 Mbps)•SDR-SDRAM (167 Mbps)CA91 Series3■ABSOLUTE MAXIMUM RATINGS(VSS = 0 V)*1 : Different limit values apply for L VDS, etc.*2 : Maximum supply current in normal operation. Supply current depends on the frame or the package.*3 : Maximum output current in normal operation *4 : Required when using HSTL I/O.WARNING:Semiconductor devices can be permanently damaged by application of stress (voltage, current,temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.ParameterSymbolApplicationRating Unit Min Max Power supply voltageVDDVDDI (Core)− 0.5 1.8V VDDE(for 2.5 V CMOS I/Os, 3.3 V Tolerant I/Os) − 0.5 3.6V VDDE (for 1.5 V I/Os*4) − 0.5 3.6V Input voltage *1VI2.5 V CMOS− 0.5VDDE + 0.5( ≤ 3.6) V 3.3 V Tolerant − 0.5VDDE + 3.6( ≤ 4.0) V Output voltageVO2.5 V CMOS− 0.5VDDE + 0.5( ≤ 3.6) V 3.3 V Tolerant (H/L-State) − 0.5VDDE + 0.5( ≤ 4.0)V 3.3 V Tolerant (Z-State)− 0.5 4.0V Storage temperature Tst ⎯ − 55+ 125 °C Operation junction temperature Tj⎯− 40+ 125 °C Power supply pin current *2IDEach VDDE pin⎯180mA Each VDDI pin ⎯200mA Each VSS pin⎯200mA Output current *3IO2.5 V CMOS ⎯±10mA3.3 V Tolerant⎯±7.5mACA91 Series4■RECOMMENDED OPERATING CONDITIONS• Dual power supply (VDDI =+1.2 V ± 0.1 V, VDDE =+2.5 V ± 0.2 V, (+1.5 V ± 0.1 V))(VSS = 0 V)* : Applicable to HSTL I/O.WARNING:The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device’s electrical characteristics are warranted when the device isoperated within these ranges.Always use semiconductor devices within their recommended operating condition ranges. Operationoutside these ranges may adversely affect reliability and could result in device failure.No warranty is made with respect to uses, operating conditions, or combinations not represented onthe data sheet. Users considering application outside the listed conditions are advised to contact theirFUJITSU representatives beforehand.Parameter SymbolValueUnitMin Typ MaxPower supplyvoltagePower supply voltagefor coreVDDI 1.1 1.2 1.3V Power supply voltagefor 2.5 V I/OsVDDE 2.3 2.5 2.7V Power supply voltagefor 1.5 V I/Os *VDDE 1.4 1.5 1.6V“H” level inputvoltage2.5 V CMOSVIH1.7⎯VDDE + 0.3V3.3 V Tolerant 1.7⎯ 3.6V “L” level inputvoltage2.5 V CMOSVIL− 0.3⎯0.7V3.3 V Tolerant− 0.3⎯0.7V Operation junction temperature Tj− 40⎯+ 125°CCA91 Series5■ELECTRICAL CHARACTERISTICS1.DC CHARACTERISTICS(VDDI = 1.2 V ± 0.1 V, VDDE = 2.5 V ± 0.2 V, VSS = 0 V, Tj = − 40 °C to + 125 °C)* : The input leak current may exceed the above value if an input buffer with pull-up or pull-down resistor is used.Note : Refer to the application note for details of HSTL I/O.2.AC CHARACTERISTICS*1 : Delay time = propagation delay time, enable time, and disable time.*2 : typ can be estimated from the cell specification.*3 : Measurement conditionNote : Obtains the tpd max corresponding to the maximum junction temperature Tj.■I/O PIN CAPACITANCE(Tj = +25 °C, VDDE = VI = 0 V, f = 1 MHz)Note: The capacity depends on the package, pin positions, and similar.Parameter Symbol Conditions ValueUnitMin Typ Max “H” level output voltage VOH IOH = − 100 µA VDDE − 0.2⎯VDDE V “L” level output voltage VOL IOL = 100 µA0⎯0.2V Input leak current *IL⎯− 10⎯+ 10 µA Pull-up/Pull-down resistorRP2.5 V CMOS pin,VIL = 0 V at pull-up,VIH = VDDE at pull-down 102555k Ω3.3 V Tolerant pin,VIH = 3.0 V to 3.6 V at pull-down123385k ΩParameter Symbol ValueUnit Min Typ Max Delay timetpd *1typ *2 × tmin *3typ *2 × ttyp *3typ *2 × tmax *3nsMeasurement condition tminttyp tmax VDD = 1.2 V ± 0.1 V, VSS = 0 V, Tj = − 40 °C to + 125 °C0.731.001.43ParameterSymbol Value Unit Input pin CIN Max 16pF Output pin COUT Max 16pF I/O pin CI/OMax 16pFCA91 Series6■DESIGN METHODOLOGY•T o make development faster, the number of layers customizable in AccelArray is restricted to 3 to 4. Blocks that do not need to be redesigned for each product can be designed once and then incorporated into the architecture. As only 3 to 4 customizable layers are available for development of each product, the requirements of the layout tool are low. The requirements for timing design, where excessive complexity causes convergence to be slow, are also low. As result, the time required for design work is reduced. Primarily, tools supplied by Fujitsu are used for logic design.•A special-purpose tool is used to determine the pin layout. This produces speedy and reliable results.■SUPPORT TOOL•Frame estimationFUJITSU LIMITED : FEST A•Pin assignmentFUJITSU LIMITED : P ASTEL•Logic synthesisSynopsys, Inc. : Design Compiler, Cadence Design Systems, Inc. : BuildGates•Physical synthesisSynplicity, Inc. : Amplify AccelAllay•Format verificationCadence Design Systems, Inc. : Conformal ASIC, Synopsys, Inc. : FormalityFUJITSU LIMITED : ASSURE•Delay calculationFUJITSU LIMITED : LCADFE•Timing analysisSynopsys, Inc. : PrimeTime, FUJITSU LIMITED : GIST A•SimulationCadence Design Systems, Inc. : NC-Verilog/NC-VHDL, Synopsys, Inc. : VCS,Mentor Graphics Corporation : ModelSim, FUJITSU LIMITED : LCADFE•LayoutFUJITSU LIMITED : AccelBuilder•Power calculationFUJITSU LIMITED : PScope•Power analysisCadence Design Systems, Inc. : VoltageStorm•T est synthesisFUJITSU LIMITED : DFTPlanner•A TPGFUJITSU LIMITED : FANTCAD/X-Pax/TERBAN•ValidationFUJITSU LIMITED : LCADVL•Fault simulationFUJITSU LIMITED : FANSCADNote : The company names and the product names are the trademarks or registered trademarks of their respective owners.CA91 Series■FRAME LINE UP2 groups are provided depending on the I/O transmission speed: Mega Frame (400 Mbps) and Giga Frame(622 Mbps to 3.125 Gbps).*1 : Actual available I/O count varies with the interface type.*2 : ARM9 core is supported.* : Actual available I/O count varies with the interface type.■PACKAGEHigh pin count FC-BGAs using fine solder bump pitch technology are available for high speed data networking applications.7CA91 SeriesFUJITSU LIMITEDAll Rights Reserved.The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of Fujitsu semiconductor device; Fujitsu does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information. Fujitsu assumes no liability for any damages whatsoever arising out of the use of the information.Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of Fujitsu or any third party or does Fujitsu warrant non-infringement of any third-party’s intellectual property right or other right by using such information. Fujitsu assumes no liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of information contained herein.The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).Please note that Fujitsu will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Law of Japan, the prior authorization by Japanese government will be required for export of those products from Japan.F0506©2005 FUJITSU LIMITED Printed in Japan。

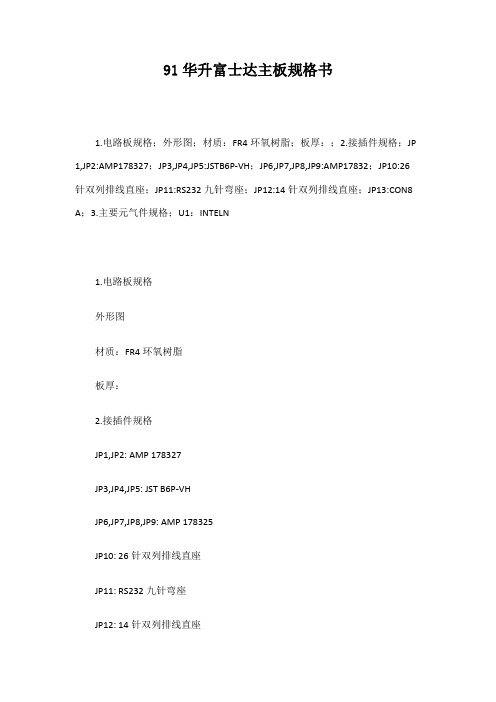

91华升富士达主板规格书

91华升富士达主板规格书1.电路板规格;外形图;材质:FR4环氧树脂;板厚:;2.接插件规格;JP 1,JP2:AMP178327;JP3,JP4,JP5:JSTB6P-VH;JP6,JP7,JP8,JP9:AMP17832;JP10:26针双列排线直座;JP11:RS232九针弯座;JP12:14针双列排线直座;JP13:CON8 A;3.主要元气件规格;U1:INTELN1.电路板规格外形图材质:FR4环氧树脂板厚:2.接插件规格JP1,JP2: AMP 178327JP3,JP4,JP5: JST B6P-VHJP6,JP7,JP8,JP9: AMP 178325JP10: 26针双列排线直座JP11: RS232九针弯座JP12: 14针双列排线直座JP13: CON8A3.主要元气件规格U1: INTEL N80C196U2: WSI PSD813F2U6,U11: PHILIPS SJA1000TU3,U5: TI TPIC6B273U7,U10,U12: FAIRCHILD 74HC245K1-K10: OMRON G6B-1114P4.端口定义★ - , - 为外部开关信号输入口,: 输入 X0,检修信号,断开为检修,闭合为自动 (输入类型不可更改): 输入 X1,上行信号. 在检修时闭合为点动上行,在司机时闭合为上行换向(输入类型不可更改): 输入 X2,下行信号. 在检修时闭合为点动下行,在司机时闭合为下行换向(输入类型不可更改): 输入 X3,上行多层终端换速开关, 2 米/秒以上电梯要求使用,(输入类型可更改,出厂值是常闭,低速电梯不用此信号时,请设置输入类型 X3为常开): 输入 X4,下行多层终端换速开关, 2 米/秒以上电梯要求使用,(输入类型可更改,出厂值是常闭,低速电梯不用此信号时,请设置输入类型X4 为常开): 输入 X5,上行限位开关 (输入类型可更改,出厂值是常闭触点) : 输入 X6,上行限位开关 (输入类型可更改,出厂值是常闭触点): 输入 X7,上行单层终端换速开关. (输入类型可更改,出厂值是常闭触点) : 输入 X8,下行单层终端换速开关. (输入类型可更改,出厂值是常闭触点) : 输入 X9,上平层干簧 (输入类型可更改,出厂值是常开触点): 输入 X10,下平层干簧 (输入类型可更改,出厂值是常开触点): 输入 X11,调速器故障输出信号 (输入类型可更改,出厂值是常开触点) : 输入 X12,消防开关 (输入类型可更改,出厂值是常开触点) : 输入 X13,安全回路继电器检测 (输入类型不可更改): 输入 X14,门锁回路继电器检测 (输入类型不可更改): 输入 X15,调速器进线接触器检测 (输入类型不可更改)★ - , - 为外部开关信号输入口和需要外部 +24V 电源输入,作为外部输入信号的隔离电源: 输入 X16,调速器出线接触器检测 (输入类型不可更改): 输入 X17,抱闸继电器检测 (输入类型不可更改): 输入 X18,门区信号输入,用于开门再平层和提前开门,闭合有效 (输入类型不可更改): 输入 X19,调速器运行信号检测,检测到此信号闭合则抱闸可以张开 (输入类型不可更改): 输入 X20,提前开门和再平层继电器检测: 输入 X21,火灾管制: 输入 X22,备用: 输入 X23,备用: 输入 X24,备用: 输入 X25,备用: X0-X25 输入信号公共端.: X0-X25 输入信号公共端.: X0-X25 隔离电路电源负极,0V.: X0-X25 隔离电路电源正极,+24V.: X0-X25 传感器用电源正极,+24V.内部与连通,负极用: X0-X25 传感器用电源正极,+24V.内部与连通,负极用★是主机板工作电源,由外部开关电源供电: 空端子: 0V 电源: +24V 电源: 0V 电源: +5V 电源: 空端子★作并联或群控用,作并联时只要连接对应两台主机的三根线: 空端子: TXV+ (+24V 电源输出): TXV- (0V 电源输出): TXA2+: TXA2-: 空端子★接外呼板和轿厢板,必须采用双绞线TXV+和TXV-用一对双绞线,TXA1+和TXA1-用另一对双绞线,推荐线径平方毫米,双绞线的绞合节距 25-35 毫米: 空端子: TXV+ (+24V 电源输出): TXV- (0V 电源输出): TXA1+: TXA1-: 空端子★是安全回路与门锁回路检测: 输入 X26 正电压端,+110V 输入,安全回路: 输入 X26 0V: 输入 X27 正电压端,+110V 输入,门锁回路: 输入 X27 0V: 输入 X28 正电压端,+110V 输入,备用: 输入 X28 0V: 空端子★ , 是继电器输出: 输出继电器 Y0,抱闸输出: 输出继电器 Y1,抱闸强激输出: 输出继电器 Y2, 调速器进线接触器★是继电器输出: 输出继电器 Y3 调速器出线接触器: 输出继电器 Y0,Y1,Y2,Y3 公共端: 输出继电器 Y4,开门继电器: 输出继电器 Y5,关门继电器: 输出继电器 Y6,提前开门或开门再平层继电器: 输出继电器 Y7,备用: 输出继电器 Y4,Y5,Y6,Y7 公共端: 输出继电器 Y8,消防输出指示指示(关门继电器1) : 输出继电器 Y9,电梯故障输出指示(开门继电器1) : 输出继电器 Y8,Y9 公共端★是 MOS 光藕隔离输出: 输出Y10,调速器上行方向: 输出Y11,调速器下行方向: 输出Y12,调速器运行使能: 输出Y13,调速器数字多段速度端口: 输出Y14,调速器数字多段速度端口: 输出Y15,调速器数字多段速度端口: 输出端口Y10-Y15的公共端Y13 Y14 Y15停车 0 0 0爬行 0 1 1检修 1 0 0单层 1 0 1双层 1 1 0多层 1 1 1★,,模拟信号输出: 模拟负载补偿信号,输出到调速器的力矩补偿端,±10V信号: 模拟速度给定,输出到调速器的速度设定端,0-10V信号: 模拟信号0V★是编码器输入接口★如果使用差分输出编码器,则,不接,适用于 CT,QuickMotion,KEB等调速器跳线 J3,J4,J5,J6 连接方式是:< - >< - >< - >< - >如果使用推挽输出编码器,请连接,到PG卡,适用于富士,安川等调速器跳线 J3,J4,J5,J6 连接方式是:< - >< - >< - >< - >: 接PG卡电源正极+12V或+15V输入: 接PG卡电源 0V.: 空端子: 空端子: 编码器 A 相,可以接受集电极开路输出或推挽输出,可接受频率为 0-100KHz: 编码器 B 相,可以接受集电极开路输出或推挽输出可接受频率为 0-100 KHz: 差分编码器 A+: 差分编码器 A-: 差分编码器 B+: 差分编码器 B-JP10: LCD 人机界面接口JP11: RS232/RS485 MODEM 远程监控接口(可以考虑成为手掌机调试接口,协议完全兼容): DCD三亿文库包含各类专业文献、生活休闲娱乐、中学教育、各类资格考试、外语学习资料、高等教育、文学作品欣赏、91华升富士达主板规格书等内容。

访客一体机参数表

1.1、18,可设置VIP人员,输入姓名,编号,如是V1P人员,则提示并打印VIP访客单,不需要选择被访人。

2.19、(可选功能)可直接在系统上进行身份证/IC卡/二维码直接授权门禁过闸机进出,离开刷闸机后系统自动签离、自动记录离开时间。

高端部件:采用比利时进口Me1exis原装红外探测器,精度高、性能稳定、质量可靠,为国内高端

配置。

金属材质:机壳采用金属材质,坚固耐用、不易变形或损坏。

产品特点

快速筛查:主动式采集红外温度数据,不需要人员操作,在小于1秒内快速完成测温。

非接触式测温:固定式红外温度传感器测量人体腕部或额头温度,避免测温人员与被测人员直接接触,引发交叉感染。

*1.6内置条码枪,红外自动连续扫描。

*1.7内置摄像头,CMOS传感器;帧速:120帧/秒;像素:130万。

*1.8内置热敏打印机:打印宽度:80mm,打印长度:26Ommo

1.9接口:USB2.0接口4个;TCP/IP网口1

1套

个;电话线接口2个;电源接口1个;音频输入输出接口各1个。

产品重量:净重10.65kgo

*2.4、拍摄存储功能:可抓拍现场图片并自动保存。(必须提供公安部检验报告或者省部级以上国家权威机构的证明文件)

2.5、登记功能:可采集访客信息,输入被访问人姓名,自动调出人员数据,完善被访人信息。

*2.6、被访人信息登记:(1)被访人姓名模糊查询,输入姓名的第一个字、或首字母、手机号(或房间号、电话号码、分机号)模糊查询,系统自动带出相应的被访人信息;(2)选择被访对象,可根据单位、部门、职工职位、职工姓名、电话等条件进行查询。

2.20、(可选功能)微信预约的访客登记时可扫描二维码通行证,系统自动带出预约信息进行快速登记。(可定制访客机内含二维码扫描器)

AMD E2 A4 A6 A9 APU处理器说明书

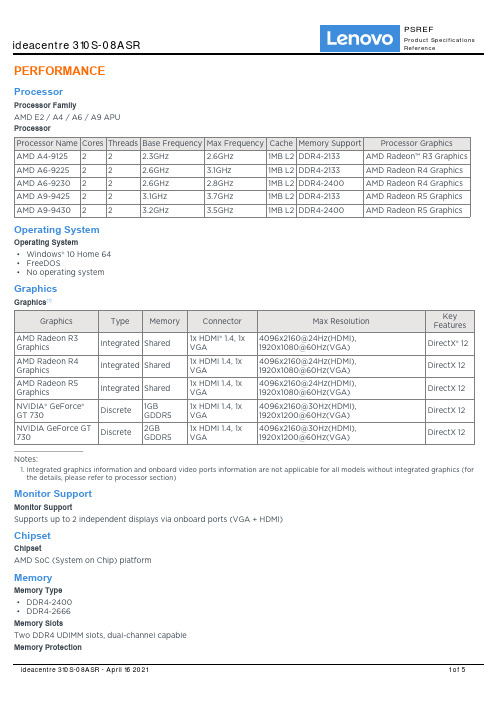

PERFORMANCEProcessorProcessor FamilyAMD E2 / A4 / A6 / A9 APUProcessorOperating SystemOperating SystemWindows® 10 Home 64••FreeDOS•No operating systemGraphicsGraphics[1]Notes:Integrated graphics information and onboard video ports information are not applicable for all models without integrated graphics (for 1.the details, please refer to processor section)Monitor SupportMonitor SupportSupports up to 2 independent displays via onboard ports (VGA + HDMI)ChipsetChipsetAMD SoC (System on Chip) platformMemoryMemory Type•DDR4-2400•DDR4-2666Memory SlotsTwo DDR4 UDIMM slots, dual-channel capableMemory ProtectionNon-ECCMax Memory[1]Up to 16GB DDR4-2666Notes:1.The max memory is based on the test results with current Lenovo® memory offerings. The system may support more memory as the technology develops.StorageStorage SupportUp to 2 drives, 1x 3.5" HDD + 1x 2.5" SSD3.5" HDD up to 2TB2.5" SSD up to 256GBRAIDNot supportStorage TypeRemovable StorageOptical•DVD burner (DVD??RW), SATA 1.5Gb/s, slim (9.0mm)•NoneCard Reader7-in-1 card reader (SD, SDHC, SDXC, MMC, MS, MS-Pro, MMC plus)••No card readerMulti-MediaAudio ChipHigh Definition (HD) Audio, Realtek® ALC662 codecPower SupplyPower SupplyDESIGNInput DeviceKeyboard•Lenovo Calliope Keyboard (USB connector), black•Lenovo Calliope Keyboard (USB connector), silver•Lenovo Calliope Wireless Keyboard, silver•No keyboardMouse•Lenovo Calliope Wireless Mouse, silverLenovo Calliope Mouse (USB connector), black••Lenovo Calliope Mouse (USB connector), silver•No mouseMechanicalButtons•Power buttonOptical drive eject button(for the models with ODD)•Form FactorSFF (8.4L)Dimensions (WxDxH)90 x 297 x 344mm (3.54 x 11.69 x 13.54 inches)Weight4.3 kg (9.5 lbs)Case ColorBlack••SilverBays•1x slim ODD bay•1x 2.5" disk bay•1x 3.5" disk bayExpansion Slots•One PCIe 2.0 x16, low-profile•One PCIe 2.0 x1, low-profile•Two M.2 slots (one for WLAN, one for SSD)CONNECTIVITYNetworkOnboard EthernetGigabit Ethernet, 1x RJ45WLAN + Bluetooth™•802.11ac 1x1 Wi-Fi + Bluetooth 4.0, M.2 card•No WLAN and BluetoothPortsFront Ports[1]•2x USB 2.0•2x USB 3.2 Gen 1•1x headphone / microphone combo jack (3.5mm)•1x microphone (3.5mm)Optional Front Ports1x card readerRear Ports[2]•2x USB 2.0•1x Ethernet (RJ-45)•1x HDMI 1.4•1x VGA•1x microphone (3.5mm)•1x line-in (3.5mm)•1x line-out (3.5mm)•1x power connectorNotes:1.The transfer speed of following ports will vary and, depending on many factors, such as the processing speed of the host device, file attributes and other factors related to system configuration and your operating environment, will be slower than theoretical speed.USB 2.0: 480 Mbit/s;USB 3.2 Gen 1 (SuperSpeed USB 5Gbps, formely USB 3.0 / USB 3.1 Gen 1): 5 Gbit/s;USB 3.2 Gen 2 (SuperSpeed USB 10Gbps, formely USB 3.1 Gen 2): 10 Gbit/s;USB 3.2 Gen 2x2 (SuperSpeed USB 20Gbps): 20 Gbit/s;Thunderbolt™ 3: 40 Gbit/s;FireWire 400: 400 Mbit/s;FireWire 800: 800 Mbit/s;For video ports on discrete graphics, please see graphics section 2.SECURITY & PRIVACYSecurityBIOS Security•Power-on password•Administrator passwordHard disk password•SERVICEWarrantyBase Warranty•1-year depot or mail-in service•1-year limited onsite service•2-year depot serviceCERTIFICATIONSGreen CertificationsGreen Certifications•ErP Lot 3•GREENGUARD®•RoHS compliant。

索尼α系摄影机电子产品说明书

フォーカスレンジ(AF駆動範囲)を切り替えるAFの駆動範囲を切り替えて、ピント合わせの時間を短縮できます。

撮影距離が一定の範囲内に限られている場合に便利です。

フォーカスレンジ切り替えスイッチで、撮影距離範囲を選択する。

••FULL•:••距離制限はありません。

全域でピント合わせが可能です。

••10m-2.4m:•10•mから2.4•mの範囲でピント合わせが可能です。

••∞-10m:••無限遠から10•mの範囲でピント合わせが可能です。

主な仕様商品名(型名)FE 200-600mm F5.6-6.3 G OSS(SEL200600G)焦点距離(mm)200-600焦点距離イメージ*1(mm)300-900レンズ群一枚17-24画角1*212°30'-4°10'画角2*28°-2°40'最短撮影距離*3(m)2.4最大撮影倍率(倍)0.2最小絞りF32-F36フィルター径(mm)95外形寸法(最大径×長さ)(約:mm)111.5×318質量(約:g)(三脚台座別)2,115手ブレ補正機能ありテレコンバーター(別売)との互換情報、装着時の主な仕様については専用サポートサイトでご確認ください。

http://support.d-imaging.sony.co.jp/www/cscs/lens_body/*1•撮像素子がAPS-Cサイズ相当のレンズ交換式デジタルカメラ装着時の35mm判換算値を表します。

*2•画角1は35mm判カメラ、画角2はAPS-Cサイズ相当の撮像素子を搭載したレンズ交換式デジタルカメラでの値を表します。

*3•最短撮影距離とは、撮像素子面から被写体までの距離を表します。

••レンズの機構によっては、撮影距離の変化に伴って焦点距離が変化する場合があります。

記載の焦点距離は撮影距離が無限遠での定義です。

同梱物(()内の数字は個数)レンズ(1)、レンズフロントキャップ(1)、レンズリヤキャップ(1)、三脚台座(1)、レンズフード(1)、レンズケース(1)、レンズストラップ(1)、印刷物一式仕様および外観は、改良のため予告なく変更することがありますが、ご了承ください。

AT91R40008中文资料