IC datasheet pdf-TPA6130A2,pdf(138-mW DirectPath Stereo Headphone Amplifier)

IC datasheet pdf-NCL30001 pdf,detasheet

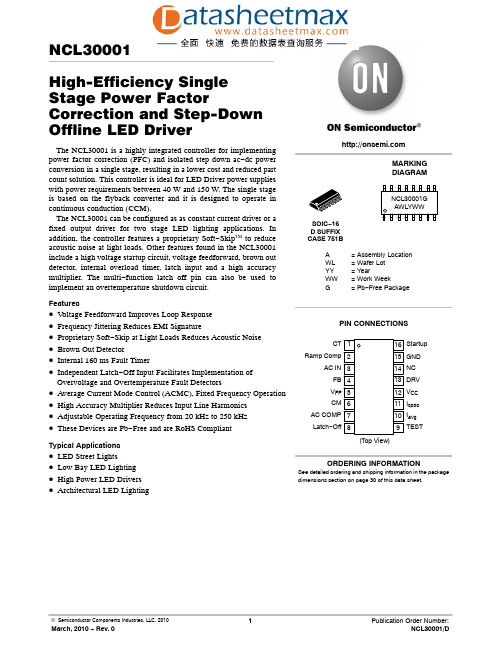

NCL30001High-Efficiency Single Stage Power FactorCorrection and Step-Down Offline LED DriverThe NCL30001 is a highly integrated controller for implementing power factor correction (PFC) and isolated step down ac −dc power conversion in a single stage, resulting in a lower cost and reduced part count solution. This controller is ideal for LED Driver power supplies with power requirements between 40 W and 150 W. The single stage is based on the flyback converter and it is designed to operate in continuous conduction (CCM).The NCL30001 can be configured as as constant current driver or a fixed output driver for two stage LED lighting applications. In addition, the controller features a proprietary Soft −Skip ™ to reduce acoustic noise at light loads. Other features found in the NCL30001include a high voltage startup circuit, voltage feedforward, brown out detector, internal overload timer, latch input and a high accuracy multiplier. The multi −function latch off pin can also be used to implement an overtemperature shutdown circuit.Features•V oltage Feedforward Improves Loop Response •Frequency Jittering Reduces EMI Signature•Proprietary Soft −Skip at Light Loads Reduces Acoustic Noise •Brown Out Detector•Internal 160 ms Fault Timer•Independent Latch −Off Input Facilitates Implementation of Overvoltage and Overtemperature Fault Detectors•Average Current Mode Control (ACMC), Fixed Frequency Operation •High Accuracy Multiplier Reduces Input Line Harmonics •Adjustable Operating Frequency from 20 kHz to 250 kHz •These Devices are Pb −Free and are RoHS Compliant Typical Applications•LED Street Lights•Low Bay LED Lighting •High Power LED Drivers •Architectural LED LightingMARKINGDIAGRAMA = Assembly Location WL = Wafer Lot YY = YearWW = Work WeekG= Pb −Free PackageSOIC −16D SUFFIX CASE 751BNCL30001G AWLYWWSee detailed ordering and shipping information in the package dimensions section on page 30 of this data sheet.ORDERING INFORMATION(Top View )V FF CT Ramp Comp AC IN FB CM AC COMP Latch −Off Startup V CC I spos TESTI avg DRV GND NC PIN CONNECTIONSStartupI sposGNDV CCLatch −DRVI avgTESTV Figure 1. Detailed Block DiagramPIN FUNCTION DESCRIPTIONPin Symbol Description1C T An external timing capacitor (C T) sets the oscillator frequency. A sawtooth between 0.2 V and 4 V sets the oscillator frequency and the gain of the multiplier.2RAMP COMP A resistor (R RC) between this pin and ground adjust the amount of ramp compensation that is added to the current signal. Ramp compensation is required to prevent subharmonic oscillations. This pin should not beleft open.3AC IN The scaled version of the full wave rectified input ac wave is connected to this pin by means of a resistive voltage divider. The line voltage information is used by the multiplier.4FB An error signal from an external error amplifier circuit is fed to this pin via an optocoupler or other isolation circuit. The FB voltage is a proportional of the load of the converter. If the voltage on the FB pin drops be-low 0.41 V (typical) the controller enters Soft−Skip to reduce acoustic noise.5VFF Feedforward input. A scaled version of the filtered rectified line voltage is applied by means of a resistive divider and an averaging capacitor. The information is used by the Reference Generator to regulate thecontroller.6CM Multiplier output. A capacitor is connected between this pin and ground to filter the modulated output of the multiplier.7AC COMP Sets the pole for the ac reference amplifier. The reference amplifier compares the low frequency compon-ent of the input current to the ac reference signal. The response must be slow enough to filter out most ofthe high frequency content of the current signal that is injected from the current sense amplifier, but fastenough to cause minimal distortion to the line frequency information. The pin should not be left open.8Latch Latch−Off input. Pulling this pin below 1.0 V (typical) or pulling it above 7.0 V (typical) latches the controller.This input can be used to implement an overvoltage detector, an overtemperature detector or both. Referto Figure 60 for a typical implementation.9TEST This pin is a TEST pin. A nominal 50K $10% resistor must be connected to GND for proper operation. 10I AVG An external resistor and capacitor connected from this terminal to ground, to set and stabilizes the gain of the current sense amplifier output that drives the ac error amplifier.11I Spos Positive current sense input. Connects to the positive side of the current sense resistor.12V CC Positive input supply. This pin connects to an external capacitor for energy storage. An internal current source supplies current from the STARTUP pin V CC. Once the voltage on V CC reaches approximately 15.3V, the current source turns off and the outputs are enabled. The drivers are disabled once V CC reachesapproximately 10.2 V. If V CC drops below 0.83 V (typical), the startup current is reduced to less than500 m A.13DRV Drive output for the main flyback power MOSFET or IGBT. DRV has a source resistance of 10.8 W (typical) and a sink resistance of 8 W (typical).14NC No Connect15GND Ground reference for the circuit.16HV Connect the rectified input line voltage directly to this pin to enable the internal startup regulator. A con-stant current source supplies current from this pin to the capacitor connected to the V CC pin, eliminatingthe need for a startup resistor. The charge current is typically 5.5 mA. Maximum input voltage is 500 V.MAXIMUM RATINGS (Notes 1 and 2)Rating Symbol Value UnitStart_up Input Voltage Start_up Input Current V HVI HV−0.3 to 500$100VmAPower Supply Input Voltage Power Supply Input Current V CCI CC−0.3 to 20$100VmALatch Input Voltage Latch Input Current V LatchI Latch−0.3 to 10$100VmAAll Other Pins Voltage All Other Pins Current −0.3 to 6.5$100VmAThermal Resistance, Junction−to−Air 0.1 in” Copper0.5 in” Copper q JA130110°C/WThermal Resistance, Junction−to−Lead RΘJL50°C/W Maximum Power Dissipation @ T A = 25°C P MAX0.77W Operating Temperature Range T J−40 to 125°C Storage Temperature Range T STG−55 to 150°C Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.1.This device contains ESD protection and exceeds the following tests:Pin 1−15: Human Body Model 2000 V per MIL−Std−883, Method 3015.Machine Model Method 200 VPin 16 is the high voltage startup of the device and is rated to the maximum rating of the part, 500 V.2.This device contains Latchup protection and exceeds ±100 mA per JEDEC Standard JESD78.NCL30001Figure 2. Typical Application SchematicR L E DTEST RC J JParameter Test Condition Symbol Min Typ Max Unit OSCILLATORFrequency f osc90100110kHz– 6.8–% Frequency Modulation in Percentageof f OSCFrequency Modulation Period– 6.8–ms Ramp Peak Voltage V CT(peak)– 4.0–V Ramp Valley Voltage V CT(valley)–0.10–V Maximum Duty Ratio R TEST = open D94−–% Ramp Compensation Peak Voltage V RCOMP(peak)–4–V AC ERROR AMPLIFIERInput Offset Voltage (Note 3)Ramp I AVG, V FB = 0 V ACV IO40–mV Error Amplifier Transconductance g m–100–m SI EA(source)2570–m A Source Current V AC COMP = 2.0 V, V AC IN = 2.0 V,V FF = 1.0 VSink Current V AC COMP = 2.0 V, V A C_IN = 2.0 V,I EA(sink)−25−70–m AV FF = 5.0 VCURRENT AMPLIFIERTEST RC J JParameter UnitMaxTypMinSymbolTest ConditionAC INPUTInput Bias Current Into ReferenceMultiplier & Current CompensationAmplifierI AC IN(IB)–0.01–m A DRIVE OUTPUTDrive Resistance (Thermally Limited)DRV SinkDRV SourceV DRV = 1 VI DRV = 100 mAR SNKR SRC––810.81824WRise Time (10% to 90%)DRV t r–40–ns Fall Time (90% to 10%)DRV t f–20–ns Driver Out Low VoltageDRV I DRV = 100 m A V DRV(low)– 1.0100mV Soft−SkipSkip Synchronization to ac LineVoltage ThresholdV ACIN Increasing, V FB = 1.5 V V SSKIP(SYNC)210267325mVSkip Synchronization to ac Line Voltage Threshold Hysteresis V ACIN Decreasing V SSKIP(SYNCHYS)–40–mVSkip Ramp Period (Note 3)t SSKIP− 2.5–ms Skip Voltage Threshold V SSKIP360410460V Skip Voltage Hysteresis V SSKIP(HYS)4590140mV Skip Transient Load Detect Threshold(Note 3)V SSKIP(TLD)− 1.75−V FEEDBACK INPUTPull−Up Current Source V FB = 0.5 V I FB600750920m A Pull−Up Resistor R FB– 6.7–k W Open Circuit Voltage V FB(open) 5.3 5.7 6.3V STARTUP AND SUPPLY CIRCUITSSupply VoltageStartup ThresholdMinimum Operating VoltageLogic Reset Voltage V CC IncreasingV CC DecreasingV CC DecreasingV CC(on)V CC(off)V CC(reset)14.39.3–15.410.27.016.311.3–VInhibit Threshold Voltage V HV = 40 V, I inhibit = 500 m A V inhibit−0.83 1.15V Inhibit Bias Current V HV = 40 V, V CC = 0.8 * V inhibit I inhibit40-500m A Minimum Startup Voltage I start = 0.5 mA, V CC = V CC(on) – 0.5 V V start(min)––40V Startup Current V CC = V CC(on) – 0.5 V, V FB = Open I start 3.0 5.628.0mAOff−State Leakage Current V HV = 400 V, T J = 25°CT J = −40°C to 125°C I HV(off)––17154080m ASupply CurrentDevice Disabled (Overload) Device SwitchingV FB = Openf OSC[ 100 kHzI CC1I CC2––0.726.251.27.2mAFAULT PROTECTIONOverload Timer t OVLD120160360ms Overload Detect Threshold V OVLD 4.7 4.9 5.2V 3.Guaranteed by DesignTEST RC J JParameter UnitMaxTypMinSymbolTest ConditionFAULT PROTECTIONBrown−Out Detect Threshold (entering fault mode)V FF Decreasing, V FB = 2.5 V,V AC IN = 2.0 VV BO(low)0.410.450.49VBrown−Out Exit Threshold (exiting fault mode)V FF Increasing, V FB = 2.5 V,V AC IN = 2.0 VV BO(high)0.570.630.69VBrown−Out Hysteresis V BO(HYS)−174−mV LATCH INPUTPull−Down Latch Voltage Threshold V Latch Decreasing V latch(low)0.90.98 1.1V Pull−Up Latch Voltage Threshold V Latch Increasing V latch(high) 5.67.08.4V Latch Propagation Delay V Latch =V latch(high)t latch(delay)305690m s Latch Clamp Current (Going Out)V Latch = 1.5 V I latch(clamp)425158m A Latch Clamp Voltage (I Latch Going In)I Latch = 50 m A V latch(clamp) 2.5 3.27 4.5V Latch−Off Current Shutdown(Going In)V Latch Increasing I latch(shdn)−95−m A 3.Guaranteed by DesignFigure 3. Oscillator Frequency (f OSC ) vs.Junction Temperature6.06.57.07.58.0−50−250255075100125150Figure 4. Oscillator Frequency Modulation in Percentage of f OSC vs. Junction TemperatureT J , JUNCTION TEMPERATURE (°C)6.06.57.07.58.0−50−250255075100125150T J , JUNCTION TEMPERATURE (°C)Figure 5. Oscillator Frequency ModulationPeriod vs. Junction Temperature3.83.853.93.954.04.054.1−50−250255075100125150T J , JUNCTION TEMPERATURE (°C)Figure 6. Ramp Peak Voltage vs. JunctionTemperatureV C T (p e a k ), O S C I L L A T O R R A M P P E A K V O L T A G E (V )9092949698100−50−250255075100125150D , M A X I M U M D U T Y R A T I O (%)Figure 7. Maximum Duty Ratio vs. JunctionTemperature T J , JUNCTION TEMPERATURE (°C)−50−2502550751001251503.83.853.93.954.04.054.1T J , JUNCTION TEMPERATURE (°C)V C O M P (p e a k ), R A M P C O M P P E A K V O L T A G E (V )Figure 8. Ramp Compensation Peak Voltagevs. Junction Temperature9095100105110−50−25255075100125150T J , JUNCTION TEMPERATURE (°C)f O S C , O S C I L L A T O R F R E Q U E N C Y (k H z )O S C I L L A T O R F R E Q U E N C Y M O D U L A T I O N P E R I O D (m s )O S C I L L A T O R F R E Q U E N C Y M O D U L A T I O N (%)505560657075808590−50−25255075100125150T J , JUNCTION TEMPERATURE (°C)I E A (S O U R C E ), E R R O R A M P L I F I E R S O U R C E C U R R E N T (m A )Figure 9. Error Amplifier Source Current vs.Junction Temperature505560657075808590−50−25255075100125150Figure 10. Error Amplifier Sink Current vs.Junction TemperatureT J , JUNCTION TEMPERATURE (°C)I E A (S I N K ), E R R O R A M P L I F I E R S I N K C U R R E N T (m A )40.042.545.047.550.052.555.057.560.0−50−25255075100125150Figure 11. Current Amplifier Input Bias Current vs. Junction TemperatureT J , JUNCTION TEMPERATURE (°C)C A V B I A S , C U R R E N T A M P L I F I E R I N P U T B I A S C U R R E N T (m A )700710720730740750760770−50−25255075100125150T J , JUNCTION TEMPERATURE (°C)Figure 12. Current Limit Threshold vs.Junction Temperature V I L I M , C U R R E N T L I M I T T H R E S H O L D (m V )5.05.25.45.65.86.0−50−250255075100125150T J , JUNCTION TEMPERATURE (°C)P W M k , P W M V O L T A G E G A I N (V /V )Figure 13. PWM Output Voltage Gain vs.Junction TemperatureFigure 14. Oscillator CS Limit Voltage Gain vs.Junction Temperature16171819202122−50−250255075100125150T J , JUNCTION TEMPERATURE (°C)I S V k , C U R R E N T L I M I T V O L T A G E G A I N (V /V )5.25T J , JUNCTION TEMPERATURE (°C)Figure 15. Oscillator Reference Generator Output Voltage vs. Junction TemperatureR G o u t , R E F E R E N C E G E N E R A T O R O U T P U T V O L T A G E (V )4.06.08.0101214−50−250255075100125150T J , JUNCTION TEMPERATURE (°C)R S N K 1, D R V S I N K D R I V E R E S I S T A N C E (W )Figure 16. DRV Sink Resistance vs. JunctionTemperature 6.08.010121416−50−250255075100125150Figure 17. DRV Source Drive Resistance vs.Junction TemperatureT J , JUNCTION TEMPERATURE (°C)R S R C 1, D R V S O U R C E R E S I S T A N C E (W )T J , JUNCTION TEMPERATURE (°C)V D R V (l o w ), D R V L O W V O L T A G E (m V )Figure 18. DRV Low Voltage vs. JunctionTemperature200220240260280300−−250255075100125150Figure 19. Skip Synchronization to ac Line Voltage Threshold vs. Junction Temperature T J , JUNCTION TEMPERATURE (°C)V S S K I P (S Y N C ), S K I P S Y N C T O A C L I N E V O L T A G E T H R E S H O L D (m V )T J , JUNCTION TEMPERATURE (°C)V S S K I P , S K I P V O L T A G E T H R E S H O L D (V )Figure 20. Skip Voltage Threshold vs. JunctionTemperature30507090110130−50−2502550751001251500.3900.3920.3940.3960.3980.4000.4020.4040.4060.4080.41080859095100−50−25255075100125150Figure 21. Skip Voltage Hysteresis vs.Junction TemperatureT J , JUNCTION TEMPERATURE (°C)V S S K I P , S K I P V O L T A G E H Y S T E R E S I S (m V )680705730755780−50−250255075100125150T J , JUNCTION TEMPERATURE (°C)I F B , F E E D B A C K P U L L −U P C U R R E N T S O U R C E (m A )Figure 22. Feedback Pull −Up Current Sourcevs. Junction Temperature5.25.45.65.86.06.2−50−250255075100125150V F B (o p e n ), F E E D B A C K O P E N C I R C U I T V O L T A G E (V )T J , JUNCTION TEMPERATURE (°C)Figure 23. Feedback Open Circuit Voltage vs.Junction Temperature14.7514.9515.1515.3515.5515.75−50−250255075100125150T J , JUNCTION TEMPERATURE (°C)V C C (o n ), S T A R T U P T H R E S H O L D (V )Figure 24. Startup Threshold vs. JunctionTemperature9.59.79.910.110.310.5−50−250255075100125150Figure 25. Minimum Operating Voltage vs.Junction TemperatureV C C (o f f ), M I N I M U M O P E R A T I N G V O L T A G E (V )T J , JUNCTION TEMPERATURE (°C)Figure 26. Inhibit Threshold Voltage vs.Junction Temperature6507007508008509009501000−50−25T J , JUNCTION TEMPERATURE (°C)V i n h i b i t , I N H I B I T T H R E S H O L D V O L T A G E (V )250270290310330350−50−250255075100125150I i n h i b i t , I N H I B I T B I A S C U R R E N T (m A )T J , JUNCTION TEMPERATURE (°C)Figure 27. Inhibit Bias Current vs. JunctionTemperature22.022.523.023.524.024.525.0V s t a r t u p (m i n ), M I N I M U M S T A R T U P V O L T A G E (V )T J , JUNCTION TEMPERATURE (°C)Figure 28. Minimum Startup Voltage vs.Junction Temperature5.05.25.45.65.86.0−50−250255075100125150T J , JUNCTION TEMPERATURE (°C)s t a r t Figure 29. Startup Current vs. JunctionTemperature1015202530−50−250255075100125150Figure 30. Off −State Leakage Current vs.Junction Temperature T J , JUNCTION TEMPERATURE (°C)I H V (o f f ), O F F −S T A T E L E A K A G E C U R R E N T (m A )650675700725750775800825850−50−250255075100125150T J , JUNCTION TEMPERATURE (°C)Figure 31. Supply Current Device Disabled (Overload) vs. Junction TemperatureI C C 1, S U P P L Y C U R R E N T D E V I C E D I S A B L E D (m A )5.755.956.156.356.556.75−50−25255075100125150T J , JUNCTION TEMPERATURE (°C)I C C 2, S U P P L Y C U R R E N T D E V I C E S W I T C H I N G (m A )Figure 32. Supply Current Device Switchingvs. Junction Temperature100120140160180200−50−250255075100125150Figure 33. Overload Timer vs. JunctionTemperatureT J , JUNCTION TEMPERATURE (°C)t O V L D , O V E R L O A D T I M E R (m s )4.54.74.95.15.35.5−50−250255075100125150T J , JUNCTION TEMPERATURE (°C)V O V L D , O V E R L O A D D E T E C T T H R E S H O L D (V )Figure 34. Overload Detect Threshold vs.Junction Temperature400420440460480500−50−250255075100125150Figure 35. Brown −Out Detect Threshold vs.Junction TemperatureT J , JUNCTION TEMPERATURE (°C)V B O (l o w ), B R O W N −O U T D E T E C T T H R E S H O L D (m V )600610620630640650−50−250255075100125150V B O (h i g h ), B R O W N −O U T E X I T T H R E S H O L D (m V )Figure 36. Brown −Out Exit Threshold vs.Junction Temperature T J , JUNCTION TEMPERATURE (°C)160165170175180−50−250255075100125150T J , JUNCTION TEMPERATURE (°C)V B O (H Y S ), B R O W N −O U T H Y S T E R E S I S (m V )Figure 37. Brown −Out Hysteresis vs. JunctionTemperature9009209409609801000−50−25255075100125150V L A T C H (l o w ), L A T C H P U L L −D O W N V O L T A G E T H R E S H O L D (m V )Figure 38. Latch Pull −Down Voltage Thresholdvs. Junction TemperatureT J , JUNCTION TEMPERATURE (°C)−50−2502550751001251506.56.76.97.17.37.5T J , JUNCTION TEMPERATURE (°C)V L A T C H (l o w _H Y S ), L A T C H P U L L −U P T H R E S H O L D (V )Figure 39. Latch Pull −Up Threshold vs.Junction Temperature6.56.76.97.17.37.5−50−250255075100125150Figure 40. Latch Pull −Up Voltage Thresholdvs. Junction TemperatureT J , JUNCTION TEMPERATURE (°C)V L A T C H (l h i g h ), L A T C H P U L L −U P V O L T A G E T H R E S H O L D (V )505254565860−50−250255075100125150T J , JUNCTION TEMPERATURE (°C)V L A T C H (d e l a y ), L A T C H P R O P A G A T I O N D E L A Y (m s )Figure 41. Latch Propagation Delay vs.Junction Temperature505152535455−50−250255075100125150Figure 42. Latch Clamp Current vs. JunctionTemperatureT J , JUNCTION TEMPERATURE (°C)I L A T C H (c l a m p ), L A T C H C L A M P C U R R E N T (m A )3.03.13.23.33.43.5−50−25255075100125150T J , JUNCTION TEMPERATURE (°C)V L A T C H (c l a m p ), L A T C H C L A M P V O L T A G E (V )Figure 43. Latch Clamp Voltage vs. JunctionTemperature 9092949698100−50−250255075100125150T J , JUNCTION TEMPERATURE (°C)V L A T C H (s h d n ), L A T C H −O F F C U R R E N T S H U T D O W N (m A )Figure 44. Latch −Off Current Shutdown vs.Junction TemperatureDETAILED DEVICE DESCRIPTIONIntroductionThe NCL30001 is a highly integrated controller combining PFC and isolated step down power conversion in a single stage, resulting in a lower cost and reduced part count solution. This controller is ideal for LED Lighting applications with power requirements between 40 W and 150 W with an output voltage greater than 12 V . The single stage is based on the flyback converter and it is designed to operate in CCM mode.Power Factor Correction (PFC) IntroductionPower factor correction shapes the input current of off −line power supplies to maximize the real power available from the mains. Ideally, the electrical appliance should present a load that emulates a pure resistor, in which case the reactive power drawn by the device is zero. Inherent in this scenario is the freedom from input current harmonics.The current is a perfect replica of the input voltage (usually a sine wave) and is exactly in phase with it. In this case the current drawn from the mains is at a minimum for the real power required to perform the needed work, and this minimizes losses and costs associated not only with the distribution of the power, but also with the generation of the power and the capital equipment involved in the process.The freedom from harmonics also minimizes interference with other devices being powered from the same source.Another reason to employ PFC in many of today’s power supplies is to comply with regulatory requirements. Today,lighting equipment in Europe must comply with IEC61000−3−2 Class C. This requirement applies to most lighting applications with input power of 25 W or greater,and it specifies the maximum amplitude of line −frequency harmonics up to and including the 39th harmonic. Moreover power factor requirements for commercial lighting is included within the ENERGY STAR ® Solid State Lighting Luminaire standard regardless of the applications power level.Typical Power Supply with PFCA typical power supply consists of a boost PFC preregulator creating an intermediate X 400 V bus and an isolated dc −dc converter producing the desired output voltage as shown in Figure 45. This architecture has two power stages.Figure 45. Typical Two Stage Power ConverterRectifier &FilterPFC PreregulatorDC −DC Converter with isolationAC Input V outA two stage architecture allows optimization of each individual power stage. It is commonly used because of designer familiarity and a vast range of availablecomponents. But, because it processes the power twice, the search is always on for a more compact and power efficient solution.The NCL30001 controller offers the convenience of shrinking the front −end converter (PFC preregulator) and the dc −dc converter into a single power processing stage as shown in Figure 46.Figure 46. Single Stage Power ConverterRectifier &FilterNCL30001 Based Single −Stage Flyback ConverterAC InputV outThis approach significantly reduces the component count.The NCL30001 based solution requires only one each of MOSFET, magnetic element, output rectifier (low voltage)and output capacitor (low voltage). In contrast, the 2−stage solution requires two or more of the above −listed components. Elimination of certain high −voltage components (e.g. high voltage capacitor and high voltage PFC diode) has significant impact on the system design. The resultant cost savings and reliability improvement are often worth the effort of designing a new converter.Single PFC StageWhile the single stage offers certain benefits, it is important to recognize that it is not a recommended solution for all requirements. The following three limitations apply to the single stage approach:•The output voltage ripple will have a 2x line frequency component (120 Hz for North American applications)that can not be eliminated easily. The cause of this ripple is the elimination of the energy storage element that is typically the boost output capacitor in the2−stage solution. The only way to reduce the ripple is to increase the output filter capacitance. The required value of capacitance is inversely proportional to the output voltage. Normally the presence of this ripple is not a issue for most LED lighting applications.•The hold −up time will not be as good as the 2−stage approach – again due to the lack of an intermediate energy storage element.•In a single stage converter, one FET processes all the power – that is both a benefit and a limitation as the stress on that main MOSFET is relatively higher.Similarly, the magnetic component (flybacktransformer/inductor) can not be optimized as well as in the 2−stage solution. As a result, potentially higher leakage inductance induces higher voltage spikes (like the one shown in Figure 47) on the MOSFET drain.This may require a MOSFET with a higher voltagerating compared to similar dc −input flybackapplications.Figure 47. Typical Drain Voltage Waveform of aFlyback Main SwitchThere are two methods to clamp the voltage spike on the main switch, a resistor −capacitor −diode (RCD) clamp or a transient voltage suppressor (TVS).RCD V outTVS V outFigure 49. TVS ClampBoth methods result in dissipation of the leakage energy in the clamping circuits – the dissipation is proportional to LI 2 where L is the leakage inductance of the transformer and I is the peak of the switch current at turn −off. An RCD snubber is simple and has the lowest cost, but constantly dissipates power. A TVS provides good voltage clamping ata slightly higher cost and dissipates power only when the drain voltage exceeds the voltage rating of the TVS.Other features found in the NCL30001 include a high voltage startup circuit, voltage feedforward, brown out detector, internal overload timer, latch input and a high accuracy multiplier.NCL30001 PFC LoopThe NCL30001 incorporates a modified version of average current mode control used for achieving the unity power factor. The PFC section includes a variable reference generator, a low frequency voltage regulation error amplifier (AC error AMP), ramp compensation (Ramp Comp) and current shaping network. These blocks are shown in the lower portion of the bock diagram (Figure 45).The inputs to the reference generator include feedback signal (FB), scaled AC input signal (AC_IN) and feedforward input (V FF ). The output of the reference generator is a rectified version of the input sine −wave scaled by the FB and V FF values. The reference amplitude is proportional to the FB and inversely proportional to the square of the V FF . This, for higher load levels and/or lower input voltage, the signal would be higher.The function of the AC error amp is to force the average current output of the current sense amplifier to match the reference generator output. The output of the AC error amplifier is compensated to prevent response to fast events.This output (V error ) is fed into the PWM comparator through a reference buffer. The PWM comparator sums the V error and the instantaneous current and compares it to a 4.0 V threshold to provide the desired duty cycle control. Ramp compensation is also added to the input signal to allow CCM operation above 50% duty cycle.High Voltage Startup CircuitThe NCL30001 internal high voltage startup circuit eliminates the need for external startup components and provides a faster startup time compared to an external startup resistor. The startup circuit consists of a constant current source that supplies current from the HV pin to the supply capacitor on the V CC pin (C CC ). The startup current (I start ) is typically 5.5 mA.The DRV driver is enabled and the startup current source is disabled once the V CC voltage reaches V CC(on), typically 15.4 V . The controller is then biased by the V CC capacitor.The drivers are disabled if V CC decays to its minimum operating threshold (V CC(off)) typically 10.2 V . Upon reaching V CC(off) the gate driver is disabled. The V CC capacitor should be sized such V CC is kept above V CC(off)while the auxiliary voltage is building up. Otherwise, the system will not start.The controller operates in double hiccup mode while in overload or V CC(off). A double hiccup fault disables the drivers, sets the controller in a low current mode and allows V CC to discharge to V CC(off). This cycle is repeated twice to minimize power dissipation in external components during。

IC datasheet pdf-MX25L1005C pdf,datasheet

MX25L1005C DATASHEET1M-BIT [x 1] CMOS SERIAL FLASH FEATURESGENERAL• Serial Peripheral Interface compatible -- Mode 0 and Mode 3• 1,048,576 x 1 bit structure• 32 Equal Sectors with 4K byte each- Any Sector can be erased individually• 2 Equal Blocks with 64K byte each- Any Block can be erased individually• Single Power Supply Operation- 2.7 to 3.6 volt for read, erase, and program operations• Latch-up protected to 100mA from -1V to Vcc +1VPERFORMANCE• High Performance- Fast access time: 85MHz serial clock- Fast program time: 1.4ms(typ.) and 5ms(max.)/page (256-byte per page)- Fast erase time: 60ms(typ.)/sector (4K-byte per sector) ; 1s(typ.) and 2s(max.)/block (64K-byte per block)• Low Power Consumption- Low active read current: 12mA(max.) at 85MHz and 4mA(max.) at 33MHz- Low active programming current: 15mA (max.)- Low active erase current: 15mA (max.)- Low standby current: 10uA (max.)• Minimum 100,000 erase/program cycles• 20 years data retentionSOFTWARE FEATURES• I nput Data Format- 1-byte Command code• Block Lock protection- The BP0~BP1 status bit defines the size of the area to be software protected against Program and Erase instructions.• A uto Erase and Auto Program Algorithm- Automatically erases and verifies data at selected sector- Automatically programs and verifies data at selected page by an internal algorithm that automatically times the program pulse widths (Any page to be programed should have page in the erased state first)• Status Register Feature• Electronic Identification- JEDEC 2-byte Device ID- RES command, 1-byte Device IDHARDWARE FEATURES• S CLK Input- Serial clock input• SI Input- Serial Data Input• SO Output- Serial Data Output• WP# pin- Hardware write protection• HOLD# pin- pause the chip without diselecting the chip• PACKAGE- 8-pin SOP (150mil)- 8-land USON (2x3x0.6mm)- All Pb-free devices are RoHS CompliantGENERAL DESCRIPTIONMX25L1005C is a CMOS 1,048,576 bit serial Flash memory, which is configured as 131,072 x 8 internally.The MX25L1005C feature a serial peripheral interface and software protocol allowing operation on a simple 3-wire bus. The three bus signals are a clock input (SCLK), a serial data input (SI), and a serial data output (SO). Serial access to the device is enabled by CS# input.The MX25L1005C provide sequential read operation on whole chip.After program/erase command is issued, auto program/ erase algorithms which program/ erase and verify the speci-fied page or sector/block locations will be executed. Program command is executed on page (256 bytes) basis, and erase command is executes on chip or sector(4K-bytes) or block(64K-bytes).To provide user with ease of interface, a status register is included to indicate the status of the chip. The status read command can be issued to detect completion status of a program or erase operation via WIP bit.When the device is not in operation and CS# is high, it is put in standby mode and draws less than 10uA DC cur-rent.The MX25L1005C utilize Macronix's proprietary memory cell, which reliably stores memory contents even after 100,000 program and erase cycles.PIN CONFIGURATIONSPIN DESCRIPTION8-PIN SOP (150mil)8-LAND USON (2x3mm)CS#SO WP#GNDVCC HOLD#SCLK SICS#SO WP#GNDVCC HOLD#SCLK SISYMBOL DESCRIPTION CS#Chip SelectSI Serial Data Input SO Serial Data Output SCLK Clock InputHOLD#Hold, to pause the device without deselecting the device VCC + 3.3V Power Supply GNDGroundDATA PROTECTIONThe MX25L1005C is designed to offer protection against accidental erasure or programming caused by spurious system level signals that may exist during power transition. During power up the device automatically resets the state machine in the standby mode. In addition, with its control register architecture, alteration of the memory con-tents only occurs after successful completion of specific command sequences. The device also incorporates sev-eral features to prevent inadvertent write cycles resulting from VCC power-up and power-down transition or system noise.• Valid command length checking: The command length will be checked whether it is at byte base and completed on byte boundary.• Write Enable (WREN) command: WREN command is required to set the Write Enable Latch bit (WEL) before other command to change data. The WEL bit will return to reset stage under following situation:- Power-up- Write Disable (WRDI) command completion- Write Status Register (WRSR) command completion- Page Program (PP) command completion- Sector Erase (SE) command completion- Block Erase (BE) command completion- Chip Erase (CE) command completion• Software Protection Mode (SPM): by using BP0-BP1 bits to set the part of Flash protected from data change.• Hardware Protection Mode (HPM): by using WP# going low to protect the BP0-BP1 bits and SRWD bit from data change.• Deep Power Down Mode: By entering deep power down mode, the flash device also is under protected from writing all commands except Release from deep power down mode command (RDP) and Read Electronic Sig-nature command (RES).Table 1. Protected Area SizesHOLD FEATUREHOLD# pin signal goes low to hold any serial communications with the device. The HOLD feature will not stop the operation of write status register, programming, or erasing in progress.The operation of HOLD requires Chip Select(CS#) keeping low and starts on falling edge of HOLD# pin signal while Serial Clock (SCLK) signal is being low (if Serial Clock signal is not being low, HOLD operation will not start until Serial Clock signal being low). The HOLD condition ends on the rising edge of HOLD# pin signal while Se-rial Clock(SCLK) signal is being low( if Serial Clock signal is not being low, HOLD operation will not end until Serial Clock being low), see Figure 1.Figure 1. Hold Condition OperationThe Serial Data Output (SO) is high impedance, both Serial Data Input (SI) and Serial Clock (SCLK) are don't care during the HOLD operation. If Chip Select (CS#) drives high during HOLD operation, it will reset the internal logic of the device. To re-start communication with chip, the HOLD# must be at high and CS# must be at low.Status bitProtect level 1Mb BP1 BP00 0 0 (none) None 0 1 1 (1 block) Block 1 1 0 2 (2 blocks) All 113 (All)AllTable 2. COMMAND DEFINITION(1) ADD=00H will output the manufacturer's ID first and ADD=01H will output device ID first.(2) It is not allowed to adopt any other code which is not in the above command definition table.Command (byte)WREN (write enable)WRDI (write disable)RDID (read identification)RDSR (read status register)WRSR (write status register)READ (read data)FAST READ(fast readdata)SE (sectorerase)1st byte 06 (hex)04 (hex)9F (hex)05 (hex)01 (hex)03 (hex)0B (hex)20 (hex)2nd byte AD1 AD1AD13rd byte AD2 AD2AD24th byte AD3 AD3AD35th byte xAction sets the (WEL) write enable latch bit resets the (WEL) write enable latch bit outputs JEDEC ID: 1-byte Manufacturer ID & 2-byte Device IDto read out the values of the status register to write new values of the status registern bytes read out until CS# goes high n bytes read out until CS# goes high to erase the selected sectorCommand(byte)BE (block erase)CE (chip erase)PP (page program)DP (Deep power down)RDP (Releasefrom deeppower down)RES (read electronic ID)REMS (readelectronicmanufacturer &device ID)1st byte D8 (hex)60 or C7 (hex)02 (hex)B9 (hex)AB (hex)AB (hex)90 (hex)2nd byte AD1 AD1 x x 3rd byte AD2 AD2 x x 4th byteAD3 AD3x ADD (1)Actionto erase the selected block to erase whole chip to program the selected pageenters deeppower down moderelease from deep power down mode to read out 1-byte Device ID output the Manufacturer ID & Device IDTable 3. Memory OrganizationBlock Sector Address Range13101F000h01FFFFh ::: 16010000h010FFFh01500F000h00FFFFh ::: 3003000h003FFFh 2002000h002FFFh 1001000h001FFFh 0000000h000FFFhDEVICE OPERATION1. Before a command is issued, status register should be checked to ensure device is ready for the intended op-eration.2. When incorrect command is inputted to this LSI, this LSI becomes standby mode and keeps the standby mode until next CS# falling edge. In standby mode, SO pin of this LSI should be High-Z.3. When correct command is inputted to this LSI, this LSI becomes active mode and keeps the active mode until next CS# rising edge.4. Input data is latched on the rising edge of Serial Clock(SCLK) and data shifts out on the falling edge of SCLK. The difference of Serial mode 0 and mode 3 is shown as Figure 2.5. For the following instructions: RDID, RDSR, READ, FAST_READ, RES and REMS the shifted-in instruction se-quence is followed by a data-out sequence. After any bit of data being shifted out, the CS# can be high. For the following instructions: WREN, WRDI, WRSR, SE, BE, CE, PP , RDP and DP the CS# must go high exactly at the byte boundary; otherwise, the instruction will be rejected and not executed.6. During the progress of Write Status Register, Program, Erase operation, to access the memory array is neglect-ed and not affect the current operation of Write Status Register, Program, Erase.Figure 2. Serial Modes SupportedNote:CPOL indicates clock polarity of Serial master, CPOL=1 for SCLK high while idle, CPOL=0 for SCLK low while not transmitting. CPHA indicates clock phase. The combination of CPOL bit and CPHA bit decides which Serial mode is supported.SCLKMSBCPHA shift inshift outSI 01CPOL(Serial mode 0)(Serial mode 3)1SO SCLKMSBCOMMAND DESCRIPTION(1) Write Enable (WREN)The Write Enable (WREN) instruction is for setting Write Enable Latch (WEL) bit. For those instructions like PP, SE, BE, CE, and WRSR, which are intended to change the device content, should be set every time after the WREN in-struction setting the WEL bit.The sequence of issuing WREN instruction is: CS# goes low→ sending WREN instruction code→ CS# goes high. (see Figure 11)(2) Write Disable (WRDI)The Write Disable (WRDI) instruction is for resetting Write Enable Latch (WEL) bit.The sequence of issuing WRDI instruction is: CS# goes low→ sending WRDI instruction code→ CS# goes high. (see Figure 12)The WEL bit is reset by following situations:- Power-up- Write Disable (WRDI) instruction completion- Write Status Register (WRSR) instruction completion- Page Program (PP) instruction completion- Sector Erase (SE) instruction completion- Block Erase (BE) instruction completion- Chip Erase (CE) instruction completion(3) Read Identification (RDID)The RDID instruction is for reading the manufacturer ID of 1-byte and followed by Device ID of 2-byte. The MXIC Manufacturer ID is C2(hex), the memory type ID is 20(hex) as the first-byte device ID, and the individual device ID of second-byte ID is as followings: 11(hex) for MX25L1005C.The sequence of issuing RDID instruction is: CS# goes low→ sending RDID instruction code → 24-bits ID data out on SO→ to end RDID operation can use CS# to high at any time during data out. (see Figure. 13)While Program/Erase operation is in progress, it will not decode the RDID instruction, so there's no effect on the cy-cle of program/erase operation which is currently in progress. When CS# goes high, the device is at standby stage.(4) Read Status Register (RDSR)The RDSR instruction is for reading Status Register Bits. The Read Status Register can be read at any time (even in program/erase/write status register condition) and continuously. It is recommended to check the Write in Progress (WIP) bit before sending a new instruction when a program, erase, or write status register operation is in progress. The sequence of issuing RDSR instruction is: CS# goes low→ sending RDSR instruction code→ Status Register data out on SO (see Figure. 14)The definition of the status register bits is as below:WIP bit. The Write in Progress (WIP) bit, a volatile bit, indicates whether the device is busy in program/erase/write status register progress. When WIP bit sets to 1, which means the device is busy in program/erase/write status register progress. When WIP bit sets to 0, which means the device is not in progress of program/erase/write status register cycle.WEL bit. The Write Enable Latch (WEL) bit, a volatile bit, indicates whether the device is set to internal write enable latch. When WEL bit sets to 1, which means the internal write enable latch is set, the device can accept program/erase/write status register instruction. When WEL bit sets to 0, which means no internal write enable latch; the de-vice will not accept program/erase/write status register instruction.BP1, BP0 bits. The Block Protect (BP1, BP0) bits, non-volatile bits, indicate the protected area(as defined in table 1) of the device to against the program/erase instruction without hardware protection mode being set. To write the Block Protect (BP1, BP0) bits requires the Write Status Register (WRSR) instruction to be executed. Those bits define the protected area of the memory to against Page Program (PP), Sector Erase (SE), Block Erase (BE) and Chip Erase(CE) instructions (only if all Block Protect bits set to 0, the CE instruction can be executed)SRWD bit. The Status Register Write Disable (SRWD) bit, non-volatile bit, is operated together with Write Protec-tion (WP#) pin for providing hardware protection mode. The hardware protection mode requires SRWD sets to 1 and WP# pin signal is low stage. In the hardware protection mode, the Write Status Register (WRSR) instruction is no longer accepted for execution and the SRWD bit and Block Protect bits (BP1, BP0) are read only.Note: 1. See the table "Protected Area Sizes".2. The endurance cycles of protect bits are 100,000 cycles; however, the tW time out spec of protect bits isrelaxed as tW = N x 15ms (N is a multiple of 10,000 cycles, ex. N = 2 for 20,000 cycles) after 10,000 cycles on those bits.bit7bit6bit5bit4bit3bit2bit1bit0SRWD (status register write protect)00)BP1 (level of protected block)BP0 (level of protected block)WEL (write enable latch)WIP (write inprogress bit)1=status register write disable(note 1)(note 1)1=write enable 0=not write enable 1=write operation 0=not in write operation(5) Write Status Register (WRSR)The WRSR instruction is for changing the values of Status Register Bits. Before sending WRSR instruction, the Write Enable (WREN) instruction must be decoded and executed to set the Write Enable Latch (WEL) bit in ad-vance. The WRSR instruction can change the value of Block Protect (BP1, BP0) bits to define the protected area of memory (as shown in table 1). The WRSR also can set or reset the Status Register Write Disable (SRWD) bit in accordance with Write Protection (WP#) pin signal. The WRSR instruction cannot be executed once the Hardware Protected Mode (HPM) is entered.The sequence of issuing WRSR instruction is: CS# goes low→ sending WRSR instruction code→ Status Register data on SI→ CS# goes high. (see Figure 15)The WRSR instruction has no effect on b6, b5, b4, b1, b0 of the status register.The CS# must go high exactly at the byte boundary; otherwise, the instruction will be rejected and not executed. The self-timed Write Status Register cycle time (tW) is initiated as soon as Chip Select (CS#) goes high. The Write in Progress (WIP) bit still can be check out during the Write Status Register cycle is in progress. The WIP sets 1 during the tW timing, and sets 0 when Write Status Register Cycle is completed, and the Write Enable Latch (WEL) bit is reset.Table 4. Protection ModesNote:1. As defined by the values in the Block Protect (BP1, BP0) bits of the Status Register, as shown in Table 1.As the above table showing, the summary of the Software Protected Mode (SPM) and Hardware Protected Mode (HPM). Software Protected Mode (SPM):- When SRWD bit=0, no matter WP# is low or high, the WREN instruction may set the WEL bit and can changethe values of SRWD, BP1, BP0. The protected area, which is defined by BP1, BP0, is at software protected mode (SPM).- When SRWD bit=1 and WP# is high, the WREN instruction may set the WEL bit can change the values ofSRWD, BP1, BP0. The protected area, which is defined by BP1, BP0, is at software protected mode (SPM)Note: If SRWD bit=1 but WP# is low, it is impossible to write the Status Register even if the WEL bit has previously been set. It is rejected to write the Status Register and not be executed.ModeStatus register condition WP# and SRWD bit status Memory Software protectionmode(SPM)Status register can be written in (WEL bit is set to "1") andthe SRWD, BP0-BP1bits can be changed WP#=1 and SRWD bit=0, or WP#=0 and SRWD bit=0, or WP#=1 and SRWD=1The protected areacannotbe program or erase.Hardware protectionmode (HPM)The SRWD, BP0-BP1 of status register bits cannot bechangedWP#=0, SRWD bit=1The protected areacannotbe program or erase.Hardware Protected Mode (HPM):- When SRWD bit=1, and then WP# is low (or WP# is low before SRWD bit=1), it enters the hardware protected mode (HPM). The data of the protected area is protected by software protected mode by BP1, BP0 and hard-ware protected mode by the WP# to against data modification.Note: to exit the hardware protected mode requires WP# driving high once the hardware protected mode is entered. If the WP# pin is permanently connected to high, the hardware protected mode can never be entered; only can use software protected mode via BP1, BP0.(6) Read Data Bytes (READ)The read instruction is for reading data out. The address is latched on rising edge of SCLK, and data shifts out on the falling edge of SCLK at a maximum frequency fR. The first address byte can be at any location. The address is automatically increased to the next higher address after each byte data is shifted out, so the whole memory can be read out at a single READ instruction. The address counter rolls over to 0 when the highest address has been reached.The sequence of issuing READ instruction is: CS# goes low→ sending READ instruction code→ 3-byte address on SI→data out on SO→ to end READ operation can use CS# to high at any time during data out. (see Figure. 16) (7) Read Data Bytes at Higher Speed (FAST_READ)The FAST_READ instruction is for quickly reading data out. The address is latched on rising edge of SCLK, and data of each bit shifts out on the falling edge of SCLK at a maximum frequency fC. The first address byte can be at any location. The address is automatically increased to the next higher address after each byte data is shifted out, so the whole memory can be read out at a single FAST_READ instruction. The address counter rolls over to 0 when the highest address has been reached.The sequence of issuing FAST_READ instruction is: CS# goes low→ sending FAST_READ instruction code→3-byte address on SI→1-dummy byte address on SI→data out on SO→ to end FAST_READ operation can use CS# to high at any time during data out. (see Figure. 17)While Program/Erase/Write Status Register cycle is in progress, FAST_READ instruction is rejected without any im-pact on the Program/Erase/Write Status Register current cycle.(8) Sector Erase (SE)The Sector Erase (SE) instruction is for erasing the data of the chosen sector to be "1". A Write Enable (WREN) in-struction must execute to set the Write Enable Latch (WEL) bit before sending the Sector Erase (SE). Any address of the sector (see table 3) is a valid address for Sector Erase (SE) instruction. The CS# must go high exactly at the byte boundary (the latest eighth of address byte been latched-in); otherwise, the instruction will be rejected and not executed.Address bits [Am-A12] (Am is the most significant address) select the sector address.The sequence of issuing SE instruction is: CS# goes low→ sending SE instruction code→ 3-byte address on SI →CS# goes high. (see Figure 19)The self-timed Sector Erase Cycle time (tSE) is initiated as soon as Chip Select (CS#) goes high. The Write in Progress (WIP) bit still can be check out during the Sector Erase cycle is in progress. The WIP sets 1 during the tSE timing, and sets 0 when Sector Erase Cycle is completed, and the Write Enable Latch (WEL) bit is reset. If the page is protected by BP1, BP0 bits, the Sector Erase (SE) instruction will not be executed on the page.(9) Block Erase (BE)The Block Erase (BE) instruction is for erasing the data of the chosen block to be "1". A Write Enable (WREN) in-struction must execute to set the Write Enable Latch (WEL) bit before sending the Block Erase (BE). Any address of the block (see table 3) is a valid address for Block Erase (BE) instruction. The CS# must go high exactly at the byte boundary (the latest eighth of address byte been latched-in); otherwise, the instruction will be rejected and not executed.The sequence of issuing BE instruction is: CS# goes low→ sending BE instruction code→ 3-byte address on SI → CS# goes high. (see Figure 20)The self-timed Block Erase Cycle time (tBE) is initiated as soon as Chip Select (CS#) goes high. The Write in Progress (WIP) bit still can be check out during the Sector Erase cycle is in progress. The WIP sets 1 during the tBE timing, and sets 0 when Sector Erase Cycle is completed, and the Write Enable Latch (WEL) bit is reset. If the page is protected by BP1, BP0 bits, the Block Erase (BE) instruction will not be executed on the page.(10) Chip Erase (CE)The Chip Erase (CE) instruction is for erasing the data of the whole chip to be "1". A Write Enable (WREN) instruc-tion must execute to set the Write Enable Latch (WEL) bit before sending the Chip Erase (CE). Any address of the sector (see table 3) is a valid address for Chip Erase (CE) instruction. The CS# must go high exactly at the byte boundary( the latest eighth of address byte been latched-in); otherwise, the instruction will be rejected and not ex-ecuted.The sequence of issuing CE instruction is: CS# goes low→sending CE instruction code→ CS# goes high. (see Fig-ure 20)The self-timed Chip Erase Cycle time (tCE) is initiated as soon as Chip Select (CS#) goes high. The Write in Progress (WIP) bit still can be check out during the Chip Erase cycle is in progress. The WIP sets 1 during the tCE timing, and sets 0 when Chip Erase Cycle is completed, and the Write Enable Latch (WEL) bit is reset. If the chip is protected by BP1, BP0 bits, the Chip Erase (CE) instruction will not be executed. It will be only executed when BP1, BP0 all set to "0".(11) Page Program (PP)The Page Program (PP) instruction is for programming the memory to be "0". A Write Enable (WREN) instruction must execute to set the Write Enable Latch (WEL) bit before sending the Page Program (PP). If the eight least sig-nificant address bits (A7-A0) are not all 0, all transmitted data which goes beyond the end of the current page are programmed from the start address if the same page (from the address whose 8 least significant address bits (A7-A0) are all 0). The CS# must keep during the whole Page Program cycle. The CS# must go high exactly at the byte boundary( the latest eighth of address byte been latched-in); otherwise, the instruction will be rejected and not executed. If more than 256 bytes are sent to the device, the data of the last 256-byte is programmed at the request page and previous data will be disregarded. If less than 256 bytes are sent to the device, the data is programmed at the request address of the page without effect on other address of the same page.The sequence of issuing PP instruction is: CS# goes low→ sending PP instruction code→ 3-byte address on SI→at least 1-byte on data on SI→CS# goes high. (see Figure 18)The self-timed Page Program Cycle time (tPP) is initiated as soon as Chip Select (CS#) goes high. The Write in Progress (WIP) bit still can be check out during the Page Program cycle is in progress. The WIP sets 1 during the tPP timing, and sets 0 when Page Program Cycle is completed, and the Write Enable Latch (WEL) bit is reset. If the page is protected by BP1, BP0 bits, the Page Program (PP) instruction will not be executed.(12) Deep Power-down (DP)The Deep Power-down (DP) instruction is for setting the device on the minimizing the power consumption (to enter-ing the Deep Power-down mode), the standby current is reduced from ISB1 to ISB2). The Deep Power-down mode requires the Deep Power-down (DP) instruction to enter, during the Deep Power-down mode, the device is not ac-tive and all Write/Program/Erase instruction are ignored. When CS# goes high, it's only in standby mode not deep power-down mode. It's different from Standby mode.The sequence of issuing DP instruction is: CS# goes low→ sending DP instruction code→CS# goes high. (see Fig-ure 22)Once the DP instruction is set, all instruction will be ignored except the Release from Deep Power-down mode (RDP) and Read Electronic Signature (RES) instruction. (RES instruction to allow the ID been read out). When Power-down, the deep power-down mode automatically stops, and when power-up, the device automatically is in standby mode. For RDP instruction the CS# must go high exactly at the byte boundary (the latest eighth bit of instruction code been latched-in); otherwise, the instruction will not executed. As soon as Chip Select (CS#) goes high, a delay of tDP is required before entering the Deep Power-down mode and reducing the current to ISB2.(13) Release from Deep Power-down (RDP), Read Electronic Signature (RES)The Release from Deep Power-down (RDP) instruction is terminated by driving Chip Select (CS#) High. When Chip Select (CS#) is driven High, the device is put in the Stand-by Power mode. If the device was not previously in the Deep Power-down mode, the transition to the Stand-by Power mode is immediate. If the device was previously in the Deep Power-down mode, though, the transition to the Stand-by Power mode is delayed by tRES2, and Chip Select (CS#) must remain High for at least tRES2(max), as specified in Table 6. Once in the Stand-by Power mode, the device waits to be selected, so that it can receive, decode and execute instructions.RES instruction is for reading out the old style of 8-bit Electronic Signature, whose values are shown as table of ID Definitions. This is not the same as RDID instruction. It is not recommended to use for new design. For new deisng, please use RDID instruction. Even in Deep power-down mode, the RDP and RES are also allowed to be executed, only except the device is in progress of program/erase/write cycle; there's no effect on the current program/erase/ write cycle in progress.The sequence is shown as Figure 23,24.The RES instruction is ended by CS# goes high after the ID been read out at least once. The ID outputs repeat-edly if continuously send the additional clock cycles on SCLK while CS# is at low. If the device was not previously in Deep Power-down mode, the device transition to standby mode is immediate. If the device was previously in Deep Power-down mode, there's a delay of tRES2 to transit to standby mode, and CS# must remain to high at least tRES2(max). Once in the standby mode, the device waits to be selected, so it can be receive, decode, and execute instruction.The RDP instruction is for releasing from Deep Power Down Mode.。

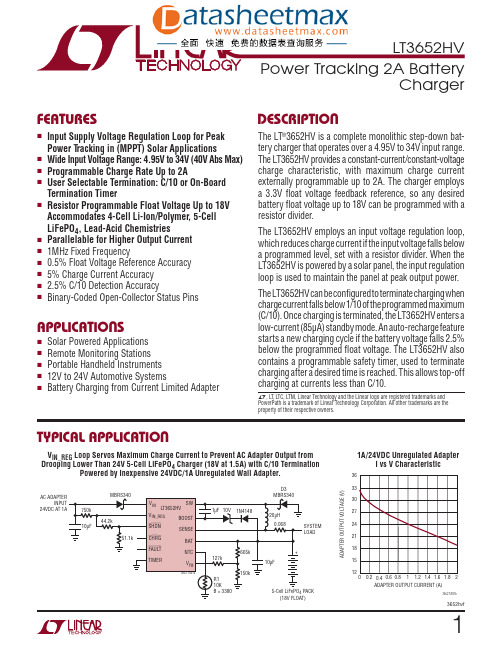

IC datasheet pdf-LT3652HV PDF DATASHEET