美光科技推出专为消费类应用设计的新型闪存

英特尔美光公布存储密度更高的新型闪存芯片

亚 科鸿 禹 星火 ( t Fr ) Sa i 系列 原 型 验 证板 最 新 r e

的 三 个 型 号 分 别 是 :t Fr— 2 ,tri — 8 0 Sa i H8 0 SaFr T 2 , r e e

SaFr— C 2 。H80 亚 科鸿 禹经 典 的 v系列 的 tri D 80 e 2是 升 级版 , 供更 齐全 的视音 频 接 口, 提 涵盖 了几 乎所 有 数 字 电视 、机 顶 盒 以及 多 媒 体 终 端 的 SC验 证 需 o 求。 T 2 8 0是专 门针对 方 兴未 艾 的 监控 SC芯 片 的 o 验证 方 案 ,并 为 P IE和 S T I高 速 接 口验 证 提 C— A AI

【【Caet i 巾 gd路 ■ hIr电c n成 u i集 e r nt Ci 国 a t

增 益 ( ntgi 跟 随缓 冲器 , ui a y n) 或另行 用 作提 供第 一 段 的 4点 低 通滤 波 器 。输 出段 能 够驱 动 高 达 2 .A 0 峰 值 电流 , 隔 离变 压器 或 简 单 的线 圈耦 合 至 主 电 经 源 。在输 出电流 为 1 .A时 , 出电压确 保 在任 意输 5 输 入端 以 1 .V或更 低 的摆 幅摆 动 ,确保 在 严 格 的环 0

皿

际上 , 体来 看 ,0 9 2 1 整 20 — 04年 ME MS扩 张速度 将快

万 A S 门 的 F G 芯 片 , 同 时 推 出 了 基 于 IC PA

Srt I 8 0的三个重 量级 新产 合 物 激励 ( A 。 在公 E P)

司 的 MA 13 X18 5取 得 成 功 的 基 础 上 , X18 6增 MA 13

的批 准 。

业 要闻 界

ufs闪存

ufs闪存UFS闪存概述随着信息技术的快速发展,存储技术也在不断进步。

其中,闪存技术作为一种非易失性存储介质,具有高速度、高密度和低功耗等特点,引起了广泛关注。

UFS(Universal Flash Storage)作为一种新兴的存储技术,具备高性能、高可靠性和广泛的应用领域,逐渐取代了传统的eMMC存储技术成为主流。

UFS闪存技术的特点1. 高速度:UFS闪存采用了2个通道以及高速的差分信号传输机制,实现更快的数据传输速度。

相比于eMMC存储技术,UFS闪存的读写速度可提高近4倍,大大提升了设备响应速度。

2. 高密度:UFS闪存支持多层堆叠技术,可以在同样的芯片面积上实现更高的存储容量。

这为移动设备提供了更大的存储空间,以满足用户对大容量媒体文件和应用程序的需求。

3. 低功耗:UFS闪存采用了新型的低功耗架构,将读写操作与控制器的其他部分分离,以降低功耗。

这不仅延长了电池寿命,还使得移动设备能够更好地实现节能。

4. 高可靠性:UFS闪存支持数据报告和写入保护等功能,可以确保数据的可靠性和安全性。

此外,UFS闪存还具备抗震动、抗干扰和抗高温等特性,适应于各种恶劣环境下的使用。

UFS闪存技术的应用1. 移动设备:UFS闪存广泛应用于智能手机、平板电脑和便携式游戏机等移动设备中。

其高速度和高可靠性,使得用户可以更快地下载应用程序、浏览网页和播放高清视频。

2. 数字相机:UFS闪存也被用于数字相机中,提供快速的连拍和高清视频录制功能。

相比于传统的SD卡,UFS闪存可以更好地满足用户对高速数据传输的需求。

3. 汽车电子:随着汽车智能化的发展,UFS闪存在汽车电子领域也有着广泛的应用。

它可以用于存储车载娱乐系统的音乐、视频和地图数据,同时还可以提供快速的系统启动和响应速度。

4. 工业控制:UFS闪存可用于工业控制领域,提供高速的数据存储和传输能力。

它适用于工厂自动化、机器人和物联网等应用场景,能够有效提高设备的响应速度和可靠性。

美光3D NAND TLC 750GB闪存硬盘上市

龙源期刊网

美光3D NAND TLC 750GB闪存硬盘上市作者:

来源:《电脑爱好者》2016年第13期

在四大NAND豪门中,三星3D NAND闪存量产最早,Intel、美光算是比较晚的了,今年才有3D NAND SSD发布,其中Intel目前只在企业级产品上应用了3D NAND,美光则是在最近推出的MX300硬盘应用了自家3D NAND闪存,容量直接杀向750GB。

美光官方数据显示MX300的连续读取速度530MB/s,写入速度510MB/s,4K读取为93000 IOPS,4K写入为83000 IOPS,硬盘总写入量可达220TB,支持Momentum Cache缓存模式,支持AES-256bit加密,质保三年。

点评:单从指标上看,美光MX300硬盘的表现可谓一般,总体性能不如三星850 Evo。

不过好在价格合适,750GB的建议零售价仅为199.99美元(约合人民币1314元)。

美光看好CMOS影像传感器在安防监控领域的应用

h什 n . hA A I ^川

r,- a 一 , ^ m -r, ;m 、

维普资讯

L 企与品 一 业产

及高速率产品等,MO 已超过了 C D 美光除了把 C S C 。 所有的相机功能都集成到一块芯片上 ,即从光子 的 捕捉到数码 比特 的输出外 ,M S C O 影像传感器还可

多的公 司” 中名列第六位 。 相比其他大公 司, 美光 的 雇员数排名第十, 只有 2 90 , 0 0 人 而美光每千人获得 的专利数排名第一。

20 年 1 月 收 购美 国 P o bt 技公 司后 , 01 1 ht i科 o 开

影像传感器出货量的 4 %。目前在美光涉足的产品 0

在 其他产 品领域 的增 长非 常快 。 光 于 20 年 进 入 美 01

的供应 商 ,06 4月份美光 C O 产 品已占全球 20 年 M S 影像传感器市场的 3 %, 6 到现在 已超过 了 4 %。从 0

市场 细 分来 看 , 全球 有 1 / 3的拍 照 手机 、 超过 6 %的 0

维普资讯

【 国 集 成 电 路 l 】

C hi nt na I egr ed C icui at r t

企 业 与 产 品

美光看好 CMOS影像传感器 在安防监控领域的应用

本刊记者 胡 亢

美 国 美 光 科 技 有 限 公 司 ( c ̄ Mir1 ) 3

当记者谈到 C D为何还 存在 时 ,al aahr C P u G lg e 表 l 示 , C D的存在是因为这些公司本身又做 C D芯 “C C 片, 同时又做产品, 所以依然在采用 C D C 。目前数码 相机 C O M S主要集 中在 50万像素 以下 和 80万 0 0 像 素以上的领域 ,而 C D只集 中在 5 0 80万之 C 0—0 间。 我认为 , 随着高清晰成像技术的发展 ,C C D越来 越难满足这种要求 , 最终会被 C O 所取代。” M S

3-bit-per-cell NAND闪存

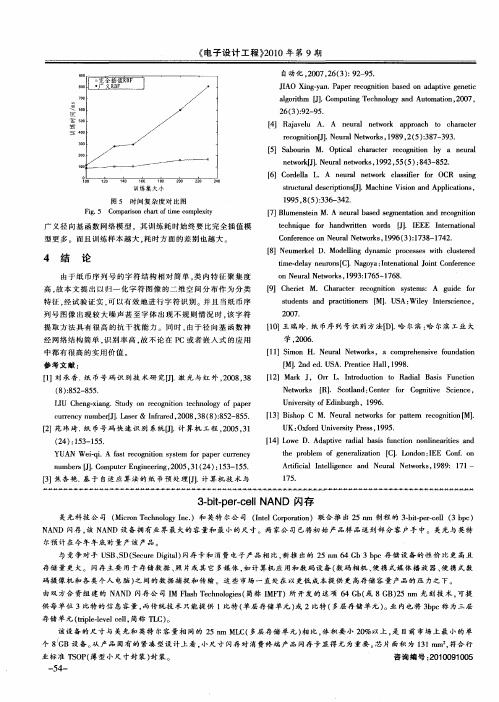

特 征 , 试 验证 实 , 以 有 效 地进 行字 符 识 别 。 且 当纸 币 序 经 可 并 列 号 图像 出 现较 大 噪 声 甚 至 字 体 出 现 不 规 则 情 况 时 , 字 符 该 提 取 方 法 具 有 很 高 的 抗 干 扰 能 力 。同 时 , 于径 向 基 函 数 神 由

N N 闪存 , N N 设 备拥 有 业界 最 大的 容 量 和 最 小 的 尺 寸 。两 家公 司 已将 初 始 产 品 样 品 送 到 部 分 客 户 手 中 。美 光 与 英特 A D 该 A D

尔预 计 在 今 年 年 底 时量 产该 产品 。

与 竞 争 对 手 U B、D Scr ii1闪存 卡和 消 费 电子 产 品 相 比 , 推 出的 2 m 6 b3b c存 储 设 备 的 性 价 比更 高且 S S (eueDgt ) a 新 5n 4G p 存 储 量 更 大 。 闪存 主要 用 于存 储 数 据 、 片或 其 它 多媒 体 , 计 算 机 应 用 和数 码 设 备 ( 码 相 机 、 携 式媒 体播 放 器 、 携 式 数 照 如 数 便 便

(4 :5 — 5 . 2 ) 1 3 1 5

YUAN e— i W iq .A a tr c g to y tm o a rc r nc fs e o niin s se fr p pe ure y

【3 i o 1】Bs p C M.N ua n tok rpt r eont nM】 h e r e rsf a e rcg io 【 . l w o tn i

经 网络 结 构 简 单 , 别 率 高 , 不 论 在 P 识 故 C或 者 嵌 入 式 的 应 用

【0 王 瑞 玲 . 币序 列 号 识 别 方 法【1哈 尔滨 : 尔滨 工 业 大 11 纸 D. 哈

MEMORY存储芯片M25P80-VMW6TG中文规格书

SUMMARY DESCRIPTIONThe M25P80 is a 8 Mbit (1M x 8) Serial Flash Memory, with advanced write protection mecha-nisms, accessed by a high speed SPI-compatible bus.The memory can be programmed 1 to 256 bytes at a time, using the Page Program instruction.The memory is organized as 16 sectors, each con-taining 256 pages. Each page is 256 bytes wide.Thus, the whole memory can be viewed as con-sisting of 4096 pages, or 1,048,576 bytes.The whole memory can be erased using the Bulk Erase instruction, or a sector at a time, using the Sector Erase instruction.Table 1. Signal NamesNote: 1.There is an exposed die paddle on the underside of theMLP8 package. This is pulled, internally, to V SS , and must not be allowed to be connected to any other voltage or signal line on the PCB.2.See PACKAGE MECHANICAL section for package di-mensions, and how to identify pin-1.Note: 1.DU = Don’t Use2.See PACKAGE MECHANICAL section for package di-mensions, and how to identify pin-1.C Serial ClockD Serial Data Input QSerial Data Output SChip Select W Write Protect HOLD HoldV CC Supply Voltage V SSGroundINSTRUCTIONSAll instructions, addresses and data are shifted in and out of the device, most significant bit first. Serial Data Input (D) is sampled on the first rising edge of Serial Clock (C) after Chip Select (S) is driven Low. Then, the one-byte instruction code must be shifted in to the device, most significant bit first, on Serial Data Input (D), each bit being latched on the rising edges of Serial Clock (C). The instruction set is listed in Table 4..Every instruction sequence starts with a one-byte instruction code. Depending on the instruction, this might be followed by address bytes, or by data bytes, or by both or none.In the case of a Read Data Bytes (READ), Read Data Bytes at Higher Speed (Fast_Read), Read Status Register (RDSR) or Release from Deep Power-down, and Read Electronic Signature (RES) instruction, the shifted-in instruction se-quence is followed by a data-out sequence. Chip Select (S) can be driven High after any bit of the data-out sequence is being shifted out.In the case of a Page Program (PP), Sector Erase (SE), Bulk Erase (BE), Write Status Register (WRSR), Write Enable (WREN), Write Disable (WRDI) or Deep Power-down (DP) instruction, Chip Select (S) must be driven High exactly at a byte boundary, otherwise the instruction is reject-ed, and is not executed. That is, Chip Select (S) must driven High when the number of clock pulses after Chip Select (S) being driven Low is an exact multiple of eight.All attempts to access the memory array during a Write Status Register cycle, Program cycle or Erase cycle are ignored, and the internal Write Status Register cycle, Program cycle or Erase cy-cle continues unaffected.Table 4. Instruction SetInstruction Description One-byte Instruction Code AddressBytesDummyBytesDataBytesWREN Write Enable0000 011006h0 0 0 WRDI Write Disable0000 010004h0 0 0 RDSR Read Status Register 0000 010105h0 0 1 to ∞WRSR Write Status Register 0000 000101h0 0 1 READ Read Data Bytes0000 001103h30 1 to ∞FAST_READ Read Data Bytes at Higher Speed0000 10110Bh31 1 to ∞PP Page Program0000 001002h30 1 to 256 SESectorErase11011000D8h300 BE Bulk Erase 1100 0111C7h0 0 0 DP Deep Power-down1011 1001B9h0 0 0RES Release from Deep Power-down,and Read Electronic Signature1010 1011ABh0 31to∞Release from Deep Power-down0 00Read Data Bytes at Higher Speed(FAST_READ)The device is first selected by driving Chip Select (S)Low. The instruction code for the Read Data Bytes at Higher Speed (FAST_READ) instruction is followed by a 3-byte address (A23-A0) and a dummy byte, each bit being latched-in during the rising edge of Serial Clock (C). Then the memory contents, at that address, is shifted out on Serial Data Output (Q), each bit being shifted out, at a maximum frequency f C, during the falling edge of Serial Clock (C).The instruction sequence is shown in Figure 14.. The first byte addressed can be at any location. The address is automatically incremented to the next higher address after each byte of data is shift-ed out. The whole memory can, therefore, be read with a single Read Data Bytes at Higher Speed (FAST_READ) instruction. When the highest ad-dress is reached, the address counter rolls over to 000000h, allowing the read sequence to be contin-ued indefinitely.The Read Data Bytes at Higher Speed (FAST_READ) instruction is terminated by driving Chip Select (S) High. Chip Select (S) can be driv-en High at any time during data output. Any Read Data Bytes at Higher Speed (FAST_READ) in-struction, while an Erase, Program or Write cycle is in progress, is rejected without having any ef-fects on the cycle that is in progress.Figure 14. Read Data Bytes at Higher Speed (FAST_READ)Instruction Sequence and Data-OutM25P80Page Program (PP)The Page Program (PP) instruction allows bytes to be programmed in the memory (changing bits from 1 to 0). Before it can be accepted, a Write Enable (WREN) instruction must previously have been ex-ecuted. After the Write Enable (WREN) instruction has been decoded, the device sets the Write En-able Latch (WEL).The Page Program (PP) instruction is entered by driving Chip Select (S) Low, followed by the in-struction code, three address bytes and at least one data byte on Serial Data Input (D). If the 8 least significant address bits (A7-A0) are not all zero, all transmitted data that goes beyond the end of the current page are programmed from the start address of the same page (from the address whose 8 least significant bits (A7-A0) are all zero). Chip Select (S) must be driven Low for the entire duration of the sequence.The instruction sequence is shown in Figure 15.. If more than 256 bytes are sent to the device, pre-viously latched data are discarded and the last 256 data bytes are guaranteed to be programmed cor-rectly within the same page. If less than 256 Data bytes are sent to device, they are correctly pro-grammed at the requested addresses without hav-ing any effects on the other bytes of the same page.Chip Select (S) must be driven High after the eighth bit of the last data byte has been latched in, otherwise the Page Program (PP) instruction is not executed.As soon as Chip Select (S) is driven High, the self-timed Page Program cycle (whose duration is t PP) is initiated. While the Page Program cycle is in progress, the Status Register may be read to check the value of the Write In Progress (WIP) bit. The Write In Progress (WIP) bit is 1 during the self-timed Page Program cycle, and is 0 when it is completed. At some unspecified time before the cycle is completed, the Write Enable Latch (WEL) bit is reset.A Page Program (PP) instruction applied to a page which is protected by the Block Protect (BP2, BP1, BP0) bits (see Table 3. and Table 2.) is not execut-ed.M25P80。

兴存储的线路图

新闻稿美光科技宣布收购其在IM Flash Technologies 合资公司中的剩余股份的意向此次收购完成后,美光科技将能独立推进其美国犹他州工厂的3D XPoint™ 技术的研发生产和新兴存储的线路图美国爱达荷州博伊西,2018 年10 月18 日——美光科技有限公司(纳斯达克代码:MU)今日宣布,公司计划对英特尔在双方的合资公司 IM Flash Technologies, LLC (简称“IM Flash”) 中的权益行使认购期权。

美光科技总裁兼首席执行官 Sanjay Mehrotra 表示:“美光科技对 IM Flash 的收购表明,我们坚信3D XPoint 技术和其他新兴存储技术将为公司提供独一无二的差异化优势,并为海量数据需求的新型应用提供不可或缺的重要解决方案。

这项投资能让美光科技拥有成熟的研发和制造工厂,拥有在创新和执行方面有着卓越纪录并高技能型人才队伍。

”美光科技可以从2019 年1 月1 日起行使认购期权。

这笔交易将在美光科技执行认购期权后的6 到12 个月之内完成。

IM Flash 合资公司目前已并入美光科技的财务报表中。

美光科技预测,此笔交易不会对其整体财务业绩产生实质性影响,也不会改变其2019 财年和长期的资本支出目标。

该交易完结时,美光科技预计将支付约 15 亿美元现金,解除英特尔在 IM Flash 的非控股权益以及英特尔对该合资企业的债务。

截至 2018 年 8 月 30 日,这笔债务约为 10 亿美元。

2018 年 7 月,美光科技和英特尔同意在完成第二代节点(预计于 2019 财年下半年完成)后结束 3D XPoint 技术的联合开发工作。

两家公司将独立推动自己的未来技术路线图。

美光科技目前正在与其生态系统合作伙伴携手合作,预计将于 2019 年末推出 3D XPoint 产品,并于 2020 年开始实现营收。

交易完成前,两家公司将继续在犹他州李海的 IM Flash 工厂联合生产 3D XPoint 存储产品。

英特尔与美光联合推出34纳米闪存芯片

英特尔与美光联合推出34纳米闪存芯片据《电子产品世界》2009年第9期报道,英特尔和美光科技日前发布了用于闪存卡和优盘的高数据容量闪存技术。

这两家公司称,他们已经开发出了基于34纳米技术的NAND闪存芯片,存储容量为每个储存单元3比特。

这个存储密度高于目前标准的每个存储单元2比特的技术,从而将实现高容量的存储设备。

据悉,美光目前提供这种芯片的样品,大批量生产将在今年第四季度。

江 兴 摘安森美半导体推出带集成ES D保护的共模扼流圈EM I滤波器安森美半导体(ON Se m iconductor)推出新型共模扼流圈及静电放电(ES D)保护集成电路(I C),这种新型的静电放电(ES D)保护集成电路(I C)可应用于高速数据线路。

新的NU C2401M N结合了高带宽差分滤波、固体共模停止带宽衰减及世界级ES D保护功能。

这些综合的特性,使得这一方案远远优于典型的电磁干扰(E M I)滤波器及分立可选方案,同时有助于显著减少元件数量。

这种新器件可以让设计人员实现优异的滤波及保护性能,且节省空间及成本,并提高总体可靠性,非常适用于基于高速差分数据线路的广泛应用,包括U S B2.0、IEEE1394、低压差分信令(LVD S)、移动行业处理器接口(M IP I)及移动显示数字接口(M DD I)。

NU C240I M N在尺寸仅为2.0mm×2.2mm的D FN封装中集成了等同于5个分立元件的电路,结合共模EM I滤波及符合IEC610002422接触放电业界标准的±12千伏(kV)ES D保护。

机器模型(MM)及人体模型(HB M)ES D额定值分别为1.6kV及16kV。

这器件额定遵从1级湿敏等级(M S L1),工作温度范围为-40°C~85°C。

由于NU C2401M N是集成方案,可帮助减少寄生电感,从而提供更出色的共模滤波。

共模噪声消减的截止频率为40M H z、100M H z及500M H z频率时的典型共模阻抗分别为200及5008。

Micron发布Managed NAND闪存,应对多媒体手机等存储需求

司称 ,这种 高度整合的解决 方案简化 擦除操作,实现缺陷管理功能 。

了制造商 产品设计流程 ,同时 使制造

越 多功能集成在一起 , 高密度、 低成本

今年 五月 ,美 光科技联手 Hy i NAND闪存产品是实现高容量消费类 nx

商对于元 器件采购工程 中的物流 管理 S mio d co 、Itl、S n e c n u tr ne o y公 司以 及 电子存储的最佳选择。O F 的 目标是 N I 等更加方便 。美光科技战略营 销和产 P i nEet n s hs l r i 等厂商成立 了开放式 提供一个N N o co c A D产品接 口 ◎ 下转8 3

gs 为 Acu i、E e e 、Iut和 O i cpx yn o c i i r c等 Vea举办的消费类 电子产品展将众人 费者选用视频 眼镜后 ,他们可 以沉浸 s E 创新 2 0 设计与工程奖授 在 电话 内置显示 器无法达到的高分辨 05 公司提供 个人视 频 配镜 的核 心器 件。 觊觎的 C S ci。Iu i r. t tC al. E ee AS ( ytpD D制造商,一 予了Iu i ci op的董事长P u J 率 的视频 中。 y noS E eo V 种 可佩戴 的 DVD播放 器 )的总经理 T aes ,“c i V 2 在小型电子产 r r说 v Iut 9 0 i Ko i pn的董事长和首席执行官 D r

显示器。

通过V 微 显示器提供标 准的3 GA D立体 面 前。某些视频 眼镜 系统还可以插入

视频 。

到 Pn snc 9 0 照相 电话 上 ,该 电 aao iP 0 i V

目前的应用

由于该系统具 有时髦的设计和高 话能进行静、 动态 图像的拍摄 、 存储和

IC品牌大全

IC品牌大全IC(Integrated Circuit,集成电路)是现代电子技术中的重要组成部分,广泛应用于各个领域,包括通信、计算机、消费电子、汽车电子等。

随着科技的不断进步,市场上涌现出了众多的IC品牌,本文将为您介绍一些知名的IC品牌及其特点。

1. 英特尔(Intel)英特尔是全球最大的半导体芯片制造商之一,成立于1968年。

该公司以生产微处理器而闻名,其产品广泛应用于个人电脑、服务器和移动设备等。

英特尔的芯片具有高性能、低功耗和可靠性强的特点,深受消费者和企业的青睐。

2. AMD(Advanced Micro Devices)AMD是一家全球领先的半导体公司,成立于1969年。

该公司专注于设计和制造微处理器、图形处理器和其他半导体产品。

AMD的产品在性能和价格方面具有竞争力,被广泛应用于个人电脑、游戏主机和数据中心等领域。

3. 德州仪器(Texas Instruments)德州仪器成立于1930年,是一家知名的半导体公司。

该公司提供广泛的模拟和数字信号处理解决方案,包括放大器、数据转换器、传感器和微控制器等产品。

德州仪器的产品在工业自动化、汽车电子和医疗设备等领域具有广泛的应用。

4. 高通(Qualcomm)高通是全球领先的无线通信技术公司,成立于1985年。

该公司专注于设计和制造移动通信芯片,包括手机处理器、无线调制解调器和射频前端等。

高通的产品在移动设备和物联网等领域具有广泛的应用,提供高速、稳定的无线连接。

5. 英飞凌(Infineon)英飞凌是一家总部位于德国的半导体公司,成立于1999年。

该公司提供广泛的半导体解决方案,包括功率半导体、传感器和安全芯片等。

英飞凌的产品在汽车电子、工业自动化和智能手机等领域具有重要的应用。

6. 台积电(TSMC)台积电是全球最大的半导体代工厂商之一,成立于1987年。

该公司提供先进的制造工艺和技术,为全球各大IC设计公司生产芯片。

台积电的产品广泛应用于通信、计算机和消费电子等领域,以高质量和可靠性著称。

Marvell推出突破性的HyperDuo SATA控制器88SE9230

Marvell推出突破性的HyperDuo SATA控制器88SE9230全球集成芯片解决方案的领导厂商美满电子科技(Marvell,纳斯达克代码:MRVL)今日宣布,推出Marvell® 88SE9230 6Gb/s SATA控制器,该控制器基于HyperDuo™嵌入式处理器技术。

新的Marvell 88SE9230解决方案与前一代解决方案相比,性能、容量和可扩展性提高了一倍,从而使消费类台式电脑主板和消费类电子产品充分受益于固态硬盘(SSD)的技术优势。

Marvell的HyperDuo技术实现了像SSD一样的性能,同时允许所有数据存储在传统SATA硬盘(HDD)中。

Marvell最新推出的高级SATA控制器为实现新一代高端消费类应用奠定了基础,有4个端口用于SSD或硬盘连接,容量翻了一番,同时该控制器现在还配备了两个PCIe 2.0通道,可提供增大一倍的PCIe总线带宽,以容纳多个SATA SSD。

88SE9230 SATA控制器采用智能算法,以自动从引脚输出多达3个SATA SSD的热门数据文件和目录,同时使所有数据都能安全地存储在容量更大的SATA硬盘中。

88SE9230还可提供无与伦比的安全性,包括128/256位实时AES加密,以确保实现最高的数据安全性。

Marvell产品市场总监Shawn Kung表示:“Marvell致力于通过闻名于世的高性能、低成本和低功耗芯片解决方案,向主流消费类技术市场提供领先的自动化和集成式SSD加速技术,这是Marvell一直以来的使命。

我们在SATA技术产品领域拥有领先地位,今天推出的具有里程碑意义的88SE9230以及我们为重要客户提供的专门支持,再次肯定了这一点。

” Marvell SATA 6Gb/s控制器基于HyperDuo技术,为主流消费类技术市场提供了集成式SSD 加速技术,尤其是高端台式电脑和笔记本电脑、家用NAS和机顶盒以及主机总线适配器市场。

美光发布25nm闪存芯片ClearNAND

芯片设计工程师技术合作伙伴与供应商参与。出席

会议 的还有 中国半导 体行业 协会 执行 副理事 长徐 小

田, 中国半导体行业协会副秘书长 、 中国半导体行业

协 会集 成 电路设计 分会 常 务副理 事长 、国家科 技 重

为华润微电子有限公司旗下负责晶圆代工业务的华

润上华 已经确 立将绿 色 节能领域 、物联 网等相关 产

业 链 中的各 家企业 尤应 注重 合作互 动 ,建立 相互 依 存 的关 系 , 同时 在 3 c融 合及 物联 网时代 , 了注 重 除 数 字 产 品的发 展外 ,更 不能 忽 略模 拟 产 品 的开 发 。

华 润上 华模 拟 产 品 的销 售 比重 达 6 %, 艺最 高可 0 工

设 备 和系统 制造商 用 于手持设 备 、 业级 服务器 、 企 平 板 电脑 、 P M 3播 放器 、 码相 机 、 视 摄像 机 和 其他 数 监 诸 多应 用 。 这款命 名 为 CerA D的芯 片分为 标准 l N N a 型和增 强 型两个 版本 , 准版 的存储 容 量 为 8 B和 标 G 3 G , CerA D增 强 版 的存 储 容 量 为 1G 2B la N N 6 B和

大专项 O 专项总体组组长魏少军 , 1 中国半导体行业

协 会秘 书长 陈贤 ,深圳 市半 导体行业 协 会秘 书长蔡

锦 江

品领域作为未来重要发展方向, 并已经启动资金 、 技

术 、 才等 方 面的准备 , 人 更加 着重 开发针 对 中 国新 兴 应用 市场 的工艺及 设计 服 务平 台。最后 邓茂 松感 谢 华 润上 华 所 有 客 户 以 及 合作 伙 伴 的 长期 支持 与 合 作, 并期 待今 后继续 并肩 协作 , 共商 大业 , 共襄 盛举 ,

MEMORY存储芯片MT29F2G08ABBGAH4-IT-G中文规格书

General DescriptionMicron NAND Flash devices include an asynchronous data interface for high-perform-ance I/O operations. These devices use a highly multiplexed 8-bit bus (I/Ox) to transfercommands, address, and data. There are five control signals used to implement theasynchronous data interface: CE#, CLE, ALE, WE#, and RE#. Additional signals controlhardware write protection and monitor device status (R/B#).This hardware interface creates a low pin-count device with a standard pinout that re-mains the same from one density to another, enabling future upgrades to higher densi-ties with no board redesign.A target is the unit of memory accessed by a chip enable signal. A target contains one ormore NAND Flash die. A NAND Flash die is the minimum unit that can independentlyexecute commands and report status. A NAND Flash die, in the ONFI specification, isreferred to as a logical unit (LUN). There is at least one NAND Flash die per chip enablesignal. For further details, see Device and Array Organization.This device has an internal 4-bit ECC that can be enabled using the GET/SET features.See Internal ECC and Spare Area Mapping for ECC for more information.Signal DescriptionsTable 1: Signal DefinitionsNotes: 1.See Device and Array Organization for detailed signal connections.2.See Asynchronous Interface Bus Operation for detailed asynchronous interface signaldescriptions.Column Address OperationsThe column address operations affect how data is input to and output from the cacheregisters within the selected die (LUNs). These features provide host flexibility for man-aging data, especially when the host internal buffer is smaller than the number of databytes or words in the cache register.When the asynchronous interface is active, column address operations can address anybyte in the selected cache register.RANDOM DATA READ (05h-E0h)The RANDOM DATA READ (05h-E0h) command changes the column address of the se-lected cache register and enables data output from the last selected die (LUN). Thiscommand is accepted by the selected die (LUN) when it is ready (RDY = 1; ARDY = 1). Itis also accepted by the selected die (LUN) during CACHE READ operations(RDY = 1; ARDY = 0).Writing 05h to the command register, followed by two column address cycles containingthe column address, followed by the E0h command, puts the selected die (LUN) intodata output mode. After the E0h command cycle is issued, the host must wait at leastt WHR before requesting data output. The selected die (LUN) stays in data output modeuntil another valid command is issued.In devices with more than one die (LUN) per target, during and following interleaveddie (multi-LUN) operations, the READ STATUS ENHANCED (78h) command must beissued prior to issuing the RANDOM DATA READ (05h-E0h). In this situation, using theRANDOM DATA READ (05h-E0h) command without the READ STATUS ENHANCED(78h) command will result in bus contention because two or more die (LUNs) couldoutput data.Figure 32: RANDOM DATA READ (05h-E0h) Operation Array Cycle typeI/O[7:0]SR[6]ble for additional PROGRAM PAGE CACHE (80h-15h) or PROGRAM PAGE (80h-10h) commands. The PROGRAM PAGE CACHE (80h-15h) command is accepted by the die (LUN) when it is ready (RDY =1, ARDY = 1). It is also accepted by the die (LUN) when busy with a PROGRAM PAGE CACHE (80h-15h) operation (RDY = 1, ARDY = 0).To input a page to the cache register to move it to the NAND array at the block and page address specified, write 80h to the command register. Unless this command has been preceded by a PROGRAM PAGE TWO-PLANE (80h-11h) command, issuing the 80h to the command register clears all of the cache registers' contents on the selected target. Then write n address cycles containing the column address and row address. Data input cycles follow. Serial data is input beginning at the column address specified. At any time during the data input cycle the RANDOM DATA INPUT (85h) and PROGRAM FOR IN-TERNAL DATA INPUT (85h) commands may be issued. When data input is complete, write 15h to the command register. The selected LUN will go busy(RDY = 0, ARDY = 0) for t CBSY to allow the data register to become available from a pre-vious program cache operation, to copy data from the cache register to the data register, and then to begin moving the data register contents to the specified page and block ad-dress.To determine the progress of t CBSY, the host can monitor the target's R/B# signal or, al-ternatively, the status operations (70h, 78h) can be used. When the LUN’s status shows that it is busy with a PROGRAM CACHE operation (RDY = 1, ARDY = 0), the host should check the status of the FAILC bit to see if a previous cache operation was successful.If, after t CBSY, the host wants to wait for the program cache operation to complete, without issuing the PROGRAM PAGE (80h-10h) command, the host should monitor AR-DY until it is 1. The host should then check the status of the FAIL and FAILC bits.In devices with more than one die (LUN) per target, during and following interleaved die (multi-LUN) operations, the READ STATUS ENHANCED (78h) command must be used to select only one die (LUN) for status output. Use of the READ STATUS (70h) com-mand could cause more than one die (LUN) to respond, resulting in bus contention. The PROGRAM PAGE CACHE (80h-15h) command is used as the final command of a two-plane program cache operation. It is preceded by one or more PROGRAM PAGE TWO-PLANE (80h-11h) commands. Data for all of the addressed planes is transferred from the cache registers to the corresponding data registers, then moved to the NAND Flash array. The host should check the status of the operation by using the status opera-tions (70h, 78h).Figure 43: PROGRAM PAGE CACHE (80h–15h) Operation (Start)Cycle type I/O[7:0]RDYFigure 44: PROGRAM PAGE CACHE (80h–15h) Operation (End)As defined forPAGE CACHE PROGRAMPROGRAM PAGE TWO-PLANE (80h-11h)。

DRAM存储器行业分析

DRAM存储器行业分析DRAM(Dynamic Random Access Memory)存储器是计算机内存的一种主要类型,用于暂时存储正在使用的数据和指令。

DRAM存储器行业是信息技术领域中一个重要的产业链条之一,对整个信息技术行业的发展和进步起着至关重要的作用。

本文将从行业概况、市场需求、发展趋势等多个角度对DRAM存储器行业进行分析。

一、行业概况DRAM存储器行业是半导体行业中的一个重要分支,主要产品包括DDRSDRAM、DDR2SDRAM、DDR3SDRAM、DDR4SDRAM等不同类型的DRAM存储器芯片。

DRAM存储器具有高速度、低功耗和大容量等优点,被广泛应用于个人电脑、服务器、手机、平板电脑、汽车电子等各个领域。

根据市场研究公司的数据显示,全球DRAM存储器市场规模在不断扩大,2024年全球DRAM市场规模已达到约100亿美元,预计未来几年还将继续保持增长态势。

目前,全球DRAM市场主要由三大厂商垄断,分别为三星、SK海力士和美光科技,这三家厂商在全球DRAM市场上的份额超过了80%,形成了一定的市场壁垒。

二、市场需求随着信息技术的不断发展和普及,以及5G、人工智能、物联网等新技术的快速崛起,对DRAM存储器的需求量也在不断增加。

智能手机、数据中心、云计算、人工智能等领域对DRAM存储器的需求量巨大,这些领域的快速发展为DRAM存储器行业提供了广阔的市场空间。

此外,随着全球计算机产量的增加,以及电子产品的智能化和功能的提升,对高速度、大容量DRAM存储器的需求也在逐渐增加。

智能手机、平板电脑、笔记本电脑等个人设备对DRAM存储器的需求量较大,同时,车载电子、医疗设备、工业控制等领域也对DRAM存储器有着不小的需求。

三、发展趋势1.技术升级:随着半导体技术的不断进步,DRAM存储器的制造工艺和存储密度也在不断提升。

未来,DRAM存储器行业将继续推动技术革新,提高存储器的性能和稳定性,以满足市场对高速度、低功耗、大容量存储器的需求。

SLC和MLC闪存nand flsah的区别和历史

SLC和MLC闪存nand flsah的区别和历史Flash闪存是非易失性存储器,这是相对于SDRAM等存储器所说的。

即存储器断电后,内部的数据仍然可以保存。

Flash根据技术方式分为Nand 、Nor Flash和AG-AND Flash,而U 盘和MP3中最常用的内存就是Nand Flash。

Nand Flash也有几种,根据技术方式,分为SLC、MCL、MirrorBit等三种。

SLC是Single level cell的缩写,意为每个存储单元中只有1bit数据。

而MLC就是Multi-Level-Cell,意为该技术允许2 bit的数据存储在一个存储单元当中。

而MirrorBit则是每个存储单元中只有4bit数据。

SLC的技术存储比较稳定,SLC的技术也最为成熟。

然而MLC可以在一个单元中有2bit 数据,这样同样大小的晶圆就可以存放更多的数据,也就是成本相同的情况下,容量可以做的更大,这也是同样容量,MLC价格比SLC低很多的原因。

通常情况下相同容量的MLC 和SLC,MLC的价格比SLC低30%~40%,有些甚至更低。

区分SLC(停产)和MLC(现在主流,分新老制程,60NM 和56/50NM )1、看Flash的型号:根据Flash的命名规则,进行区分。

2、测试读写速度:SLC的非常快,MLC的很慢。

SLC闪存:即单层式储存(Single Level Cell;SLC),包括三星电子、Hynix、美光(Micron)以及东芝都是此技术使用者MLC闪存:多层式储存(Multi Level Cell;MLC),目前有东芝、Renesas、三星使用,英飞凌(Infineon)与Saifun Semiconductors合资利用NROM技术所共同开发的多位储存(Multi Bit Cell;MBC)。

MLC是英特尔(Intel)在1997年9月最先开发成功的,其作用是将两个单位的信息存入一个Floating Gate,闪存存储单元中存放电荷的部分),然后利用不同电位(Level)的电荷,透过内存储存的电压控制精准读写,假设以4种电压控制、1个晶体管可存取2bits的数据,若是控制8种电压就可以存取3 bits的数据,使Flash 的容量大幅提升,类似Rambus的QRSL技术,通过精确控制Floating Gat上的电荷数量,使其呈现出4种不同的存储状态,每种状态代表两个二进制数值(从00到11)。

国内外IC品牌大全

国内外IC品牌大全一、国内IC品牌大全1. 中国电子集团有限公司(CEC)中国电子集团有限公司(CEC)是中国最大的集成电路设计和制造企业之一,拥有多家子公司和研发中心。

该公司在各个领域都有广泛的产品线,包括模拟集成电路、数字集成电路、存储器、传感器等。

其产品广泛应用于通信、电子消费品、汽车电子、工业控制等领域。

2. 中芯国际集成电路制造有限公司(SMIC)中芯国际集成电路制造有限公司(SMIC)是中国领先的集成电路制造企业之一。

该公司提供从0.35微米到14纳米的先进制程,并提供多种工艺选项,满足不同应用的需求。

SMIC的产品广泛应用于通信、消费电子、汽车电子等领域。

3. 神州高铁电子股份有限公司(CSR)神州高铁电子股份有限公司(CSR)是中国领先的铁路电子设备供应商之一。

该公司专注于开发和制造铁路信号设备、列车控制系统、车辆电气设备等。

CSR 的产品在中国国内铁路系统中得到广泛应用。

4. 紫光国芯集成电路设计有限公司(ZTE Microelectronics)紫光国芯集成电路设计有限公司(ZTE Microelectronics)是中国知名的集成电路设计公司之一。

该公司专注于高性能通信芯片的设计和制造,产品包括基带处理器、射频芯片、光通信芯片等。

其产品在通信领域具有广泛的应用。

5. 立锜微电子股份有限公司(Richtek)立锜微电子股份有限公司(Richtek)是一家专注于模拟和混合信号电源管理解决方案的领先供应商。

该公司的产品涵盖了电源管理IC、DC-DC转换器、LDO稳压器等。

Richtek的产品广泛应用于消费电子、通信、工业控制等领域。

二、国外IC品牌大全1. 英特尔公司(Intel)英特尔公司(Intel)是全球最大的半导体芯片制造商之一。

该公司的产品包括微处理器、芯片组、闪存存储器等。

英特尔的产品广泛应用于个人电脑、服务器、网络设备等领域。

2. 三星电子(Samsung Electronics)三星电子(Samsung Electronics)是韩国知名的电子产品制造商之一。

Chips

美光 科 技 采 用 的 1 6 n m工艺被 T e c h l n s i g h t s 评

为“ 最具创新性的存储设备 ” 和“ 2 0 1 4年度半导体

技 术 ”。 作 为一项 成 熟且 经过 实 战检验 的存储 技 术 , 1 6 n m 工艺 为打 造 可靠 的 T L C设 计 奠定 了坚实 的基

业 界 要 闻

如运动 、 健 身 和保健 用 的可穿 戴传 感 恩智浦射频功率事业部是高性能射频功率放大 用 于很 多 应用 , 器、 行 人导 航 、 自主机 器 人 , 以 及 虚拟 和增 强 实 境 。

点火系统领域的应用 中也很有发展潜力。

根据协议 ,原恩智浦射频功率事业部的全部业 务 、以及包括管理 团队在 内的全球约 2 0 0 0 名员工 ,

础 。T L C又被称作 “ 三级单元”( t r i p l e — l e v e l c e l 1 ) ,

是一种在每个闪存数据单元 中存储 三位数据的技

术, 能有效 降低成本并缩小芯片尺寸。 采用这项技术后 ,客户能从美光科技全面的设

F a i r c h i I d推 出 M E M S 产 品 系列

率 事业 部 的所 有相 关 专 利和 知识 产权 ,以及 恩智 浦

设在菲律宾 的一家专注于射频功率产品高级包装 、 测试和组装的后端制造企业 , 都将在交易后转到建 广资产名下 。

本 次 交 易 ,包 括 进 入最 终 协议 和协议 条 款 的达

决方案。新型 T L C N A N D是基于 1 6 n m工艺制造而

他审核恩智浦公 司收购飞思卡尔半导体提议的相关

机构的许可 。 恩智浦和建广 资产 预计本次交易将 于 2 0 1 5 年 下半年完成 ,期间将寻求监管机构审核并和员工代 表进行沟通 。恩智浦预计本次 出售其射频功率事业 部将会稀 释其 2 0 1 5 年第 四季度及 2 0 1 6 年的每股收 益。该交 易的获利将用于资助之前宣布的对飞思卡 尔半导体的收购。 ( 来 自恩智浦半导体 )

闪存颗粒基础知识单选题100道及答案解析

闪存颗粒基础知识单选题100道及答案解析1. 闪存颗粒的主要存储介质是()A. 磁性材料B. 半导体材料C. 光学材料D. 超导材料答案:B解析:闪存颗粒主要基于半导体材料来实现数据存储。

2. 以下哪种闪存颗粒类型的擦写寿命通常较长?()A. SLCB. MLCC. TLCD. QLC答案:A解析:SLC(Single-Level Cell)每个存储单元只存储1 位数据,擦写寿命最长。

3. 闪存颗粒的读取速度一般取决于()A. 存储密度B. 制程工艺C. 接口类型D. 控制芯片答案:B解析:制程工艺越先进,闪存颗粒的读取速度通常越快。

4. 闪存颗粒的存储容量主要由()决定。

A. 单元尺寸B. 存储单元数量C. 封装技术D. 颗粒层数答案:B解析:存储单元数量越多,闪存颗粒的存储容量越大。

5. 以下哪种闪存颗粒的成本相对较低?()A. SLCB. MLCC. TLCD. QLC答案:D解析:QLC(Quad-Level Cell)每个存储单元存储 4 位数据,成本相对较低。

6. 闪存颗粒在工作时会产生一定的热量,主要原因是()A. 电流通过B. 数据读写C. 电容充放电D. 晶体管开关答案:D解析:晶体管开关动作时会有能量损耗,产生热量。

7. 衡量闪存颗粒性能的重要指标不包括()A. 写入速度B. 顺序读写速度C. 随机读写速度D. 颜色答案:D解析:颜色与闪存颗粒的性能无关。

8. 闪存颗粒的制程越小,意味着()A. 性能越好B. 成本越低C. 能耗越高D. 可靠性越高答案:A解析:制程越小,能在同样面积上集成更多晶体管,从而提升性能。

9. 以下关于闪存颗粒的说法,错误的是()A. 具有非易失性B. 可以快速随机读写C. 数据保存不需要电源D. 读写次数无限答案:D解析:闪存颗粒的读写次数是有限的。

10. 闪存颗粒通常用于()A. 内存B. 硬盘C. CPUD. 显卡答案:B解析:闪存颗粒常用于固态硬盘等存储设备。

美光3D NAND技术逐渐成熟,积极推动工业领域应用

美光3D NAND技术逐渐成熟,积极推动工业领域应

用

美系存储器大厂美光(Micron)3D NAND技术逐渐成熟后,开始拓展旗下产品线广度,日前耕耘工业领域有成,将推出影像监控边缘储存解决方案,32GB和64GB版microSD卡抢先问世,预计2018年第1季128GB和256GB版会开始送样,同年第2季量产。

下面就随小编一起来了解一下相关内容吧。

美光的64层3D NAND技术今年成熟且开始量产,除了主攻服务器∕企业端、消费性固态硬盘(SSD)领域,也积极推动工业领域应用,日前推出全系列的影像监控边缘装置储存解决方案产品组合,以32GB和64GB版microSD卡抢先试水温。

近期边缘运算(Edge Computing)成为热门的名词,过去在各种终端产品上搜集到的大量数据,需要上传到云端进行分析,然随着回应时间越缩越短,市场在云与端之间出现了这样一个新的名词,也就是直接在终端装置上,进行数据辨识与分析的概念。

这类的边缘影像需要独特的储存方式,美光就是锁定这块市场,推出microSD卡,来满足系统整合商因应IP网路负载量和可用容量、录制冗余影。

含美光芯片产品清单

含美光芯片产品清单美光是全球领先的半导体存储解决方案供应商,其产品广泛应用于计算机、移动设备和数据中心等领域。

以下是美光芯片产品的清单,包括存储器、固态硬盘和内存模块等。

一、存储器产品1. 闪存存储器:美光生产的闪存存储器具有高速读写、可靠性强的特点,广泛应用于移动设备、相机和汽车电子等领域。

其中包括eMMC、UFS和SSD等产品系列。

2. DRAM存储器:美光的DRAM存储器具有高密度、高速度和低功耗的特点,被广泛应用于计算机和数据中心等领域。

其中包括DDR4、DDR5和LPDDR4等产品系列。

二、固态硬盘产品1. SATA固态硬盘:美光的SATA固态硬盘具有高速读写、可靠性强的特点,适用于个人电脑和商业领域。

其中包括MX500和BX500等产品系列。

2. NVMe固态硬盘:美光的NVMe固态硬盘具有超高速的数据传输速度和低延迟,适用于高性能计算和数据中心等领域。

其中包括P1和600p等产品系列。

三、内存模块产品1. 服务器内存模块:美光的服务器内存模块具有高容量、高速度和可靠性强的特点,适用于大型数据中心和企业服务器等领域。

其中包括RDIMM、LRDIMM和NVDIMM等产品系列。

2. 笔记本电脑内存模块:美光的笔记本内存模块采用低电压设计,具有高速度和低功耗的特点,适用于轻薄笔记本和游戏本等领域。

其中包括SODIMM和宽温内存等产品系列。

四、其他产品除了上述产品,美光还提供一系列与芯片相关的解决方案,如内存卡、存储卡和USB闪存驱动器等。

这些产品广泛应用于消费电子、工业控制和物联网等领域,满足不同用户的存储需求。

总结:美光芯片产品清单包括存储器、固态硬盘和内存模块等产品系列。

这些产品具有高速度、可靠性强的特点,并广泛应用于计算机、移动设备和数据中心等领域。

无论是个人用户还是企业用户,都能找到适合自己需求的美光芯片产品。

美光将继续致力于半导体存储技术的创新,为用户提供更先进、更可靠的产品和解决方案。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ቤተ መጻሕፍቲ ባይዱ

美光科技有限公司(纳斯达克代码:MU)今天宣布,其丰富的闪存产品系列又添新成员——为寻求高性能和高可靠性,且极其注重成本的消费类应用提供了量身定制的解决方案。新型TLC NAND是基于16纳米(nm)工艺制造而成,能让U盘和消费类固态硬盘等应用的各方面功能取得理想平衡。预计市场在整个2015年都将对TLC有强劲需求,占到NAND存储总量的几乎一半。 美光科技采用的16 纳米工艺被TechInsights评为“最具创新性的存储设备”和“2014年度半导体技术”。作为一项成熟且经过实战检验的存储技术,16纳米工艺为打造可靠的TLC设计奠定了坚实的基础。TLC又被称作“三级单元”(triple-level cell),是一种在每个闪存数据单元中存储三位数据的技术,能有效降低成本并缩小芯片尺寸。 采用这项技术后,客户能从美光科技全面的设计支持团队获得诸多益处。他们将担当客户信赖的顾问,帮助客户顺利通过鉴定测试和确保最终解决方案的最佳实施效果。全球范围内主要的闪存客户和生态系统合作伙伴已经开始集成这种新型NAND到其最新设计中,确保这项技术能快速被终端应用采用。 “我们新推出的TLCNAND技术满足了客户对可靠、高容量存储的日益增长的需求。”美光科技 NAND规划总监Kevin Kilbuck说道,“16nm TLC被我们视为2015年消费类应用的绝佳解决方案,我们也持续向在 2016 年产出3D NAND TLC迈进。” 新型TLC产品进一步完善和扩大了美光广泛的闪存产品组合。这一产品组合已跨越四代工艺和多项技术,能够为已知的几乎所有应用提供集中解决方案——从消费电子、移动产品到企业级存储、嵌入式和汽车市场,可以说是无所不包。新型16GB TLC NAND现已量产并开始供货。美光也已开始为多个合作伙伴提供样品,这将推动基于此技术的消费类SSD解决方案于今年秋季的上市。美光科技也预计在同期发布自主生产的基于TLC技术的客户端SSD。 客户评价 ADATA 副总裁 Kevin Chen “我们很高兴推出了采用美光科技TLC的新消费类SSD产品系列。美光科技带来的性价比、技术支持和可靠性保证了客户能从他们的存储中获得最大价值。” 金泰克总裁 James Lee “可靠的TLC闪存对于打造服务于发展中市场的存储产品至关重要。美光科技的16纳米TLC能让客户获得的各方面功能取得理想平衡。” Transcend Information 产品管理总监 Chris Chen “消费者对产品的青睐源于高密度存储和实惠的价格。美光科技16纳米TLC将成为消费类介质卡和存储的绝佳选择。” Seagate SSD产品副总裁 Brett Pemble “我们与美光科技一直保持紧密的合作关系,并期待继续发运集成双方最新技术的解决方案。我们的SF3500控制器将在OEM制造商和我们自有的PCIe和SATA SSD中使用美光科技16纳米TLC打造一个极具吸引力的平台——实现各方共赢。” Silicon Motion Inc. 产品营销副总裁 Nelson Duann “我们与美光科技深入合作已久,共同确保在我们先进的控制器技术中无缝集成由美光科技提供的闪存。我们很高兴成为首家提供支持美光科技16纳米TLC NAND技术的高性能、高成本效益 USB和SSD控制器的公司。”