BD708中文资料

H708-H708B规格书V1.2(固定600mA充电电流带反接保护充电管理芯片)

SXH708SXH708SXH708SXH708高端单节锂电池充电管理芯片600mA 带锂电池反接保护充电芯片描述是一款完整的单节锂离子电池采用恒定电流/恒定电压线性充电器。

采用SOT-23-6封装与较少的外部元件数目使得 成为便携式应用的理想选择。

可以适合 U SB 电源和适配器电源工作。

由于采用了内部 PMOSFET 架构,加上防倒充电路,所以不需要外部隔离二极管。

热反馈可对充电电流进行自动调节,以便在大功率操作或高温条件下对芯片温度加以限制。

充电电压固定于 4.25V 。

当充电电流在达到最终浮充电压之后降至100mA 时,将自动终止充电循环。

当输入电压(交流适配器或 USB 电源)被拿掉时,自动进入一个低电流状态,将电池漏电流降至 2uA 以下。

在有电源时也可置于停机模式,以将供电电流降至 55uA 。

的其他特点包括欠压闭锁、自动再充电和两个用于指示充电、结束的 L ED 状态引脚。

特点·具有电池反接保护功能 ·600mA 的充电电流·无需 M OSFET 、检测电阻器或隔离二极管 ·用于单节锂离子电池线性充电器·恒定电流/恒定电压操作,并具有可在无过热 危险的情况下实现充电速率最大化的热调节 功能·精度达到±1%的 4.25V 预设充电电压 ·用于电池电量检测的充电电流监控器输出 ·自动再充电·充电状态双输出和故障状态显示 ·100mA 充电终止·待机模式下的供电电流为 55uA ·2.9V 涓流充电·软启动限制了浪涌电流 ·电池温度监测功能 ·采用 S OT23-6 封装绝对最大额定值·输入电源电压(V CC ):-0.3V ~5.5V · BAT :-0.3V ~5.5V ·LEDR :-0.3V ~5.5V ·LEDG :-0.3V ~5.5V·BAT 短路持续时间:连续 ·BAT 引脚电流:600mA ·最大结温:145℃·工作环境温度范围:-40℃~85℃ ·贮存温度范围:-65℃~125℃·引脚温度(焊接时间 10秒):260℃SXH708SXH708SXH708SXH708高端单节锂电池充电管理芯片典型应用原理图2SXH708 SXH708电特性引脚功能内部框图工作原理SXH708高端单节锂电池充电管理芯片SOT23-6封装尺寸说明SXH708。

BD682中文资料

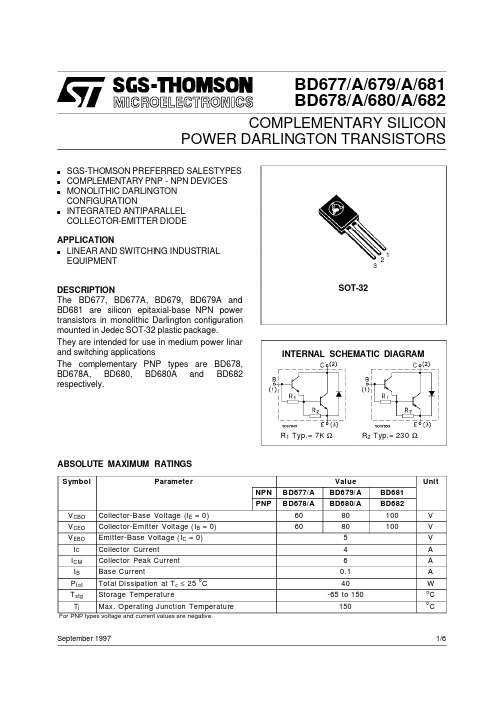

BD677/A/679/A/681BD678/A/680/A/682COMPLEMENTARY SILICONPOWER DARLINGTON TRANSISTORSs SGS-THOMSON PREFERRED SALESTYPES s COMPLEMENTARY PNP -NPN DEVICES sMONOLITHIC DARLINGTON CONFIGURATIONsINTEGRATED ANTIPARALLEL COLLECTOR-EMITTER DIODEAPPLICATION s LINEAR AND SWITCHING INDUSTRIAL EQUIPMENT DESCRIPTIONThe BD677,BD677A,BD679,BD679A and BD681are silicon epitaxial-base NPN power transistors in monolithic Darlington configuration mounted in Jedec SOT-32plastic package.They are intended for use in medium power linar and switching applicationsThe complementary PNP types are BD678,BD678A,BD680,BD680A and BD682respectively.INTERNAL SCHEMATIC DIAGRAMR 1Typ.=7K ΩR 2Typ.=230ΩSeptember 1997ABSOLUTE MAXIMUM RATINGSSymbolParameterValueUnitNPN BD677/A BD679/A BD681PNPBD678/ABD680/ABD682V CBO Collector-Base Voltage (I E =0)6080100V V CEO Collector-Emitter Voltage (I B =0)6080100V V EBO Emitter-Base Voltage (I C =0)5V I C Collector Current 4A I CM Collector Peak Current 6A I B Base Current0.1A P t ot Total Dissipation at T c ≤25oC 40WT stg Storage Temperature-65to 150o C T jMax.Operating Junction Temperature150oCFor PNP types voltage and current values are negative.321SOT-321/6THERMAL DATAR t hj-ca se R t hj-amb Thermal Resistance Junction-case MaxThermal Resistance Junction-ambient Max3.12100o C/Wo C/WELECTRICAL CHARACTERISTICS(T case=25o C unless otherwise specified)Symbol Parameter Test Conditions Min.Typ.Max.UnitI CBO Collector Cut-offCurrent(I E=0)V CE=rated V CBOV CE=rated V CBO T C=100o C0.22mAmAI CEO Collector Cut-offCurrent(I B=0)V CE=half rated V CEO0.5mAI EBO Emitter Cut-off Current(I C=0)V EB=5V2mAV CEO(sus)∗Collector-EmitterSustaining VoltageI C=50mAfor BD677/677A/678/678Afor BD679/679A/680/680Afor BD681/6826080100VVVV CE(sat)∗Collector-EmitterSaturation Voltagefor BD677/678/679/680/681/682I C=1.5A I B=30mAfor BD677A/678A/679A/680AI C=2A I B=40mA2.52.8VVV BE∗Base-Emitter Voltage for BD677/678/679/680/681/682I C=1.5A V CE=3Vfor BD677A/678A/679A/680AI C=2A V CE=3V2.52.5VVh FE∗DC Current Gain for BD677/678/679/680/681/682I C=1.5A V CE=3Vfor BD677A/678A/679A/680AI C=2A V CE=3V750750h f e Small Signal CurrentGainI C=1.5A V CE=3V f=1MHz1∗ Pulsed:Pulse duration=300µs,duty cycle1.5%Safe Operating Areas Derating Curve BD677/677A/678/678A/679/679A/680/680A/681/6822/6DC Current Gain(NPN type)Collector-Emitter Saturation Voltage(NPN type) Base-Emitter Saturation Voltage(NPN type)DC Current Gain(PNP type)Collector-Emitter Saturation Voltage(PNP type) Base-Emitter Saturation Voltage(PNP type)BD677/677A/678/678A/679/679A/680/680A/681/6823/6BD677/677A/678/678A/679/679A/680/680A/681/682Base-Emitter On Voltage(NPN type)Base-Emitter On Voltage(PNP type) Freewheel Diode Forward Voltage(NPN types)Freewheel Diode Forward Voltage(PNP types)4/6DIM.mm inch MIN.TYP.MAX.MIN.TYP.MAX.A 7.47.80.2910.307B 10.510.80.4130.445b 0.70.90.0280.035b10.490.750.0190.030C 2.4 2.70.0400.106c1 1.0 1.30.0390.050D 15.416.00.6060.629e 2.20.087e3 4.154.650.1630.183F 3.80.150G 3 3.20.1180.126H 2.540.100H22.150.084H20016114SOT-32(TO-126)MECHANICAL DATABD677/677A/678/678A/679/679A/680/680A/681/6825/6BD677/677A/678/678A/679/679A/680/680A/681/682Information furnished is believed to be accurate and reliable.However,SGS-THOMSON Microelectronics assumes no responsability for the consequences of use of such information nor for any infringementof patents or other rights of third parties which may results from its use.No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics.Specifications mentioned in this publication are subject to change without notice.This publicationsupersedes and replaces all information previously supplied.SGS-THOMSON Microelectronics products are notauthorized for use as critical components in life support devices or systems without express written approval of SGS-THOMSON Microelectonics.©1997SGS-THOMSON Microelectronics-Printed in Italy-All Rights ReservedSGS-THOMSON Microelectronics GROUP OF COMPANIESAustralia-Brazil-Canada-China-France-Germany-Hong Kong-Italy-Japan-Korea-Malaysia-Malta-Morocco-The Netherlands-Singapore-Spain-Sweden-Switzerland-Taiwan-Thailand-United Kingdom-U.S.A...6/6。

MEMORY存储芯片ADM708ARZ-REEL中文规格书

Data SheetADuM1410/ADuM1411/ADuM1412FEATURESLow power operation 5 V operation1.3 mA per channel maximum at 0 Mbps to 2 Mbps 4.0 mA per channel maximum at 10 Mbps 3 V operation0.8 mA per channel maximum at 0 Mbps to 2 Mbps 1.8 mA per channel maximum at 10 Mbps Bidirectional communication 3 V/5 V level translationHigh temperature operation: 105°C Up to 10 Mbps data rate (NRZ)Programmable default output stateHigh common-mode transient immunity: >25 kV/µs 16-lead, RoHS compliant, SOIC wide body package Safety and regulatory approvalsUL recognition: 3750 V rms for 1 minute per UL 1577 CSA Component Acceptance Notice 5A VDE certificate of conformityDIN V VDE V 0884-10 (VDE V 0884-10): 2006-12 V IORM = 560 V peakTÜV approval: IEC/EN 60950-1V GND V V V V GND DD22OA OB OC OD2206580-001Figure 1. ADuM1410V GND V V V V CTRL GND DD22OA OB OC ID2206580-002Figure 2. ADuM1411V GND V V V V CTRL GNDDD22OA OB IC ID 2206580-003APPLICATIONSGeneral-purpose multichannel isolation SPI interface/data converter isolation RS-232/RS-422/RS-485 transceivers Industrial field bus isolationGENERAL DESCRIPTIONThe ADuM1410/ADuM1411/ADuM14121 are four-channel digital isolators based on Analog Devices, Inc., i Coupler® technology. Combining high speed CMOS and monolithic air core transformer technologies, these isolation components provide outstanding performance characteristics superior to alternatives such as optocoupler devices.By avoiding the use of LEDs and photodiodes, i Coupler devices remove the design difficulties commonly associated with opto-couplers. The usual concerns that arise with optocouplers, such as uncertain current transfer ratios, nonlinear transfer functions, and temperature and lifetime effects, are eliminated with the simple i Coupler digital interfaces and stable performance characteristics. The need for external drivers and other discrete components is eliminated with these i Coupler products. Furthermore, i Coupler1Protected by U.S. Patents 5,952,849; 6,873,065; 6,903,578; and 7,075,329.Figure 3. ADuM1412devices consume one-tenth to one-sixth the power of optocou-plers at comparable signal data rates.The ADuM1410/ADuM1411/ADuM1412 isolators provide four independent isolation channels in a variety of channel configu-rations and data rates (see the Ordering Guide) up to 10 Mbps. All models operate with the supply voltage on either side ranging from 2.7 V to 5.5 V , providing compatibility with lower voltage systems as well as enabling voltage translation functionality across the isolation barrier. All products also have a default output control pin. This allows the user to define the logic state the outputs are to adopt in the absence of the input power. Unlike other optocoupler alternatives, the ADuM1410/ADuM1411/ ADuM1412 isolators have a patented refresh feature that ensures dc correctness in the absence of input logic transitions and during power-up/power-down conditions.Data Sheet ADuM1410/ADuM1411/ADuM1412 SPECIFICATIONSELECTRICAL CHARACTERISTICS—5 V OPERATION4.5 V ≤ V DD1 ≤5.5 V, 4.5 V ≤ V DD2 ≤ 5.5 V; all minimum/maximum specifications apply over the entire recommended operation range, unless otherwise noted; all typical specifications are at T A = 25°C, V DD1 = V DD2 = 5 V. All voltages are relative to their respective ground. Table 1.Parameter Symbol Min Typ Max Unit Test Conditions/CommentsDC SPECIFICATIONSInput Supply Current per Channel,QuiescentI DDI (Q)0.50 0.73 mAOutput Supply Current per Channel,QuiescentI DDO (Q)0.38 0.53 mAADuM1410, Total Supply Current,Four Channels1DC to 2 MbpsV DD1 Supply Current I DD1 (Q) 2.4 3.2 mA DC to 1 MHz logic signal frequency V DD2 Supply Current I DD2 (Q) 1.2 1.6 mA DC to 1 MHz logic signal frequency10 Mbps (BRWZ Version Only)V DD1 Supply Current I DD1 (10)8.8 12 mA 5 MHz logic signal frequency V DD2 Supply Current I DD2 (10) 2.8 4.0 mA 5 MHz logic signal frequency ADuM1411, Total Supply Current,Four Channels1DC to 2 MbpsV DD1 Supply Current I DD1 (Q) 2.2 2.8 mA DC to 1 MHz logic signal frequency V DD2 Supply Current I DD2 (Q) 1.8 2.4 mA DC to 1 MHz logic signal frequency10 Mbps (BRWZ Version Only)V DD1 Supply Current I DD1 (10) 5.4 7.6 mA 5 MHz logic signal frequency V DD2 Supply Current I DD2 (10) 3.8 5.3 mA 5 MHz logic signal frequency ADuM1412, Total Supply Current,Four Channels1DC to 2 MbpsV DD1 or V DD2 Supply Current I DD1 (Q), I DD2(Q)2.0 2.6 mA DC to 1 MHz logic signal frequency10 Mbps (BRWZ Version Only)V DD1 or V DD2 Supply Current I DD1 (10), I DD2 (10) 4.6 6.5 mA 5 MHz logic signal frequencyAll ModelsInput Currents I IA, I IB, I IC,I ID, I CTRL1,I CTRL2, I DISABLE −10 +0.01 +10µA 0 V ≤ V IA, V IB, V IC, V ID ≤ V DD1 or V DD2,0 V ≤ V CTRL1, V CTRL2 ≤ V DD1 or V DD2,0 V ≤ V DISABLE ≤ V DD1Logic High Input Threshold V IH 2.0 V Logic Low Input Threshold V IL 0.8 VLogic High Output Voltages V OAH, V OBH,V OCH, V ODH (V DD1 or V DD2) − 0.1 5.0 V I Ox = −20 µA, V Ix = V IxH (V DD1 or V DD2) − 0.4 4.8 V I Ox = −4 mA, V Ix = V IxHLogic Low Output Voltages V OAL, V OBL,V OCL, V ODL0.0 0.1 V I Ox = 20 µA, V Ix = V IxL0.04 0.1 V I Ox = 400 µA, V Ix = V IxL0.2 0.4 V I Ox = 4 mA, V Ix = V IxL Rev. M | Page of 22ADuM1410/ADuM1411/ADuM1412 Data Sheet Parameter Symbol Min Typ Max Unit Test Conditions/Comments SWITCHING SPECIFICATIONSADuM1410ARWZ/ADuM1411ARWZ/ADuM1412ARWZMinimum Pulse Width2PW 1000 ns C L = 15 pF, CMOS signal levels Maximum Data Rate3 1 Mbps C L = 15 pF, CMOS signal levels Propagation Delay4t PHL, t PLH20 65 100 ns C L = 15 pF, CMOS signal levels Pulse Width Distortion, |t PLH − t PHL|4 PWD 40 ns C L = 15 pF, CMOS signal levels Propagation Delay Skew5t PSK50 ns C L = 15 pF, CMOS signal levels Channel-to-Channel Matching6t PSKCD/OD50 ns C L = 15 pF, CMOS signal levels ADuM1410BRWZ/ADuM1411BRWZ/ADuM1412BRWZMinimum Pulse Width2PW 100 ns C L = 15 pF, CMOS signal levels Maximum Data Rate310 Mbps C L = 15 pF, CMOS signal levels Propagation Delay4t PHL, t PLH20 30 50 ns C L = 15 pF, CMOS signal levels Pulse Width Distortion, |t PLH − t PHL|4 PWD 5 ns C L = 15 pF, CMOS signal levels Change vs. Temperature 5 ps/°C C L = 15 pF, CMOS signal levels Propagation Delay Skew5t PSK30 ns C L = 15 pF, CMOS signal levels Channel-to-Channel Matching,Codirectional Channels6t PSKCD 5 ns C L = 15 pF, CMOS signal levelsChannel-to-Channel Matching,Opposing-Directional Channels6t PSKOD 6 ns C L = 15 pF, CMOS signal levelsAll ModelsOutput Rise/Fall Time (10% to 90%) t R/t F 2.5 ns C L = 15 pF, CMOS signal levelsCommon-Mode Transient Immunity at Logic High Output7|CM H| 25 35 kV/µs V Ix = V DD1 or V DD2, V CM = 1000 V,transient magnitude = 800 VCommon-Mode Transient Immunity at Logic Low Output7 |CM L| 25 35 kV/µs V Ix = 0 V, V CM = 1000 V,transient magnitude = 800 VRefresh Rate f r 1.2 MbpsInput Enable Time8t ENABLE 2.0 µs V IA, V IB, V IC, V ID = 0 V or V DD1 Input Disable Time8t DISABLE 5.0 µs V IA, V IB, V IC, V ID = 0 V or V DD1Input Dynamic Supply Current per Channel9I DDI (D)0.12 mA/MbpsOutput Dynamic Supply Current per Channel9I DDO (D)0.04 mA/Mbps1 The supply current values for all four channels are combined when running at identical data rates. Output supply current values are specified with no output load present. The supply current associated with an individual channel operating at a given data rate can be calculated as described in the Power Consumption section. See Figure 8 through Figure 10 for information on per-channel supply current as a function of data rate for unloaded and loaded conditions. See Figure 11 through Figure 15 for total V DD1 and V DD2 supply currents as a function of data rate for ADuM1410/ADuM1411/ADuM1412 channel configurations.2 The minimum pulse width is the shortest pulse width at which the specified pulse width distortion is guaranteed.3 The maximum data rate is the fastest data rate at which the specified pulse width distortion is guaranteed.4 t PHL propagation delay is measured from the 50% level of the falling edge of the V Ix signal to the 50% level of the falling edge of the V Ox signal. t PLH propagation delay is measured from the 50% level of the rising edge of the V Ix signal to the 50% level of the rising edge of the V Ox signal.5 t PSK is the magnitude of the worst-case difference in t PHL or t PLH that is measured between units at the same operating temperature, supply voltages, and output load within the recommended operating conditions.6 Codirectional channel-to-channel matching is the absolute value of the difference in propagation delays between any two channels with inputs on the same side of the isolation barrier. Opposing-directional channel-to-channel matching is the absolute value of the difference in propagation delays between any two channels with inputs on opposing sides of the isolation barrier.7 |CM H| is the maximum common-mode voltage slew rate that can be sustained while maintaining V O > 0.8 V DD2. |CM L| is the maximum common-mode voltage slew rate that can be sustained while maintaining V O < 0.8 V. The common-mode voltage slew rates apply to both rising and falling common-mode voltage edges. The transient magnitude is the range over which the common mode is slewed.8 Input enable time is the duration from when V DISABLE is set low until the output states are guaranteed to match the input states in the absence of any input data logic transitions. If an input data logic transition within a given channel does occur within this time interval, the output of that channel reaches the correct state within the much shorter duration as determined by the propagation delay specifications within this data sheet. Input disable time is the duration from when V DISABLE is set high until the output states are guaranteed to reach their programmed output levels, as determined by the CTRL2 logic state (see Table 14).9 Dynamic supply current is the incremental amount of supply current required for a 1 Mbps increase in signal data rate. See Figure 8 through Figure 10 for information on per-channel supply current for unloaded and loaded conditions. See the Power Consumption section for guidance on calculating the per-channel supply current for a given data rate.Rev. M | Page of 22Data Sheet ADuM1410/ADuM1411/ADuM1412ELECTRICAL CHARACTERISTICS—3 V OPERATION2.7 V ≤ V DD1 ≤3.6 V, 2.7 V ≤ V DD2 ≤ 3.6 V; all minimum/maximum specifications apply over the entire recommended operation range, unless otherwise noted; all typical specifications are at T A = 25°C, V DD1 = V DD2 = 3.0 V. All voltages are relative to their respective ground. Table 2.Parameter Symbol Min Typ Max Unit Test Conditions/CommentsDC SPECIFICATIONSInput Supply Current per Channel,QuiescentI DDI (Q)0.25 0.38 mAOutput Supply Current per Channel,QuiescentI DDO (Q)0.19 0.33 mAADuM1410, Total Supply Current,Four Channels1DC to 2 MbpsV DD1 Supply Current I DD1 (Q) 1.2 1.6 mA DC to 1 MHz logic signalfrequency V DD2 Supply Current I DD2 (Q)0.8 1.0 mA DC to 1 MHz logic signalfrequency10 Mbps (BRWZ Version Only)V DD1 Supply Current I DD1 (10) 4.5 6.5 mA 5 MHz logic signal frequency V DD2 Supply Current I DD2 (10) 1.4 1.8 mA 5 MHz logic signal frequency ADuM1411, Total Supply Current,Four Channels1DC to 2 MbpsV DD1 Supply Current I DD1 (Q) 1.0 1.9 mA DC to 1 MHz logic signal frequency V DD2 Supply Current I DD2 (Q)0.9 1.7 mA DC to 1 MHz logic signal frequency10 Mbps (BRWZ Version Only)V DD1 Supply Current I DD1 (10) 3.1 4.5 mA 5 MHz logic signal frequency V DD2 Supply Current I DD2 (10) 2.1 3.0 mA 5 MHz logic signal frequency ADuM1412, Total Supply Current,Four Channels1DC to 2 MbpsV DD1 or V DD2 Supply Current I DD1 (Q), I DD2 (Q) 1.0 1.8 mA DC to 1 MHz logic signal frequency10 Mbps (BRWZ Version Only)V DD1 or V DD2 Supply Current I DD1 (10), I DD2 (10) 2.6 3.8 mA 5 MHz logic signal frequencyAll ModelsInput Currents I IA, I IB, I IC, I ID,I CTRL1,I CTRL2, I DISABLE −10 +0.01 +10µA 0 V ≤ V IA, V IB, V IC, V ID ≤ V DD1 or V DD2,0 V ≤ V CTRL1, V CTRL2 ≤ V DD1 or V DD2,0 V ≤ V DISABLE ≤ V DD1Logic High Input Threshold V IH 1.6 V Logic Low Input Threshold V IL 0.4 VLogic High Output Voltages V OAH, V OBH,V OCH, V ODH (V DD1 or V DD2) − 0.1 3.0 V I Ox = −20 µA, V Ix = V IxH (V DD1 or V DD2) − 0.4 2.8 V I Ox = −4 mA, V Ix = V IxHLogic Low Output Voltages V OAL, V OBL,V OCL, V ODL0.0 0.1 V I Ox = 20 µA, V Ix = V IxL0.04 0.1 V I Ox = 400 µA, V Ix = V IxL0.2 0.4 V I Ox = 4 mA, V Ix = V IxL Rev. M | Page of 22ADuM1410/ADuM1411/ADuM1412 Data Sheet。

MAX708规格书,MAX705,MAX706,MAX707,MAX813LCSA技术资料,datasheet,PDF

PARAMETER

SYMBOL

CONDITIONS

MIN TYP MAX UNITS

Operating Voltage Range

Supply Current

Reset Threshold (Note 2) Reset Threshold Hysteresis (Note 2) Reset Pulse Width (Note 2) RESET Output Voltage

VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20mA GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20mA

o Voltage Monitor for Power-Fail or Low-Battery Warning

______________Ordering Information

PART MAX705CPA MAX705CSA MAX705CUA MAX705C/D

TEMP. RANGE 0°C to +70°C 0°C to +70°C 0°C to +70°C 0°C to +70°C

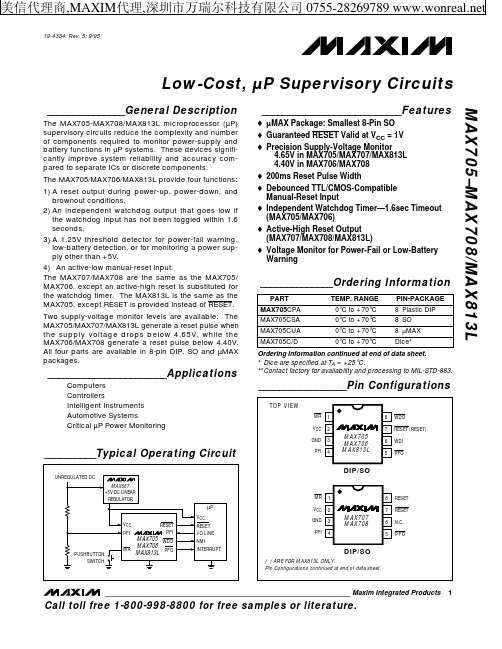

The MAX705/MAX706/MAX813L provide four functions:

1) A reset output during power-up, power-down, and brownout conditions.

半导体传感器ADG708BRUZ中文规格书

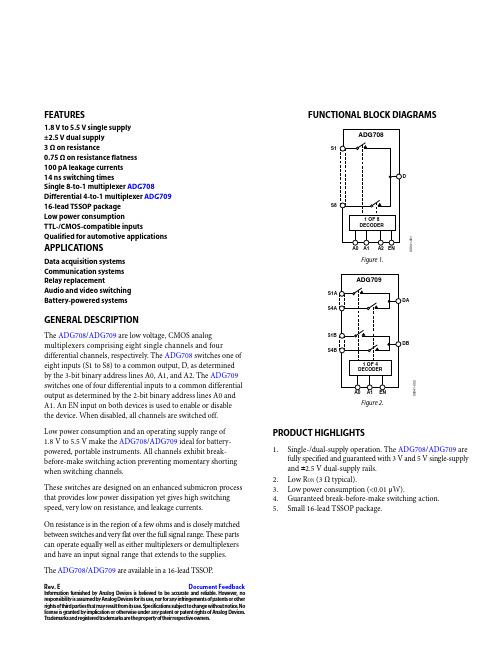

FEATURES1.8 V to 5.5 V single supply±2.5 V dual supply3 Ω on resistance0.75 Ω on resistance flatness100 pA leakage currents14 ns switching timesSingle 8-to-1 multiplexer ADG708Differential 4-to-1 multiplexer ADG70916-lead TSSOP packageLow power consumptionTTL-/CMOS-compatible inputsQualified for automotive applications APPLICATIONSData acquisition systemsCommunication systemsRelay replacementAudio and video switchingBattery-powered systemsGENERAL DESCRIPTIONThe ADG708/ADG709 are low voltage, CMOS analog multiplexers comprising eight single channels and four differential channels, respectively. The ADG708 switches one of eight inputs (S1 to S8) to a common output, D, as determined by the 3-bit binary address lines A0, A1, and A2. The ADG709 switches one of four differential inputs to a common differential output as determined by the 2-bit binary address lines A0 and A1. An EN input on both devices is used to enable or disable the device. When disabled, all channels are switched off.Low power consumption and an operating supply range of1.8 V to 5.5 V make the ADG708/ADG709 ideal for battery-powered, portable instruments. All channels exhibit break-before-make switching action preventing momentary shorting when switching channels.These switches are designed on an enhanced submicron process that provides low power dissipation yet gives high switching speed, very low on resistance, and leakage currents.On resistance is in the region of a few ohms and is closely matched between switches and very flat over the full signal range. These parts can operate equally well as either multiplexers or demultiplexers and have an input signal range that extends to the supplies.FUNCTIONAL BLOCK DIAGRAMSS1S841-1Figure 1.41-2Figure 2.PRODUCT HIGHLIGHTS1.Single-/dual-supply operation. The ADG708/ADG709 arefully specified and guaranteed with 3 V and 5 V single-supply and ±2.5 V dual-supply rails.2.Low R ON (3 Ω typical).3.Low power consumption (<0.01 μW).4.Guaranteed break-before-make switching action.5.Small 16-lead TSSOP package.The ADG708/ADG709 are available in a 16-lead TSSOP.Rev. E Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners.ADG708/ADG709Data Sheet PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONSA0EN S2S3S4V SSS1D A1A2S5S6S7GND V DDS800041-003Figure 3. ADG708 Pin Configuration A0EN S2A S3A S4AV SS S1A DAA1GND S2B S3B S4B V DD S1BDB 00041-004Figure 4. ADG709 Pin Configuration Table 5. ADG708 Pin Function DescriptionsPin No.Mnemonic Description 1A0 Digital Input. Controls the configuration of the switch, as shown in the truth table (see Table 7). 2EN Digital Input. Controls the configuration of the switch, as shown in the truth table (see Table 7). 3V SS Most Negative Power Supply Pin in Dual-Supply Applications. For single-supply applications, it should be tied to GND. 4S1 Source Terminal. Can be an input or output. 5S2 Source Terminal. Can be an input or output. 6S3 Source Terminal. Can be an input or output. 7S4 Source Terminal. Can be an input or output. 8D Drain Terminal. Can be an input or output. 9S8 Source Terminal. Can be an input or output. 10S7 Source Terminal. Can be an input or output. 11S6 Source Terminal. Can be an input or output. 12S5 Source Terminal. Can be an input or output. 13V DD Most Positive Power Supply Pin. 14GND Ground (0 V) Reference. 15A2 Digital Input. Controls the configuration of the switch, as shown in the truth table (see Table 7). 16 A1 Digital Input. Controls the configuration of the switch, as shown in the truth table (see Table 7). Table 6. ADG709 Pin Function DescriptionsPin No.Mnemonic Description 1A0 Digital Input. Controls the configuration of the switch, as shown in the truth table (see Table 8). 2EN Digital Input. Controls the configuration of the switch, as shown in the truth table (see Table 8). 3V SS Most Negative Power Supply Pin in Dual-Supply Applications. For single-supply applications, it should be tied to GND. 4S1A Source Terminal. Can be an input or output. 5S2A Source Terminal. Can be an input or output. 6S3A Source Terminal. Can be an input or output. 7S4A Source Terminal. Can be an input or output. 8DA Drain Terminal. Can be an input or output. 9DB Drain Terminal. Can be an input or output. 10S4B Source Terminal. Can be an input or output. 11S3B Source Terminal. Can be an input or output. 12S2B Source Terminal. Can be an input or output. 13S1B Source Terminal. Can be an input or output. 14V DD Most Positive Power Supply Pin. 15GND Ground (0 V) Reference. 16 A1 Digital Input. Controls the configuration of the switch, as shown in the truth table (see Table 8).Rev. E | Page 10 of 20。

BLT708C故障手册(1)

MPK708C系统电梯故障手册编制:审核:MPK708C系统电梯故障手册电梯在调试过程中会出现各种故障,系统的故障记录信息是问题分析,解决的有效途径,本手册详细介绍了MPK708C电梯控制系统、SIEI变频器提供的各种故障信息及分析解决问题的方。

一、MPK708C控制器故障记录图例:1、E1: Security circuit opened解释:安全回路断开原因:变压器TC2保险丝熔断安全回路有开关路动作安全窗、盘车手轮、底坑、轿顶、机房、曳引机急停开关动作解决办法:更换保险丝检查限速器、上/下极限、断绳、缓冲器、安全钳开关检查安全窗、盘车手轮、底坑、轿顶、机房、曳引机急停动作故障显示及恢复方法:楼层显示器可显示,微机记录故障,安全回路恢复正常即可复位故障。

2、E2:Door Lock Opened Or Error解释:门锁故障原因:关门时厅/ 轿门锁不通,超时关门运行时厅/ 轿门锁断开,电梯急停主控器检测点故障解决办法:检查门机检查轿顶板PM709输入输出信号动作是否准确主控器I3.1 , I3.2 输入信号是否正确检查厅/轿门联锁及线路故障显示及恢复方法:楼层显示器可显示,微机记录故障,门锁信号恢复正常即可复位故障。

出现此故障后可能伴有E14出现,电梯到端站重新校正后恢复运行。

3、E3: Can’t Find the Leveling Point解释:电梯减速后超过10秒检测不到门区信号原因:门区开关损坏平层板插入深度少解决办法:更换门区开关平层板至少插入开关2/3故障显示及恢复方法:楼层显示器显示,微机记录故障,检修复位。

4、E4: Can’t Find the Deceleration Point解释:检测不到减速点原因:换速(双稳态)开关故障换速磁铁位置错误变频器分频卡输出脉冲错误或有干扰参数time/floor protect错误解决办法:检查换速(双稳态)开关,并更换调整磁铁位置,磁铁距离开关水平距离6+1mm-通过主控器显示界面观察脉冲信号变化是否正常检测变频器分频模块调整加大time/floor protect参数(默认13S)故障显示及恢复方法:楼层显示器可显示,微机记录故障,出现此故障后可能伴有E14出现,电梯到端站重新校正后恢复运行。

美侬(MEROL)ME-707&708全自动咖啡机中文使用说明书

废水盒电源线电源开关蒸汽管咖啡出口旋钮保温板水箱豆粉盖豆箱加粉口粗细调节钮酿造单元酿造门接渣盘废渣盘控制面板机器各部件说明控制面板说明图1图212345678910111213141516171.了解本咖啡机2.使用前的安全须知3.开始使用机器1.1机器各部件说明1.2咖啡机的控制面板1.3咖啡机的安全装置1.4本机的规格参数1.5咖啡机的附件2.1安全2.2连接电源3.1安装机器并添入咖啡原料3.2排水3.3操作机器酿造咖啡1.3.1粉量保护1.3.2防沙石保护2.1.1电源线2.1.2不能让小孩靠近本机2.1.3机器放置2.1.4清洁2.1.5修理和维护3.3.1酿造单杯咖啡3.3.2酿造双份咖啡3.3.3中断酿造3.3.4设定记忆量3.3.5用咖啡豆酿造咖啡目录3.4机器使用中的参考和建议3.5程序设定3.6其他提示3.7咖啡机的清洁和维护4.故障检修/“三包”期限3.3.6用咖啡粉酿造咖啡3.3.7使用本机提供热水3.3.8使用本机提供蒸汽3.3.9使用蒸汽加压发泡3.4.1预热杯子3.4.2调节咖啡豆的研磨粗细度3.4.3如何使用水硬度测试纸3.4.4调节咖啡豆的研磨粉量3.4.5调节出咖啡口的高度3.4.6预先浸泡咖啡粉(即预酿造功能)3.4.7咖啡豆的储存3.4.8关于水质3.4.9关于机器工作时间3.4.10关掉机器电源3.5.1菜单3.7.1清洗主要外部件3.7.2清洁接水装置3.7.3去除水垢3.7.4清洗管路3.7.5机器的保存Contents 0101010101010102030303040505050606060808080909090909101011121213131313141414141414141719192122242425●本机酿制一杯咖啡只研磨新鲜咖啡豆的一部分,从而确保酿制最优质咖啡。

●研磨前,确定旋钮(6)是关闭的。

调节理想的研磨度数,建议值为2。

ADM708中文资料

RESET & WATCHDOG TIMEBASE

RESET GENERATOR

RESET

ADM705/ ADM706

POWER-FAIL OUTPUT (PFO)

*VOLTAGE REFERENCE = 4.65V (ADM705), 4.40V (ADM706)

VCC 250A MR VCC 4.65V* POWER-FAIL INPUT (PFI) 1.25V RESET GENERATOR RESET RESET

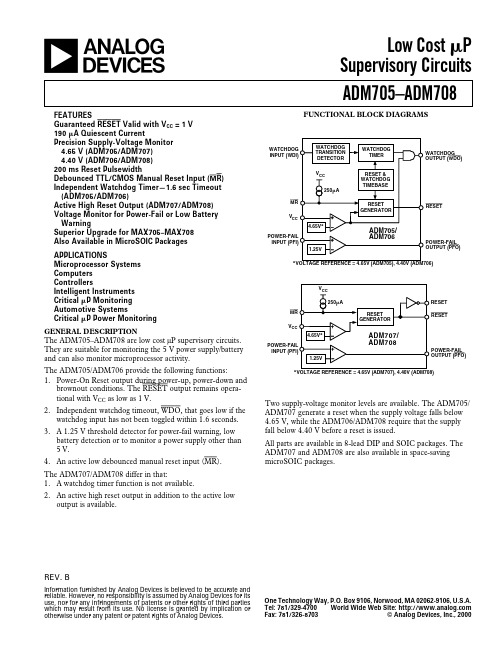

The ADM705–ADM708 are low cost µP supervisory circuits. They are suitable for monitoring the 5 V power supply/battery and can also monitor microprocessor activity. The ADM705/ADM706 provide the following functions: 1. Power-On Reset output during power-up, power-down and brownout conditions. The RESET output remains operational with VCC as low as 1 V. 2. Independent watchdog timeout, WDO, that goes low if the watchdog input has not been toggled within 1.6 seconds. 3. A 1.25 V threshold detector for power-fail warning, low battery detection or to monitor a power supply other than 5 V. 4. An active low debounced manual reset input (MR). The ADM707/ADM708 differ in that: 1. A watchdog timer function is not available. 2. An active high reset output in addition to the active low output is available.

ADM706中文资料

元器件交易网

ADM705–ADM708–SPECIFICATIONS (V

Parameter VCC Operating Voltage Range Supply Current Reset Threshold Reset Threshold Hysteresis Reset Pulsewidth RESET Output Voltage Min 1.0 190 4.5 4.25 160 VCC – 1.5 4.65 4.40 40 200 Typ Max 5.5 250 4.75 4.50 280 0.4 0.3 0.3 RESET Output Voltage Watchdog Timeout Period (tWD) WDI Pulsewidth (tWP) WDI Input Threshold Logic Low Logic High WDI Input Current WDO Output Voltage MR Pull-Up Current MR Pulsewidth MR Input Threshold MR to Reset Output Delay PFI Input Threshold PFI Input Current PFO Output Voltage

元器件交易网

a

FEATURES Guaranteed RESET Valid with VCC = 1 V 190 A Quiescent Current Precision Supply-Voltage Monitor 4.65 V (ADM705/ADM707) 4.40 V (ADM706/ADM708) 200 ms Reset Pulsewidth Debounced TTL/CMOS Manual Reset Input ( MR) Independent Watchdog Timer—1.6 sec Timeout (ADM705/ADM706) Active High Reset Output (ADM707/ADM708) Voltage Monitor for Power-Fail or Low Battery Warning Superior Upgrade for MAX705–MAX708 Also Available in MicroSOIC Packages APPLICATIONS Microprocessor Systems Computers Controllers Intelligent Instruments Critical P Monitoring Automotive Systems Critical P Power Monitoring GENERAL DESCRIPTION

EZJZZV800AA中文资料

(Unit: mm)

A Symbol

Size Code

B W F E P1 P2 P0 fD t1 t2

0201 0402

0.37 0.67

0.5 0.8

±0.03 ±0.03 8.0 3.50 1.75 2.00 2.00 4.0 1.5 max. max.

0.62

±0.05

1.12

±0.05

±0.2 ±0.05 ±0.10 ±0.05 ±0.05 ±0.05 +0.1 0

n Precautions for Handling see Page 112 to 118

n Packing method see Page 111, 182

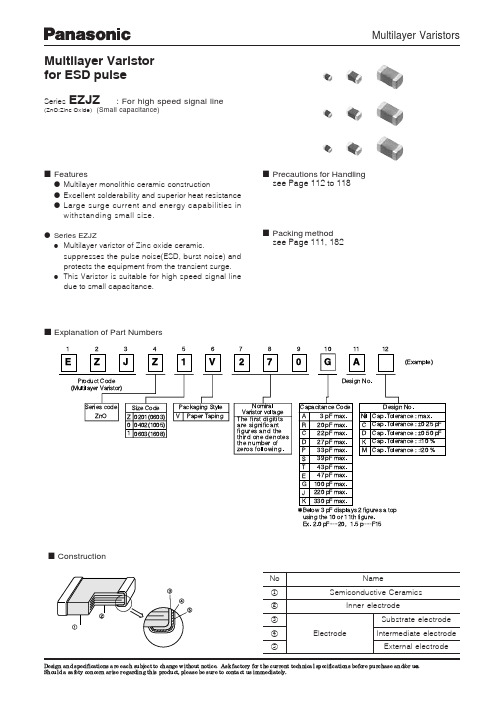

n Explanation of Part Numbers

1

2

3

4

5

6

7

8

9

10

11

12

EZ J Z 1 V 2 7 0GA

(Example)

n Typical Characteristics

l Voltage vs. Current

1000

100

10

EZJZ V171 A

EZJZ V800 A

EZJZ V500 A

EZJZ V330 A EZJZ V270 EZJZ V120

A A

1

0.000001 0.00001 0.0001 0.001

0201 EZJZZV270RA EZJZ0V120JA

0402 EZJZ0V270RA EZJZ0V270EA EZJZ1V120KA

0603 EZJZ1V270GA EZJZ1V330GA

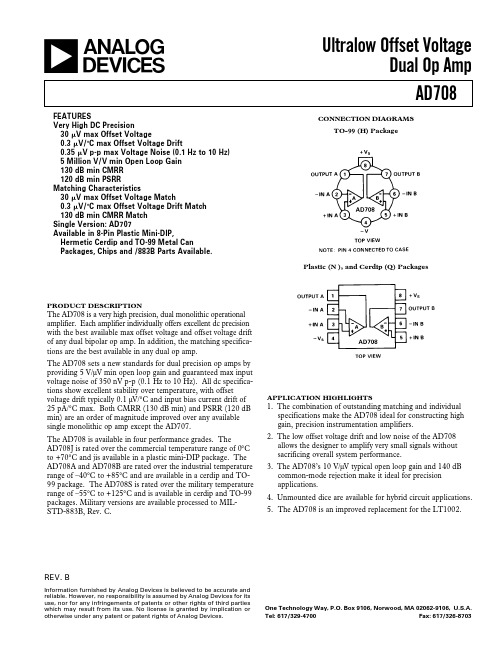

AD708中文资料

CONNECTION DIAGRAMSTO-99 (H) PackagePlastic (N ), and Cerdip (Q) PackagesREV.BInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.aUltralow Offset VoltageDual Op Amp AD708One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 617/329-4700Fax: 617/326-8703FEATURESVery High DC Precision30 V max Offset Voltage0.3 V/؇C max Offset Voltage Drift0.35 V p-p max Voltage Noise (0.1 Hz to 10 Hz)5 Million V/V min Open Loop Gain 130 dB min CMRR 120 dB min PSRRMatching Characteristics30 V max Offset Voltage Match0.3 V/؇C max Offset Voltage Drift Match 130 dB min CMRR Match Single Version: AD707Available in 8-Pin Plastic Mini-DIP,Hermetic Cerdip and TO-99 Metal CanPackages, Chips and /883B Parts Available.PRODUCT DESCRIPTIONThe AD708 is a very high precision, dual monolithic operational amplifier. Each amplifier individually offers excellent dc precision with the best available max offset voltage and offset voltage drift of any dual bipolar op amp. In addition, the matching specifica-tions are the best available in any dual op amp.The AD708 sets a new standards for dual precision op amps by providing 5 V/µV min open loop gain and guaranteed max input voltage noise of 350 nV p-p (0.1 Hz to 10 Hz). All dc specifica-tions show excellent stability over temperature, with offset voltage drift typically 0.1 µV/°C and input bias current drift of 25 pA/°C max. Both CMRR (130 dB min) and PSRR (120 dB min) are an order of magnitude improved over any available single monolithic op amp except the AD707.The AD708 is available in four performance grades. TheAD708J is rated over the commercial temperature range of 0°C to +70°C and jis available in a plastic mini-DIP package. The AD708A and AD708B are rated over the industrial temperature range of –40°C to +85°C and are available in a cerdip and TO-99 package. The AD708S is rated over the military temperature range of –55°C to +125°C and is available in cerdip and TO-99packages. Military versions are available processed to MIL-STD-883B, Rev. C.APPLICATION HIGHLIGHTS1.The combination of outstanding matching and individual specifications make the AD708 ideal for constructing high gain, precision instrumentation amplifiers.2.The low offset voltage drift and low noise of the AD708allows the designer to amplify very small signals without sacrificing overall system performance.3.The AD708’s 10 V/µV typical open loop gain and 140 dB common-mode rejection make it ideal for precision applications.4.Unmounted dice are available for hybrid circuit applications.5.The AD708 is an improved replacement for the LT1002.AD708–SPECIFICATIONS(@ +25؇C and ؎15 V dc, unless otherwise noted)AD708J/A AD708B AD708SModel Conditions Min Typ Max Min Typ Max Min Typ Max Units INPUT OFFSET VOLTAGE130100550530µVT MIN to T MAX5015015651550µV Drift0.3 1.00.10.40.10.3µV/°C Long Term Stability0.30.30.3µV/Month INPUT BIAS CURRENT 1.0 2.50.5 1.00.51nAT MIN to T MAX 2.0 4.0 1.0 2.0 1.04nA Average Drift154010251030pA/°C OFFSET CURRENT V CM = 0 V0.5 2.00.1 1.00.11nAT MIN to T MAX 2.0 4.00.2 1.50.2 1.5nA Average Drift260125125pA/°C MATCHING CHARACTERISTICS2Offset Voltage805030µVT MIN to T MAX1507550µV Offset Voltage Drift 1.00.40.3µV/°C Input Bias Current 4.0 1.0 1.0nAT MIN to T MAX 5.0 2.0 2.0nA Common-Mode Rejection120140130140130140dBT MIN to T MAX110130130dB Power Supply Rejection110120120dBT MIN to T MAX110120120dB Channel Separation135140140dB INPUT VOLTAGE NOISE0.1 Hz to 10 Hz0.230.60.230.60.230.35µV p-pf = 10 Hz10.31810.31210.312nV/√Hzf = 100 Hz10.013.010.011.010.011nV/√Hzf = 1 kHz9.611.09.611.09.611nV/√Hz INPUT CURRENT NOISE0.1 Hz to 10 Hz143514351435pA p-pf = 10 Hz0.320.90.320.80.320.8pA/√Hzf = 100 Hz0.140.270.140.230.140.23pA/√Hzf = 1 kHz0.120.180.120.170.120.17pA/√Hz COMMON-MODEREJECTION RATIO V CM = ±13 V120140130140130140dBT MIN to T MAX120140130140130140dB OPEN-LOOP GAIN V O = ±10 VR LOAD≥ 2 kΩ310510410V/µVT MIN to T MAX31051047V/µV POWER SUPPLYREJECTION RATIO V S = ±3 V to ±18 V110130120130120130dBT MIN to T MAX110130120130120130dB FREQUENCY RESPONSEClosed Loop Bandwidth0.50.90.50.90.50.9MHz Slew Rate0.150.30.150.30.150.3V/µs INPUT RESISTANCEDifferential60200200MΩCommon Mode200400400GΩOUTPUT VOLTAGE R LOAD≥ 10 kΩ13.51413.514.013.514±VR LOAD≥ 2 kΩ12.513.012.513.012.513±VR LOAD≥ 1 kΩ12.012.512.012.512.012.5±VR LOAD≥ 2 kΩT MIN to T MAX12.013.012.013.012.013±V OPEN-LOOP OUTPUTRESISTANCE606060Ω–2–REV. BAD708J/A AD708B AD708SModel Conditions Min Typ Max Min Typ Max Min Typ Max Units POWER SUPPLYQuiescent Current 4.5 5.5 4.5 5.5 4.5 5.5mA Power Consumption V S = ±15 VNo Load135165135165135165mWV S = ±3 V121812181218mW Operating Range±3±18±3±18±3±18V NOTES1Input offset voltage specifications are guaranteed after 5 minutes of operation at TA = +25°C.2Matching is defined as the difference between parameters of the two amplifiers.All min and max specifications are guaranteed. Specifications in boldface are tested on all production units at final electrical test. Results from those tests are used to calculate outgoing quality levels.Specifications subject to change without notice.ABSOLUTE MAXIMUM RATINGS1Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .±22 V Internal Power Dissipation2Input Voltage3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .±V S Output Short Circuit Duration . . . . . . . . . . . . . . . . Indefinite Differential Input Voltage . . . . . . . . . . . . . . . . . . +V S and –V S Storage Temperature Range (Q, H) . . . . . . . –65°C to +150°C Storage Temperature Range (N) . . . . . . . . . –65°C to +125°C Lead Temperature Range (Soldering 60 sec) . . . . . . . . +300°C NOTES1Stresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.2Thermal Characteristics8-Pin Plastic Package:θJC = 33°C/Watt, θJA = 100°C/Watt8-Pin Cerdip package:θJC = 30°C/Watt, θJA = 110°C/Watt8-Pin Metal Can Package:θJC = 65°C/Watt, θJA = 150°C/Watt.3For supply voltages less than ±22 V, the absolute maximum input voltage is equal to the supply voltage.METALIZATION PHOTOGRAPH Dimensions shown in inches and (mm).Contact factory for latest dimensions.REV. B–3–AD708ORDERING GUIDETemperature Package Package Model Range Description Option* AD708JN0°C to +70°C8-Pin Plastic DIP N-8AD708AQ–40°C to +85°C8-Pin Cerdip Q-8AD708BQ–40°C to +85°C8-Pin Cerdip Q-8AD708SQ–55°C to +125°C8-Pin Cerdip Q-8AD708AH–40°C to +85°C8-Pin Header H-08A AD708BH–40°C to +85°C8-Pin Header H-08A AD708SH–55°C to +125°C8-Pin Header H-08A AD708SH/883B–55°C to +125°C8-Pin Header H-08A AD708J Grade Chips0°C to +70°C DieAD708S Grade Chips–55°C to +125°C Die*N = Plastic DIP; Q = Cerdip; H = Hermetic Metal Can.REV. B–4–(V S= ؎15 V and T A= +25؇C unless otherwise noted)AD708–Typical CharacteristicsAD708πREV. B –5–REV. B–6–Figure 24.Crosstalk with No Load Figure 26.Crosstalk under Forced Source and Sink ConditionsFigure 25.Crosstalk with 2k Ω LoadFigure 20.Typical Distribution of InputBias Current MatchCrosstalk from Thermal Effects of Power DissipationAD708–Matching CharacteristicsFigure 19.Typical Distribution of Offset Voltage Drift Match Figure 18.Typical Distribution of Offset Voltage Match Figure 21.Typical Distribution of Input Offset Current Match Figure 22.PSRR Match vs.Temperature Figure 23.CMRR Match vs.TemperatureAD708REV. B–7–CROSSTALK PERFORMANCE OF THE AD708The AD708 exhibits very low crosstalk as shown in Figures 24,25 and 26. Figure 24 shows the offset voltage induced in side B of the AD708 when side A’s output is moving slowly (0.2 Hz)from –10 V to +10 V under no load. This is the least stressful situation to the part since the overall power in the chip does not change; only the location of the power in the output devices changes. Figure 25 shows side B’s input offset voltage change when side A is driving a 2k Ω load. Here the power is being changed in the chip with the maximum power change occurring at ±7.5 V. Figure 26 shows crosstalk under the most severe conditions. Side A is connected as a follower with 0 V input,and is now forced to sink and source ±5 mA of output current (Power = (30 V) (5 mA) = 150 mW). Even this large change in power causes only an 8µV (linear) change in side B’s input offset voltage.OPERATION WITH A GAIN OF –100To show the outstanding dc precision of the AD708 in realapplication, Table I shows an error budget calculation for a gain of –100 configuration shown in Figure 27.Table I.Maximum Error ContributionA V = 100 (S Grade)Error Sources (Full Scale:V OUT = 10 V, V IN = 100 mV)V OS 30 µV/100 mV= 300 ppm I OS(100 k Ω)(1 nA)/10 V = 10ppm Gain (2 k Ω load)10 V/(5*106))/100 mV = 20 ppm Noise 0.35µV/100mV = 4 ppm V OS Drift(0.3µV/°C)/100 mV= 3 ppm/°C = 334 ppm +3 ppm/°CTotal Unadjusted Error@ 25°C= 334 ppm > 11 Bits –55°C to +125°C = 634 ppm > 10 Bits With OffsetCalibrated Out@ 25°C= 34 ppm > 14 Bits –55°C to +125°C= 334 ppm > 11 BitsFigure 27. Gain of –100 ConfigurationThis error budget assumes no error in the resistor ratio and no error from power supply variation (the 120 dB minimum PSRR of the AD708S makes this a good assumption). The external resistors can cause gain error from mismatch and drift over temperature.High Precision Programmable Gain AmplifierThe three op amp programmable gain amplifier shown in Figure 28 takes advantage of the outstanding matching characteristics of the AD708 to achieve high dc precision. The gains of the circuit Figure 28.Precision PGAare controlled by the select lines, A0 and A1 of the AD7502multiplexer, and are 1, 10, 100 and 1000 in this design.The input stage attains very high dc precision due to the 30µV maximum offset voltage match of the AD708S and the 1 nA maximum input bias current match. The accuracy is maintained over temperature because of the ultralow drift performance of the AD708. The output stage uses an AD707J and well matched resistors configured as a precision subtracter.To achieve 0.1% gain accuracy, along with high common-mode rejection, the circuit should be trimmed as follows:To maximize common-mode rejection:1.Set the select lines for Gain = 1 and ground V INB .2.Apply a precision dc voltage to V INA and trim R A until V O = –V INA to the required precision.3.Next connect V INB to V INA and apply an input voltage equal to the full-scale common-mode expected.4.Trim R B until V O = 0 V.To minimize gain errors:1.Select Gain = 10 with the control lines and apply a differential input voltage.2.Adjust the 100Ω potentiometer such that V O = 10V IN (adjust V IN magnitude as necessary).3.Repeat for Gain = 100 and Gain = 1000, adjusting 1k Ω and 10k Ω potentiometers, respectively.The design shown should allow for 0.1% gain accuracy and 0.1µV/V common-mode rejection when ±1% resistors and ±5%potentiometers are used.BRIDGE SIGNAL CONDITIONERThe AD708 can be used in the circuit in Figure 29 to produce an accurate and inexpensive dynamic bridge conditioner. The low offset voltage match and low offset voltage drift match of the AD708 combine to achieve circuit performance better than all but the best instrumentation amplifiers. The AD708’s out-standing specs: open loop gain, input offset currents and low input bias currents, do not limit circuit accuracy.AD708REV. B–8–C 1252a –10–2/91P R I N T E D I N U .S .A .As configured, the circuit only requires a gain resistor, R G , of suitable accuracy and a stable, accurate voltage reference. The transfer function is:V O = V REF [∆R/(R+∆R)][R G /R]and the only significant errors due to the AD708S are:V OS out = (V OS match)(2R G /R) = 30 mVV OS out(T) = (V OS drift)(2R G /R) = 0.3 mV/°C To achieve high accuracy, the resistor R G should be 0.1% orbetter and have a low drift coefficient.Figure 29.Bridge Signal Conditioning CircuitFigure 30.Precision Absolute Value CircuitPRECISION ABSOLUTE VALUE CIRCUITThe AD708 is ideally suited to the precision absolute value circuit shown in Figure 30. The low offset voltage match of the AD708 enables this circuit to accurately resolve the input signal.In addition, the tight offset voltage drift match maintains the resolution of the circuit over the full military temperature range.The AD708’s high dc open loop gain and exceptional gain linearity allows the circuit to perform well at both large and small signal levels.In this circuit, the only significant dc errors are due to the offset voltage of the two ampliliers, the input offset current match of the amplifiers, and the mismatch of the resistors. Errors associ-ated with the AD708S contribute less than 0.001% error over –55°C to +125°C.Maximum error at 25°C30µV +10k Ω()1nA ()10V =40µV /10V =4ppm Maximumerror at +125°C or –55°C50µV +2nA ()10k Ω()10V =7ppm @+125°CFigure 31 shows V OUT vs. V IN for this circuit with a ±3mVinput signal at 0.05Hz. Note that the circuit exhibits very low offset at the zero crossing. This circuit can also produce V OUT =–|V IN | by reversing the polarity of the two diodes.Figure 31.Absolute Value Circuit Performance (Input Signal = 0.05 Hz)SELECTION OF PASSIVE COMPONENTSTo takc full advantagc of thc high precision and low driftcharacteristics of the AD708, high quality passive components must be used. Discrete resistors and resistor networks with temperature coefficients of less than 10 ppm/°C are available from Vishay, Caddock, PRP and others.OUTLINE DIMENSIONSDimensions shown in inches and (mm).TO-99 (H) PackageCerdip (Q) PackageMini-DIP (N) Package。

Unity3D中文手册

957F 5B B D 9A D8957F 5B B D 9A D 8 957F 5B B D 9A D 8Unity3D 中文手册User Manual(内部培训教材)译:Nette长宽高(北京)科技有限公司957F 5B B D 9A D8957F 5B B D 9A D 8 957F 5B B D 9A D 8说明:本文档所有资源均来自于互联网。

如果你对本文档中的内容有疑问请发送Email 到tianyhongcn@注意:本文档不包含组件参考和脚本参考的任何内容,它们将是另外的文档。

版权:1. 该文档属公司内部培训教程,不发行,不出版,仅作为公司内部的技术参考。

2. 本文档内容已申请著作权,受中国版权法保护,未经著作权人书面许可,本手册的任何部分不得以任何形式或手段复制或传播。

957F 5B B D 9A D8957F 5B B D 9A D 8 957F 5B B D 9A D 8目录欢迎使用Unity................................................................................................................................1 一、用户指南. (2)1.1. Unity 基础(Unity Basics) (2)1.1.1. 学习界面...........................................................................................................2 1.1.2. 资源工作流(Asset Workflow)........................................................................17 1.1.3. 创建场景(Creating Scenes)............................................................................18 1.1.4. 发布(Publishing Builds)..................................................................................19 1.1.5. 教程(Tutorials)................................................................................................22 1.2. 构建场景(Building Scenes) (23)1.2.1. 游戏物体(GameObject)..................................................................................23 1.2.2. 使用组件(Using Components).......................................................................25 1.2.3. 预设(Prefab)....................................................................................................30 1.2.4. 光照(Lights)....................................................................................................33 1.2.5. 相机(Cameras)................................................................................................42 1.2.6. 粒子系统(Particle Systems)............................................................................46 1.2.7. 地形引擎指南(Terrain Engine Guide)............................................................59 1.3. 使用资源(Working with Assets).. (62)1.3.1. 导入资源(Importing Assets)...........................................................................63 1.3.2. 网格(Meshes)..................................................................................................65 1.3.3. 材质和着色器(Material and Shaders)............................................................69 1.3.4. 2D 纹理(Texture 2D)......................................................................................72 1.3.5. 电影纹理(Movie Texture)...............................................................................78 1.3.6. 音频文件(Audio Files)...................................................................................80 1.3.7. 使用脚本(Using Scripts).................................................................................84 1.3.8. 资源服务器指南(Assets Server Guide)..........................................................88 1.3.9. 场景背后(Behind the Scenes).........................................................................94 1.4. 创建游戏(Creating Gameplay). (94)1.4.1. 运行时实例化预设(Instantiating Prefabs at runtime)....................................95 1.4.2. 输入(Input)....................................................................................................100 1.4.3. 变换(Transforms)..........................................................................................102 1.4.4. 物理(Physics)................................................................................................107 1.4.5. 动画(Animation)...........................................................................................124 1.4.6. 角色动画(Character Animation)...................................................................126 1.4.7. 声音(Sound)..................................................................................................133 1.4.8. 游戏接口元素...............................................................................................138 1.4.9. 多人网络. (139)二、常见问题(FAQ) (141)2.1. 游戏编码问题 (141)2.1.1. 如何制作一个简单的第一人称行走...........................................................141 2.2. 图形问题 (141)957F 5B B D 9A D8957F 5B B D 9A D 8 957F 5B B D 9A D 82.2.1. 如何导入透明贴图.......................................................................................142 2.2.2. 如何使用凹凸贴图.......................................................................................144 2.2.3. 如何使用细节纹理.......................................................................................147 2.2.4. 如何制作立方体贴图纹理...........................................................................149 2.2.5. 如何制作天空盒...........................................................................................150 2.2.6. 如何制作网格粒子发射器...........................................................................151 2.2.7. 如何制作启动画面.......................................................................................152 2.2.8. 如何制作投射光Cookie..............................................................................153 2.2.9. 如何修正导入模型的旋转...........................................................................154 2.2.10. 如何使用水...................................................................................................155 2.3. 如何从3D 程序中导入物体.. (158)2.3.1. 从Maya 中导入物体....................................................................................158 2.3.2. 从Cinema 4D 导入物体...............................................................................159 2.3.3. 从3DMax 中导入物体.................................................................................161 2.3.4. 从Cheetah3D 中导入物体...........................................................................164 2.3.5. 从Modo 中导入物体...................................................................................164 2.3.6. 从Lightwave 中导入物体............................................................................165 2.3.7. 从Blender 中导入物体................................................................................168 2.4. 工作流问题.. (169)2.4.1. 如何在工程间重用资源...............................................................................169 2.4.2. 如何安装或更新标准资源 (169)三、高级 (171)3.1. 实时加载资源.......................................................................................................171 3.2. 通过脚本修改源资源...........................................................................................171 3.3. 更新顺序...............................................................................................................173 3.4. Unity 中的阴影.. (174)3.4.1. 直射光细节...................................................................................................175 3.4.2. 调试阴影.......................................................................................................180 3.4.3. 阴影大小计算...............................................................................................181 3.5. 优化图形性能. (182)3.5.1. 角色建模优化...............................................................................................183 3.5.2. 集成显卡优化...............................................................................................184 3.5.3. 渲染统计窗口...............................................................................................185 3.6. 减小文件尺寸.......................................................................................................186 3.7. 流式Web 播放.....................................................................................................189 3.8. Web 播放器部署.. (191)3.8.1. 加载Unity 内容的HTML 代码..................................................................191 3.8.2. 自定义Unity Web 播放器的加载场景........................................................192 3.8.3. 自定义Unity Web 播放器的行为................................................................194 3.8.4. Unity Web 播放器和浏览器通信.................................................................194 3.8.5. 使用浏览器脚本检测Unity Web 播放器....................................................196 3.8.6. 发布活动内容...............................................................................................199 3.9. Web 播放器调试..................................................................................................201 3.10. 插件——Pro 版特性.. (202)957F 5B B D 9A D8957F 5B B D 9A D 8 957F 5B B D 9A D 83.11. 建立播放器流水线...............................................................................................204 3.12. 着色器. (205)3.12.1. 着色器:开始...............................................................................................205 3.12.2. 着色器:顶点和片元程序...........................................................................210 3.13. 显卡模拟...............................................................................................................216 3.14. 网络模拟 (217)957F 5B B D 9A D8957F 5B B D 9A D 8 957F 5B B D 9A D 8欢迎使用UnityUnity 使用户能够创建最好的交互式娱乐或者多媒体体验,该手册被设计用于帮助你学习如何使用Unity ,从基础到高级技术。

MAX708RESA-TG中文资料

MAX707, MAX708m P Supervisory CircuitsThe MAX707/708 are cost−effective system supervisor circuits designed to monitor V CC in digital systems and provide a reset signal to the host processor when necessary. No external components are required.The reset output is driven active within 20 m sec of V CC falling through the reset voltage threshold. Reset is maintained with 200 mS of delay time after V CC rise above the reset threshold. The MAX707/708 have a low quiescent current of 12 mA at V CC = 3.3 V, an active−high RESET and active−low RESET with a push−pull output. The output is guaranteed valid down to V CC = 1.0 V. The MAX707/708 have a Manual Reset MR input and a +1.25 V threshold detector for power−fail input PFI. These devices are available in a Micro8 and SOIC−8 package.Features•Precision Supply−V oltage MonitorMAX707: 4.63 V Reset Threshold V oltageMAX708: Standard Reset Threshold V oltages (Typical):4.38 V, 3.08 V, 2.93 V, 2.63 V•Reset Threshold Available from 1.6 V to 4.9 V with 100 mV Increments (Factory Option)•200 mS (Typ) Reset Timeout Delay•12 m A (V CC = 3.3 V) Quiescent Current•Active_High and Active_Low Reset Output •Guaranteed RESET_L and RESET Output Valid to V CC = 1.0 V •V oltage Monitor for Power−Fail or Low−Battery Warning•8 Pin SOIC or Micro8 Package•Pb−Free Packages are AvailableApplications •Computers •Embedded System •Battery Powered Equipment •Critical m P Power Supply MonitorPIN CONFIGURATIONRESET NCRESETMRV CCPFOPFIGND(Top View)Micro8MR RESETGNDPFIRESETNCPFO(Top View)See detailed ordering and shipping information in the package dimensions section on page 8 of this data sheet.ORDERING INFORMATIONV CCFigure 1. Representative Block DiagramRESETRESETPFO GNDMAXIMUM RATINGS (Note 1)RatingSymbol Value Unit Supply Voltage V CC 6.0V Output VoltageV out −0.3 to (V CC + 0.3)V Output Current (All Outputs)I out 20mA Input Current (V CC and GND)I in 20mA Thermal Resistance Junction−to−AirMicro8SOIC−8R q JA248187°C/WOperating Ambient Temperature T A −40 to +85°C Storage Temperature Range T stg −40 to +125°C LatchUp PerformancePositive NegativeI LATCHUP300280mA Maximum ratings are those values beyond which device damage can occur. Maximum ratings applied to the device are individual stress limit values (not normal operating conditions) and are not valid simultaneously. If these limits are exceeded, device functional operation is not implied,damage may occur and reliability may be affected.1.This device series contains ESD protection and exceeds the following tests: Human Body Model 2000 V per MIL−STD−883, Method 3015. Machine Model Method 200 V.2.The maximum package power dissipation limit must not be exceeded.P D +T J(max)*T AR q JAwith T J(max) = 150°CELECTRICAL CHARACTERISTICS (V CC = 1.0 V to 5.5 V, T A = −40°C to +85°C, unless otherwise noted. Typical values are at T A = 25°C, V CC = 3.3 V.)Characteristics Symbol Min Typ Max Unit Operating Voltage Range V CC 1.0− 5.5VSupply Current V CC = 3.3 V V CC = 5.5 V I CC−−12162228m AReset ThresholdMAX707T A = +25°CT A = −40°C to +85°C MAX708T A = +25°CT A = −40°C to +85°C MAX708TT A = +25°CT A = −40°C to +85°C MAX708ST A = +25°CT A = −40°C to +85°C MAX708RT A = +25°CT A = −40°C to +85°C V TH4.564.504.314.253.033.002.892.852.592.554.634.383.082.932.634.704.754.454.503.133.152.973.002.672.70VReset Threshold Hysteresis V HYS−0.01 V TH−mV V CC Falling Reset Delay (V CC = V TH + 0.2 V to V TH − 0.2 V)t PD−20−m S Reset Active Timeout Period t RP140200330mSRESET_L, RESET_H Output Low Voltage V CC w 1.0 V, I ol = 100 m AV CC u 2.7 V, I ol = 1.2 mAV CC u 4.5 V, I ol = 3.2 mA V ol−−−−−−0.30.30.3VRESET_L, RESET_H Output High Voltage V CC w 1.0 V, I oh = 50 m AV CC u 2.7 V, I oh = 500 m AV CC u 4.5 V, I oh = 800 m A V oh0.8 V CC0.8 V CC0.8 V CC−−−−−−VMR_L Pull−up Resistance R MRI50−−K W MR_L Pulse Width (V TH (max) t V CC t5.5 V)t MR 1.0−−m S MR_L Glitch Rejection (V TH (max) t V CC t5.5 V)−−0.1−m S MR_L High_level Input Threshold (V TH (max) t V CC t5.5 V)V IH0.7 V CC−−V MR_L Low_level Input Threshold (V TH (max) t V CC t5.5 V)V IL−−0.3 V CC V MR_L to RESET_L and RESET_H Output Delay(V TH (max) t V CC t5.5 V)t MD−0.2−m S PFI Input Threshold (V CC = 3.3 V, PFI Falling)− 1.20 1.25 1.3V PFI Input Current−−2500.01250nA PFI to PFO Delay (V CC = 3.3 V, V OVERDRIVE = 15 mV)−− 3.0−m SPFO_L Output Low Voltage V CC = 2.7 V, I ol = 1.2 mA V CC = 4.5 V, I ol = 3.2 mA V ol−−−−0.30.3VPFO_L Output High Voltage V CC = 2.7 V, I oh = 500 m A V CC = 4.5 V, I oh = 800 m A V oh0.8 V CC0.8 V CC−−−−VPIN DESCRIPTION (Pin No. with parentheses is for Micro8 package.)Pin No.Symbol Description1 (3)MRManual Reset Input. MR can be driven from TTL/CMOS logic or from a manual Reset switch. This input, when floating, is internally pulled up to V CC with 50 k W resistor.2 (4)V CCSupply Voltage: C = 100 nF is recommended as a bypass capacitor between V CC and GND.3 (5)GND Ground Reference4 (6)PFIPower Fail Voltage Monitor Input. When PFI is less than 1.25 V, PFO goes low. Connect PFI to GND or V CC whennot used.5 (7)PFO Power Fail Monitor Output. When PFI is less than 1.25 V, it goes low and sinks current. Otherwise, it remains high.6 (8)NC Non−connective Pin7 (1)RESET Active Low RESET can be triggered by V CC below the threshold level or by a low signal on MR. It remains low for 200 ms (typ.) after V CC rises above the reset threshold.8 (2)RESETActive high RESET output the inverse of RESET one.3.01.0I O U T , O U T P U T S I N K C U R R E N T (m A )Figure 4. MAX707/708 Series 2.93 V Reset Output Sink Current vs. Output Voltage Figure 5. MAX707/708 Series 2.93 V Reset Output Source Current vs. Input VoltageV in , INPUT VOLTAGE (V)I o u t , O U T P U T S O U R C E C U R R E N T (m A )2.00.01.06.02.03.04.05.02.51.50.52012I O U T , O U T P U T S O U R C E C U R R E N T (m A )0161814104862I O U T , O U T P U T S I N K C U R R E N T (m A )1201048620.5V out , OUTPUT VOLTAGE (V)2.01.01.52.53.0302515201050Figure 6. MAX707/708 Series 4.90 V Reset Output Sink Current vs. Output VoltageV out , OUTPUT VOLTAGE (V)Figure 7. MAX707/708 Series 4.90 V Reset Output Source Current vs. Input VoltageV in , INPUT VOLTAGE (V)I o u t , O U T P U T S I N K C U R R E N T (m A )0.04.03.02.01.05.00.01.06.02.03.04.05.0Figure 8. MAX707/708 Series 1.60 V DetectorThreshold Voltage vs. Temperature−5016152515950−25V D E T , D E T E C T O R T H R E S H O L D V O L T A G E (V O L T S )1585T A , AMBIENT TEMPERATURE (°C)160510016201610160015905075V D E T , D E T E C T O R T H R E S H O L D V O L T A G E (V O L T S )5000498049604880−50−25100492049000255075Figure 9. MAX707/708 Series 4.90 V DetectorThreshold Voltage vs. TemperatureT A , AMBIENT TEMPERATURE (°C)494030Figure 10. MAX707/708 Series 2.93 V DetectorThreshold Voltage vs. TemperatureT A , AMBIENT TEMPERATURE (°C)T P D , V C C , F A L L I N G R E S E T D E L A Y (m s )−40406020080−20203515250105V D E T , D E T E C T O R T H R E S H O L D V O L T A G E (V O L T S )31103100309030603120T A , AMBIENT TEMPERATURE (°C)−50−25100308030700255075Figure 11. MAX707/708 Series V CC FallingReset Delay vs. TemperatureAPPLICATIONS INFORMATIONMicroprocessor ResetTo generate a processor reset, the manual Reset input allows different reset sources. A pushbutton switch can beone of these. It is effectively debounced by the 1.0 m s minimum reset pulse width. As MR is TTL/CMOS logic compatible, it can be driven by an external logic line.V CCRESETFigure 12. RESET and MR TimingMRV CC Transient RejectionThe MAX707/708 provides accurate V CC monitoring and reset timing during power−up, power−down, and brownout/sag conditions, and rejects negative glitches on the power supply line. Figure 13 shows the maximum transient duration vs. maximum negative excursion(overdrive) for glitch rejection. For a given overdrive, the point of the curve is the maximum width of the glitch allowed before the device generates a reset signal. Transient immunity can be improved by adding a capacitor (100 nF for example) in close proximity to the V CC pin of the MAX707/708.300250150200100500Figure 13. Maximum Transient Duration vs.Overdrive for Glitch Rejection at 255CRESET COMPARATOR OVERDRIVE (mV)M A X I M U M T R A N S I E N T D U R A T I O N (m s )1090705030110130150V V CCDurationRESET Signal Integrity During Power−DownThe MAX707/708 RESET output is valid until V CC falls below 1.0 V . Then, the output becomes an open circuit and no longer sinks current. This means CMOS logic inputs of the m P will be floating at an undetermined voltage. Most digital systems are completely shutdown well above this voltage. However, in the case RESET must be maintained valid to V CC = 0 V , a pull down resistor must be connected from RESET to ground to discharge stray capacitances and hold the output low (Figure 14). This resistor value, though not critical, should be chosen large enough not to load RESET and small enough to pull it to ground. R = 100 k W will be suitable for most applications.Figure 14. Ensuring RESET Valid to V CC = 0 V Interfacing with m Ps with Bidirectional I/O PinsSome m Ps have bidirectional reset pins. If, for example,the RESET output is driven high and the m P wants to put it low, indeterminate logic level may result. This can be avoided by adding a 4.7 k W resistor in series with the output of the MAX707/708 (Figure 15). If there are other components in the system that require a reset signal, they should be buffered so as not to load the reset line. If the othercomponents are required to follow the reset I/O of the m P, the buffer should be connected as shown with the solid line.Figure 15. Interfacing to Bidirectional Reset I/O BUFFERED RESET TOOTHER SYSTEM COMPONENTSMonitoring Additional Supply LevelsWhen connecting a voltage divider to PFI and adjusting it properly, you can monitor a voltage different than the unregulated DC one. As shown in Figure 16, to increase noise immunity, hysteresis may be added to the power−fail comparator just by a resistor between PFO and PFI. Not to unbalance the potential divider network, R3 should be 10times the sum of the two resistors R1 and R2. If required, a capacitor between PFI and GND will reduce the sensitivity of the circuit to high−frequency noise on the line being monitored. The PFO output may be connected to MR input to generate a low level on the RESET when V CC _1 drops out of tolerance. Thus a RESET is generated when one of the two voltages is below its threshold level.Figure 16. Monitoring Additional Supply LevelsV CC_1V CC_2V CC_3PFOV CC_1V CC_20 V0 VV LV H V L +1.25)R1 ǒ1.25R2)1.25*V cc_2R3ǓV H +1.25 (1)R1 ǒR2)R3R2 R3Ǔ)V HYS +V H *V L +R1 V cc_2ORDERING INFORMATIONPackage Shipping†Device Marking Reset V CC Threshold(V)MAX707ESA−T S707 4.63SOIC−82500 Tape & Reel MAX707ESA−TG S707 4.63SOIC−82500 Tape & Reel(Pb−Free)MAX708ESA−T S708 4.38SOIC−82500 Tape & Reel2500 Tape & Reel MAX708ESA−TG S708 4.38SOIC−8(Pb−Free)MAX708RESA−T S708R 2.63SOIC−82500 Tape & Reel MAX708RESA−TG S708R 2.63SOIC−82500 Tape & Reel(Pb−Free)MAX708SESA−T S708S 2.93SOIC−82500 Tape & Reel MAX708SESA−TG S708S 2.93SOIC−82500 Tape & Reel(Pb−Free)MAX708TESA−T S708T 3.08SOIC−82500 Tape & Reel2500 Tape & Reel MAX708TESA−TG S708T 3.08SOIC−8(Pb−Free)MAX707CUA−T SAC 4.63Micro84000 Tape & Reel MAX707CUA−TG SAC 4.63Micro84000 Tape & Reel(Pb−Free)MAX708CUA−T SAD 4.38Micro84000 Tape & Reel4000 Tape & Reel MAX708CUA−TG SAD 4.38Micro8(Pb−Free)MAX708RCUA−T SAG 2.63Micro84000 Tape & Reel4000 Tape & Reel MAX708RCUA−TG SAG 2.63Micro8(Pb−Free)MAX708SCUA−T SAF 2.93Micro84000 Tape & Reel4000 Tape & Reel MAX708SCUA−TG SAF 2.93Micro8(Pb−Free)MAX708TCUA−T SAE 3.08Micro84000 Tape & Reel MAX708TCUA−TG SAE 3.08Micro84000 Tape & Reel(Pb−Free)†For information on tape and reel specifications,including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.PACKAGE DIMENSIONSMicro8CASE 846A−02ISSUE F*For additional information on our Pb−Free strategy and solderingdetails, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*8XDIM MIN MAX MIN MAX INCHESMILLIMETERS A 2.90 3.100.1140.122B 2.90 3.100.1140.122C −−− 1.10−−−0.043D 0.250.400.0100.016G 0.65 BSC 0.026 BSC H 0.050.150.0020.006J 0.130.230.0050.009K 4.75 5.050.1870.199L0.400.700.0160.028NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSION A DOES NOT INCLUDE MOLD FLASH,PROTRUSIONS OR GATE BURRS. MOLD FLASH,PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.4.DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010)PER SIDE.5.846A−01 OBSOLETE, NEW STANDARD 846A−02.PACKAGE DIMENSIONSSOIC−8CASE 751−07ISSUE AGǒmm inchesǓSCALE 6:1*For additional information on our Pb−Free strategy and solderingdetails, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.4.MAXIMUM MOLD PROTRUSION 0.15 (0.006)PER SIDE.5.DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBARPROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.6.751−01 THRU 751−06 ARE OBSOLETE. NEW STANDARD IS 751−07.DIM A MIN MAX MIN MAX INCHES4.805.000.1890.197MILLIMETERS B 3.80 4.000.1500.157C 1.35 1.750.0530.069D 0.330.510.0130.020G 1.27 BSC 0.050 BSC H 0.100.250.0040.010J 0.190.250.0070.010K 0.40 1.270.0160.050M 0 8 0 8 N 0.250.500.0100.020S5.806.200.2280.244YM0.25 (0.010)Z SXS____ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATIONMicro8 is a trademark of International Rectifier.。

max708中文手册

MAX708具有比较器手动复位输入两组复位电平输出的微处理器电源监控芯片概述MAX708 是一种微处理器电源监控芯片可同时输出高电平有效和低电平有效的复位信号复位信号可由VCC 电压手动复位输入或由独立的比较器触发独立的比较器可用于监视第二个电源信号为处理器提供电压跌落的预警功能这一功能是为器件发出复位信号前的正常关机向操作者发送警报或电源切换而考虑的MAX708 提供 SO-8 或 TSSOP-8 的表面封装形式有3种域值电平可供选择性能• RESET 信号/RESET 信号输出• 域值值为1.25V 用于电源失效或低电源警告的独立比较器 • 手动复位输入• 需要100 uA 的电源电流• 复位域值为 2.63V2.93V3.08 V• 在VCC = 1 V 时能提供有效的 RESET 信号应用• 电池供应的器件• 微处理器临界状态监控 • 控制器• 便携式工具 系统简图PMR V CCPFIGNDPFORESETRESETRESET INPUTINTERRUPTV CCRegulated DC supply (V CC )GNDPush-buttonSwitchUnregulated DC supplyMAX708定购信息型号 封装 名称 说明 温度范围MAX708 TSSOP8 极小型8引脚塑料(见尺寸图) 0 to 70 C MAX708 SO8 小型8引脚塑料(见尺寸图)0 to 70 C注意器件具有3种电压输出选项元件编号 域值电压(通常)MAX708R 2.63V MAX708S 2.93V MAX708T 3.08V 元件数字标记元件编号 标记MAX708R MAX708S MAX708T MAX708R MAX708S MAX708T 管脚定义23154678MR V CC GND PFIPFORESET RESET SO8NC 23154678MR V CCGNDPFI PFO RESET RESETTSSOP8NC管脚说明名称 功能/MR 手动复位输入低有效当 /MR 拉至0.6V 时触发一个复位脉冲未用时接至VCCVCC 电源输入 GND 在PFI 电源失效比较器输入未用时接至GND/PFO 电源失效比较器输出低有效当引脚PFI 上的电压低于1.25V 时/PFO 输出低电平拉电流未用时必须悬空 NC 未连接/RESET 低有效复位输出当VCC 低于域值电平或 /MR 保持为低时/RESET 输出低电平在复位条件结束后/RESET 信号将继续保持 200mS.RESET高有效复位输出当VCC 低于域值电平或 /MR 保持为低时RESET 输出高电平在复位条件结束后RESET 信号将继续保持 200mS.最大额定值符号 参数 最小值 最大值 单位 VCC 电源电压 0.3 6.0 V其余输入管脚电压(注1)0.3 VCC+0.3V V 输入电流电源或地 20 mA 输出电流所有引脚 20 mA VCC 管脚上的电压上升速率 100 V/uSPd 功率消耗 SO8 封装T AMB 70(注2)470 mW功率消耗T AMB 70(注3)mW T OPR 工作温度 40 +85 T STG 贮存温度 65 +160注1引脚 PFI 和 /MR 上的输入电压可超过限值但提供的电流须<10mA 注2在70以上时减少5.88mW/注3在70以上时减少4.1mW/直流电气特性注意T A T MIN至T MAX VCC V RST(MAX)0.07V至5.5V除非另外说明符号 参数 条件最小值 通常值 最大值 单位VCC 操作电压范围1.2 5.5 V VCC<3.6V 50 300I SUP 电源电流 VCC<5.5V 65 500 uAMAX708R 2.55 2.63 2.70MAX708S 2.85 2.93 3.00V RST 复位域值电平 MAX708T 3.00 3.08 3.15V 复位域值电平回滞 20 mVMAX708R: V CC = 3.0 VMAX708S/T V CC = 3.3 V 140 200 280 t RST 复位脉冲宽度(注1)MAX708R/S/T: V CC = 5.0 V 200mSV OH V RST(MAX)<V CC <3.6 V; I SOURCE = 500uA V CC x0.8 V OL V RST(MAX) <V CC <3.6 V; I SINK = 1.2mA 0.3 V OH 4.5 V <V CC <5.5 V ; I SOURCE = 800uA V CC-1.5 V OL 4.5 V <V CC <5.5 V ; I SINK = 3.2mA 0.4V OL /RESET 输出电压 V CC = 1.2 V ; I SINK = 100 uA 0.3V OH V RST(MAX)<V CC <3.6 V; I SOURCE = 500uA V CC x0.8 V OL V RST(MAX) <V CC <3.6 V; I SINK = 1.2mA 0.3V OH 4.5 V <V CC <5.5 V ; I SOURCE = 800uA V CC-1.5 V OL RESET 输出电压 4.5 V <V CC <5.5 V ; I SINK = 3.2mA 0.4V V RST(MAX) <V CC <3.6 V ; /MR = 0V 25 70 250/MR 上拉电流 4.5 V <V CC <5.5 V ; /MR = 0V 100 250 600 uAV RST(MAX) <V CC <3.6 V 150t MR /MR 脉冲宽度 4.5 V <V CC <5.5 V 500nSV IH V RST(MAX) <V CC <3.6 V 0.6 V IL V RST(MAX) <V CC <3.6 V V CC x0.7V IH 4.5 V <V CC <5.5 V 0.8 V IL /MR 输入域值 4.5 V <V CC <5.5 V 2.0V V RST(MAX) <V CC <3.6 V750 t MD /MR 至复位输出的延迟注14.5 V <V CC <5.5 V 250nS PFI 输入域值 PFI falling; MAX708R: V CC = 3.0 VMAX708S/T V CC = 3.3 V1.2 1.25 1.3 VPFI 输入电流 -25 0.01 +25 nA V OH V RST(MAX) <V CC <3.6V; I SOURCE = 500uA V CC x0.8 V OL V RST(MAX) <V CC <3.6 V; I SINK = 1.2mA 0.3V OH 4.5 V <V CC <5.5 V ; I SOURCE = 800uA V CC-1.5 V OL /PFO 输出电压 4.5 V <V CC <5.5 V ; I SINK = 3.2mA 0.4 V 注1输出 RESET 和 /RESET封装方式Cover Carrier ReelT apeGuard BarcodeBoxLabelTape DetailAssemblyBandTapeTape组装方式短语英汉对照英文短语译文Guard Band 包装带 Tape带芯Barcode Label 条形标签 Box底箱 Reel Assembly 转盘Tape Detail 带芯细节 Cover Tape 带芯覆膜Carrier Tape 带芯携带的信息。

Agilent Technologies 708-DS 溶出度仪 操作手册说明书

708-DS 溶出度仪操作手册声明© Agilent Technologies, Inc. 2017根据美国和国际版权法,未经 Agilent Technologies, Inc. 事先同意和书面许可,不得以任何形式或任何方式(包括存储为电子版、修改或翻译成外文)复制本手册的任何部分。

手册部件号70-9058版本修订版 F,2017 年 1 月Agilent Technologies, Inc.3501 Stevens Creek Blvd.Santa Clara, CA 95052 USA 担保本文档内容按“原样”提供,在将来的版本中如有更改,恕不另行通知。

此外,在适用法律允许的最大范围内,Agilent 对本手册以及其中包含的任何信息不作任何明示或暗示担保,包括但不限于适销性和针对某一特殊用途的适用性的暗示担保。

对于因提供、使用或执行本文档或其中所含任何信息而产生的错误,或造成的偶然或必然的损失,Agilent 不承担任何责任。

如果Agilent 与用户签订了单独的书面协议,其中涉及本文档内容的担保条款与这些条款存在冲突,则以协议中的担保条款为准。

技术许可本文档中所述的硬件和/或软件依据许可而提供,且只能根据此类许可的条款进行使用或复制。

受限权利说明美国政府受限权利。

授予联邦政府的软件和技术数据权利仅包括通常提供给最终用户的那些权利。

Agilent 根据 FAR12.211.0(技术数据)和 12.212(计算机软件)和(对于国防部)DFARS252.227-7015(技术数据-商品)以及DFARS 227.7202-3(商业计算机软件或计算机软件文档中的权利)来提供软件和技术数据方面的此常规商业许可。

安全声明小心声明表示危险。

提醒您注意某个操作步骤、某项操作或类似问题,如果执行不当或未遵照提示操作,可能会损坏产品或丢失重要数据。

在完全理解并符合所指出的条件前,不要忽视小心声明而继续操作。

708硅橡胶固化时间

708硅橡胶固化时间708硅橡胶是一种常用的硅橡胶材料,广泛应用于电子、通讯、航空航天、汽车等领域。

在使用过程中,其固化时间是一个非常重要的参数,直接影响着产品的质量和生产效率。

本文将从以下几个方面详细介绍708硅橡胶固化时间的相关知识。

一、708硅橡胶的基本性能708硅橡胶是一种双组份液态硅橡胶,由A组分和B组分组成。

A组分为硅酮基液体,B组分为氢氧基液体。

两者混合后反应生成交联结构,形成固态硅橡胶。

该材料具有优异的耐高低温性能、耐氧化性和耐腐蚀性能,同时还具有良好的电绝缘性能和机械强度。

二、影响708硅橡胶固化时间的因素1. 温度温度是影响708硅橡胶固化时间最主要的因素之一。

一般来说,温度越高,反应速率越快,固化时间也就越短;反之,温度越低,反应速率越慢,固化时间也就越长。

708硅橡胶的固化时间与温度之间的关系可以用Arrhenius公式表示:ln(t2/t1) = E/R(1/T1 - 1/T2),其中t1和t2分别表示在温度T1和T2下的固化时间,E为活化能,R为气体常数。

2. 混合比例708硅橡胶是由A组分和B组分按一定比例混合而成的。

混合比例不当会影响到反应速率和固化时间。

一般来说,A组分与B组分的质量比为10:1时反应最快,固化时间最短;当A组分与B组分的质量比为9:1或11:1时,反应速率会变慢,固化时间也会相应延长。

3. 活化剂在708硅橡胶中添加一定量的活化剂可以加快反应速率,缩短固化时间。

常用的活化剂有二甲基苯基羰基氧化锡(DMTO)和二甲基甲酰胺(DMF)。

活性剂的加入量需要根据具体情况进行调整,在保证反应速率的同时避免对材料性能产生不良影响。

三、708硅橡胶固化时间的测试方法1. 手感法手感法是一种简单易行的测试方法,通常用于现场快速检测。

具体方法是将混合好的硅橡胶涂抹在手背上,观察其表面是否已经干燥。

如果表面已经形成膜状物,则说明固化已经完成;反之,则需要继续等待。

708轴承的三大尺寸

708轴承的三大尺寸概述轴承是机械设备中常用的零部件之一,用于支撑旋转轴的运动,并减少摩擦。

708轴承是一种常见的轴承类型,它具有特定的尺寸规格,本文将详细介绍708轴承的三大尺寸。

1. 内径(ID)轴承的内径是指轴承内部圆筒的直径。

在708轴承中,内径通常是一个固定的尺寸,用于安装在轴上。

内径的尺寸决定了轴承与轴的配合是否紧密,过大或过小都会影响轴承的运行效果。

708轴承的内径通常为8毫米(mm),这是其最常见的尺寸。

然而,根据不同的使用需求,708轴承的内径也可以有其他尺寸的选择。

2. 外径(OD)轴承的外径是指轴承外部圆筒的直径。

外径的尺寸决定了轴承与外部零件的配合是否紧密,过大或过小都会影响轴承的安装和使用。

708轴承的外径通常为22毫米(mm),这是其最常见的尺寸。

然而,根据不同的使用需求,708轴承的外径也可以有其他尺寸的选择。

3. 宽度(W)轴承的宽度是指轴承内部圆筒的宽度,也称为轴承的厚度。

宽度的尺寸决定了轴承的承载能力和稳定性,过大或过小都会影响轴承的使用寿命和性能。

708轴承的宽度通常为7毫米(mm),这是其最常见的尺寸。

然而,根据不同的使用需求,708轴承的宽度也可以有其他尺寸的选择。

708轴承的尺寸组合708轴承的三大尺寸——内径、外径和宽度——共同决定了轴承的整体尺寸。

一般来说,708轴承的尺寸组合可以表示为“内径× 外径× 宽度”,例如8mm ×22mm × 7mm。

不同的尺寸组合可以满足不同的机械设备需求。

较小尺寸的708轴承常用于精密仪器和小型机械设备,而较大尺寸的708轴承常用于大型工业设备。

708轴承的应用708轴承广泛应用于各种机械设备中,包括:1.汽车:用于发动机、变速器和转向系统等。

2.电动工具:用于电动钻、电动锤等。

3.纺织机械:用于纺织机、织布机等。

4.电机:用于电动机、发电机等。

5.工业设备:用于机床、泵、风机等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

BD707/709/711BD708/712COMPLEMENTARY SILICON POWER TRANSISTORSsCOMPLEMENTARY PNP -NPN DEVICESAPPLICATIONs LINEAR AND SWITCHING INDUSTRIAL EQUIPMENT DESCRIPTIONThe BD707,BD709and BD711are silicon Epitaxial-Base NPN power transistors in Jedec TO-220plastic package.They are intented for use in power linear and switching applications.The BD707and BD711complementary PNP types are BD708and BD712respectively.®INTERNAL SCHEMATIC DIAGRAMSeptember 1999123TO-220ABSOLUTE MAXIMUM RATINGSSymbolParameterValue UnitNPN BD707BD709BD711PNPBD708BD712V CBO Collector-Base Voltage (I E =0)6080100V V CER Collector-Emitter Voltage (V BE =0)6080100V V CEO Collector-Emitter Voltage (I B =0)6080100V V EBO Emitter-Base Voltage (I C =0)5V I C Collector Current12A I CM Collector Peak Current 18A I B Base Current5A P tot Total Dissipation at T c ≤25o C 75W T s tg Storage Temperature-65to 150o C T jMax.Operating Junction Temperature150o CFor PNP types voltage and current values are negative1/6THERMAL DATAR thj-case R thj-case Thermal Resistance Junction-case MaxThermal Resistance Junction-ambient Max1.6770o C/Wo C/WELECTRICAL CHARACTERISTICS(T case=25o C unless otherwise specified)Symbol Parameter Test Conditions Min.Typ.Max.UnitI CBO Collector Cut-offCurrent(I E=0)for BD707/708V CB=60Vfor BD709V CB=80Vfor BD711/712V CB=100VT case=150o Cfor BD707/708V CB=60Vfor BD709V CB=80Vfor BD711/712V CB=100V100100100111µAµAµAmAmAmAI CEO Collector Cut-offCurrent(I B=0)for BD707/708V CE=30Vfor BD709V CE=40Vfor BD711/712V CE=50V100100100mAmAmAI EBO Emitter Cut-off Current(I C=0)V EB=5V1mAV CEO(s us)∗Collector-EmitterSustaining Voltage(I B=0)I C=100mAfor BD707/708for BD709for BD711/7126080100VVVV CE(sat)∗Collector-EmitterSaturation VoltageI C=4A I B=0.4A1V V CEK∗Knee Voltage I C=3A I B=**0.4V V BE∗Base-Emitter Voltage I C=4A V CE=4V 1.5Vh F E∗DC Current Gain I C=0.5A V CE=2VI C=2A V CE=2Vfor BD707/708for BD709I C=4A V CE=4VI C=10A V CE=4Vfor BD707/708for BD709for BD711/7124030301551201088400150f T Transition frequency I C=300mA V CE=3V3MHz ∗ Pulsed:Pulse duration=300µs,duty cycle1.5%**Value for which I C=3.3A at V CE=2V.For PNP types voltage and current values are negative.BD707/708/709/711/7122/6Safe Operating AreasDC Current Gain(NPN type)DC Transconductance(NPNtype)Derating CurveDC Current Gain(PNP type)DC Transconductance(PNPtype)BD707/708/709/711/7123/6BD707/708/709/711/712Collector-Emitter Saturation Voltage(NPN type)Collector-Emitter Saturation Voltage(PNP type) Base-Emitter Saturation Voltage(NPN type)Base-Emitter Saturation Voltage(PNP type) Transition Frequency(NPN type)Transition Frequency(PNP type)4/6DIM.mminch MIN.TYP.MAX.MIN.TYP.MAX.A 4.40 4.600.1730.181C 1.23 1.320.0480.051D 2.402.720.0940.107D1 1.270.050E 0.490.700.0190.027F 0.610.880.0240.034F1 1.14 1.700.0440.067F2 1.14 1.700.0440.067G 4.95 5.150.1940.203G1 2.4 2.70.0940.106H210.010.400.3930.409L216.40.645L413.014.00.5110.551L5 2.65 2.950.1040.116L615.2515.750.6000.620L7 6.2 6.60.2440.260L9 3.5 3.930.1370.154DIA.3.75 3.850.1470.151P011CTO-220MECHANICAL DATABD707/708/709/711/7125/6BD707/708/709/711/712Information furnished is believed to be accurate and reliable.However,STMicroelectronics assumes no responsibility for the consequence s of use of such information nor for any infringement of patents or other rights of third parties which may result from its use.No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics.Specification mentioned in this publication are subject to change without notice.This publication supersedes and replaces all information previously supplied.STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.The ST logo is a trademark of STMicroelectronics©1999STMicroelectronics–Printed in Italy–All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia-Brazil-China-Finland-France-Germany-Hong Kong-India-Italy-Japan-Malaysia-Malta-Morocco-Singapore-Spain-Sweden-Switzerland-United Kingdom-U.S.A..6/6。