应变硅技术在纳米CMOS中的应用

cmos工艺中材料的功能

cmos工艺中材料的功能【最新版】目录1.CMOS 工艺简介2.CMOS 材料在集成电路中的功能3.CMOS 材料的种类及其特点4.CMOS 材料的发展趋势正文一、CMOS 工艺简介CMOS(互补金属氧化物半导体)是一种集成电路技术,广泛应用于现代电子设备中。

与传统的硅晶体管相比,CMOS 技术具有低功耗、高噪声抑制能力、高集成度等优点。

因此,CMOS 技术在半导体领域得到了广泛应用,成为当代集成电路的主流技术。

二、CMOS 材料在集成电路中的功能在 CMOS 工艺中,材料扮演着至关重要的角色。

它们可以决定电路的性能、稳定性和可靠性。

CMOS 材料主要包括以下几类:1.硅(Si):作为集成电路的基础材料,硅具有优良的半导体性能,被广泛应用于 CMOS 工艺。

2.氧化物:在 CMOS 工艺中,氧化物主要用于制作栅极绝缘层,以实现良好的隔离效果。

常见的氧化物材料有二氧化硅(SiO2)和氮氧化物(N Oxide,NOx)。

3.金属导电材料:金属导电材料主要用于制作电路中的导线、接触点和金属栅极。

在 CMOS 工艺中,常用的金属材料包括铝(Al)、铜(Cu)和钨(W)。

4.掺杂剂:掺杂剂用于改变硅的导电性质,以实现 n 型和 p 型半导体。

常见的掺杂剂有硼(B)、磷(P)和砷(As)。

5.绝缘层:在 CMOS 工艺中,绝缘层用于隔离不同区域的半导体材料,防止电流泄露。

常见的绝缘层材料有硅氮化物(Si3N4)和氟化硅(SiF4)。

三、CMOS 材料的种类及其特点1.硅(Si):作为基础材料,硅具有优良的半导体性能,但随着制程工艺的不断缩小,硅材料的局限性逐渐显现,如电子迁移率降低、漏电流增加等。

2.氧化物:二氧化硅具有良好的绝缘性能,但随着制程工艺的缩小,其厚度也越来越薄,可能导致泄漏电流增加。

氮氧化物具有较高的介电常数,可减小栅极绝缘层的厚度,提高集成度,但制作工艺相对复杂。

3.金属导电材料:铝具有较低的电阻率和良好的导电性能,但容易与氧化物发生反应,影响电路稳定性。

应变硅技术(原理部分)

英特尔Process Architecture and Integration经理Mark

Bohr曾经非常形象地描述:“只需将硅原子拉长1%就可以

将MOS晶体管电流速度提高10%~20%,而应变硅的生产

成本只增加2%”。

据报道,利用现有硅生产线制造出的应变硅 MOSFET与同尺寸体Si MOSFET相比,功耗减小三分之 一,速度提高30%,特征频率提高50%以上,功耗延迟 积仅为后者的1/5到1/6,器件的封装密度提高50%。

A

mc 0.26m0

12

对于生长在(001)晶面的应变硅MOSFET来说, 由于张应力的作用,原有的六重简并能谷(Δ6)的 简并被解除,分为两组:两个能量降低的二重简并 能谷(Δ2)沿与沟道垂直的轴向;四个能量升高的 四重简并能谷(Δ4),沿与沟道平行的轴向。低能 谷与高能谷之间能量差的经验值为0.6xeV(x为锗含 量)。

用于P型MOSFET。

A

9

异质结能带结构

第二类能带调整:体Si0.7Ge 0.3 (弛豫)上的应变Si

应变Si与弛豫SiGe层相比,既有大的导带突变量,又有大

的价带突变量,电子势阱和空穴势阱处在不同的层中,导

带突变量处于应变硅中,价带突变量集中于锗硅层,形成

Ⅱ型量子阱。Ⅱ型量子阱由于导带和价带的能带的突变量

都比较大,电子和空穴的迁移率都有所增强,因而应变

Si/SiGe在CMOS工艺中既可做AN型也可做P型器件。

10

应变硅MOSFET迁移率的增强机理

迁移率增强的物理解释:

电子迁移率:

n

q n

m

n

空穴迁移率: p

q p

m

p

其中τ是载流子运动的平均自由时间,它是散射几率p的倒 数,m*为运动方向上的有效质量。应力增强载流子迁移 率主要通过两个途径:减小有效质量,降低散射几率。

新型材料在传感器上的应用

新型材料在传感器上的应用随着科技的飞速发展,对传感器的要求越来越高,而新型材料的性能逐渐被人们所认识和开发应用,新型材料的应用将极大地推动传感器技术的发展。

一、新型材料在传感器上的应用1.纳米材料纳米材料是指粒径在1-100纳米之间的材料,纳米材料具有巨大的比表面积、量子尺寸效应和量子隧穿效应,具有一系列特殊的物理和化学性质。

由于其唯一的性质,纳米材料常用于传感器中的高灵敏度检测,如气体传感器、生物传感器等。

2.载体材料载体材料是指能够载体传感器所需物质的一类材料。

传统的载体材料为硅胶、氧化锌等,但由于其具有一定的毒性和不良影响,研究者开始寻找新的载体材料。

现在,氧化铝、碳纳米管等新型材料因其独特的物理和化学性质成为载体材料研究的热点,因为这些新型材料具有良好的生物适应性和生物相容性,并且不会对环境产生污染。

3.共价有机框架材料(COFs)共价有机框架材料是一种具有多孔性的新型材料,由于其高孔隙度和低密度,是天然气的理想的分离材料。

通过将各种配位体连接起来形成纳米孔道,在孔道内进行气体分子吸附和脱附,以达到理想的分离效果。

所以COFs在传感器中的应用,已经逐渐成为了一个非常重要的方向。

二、新型材料的优势和应用前景1.优势新材料具有优异的物理和化学性质,具有更高的灵敏度和选择性,能够满足更高的检测要求。

此外,新型材料的生物相容性和环境适应性更好,使得传感器得以更为广泛地应用于生物医学和环境监测等领域,具有很高的应用前景。

2.应用前景随着技术的不断进步,新型材料将会在未来更广泛地应用于传感器领域。

例如,在医学领域中,使用新型材料的传感器可以有效地监测人体健康状况,实现出色的生命检测效果。

同时,在环境领域中,新型材料的传感器可以广泛地应用于大气污染、水质监测、大气质量检测等方面等。

而且,配合物联网技术等前沿技术,还可以有效地解决一系列复杂的问题。

三、结论新型材料在传感器上的应用开创了一种崭新的传感器研究和应用领域,其优异的物理和化学性质,使传感器能够更好地满足高精度检测的要求。

应变硅技术在纳米CMOS中的应用

物 理 、 工 艺 的 限 制 。 为 了使 集 成 度 继 续 延 续 摩 尔

l 引 言

随 着 微 纳 技 术 的 发 展 ,CMOS 艺 已 经进 入 工 了 ( )深 亚 微 米 阶 段 ,晶体 管 的特 征 尺 寸 已达 超 纳 米 级 。S 0, 为栅 介 质 , 厚 度 已 降低 到物 理 极 i 作 限 ( 1 m) ,使 MOS E 性 能 恶化 ,如 关态 漏 约 n F T

(. 1中国电子 科技 集团公司第5 研究所 ,江苏 无锡 2 4 3 ; 8 10 5 2 南通航运职业技术 学院船 舶与海洋工程系 ,江苏 南通 2 62 ) . 2有 迁移率 高、 能带结构 可调的优 点 ,且 与传 统的体硅 工 艺相 兼容,在C S MO

工 艺中得到广泛地应 用,尤其是MOS 器件 的尺寸进入纳米 节点 。文章综述 了应 变硅 技术对载流子迁 移率影响 的机理 ,并从 全局应 变和局部应 变两个 方 面介 绍 了应 变硅 在C MOS 器件 中的应 用。同时 , 将 多种应 变硅技术 整合在一起提 升MOS 器件的性 能是 未来发展 的趋 势。 关键词 :应 变硅 ;C MO ;全局应 变;局部应 变 S

中图分类号 :T 7 2 P0

文献标识码 :A

文章编号 :18 -0 0 (0 2 1 0 10 6 117 2 1 )0 — 3 -6 0

TheApp i a i n o t a ne ii o n t eNa lc to fS r i d S l n i h no CM OS Te hnis c c c

L U G oz u, AOF i WA h -e, I L I u :h Y e , NG S uj LN i i ( .hn l t nc cn lg ru op rt n . ee r s tt W x 10 5 C ia 1 i E e r i T h ooyG op C roai 5 R sac I tu , ui 4 3 , hn ; C a co se o No 8 hn i e 2

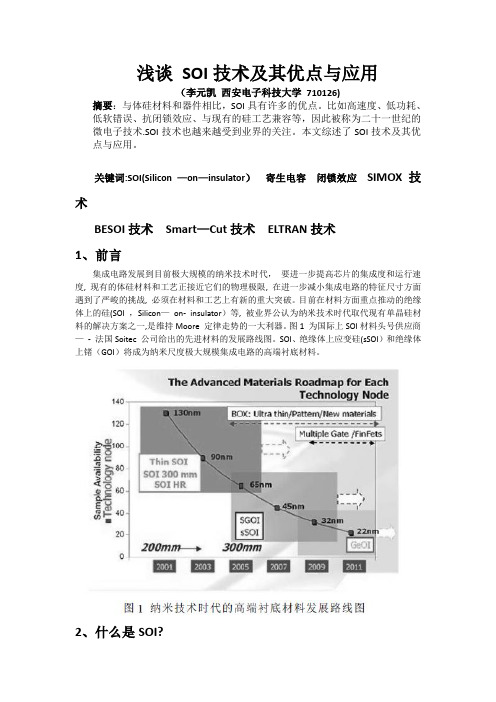

浅谈-SOI技术及其优点与应用分析

浅谈SOI技术及其优点与应用(李元凯西安电子科技大学710126)摘要:与体硅材料和器件相比,SOI具有许多的优点。

比如高速度、低功耗、低软错误、抗闭锁效应、与现有的硅工艺兼容等,因此被称为二十一世纪的微电子技术.SOI技术也越来越受到业界的关注。

本文综述了SOI技术及其优点与应用。

关键词:SOI(Silicon —on—insulator)寄生电容闭锁效应SIMOX技术BESOI技术Smart—Cut技术ELTRAN技术1、前言集成电路发展到目前极大规模的纳米技术时代,要进一步提高芯片的集成度和运行速度, 现有的体硅材料和工艺正接近它们的物理极限, 在进一步减小集成电路的特征尺寸方面遇到了严峻的挑战, 必须在材料和工艺上有新的重大突破。

目前在材料方面重点推动的绝缘体上的硅(SOI ,Silicon—on- insulator)等, 被业界公认为纳米技术时代取代现有单晶硅材料的解决方案之一,是维持Moore 定律走势的一大利器。

图1 为国际上SOI材料头号供应商—- 法国Soitec 公司给出的先进材料的发展路线图。

SOI、绝缘体上应变硅(sSOI)和绝缘体上锗(GOI)将成为纳米尺度极大规模集成电路的高端衬底材料。

2、什么是SOI?SOI(Silicon-On-Insulator)指的是绝缘衬底上的硅。

SOI技术被国际上公认为“二十一世纪的硅基础电路技术”。

它是一种在硅材料与硅集成电路的巨大基础上出现的、有独特优势的、能突破硅材料与硅集成电路限制的新技术。

SOI的基本结构如图2所示:图2:(a)绝缘体作为衬底(b)绝缘薄膜位于绝缘体上3、SOI技术的优点SOI是一种具有独特的“Si/ 绝缘层/Si”三层结构的新型硅基半导体材料.它通过绝缘埋层( 通常为SiO2) 实现了器件和衬底的全介质隔离,在器件性能上具有以下优点:1) 减小了寄生电容, 提高了运行速度。

与体硅材料相比,SOI 器件的运行速度提高了20- 35%;2)具有更低的功耗。

双轴应变Si_应变SiGeCMOS关键技术研究

题(中、英文)作者姓指导教师姓名、学科门代号 分类号学号 密级10701 1040421990 TN4公 开西安电子科技大学学位论文独创性(或创新性)声明秉承学校严谨的学风和优良的科学道德,本人声明所呈交的论文是我个人在导师指导下进行的研究工作及取得的研究成果。

尽我所知,除了文中特别加以标注和致谢中所罗列的内容以外,论文中不包含其他人已经发表或撰写过的研究成果;也不包含为获得西安电子科技大学或其它教育机构的学位或证书而使用过的材料。

与我一同工作的同志对本研究所做的任何贡献均已在论文中做了明确的说明并表示了谢意。

申请学位论文与资料若有不实之处,本人承担一切的法律责任。

本人签名:日期西安电子科技大学关于论文使用授权的说明本人完全了解西安电子科技大学有关保留和使用学位论文的规定,即:研究生在校攻读学位期间论文工作的知识产权单位属西安电子科技大学。

学校有权保留送交论文的复印件,允许查阅和借阅论文;学校可以公布论文的全部或部分内容,可以允许采用影印、缩印或其它复制手段保存论文。

同时本人保证,毕业后结合学位论文研究课题再撰写的文章一律署名单位为西安电子科技大学。

(保密的论文在解密后遵守此规定)本学位论文属于保密,在年解密后适用本授权书。

本人签名:日期导师签名:日期摘要摘要随着CMOS器件的特征尺寸进入纳米级,传统的CMOS越来越难以按照原来速度等比例缩小,因此探索新型器件材料、研究新型器件结构已经成为提高集成电路性能的必然选择。

应变Si/应变SiGe具有载流子迁移率高、带隙可调等优点,而且与目前已经很成熟的Si工艺相兼容,因此是延续摩尔定律最有潜力的新技术。

本文通过理论分析和仿真重点研究双轴应变Si/应变SiGe CMOS关键理论与技术,主要包括双轴应变Si、应变SiGe材料基本物理属性以及双轴应变MOS器件物理模型及其电学特性。

建立双轴应变MOS的阈值电压、I-V特性等关键电学参数模型并研究了双轴应变MOS器件的几何结构和物理参数与阈值电压的理论关系。

应变硅工艺技术

应变硅工艺技术应变硅工艺技术(strained silicon process technology)是一种在硅基材料上引入应变的先进制程技术。

应变硅工艺技术通过拉伸或压缩硅基材料,使其晶格略有扭曲,从而改变硅材料的电子运动特性,提高晶体管的性能。

在集成电路制造中,应变硅技术已被广泛采用,以提高性能和节约能源。

下面将对应变硅工艺技术进行详细介绍。

应变硅工艺技术最初是由IBM在20世纪80年代首次提出的。

该技术的基本原理是通过在硅基材料上施加应力,改变硅晶体中的键长和键角,从而改变晶体管中的载流子有效质量和迁移率。

在应变硅技术中,常用的方法包括晶格匹配、硅嵌二硅(Silicon on Insulator, SOI)、嵌入式硅锗(Embedded Silicon Germanium, e-SiGe)等。

晶格匹配是最基本的应变硅工艺技术,通过在硅基材料上生长外延层,改变硅晶体的格位常数,从而引入应变。

例如,当在硅基材料上生长纯Ge外延层时,由于硅和锗之间存在晶格的不匹配,会导致硅晶体产生拉伸应变。

这种拉伸应变会改变硅晶体的一些物理特性,如载流子迁移率和能隙,进而提高晶体管的性能。

硅嵌二硅技术是一种在硅基材料上生长氧化层(SiO2)后再生长一层薄的硅层(Si),从而形成硅嵌二硅结构。

硅嵌二硅层和硅基材料之间的晶格匹配度较低,从而引入了压缩应变。

压缩应变可以提高硅晶体的迁移率,从而提高晶体管的效能。

嵌入式硅锗技术是一种在硅晶体中嵌入硅锗合金层的方法,通过控制硅锗的组分和厚度,可以引入拉伸或压缩应变。

与硅嵌二硅技术相比,硅锗合金层的应变效应更大,可以进一步提高晶体管的性能。

应变硅工艺技术的应用主要集中在高性能微处理器和存储器上。

通过改变硅材料的应变状态,可以调节电子在晶体管中的传输速度和能隙,从而提高芯片的性能和能效。

例如,在高速微处理器中,采用应变硅技术可以增加晶体管的开关速度、降低漏电流、提高功耗效率。

硅基应变CMOS研究与设计

硅基应变CMOS研究与设计硅基应变CMOS研究与设计摘要:本文主要探讨了硅基应变互补金属氧化物半导体(CMOS)在集成电路领域的研究与设计。

首先介绍了应变技术对CMOS器件性能的影响,包括传统的硅衬底应变技术和新兴的晶格匹配外延(GAS),并详细介绍了应变技术的原理。

然后,对硅基应变CMOS器件在逻辑和存储方面的研究进展进行了综述。

最后,讨论了硅基应变CMOS器件的设计策略,并展望了其未来发展的方向。

关键词:硅基应变CMOS、传统硅衬底应变技术、晶格匹配外延、逻辑器件、存储器件、设计策略、未来发展1. 引言硅基应变互补金属氧化物半导体(CMOS)技术是当今集成电路领域的重要研究方向之一。

随着微电子器件尺寸逐渐缩小,传统的CMOS技术面临着电子迁移率下降等问题。

应变技术作为一种有效的解决方案,可以通过引入应变效应,提高CMOS器件的性能。

本文将重点探讨硅基应变CMOS研究与设计的最新进展。

2. 应变技术的原理硅衬底应变技术是一种较为成熟的应变技术,通过在衬底上引入压应变或拉应变,可以提高电子迁移率,提高器件性能。

晶格匹配外延是一种新兴的应变技术,通过在晶格中引入外延层,改变晶体结构,实现应变效应。

应变技术的原理是通过改变晶格常数,影响电子轨道结构,从而改变电子迁移率和载流子浓度。

3. 硅基应变CMOS的研究进展硅基应变CMOS在逻辑和存储方面都取得了重要的研究进展。

在逻辑器件方面,应变技术可以提高开关速度、减小开关能耗。

在存储器件方面,应变技术可以提高储存密度和读取速度。

研究表明,硅基应变CMOS技术可以显著提高器件性能,适用于各种集成电路应用。

4. 硅基应变CMOS器件的设计策略在硅基应变CMOS器件的设计中,需要考虑的因素包括器件结构、压应变和拉应变的比例、外延层材料的选择等。

器件结构的合理设计可以充分利用应变效应,提高器件性能。

压应变和拉应变的比例需要根据具体应用场景进行优化,以兼顾不同性能指标。

集成电路制造工艺-应变硅技术

高速化是集成芯片制造的重要技术指标,它可通过减小集成芯片的尺 寸提高工作速度,也可通过其它措施提高工作速度,如:提高沟道载流子 的迁移率,其中应变硅技术是应用广泛的技术手段。据报道,采用应变硅 技术的MOSFET与同尺寸的体Si MOSFET相比,功耗减少三分之一,速度 提高30%,特征频率提高50%以上,器件的封装密度提高50%。

第一模块

应变硅技术简介

干法刻蚀类型及特点

应变硅技术

应变硅技术是指通过应变材料产生应力,并把应力引

1

向器件的沟道,改变沟道中硅材料的导带或价带的能带结构,

从而减小能带谷内、谷间的散射率以及载流子在沟道方向上

2

的有效质量,达到提高载流子迁移率和器件工作速度的目的。

应变硅技术简介 应力的分类

应力可分为张应力和压应力,它们对电子和空穴迁移率的影响不同。

双轴应变

单轴应变

应变-弛豫缓冲层结构应变结构

源漏端嵌入应变材料技术

绝缘层上应变结构

应力记忆技术

1

......

接触刻蚀阻挡层应变技术

浅槽隔离技术

2

......

源漏端嵌入应变材料技术是用应变材料做MOSFET的源漏端,如用SiGe和SiC分别作pMOS 和nMOS的源漏材料。

应变硅技术简介 SiGe应变力的产生

NW

PW

Si-sub

1

NW

PW

2

Si-sub

源漏嵌入SiC和SiGe应变技术

源漏嵌入SiC和SiGe制备CMOS工艺过程

4. 选择性刻蚀Si衬底,在源漏区的位置形成 凹槽。

5. 通过循环多次CVD淀积和多次湿法刻蚀 ,在nMOS的源漏区凹槽位置选择性地外延 生长单晶态的SiC薄膜,同时进行磷掺杂, 形成n型的SiC源漏区。

Intel晶元制造工艺

Intel 65nm工艺实现与45nm工艺预览作者濮元恺 2006年8月一, 工艺的提升带来了什么那些说摩尔定律“脑死亡”的人应该清醒的了,虽然我自己也曾对摩尔定律的未来抱有很大的怀疑和迷茫,但Intel正用实际行动一次次证明自己。

high-k方面的突破,应变硅技术上升级,晶体管结构上的创新……一个个激动人心的技术,印证了Intel在半导体制造技术的足迹。

下面将结合最近收集到的材料,和大家一起了解Intel的65nm与未来的45nm工艺。

文中出现的技术词汇不单独注解,而是在原文里整体说明,希望本文能给硬件技术爱好者在晋级道路上提供一些帮助。

1, Intel的全盘计划1.jpg这张图片就是Intel的CPU整体计划,它是一项粗略的计划。

P1262是我们熟悉的采用90nm制造的Pentium 4处理器,第一批产品在2003年末出厂,典型代表是Pentium 4 Prescott。

P1262延续了上一代Pentium 4的NetBrust(网络爆发)架构,在频率方面疯狂飙升,而且90nm工艺内有一些问题没有很好地解决。

P1262计划预期达到的频率是4.0GHz,实际最后一款产品止步于3.8 GHz。

P1264是我们正在经历的时代,周期同样是2年。

我们熟悉的产品是Core微架构的Conroe处理器,采用65nm工艺制造,功耗控制表现优秀,性能强大。

P1266是未来45nm工艺制造的处理器,它将从2007年持续到2009年,产品的名称和型号我们还不知。

然后由32nm工艺的P1268接替它继续实现摩尔定律。

P1264和P1266正是我们下面要说明的计划,因为它们使用了65nm与45nm工艺,这两款工艺的实现对Intel非常重要,Intel 借助它们证实了自己在芯片制造界的领先地位,同时成功地延续着摩尔定律,也同时突破了很多技术壁垒。

2. 新工艺带来了什么a、更高的性能我们在这里说的65nm、45nm是指每一个晶体管的大小,晶体管越小,单个芯片能容纳的晶体管也越多,性能由此得到提升。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

应变硅技术在纳米CMOS中的应用刘国柱;姚飞;王树杰;林丽【摘要】应变硅技术具有迁移率高、能带结构可调的优点,且与传统的体硅工艺相兼容,在CMOS工艺中得到广泛地应用,尤其是MOS件的尺寸进入纳米节点。

文章综述了应变硅技术对载流子迁移率影响的机理,并从全局应变和局部应变两个方面介绍了应变硅在CMOS器件中的应用。

同时,将多种应变硅技术整合在一起提升MOS器件的性能是未来发展的趋势。

%Strained silicon technology, which provided with merits of high mobility, modifiable band-gap, compatible with conventional sub-silicon technics, was widely used in CMOS technics, and especially in the nano-meter node CMOS devices. In this text, the principle of carrier mobility ,which influenced by strain,was Simply summarized, and the application of Global strain and Local strain in the nano CMOS technics was introduced. Meanwhile,multi-strain technics would become the trend of improvement of the nano CMOS devices'performance in the future.【期刊名称】《电子与封装》【年(卷),期】2012(012)001【总页数】6页(P31-36)【关键词】应变硅;CMOS;全局应变;局部应变【作者】刘国柱;姚飞;王树杰;林丽【作者单位】中国电子科技集团公司第58研究所,江苏无锡214035;中国电子科技集团公司第58研究所,江苏无锡214035;南通航运职业技术学院船舶与海洋工程系,江苏南通226026;中国电子科技集团公司第58研究所,江苏无锡214035【正文语种】中文【中图分类】TP702随着微纳技术的发展,CMOS工艺已经进入了(超)深亚微米阶段,晶体管的特征尺寸已达纳米级。

SiO2作为栅介质,厚度已降低到物理极限(约1nm),使MOSFET性能恶化,如关态漏电、功耗密度增大、迁移率退化、短沟道效应、热载流子效应等。

因此,通过等比例缩小的方法提高当前主流硅CMOS器件的性能,受到越来越多物理、工艺的限制。

为了使集成度继续延续摩尔定律的发展速度,必须开发与硅工艺兼容的新材料、新结构和新性质,如SOI技术、应变工程技术(strained engineering)、浅结工程技术(shallow junction engineering)、低接触电阻及多层内连技术(multilayer interconnect)等。

近年来,与硅工艺相兼容的应变硅技术在MOS器件中表现出了独到的优势而备受关注。

高质量的应变硅的生长可以把应变工程和带隙工程引入成熟的硅工艺中。

在MOS器件的沟道中引入应变,不仅可以提高载流子的迁移率,且有助于抑制DIBL效应。

据报道,同尺寸的应变硅与体硅MOSFET相比,功耗减小1/3、速度提高30%、特征频率提高50%以上、功耗延迟积仅为后者的1/5~1/6、器件的封装密度提高50%。

因此,应变硅技术在高速和低功耗领域有很大的应用潜力。

本文主要简述了应变硅技术对载流子迁移率影响的机理,同时从全局应变和局部应变两个方面综述了其应用,并简述了各自在MOS工艺中应用的优缺点。

在MOS器件的沟道中引入应变可以提高载流子的迁移率,其主要原因来源于两方面:载流子有效质量的降低和能谷间声子散射率的降低[1,20,25,26]。

在室温的条件下,与体硅相比,应变硅中的电子迁移率增加约60%~95%[3,4],空穴迁移率增加约30%[3]。

公式(1)描述了迁移率(μ)与散射率(1/τ)、载流子的有效质量(m*)之间的关系[1]。

硅的导带由于应力的作用,使得其能级的分裂,由六重简并能谷分裂为两组:两个降低的能谷沿与界面垂直的轴向Δ2;四个抬高的能谷沿与界面平行的轴向Δ4,如图1所示。

低能谷与高能谷之间的能级差的经验值为0.67xeV(其中x是指Ge 的摩尔数)。

大多数反型层电子占据两个低能谷,在于界面平行方向输运,具有较低的导带有效质量,导致低场迁移率增大。

谷间声子散射率因能谷分裂而降低。

由于初末态之间的能差增大,在非等能谷之间的散射率降低[1,2,22,25]。

如在弛豫SiGe层上外延顶层Si,在顶层Si的厚度小于临界厚度时,硅原子与弛豫SiGe晶格常数达到匹配,则顶层中的硅原子收拉伸作用,在in-plane方向形成了双轴应变。

该结构的应变硅的导带和价带均有加大的突变量,电子势阱和空穴势阱处在不同的层中,导带突变量处于应变硅中,价带突变量集中于SiGe层,形成Ⅱ型量子阱,如图2所示。

Ⅱ型量子阱由于导带和价带的能带突变量都比较大,电子和空穴的迁移率都有所增强,因而应变Si/SiGe在CMOS工艺中既可做N型也可做P型器件。

硅的价带因应力的作用,引起价带结构的畸变使得有效空穴质量降低,同时,因布里渊区中心的重空穴带与轻空穴带分离降低了带间散射[2,22,25],如图3、图4所示。

价带顶轻重空穴带在Г点的能量分裂值可用下式近似表示[2]:其中x是弛豫Si/Ge中的锗的摩尔分数。

减小平面内电导有效质量或增加平面外电导有效质量可增强载流子迁移率。

当电场增加时,即应变引起能带的卷曲,使得单轴压应变引起的轻空穴带平面外电导有效质量高于重空穴的,进而单轴压应变比双轴的伸张应变更易提高空穴的迁移率[22,25,26]。

如Si1-xGex薄膜淀积在Si衬底上,薄膜在平行于衬底方向受到压应力。

此时电子势阱和空穴势阱都处在Si1-xGex层中,这种能带称之为I型量子阱,如图5所示。

Si1-xGex薄膜的价带突变量明显,与之相比导带突变量非常小,因此该结构适用于PMOSFET。

应变硅应用到MOS器件中,首要条件是应变硅材料的性能要达到器件级的标准,如表面粗糙度(RMS)、缺陷(defect density)和位错密度(TD)等。

因此如何获得高质量的应变硅材料一直是研究的热点。

应变硅技术主要包括两方面:(1)全局应变,指在整个圆片都生长应变硅层,不同的沟道位置具有相同的应力大小和方向,通过引入压应力(compressive strain)或伸张应力(tensile strain),提高载流子的迁移率;(2)局部应变,通过一定的技术仅在沟道处引入应力的方法。

前者是虚拟衬底诱生双轴应变,即在MOS器件的沟道两个方向均存在应变;后者是在MOS器件的工艺制程中诱生的单轴应变。

应变技术在MOS器件中的应用情况详见表1。

全局应变是利用材料晶格常数的差异产生的应变。

Ge比Si的晶格常数大4.2%,当在Si/Ge弛豫层上外延一层硅时,硅的晶格将受四方畸变,在生长平面内诱生了双轴张应变,在垂直平面上诱生了压应变的薄单晶硅,如图6、图7所示。

其外延层的厚度需要小于临界厚度,当外延层的厚度超过临界厚度时,应变所产生的能量将被消耗在与应变诱生层和衬底的匹配中,这时产生了大量的缺陷,尤其是位错会进一步降低应变的程度,从而使得载流子的迁移率降低。

应变弛豫缓冲层结构(Strained Relaxed Buffer,SRB)、绝缘层上的SiGe (SiGe On Insulator,SGOI)、绝缘层上应变硅(Strained Si On Insulator,SSOI)都属于全局应变。

3.1.1 应变弛豫缓冲层结构(SRB)应变弛豫缓冲层结构是在硅衬底上按一定的方法生长应变弛豫的SiGe缓冲层,然后在上面生长硅帽层,Si/SiGe界面的晶格常数匹配时,硅原子受到拉伸,形成了双轴张应变。

为了获得高质量的双轴应变硅,则需要优质的器件级的弛豫(relaxed layer)SiGe层作为虚拟衬底(Virtual substrate)。

生长低RMS、低TD、高弛豫度(relaxation degree)、薄的弛豫层SiGe的方法主要有三种:渐变的Si1-yGey缓冲层技术(the grading SiGe buffer layer technique)、离子注入技术(ion implantation technology.)、低温硅技术(low temperature Si (LT-Si)technology)[5~15]。

其中,渐变的Si1-yGey缓冲层技术是最为常见的一种制备质量较高的SiGe虚拟衬底的方法,但外延层的厚度较厚,致使在MOS器件中的自加热效应较为突出[15,16]。

离子注入技术可以获得高弛豫度、超薄的SiGe虚拟衬底,但因注入损伤引起SiGe层中的缺陷、位错密度、粗糙度较高,不易于制备质量高的弛豫层[16]。

低温硅技术是制备高质量、超薄SiGe的虚拟衬底的选择,但应变的弛豫度(the degree of strain relaxation )受到膜层厚度的限制[15、17]。

如果在应变硅层与弛豫层之间增加一层应变的缓变Si1-yGey 缓冲层(其中,缓冲层中Ge的摩尔分数是梯度性变化的),以分担Si/SiGe异质结不匹配产生的应力,这个缓冲层也可以避免Si/SiGe界面的空穴限越问题[18]。

3.1.2 绝缘层上应变硅(SSOI)将SOI技术与应变硅技术结合可以组合成多种复合结构,如SGOI、SSOI等。

与体硅MOSFET相比,有如下的特点:(1)应变硅的高迁移率和低掺杂浓度;(2)低结电容;(3)抑制短沟道效应;(4)杂质浮动统计变化减小;(5)与SOI器件相似的简单的绝缘和阱隔离。

其制备方法有:含Ge溶缩、融熔固化、晶圆键合与智能剥离等[21~23]。

全局应变硅技术存在的问题是SiGe衬底中Ge在热处理过程中外扩到应变硅层,同时,降低了应变度。

而Ge到栅氧界面时,表面的缺陷浓度会大大增加,从而降低了MOS管的性能和可靠性。

目前也有一种应变硅技术就是全晶片无Ge应变硅,S. Christiansen等采用键合技术制备了SSOI,如图8所示,首先在SiGe缓冲虚拟衬底上外延生长应变硅层,应变硅部分被热氧化,将另外一部分氧化层作为硅衬底,通过键合SiO2层,同时生长应变硅的SiGe缓冲虚拟衬底和初始Si衬底与应变硅玻璃,而中间的氧化层则成为绝缘硅的埋层[21,24]。

局部应变又称为工艺诱生应变,将部分工艺诱生的应变施加于MOS沟道处,提高MOS器件的性能。