APM2301CA中文资料

ST2301中文资料

-2.8ADESCRIPTIONThe ST2301 is the P-Channel logic enhancement mode power field effect transistor are produced using high cell density, DMOS trench technology.This high density process is especially tailored to minimize on-state resistance.These devices are particularly suited for low voltage application such as cellular phone and notebook computer power management and other batter powered circuits, and low in-line power loss are needed in a very small outine surface mount package.PIN CONFIGURATION SOT-23-3L1.Gate2.Source3.DrainS: Subcontractor Y: Year Code A: Process CodeFEATUREz -20V/-2.8A, R DS(ON) = 120m-ohm@VGS = -4.5Vz -20V/-2.0A, R DS(ON) = 170m-ohm@VGS = -2.5Vz Super high density cell design forextremely low R DS(ON)z Exceptional on-resistance and maximumDC current capabilityz SOT-23-3L package design-2.8AABSOULTE MAXIMUM RATINGS (Ta = 25J Unless otherwise noted )Parameter Symbol Typical Unit Drain-Source Voltage V DSS -20 V Gate-Source VoltageV GSS +12V Continuous Drain Current (TJ=150J ) T A =25¢JT A =70J I D-2.5 -1.5A Pulsed Drain CurrentI DM -10 A Continuous Source Current (Diode Conduction) I S -1.6 A Power DissipationT A =25¢J T A =70JP D 1.250.8W Operation Junction Temperature T J 150 J Storgae Temperature RangeT STG -55/150 J Thermal Resistance-Junction to AmbientR cJA 120J /W-2.5AELECTRICAL CHARACTERISTICS ( Ta = 25J Unless otherwise noted )Parameter Symbol Condition Min Typ Max UnitStaticDrain-Source Breakdown Voltage V (BR)DSS V GS =0V,I D =-250uA -20VGate Threshold Voltage V GS(th) V DS =V GS ,I D =-250uA -0.45 -1.5VGate Leakage CurrentI GSS V DS =0V,V GS =+8V +100nAV DS =-30V,V GS =0V -1Zero Gate Voltage Drain CurrentI DSS V DS =-30V,V GS =0V T J =55J-10uAOn-State Drain Current I D(on) V DS -5V,V GS =-4.5V V DS -5V,V GS =-2.5V -6 -3ADrain-source On-Resistance R DS(on)V GS =-4.5V,I D =-2.8AV GS =-2.5V,I D =-2.0A0.09 0.1450.120.17Forward Transconductance g fsV DS =-5V,I D =-2.8V 6.5 S Diode Forward Voltage V SD I S =-1.6A,V GS =0V -0.8 -1.2VDynamicTotal Gate Charge Qg 5.8 10 Gate-Source Charge Qgs 0.85Gate-Drain Charge Qgd V DS =-6V,V GS =-4.5VI D -2.8A 1.7nC Input Capacitance Ciss 415Output CapacitanceCoss 223Reverse Transfer Capacitance CrssV DS =-6V,V GS =0VF=1MHz 23pF 13 25Turn-On Timet d(on) t r 36 60 42 70 Turn-Off Timet d(off) t fV DD =-6V,R L =6 I D =-1A,V GEN =-4.5VR G =634 60nS-2.5ASOT-23-3L PACKAGE OUTLINE-2.5ATYPICAL CHARACTERICTICS (25J Unless noted)-2.5ATYPICAL CHARACTERICTICS (25J Unless noted)。

APM2300CA

APM2300C A : C00X

X - Date Code

Note: ANPEC lead-free products contain molding compounds/die attach materials and 100% matte tin plate termination finish; which are fully compliant with RoHS. ANPEC lead-free products meet or exceed the lead-free requirements of IPC/JEDEC J-STD-020C for MSL classification at lead-free peak reflow temperature. ANPEC defines “Green” to mean lead-free (RoHS compliant) and halogen free (Br or Cl does not exceed 900ppm by weight in homogeneous material and total of Br and Cl does not exceed 1500ppm by weight).

2

1

Duty = 0.5

0.2

0.1

0.1

0.05

0.02

0.01

0.01 Single Pulse

1E-3 1E-4 1E-3 0.01 0.1

Mounted on 1in2 pad R : 150 oC/W

θJA

1 10 100

Square Wave Pulse Duration (sec)

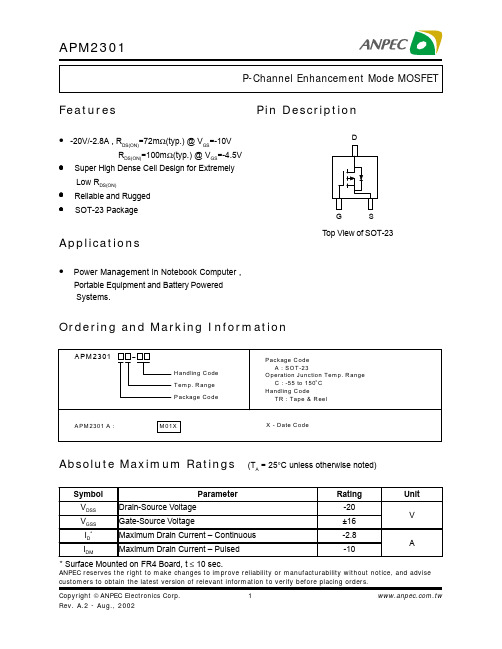

APM2301中文资料

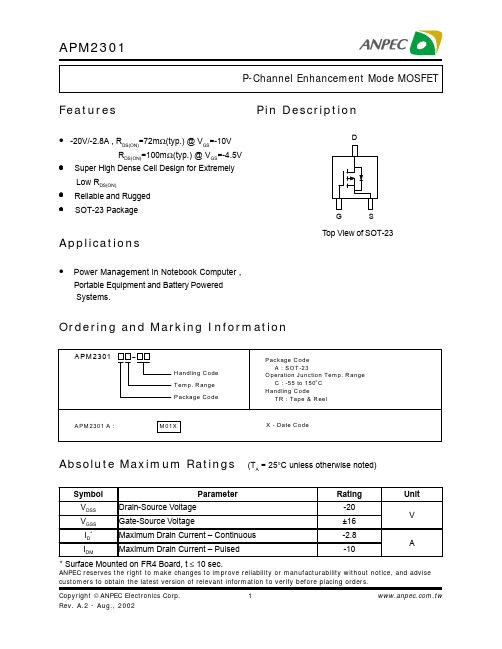

ANPEC reserves the right to make changes to improve reliability or manufacturability without notice, and advise customers to obtain the latest version of relevant information to verify before placing orders.Pin DescriptionOrdering and Marking InformationFeaturesApplicationsAbsolute Maximum Ratings (T A = 25°C unless otherwise noted)• -20V/-2.8A , R DS(ON)=72m Ω(typ.) @ V GS =-10VR DS(ON)=100m Ω(typ.) @ V GS =-4.5V• Super High Dense Cell Design for ExtremelyLow R DS(ON)• Reliable and Rugged • SOT-23 Package• Power Management in Notebook Computer ,Portable Equipment and Battery Powered Systems.* Surface Mounted on FR4 Board, t ≤ 10 sec.G DSTop View of SOT-23Notesa : Pulse test ; pulse width ≤300µs, duty cycle ≤ 2%b: Guaranteed by design, not subject to production testingAbsolute Maximum Ratings Cont. (T A = 25°C unless otherwise noted)Electrical Characteristics (T A = 25°C unless otherwise noted)2468100.0300.0450.0600.0750.0900.1050.1200.1350.150012345246810-50-2502550751001251500.000.250.500.751.001.251.500.00.5 1.0 1.5 2.0 2.50246810Typical Characteristics-I D -D r a i n C u r r e n t (A )Transfer Characteristics-V GS - Gate-to-Source Voltage (V)Threshold Voltage vs. Junction T emperatureTj - Junction T emperature (°C)-V G S (t h )-T h r e s h o l d V o l t a g e (V )(N o r m a l i z e d )R D S (O N )-O n -R e s i s t a n c e (Ω)On-Resistance vs. Drain Current-I D - Drain Current (A)Output Characteristics-I D -D r a i n C u r r e n t (A )-V DS - Drain-to-Source Voltage (V)369121505101520-50-25025507510012515012345678910Typical CharacteristicsR D S (O N )-O n -R e s i s t a n c e (Ω)(N o r m a l i z e d )On-Resistance vs. Junction TemperatureT J - Junction Temperature (°C)-V DS - Drain-to-Source Voltage (V)CapacitanceC a p a c i t a n c e (p F )-V GS - Gate-to-Source Voltage (V)R D S (O N )-O n -R e s i s t a n c e (Ω)On-Resistance vs. Gate-to-Source VoltageGate ChargeQ G - Gate Charge (nC)-V G S -G a t e -S o u r c e V o l t a g e (V )0.00.20.40.60.8 1.0 1.2 1.4 1.61100.010.1110100024681012141E-41E-30.010.11101000.010.11Typical CharacteristicsP o w e r (W )Single Pulse PowerTime (sec)Square Wave Pulse Duration (sec)Source-Drain Diode Forward Voltage-I S -S o u r c e C u r r e n t (A )-V SD -Source-to-Drain Voltage (V)N o r m a l i z e d E f f e c t i v e T r a n s i e n t T h e r m a l I m p e d a n c eNormalized Thermal Transient Impedence, Junction to AmbientPackaging Information SOT-23Physical SpecificationsReflow Condition (IR/Convection or VPR Reflow)Reference JEDEC Standard J-STD-020A APRIL 1999Classification Reflow ProfilesPackage Reflow ConditionsPre-heat temperature183 CPeak temperatureTime°t e m p e r a t u r eReliability test programCarrier Tape & Reel DimensionsCover Tape DimensionsCustomer ServiceAnpec Electronics Corp.Head Office :5F, No. 2 Li-Hsin Road, SBIP,Hsin-Chu, T aiwan, R.O.C.T el : 886-3-5642000Fax : 886-3-5642050Taipei Branch :7F, No. 137, Lane 235, Pac Chiao Rd.,Hsin Tien City, Taipei Hsien, T aiwan, R. O. C.T el : 886-2-89191368Fax : 886-2-89191369。

AM2301

温湿度模块AM2301 产品手册更多详情请登陆:一、产品概述AM2301湿敏电容数字温湿度模块是一款含有己校准数字信号输出的温湿度复合传感器。

它应用专用的数字模块采集技术和温湿度传感技术,确保产品具有极高的可靠性与卓越的长期稳定性。

传感器包括一个电容式感湿元件和一个高精度测温元件,并与一个高性能8位单片机相连接。

因此该产品具有品质卓越、超快响应、抗干扰能力强、性价比极高等优点。

每个传感器都在极为精确的湿度校验室中进行校准。

校准系数以程序的形式储存在单片机中,传感器内部在检测信号的处理过程中要调用这些校准系数。

标准单总线接口,使系统集成变得简易快捷。

超小的体积、极低的功耗,信号传输距离可达20米以上,使其成为各类应用甚至最为苛刻的应用场合的最佳选择。

产品为3引线(单总线接口)连接方便。

特殊封装形式可根据用户需求而提供。

实物图外形尺寸(单位:mm)二、应用范围暖通空调、除湿器、测试及检测设备、消费品、汽车、自动控制、数据记录器、家电、湿度调节器、医疗、气象站、及其他相关湿度检测控制等。

三、产品亮点超低能耗、传输距离远、全部自动化校准、采用电容式湿敏元件、完全互换、标准数字单总线输出、卓越的长期稳定性、采用高精度测温元件。

四、单总线接口定义4.1 AM2301引脚分配表1:AM2301引脚分配图1:AM2301引脚分配图4.2 电源引脚(VDD GND)AM2301的供电电压范围为3.3V - 5.2V,建议供电电压为5V。

4.3 串行数据(SDA)SDA引脚为三态结构,用于读、写传感器数据。

具体的通信时序,见通信协议的详细说明。

五、传感器性能 5.1 相对湿度表2: AM2301相对湿度性能表图2: 25℃时AM2301的相对湿度最大误差 图3:温度传感器的温度最大误差六、电气特性电气特性,如能耗,高、低电平,输入、输出电压等,都取决于电源。

表4详细说明了AM2301的电气特性,若没有标明,则表示供电电压为5V 。

APM使用Copter(直升机和多轴)固件的中文参数表

10

米

1 -- 127

circle繞圈模式時的繞圈半徑

CIRCLE_RATE

20

度/秒

-90 -- 90

circle繞圈模式時的繞圈角速度

COMPASS-AUTODEC

1

0,1

自動磁偏角開關,0關閉,1開啟

COMPASS_DEC

-0.083

度

磁偏角設置,請根據本地磁偏角輸入,具體可登入/查詢

電池資訊顯示開關,0-不顯示;3-只顯示電壓;4-顯示電流和電壓

BATT_VOLT_MULT

10.1

設置電壓感測器埠採集的電壓與實際電壓的倍數,如:電壓檢測PIN腳測出來2V,那麼實際電壓應該是2X10.1=20.2V

BATT_VOLT_PIN

13

-1,0,1,2,13,100

設置電壓感測器使用的埠,-1不使用;0-A0;1—A1;2- Pixhawk用;13-A13;100-PX4用

快門觸發設置,如果不為零將根據GPS的移動距離進行拍照,例如:設置5米,那麼將根據GPS定位資訊,每飛行5秒就按一次快門

CAM_TRIGG_TYPE

0

0,1

快門觸發類型設置,0-舵機,1-繼電器

CH7_OPT

0

通道7操作設置(PWM值1800以上),0:無, 2:Flip, 3:簡單模式, 4:返航, 5:Save Trim, 7:Save WP, 8:Multi Mode, 9:Camera Trigger, 10:開聲納, 11:Fence, 12:ResetToArmedYaw, 13:Super Simple Mode, 14:Acro Trainer, 16:自動, 17:自動調參

SPP2301A P-Channel Enhancement Mode MOSFET 说明书

现货库存、技术资料、百科信息、热点资讯,精彩尽在鼎好!SPP2301AP-Channel Enhancement Mode MOSFET DESCRIPTION APPLICATIONSThe SPP2301A is the P-Channel logic enhancementmode power field effect transistors are produced using high cell density , DMOS trench technology.This high density process is especially tailored to minimize on-state resistance.These devices are particularly suited for low voltage application such as cellular phone and notebook computer power management and other battery powered circuits, and low in-line power loss are needed in a very small outline surface mount package.z Power Management in Note book z Portable Equipmentz Battery Powered System z DC/DC Converterz Load Switchz DSCz LCD Display inverter FEATURES PIN CONFIGURATION(SOT-23-3L)PART MARKING-20V/-2.8A,R DS(ON)=150m Ω@V GS =-4.5V-20V/-2.0A,R DS(ON)=275m Ω@V GS =-2.5VSuper high density cell design for extremely lowR DS (ON)Exceptional on-resistance and maximum DCcurrent capabilitySOT-23-3L package designTYPICAL CHARACTERISTICSTYPICAL CHARACTERISTICSTYPICAL CHARACTERISTICSInformation provided is alleged to be exact and consistent. SYNC Power Corporation presumes no responsibility for the penalties of use of such information or for any violation of patents or other rights of third parties which may result from its use. No license is granted by allegation or otherwise under any patent or patent rights of SYNC Power Corporation. Conditions mentioned in this publication are subject to change without notice. This publication surpasses and replaces all information previously supplied. SYNC Power Corporation products are not authorized for use as critical components in life support devices or systems without express written approval of SYNC Power Corporation.©The SYNC Power logo is a registered trademark of SYNC Power Corporation©2004 SYNC Power Corporation – Printed in Taiwan – All Rights ReservedSYNC Power Corporation9F-5, No.3-2, Park StreetNanKang District (NKSP), Taipei, Taiwan, 115, R.O.CPhone: 886-2-2655-8178Fax: 886-2-2655-8468©。

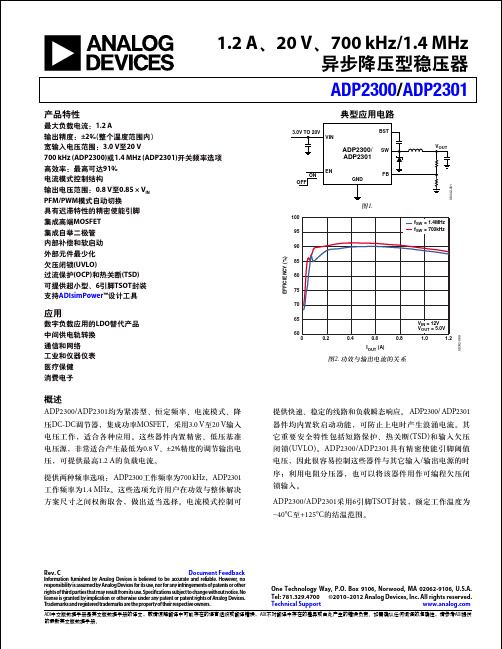

ADP2300_2301_cn开关电源中文版

65 60

0 0.2 0.4 0.6 IOUT (A) 0.8

VIN = 12V VOUT = 5.0V 1.0 1.2

08342-069

图2. 功效与输出电流的关系

概述

ADP2300/ADP2301均为紧凑型、恒定频率、电流模式、降 压DC-DC调节器,集成功率MOSFET,采用3.0 V至20 V输入 电压工作,适合各种应用。这些器件内置精密、低压基准 电压源,非常适合产生最低为0.8 V、±2%精度的调节输出电 压,可提供最高1.2 A的负载电流。 提供两种频率选项: ADP2300工作频率为700 kHz,ADP2301 工作频率为1.4 MHz。这些选项允许用户在功效与整体解决 方案尺寸之间权衡取舍,做出适当选择。电流模式控制可 提供快速、稳定的线路和负载瞬态响应。 ADP2300/ ADP2301 器件均内置软启动功能,可防止上电时产生浪涌电流。其 它重要安全特性包括短路保护、热关断 (TSD)和输入欠压 闭锁 (UVLO)。 ADP2300/ADP2301具有精密使能引脚阈值 电压,因此很容易控制这些器件与其它输入/输出电源的时 序;利用电阻分压器,也可以将该器件用作可编程欠压闭 锁输入。 ADP2300/ADP2301采用6引脚TSOT封装,额定工作温度为 −40°C至+125°C的结温范围。

ADI中文版数据手册是英文版数据手册的译文,敬请谅解翻译中可能存在的语言组织或翻译错误,ADI不对翻译中存在的差异或由此产生的错误负责。如需确认任何词语的准确性,请参考ADI提供 的最新英文版数据手册。

ADP2300/ADP2301

目录

特性 ..............................................................................

APM2300AA中文资料

ANPEC reserves the right to make changes to improve reliability or manufacturability without notice, and advise customers to obtain the latest version of relevant information to verify before placing orders.APM2300AAFeaturesApplications• Power Management in Notebook Computer ,Portable Equipment and Battery Powered Systems.Pin DescriptionOrdering and Marking InformationAPM2300AHandling Code Tem p. Range Package CodePackage Code A : SOT-23Operating Junction Tem p. Range C : -55 to 150°C Handling CodeTU : Tube TR : Tape & Reel Lead Free CodeL : Lead Free Device Blank : Original Device APM2300A A :A00XXXXXX - Date CodeLead Free Code T op View of SOT-23N-Channel MOSFET• 20V/6A ,R DS(ON)=25m Ω(typ.) @ V GS =10V R DS(ON)=32m Ω(typ.) @ V GS =4.5V R DS(ON)=40m Ω(typ.) @ V GS =2.5V• Super High Dense Cell Design • Reliable and Rugged•Lead Free Available (RoHS Compliant)DGSGNote: ANPEC lead-free products contain molding compounds/die attach materials and 100% matte in plate termina-tion finish; which are fully compliant with RoHS and compatible with both SnPb and lead-free soldiering operations.ANPEC lead-free products meet or exceed the lead-free requirements of IPC/JEDEC J STD-020C for MSL classifica-tion at lead-free peak reflow temperature.APM2300AAAbsolute Maximum Ratings (T A = 25°C unless otherwise noted)*Surface Mounted on 1in2 pad area, t ≤ 10sec.Electrical Characteristics (T A = 25°C unless otherwise noted)APM2300AAElectrical Characteristics (Cont.) (T A = 25°C unless otherwise noted)a : Pulse test ; pulse width≤300µs, duty cycle≤2%.b : Guaranteed by design, not subject to production testing.APM2300AA1E-41E-30.010.11101001E-30.010.112Typical CharacteristicsI D - D r a i n C u r r e n t (A )Drain CurrentT j - Junction Temperature (°C)Safe Operation AreaV DS - Drain - Source Voltage (V)N o r m a l i z e d T r a n s i e n t T h e r m a l R e s i s t a n c eThermal Transient ImpedanceSquare Wave Pulse Duration (sec)Power DissipationP t o t - P o w e r (W )T j - Junction T emperature (°C)I D - D r a i n C u r r e n t (A )204060801001201401600.00.10.20.30.40.50.60.70.80.91.020406080100120140160012345670.11101000.010.1110100APM2300AADrain-Source On Resistance I D - Drain Current (A)T j - Junction T emperature (°C)Gate Threshold VoltageV DS - Drain - Source Voltage (V)I D - D r a i n C u r r e n t (A )Output Characteristics Transfer CharacteristicsV GS - Gate - Source Voltage (V)I D - D r a i n C u r r e n t(A )N o r m a l i z e d T h r e s h o l d V o l ta g eTypical Characteristics (Cont.)246810024681012141618204812162002468101214161820-50-2502550751001251500.000.250.500.751.001.251.50APM2300AAV DS - Drain - Source Voltage (V)Drain-Source On ResistanceN o r m a l i z e d O n R e s i s t a n c eT j - Junction T emperature (°C)C - C a p a c i t a n c e (p F )I S - S o u r c e C u r r e n t (A )CapacitanceQ G - Gate Charge (nC)V G S - G a t e - s o u r c e V o l t a g e (V )Typical Characteristics (Cont.)-50-252550751001251500.00.20.40.60.81.01.21.41.61.82.0110200160320480640800012345612345APM2300AA Packaging Information SOT-23APM2300AAT LT P25T e m p e r a t u r eTim eReflow Condition (IR/Convection or VPR Reflow)Classification Reflow ProfilesPhysical SpecificationsAPM2300AAClassification Reflow Profiles(Cont.)Reliability Test ProgramCarrier Tape & Reel DimensionsAPM2300AACarrier Tape & Reel Dimensions(Cont.)(mm) Cover Tape DimensionsCustomer ServiceAnpec Electronics Corp.Head Office :5F, No. 2 Li-Hsin Road, SBIP,Hsin-Chu, T aiwan, R.O.C.T el : 886-3-5642000Fax : 886-3-5642050Taipei Branch :7F, No. 137, Lane 235, Pac Chiao Rd.,Hsin Tien City, Taipei Hsien, T aiwan, R. O. C.T el : 886-2-89191368Fax : 886-2-89191369。

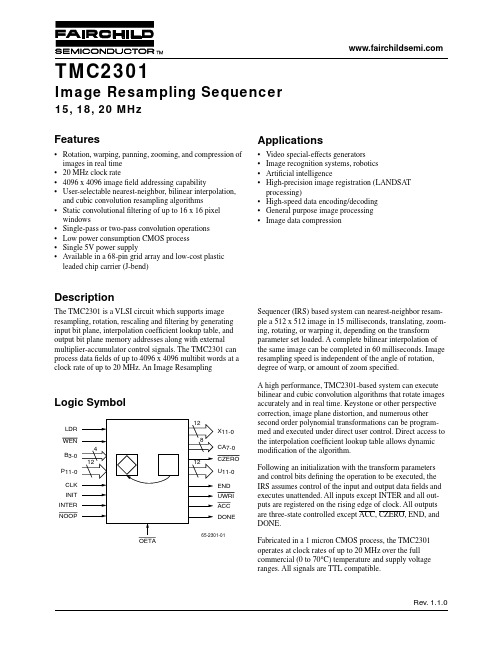

TMC2301资料

TMC2301PRODUCT SPECIFICATIONFunctional DescriptionGeneral InformationThe IRS is a versatile self-sequencing address generator designed primarily to filter a two-dimensional image or to remap and resample it from one set of Cartesian coordinates (x, y) into a new transformed set (u, v). Most applications use two identical devices in tandem, one generating the row coordinates (X and U), the other generating the column coor-dinates (Y and V). The algorithm performed by theTMC2301 consists of two steps: a coordinate system trans-formation, followed by pixel interpolation. Interpolation is necessary when the transformed pixel positions (U, V) do not coincide with the original pixel positions (X, Y). The new pixel intensity values are obtained by interpolating the original pixels in the neighborhood of the transformed pixel positions. See Figure 1.The IRS executes a general second order coordinate transfor-mation of the form:X(u, v) = Au2 + Bu + Cuv + Dv2 + Ev + FY(u, v) = Gu2 + Hu + Kuv + Lv2 + Mv + Nwhere A through N are user-defined parameters. It steps sequentially through the pixels of a user-defined rectangle in the new set of coordinates, computing the "old" address (X, Y) corresponding to each "new" location (U, V).The TMC2301 uses the external multiplier-accumulator, connected to the system clock, to calculate the interpolated pixel value by summing the products of the original pixel values stored in the source buffer RAM and the appropriate weights from the polynomial transform lookup table. The new interpolated image value is then stored in the corre-sponding (U, V) memory location. Finally, the new image address is incremented by one pixel in the "U" direction or reset to the start of the next line (with "V" incremented) pro-ceeding line-by-line through the entire destination image. The TMC2301 can support any nearest neighbor, bilinear, or cubic resampling, according to the user's requirements. The bilinear and cubic kernels require a coefficient lookup table and multiplier-accumulator. Both one-pass and two-pass algorithms are supported. Sophisticated "walkaround" algo-rithms implementing static filters are also easily realized uti-lizing convolutional kernels of up to 16 x 16 pixels. For each output point in a typical static single-pass filter, the IRS will generate a series of addresses, "walking" around that point in two dimensions. At the end of each walk, it will advance one pixel along the output scan line, then begin the walk for the next pixel.PRODUCT SPECIFICATION TMC2301A basic TMC2301-based system is shown in Figure 2. In this typical system, two Image Resampling Sequencers process the image. The only other external parts needed are a multiplier-accumulator, external interpolation coefficient lookup table RAM, and the user-specified Source and Destination Image Memory.TMC2301PRODUCT SPECIFICATION Pin Assignments68 Pin Grid Array68 Pin PLCCPRODUCT SPECIFICATION TMC2301 Pin DescriptionsPin NamePin NumberPin Function Description PGA PLCCPowerGND F2, F10, K1,K6, L10, B61, 9, 18, 35,52, 60Supply Voltage. The TMC2301 operates from a single +5Vsupply. All pins must be connected.V DD L5, A636, 68Ground. The TMC2301 operates from a single +5V supply. Allpins must be connected.ClockCLK A734System Clock. The TMC2301 has a angle clock input. The risingedge of CLK strobes all enabled registers. All timingspecifications are referenced to the rising edge of CLK.InputsB3-0A3, B3, A4, B442-39Parameter Register Address. The write addresses for theindividual coordinate transform parameters are presented at theregistered 4-bit B input port. B3 is the Most Significant Bit.P11-0D10, D11,C10, C11,B11, B10, A10,B9, A9, B8,A8, B722-33Parameter Register Data. The coordinate transformation parameters are loaded through the registered 12-bit P input port.P11 is the Most Significant Bit.OutputsCA7-0K9, L8, K8, L7,K7, L6, K5, L47-2, 67, 66Coefficient Address. The current interpolation kernel coefficient lookup table address is indicated by the registered 8-bit CA7-0output bus. This output is forced to the high impedance statewhen NOOP is LOW. CA7 is the Most Significant Bit.U11-0L2, K2, J1, J2,H1, H2, G1,G2, F1, E1,E2, D162, 61, 59-53,51-49Target Address. The U (or V) target address of the image beinggenerated is indicated by the registered 12-bit U11-0 output bus.This output is forced to the high impedance state when OETA isHIGH. U11 is the Most Significant Bit.X11-0E11, E10, F11,G11, G10,H11, H10, J11,J10, K11, K10,L921-19, 17-10,8Source Address. The current X (or Y) source pixel address ofthe image being resampled is indicated by the registered 12-bitX11-0 output bus. This output is forced to the high impedancestate when NOOP is LOW. X11 is the Most Significant Bit.ControlsACC L364Accumulate. The accumulation register of the external multiplier-accumulator is initialized by the registered ACC output. ACCgoes LOW for one cycle at the start of each interpolation "walk,"effectively clearing the storage register by loading in only the newfirst product. See Figure 9.INIT B244Initialize. The control logic is cleared and initialized for the startof a new image transformation when the registered INIT input isHIGH for a minimum of two clock cycles. Normal operation beginsafter INIT goes LOW.INTER C246Interconnect. In the common two-device system configuration,the Interconnect inputs are connected to the END flag outputs.The END flag from the row (X) sequencer thus indicates an "endof line" to the column (Y) device, while the column sequencer inturn sends a "bottom of frame" signal to the row device, forcing areset of the address counter.TMC2301PRODUCT SPECIFICATIONLDRA538Load Parameter Data Registers. The data held in alltransformation parameter preload registers are latched into the working registers when the registered input LDR is HIGH. When LDR is LOW, the working parameters remain unchanged. See Figure 4.NOOP B537No Operation. The Clock is overidden when the registered input NOOP is LOW, holding each address generator in their current state. Also, the output buffers for the address busses X 11-0 and CA 7-0 are forced to the high impedance state. This allows the user access to all external memory. When NOOP goes HIGH, normal operation resumes on the next clock cycle.OETA B145Target Memory Output Enable. The target memory outputs UWRI and address bus U 11-0 are in the high-impedance state when the registered Output Enable input is HIGH. When OETA is LOW, they are enabled on the next clock cycle.UWRI K363Target Memory Write Enable. After the end of each interpolation "walk," the Target Memory (U or V) Write Enable goes LOW for one clock cycle. See Figure 9. This registered output is forced to the high impedance state when OETA is HIGH.WEN A243Parameter Write Enable. The registered Write Enable input allows the transformation parameters to be written into thepreload register indicated by the address at the B input port when LOW. See Figure 4.Flags CZEROK465Coefficient Zero. The registered CZERO flag of a horizontal dimension TMC2301 goes HIGH if X < 0, XMIN ≤ X ≤ XMAX, or X ≥ 4096 (1000 hex). It goes LOW if 0 ≤ X ≤ XMIN or XMAX < X < 4096. The logical AND of the CZERO flags of a two-dimensional pair of TMC2301s will go LOW when the source address falls outside a rectangle with vertices (XMIN, YMIN), (XMAX, YMIN), (XMIN, YMAX), and (XMAX, YMAX), denoting an invalid address. The external data path can be wired to substitute a selected background value whenever this AND = 0.DONED248End of Transform. In the standard two-device system, a row sequencer DONE flag HIGH after the last walk at the end of the last row of an image (during UWRI LOW) indicates the end of the transform. This registered output is usually ignored on the column device. See the Transformation Control Parameters, AUTOINIT.END C147End of Row/Page. The registered END flag goes HIGH during the last pixel of the last walk in a row in the case of the row chip, and the last pixel of the last walk in a column in the column chip, in the two-device architecture. This output is used as the end-of-line and end-of-frame indicator in conjunction with the INTER inputs of both TMC2301s.Pin Descriptions (continued)Pin Name Pin NumberPin Function DescriptionPGA PLCCPRODUCT SPECIFICATIONTMC2301Transformation Control ParametersThe TMC2301 is a self-sequencing device which requires no cycle-to-cycle intervention from the host system. To program the device, the user loads the 16 operating parameters, which define the transformation to be performed, which sections of the original and resampled image spaces are to be utilized, and various control words. Filtering operations are further defined by the values the user loads into the external coeffi-cient memory. The transform parameters are described below. See also Tables 1 through 3.Note:1.For each incremental move along the U axis, the startingpoint of the new "walk around spiral" is indexed to the ENDING point of the previous walk around spiral, rather than to its center. Therefore, the terms dX/dU 0 and dY/dU 0 must be adjusted accordingly. Since each new line is referenced back to the previous line's initial spiral starting point, no similar dX/dV 0 or dY/dV 0 correction is needed.XMIN, XMAX, YMIN, YMAX These four parameters outline the "source" rectangular region of theoriginal image. Whenever the IRS pair generates an (X, Y) address within this boundary the CZERO flags will denote a valid memory read. In the most common case, XMIN < XMAX, YMIN < YMAX, 000h < X < FFFh, and 000h < Y< FFFh. In this case, addresses out of bounds cause one or both CZEROs to go LOW. Refer to Application NoteTP-38 for further information on other boundary violation cases. Each parameter is expressed in 12-bit unsigned binary integer notation. See Figure 12.UMIN, UMAX,VMIN, VMAXThese four parameters outline the "target" region of the (u, v) plane, into which the resampled image will be written. The IRS will generate, line by line, a scan that fills only this portion of the plane, permitting the user to assemble a mosaic of multiple rectangular subimages. Care must be taken to ensure that UMAX > UMIN and VMAX > VMIN. Each parameter is expressed in 12-bit unsigned binary integer notation. See Figure 12.(X 0, Y 0)These are the coordinates of the first pixel to be read from the original image. In many applications, this point will be one of the four corners of the original image to beresampled. The pixels near (X 0, Y 0) in the original image will be used to compute the upper left pixel of the transformed image. In non-inverting, non-reversing applications (X 0, Y 0) will be the upper left corner of the original subimage. Each coordinate is expressed in 13-bit integer plus 5-bit fraction, two's complement notation.dX/dU 0Is the initial horizontal partial first derivative indicating thedisplacement along the X axis which corresponds to each one pixelmovement along the U axis. Usually, 0 < dX/dU 0 < 1 corresponds to magnification, whereas dX/dU 0 > 1 represents reduction and dX/dU 0 < 0 denotes reflection about a vertical axis. The first derivatives are expressed in 8-bit integer, 12-bit fraction two's complement notation.dX/dV 0Is the initial horizontal-vertical partial first derivative. It indicates the displacement along the X axis corresponding to each one pixel movement along the V axis. The coefficients dX/dV 0 and dX/dU 0 define image rotation and shear.dY/dU 0Is the initial vertical-horizontal partial first derivative. It indicates the displacement along the Y axis corresponding to each one pixel movement along the U axis.dY/dV 0Is the initial vertical partial first derivative. It indicates thedisplacement along the Y axiscorresponding to each one-pixel step along the V axis. Since dX/dV 0 and dY/dV 0 are separate parameters, vertical magnification and reflection need not match their horizontal counterparts.d 2X/dU 2Is the second order horizontal derivative. It indicates the rate of change of the horizontal-horizontal first derivative with each step along a line in the output image space. All six second-order derivatives are 4-bit integer, 20-bit fractional two's complement parameters.d 2X/dV 2Is the second order horizontal-vertical-vertical derivative. Itindicates the rate of change of the horizontal-vertical first derivative with each step down a column in the output image space.TMC2301PRODUCT SPECIFICATIONIn single-pass operation, the device walks through the entire (k + 1) x (k + 1) kernel for each output pixel, where k is the value written into the Kernel section (see below) of the parameter register. Two-pass operation, which requires a dimensionally separable kernel, is executed first for a (k + 1) element kernel in one direction, then for a (k + 1) element kernel in the other direction. For kernel sizes exceeding 2 x 2, the two-pass algorithm is obviously beneficial, requir-ing 2n samples per output point instead of n x n. In this case, the intermediate image data stored in the destination image memory following the first pass is used as the source image data on the second pass. The user may design a system tod 2Y/dU 2Is the second order vertical-horizontal-horizontal derivative. It indicates the rate of change of the the vertical-horizontal first derivative with each step along a line of the output image space.d 2Y/dV 2Is the second order verticalderivative. It indicates the rate of change of the vertical-vertical first derivative with each step down a column of the output image space.d 2X/dUdVIs the mixed second order derivative indicating the rate of change of the first order horizontal derivative as one proceeds downwards through the output image space. This is also the rate of change of the first order horizontal-vertical derivative during horizontal sweeps in the output image space.d 2Y/dUdVIs the mixed second order derivative indicating the rate of change of the first order vertical derivative as one moves horizontally across the output space, or, equivalently, the rate of change of the first order vertical-horizontal derivative as one moves vertically in the output image space Row/Column Select Sets the mode to either Row (0) or Column (1) operation.ModeThis 2-bit control word defines three unique instructions:Code Instruction00, 01single-pass operation 10pass 1 of two-pass operation11pass 2 of two pass operationswitch source and destination memory bank addresses in place, or could utilize a second TMC2301 pair in a pipelined architecture. This would require a third image buffer for the final destination image. Both devices of a system pair are usually set to the same mode.KernelThe effective kernel width (height)exceeds this 4-bit unsigned number by 1, thereby providing kernels of 1 x 1 to 16 x 16 source pixels per output, for either resampling or filtering. Simple static filters can be implemented with kernels of up to 16 x 16 pixels (Kernel = 15), while resampling interpolationkernels are limited to 4 x 4 pixels (Kernel = 3), due to the four bits of fractional X (or Y) address generated by the TMC2301. See the Applications Discussion. Again, both devices in a pair are generally initialized with equal Kernel values.Field of View (FOV)As the device walks through its kernel coefficients, each corresponding step in (x, y) space is normally one pixel length or height; this is a field of view of 1. However, the user can subsample the original space before filtering orresampling, by applying the coefficient kernel over a view field of up to 7 units. At a field of view of F, the pixels selected for each kernel operation are F pixels apart. This is useful in oversampled pictures, whose intensity changes only slowly from pixel to pixel.Autoload (ALR)When set to 1 (HIGH), the LDR control is automatically asserted when INIT is strobed, loading the coefficient setcurrently stored in the preload registers.Autoinit (AIN)At the end of an image, if the AIN bit is 1 (HIGH) the DONE flag goes HIGH for one clock cycle and a new transform begins. If 0 (LOW), UWRI and the DONE flag remain HIGH during the sequence until the user strobes the INIT control to begin a new image transformation.Pipe (PIPE)Adjusts the timing of the target memory write controls, to compensate forbuffered source image RAM. If the PIPE bit is 1 (HIGH), outputs ACC and UWRI will be delayed one clock cycle relative to the generation of the target address (U or V). See Figure 9.PRODUCT SPECIFICATION TMC2301Test Mode (TM)This mode is available for user inspectionof the coefficient data. The source imageand coefficient addresses are calculatedby an internal 28-bit accumulator. WhenTM is 1 (HIGH), the sign bit, normallydiscarded, and the lower 11 bits ofinternal data are substituted for the upper12 bits appearing at the source addressport (X) during a standard transformcycle. This allows user verification ofalgorithm mathematics during debug.Since the TM bit is registered and cannotbe changed during a single clock cycle,two distinct clock cycles are required toaccess both the MSW and LSW of theinternal accumulator. See Figure 3.Figure 3. Test Mode Data RoutingTMC2301PRODUCT SPECIFICATIONTable 3. Parameter Registers Binary Format (Row or Column Sequencer)Notes:1.* unsigned binary notation2. A “–” indicates MSB is sign bitAddress FormatLimitsMSB LSB Dec Hex 0000*2112102928272625242322212040950FFF 0000001*2112102928272625242322212040950FFF 0000010001126252423222120–2122-12112-22102-3292-4282-5274096-2-5-40960FFF .F8F000.000011 (Control)ALR AIN PIPE R/C M 1M 0010001012-12-22-32-42-5-272-6262-7252-8242-9232-10222-11212-1220128-2-12-128007F .FFF FF80.0000101* (TM, FOV)TM 222120*********-12-22-32-42-5-272-6262-7252-8242-9232-10222-11212-1220128-2-12-128007F .FFF FF80.0000111* (Kernel)23222120150f 010*******-9-232-10222-11212-12202-132-12-142-22-152-32-162-42-172-52-182-62-192-72-102-88-2-20-80007.FFFFF101010112-9-232-10222-11212-12202-132-12-142-22-152-32-162-42-172-52-182-62-192-72-102-88-2-20-80007.FFFFF110011012-9-232-10222-11212-12202-132-12-142-22-152-32-162-42-172-52-182-62-192-72-102-88-2-20-80007.FFFFF1110*2112102928272625242322212040950FF 0001111*2112102928272625242322212040950FF 000Internal Bit Mapping (For parametric inputs, integers in table are bits of P , the input point)212211210292827262524232221202-12-22-32-4X OUT [11:0]1110987654321C ADN [7:4]7654XMAX, XMIN 11109876543210X O5432101110987654321DX/DU, DX/DV 76543210111098D 2X/DUDV, D 2X/DU 2,D 2X/DV 211109876542-52-62-72-82-92-102-112-122-132-142-152-162-172-182-192-20X OUT [11:0]C ADN [7:4]XMAX, XMIN X O0DX/DU, DX/DV 76543210D 2X/DUDV, D 2X/DU 2,D 2X/DV 23211110987654321Equivalent Circuits and Transition LevelsFigure 5. Equivalent Input Circuit Figure 6. Equivalent Output CircuitFigure 7. Transition Level for Three-State OutputAbsolute Maximum Ratings (beyond which the device may be damaged)1Parameter Min Typ Max Unit Supply Voltage-0.57.0V Input Voltage-0.5V DD + 0.5V OutputApplied Voltage2-0.5V DD + 0.5V Forced Current3,4-1.0 6.0mA Short Circuit Duration (single output in HIGH state to ground)1sec TemperatureOperating, Case-60130°C Operating, Junction175°C Lead Soldering (10 seconds)300°C Storage-65150°CNotes:1.Absolute maximum ratings are limiting values applied individually while all other parameters are within specified operatingconditions. Functional operation under any of these conditions is NOT implied.2.Applied voltage must be current limited to specified range, and measured with respect to GND.3.Forcing voltage must be limited to specified range.4.Current is specified as conventional current flowing into the device.Operating ConditionsParameter Min Typ Max UnitsV DD Supply Voltage 4.75 5.0 5.25VV IL Input Voltage, Logic LOW0.8VV IH Input Voltage, Logic HIGH 2.0VI OL Output Current, Logic LOW8.0mAI OH Output Current, Logic HIGH-4.0mAT A Ambient Temperature, Still Air070°CT C Case Temperature°CDC Characteristics within specified operating conditions 1Notes:1.Actual test conditions may vary from those shown, but guarantee operation as specified.2.Guaranteed but not tested.AC Characteristics within specified operating conditionsNotes:1.t S + t D(E) = t CY max.2.Excluding output pin END.Parameter ConditionsMinMax Units I DDQ Supply Current, Quiescent V DD = Max, V IN = 0V 5mA I DDU Supply Current, Unloaded V DD = Max, f = 15MHz 75mA I IL Input Current, Logic LOW V DD = Max, V IN = 0V -1010µA I IH Input Current, Logic HIGH V DD = Min, V IN = V DD -1010µA V OL Output Voltage, Logic LOW V DD = Min, I OL = Max 0.4V V OH Output Voltage, Logic HIGH V DD = Min, I OH = Max 2.4V I OZL Hi-Z Output Leakage Current, Output LOWV DD = Min, V IN = 0V -4040µA I OZH Hi-Z Output Leakage Current, Output HIGHV DD = Min, V IN = V DD-4040µA I OS Short-Circuit Output Current 2V DD = Max, Output HIGH, one pin to ground, one second duration max.-100mA C I Input Capacitance T A = 25°C, f = 1MHz 10pF C OOutput CapacitanceT A = 25°C, f = 1MHz10pFParameter Conditions -2-1Min Max UnitMin Max Min Max t CY Cycle TimeV DD = Min 505566ns t PWL Clock Pulse Width LOW V DD = Min 202225ns t PWH Clock Pulse Width HIGH V DD = Min252833ns t S Input Setup Time 1151820ns t H Input Hold Time 122ns t H(I)Input Hold Time, INTER 81010ns t D Output Delay 2V DD = Min, C LOAD = 40pF 252735ns t D(E)Output Delay, END 1V DD = Min, C LOAD = 10pF 353745ns t HO Output Hold Time 2V DD = Max, C LOAD = 40pF 555ns t HO(E)Output Hold Time, END V DD = Max, C LOAD = 10pF 101010ns t DIS Three-State Disable Delay V DD = Min, C LOAD = 40pF 252735ns t ENAThree-State Enable DelayV DD = Min, C LOAD = 40pF252735nsApplications DiscussionBasic OperationEach TMC2301 pair contains address controllers which exe-cute patterns much like the following FORTRAN 3-level nested DO loop:1.The inner loop is a clockwise outgoing spiral "walk"through the N-element coefficient kernel.2.The middle loop is a left-to-right "scan" along each rowof the output image space.3.Finally, the outer loop is a top-to-bottom "scan" downeach column of the output image space.A typical one pass image transformation proceeds as follows:1.The device pair outputs the addresses (X0, Y0), which isthe first point in the source image, and (CAX, CAY), the interpolation lookup table address for the first pixel inthe kernel. The output ACC goes LOW, causing theexternal accumulator to load the first product withoutsummation, clearing the accumulator.2.For the next N cycles, the IRS walks through an outwardclockwise spiral in (x, y) space, accumulating pixel-interpolation coefficient products. The spiral sequence is depicted in Figure 8.3.After the completion of the first spiral walk, the IRS out-puts the target address of the first pixel, (UMIN, VMIN) and the control UWRI, along with the initial (X, Y) val-ues of the next spiral walk. ACC and UWRI can bedelayed by one clock cycle by setting the control bitPIPE to 1 (HIGH) simplifying the task of interfacing the TMC2301 to buffered source image memory.4.After the last cycle of the next spiral, UWRI again goesLOW for one clock, and the target address outputs areupdated, pointing to the location of the pixel calculation just completed, (UMIN + 1, VMIN).5.The third spiral walk begins with ACC going LOW, andends with (UMIN + 2, VMIN) output and UWRI going LOW.6.The procedure continues until (UMAX + 1, VMIN) isreached, at which point the device resets to U (position within row) and increments V (number of row). Thus,the next (U, V) set after (UMAX + 1, VMIN) will be(UMIN, VMIN + 1), followed by (UMIN + 1,VMIN + 1), etc.7.Upon completion of the walk corresponding to(UMAX + 1, VMAX + 1), the TMC2301 will generate a DONE flag with the final UWRI, and begin a newsequence.On any given clock cycle, the actual (X, Y) and (U, V) out-puts of the IRS are given by the following equations:x = X0 + dX/dU0 * m + dX/dV0 * n + d2X/dUdV * m * n + d2X/dU2 * (m2 – m)/2 + d2X/dV2 * (n2 – n)/2+ FOV * CAX(w) + FOV * m * CAX(Ker)y = Y0 + dY/dU0 * m + dX/dV0 * n + d2Y/dUdV * m * n + d2Y/dU2 * (m2 – m)/2 + d2Y/dV2 * (n2 – n)/2+ FOV * CAY(w) + FOV * m * CAY(Ker)u = UMIN + mv = VMIN + nwhere FOV is the 4-bit field of view parameter, normally set to 1 so that the spiral walk proceeds in single-pixel steps. Setting FOV to 4 would expand the spiral walk, allowing the user to trade two bits of image size for two bits of additional interpixel positioning resolution. CAX(w) and CAY(w) are the current value of the coefficient address outputs and CAX(KER) and CAY(KER) are the terminal values of each pixel walk. The CA(KER) terms arise because the IRS com-putes each new walk's starting paint from the previous spiral walk's end point rather than its starting point. Interpolation Coefficient Lookup Table AddressingThe external coefficient lookup table RAM stores the inter-polation values used to calculate the value of the new pixel. These values are selected by the user allowing maximum fil-tering flexibility. In simple filtering applications, all 8 bits of coefficient address are available to access up to 256 interpo-lation coefficients, for kernels of 16 x 16 pixels. This address is generated by the internal walk counter of the TMC2301. In most applications, the same Kernel parameter value is selected in both IRS devices; thus, the Coefficient Address outputs CA7-0 for the X and Y devices are identical, and the user needs only one of the 8-bit buses for memory access. Applications executing a coordinate transformation, however will almost always generate non-integer source pixel addresses; that is the U (or V) locations will not map to the X (or Y) addresses exactly and fractional address components are generated. The user then must account for this spatial off-set in both dimensions by storing the appropriate corrected interpolation kernel values in the lookup table. The 8-bit address bus is broken up into two parts: the fractional portion (upper 4 bits), and the walk counter (lower 4 bits). Thus, in resampling applications, the maximum kernel size is 4 x 4 pixels, or 16 locations. As in the filtering example, assuming that the user has selected the same kernel size for both IRS devices, the 4 bits of least-significant address generated by both devices will be identical and redundant. The four most significant address bits, however, will reflect the current frac-tional offsets of the resampled pixel from the nearest X (Y) location, to a spatial resolution of 4 bits in the X (or Y) direc-tions. Utilization of the 12 bits (total) of lookup table address is left to the user to be arranged as desired for memory access. See Figure 3.Application ExamplesOne of the more common applications for the TMC2301 is simple static filtering In this case the source and target mem-ories locations are identical and no coordinate transforma-tion is performed. The (X, Y) and (U, V) outputs listed in Table 4 show the address sequencing generated by the TMC2301 to execute the walk of a 5 x 5 pixel interpolation kernel. The normalized coefficients shown implement a first-order Butterworth Low Pass Filter with cutoff radius of1/. Note that the (U, V) output address is updated follow-ing the completion of the walk for that location.Figure 9. Pixel Map Showing Walk Sequencefor 5x5 Static Filter2。

场效应管的代替型号

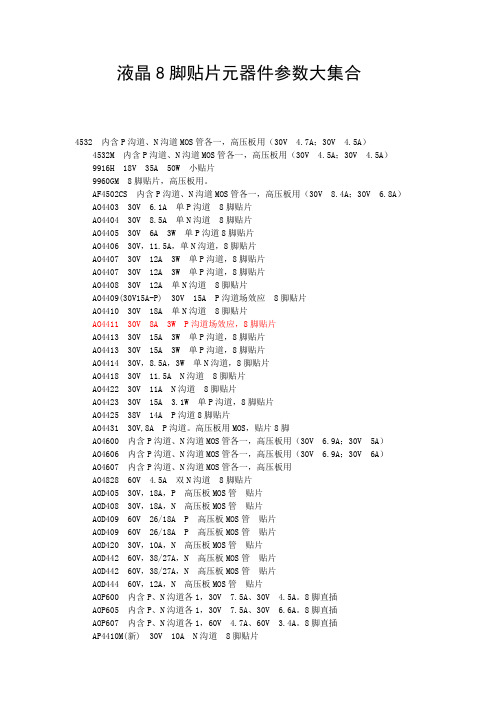

液晶 8 脚贴片元器件参数大集合

4532 内含 P 沟道、N 沟道 MOS 管各一,高压板用(30V 4.7A;30V 4.5A)

4532M 内含 P 沟道、N 沟道 MOS 管各一,高压板用(30V 4.5A;30V 4.5A)

AO4409(30V15A-P) 30V 15A P 沟道场效应 8 脚贴片

AO4410 30V 18A 单 N 沟道 8 脚贴片

AO4411 30V 8A 3W P 沟道场效应,8 脚贴片

AO4413 30V 15A 3W 单 P 沟道,8 脚贴片

AO4413 30V 15A 3W 单 P 沟道,8 脚贴片

9916H 18V 35A 50W 小贴片 9960GM 8 脚贴片,高压板用。

AF4502CS 内含 P 沟道、N 沟道 MOS 管各一,高压板用(30V 8.4A;30V 6.8A)

AO4403 30V 6.1A 单 P 沟道 8 脚贴片 AO4404 30V 8.5A 单 N 沟道 8 脚贴片

TPC8401 内含 P 沟道、N 沟道 MOS 管各一,高压板用(30V 4.5A;30V 4.5A)

AP1501/AP1506 , 3A 降压 DC/DC ,直接替换 LM2576/LM2596 ,广泛应用于车载 DVD ,车载音响, LCD/LCM ; AP1507 , 3A 降压 DC/DC ,替换 SHARP PQ1CZ21 , PQICZ41 , PQ1CG21 。应用于车 载 DVD ,车载音响; AP1509 , 2A 降压 DC/DC 。替换 MP1410 ;应用于 DVD 译码版,网络产品; AP2001 , CCFL 驱动 IC ,

APM2301A中文资料

ANPEC reserves the right to make changes to improve reliability or manufacturability without notice, and advise customers to obtain the latest version of relevant information to verify before placing orders.Pin DescriptionOrdering and Marking InformationFeaturesApplicationsAbsolute Maximum Ratings (T A = 25°C unless otherwise noted)• -20V/-2.8A , R DS(ON)=72m Ω(typ.) @ V GS =-10VR DS(ON)=100m Ω(typ.) @ V GS =-4.5V• Super High Dense Cell Design for ExtremelyLow R DS(ON)• Reliable and Rugged • SOT-23 Package• Power Management in Notebook Computer ,Portable Equipment and Battery Powered Systems.* Surface Mounted on FR4 Board, t ≤ 10 sec.G DSTop View of SOT-23Notesa : Pulse test ; pulse width ≤300µs, duty cycle ≤ 2%b: Guaranteed by design, not subject to production testingAbsolute Maximum Ratings Cont. (T A = 25°C unless otherwise noted)Electrical Characteristics (T A = 25°C unless otherwise noted)2468100.0300.0450.0600.0750.0900.1050.1200.1350.150012345246810-50-2502550751001251500.000.250.500.751.001.251.500.00.5 1.0 1.5 2.0 2.50246810Typical Characteristics-I D -D r a i n C u r r e n t (A )Transfer Characteristics-V GS - Gate-to-Source Voltage (V)Threshold Voltage vs. Junction T emperatureTj - Junction T emperature (°C)-V G S (t h )-T h r e s h o l d V o l t a g e (V )(N o r m a l i z e d )R D S (O N )-O n -R e s i s t a n c e (Ω)On-Resistance vs. Drain Current-I D - Drain Current (A)Output Characteristics-I D -D r a i n C u r r e n t (A )-V DS - Drain-to-Source Voltage (V)369121505101520-50-25025507510012515012345678910Typical CharacteristicsR D S (O N )-O n -R e s i s t a n c e (Ω)(N o r m a l i z e d )On-Resistance vs. Junction TemperatureT J - Junction Temperature (°C)-V DS - Drain-to-Source Voltage (V)CapacitanceC a p a c i t a n c e (p F )-V GS - Gate-to-Source Voltage (V)R D S (O N )-O n -R e s i s t a n c e (Ω)On-Resistance vs. Gate-to-Source VoltageGate ChargeQ G - Gate Charge (nC)-V G S -G a t e -S o u r c e V o l t a g e (V )0.00.20.40.60.8 1.0 1.2 1.4 1.61100.010.1110100024681012141E-41E-30.010.11101000.010.11Typical CharacteristicsP o w e r (W )Single Pulse PowerTime (sec)Square Wave Pulse Duration (sec)Source-Drain Diode Forward Voltage-I S -S o u r c e C u r r e n t (A )-V SD -Source-to-Drain Voltage (V)N o r m a l i z e d E f f e c t i v e T r a n s i e n t T h e r m a l I m p e d a n c eNormalized Thermal Transient Impedence, Junction to AmbientPackaging Information SOT-23Physical SpecificationsReflow Condition (IR/Convection or VPR Reflow)Reference JEDEC Standard J-STD-020A APRIL 1999Classification Reflow ProfilesPackage Reflow ConditionsPre-heat temperature183 CPeak temperatureTime°t e m p e r a t u r eReliability test programCarrier Tape & Reel DimensionsCover Tape DimensionsCustomer ServiceAnpec Electronics Corp.Head Office :5F, No. 2 Li-Hsin Road, SBIP,Hsin-Chu, T aiwan, R.O.C.T el : 886-3-5642000Fax : 886-3-5642050Taipei Branch :7F, No. 137, Lane 235, Pac Chiao Rd.,Hsin Tien City, Taipei Hsien, T aiwan, R. O. C.T el : 886-2-89191368Fax : 886-2-89191369。

液晶8脚贴片元器件参数大集合

液晶8脚贴片元器件参数大集合4532 内含P沟道、N沟道MOS管各一,高压板用(30V 4.7A;30V 4.5A)4532M 内含P沟道、N沟道MOS管各一,高压板用(30V 4.5A;30V 4.5A)9916H 18V 35A 50W 小贴片9960GM 8脚贴片,高压板用。

AF4502CS 内含P沟道、N沟道MOS管各一,高压板用(30V 8.4A;30V 6.8A) AO4403 30V 6.1A 单P沟道 8脚贴片AO4404 30V 8.5A 单N沟道 8脚贴片AO4405 30V 6A 3W 单P沟道8脚贴片AO4406 30V,11.5A,单N沟道,8脚贴片AO4407 30V 12A 3W 单P沟道,8脚贴片AO4407 30V 12A 3W 单P沟道,8脚贴片AO4408 30V 12A 单N沟道 8脚贴片AO4409(30V15A-P) 30V 15A P沟道场效应 8脚贴片AO4410 30V 18A 单N沟道 8脚贴片AO4411 30V 8A 3W P沟道场效应,8脚贴片AO4413 30V 15A 3W 单P沟道,8脚贴片AO4413 30V 15A 3W 单P沟道,8脚贴片AO4414 30V,8.5A,3W 单N沟道,8脚贴片AO4418 30V 11.5A N沟道 8脚贴片AO4422 30V 11A N沟道 8脚贴片AO4423 30V 15A 3.1W 单P沟道,8脚贴片AO4425 38V 14A P沟道8脚贴片AO4431 30V,8A P沟道。

高压板用MOS,贴片8脚AO4600 内含P沟道、N沟道MOS管各一,高压板用(30V 6.9A;30V 5A)AO4606 内含P沟道、N沟道MOS管各一,高压板用(30V 6.9A;30V 6A)AO4607 内含P沟道、N沟道MOS管各一,高压板用AO4828 60V 4.5A 双N沟道 8脚贴片AOD405 30V,18A,P 高压板MOS管贴片AOD408 30V,18A,N 高压板MOS管贴片AOD409 60V 26/18A P 高压板MOS管贴片AOD409 60V 26/18A P 高压板MOS管贴片AOD420 30V,10A,N 高压板MOS管贴片AOD442 60V,38/27A,N 高压板MOS管贴片AOD442 60V,38/27A,N 高压板MOS管贴片AOD444 60V,12A,N 高压板MOS管贴片AOP600 内含P、N沟道各1,30V 7.5A、30V 4.5A。

AP2301N中文资料

Advanced Power P-CHANNEL ENHANCEMENT MODE Electronics Corp.POWER MOSFET▼Simple Drive Requirement BV DSS-20V▼Small Package Outline R DS(ON)130mΩ▼Surface Mount Device I D- 2.6ADescriptionAbsolute Maximum RatingsSymbol UnitsV DS VV GS VI D@T A=25℃AI D@T A=70℃AI DM AP D@T A=25℃WW/℃T STG℃T J℃Symbol Value Unit Rthj-a Thermal Resistance Junction-ambient3Max.90℃/WData and specifications subject to change without notice200407043AP2301NRating- 20± 12-2.60.011.38-55 to 150ParameterDrain-Source VoltageGate-Source VoltageContinuous Drain Current3Continuous Drain Current3-2.1Pulsed Drain Current1,2-10ParameterTotal Power DissipationOperating Junction Temperature RangeStorage Temperature Range-55 to 150Linear Derating FactorThermal DataThe Advanced Power MOSFETs from APEC provide thedesigner with the best combination of fast switching,, low on-resistance and cost-effectiveness.The SOT-23 package is universally preferred for all commercial-industrial surface mount applications and suited for low voltageapplications such as DC/DC converters.DGSSOT-23AP2301NElectrical Characteristics@T j=25o C(unless otherwise specified) Symbol Parameter Test Conditions Min.Typ.Max.UnitsBV DSS Drain-Source Breakdown Voltage V GS=0V, I D=-250uA-20--V ΔB V DSS/ΔT j Breakdown Voltage Temperature Coefficient Reference to 25℃, I D=-1mA--0.1-V/℃R DS(ON)Static Drain-Source On-Resistance2V GS=-5V, I D=-2.8A--130mΩV GS=-2.8V, I D=-2.0A--190mΩV GS(th)Gate Threshold Voltage V DS=V GS, I D=-250uA-0.5--V g fs Forward Transconductance V DS=-5V, I D=-2.8A- 4.4-S I DSS Drain-Source Leakage Current (Tj=25o C)V DS=-20V, V GS=0V---1uA Drain-Source Leakage Current (T j=70o C)V DS=-16V, V GS=0V---10uAI GSS Gate-Source Leakage VGS=±12V--nA Q g Total Gate Charge2I D=-2.8A- 5.210nC Q gs Gate-Source Charge V DS=-6V- 1.36-nC Q gd Gate-Drain ("Miller") Charge V GS=-5V-0.6-nC t d(on)Turn-on Delay Time2V DS=-15V- 5.2-ns t r Rise Time I D=-1A-9.7-ns t d(off)Turn-off Delay Time R G=6Ω,V GS=-10V-19-ns t f Fall Time R D=15Ω-29-ns C iss Input Capacitance V GS=0V-295-pF C oss Output Capacitance V DS=-6V-170-pF C rss Reverse Transfer Capacitance f=1.0MHz-65-pF Source-Drain DiodeSymbol Parameter Test Conditions Min.Typ.Max.Units I S Continuous Source Current ( Body Diode )V D=V G=0V , V S=-1.2V---1A I SM Pulsed Source Current ( Body Diode )1---10A V SD Forward On Voltage2T j=25℃, I S=-1.6A, V GS=0V---1.2VNotes:1.Pulse width limited by Max. junction temperature.2.Pulse width <300us , duty cycle <2%.3.Surface mounted on 1 in2 copper pad of FR4 board ; 270℃/W when mounted on min. copper pad.±100Fig 1. Typical Output Characteristics Fig 2. Typical Output CharacteristicsFig 3. On-Resistance v.s. Gate Voltage Fig 4. Normalized On-ResistanceFig 5. Forward Characteristic ofFig 6. Gate Threshold Voltage v.s.Reverse DiodeJunction TemperatureAP2301NFig 7. Gate Charge Characteristics Fig 8. Typical Capacitance CharacteristicsFig 9. Maximum Safe Operating Area Fig 10. Effective Transient Thermal ImpedanceFig 11. Switching Time Waveform Fig 12. Gate Charge Waveform。

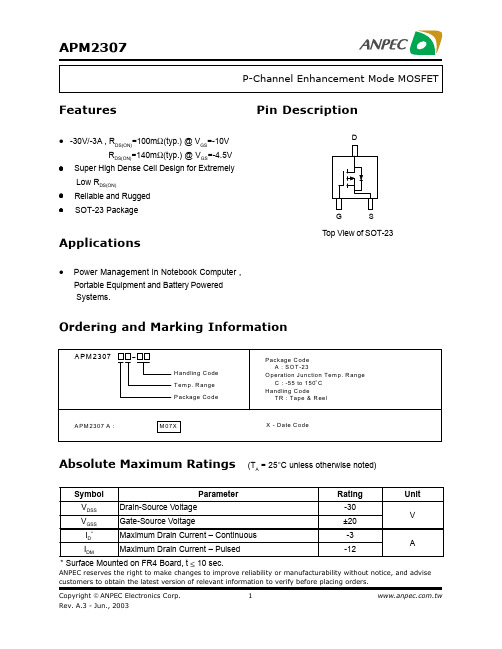

APM2307中文资料

ANPEC reserves the right to make changes to improve reliability or manufacturability without notice, and advise customers to obtain the latest version of relevant information to verify before placing orders.Pin DescriptionOrdering and Marking InformationFeaturesApplicationsAbsolute Maximum Ratings (T A = 25°C unless otherwise noted)• -30V/-3A , R DS(ON)=100m Ω(typ.) @ V GS =-10VR DS(ON)=140m Ω(typ.) @ V GS =-4.5V• Super High Dense Cell Design for ExtremelyLow R DS(ON)• Reliable and Rugged • SOT-23 Package• Power Management in Notebook Computer ,Portable Equipment and Battery Powered Systems.* Surface Mounted on FR4 Board, t ≤ 10 sec.G DSTop View of SOT-23Notesa : Pulse test ; pulse width ≤300µs, duty cycle ≤ 2%b: Guaranteed by design, not subject to production testingAbsolute Maximum Ratings Cont. (T A = 25°C unless otherwise noted)Electrical Characteristics (T A = 25°C unless otherwise noted)01234524681002468102468100123456780.000.050.100.150.200.250.30-50-2502550751001251500.000.250.500.751.001.251.50Typical Characteristics-I D -D r a i n C u r r e n t (A )Transfer Characteristics-V GS - Gate-to-Source Voltage (V)Threshold Voltage vs. Junction T emperatureTj - Junction T emperature (°C)-V G S (t h )-T h r e s h o l d V o l t a g e (V )(N o r m a l i z e d )R D S (O N )-O n -R e s i s t a n c e (Ω)On-Resistance vs. Drain Current-I D - Drain Current (A)Output Characteristics-I D -D r a i n C u r r e n t (A )-V DS - Drain-to-Source Voltage (V)012345678123456789100510********-50-2502550751001251500.000.250.500.751.001.251.501.752.0002468100.00.10.20.30.40.5Typical CharacteristicsR D S (O N )-O n -R e s i s t a n c e (Ω)(N o r m a l i z e d )On-Resistance vs. Junction TemperatureT J - Junction Temperature (°C)-V DS - Drain-to-Source Voltage (V)CapacitanceC a p a c i t a n c e (p F )-V GS - Gate-to-Source Voltage (V)R D S (O N )-O n -R e s i s t a n c e (Ω)On-Resistance vs. Gate-to-Source VoltageGate ChargeQ G - Gate Charge (nC)-V G S -G a t e -S o u r c e V o l t a g e (V )1E-41E-30.010.11101000.010.110.00.20.40.60.8 1.0 1.2 1.40.1110Typical CharacteristicsP o w e r (W )Single Pulse PowerTime (sec)Square Wave Pulse Duration (sec)Source-Drain Diode Forward Voltage-I S -S o u r c e C u r r e n t (A )-V SD -Source-to-Drain Voltage (V)N o r m a l i z e d E f f e c t i v e T r a n s i e n t T h e r m a l I m p e d a n c eNormalized Thermal Transient Impedence, Junction to Ambient0.010.1110100024681012500500Packaging Information SOT-23Physical SpecificationsReflow Condition (IR/Convection or VPR Reflow)Reference JEDEC Standard J-STD-020A APRIL 1999Classification Reflow ProfilesPackage Reflow ConditionsPre-heat temperature183 CPeak temperatureTime°t e m p e r a t u r eReliability test programCarrier Tape & Reel DimensionsCover Tape DimensionsCustomer ServiceAnpec Electronics Corp.Head Office :5F, No. 2 Li-Hsin Road, SBIP,Hsin-Chu, T aiwan, R.O.C.T el : 886-3-5642000Fax : 886-3-5642050Taipei Branch :7F, No. 137, Lane 235, Pac Chiao Rd.,Hsin Tien City, Taipei Hsien, T aiwan, R. O. C.T el : 886-2-89191368Fax : 886-2-89191369。

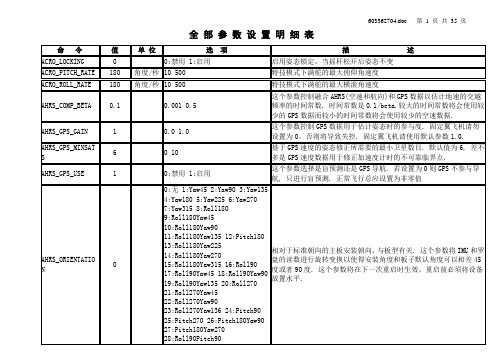

APM全部参数表

1.9936 0

ARSPD_TUBE_ORDE R

2

ARSPD_USE

0

AUTO_FBW_STEER

0

0:禁用 1:启用

AUTOTUNE_LEVEL BATT_AMP_OFFSET BATT_AMP_PERVOL T BATT_CAPACITY BATT_CURR_PIN BATT_MONITOR BATT_VOLT_MULT

AHRS_YAW_P

0.2

0.1 0.4

ALT_CTRL_ALG

0

0:自动

ALT_HOLD_FBWCM

0

厘米

ALT_HOLD_RTL

10000

厘米

ALT_MIX

1

百分比 0 1

603362704.doc

第 3 页 共 35 页

空开启的 GPS, 例如你在离地几千米的地方从气球上抛下一个飞机 时. ALT_OFFSET 0 米 -32767 32767 这是在自动飞行模式下加入到目标高度数值的高度偏移量. 这可以 用来在自动模式中加入全球高度偏移

603362704.doc

第 4 页 共 35 页

ARSPD_PIN

0

空速计连接到的模拟 IO 口. 设置这个参数为 0-9 来对应 APM2 的模拟 引脚. 使用 APM1 时设置为 64,对应于板子末端的空速计接口. 使用 PX4 时设为 11,对应于模拟空速计接口. 使用 Pixhawk 时设为 15, 对应于模拟空速计接口. 使用 EagleTree 或 MEAS I2C 空速计的 PX4 或者 Pixhawk,设置为 65. 空速计校准后的比率 这个参数允许你在皮托管里的连接顺序有影响时选择. 如果设置为 0 则顶部连接的传感器是动态压强. 如果设置为 1 则底部连接的传感 器是动态压强. 若设为 2(默认)则空速管驱动器将会接受任意一种 顺序.你可能想要指定顺序的原因在于它能够使你的空速计检测飞行 器是不是受到了过大的静压强,而这可能被解读成正空速. 1:使用 0:不使用 使用空速数据进行飞行控制 开启此项将使得在自动模式中可以使用 FBWA 的方式进行操控. 这可 以用来执行带有航点逻辑的人工增稳飞行,或可用于载荷[译注:即 飞的时候知道航点,一个个航点飞过去]. 启用后飞行员拥有和 FBWA 模式中一样的操控, 但普通的自动模式导航被完全禁用. 寻常情况 不推荐这个选项. 自动调参的激烈程度. 在较低等级的 AUTOTUNE_LEVEL 上自动调参较 为柔和, 增益较小. 对于大多数用户而言推荐 5 级. 在 0 电流情况下传感器的电压读数偏移值 当电流传感器读数为 1V 时转换得到的电流值. 对于使用 3DR 电源模 块的 APM2 或者 Pixhwak 这个值必须为 17. 对于使用 3DR 四合一电调 的 Pixhawk 这个值必须为 17. 满电电池的容量,以 mAh 计 -1:禁 用 1:A1 12:A12 2:A2 3:Pixhawk 101:PX4 设置这个参数为 0 至 13 将指定电池电流传感器的管脚对应于 A0 至 A13. 对于 APM2.5 的电源模块,这个值必须为 12. 在 PX4 上这个值 必须为 101. 对于使用电源模块的 Pixhawk 这个值必须为 3. 控制电池电流或电压监控 用来将电压传感器管脚检测到的电压值(BATT_VOLT_PIN)转换成实际 电压值(管脚电压*VOLT_MULT). 对于 APM2 或者 Pixhawk 的 3DR 电源

2301A产品简介

2301A 外形尺寸

执行器信号 0-200mA,标准,30-45Ω 温度限制 操作温度:-40ºC 至+85ºC 存放温度:-55ºC 至+105ºC 湿度限制 38ºC 时 95% 振动和冲击 可承受 5Hz 和 500Hz,4 倍于重力加速度的振动和 60 倍于重力加速度的冲击。 稳态转速带宽 为额定转速的 1%的±0.25 当选用负载感应设备时,允许与速度设定相匹配的额定负载的±5%的负载分配精度。

速度微调 外接一个电位计或数字式速度设定单 元,可以对原动机的速度进行远程微 调。

最小燃料控制 控制器上接一个开关可对原动机进行 最小燃料控制。此开关可用于一般的 停机操作。

转速信号失效保护电路 2301A 速度控制器通常监测速度传感 器信号。当速度信号低于某一设定最 小值时,控制器发出一最小燃油信号 给执行器,使发动机停机。当发动机 为慢拖动起动方式时,起机时外接一 个触点开关可以暂时取消速度信号失 效保护功能。

说明

速度范围 每个开关位对应一定的速度范围,共有四种范 围可选择:(基于速度齿盘的信号频率)

500-1500Hz 2000-6000Hz 1000-3000Hz 4000-12000Hz

速度感应 有效幅值:1~30Vac 。最大负载为:1KΩ/ 1Khz

外部速度微调 使用 100Ω 电位计速度调整量为:±5%

产品说明

82021Dcn

2301A 速度控制器

• 电源模式:低 压及高压型

应用

2301A 速度控制器用于柴油机、气体 发动机、蒸汽轮机及燃气轮机的速度 或负载控制。 2301A 提供等速模式的控制,通过外 接电位计也可进行有差调节。只要原 动机产生的功率满足负载的需要,等 速控制模式就可以保证原动机恒速运 行。 2301A 速度控制器与 Woodward SPMA 同步器、负载感应器及其他发电用 控制器兼容。任何时刻,这些控制都 可通过输入附加信号或 SPM 信号加 入到 2301A 控制器系统。 控制器的输出有正向动作型和反向动 作型两种,可控制一个单独的或两个 串联的执行器。高压型模块电源电压 为:88-132Vac 或 90-150Vdc;低压型 模块电源电压为:10-40Vdc。 2301A 还具有 4-20mA 速度设定输入 功能(见产品说明 02301)。

APM2301中文资料

APM2301中文资料ANPEC reserves the right to make changes to improve reliability or manufacturability without notice, and advise customers to obtain the latest version of relevant information to verify before placing orders.Pin DescriptionOrdering and Marking InformationFeaturesApplicationsAbsolute Maximum Ratings (T A = 25°C unless otherwise noted)-20V/-2.8A , R DS(ON)=72m ?(typ.) @ V GS =-10VR DS(ON)=100m ?(typ.) @ V GS =-4.5VSuper High Dense Cell Design for ExtremelyLow R DS(ON)Reliable and Rugged ? SOT-23 PackagePower Management in Notebook Computer ,Portable Equipment and Battery Powered Systems.* Surface Mounted on FR4 Board, t ≤ 10 sec.G DSTop View of SOT-23Notesa : Pulse test ; pulse width ≤300μs, duty cycle ≤ 2%b: Guaranteed by design, not subject to production testingAbsolute Maximum Ratings Cont. (T A = 25°C unless otherwise noted)Electrical Characteristics (T A = 25°C unless otherwise noted) 2468100.0300.0450.0600.0750.0900.1050.1200.1350.150012345246810-50-2502550751001251500.000.250.500.751.001.251.500.00.5 1.0 1.5 2.0 2.50246810Typical Characteristics-I D -D r a i n C u r r e n t (A )Transfer Characteristics-V GS - Gate-to-Source Voltage (V)Threshold Voltage vs. Junction T emperatureTj - Junction T emperature (°C)-V G S (t h )-T h r e s h o l d Vo l t a g e (V )(N o r m a l i z e d )R D S (O N )-O n -R e s i s t a n c e (?)On-Resistance vs. Drain Current-I D - Drain Current (A)Output Characteristics-I D -D r a i n C u r r e n t (A )-V DS - Drain-to-Source Voltage (V)369121505101520-50-25025507510012515012345678910Typical CharacteristicsR D S (O N )-O n -R e s i s t a n c e (?)(N o r m a l i z e d )On-Resistance vs. Junction TemperatureT J - Junction Temperature (°C)-V DS - Drain-to-Source Voltage (V)CapacitanceC a p a c i t a n c e (p F )-V GS - Gate-to-Source Voltage (V)R D S (O N )-O n -R e s i s t a n c e (?)On-Resistance vs. Gate-to-Source Voltage Gate ChargeQ G - Gate Charge (nC)-V G S -G a t e -S o u r c e V o l t a g e (V )0.00.20.40.60.8 1.0 1.2 1.4 1.61100.010.1110100024681012141E-41E-30.010.11101000.010.11Typical CharacteristicsP o w e r (W )Single Pulse PowerTime (sec)Square Wave Pulse Duration (sec)Source-Drain Diode Forward Voltage-I S -S o u r c e C u r r e n t (A )-V SD -Source-to-Drain Voltage (V)N o r m a l i z e d E f f e c t i v e T r a n s i e n t T h e r m a l I m p e d a n c eNormalized Thermal Transient Impedence, Junction to AmbientPackaging Information SOT-23Physical SpecificationsReflow Condition (IR/Convection or VPR Reflow)Reference JEDEC Standard J-STD-020A APRIL 1999Classification Reflow ProfilesPackage Reflow ConditionsPre-heat temperature183 CPeak temperatureTime°t e m p e r a t u r eReliability test programCarrier Tape & Reel DimensionsCover Tape DimensionsCustomer ServiceAnpec Electronics Corp.Head Office :5F, No. 2 Li-Hsin Road, SBIP,Hsin-Chu, T aiwan, R.O.C.T el : 886-3-5642000Fax : 886-3-5642050Taipei Branch :7F, No. 137, Lane 235, Pac Chiao Rd.,Hsin Tien City, Taipei Hsien, T aiwan, R. O. C. T el : 886-2-89191368Fax : 886-2-89191369。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

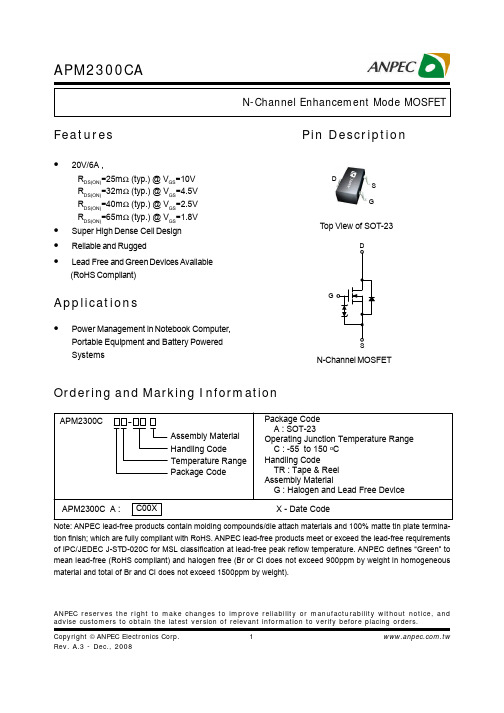

APM2301CA

ANPEC reserves the right to make changes to improve reliability or manufacturability without notice, and advise

customers to obtain the latest version of relevant information to verify before placing orders.Pin Description

Ordering and Marking Information

Features

Applications

•

-20V/-2.8A

R DS(ON)= 56m Ω (typ.) @ V GS = -4.5V R DS(ON)= 85m Ω (typ.) @ V GS = -2.5V R DS(ON)= 106m Ω (typ.) @ V GS = -1.8V

•Super High Dense Cell Design •

Reliable and Rugged

APM2301CA

Handling Code Temp. Range Package Code

Package Code A : SOT-23

Operating Junction Temp. Range

C : -55 to 150 C

Handling Code TR : Tape & Reel Lead Free Code

L : Lead Free Device Blank : Original Device APM2301CA:C01X

XXXXX - Date Code

Lead Free Code Note: ANPEC lead-free products contain molding compounds/die attach materials and 100% matte tin plate termination finish; which are fully compliant with RoHS and compatible with both SnPb and lead-free soldiering operations. ANPEC lead-free products meet or exceed the lead-free requirements of IPC/JEDEC J STD-020C for MSL classification at lead-free peak reflow temperature.

°•

Power Management in Notebook Computer,

Portable Equipment and Battery Powered Systems.

P Channel MOSFET

SOT-23

G

S

APM2301CA

Absolute Maximum Ratings (T A = 25°C Unless Otherwise Noted)

Electrical Characteristics (T A = 25°C Unless Otherwise Noted)

Notes: *Surface Mounted on 1in 2

pad area, t ≤ 10sec.

APM2301CA

Electrical Characteristics (Cont.) (T

= 25°C Unless Otherwise Noted)

A

Notes:

a : Pulse test ; pulse width≤300µs, duty cycle≤2%.

b : Guaranteed by design, not subject to production testing.

APM2301CA

Typical Characteristics

-I D - D r a i n C u r r e n t (A )

Drain Current

T j - Junction Temperature (°C)

Safe Operation Area

-V DS - Drain - Source Voltage (V)Thermal Transient Impedance

Square Wave Pulse Duration (sec)

Power Dissipation

P t o t - P o w e r (W )

T j - Junction Temperature (°C)

-I D - D r a i n C u r r e n t (A )

N o r m a l i z e d E

f f e c t i v e T r a n s i e n t 0

20

40

60

80100120140160

0.0

0.10.20.30.40.5

0.60.7

0.80.91.0

0.0

0.5

1.0

1.5

2.0

2.5

3.0

0.01

0.11

10100

0.010.1

1

10

50

1E-30.01

0.1

1

2

-50-250255075100125150 -V GS - Gate - Source Voltage (V)

T j - Junction Temperature (°C)

APM2301CA

-V DS - Drain - Source Voltage (V)

Drain-Source On Resistance

N o r m a l i z e d O n R e s i s t a n c e

T j - Junction Temperature (°C)

C - C a p a c i t a n c e (n C )

-I S - S o u r c e C u r r e n t (A )

Capacitance

Q G - Gate Charge (nC)

-V G S - G a t e - S o u r c e V o l t a g e (V )

Typical Characteristics (Cont.)

-50-25

25

50

75100125150

0.2

0.40.60.81.01.21.41.6

1.8

2.0

0.11

10

0100200300400500600

700

800

1

2

3

4

5

6

7

0.00.51.01.52.02.53.03.54.04.5

APM2301CA

Packaging Information SOT-23

Physical Specifications

APM2301CA

Reflow Condition

(IR/Convection or VPR Reflow)

T L

T P

25

T e m p e r a t u r e

Reflow Condition

Notes: All temperatures refer to topside of the package .Measured on the body surface.

APM2301CA

Reflow Condition

Reliability test program

Carrier Tape & Reel Dimensions

APM2301CA

Carrier Tape & Reel Dimensions (Cont.)

Cover Tape Dimensions

Customer Service

Anpec Electronics Corp.

Head Office :

No.6, Dusing 1st Road, SBIP,

Hsin-Chu, Taiwan, R.O.C.

Tel : 886-3-5642000

Fax : 886-3-5642050

Taipei Branch :

7F, No. 137, Lane 235, Pac Chiao Rd.,

Hsin Tien City, Taipei Hsien, Taiwan, R. O. C.

Tel : 886-2-89191368

Fax : 886-2-89191369。