基于PowerPC440处理器的网卡驱动的设计与实现

基于PowerPC的SATA固态硬盘存储阵列设计

基于PowerPC的SATA固态硬盘存储阵列设计孟琪;张杰;范晓星【摘要】设计了基于SATA接口的固态阵列存储系统.系统选用FPGA作为硬件平台,内嵌PPC440处理器作为处理单元,以SATA接口的固态硬盘阵列作为存储介质,并采用RAID0技术.该存储阵列系统具有海量、高带宽等特点.系统同时具有实时存储、传输和管理等功能,并可脱机运行.【期刊名称】《电子科技》【年(卷),期】2015(028)004【总页数】5页(P111-115)【关键词】FPGA;PPC440处理器;SATA接口;固态硬盘;RAID0【作者】孟琪;张杰;范晓星【作者单位】西安电子科技大学电子信息攻防对抗与仿真技术教育部重点实验室,陕西西安710071;西安电子科技大学电子信息攻防对抗与仿真技术教育部重点实验室,陕西西安710071;西安电子科技大学电子信息攻防对抗与仿真技术教育部重点实验室,陕西西安710071【正文语种】中文【中图分类】TN79在科研和生产中,往往需要记录实时性强的信息便于后续的分析处理。

随着科学技术的发展,高速、海量、能脱机的数据存储设备已成为工业和科研不可或缺的关键设备。

而目前市场上常见的硬盘、Flash等存储介质均不具有海量且高速的特点,无法满足需求。

因此研究一种同时具有高速传输、海量存储、能脱机运行等特点的数据存储设备具有重要意义。

磁盘阵列(RAID)基本思想是将多个相对便宜的硬盘组合,成为一个硬盘阵列组,使性能达到甚至超过一个价格昂贵、容量巨大的硬盘性能。

RAID由多个硬盘组成,通过在多个硬盘上同时存储数据来大幅度提高存储系统的数据吞吐量。

固态硬盘(SSD)是一种基于闪存的存储技术。

与普通磁盘相比,固态硬盘由半单体存储器构成,没有移动的部件,因而随机访问的时间比旋转磁盘要快,能耗更低,同时也更结实。

不过,SSD也有一些缺点。

首先,因为反复写之后,闪存块会磨损,所以SSD也容易磨损。

其次,SSD的价格较高。

基于PowerPC440GP型微控制器的嵌入式系统设计与研究

关

键

词: 简指 令 集计算机 (IC ; Pw rC 4 G ; V Wok S ; B o O 精 RS ) o eP 4 0 P x rsB P ot M R

文献 标识 码 : A 文章 编号 :0 6 6 7 (0 6 0 — o 7 0 l o — 9 7 2 o )7 0 l — 5

网 口、 外部 总线 控制 器 、C 口等低 性能设 备 , I 2 以提 高

P B总线利 用率 。 L

l 0位 寻址 的 D R总 线访 问 PJ C IB总线上 各种 主

1 引言

P w rC 4 G 0 eP 4 0 P是 I M 公 司推 出 的高 性 能 3 B 2 位 mS C嵌 入式 处 理器 , 片上集 成 了 P w r C 4 o eP 4 0内

cl m e d dss m ad aed s n poet bu e oksre rd c bsdo o eP 4 0 P a b d e yt h rw r ei r c o t t r evr o ut ae nP w rC 4 G , e e g j a nw p

a d ap r f ei egv ni em1 ed v lp n,otn d d v lp n o S o tt p n ato sg a ie d t . e eo me t riga e eo me t w o B P b osr d n r n h T p n l f f a

YANG a Fn

惭 Sat o p tr q m n m ay F o 3 00 ,h a t m u  ̄ et p n,  ̄hu 5 0 2 i ) rC eE o C C n

Ab ta tA n w tl 2 b t ih p roma c e o o tolrP w r C 4 GP i i t d c dT etp— sr c : e s e 3 - i hs efr n e mire nr l o eP 4 0 s nr u e .h y i y e o

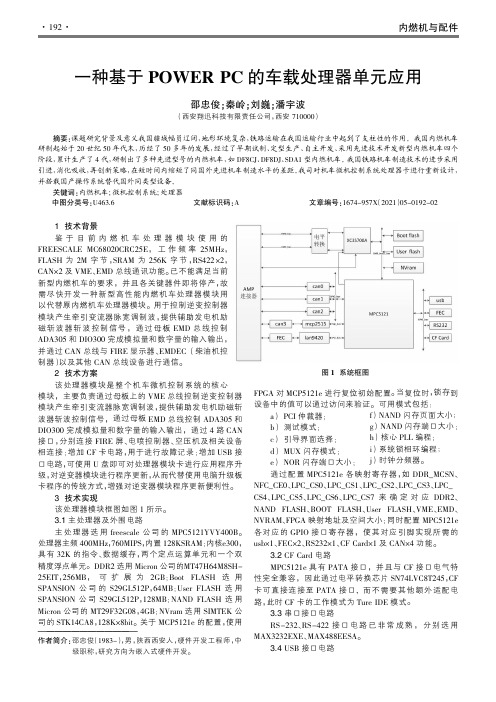

一种基于POWER PC的车载处理器单元应用

,,完成模拟量和数字量的输入输出,总线控制逆变控制器提供辅助发电机励磁斩和CAN空压机及相关设备接盘即可对处理器模块卡进行应用程序升从而代替使用电脑升级板增强对逆变器模块程序更新便利性。

FPGA对MCP5121e进行复位初始配置。

当复位时,锁存到设备中的值可以通过访问来验证。

可用模式包括:a)PCI仲裁器;b)测试模式;c)引导界面选择;d)MUX闪存模式;e)NOR闪存端口大小;通过配置MPC5121e各映射寄存器,如DDR_MCSN、NFC_CE0、LPC_CS0、LPC_CS1、LPC_CS2、LPC_CS3、LPC_ CS4、LPC_CS5、LPC_CS6、LPC_CS7来确定对应DDR2、图1系统框图f)NAND闪存页面大小;g)NAND闪存端口大小;h)核心PLL编程;i)系统锁相环编程;j)时钟分频器。

此部分电路使用USB功率芯片MIC2536-2BM 及静电保护芯片IP4220CZ6。

EMD总线接口电路总线挂接在Local Bus上,其寻址范围为对应的地址空间,LPC_CS2配置为模式。

EMD地址/数据线需经电平转换后连连接器上,转换芯片为TI公司的SN74LVTH16500,3-8译码器为NXP公司的VME总线接口电路上,其寻址范围为过转换芯片为路采用LAN9420通过故接口电层协议芯片和电平转换电路的设计。

本部分设计已在车载容错计算机服务板上成熟应用,可借用,其扩展实现另外一路以3.10POWER电路本处理器卡输入电源由底板供电(+5VDC),通过LT4600及MIC68220YML将5V电源转换为1.8V及0.9V,用于对DDR2电路进行供电;再转换一路1.4V、1.8V 及0.9V,用于对MPC5121电路进行供电;同时通过TPS78003将5V电源转换为3.3V及1.2V,用于对FPGA电路进行供电。

电源拓扑如图3所示。

4结束语①处理器主频400MHz,760MIPS,内置128KSRAM;内核e300,具有32K的指令、数据缓存及丰富的对外通讯接口,不仅从功能/性能上满足当前车辆的需求,丰富且可配置的对外通讯接口更加增强了该模块的二次开发升级图2RTL逻辑图图3电源拓扑图。

基于PowerPC440EPx的嵌入式系统引导加载程序的移植和配置

文章编号 :10 4 2 ( 0 1 0 —06 — 5 0 6— 79 2 1 ) 1 0 1 0

基 于 P w r C 4 E x的嵌 入 式 系统 引导 o eP 4 0 P 加 载 程 序 的移 植 和 配 置

袁三男

( 上海 电力学 院 计算机与信息工程学 院 , 上海 摘 209 ) 000

等.

关键词 :P w rC 4 E x .ot o eP 4 0 P ;U B 引导 加载程序 ; 数配置 参

中图分类号 :T 3 1 P 9 文献标 识码 :A

Bo tLo d r Po tng a n g r to o o a e r i nd Co f u a n f r Em b d e y t m i i e d d S se Ba e n Po

要 :引导加载程序是计算机 系统加 电后运 行 的第一段 程序代码 , 负责 系统硬 件的初 始化 和加载 操作 系

统 , 和系统硬件结构密切相关 . 对一个基于 Pw rC 4 E x处理器的应 用系统平 台 , 行 了 U Bo 移植 , 它 针 o eP 4 0 P 进 .ot 介 绍了该系统 的特性 、 处理器 引导加载程序设 计和移植方法 , 以及 U B t .o 参数 的设 置和 系统上 电参 数的配置

要 进 行 重 新 设 计 移 植 ,如 针 对 lu 环 境 ix n

第2 7卷 第 l期 2 1 年 2月 01

上

海

电 力 学

院

学

报

V0 . 7. No 1 12 . F b 2 1 e. 0l

J u l l o S a g a Un v ri o El crc Po r o rl f a hn h i iest y f e ti we

基于PowerPC440EPx的嵌入式系统引导加载程序的移植和配置

基于PowerPC440EPx的嵌入式系统引导加载程序的移植和配置本报告介绍了在PowerPC440EPx嵌入式系统中移植和配置引导加载程序的过程。

PowerPC 440EPx是一种受欢迎的PowerPC处理器,其嵌入式系统可在高度集成的嵌入式环境中处理多种信号和数据。

为使该处理器在嵌入式系统中正常工作,必须在其上移植并配置一个引导加载程序。

本文研究的目的是移植该引导加载程序以便将它安装到PowerPC 440EPx处理器并最终配置它以适应嵌入式系统。

首先,在移植引导加载程序之前,必须先准备好软件开发环境,包括编译器、汇编器、操作系统(如LINUX)、编辑器、调试器和文件管理器等。

其次,安装引导加载程序可以采用两种方法。

第一种是直接将已经存在的引导加载程序文件从硬盘中复制到内存中并设置其启动地址(也就是可引导位置)。

第二种是将已编译的机器码文件写入Flash存储器,然后在此前此处设置可引导位置。

之后,需要为引导加载程序构建中断服务子程序,因为该引导加载程序在PowerPC 440EPx处理器上需要与操作系统和硬件设备进行协同通信。

此外,还需要配置内存管理模块来划分内存,设置页表,以及设置总线和外部存储器的地址。

最后,用户可以测试移植的引导加载程序,确保引导加载程序可以正常运行。

使用嵌入式系统调试器可以修正任何问题,并且所有的调试语句可以在终端窗口中输入。

综上所述,PowerPC 440EPx嵌入式系统中的引导加载程序移植和配置涉及许多重要步骤,包括准备软件开发环境,安装引导加载程序,构建中断服务子程序,配置内存管理模块,以及测试引导加载程序。

在完成所有步骤后,即可期望引导加载程序在PowerPC 440EPx嵌入式系统上能够正常工作。

一种FPGA内嵌PowerPC处理器改进型程序固化方法

一种FPGA内嵌PowerPC处理器的改进型程序固化方法摘要:本文主要针对目前应用比较广泛的fpga芯片的嵌入式cpu 硬核,结合使用需求,并通过对厂商提供的程序固化方式的研究,从硬件平台,软件加载流程等方面综合分析,提出一种改进型的程序固化方法,以较小的代价,实现了不同应用环境下的一致程序固化方法,方便了用户调试和固化程序,提高了工作效率。

关键词:fpga;嵌入式;cpu硬核;固化;加载中图分类号:tp368随着现场可编程门阵列技术的发展,目前主流的fpga都具备大规模、高速度的特性,并且为特定的应用集成了诸如dsp,高速串行io口等资源。

但是面向通用处理或者高集成控制的嵌入式应用领域,如果单纯使用大规模的fpga芯片,依靠逻辑设计完成相关功能,则在技术、时间以及可维护性上具有一定的难度。

随着这种要求的逐步增多,在fpga中首先出现的具备通用处理功能的cpu 均是以软核形式提供的,比如xilinx的microblaze系列软核,满足了一部分用户的使用要求。

当用户需要更为复杂的功能时,比如高速、复杂的智能板卡和面向硬实时应用的领域,既需要解决板卡集成问题,同时还需要一个高性能处理器,此时基于fpga的cpu软核所提供的功能则无法满足。

因此,xilinx在virtex系列之后就推出了集成powerpc405处理器硬核的virtex2pro以及virtex4系列,并在最新的virtex5系列中集成了性能更为强大的powerpc440处理器硬核。

在使用含有cpu核的fpga进行逻辑设计并开发软件时,cpu核的工作模式对硬件逻辑资源分配,尤其是存储器资源分配有相应限制,并且需要根据cpu的启动模式和加载流程对资源分配进行规划。

同时,在使用xilinx官方所提供的方法时又具有一定的局限性,因此,结合实际使用,本文提出了一种更为全面的基于fpga嵌入式处理器硬核的程序调试、固化以及加载方法,能够适应更为广泛的情况。

基于440epx的workbench工程配置文档

基于440epx的workbench工程配置文档按以下步骤进行配置一、拷贝适当的基于440epx的bsp开发包到C:\WindRiver-GPPVE-3.6-PPC-Eval\vxworks-6.6\target\config目录。

二、打开Wind River Workbench 3.0,新建VxWorks Image Project工程,填写工程名称image-kernel-inf-rtdb-diab-zxj-20091019,工程名称尽量包含多的信息,比较直观,比如下图对应的中文是:内核镜像-接口程序-实时库-toolchain-姓名-日期。

下一步下一步下一步下一步三、上述步骤完成后,会在系统建立一个目录,里面含有相关配置文件,路径是:C:\WindRiver-GPPVE-3.6-PPC-Eval\workspace\image-kernel-inf-rtdb-diab-zxj-200910191、拷贝应用程序项目kxBHApp_090907到这个目录,如下图。

工程kxBHApp_090907的文件结构同样如下图所示。

2、拷贝ftpdLib.c和ftpdLib.h到新建的工程下四、Kernel Configuration配置注:配置时,使用ctrl+F键可以对关键字进行搜索,比如:*default boot line1、修改default bootline ,根据需要修改,一般只修改h和e的参数,修改成主机和目标板的IP地址:"emac(0,0)host:vxWorks h=192.168.0.48 e=192.168.0.215 u=440epx pw=1234"2、修改串口波特率,修改为1152003、添加doFs File System Components(dosFs2)包含即可4、添加XBD Block Device包含即可5、添加ifconfig包含即可6、添加PING Components包含即可7、添加kernel shell components8、添加TrueFFS支持(下图指示为正确配置)9、确定Include Pci support(default)没有被包含进内核配置中五、针对vxWorks系统,修改用户应用程序工程,并且修改usrAppInit.c文件,使应用程序开机能够启动,如下图。

PowerPC 440中文资料

The PowerPC® 440 Core A high-performance, superscalar processor core for embedded applicationsIBM Microelectronics DivisionResearch Triangle Park, NC09/21/1999OverviewThe PowerPC 440 CPU core is the latest addition to IBM’s family of 32-bit RISC PowerPC embedded processor cores. The PPC440’s high-speed, superscalar design and Book E Enhanced PowerPC Architecture™ put it at the leading edge for high performance system-on-a-chip (SOC) designs. The PPC440 core marries the performance and features of standalone microprocessors with the flexibility, low power, and modularity of embedded CPU cores.Target ApplicationsThe PPC440 Core is primarily designed for applications in which maximum performance and extensive peripheral integration are the critical selection criteria.Target market segments for the PPC440 core include:•Consumer applications including digital cameras, video games, set-top boxes, and internet appliances •Office automation products such as laser printers, thin-client systems, and sub-notebooks •Storage and networking products such as RAID controllers, routers, ATM switches, cellular basestations, and network cardsFeatures•2-way superscalar design•Out-of-order issue, execution, and completion•Dynamic branch prediction•Single-cycle branch latency•Three execution pipelines•Single-cycle throughput on 32x32 multiply•24 DSP operations (16x16+32->32, MAC with single-cycle throughput)•Real-time non-invasive instruction traceTypical ApplicationA typical system on a chip design with the PPC440 Core uses the CoreConnect TM bus structure for system level communication. High bandwidth peripherals and the PPC440 core communicate with one another over the processor local bus (PLB). Less demanding peripherals share the on-chip peripheral bus (OPB) and communicate to the PLB through the OPB Bridge. The PLB and OPB provide common interfaces for peripherals and enable quick turnaround, custom solutions for high volume applications.F igure 1 shows an example PPC440 Core-based system on a chip, illustrating the two-level bus structure and modular core-based design.Figure 1. Example PPC440 Core + ASIC SpecificationsPerformance (Dhrystone 2.1)1000 MIPS @ 555MHz (est.), Nominal silicon, 1.8V, 55°C 720 MIPS @ 400MHz (est.), Slow silicon, 1.65V, 85°CFrequency0 – 400MHz , Slow silicon, 1.65V, 85°C555MHz nominalPower Dissipation 2.5mW / MHz @ 1.8V (est.), hard core with 32KI / 32KD cachesArchitecture32-bit PowerPC Book E compliant, application code compatible withall PowerPC processorsDie Size 4.0 mm2 for CPU only (est.)Caches0-64KB, 32-way to 128-way associativeTechnology0.18 µm CMOS copper technology0.12 µm L eff , 4 levels of metalPower Supply 1.8 VoltsTransistors 5.5M, hard core with 32KI / 32KD cachesOperating Range-40°C to 125°C, 1.6V to 1.9VData Bandwidth Up to 6.4 GB/sec via three 128-bit, 200MHz CoreConnect businterfacesTable 1- 440 CPU Core SpecificationsEmbedded Design SupportThe PPC440 Core, as a member of the PowerPC 400 Family, is supported by the IBM PowerPC Embedded Tools TM program, in which over 80 third party vendors have combined with IBM to provide a complete tools solution. Development tools for the PPC440 include C/C++ compilers, debuggers, bus functional models, hardware/software co-simulation environments, and real-time operating systems. As part of the tools program, IBM maintains a complete set of development tools by offering the High C/C++ Compiler, RISCWatch TM debugger with RISCTrace TM trace interface, VHDL and Verilog simulation models and a PPC440 Core Superstructure development kit.PPC440 CPU Core OrganizationPPC440 CPUThe PPC440 CPU operates on instructions in a dual issue, seven stage pipeline, capable of dispatching two instructions per clock to multiple execution units and to optional Auxiliary Processor Units (APUs). The PPC440 core is shown in Figure 2.Figure 2 - PPC440 Core Block DiagramThe pipeline contains the following stages, as shown in Figure 3:1.IFTH – Fetch instructions from instruction cache2.PDCD – Pre-decode; partial instruction decode3.DISS – Decode/Issue; final decode and issue to units4.RACC – Register Access; read from multi-ported General Purpose Register (GPR) file5.EXE1/AGEN – Execute stage 1; complete simple arithmetics, generate load/store address6.EXE2/CRD – Execute stage 2; multiplex in results from units in preparation for writing into GPRfile, Data Cache access7.WB – Writeback; write results into GPR file from integer operation or load operationFigure 3 - PPC440 CPU PipelineInstruction Fetch and Pre-decodeDuring the Instruction Fetch stage (IFTH), an entire cache line (eight words) is read into the instruction cache line read buffer. From there, the next two instructions in the pre-decode buffers PDCD0 and PDCD1 during the PDCD stage. The instruction cache is virtually indexed and tagged, and translation is performed in parallel with the cache access.Branch UnitThe PPC440 uses a Branch History Table (BHT) to maintain dynamic branch prediction of conditional branches. To perform dynamic branch prediction, a 2-bit counter in the BHT is used to decide whether prediction should agree or disagree with the normal PowerPC static branch prediction. The counter counts up if branch determination agrees, and down if it disagrees. Once the counter saturates, it can only count away from saturation. Therefore, four valid states exist: “Strongly agree”, “Agree”, “Disagree”, and “Strongly disagree”. By agreeing or disagreeing with static branch prediction, different branches can use the same counter in the BHT and have opposite static predictions, without the machine necessarily mispredicting a branch.The Branch Target Address Cache (BTAC) is used to predict branches and deliver their target addresses before the instruction cache can deliver the same data. It is accessed during IFTH, whereas normal branch prediction would not occur until PDCD, and therefore avoids a one cycle penalty. The BTAC is made up of an odd and even BTAC containing eight entries each. Only unconditional branches and bdnzinstructions are stored, which gives a significant performance boost while keeping the design straightforward.Decode and IssueThe four-entry decode queue accepts up to two instructions per clock submitted from the pre-decode buffers. Instructions always enter the lowest empty or emptying queue position, behind any instructions already in the queue. Therefore, the queue fills from the bottom up, instructions stay in order, and no bubbles exist in the queue. A significant portion of decode is performed in the lowest two positions (DISS0 and DISS1). Up to two instructions exit the queue based on the instructions’ decode and pipeline availability, and are issued to the RACC stage. DISS1 can issue out of order with respect to DISS0. Register AccessConceptually, the GPR file consists of thirty-two, 32-bit general purpose registers. It is implemented as two 6-port arrays, (one array for LRACC, one for IRACC) each with thirty-two, 32-bit registers containing three write ports and three read ports. On all GPR updating instructions, the appropriate GPR write ports will be written in order to keep the contents of the files the same. On GPR reads, however, the GPR read ports are dedicated to instructions that are dispatched to a RACC’s associated pipe(s). Execution PipelinesThe PPC440 contains three execution pipes: a load/store pipe (“L-pipe”), a simple integer pipe (“J-pipe”), and a complex integer pipe (“I-pipe”). The L-pipe and J-pipe instructions are dispatched from the LRACC; I-pipe instructions are dispatched from IRACC. The three pipes together perform all 32-bit PowerPC integer instructions in hardware compliant with the PowerPC Book E specification. Table 2 lists the rules for dispatching to each of the three execution pipes.L-pipe only Loads/stores1, cache instructions, mbar, msyncI-pipe or J-pipe2Add, addi, addis, and, andc, cntlzw, eqv, extsb, extsh, nand, neg, nor, or, orc, ori, oris, xori, xoris, rlwimi, rlwinm, rlwnm, slw, srw, subfI-pipe only Branches, multiplies, divides, move to/from DCR/SPR, indirect XER updates,indirect LR/CTR updates, indirect CR updates, CR-logicals, MAC instructions,mcrf, mcrxr, mtcrf, mfcr, compares, dlmzb, isync, rfi, rfci, sc, wrtee, wrteei,mtmsr, mfmsr, trapsTable 2 – Rules for Instruction IssueThe MAC unit is an auxiliary processor unit (APU) which adds 24 operations to the PPC440 instruction set. MAC instructions operate on either signed or unsigned 16 bit operands and accumulate the results in a 32-bit GPR. All MAC unit instructions have single cycle throughput. The MAC unit is contained within the I-pipe.1 The stwcx. instruction goes down both the L-pipe as well as the I-pipe, in order to update the CR.2 Instructions which update the CR or XER are not issued to the J-pipe.Instruction and Data CachesProcessor Local Bus (PLB) Memory AccessThe PPC440 has three independent 128-bit Processor Local Bus (PLB) master interfaces, one for instruction fetches, one for data reads, and a third for data writes. Memory accesses are performed through the PLB interfaces to/from the instruction cache (I-Cache) or data cache (D-Cache) units. Having three independent bus interfaces for the cache units provides maximum flexibility for designs to optimize system throughput. Memory accesses (loads/stores) which hit in the cache achieve single-cycle throughput.Cache ConfigurationThe PPC440 has separate instruction and data caches with 8 word (32 byte) cache lines. Instruction and data cache sizes are factory-configurable to any combination of 0KB, 8KB, 16KB, 32KB, or 64KB cache sizes. Configurable cache sizes provide designers with a parameter for optimizing the PPC440 to a desired price-performance for a particular application. The caches are highly associative, with associativity varying with cache size as shown in Table 3. High associativity enables advanced cache functions such as locking and transient memory regions (see “Cache Partitioning” below).Cache Size Ways8 KB3216KB6432KB6464KB128Table 3 – Number of Ways for Different PPC440 Cache SizesThe cache arrays are non-blocking. Non-blocking caches allow the PPC440 to overlap execution ofload/store instructions while instruction fetches take place over the PLB. The caches, therefore, continue supplying data and instructions without interruption to the pipeline. The PPC440 replaces cache lines according to a round-robin replacement policy.The initial PPC440A4 core offering will include a 32KB instruction cache and 32KB data cache. These caches are physically constructed using two, 16KB CAMRAM macros, each consisting of 8, 2KB sub-banks (or “sets”). This organization facilities low-power operation and fast hit/miss determination. Cache PartitioningThe PPC440 caches have the ability to be separated into “normal”, “transient”, and “locked” regions. Normal regions are what is traditionally thought of regarding cache replacement. Transient regions are used for data that is used temporarily and then not needed again, such as the data in a particular JPEG image. A separate transient region avoids castouts of more commonly accessed code in the normal region. The locked region is for code that is not to be cast out of the cache, and is the resulting region not included in the normal and transient regions. The regions are set via “victim” ceiling and floor pointers, as shown in Figure 4. Figure 4 shows two examples of cache partitioning, the left side shows separate transient and normal regions, and the right side shows part of the normal region overlapping with the transient region. The normal ceiling is defined as the top of the cache.Figure 4 – Two Examples of Cache PartitioningI-Cache Speculative Pre-fetchingThe I-Cache utilizes a programmable speculative pre-fetch mechanism to enhance performance. Software can enable up to three additional lines to be speculatively pre-fetched, using a burst protocol, upon any instruction cache miss. When this mode is enabled, the I-Cache controller will automatically inspect the I-Cache on a miss to see if any of up to the next three lines are also misses. If so, the hardware will present a burst request to the PLB immediately after the original line fill request. This speculative burst request takes advantage of the throughput capability of standard memory architectures such as SDRAM and brings in anticipated subsequent instructions after a miss. Furthermore, if the instruction stream branches away from the lines which are being speculatively filled, the burst request which is filling the speculative lines can be abandoned in the middle, and a new fill request at the branch target location immediately initiated. There is a programmable "threshold" to determine when to abandon a speculative line fill that may have been in progress at the time of a branch redirection. This threshold designates how many doublewords of the speculative cache line must be received to not abandon a current line fill. In this fashion, the speculative pre-fetch mechanism can be carefully tailored to provide optimum performance for specific applications and memory subsystems.D-Cache Line FillsThe D-Cache contains three line fill buffers and can queue up to four load misses to three separate cache lines. The PPC440 will then execute past these load misses, until the queue is full or the pipes are held waiting for a load value. The D-Cache controller places the target word on the bypass path as the fill buffer captures data words off the PLB. Additional requests of the cache line held in the fill buffer are also forwarded directly to the operand registers in the execute unit.D-Cache Non-cacheable Store GatheringThe D-Cache “gathers” up to 16 bytes for non-cacheable, write-through, and w/o allocate stores, and will burst the quadword to the PLB for fast writes to non-cacheable memory.D-Cache Write-Back and Write-Through ModesThe D-Cache supports write-back or write-through mode. In write-back mode, store hits are written to the cache and not to main memory. Main memory is later modified if and when the line is flushed from the cache. In write-through mode, the data cache controller writes main memory for store misses as well asstore hits; every store operation generates a PLB write request. (Although write-through requests to non-cacheable memory can be gathered as previously mentioned).D-Cache Store AllocationThe D-Cache can be programmed whether or not to allocate a line on a D-Cache store miss. Write-on-allocate is enabled by default. In this mode, a store miss to cacheable memory forces the data cache controller to allocate a line in the data cache and generate a line fill. In contrast, when “without allocate”is enabled, a store miss to cacheable memory will not allocate a line data cache and will simply write the data to memory.Big Endian and Little Endian SupportThe PPC440 supports big endian or little endian byte ordering for instructions and data stored in external memory. The PowerPC Book E architecture is endian neutral; each page in memory can be configured for big or little endian byte ordering via a storage attribute contained in the TLB entry for that region. Strapping signals on the PPC440 core initialize the beginning TLB entry’s endian attribute, so thePPC440 can boot from little or big endian memory.Memory Management Unit (MMU)The MMU supports multiple page sizes as well as a variety of storage protection attributes and access control options. Multiple page sizes improve TLB efficiency and minimize the number of TLB misses. The PPC440 gives programmers the flexibility to have any combination of the following eight possible page sizes in the translation look-aside buffer (TLB) simultaneously: 1KB, 4KB, 16KB, 64KB, 256KB,1MB, 16MB and 256MB. Having an extremely large page size allows users to define system memory with a minimal number of TLB entries, thereby simplifying TLB allocation and replacement. Small page sizes prevent the wasting of memory when allocating small areas of data.Each page of memory is accompanied by a set of storage attributes. These attributes include cacheability, write through/write back mode, big/little endian, guarded and four user-defined attributes. The user-defined attributes can be used to mark a memory page with an application-specific meaning. The guarded attribute controls speculative accesses. The big/little endian attribute marks a memory page as having big or little endian byte ordering. Write through/write back specifies whether memory is updated in addition to the cache during store operations.Two of the user-defined storage attributes can be programmed for special functions inside the core. One can be enabled to designate normal or transient cache regions. Another can be enabled to control whether or not store misses allocate a line in the D-Cache.Access control bits in the TLB entries enable system software to control read, write, and execute access for programs in both user and supervisor states.The MMU includes a 64-entry fully-associative unified TLB to reduce the overhead of address translation. Contention for the main TLB between data address and instruction address translation is minimized through the use of a four-entry instruction shadow TLB (ITLB) and an eight-entry data shadow TLB (DTLB). The ITLB and DTLB shadow the most recently used entries in the unified TLB. The MMU manages the replacement strategy of the ITLB and DTLB leaving the unified TLB to software control. Real-time operating systems are free to implement their own replacement algorithm for the unified TLB.Interrupt Handling LogicThe PPC440 services exceptions generated by error conditions, the internal timer facilities, debug events, and the external interrupt controller (EIC) interface. Altogether, there are sixteen different interrupt types supported.Interrupts are divided into two classes, critical and non-critical. Each class of interrupt has its own pair of save/restore registers for holding the program counter and machine state. Separate save/restore registers allow the PPC440 to quickly handle critical interrupts even within a non-critical interrupt handler. When an interrupt is taken, the PPC440 automatically writes the program counter and machine state to save/restore register SRR0 and SRR1 respectively for non-critical interrupts, or CSRR0 and CSRR1 respectively for critical interrupts. The machine status and program counter are automatically restored at the end of an exception handler when the return from interrupt (rfi) or return from critical interrupt (rfci) instruction is executed.TimersThe PPC440 contains a 64-bit time base and three timers: the Decrementer (DEC), the Fixed Interval Timer (FIT), and the WatchDog Timer (WDT). The time base counter increments synchronously with the CPU clock or an external clock source. The three timers are synchronous with the time base.The DEC is a 32-bit register that decrements at the time base increment rate. The user loads the DEC register with a value to create the desired delay. When the register reaches zero, the timer stops decrementing and generates a decrementer interrupt. Optionally, the DEC can be programmed to auto-reload the value last written to the DEC auto-reload register, after which the DEC continues to decrement.The FIT generates periodic interrupts based on one of four selectable bits in the time base. When the selected bit changes from 0 to 1, the PPC440 generates a FIT exception.The watchdog timer provides a periodic critical-class interrupt based on a selected bit in the time base. This interrupt can be used for system error recovery in the event of software or system lockups. Users may select one of four time periods for the interval and the type of reset generated if the watchdog timer expires twice without an intervening clear from software. If enabled, the watchdog timer generates a reset unless an exception handler updates the watchdog timer status bit before the timer has completed two of the selected timer intervals.Debug LogicAll architected resources on the PPC440 can be accessed through the debug logic. Upon a debug event, the PPC440 provides debug information to an external debug tool. Three different types of tools are supported depending on the debug mode: ROM Monitors, JTAG debuggers and instruction trace tools. Internal Debug ModeIn internal debug mode, a debug event enables exception-handling software at a dedicated interrupt vector to take over the PPC440 and communicate with a debug tool. Exception-handling software has read-write access to all registers and can set hardware or software breakpoints. ROM monitors typically use the internal debug mode.External Debug ModeIn external debug mode, the PPC440 enters stop state (i.e., stops instruction execution) when a debug event occurs. This mode offers a debug tool non-invasive read-write access to all registers in the PPC440 via the JTAG interface. Once the PPC440 is in stop state, the debug tool can start the PPC440, step an instruction, freeze the timers or set hardware or software break points. In addition to PPC440 control, the debug logic is capable of writing instructions into the instruction cache, eliminating the need for external memory during initial board bring up.Debug Wait ModeDebug wait mode offers the same functionality as external debug mode with one difference; in debug wait mode, the PPC440 will respond to interrupts and temporarily leave stop state to service them before returning to debug wait mode. In external debug mode, by contrast, interrupts are disabled while in stop state. Debug wait mode is particularly useful when debugging real-time control systems.Real-Time Trace Debug ModeIn real-time trace debug mode, instruction trace information is continuously broadcast to the trace port. When a debug event occurs, an external debug tool saves instruction trace information before and after the event. The number of traced instructions depends only on the memory buffer depth of the trace tool. Debug EventsDebug events signal the debug logic to either stop the PPC440, put the PPC440 in debug wait state, cause a debug exception, or save instruction trace information, depending on the debug mode. Table 4 on the following page lists the possible debug events and their description.Debug Event DescriptionBranch Taken A Branch Taken debug event occurs prior to the execution ofa taken branch instruction.Instruction Completion The Instruction Completion debug event occurs after thecompletion of any instruction.Return from Interrupt The Return From Interrupt debug event occurs after thecompletion of an rfi or rfci instruction.Interrupt The Interrupt debug event occurs after an interrupt is taken. Trap The Trap debug event occurs prior to the execution of a trapinstruction, where the trap condition is met.Instruction Address Compare (IAC)The IAC debug event occurs prior to the execution of aninstruction at an address that matches the contents of one offour IAC registers (IAC1, IAC2, IAC3, and IAC4).Alternatively, the registers can be combined to cause an IACdebug event prior to the execution of an instruction at anaddress contained in one of the following ranges as specifiedby the four IAC registers:IAC1 <= range < IAC2 (inclusive),IAC3 <= range < IAC4 (inclusive),range low < IAC1 < IAC2 <= range high (exclusive), orrange low < IAC3 < IAC4 <= range high (exclusive).Data Address Compare (DAC)The DAC debug event occurs prior to the execution of aninstruction that accesses a data address matching the contentsof one of the two DAC registers (DAC1 and DAC2).Alternatively, the registers can be combined to cause a DACdebug event occurs prior to the execution of an instructionthat accesses a data address within one of the followingranges specified by the two DAC registers:DAC1 <= range < DAC2 (inclusive), orrange low < DAC1 < DAC2 <= range high (exclusive). Data Value Compare (DVC)The Data Value Compare debug event occurs prior to theexecution of an instruction that accesses a data addressmatching one of the two DAC registers (or within a DACrange) and containing a particular data value as specified byone of the two DVC registers. The DVC debug event mayoccur when a selected data byte, half-word or word matchesthe corresponding element in DVC1 or DVC2. Unconditional Event An unconditional debug event is set by a debug tool throughthe JTAG port or by ASIC logic external to the PPC440.Table 4 - Debug EventsPower ManagementThe PPC440 core, in keeping with the IBM PowerPC 400 family tradition, utilizes aggressive power management techniques for minimizing power. The PPC440 utilizes three key techniques: redundant operand registers, half-cycle latch stabilization, and dynamic clock gating.Redundant Operand RegistersRedundant operand registers are used at various pipeline stages for feeding operands to each of the execution units. This saves power by preventing unused units from seeing the operand values being used by other units and improves performance by reducing loading and wire length in critical stages.Half-Cycle Latch StabilizationHalf-cycle stabilization latches minimize the propagation of glitches to downstream logic. This is easily employed since the PPC440 core contains a master/slave latch arrangement for scan-test purposes. Therefore, a master-only latch is simply needed in the logic path that is switching in the first half of a cycle. For example, if the select lines for a mux are being determined in the first half of a cycle, then by putting a master-only latch on these select lines before delivering them to the mux, the mux outputs are prevented from glitching while the select lines are being determined. Conversely, if the data lines are unstable in the first half of a cycle, a stabilization latch may be used on the data inputs, while leaving the select lines alone.Dynamic Clock GatingThe most important feature of the PPC440’s dynamic power management is the extensive use of clock gating. Given the PPC440’s master/slave latch organization, there are two possible gates that can be used. The relationship between them, and their relative affect on the clock splitter and hence power are shown in Figure 5.Figure 5 - PPC440 Clock GatingIn this figure, the early gate blocks the phase 1 clock and prevents the master latch from loading, while the late gate blocks the phase 2 clock and prevents the slave latch from loading. As illustrated in the simplified block diagram of the clock splitter, the early gate must arrive by mid-cycle -- which is when the system clock falls. If the gate is activated by this point, then the net effect is that internal to the clock splitter the fall on the system clock is never observed, and both the phase 1 and the phase 2 clock splitteroutputs remain stable, preventing any downstream master latches from loading, and hence their associated slave latches will not change either. This affords the maximum power savings, with the downstream logic dissipating no power other than leakage, and the clock splitter itself using almost zero power.In the event that the gate for a given latch cannot be determined by mid-cycle, the late gate can be used, which does not prevent the system clock fall and consequent phase 1 clock rise, but does prevent the corresponding next phase 2 clock rise. This does not save as much power, but the timing is much more relaxed and the power savings are still considerable.。

基于POWER PC的数据处理系统设计

基于POWER PC的数据处理系统设计吴杰【摘要】数据处理系统适合于车载、机载等恶劣环境下,运行多任务实时操作系统,完成信息层数据运算,以及高性能图形显示等多种应用.本文对于相关数据处理系统设计具有参考意义.【期刊名称】《科技视界》【年(卷),期】2018(000)008【总页数】4页(P4-7)【关键词】POWERPC;数据处理【作者】吴杰【作者单位】中国电子科技集团公司第二十研究所,陕西西安 710068【正文语种】中文【中图分类】TP274.2随着嵌入式系统的广泛应用,数据处理系统的扩展性和通用型越来越受到大家的关注。

本文中的数据处理板核心处理芯片采用基于POWER PC架构的MPC8548芯片,具有处理速度快,通用接口丰富、工作温度范围大的特点;软件部分选用多任务实时操作系统VxWorks,可以同时完成数据运算、高性能图形显示等多种工作,支持透明的底层硬件操作,实现软件编写与硬件设计分离,简化了底层软件设计,有很好的的扩展性和移植性。

1 系统设计本设计中采用POWER PC作为核心处理芯片,实现多任务并行数据处理功能;CPU主控MPC8548为整个模块数据处理中枢,处理外围各种芯片采集的数据,并将必要的数据保存到非易失存储器。

系统将高性能 MPC8548与嵌入式显示芯片SM722集成在一起,CPU通过PCI总线传输数据到显卡,提供用户交互界面;FPGA通过构建寄存器和双口RAM实现接口通信和时序控制等功能;DSP完成浮点运算和数据处理的功能;话音电路完成话音编解码和数模转换功能。

系统提供丰富的外部接口,包括串口(RS2232和 RS422)、以太网接口、USB接口、LVDS 总线接口以及VGA接口。

系统设计框架如图1所示。

2 硬件设计2.1 主控芯片设计本设计的POWER PC芯片选用Freescale公司的MPC8548处理器,该芯片是一款高性能、低功耗的32位RISC处理器。

最高主频超过800MHz,具有很强的定点和浮点计算能力。

基于POWER PC处理器的处理器子卡[实用新型专利]

![基于POWER PC处理器的处理器子卡[实用新型专利]](https://img.taocdn.com/s3/m/5195c8054afe04a1b171dec6.png)

专利名称:基于POWER PC处理器的处理器子卡专利类型:实用新型专利

发明人:邵忠俊,孙小杰,许征锋,余齐严,尹晓明申请号:CN201822197548.6

申请日:20181225

公开号:CN209312010U

公开日:

20190827

专利内容由知识产权出版社提供

摘要:本实用新型提出一种基于POWER PC处理器的处理器子卡,能够解决现有基于POWERPC 架构的板卡结构尺寸、功耗以及重量较大的问题。

该处理器子卡中,CPLD接入看门狗电路,实现主处理器复位以及相应的配置;CPLD还用于对主处理器经LPC总线传输的地址和数据进行解析;主处理器配置有PCI接口,相应通过PCI总线接至PMC规范定义的连接器X1和X2;CPLD配置有多路离散量输入输出接口,相应通过电平缓冲芯片接至连接器X4;所述连接器X4同时还作为串口接口电路、以太网接口电路、USB接口电路、CAN总线接口电路以及电源电路对外的接口。

申请人:西安翔迅科技有限责任公司

地址:710077 陕西省西安市锦业二路15号中航工业西安计算技术研究所1号厂房112室

国籍:CN

代理机构:西安智邦专利商标代理有限公司

代理人:胡乐

更多信息请下载全文后查看。

基于POWER PC通用处理器的CPU模块设计

基于POWER PC通用处理器的CPU模块设计

龚清萍;何亦征

【期刊名称】《航空电子技术》

【年(卷),期】2003(034)003

【摘要】POWER PC通用处理器是一种低功耗超标量的RISC处理器.本文描述了基于POWER PC通用处理器的CPU模块的基本体系结构,并以Motorola通用处理器POWER PC603e为例,阐述了CPU模块的实现方法.

【总页数】6页(P29-33,42)

【作者】龚清萍;何亦征

【作者单位】中国航空无线电电子研究所,上海,200233;中国航空无线电电子研究所,上海,200233

【正文语种】中文

【中图分类】TP368.1

【相关文献】

1.基于Intel 855GM芯片组的PCI-104 CPU模块设计 [J], 叶斌元;吴灏;张运吉

2.基于MPC8245的通用处理器模块的设计 [J], 张斌峰;曹兴冈;王斌

3.基于PCI6254的CPCI通用处理器模块的设计 [J], 段桂平;孙勇;柴小丽;蒋祺明

4.基于PowerPC架构的通用处理器系统虚拟验证 [J], 王婷;马超;田泽

5.基于Intel 815E芯片组的PCI-104 CPU模块设计 [J], 喻强;戴晓明;徐峥

因版权原因,仅展示原文概要,查看原文内容请购买。

基于PowerPC的EPON系统中主控板驱动程序开发

基于PowerPC的EPON系统中主控板驱动程序开发徐沛;黄俊;肖义;张际生【摘要】First, this paper introduces the overall design scheme of control board based on PowerPC processor and states the important role of GbE switch. And then we provide the structure of network device driver in embedded Linux.Based on that,we mainly analyze the development of switch driver on control board.%介绍了基于PowerPC处理器的主控板总体设计方案,阐述了千兆以太网交换芯片的重要作用,给出了嵌入式Linux操作系统中网络设备驱动程序的体系结构.在此基础上,重点分析了主控板交换芯片驱动程序的具体开发过程.【期刊名称】《光通信技术》【年(卷),期】2011(035)011【总页数】3页(P60-62)【关键词】EPON;主控板;PowerPC;嵌入式Linux;交换芯片驱动程序【作者】徐沛;黄俊;肖义;张际生【作者单位】重庆邮电大学信号处理与片上系统实验室,重庆400065;重庆邮电大学信号处理与片上系统实验室,重庆400065;重庆邮电大学信号处理与片上系统实验室,重庆400065;重庆邮电大学信号处理与片上系统实验室,重庆400065【正文语种】中文【中图分类】TN9290 引言EPON(以太网无源光网络)是一种新型光接入网技术,它采用点到多点(P2MP)网络拓扑结构、无源光纤传输方式,在以太网之上提供多种业务,具有运营维护成本低,便于拓展、传输距离远、带宽高及业务范围广等优点,因此其应用前景得到业内人士的普遍看好。

基于PowerPC处理器的SATA电子盘驱动设计与实现

基于PowerPC处理器的SATA电子盘驱动设计与实现王婷;朱守园;段海军;贠海顺

【期刊名称】《信息通信》

【年(卷),期】2017(000)003

【摘要】随着航空电子系统的日益复杂,需要记录的数据量越来越大,SATA电子盘日益成为存储数据的主流选择.文章首先介绍了SATA标准及一种集成了SATA控制器的CPU(P1010),然后详细说明了基于该款CPU的驱动软件的数据结构及实现等内容.

【总页数】2页(P65-66)

【作者】王婷;朱守园;段海军;贠海顺

【作者单位】中国航空计算技术研究所,陕西西安710119;中国航空计算技术研究所,陕西西安710119;中国航空计算技术研究所,陕西西安710119;中国航空计算技术研究所,陕西西安710119

【正文语种】中文

【中图分类】TP336

【相关文献】

1.基于 VxWorks 的大容量 SATA 电子盘驱动实现 [J], 肖忠炳;吴林峰;任金牛

2.基于PowerPC7447处理器的显示平台设计与实现 [J], 童明成

3.基于PCI总线的PowerPC8245处理器嵌入式系统硬件的设计与实现 [J], 樊江锋;徐连波;叶波;王旭东

4.基于PowerPC处理器的嵌入式系统电源设计与实现 [J], 亢晓丽;张鹏

5.基于PowerPC440处理器的网卡驱动的设计与实现 [J], 张前;张钰尧;王宏伟因版权原因,仅展示原文概要,查看原文内容请购买。

一种操作系统的PowerPC440内存管理机制研究

一种操作系统的PowerPC440内存管理机制研究颜纪迅;冉鹏;汤小明【期刊名称】《计算机工程与应用》【年(卷),期】2012(048)030【摘要】以PowerPC440为平台,设计了完全基于Hash页表的段页式存储管理方法,实现了操作系统内核以及各应用进程之间的存储空间保护.针对Hash页表构筑方式和特点的研究证明,给嵌入式操作系统施加特定约束后,该方法能够显著减少空间开销和时间开销,增加空间确定性,满足无人机系统的应用要求.该研究为进一步提出更优化的内存管理设计方法奠定了基础.%Using the PowerPC440 as the platform, a memory management method which is totally based on Hash page table, realizes the memory protection between the kernel of operating system and the processes. The study on the construction method and characteristics of Hash page table proves that, by adding some specific constraints, this method can reduce space and time loads, enhance space certainty and satisfy the application requirements of the UVA system. Besides, This research lays a foundation for the further optimization of the memory management design.【总页数】6页(P62-67)【作者】颜纪迅;冉鹏;汤小明【作者单位】西安飞行控制研究所,西安710065;西安飞行控制研究所,西安710065;西安飞行控制研究所,西安710065;西北工业大学自动化学院,西安710072【正文语种】中文【中图分类】TP316.2【相关文献】1.嵌入式操作系统MQX内存管理机制分析与改进 [J], 文瑾;王宜怀;柏祥2.嵌入式操作系统中基于MIPS处理器的内存管理机制实现 [J], 郭锋;王宏伟;黄保垒;齐晓斌3.AndlinkOS操作系统内存管理算法设计 [J], 李峰;陈维;李坤明;童超4.操作系统与Oracle内存管理比较 [J], 王润中5.嵌入式操作系统μC/OS-Ⅱ的一种内存管理算法 [J], 李平勇;游磊因版权原因,仅展示原文概要,查看原文内容请购买。

基于powerPC的处理器修复技术研究

基于power PC的处理器修复技术研究发布时间:2022-06-08T07:48:43.806Z 来源:《中国科技信息》2022年第4期作者:王闯张赟枫[导读] Power PC系列处理器的是一种具有升级性能好、功耗低优点的处理器。

王闯张赟枫江苏金陵机械制造总厂江苏南京210000摘要:Power PC系列处理器的是一种具有升级性能好、功耗低优点的处理器。

广泛应有与许多领域,但是在使用过程中也会存在各种各样的错误。

本篇文章通过讲述PowerPC系列处理器的工作原理,故障的排除等方面来分析经常出现的故障,供相关人员参考。

关键词:PowerPC处理器前言计算机的诞生和发展已经渗透到生活和生产的各个方面,Power PC在很多领域都扮演着非常重要的角色,比如通信、国防、工控领域,因为Power PC的众多优点,受到了许多设计师的喜爱,所以被应用到许多领域,随着众多处理器模块的出现,也出现了各种各样的故障,这些在生产、调试、维修中出现的故障,看着毫无关联,实际上有着紧密联系。

一、Power PC处理器简介Power PC诞生于1991年。

由IBM、苹果和摩托罗拉三个企业共同合作,,最终才成功开发。

1992年,第一代Power PC采用的单管密度是0.6 cm的生产工艺,其中,规模最大达到300万人。

目前Visca正在研究和制造Power PC处理器。

经过长时间的开发,该处理器已达到2GHz。

1998年,是另一个大发展时期,铜Power PC处理器出现开创了一个新的历史时代。

2000年代,IBM开始销售大量铜产品,如rs-6000-x80。

在逐步发展的过程中铜技术取代了铝技术。

铝技术在长期的发展中已经沿用了30年的。

铜技术的广泛的使用得到快速的发展,甚至在发展到,可以使硅芯片生产工艺达到了0.20微米的水平。

在不断的发展的过程中,集成在一个2亿个晶体管集成在一个电路中,大大提高了工作效率:工作电压目前是1.8V,相比于以前的工作电压为2.5V,大大减少了能耗,而且这种能耗的低压操作大大降低了芯片的损耗,更主要易于散热,并且少量大大提高了系统的稳定性。

PowerPC 440GP嵌入式处理器

PowerPC 440GP嵌入式处理器

无

【期刊名称】《世界产品与技术》

【年(卷),期】2003(000)009

【摘要】PowerPC440GP嵌入式处理器提供了无与伦比的性能,设计灵活性,以及适合高要求网络、存储及其它嵌入式应用稳定的特性。

PowerPC440GP处理器具有最高可达500MHz的速度,Power Book E体系结构以及各种外围组件组合,是各种高性能应用的理想选择。

【总页数】2页(P42-43)

【作者】无

【作者单位】无

【正文语种】中文

【中图分类】TP332

【相关文献】

1.进驻桌面:PowerPC主宰苹果电脑——深度透视PowerPC家族(二) [J], BackFIRE

2.XILINX嵌入式PowerPC参考设计采用Treek软件提供千兆位以太网性能——Treck TCP/IP协议栈与Xilinx Virtex-4 FX PowerPC核吞吐率比竞争 FPGA高出6倍 [J],

3.PowerPC系统PowerPC:IBM和Motorola缺乏软件支持 [J], Brain Nadel;李兆勤

4.嵌入式处理器程序远程加载通用方法 [J], 邵龙

5.EnCorePPI高集成、高性能、基于PowerPC嵌入式处理器 [J],

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

驱动功能抽象网卡设备驱动基于PowerPC 440处理器的网卡驱动的设计与实现张前,张钰尧,王宏伟(中国航空工业集团公司西安航空计算技术研究所,陕西西安710065)摘要:针对某夜入式项目基于天脉1操作系统的网络协议栈组件在P 〇werPC 440处理器平台上实现以太网通信功能的 要求,文章分析了天脉1操作系统的网络协议栈模型,并针对该模型设计实现了配套的PowerPC 440处理器的网卡驱动 程序,同时对文章设计的网卡驱动进行了测试。

测试结果表明文章设计的网卡驱动功能正确,运行稳定,可以使用户可靠地通过网络协议栈完成网络数据的接收和发送。

关键词:PowerPC 440;网卡驱动;网络协议栈;天脉1操作系统中图分类号:TN 958文献标识码:A文章编号= 1673-1131(2019)03-0125-02目前嵌入式设备已应用在生活中的各个方面,通常情况 下操作系统都会为其提供网络通信组件。

在众多的操作系统 中,天脉1操作系统作为一款面向机载嵌入式设备的国产操 作系统,不仅满足机载环境要求的强实时、高安全等特殊要求, 同时提供了标准的TCP /IP 协议栈,用户可以便捷的调用多种 通信应用编程接口进行开发。

本文结合实际项目开发,基于 天脉1的TCP /IP 网络协议栈组件在PowerPC 440处理器平台 上设计实现了配套的网卡驱动,使得用户可以可靠地利用天 脉1操作系统的网络协议栈组件完成以太网通信功能。

1 PowerPC 440的网卡设备PowerPC 440处理器作为一款32位RISC 处理器,其内核 采用了 Book -E 增强型PowerPC 体系结构,方便灵活,同时其 可调节的存储管理功能和稳定可靠的调试功能非常适用于实时操作环境[1]。

在以太网通信功能方面,P 〇werPC 440处理器 在片上集成了网卡设备,支持M il 接口,可以实现10/100Mbps 的全双工或半双工通信功能。

同时网卡设备采用了乒乓数据 流工作模式,发送buffer 和接收buffer 均有ping 和pong 两个 通道,大大提高了数据的传输能力。

2网卡驱动的设计与实现本文结合实际项目基于天脉1操作系统的TCP /I P 网络 协议栈组件在P 〇werPC 440处理器平台上实现了以太网通信 功能,因此需要针对P 〇werPC 440处理器平台设计配套的网卡 驱动。

天脉1操作系统的网络协议栈模型结构如图1所示M 。

图1天脉1操作系统的网络协议栈模型由于驱动功能层的存在,协议驱动程序和网卡驱动程序 之间相互独立,大大简化了网络设备增加和网络组件扩展的 复杂度[3]。

目前网络协议栈主要支持增强型的网络设备驱动 (EnhancedNetworkDriver ,END )。

针对天脉1的网络协议桟 模型,本文设计的网卡驱动需要实现以下功能:(1) E N D 设备驱动程序的装载;(2) 启动E N D 设备;(3) 网络数据的接收;(4) 网络数据的发送。

2.1 E N D 设备驱动程序的装载E N D 设备驱动程序的装载主要就是完成E N D 设备驱动 程序与驱动功能抽象层的挂接,使得网络协议栈实现对END 设备的控制。

具体过程包括:①初始化网卡和P H Y 设备,配 置网卡和P H Y 设备的通信参数等;②为网卡控制结构分配空 间同时初始化END _O B J 结构,END _O B J 结构主要包括网卡 控制结构以及与网&协议栈相关的参数信息;③对网卡驱动 对应的参数串进行解析和处理;④为接收数据分配空间,保证 接收数据的存放;⑤通过配置END_OB J 结构中的NET _FUN - C S 参数实现网卡驱动与网络协议&的挂接。

2.2启动E N D 设备END 设备的启动过程主要包括中断处理程序的挂接和使 能网卡中断。

对于网卡设备来说,其处理数据的方式可分为 中断和轮询两种工作模式[4],在E N D 设备启动过程中,将接收 数据和发送数据均设置为中断模式,并挂接接收和发送数据 的中断处理程序,最后使能网卡中断、接收和发送中断,则可 完成E N D 设备的启动。

2.3网络数据包的接收对于网络数据包的接收来说,天脉1操作系统的网络协 议栈无需网卡驱动实现对网络数据包的处理。

当网卡设备接 收到数据后,其会产生一个接收中断,在接收中断处理程序中, 程序会调用neUobAdd 函数启动一个任务程序将网卡设备接 收到的数据传递给驱动功能抽象层,网络协议栈通过驱动功 能抽象层的接收函数获取到网络数据包并进行相应的数据处 理。

此处利用netJobAdd 函数可以大大减少接收中断的处理 时间,提高网络数据的接收能力。

2.4网络数据包的发送对于网络数据包的发送来说,当网络协议桟发送数据时, 其会将数据放置到缓冲区中,并通过调用驱动功能抽象层的 发送函数将缓冲区中的数据发送给网卡设备,网卡设备接收 到数据后就将其置于发送buffer 中等待数据的发送。

3驱动测试为验证设计的网卡驱动的可用性和正确性,本文利用 PowerPC 440目标机、以太网交换机和P C 机搭建了网络测试 环境,具体的网络测试环境如图2所示。

在测试中,配置P C 机的I P 为10.5.236.100,交换机的IP 网络协驱动网s s l125基于门控循环单元的语音识别研究张忠豪,孙水发(三峡大学水电工程智能视觉监測湖北省重点实验室,湖北宜昌443002)摘要:针对传统门控循环单元的梯度消失问题,文章提出结合批标准化的同时将饱和激活函数替换为非饱和激活函数,更好的缓解网络发生梯度消失问题。

文中通过实验结果表明,相比传统的模型结构,改进后的模型拥有更高的识别率,同时也没有增加算法运行时间。

关键词:语音识别;深度学习;门控循环单元;激活函数;批标准化中图分类号:TN912 文献标识码:A文章编号:1673-1131(2019)03-0126-03Research on speech recognition based on gated recurrent unitZhang Zhonghao, Sun Shuifa(China Three Gorges University Hubei Key Laboratory o f I ntelligent\^sion Based Monitcoiiig for Hydroelectric Engineering,Yichang443002, China)Abstract:In order to solve the vanishing gradient problem o f traditional Gated Recurrent Unit,this paper proposes to replace saturated activation functions with non-saturated activation functions,and at the same time combine batch narmalizatioii to better avoid vanishing gradient o f t he models.Our expenments show that compared with the traditional models,the proposed model has a higher correct recognition rate and doesn't increase the running time o f t he algorithm.K ey words:speech recognition;deep leaming;GRU;activatictn functions;batch normalization0引言深度学习是一种新兴的技术,被认为是达到更髙水平人工智能最有前途的方向之一气目前,深层神经网络(de印neural network^DNN)、卷积神经网络 (Convolutional Neural Net- workj C NN)、循环神经网络(Recurrent Neural NetworkjRNN) 等深度神经网络模型被广泛应用于生物信息、计算机视觉、机器翻译、自然语言处理以及语音领域^由于语音信号是连续的,所以在涉及语音的领域中使用 K N N来处理是非常合适的。

因为R N N能正确捕获长期依赖 关系,一些研究已经展现了 RNN在语音识别1^1、语音増强[4语音分离151以及语音活性检测等多种语音任务中取得很好的效果。

其中,在语音识别方面,深度学习技术显著的超过了传统的髙斯混合隐马尔可夫模型(Gaussian o f Mixture Hidden Markov ModeLGMM-HMM) 模型然而,训练传统的RN N可能会因为梯度消失和梯度爆炸而产生糟糕的后果,同时也削弱了学习长期依赖[7]的能力。

于 是,人们提出了长短期记忆网络(Long Short-Term Memory,L S IM) 01来缓解梯度消失和梯度爆炸。

虽然L ST M是有效的, 但是L S T M的结构繁琐复杂,于是研究人员将L S T M改进而 提出了著名的门控循环单元(Gated Recurrent U nit GRU) w,为10.5_236.253,目标机的IP为10_5.236.166,同时配置子网掩 4结语码为255.255.255,0保证目标机和P C机在同一网段。

当目标 机上电后,;PowerPC440处理器会进入以太网通信状态。

此时,本文利用网络协议栈测试程序进行P C机和目标机之间的通 信。

首先启动主机端测试程序,在测试程序中完成主机端和 目标机端的EP地址配置后,运行目标机端的测试程序来测试主机和目标机之间的通信,通信结果如图3所示。

本文结合实际项目开发,基于天脉1操作系统的网络协议栈组件在PowerPC440处理器平台上设计实现了配套的P〇werPC440处理器的网卡驱动程序,并完成了网卡驱动程序的测试。

测试结果表明本文设计的PowerPC440网卡驱动程序功能正确,网卡工作正常,可以稳定地完成以太网通信功能。

参考文献:[1]宋晓翠,张晋宁.基于P〇werPC440的嵌入式系统设计与研究[J]■电子元器件应用,2009(7):19-22.[2]梅涛,黄保垒,徐晓光.嵌入式系统网卡驱动模型设计与实现[J].电子纖,2016…29(4):111-115.[3]孙照林.实时嵌入式网络协议栈的研究与优化[D].北京邮电大学,2014.[4]梅涛,王宏伟,麦先根.天脉1下龙芯1B网卡驱动设计与实现[J].电子科技,2016,29(10>:54~57.图3通倍测试结果从实验结果可以看出主机端和目标机端之间的通信稳定,作者简介:张前(1994-),男,山西忻州人,硕士,助理工程师,研表明本文设计的P〇werPC440网卡驱动功能正确,网卡工作正 究方向:软件设计与研发。