VGA显示控制实验及原理

实验9 VGA显示控制器实验

实验9 VGA显示控制器实验1、实验目的:1)理解VGA显示的基本原理。

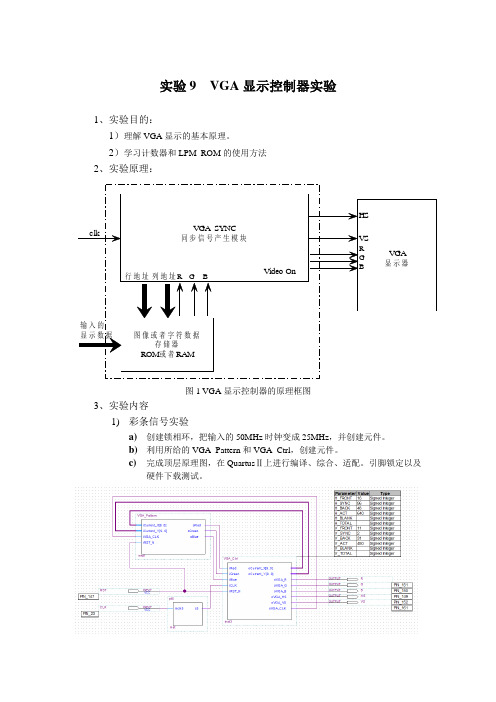

2)学习计数器和LPM_ROM的使用方法2、实验原理:图1 VGA显示控制器的原理框图3、实验内容1)彩条信号实验a)创建锁相环,把输入的50MHz时钟变成25MHz,并创建元件。

b)利用所给的VGA_Pattern和VGA_Ctrl,创建元件。

c)完成顶层原理图,在QuartusⅡ上进行编译、综合、适配。

引脚锁定以及硬件下载测试。

2)显示自己的姓实验。

修改VGA_Pattern,利用if语句控制相应区域的相应值,在QuartusⅡ上进行编译、综合、适配。

引脚锁定以及硬件下载测试。

3)显示数字实验a)创建lpm_rom,手动输入“0”的mif文件。

b)顶层文件为numTop.v,在QuartusⅡ上进行编译、综合、适配,硬件下载测试。

4)计数显示实验a)创建“1~9”的lpm_rom,mif文件已给出。

b)加入计数器。

c)完成顶层文件,在QuartusⅡ上进行编译、综合、适配,硬件下载测试。

5)数字钟实验在4)基础上加入位置控制,完成顶层文件,在QuartusⅡ上进行编译、综合、适配,硬件下载测试。

6)显示理工校徽实验(2)moduleVGA_Pattern(//HostSideoRed,oGreen,oBlue,iCurrent_X,iCurrent_Y,iVGA_CLK,iRST_N); // Host Sideoutput reg oRed;output reg oGreen;output reg oBlue;input [9:0] i Current_X;input [9:0] i Current_Y;// Control Signalinput iVGA_CLK;input iRST_N;always@(posedge iVGA_CLK or negedge iRST_N)beginif(!iRST_N)beginoRed <= 0;oGreen <= 0;oBlue <= 0;endelsebeginif((( iCurrent_Y>60)&& (iCurrent_Y <80))&&((iCurrent_X>200)&&(iCurrent_X <400)))beginoRed <= 1;oGreen <= 0;oBlue <= 0;endelse if((( iCurrent_Y>80)&& (iCurrent_Y <240))&&((iCurrent_X>200)&&(iCurrent_X <240)))beginoRed <= 1;oGreen <= 0;oBlue <= 0;end/*else if((( iCurrent_Y>150)&& (iCurrent_Y <170))&&((iCurrent_X>260)&&(iCurrent_X <340)))/*else if((150 < iCurrent_Y < 170)&&(260<iCurrent_X < 340))beginoRed <= 1;oGreen <= 0;oBlue <= 0;endelse if((( iCurrent_Y>170)&& (iCurrent_Y <240))&&((iCurrent_X>290)&&(iCurrent_X <310)))/*else if((170 < iCurrent_Y < 240)&&(290 < iCurrent_X < 310))beginoRed <= 1;oGreen <= 0;oBlue <= 0;end*/else if((( iCurrent_Y>240)&& (iCurrent_Y <260))&&((iCurrent_X>200)&&(iCurrent_X <400)))/*else if((240 < iCurrent_Y < 260)&&(150 < iCurrent_X < 450))*/beginoRed <= 1;oGreen <= 0;oBlue <= 0;endelsebeginoRed <= 0;oGreen <= 0;oBlue <= 0;endendendendmodule(3)(4)module numTop1(CLK,RST,R,G,B,HS,VS); input CLK,RST;output R,G,B,HS,VS;wire clk25Mhz,vga_clk;wire [9:0]ram_data;wire [9:0] X,Y;wire [6:0] ram_addr;wire [3:0]COUNT;wire carry1;wire CLK1HZ;reg vga_data;assign ram_addr = {Y[5:2],X[4:2]};altPLL0 u1(CLK,clk25Mhz);VGA_Ctrl u2(.iRed(vga_data),.iGreen(vga_data),.iBlue(vga_data),.oCurrent_X(X),.oCurrent_Y(Y),// VGA Side.oVGA_R(R),.oVGA_G(G),.oVGA_B(B),.oVGA_HS(HS),.oVGA_VS(VS),.oVGA_CLK(vga_clk),// Control Signal.iCLK(clk25Mhz),.iRST_N(RST) ); demo_shuzi u17(ram_addr,vga_clk,ram_data[0]); ROM1 u21(ram_addr,vga_clk,ram_data[1]);ROM2 u14(ram_addr,vga_clk,ram_data[2]);ROM3 u15(ram_addr,vga_clk,ram_data[3]);ROM4 u6(ram_addr,vga_clk,ram_data[4]);ROM5 u7(ram_addr,vga_clk,ram_data[5]);ROM6 u8(ram_addr,vga_clk,ram_data[6]);ROM7 u9(ram_addr,vga_clk,ram_data[7]);ROM8 u10(ram_addr,vga_clk,ram_data[8]);ROM9 u11(ram_addr,vga_clk,ram_data[9]);/*demo_shuzi u3(ram_addr,vga_clk,ram_data);*/ GeneralCnt #(4,9) u4(CLK1HZ,RST,1,COUNT,carry1); ClkDiv #(26,50000000) u5(CLK,RST,CLK1HZ);always@(X,Y)if(X<32 && Y<64)vga_data=ram_data[COUNT];else if(X<64 && Y<64)vga_data=ram_data[COUNT];elsevga_data=0;endmodule//任意倍整数分频器module ClkDiv(clk_in,rst_n,clk_out);parameter MSB = 4, DIV_TIMES = 10;input clk_in,rst_n;output clk_out;reg clk_out;reg [MSB-1:0] count;always @(negedge rst_n or posedge clk_in)beginif(rst_n==0)begincount<=0;endelsebeginif(count < (DIV_TIMES-1))count<=count+1'b1;elsecount<=0;endendalways @(negedge rst_n or posedge clk_in) beginif(rst_n==0)beginclk_out<=1'b0;endelsebeginif(count<(DIV_TIMES>>1))clk_out<=1'b0;elseclk_out<=1'b1;endendendmodule//通用计数器module GeneralCnt(clk,reset_n,ena,cnt,carry_out);parameter MSB = 4, CNT_END = 9; input clk;input reset_n;input ena;output [MSB-1:0]cnt;output carry_out;reg [MSB-1:0]cnt;reg carry_out;//计数always@(posedge clk or negedge reset_n) beginif(!reset_n)cnt <= 0;else if(ena && cnt==CNT_END)cnt <= 0;else if (ena && cnt < CNT_END)cnt <= cnt + 1'b1;end//产生进位输出always@(posedge clk or negedge reset_n) begin if(!reset_n)carry_out <= 1'b0;else if(ena && cnt==CNT_END)carry_out <= 1'b1;elsecarry_out <= 1'b0;endendmodule。

实验一 VGA显示模式的实现

实验报告(报告要存档,请单面打印)姓名陈梓杰学号201131120207 专业电子信息科学与技术班级2班一、设计/实验项目名称:VGA显示模式的实现基本内容描述:多功能计数器具有异步清零、同步使能功能,计数满12进位,进位位输出高电平。

清零端RST;使能端EN;进位输出COUT。

二、电路设计及原理多功能计数器VHDL程序如下所示:生成RTL电路图如下:多功能计数器实现12进制异步清零、同步使能功能。

异步清零RST、同步使能EN接按键,低电平触发有效。

在时钟上升沿,计数器计数到11时,计数器自动清零,开始下一个计数。

当异步清零RST为‘0’时,输出端DOUT218输出为“0000”,即异步清零RST为低电平时有效;否则,如果在上升沿时钟和同步计数使能ENA有效(ENA=‘1’)时,允许计数。

当计数达到“1011”时,表明已经达到12进制的最大值,向进位端COUT输出一个高电平,在下一个上升沿来到的时候,计数将清零,并重新开始计数。

另一种情况就是,当时钟为上升沿而同步计数使能ENA却无效(ENA=‘0’)时,计数功能是不允许的。

三、设计电路仿真与分析多功能计数器仿真图如下所示:由仿真图可看出,当RST和ENA同时为高电平时,允许计数,对时钟CLK的上升沿进行计数。

当计数到12进制的最大值(图中对应为“1011”)时,COUT端将输出一个高电平,表示有进位。

下一个上升沿到来时,计数将清零。

当RST为低电平时,计数清零,不依赖于上升沿时钟。

当ENA为低电平时,不允许计数,输出值保持不变,直到ENA为高电平时继续计数。

四、SIGNALTAP II硬件信号的采集与分析仿真分析通过后,将设计方案下载到FPGA中,通过SIGNALTAP II对多功能计数器进行采集,采集波形如下图所示:五、实验结论由仿真试验可知:(1)设计功能正确,实现4位12进制计数器的功能;(2)异步清零信号为低电平有效,同步使能ENA要保持高电平时才允许计数;(3)当计数达到12进制的最大值时,进位端COUT会输出一个高电平。

10-实验报告

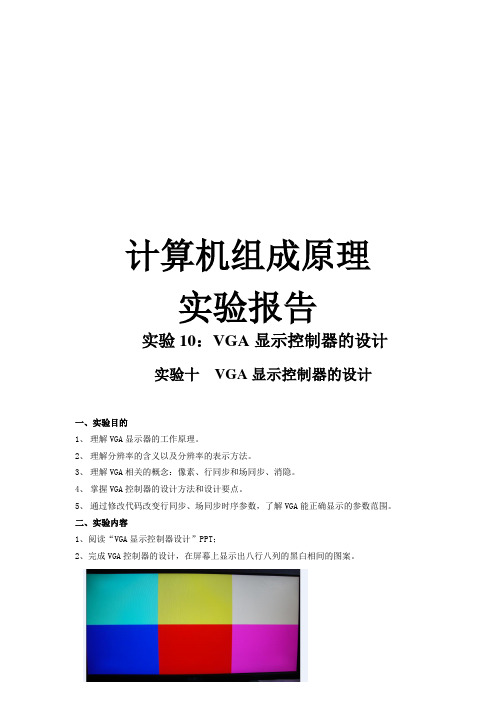

计算机组成原理实验报告实验10:VGA显示控制器的设计实验十VGA显示控制器的设计一、实验目的1、理解VGA显示器的工作原理。

2、理解分辨率的含义以及分辨率的表示方法。

3、理解VGA相关的概念:像素、行同步和场同步、消隐。

4、掌握VGA控制器的设计方法和设计要点。

5、通过修改代码改变行同步、场同步时序参数,了解VGA能正确显示的参数范围。

二、实验内容1、阅读“VGA显示控制器设计”PPT;2、完成VGA控制器的设计,在屏幕上显示出八行八列的黑白相间的图案。

3、掌握PLL的定制方法。

4、在2的基础上,调整屏幕分辨率,将原来640*480的分辨率,通过修改代码改变行同步、场同步时序参数,变成1280*1024的分辨率,帧频不变,均为60HZ。

为了满足显示的需要,需要用PLL将50MHz的频率倍频到108MHz。

5、利用VGA+ROM的结构显示给定图片。

6、利用VGA+ROM的结构显示字符,要求通过修改代码可以实现各种显示效果:改变字符颜色和大小;改变字符位置;其它显示效果。

7、在屏幕上显示一个4*4的红色小球,控制小球从左上至右下移动小球,也可以选择其它的运动轨迹。

三、实验仪器及设备:一、PC机二、 QuartusⅡ 9.0 三、 DE2-70 四、显示器四、实验步骤1、阅读“VGA显示控制器设计”PPT,理解VGA显示器的工作原理、分辨率的含义以及分辨率的表示方法和VGA相关的概念:像素、行同步和场同步、消隐。

2、认真阅读显示出八行八列的黑白相间的图案的verilog代码(640*480的分辨率),掌握编写类似代码的思路。

3、修改给定的分辨率为1280*1024的代码,显示出实验要求的黑白格团。

主要修改三点:a、x和y的位数,由于分辨率要达到1280,所以x和y的位数至少要有 11位。

b、修改输入频率,把25MHZ改为108MHZ(通过宏模块)。

c、always显示输出模块内有一些问题,需要作相应修改。

数电实验-vga图像显示控制

数字电路综合实验报告学校:北京邮电大学学院:信息与通信工程学院专业:通信工程班级:2008211115学号:********班内序号:30姓名:***2011年1月5日VGA图像显示控制器一、摘要和关键词摘要:VGA显示屏显示采用逐行扫描的方式解决,阴极射线枪发出电子束打在涂有荧光粉的荧光屏上,产生GRB基色,合成一个彩色像素。

扫描从屏幕的左上方开始,从左到右,从上到下,逐行扫描,每扫完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信号进行行同步;扫描完所有行,用场同步信号进行场同步,并使扫描回到屏幕的左上方,同时进行场消隐,并预备进行下一次的扫描。

通过控制扫描计数器不同值时对RGB三原色信号的控制,来完成显示设计。

关键词:行列扫描行列同步RGB三原色控制二、设计任务要求实验目的1. 熟练掌握VHDL 语言和QuartusII 软件的使用;2. 理解状态机的工作原理和设计方法;3. 掌握利用EDA 工具进行自顶向下的电子系统设计方法;4. 熟悉VGA 接口协议规范。

实验要求:设计一个VGA 图像显示控制器,达到如下功能:显示模式为640×480×60HZ 模式;用拨码开关控制R、G、B(每个2 位),使显示器可以显示64种纯色;在显示器上显示横向彩条信号(至少6 种颜色);在显示器上显示纵向彩条信号(至少8 种颜色);在显示器上显示自行设定的图形、图像等。

选做:自拟其它功能。

三、实验原理1、显示控制原理常见的彩色显示器一般由阴极射线管(CRT)构成,彩色由GRB(Green Red Blue)基色组成。

显示采用逐行扫描的方式解决,阴极射线枪发出电子束打在涂有荧光粉的荧光屏上,产生GRB基色,合成一个彩色像素。

扫描从屏幕的左上方开始,从左到右,从上到下,逐行扫描,每扫完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT、对电子束进行消隐,每行结束时,用行同步信号进行行同步;扫描完所有行,用场同步信号进行场同步,并使扫描回到屏幕的左上方,同时进行场消隐,并预备进行下一次的扫描。

VGA显示系统设计

《电子系统综合设计》课程设计报告VGA显示系统设计专业:集成电路班级:电子0 6 0 4学号:200681131姓名:高丕龙一.实验目的:1、根据VGA视频信号时序,利用FPGA控制产生视频信号,在普通彩色显示器上显示8色彩色图像。

2、在显示器上显示自行设计的彩色规则图形——棋盘形。

二.实验原理:1概述该系统实现的目标是将数据源写入视频存储器中的视频数据通过D/A转换器输出给VGA显示器,从而得到预期的视频显示。

按照这个目的,FPGA作为整个设计的核心,负责产生正确的行同步信号和场同步信号输出给VGA显示器,使VGA显示器能够正确的同步:负责进行水平、垂直计数,并将计数器的值或行、场同步信号转换成存储器的地址数据输出给视频存储阵列,使视频存储阵列能够正确的输出图像的颜色信息:负责根据同步时序控制D/A转换器及时的把视频存储阵列输出的颜色的数字量转换成模拟量送给VGA显示器。

FPGA是整个系统的中枢,在FPGA内部,主要有两个模块:一个是时序生成模块,另一个是地址产生模块。

它根据外部时钟CLK进行计数,并根据计数器的值来确定行、场所处的位置,并依此产生以下信号:行同步信号(Hs),场同步信号(Vs),地址信号,和输出允许信号。

其中,行同步信号和场同步信号是严格的周期信号,直接送给通过VGA接口相连的VGA显示器做同步使用。

只要连接这两个信号就完全可以点亮显示器,只不过在显示器上没有任何的颜色信息。

输入允许段一共有两个,一个是视频存储阵列的输出允许端,它控制视频存储阵列锁存地址线上的地址对应单元的数据。

另外一个输出允许端是控制D/A转换阵列的。

视频存储阵列是由三块容量和参数一样的双口RAM堆叠而成,三块RAM是独立的并列关系。

它们每一块负责存储三原色中一种颜色的数字量。

三块RAM 分别存储红(R),绿(G),蓝(B)分量。

双口RAM输入端的地址和数据全部来自CPU或外部的数据采集源,输出端的地址由FPGA产生,而数据则直接输出给视频D/A转换阵列。

VGA显示原理

LCD显示原理LCD(Liquid Crystal Display)也就是我们俗称的液晶显示器,LCD不光应用在显示器方面,而且像电子表、手持游戏机以及PDA等产品中都能见到LCD的影子。

LCD可分为扭曲向列型(TN-LCD)、超扭曲向列型(STN-LCD)、薄膜晶体管(TFT-LCD)等几种,现在笔记本电脑上和绝大多数桌面型LCD都是TFT-LCD,它已经成为目前液晶显示器的主要发展方向。

就像CRT的主要部件是显像管一样,LCD的主要部件是它的液晶板,液晶板包含两片无钠玻璃素材(Substrates),中间夹着一层液晶,当光束通过这层液晶时,液晶体会并排或呈不规则扭转形状,所以液晶更像是一个个闸门,选择光线穿透是否,我们才能在屏幕看到深浅不一,错落有致的图像。

从逻辑的角度分析重要参数如下:一、点距我们常问到液晶显示器的点距是多大,但是多数人并不知道这个数值是如何得到的,现在让我们来了解一下它究竟是如何得到的。

举例来说一般14英寸LCD的可视面积为285.7 mm ×214.3 mm,它的最大分辨率为1024×768(LCD的最大分辨率就是它的真实分辨率,也就是最佳分辨率液晶显示器都只有一个最佳的分辨率调成其他的画质会很差),那么点距就等于:可视宽度/水平像素(或者可视高度/垂直像素),即285.7mm/1024=0.279mm (或者是214.3mm/768=0.279mm)。

二、色彩度LCD重要的当然是的色彩表现度。

我们知道自然界的任何一种色彩都是由红、绿、蓝三种基本色组成的。

比如:14 英寸LCD面板上是由1024×768个像素点组成显像的,每个独立的像素色彩是由红、绿、蓝(R、G、B)三种基本色来控制。

大部分厂商生产出来的液晶显示器,每个基本色(R、G、B)达到6位,即64种表现度,那么每个独立的像素就有64 ×64×64=262144种色彩。

精华资料图片的VGA显示的实验报告

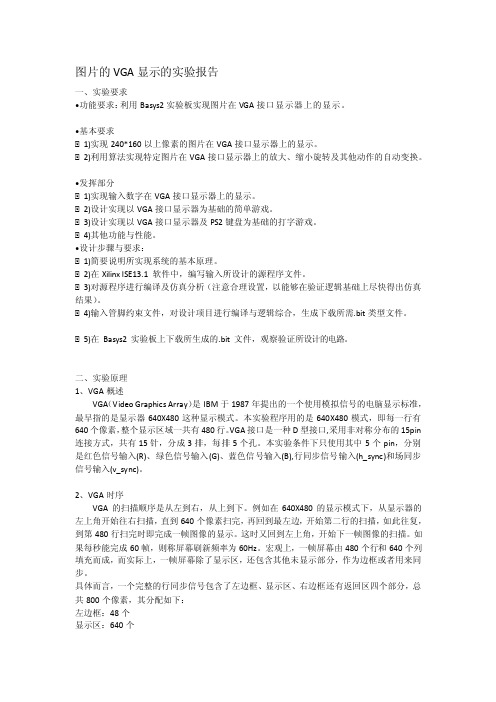

图片的VGA显示的实验报告一、实验要求•功能要求:利用Basys2实验板实现图片在VGA接口显示器上的显示。

•基本要求1)实现240*160以上像素的图片在VGA接口显示器上的显示。

2)利用算法实现特定图片在VGA接口显示器上的放大、缩小旋转及其他动作的自动变换。

•发挥部分1)实现输入数字在VGA接口显示器上的显示。

2)设计实现以VGA接口显示器为基础的简单游戏。

3)设计实现以VGA接口显示器及PS2键盘为基础的打字游戏。

4)其他功能与性能。

•设计步骤与要求:1)简要说明所实现系统的基本原理。

2)在Xilinx ISE13.1 软件中,编写输入所设计的源程序文件。

3)对源程序进行编译及仿真分析(注意合理设置,以能够在验证逻辑基础上尽快得出仿真结果)。

4)输入管脚约束文件,对设计项目进行编译与逻辑综合,生成下载所需.bit类型文件。

5)在Basys2实验板上下载所生成的.bit文件,观察验证所设计的电路。

二、实验原理1、VGA概述VGA(Video Graphics Array)是IBM于1987年提出的一个使用模拟信号的电脑显示标准,最早指的是显示器640X480这种显示模式。

本实验程序用的是640X480模式,即每一行有640个像素,整个显示区域一共有480行。

VGA接口是一种D型接口,采用非对称分布的15pin 连接方式,共有15针,分成3排,每排5个孔。

本实验条件下只使用其中5个pin,分别是红色信号输入(R)、绿色信号输入(G)、蓝色信号输入(B),行同步信号输入(h_sync)和场同步信号输入(v_sync)。

2、VGA时序VGA的扫描顺序是从左到右,从上到下。

例如在640X480的显示模式下,从显示器的左上角开始往右扫描,直到640个像素扫完,再回到最左边,开始第二行的扫描,如此往复,到第480行扫完时即完成一帧图像的显示。

这时又回到左上角,开始下一帧图像的扫描。

如果每秒能完成60帧,则称屏幕刷新频率为60Hz。

vga显示实验报告

VGA显示实验报告●技术资料对于普通的VGA 显示器,其引出线共含五个信号:●R、G、B:三基色信号。

●HS:行同步信号。

●VS:场同步信号。

VGA工业标准要求的频率:产生时钟频率25.175 MHz(像素输出的频率)行频31469 Hz 场频59.94 Hz(每秒图像刷新频率)VGA显示的关键是行、场扫描时序的产生。

显示器扫描方式分为逐行扫描和隔行扫描:逐行扫描是扫描从屏幕左上角一点开始,从左像右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信号进行同步;当扫描完所有的行,形成一帧,用场同步信号进行场同步,并使扫描回到屏幕左上方,同时进行场消隐,开始下一帧。

隔行扫描是指电子束扫描时每隔一行扫一线,完成一屏后在返回来扫描剩下的线,隔行扫描的显示器闪烁的厉害,会让使用者的眼睛疲劳。

完成一行扫描的时间称为水平扫描时间,其倒数称为行频率;完成一帧(整屏)扫描的时间称为垂直扫描时间,其倒数称为场频率,即刷新一屏的频率,常见的有60Hz,75Hz等等。

标准的VGA显示的场频60Hz,行频31.5KHz。

行场消隐信号:是针对老式显像管的成像扫描电路而言的。

电子枪所发出的电子束从屏幕的左上角开始向右扫描,一行扫完需将电子束从右边移回到左边以便扫描第二行。

在移动期间就必须有一个信号加到电路上,使得电子束不能发出。

不然这个回扫线会破坏屏幕图像的。

这个阻止回扫线产生的信号就叫作消隐信号,场信号的消隐也是一个道理。

显示带宽:带宽指的显示器可以处理的频率范围。

如果是60Hz刷新频率的VGA,其带宽达640x480x60=18.4MHz,70Hz的刷新频率1024x768分辨率的SVGA,其带宽达1024x768x70=55.1MHz。

时钟频率:以640x480@59.94Hz(60Hz)为例,每场对应525个行周期(525=10+2+480+33),其中480为显示行。

VGA显示实验报告——孙小喃

学生实验报告实验课名称:VHDL硬件描述语言实验项目名称:VGA显示专业名称:电子科学与技术班级:32050801学号:05学生姓名:孙小喃教师姓名:程鸿亮2010年11月13日组别第三组实验日期2010年11月13日实验室名称______________成绩_____ 一.实验名称VGA显示二.实验目的与要求目的:通过对VGA接口的显示控制设计,理解VGA接口的时序工作原理,掌握通过计数器产生时序控制信号的方法以及用MEGEFUNCTION制作锁相环的方法。

要求:通过VHDL编程,在VGA显示器上实现竖形彩条的显示,显示模式为640×480 60Hz刷新率。

本实验需要使用25MHz的时钟,而开发平台中并没有这个时钟资源,所以需要通过锁相环来实现。

三实验内容1. 打开QuartusII软件,建立一个新的工程:1) 单击菜单File\New Project Wizard…2) 输入工程的路径、工程名以及顶层实体名。

3) 单击Next>按钮,出现以下窗口由于我们建立的是一个空的项目,所以没有包含已有文件,单击Next>继续。

4) 设置我们的器件信息:5) 单击Next>,指定第三方工具:这里我们不指定第三方EDA工具,单击Next>后结束工程建立。

2. 建立VHDL文件:1) 单击File\New菜单项,选择弹出窗口中的VHDL File项,单击OK 按钮以建立打开空的VHDL文件,注意此文件并没有在硬盘中保存。

2) 首先编制实体“color”的代码,要求输入为25MHz的时钟信号,输出为行同步、帧同步以及三色数据线RGB[2..0]信号。

注意这个文件的实体名、文件名为“color”,不是顶层实体。

(参考程序附后)3) 生成符号由于此文件是整个工程的一个模块,我们需要把此文件转换为符号,以便后面可以通过绘图方式连接电路,点击File\Creat\Update\Create Symbol Files for Current File菜单,生成对应的符号。

实验九 VGA彩条信号显示

实验九VGA彩条信号显示控制器设计1.实验目的:学习VGA彩条信号发生器的设计。

2.实验内容设计并调试好一个VGA彩条信号发生器,并用EDA实验开发系统(拟采用的实验芯片的型号可选Altera CycloneII系列的EP2C5T144C8 FPGA,)进行硬件验证。

(1)R,G,B:三基色信号HS:行同步信号VS:场同步信号VGA工业标准要求的频率:时钟频率25.175MHz行频31469Hz场频59.94Hz(2)程序可参照书本P177(3)实验程序:通过对彩条模式选择按键的控制来改变彩条模式, 可产生竖彩条、横彩条、棋盘格等多种彩条模式。

出来的彩条信号并不是书里要求的按照横条,竖条,棋盘分布,而是按照棋盘,竖条,横条分布,原因是程序执行时是离进程最近的最先执行,可以通过修改程序把希望最先显示的信号放在离进程最近的地方。

由于受到存储器件容量的限制,本设计中存储的图像数据所采用的像素位深为3位,共可显示8种颜色。

在实际应用中,可以使用更大的存储器,最终实现256色图像,乃至真彩色图像的显示。

LIBRARY IEEE; -- 显示器彩条发生器USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY COLOR ISPORT ( CLK, MD : IN STD_LOGIC;HS, VS, R, G, B : OUT STD_LOGIC ); -- 行场同步/红,绿,兰END COLOR;ARCHITECTURE behav OF COLOR ISSIGNAL HS1,VS1,FCLK,CCLK : STD_LOGIC;SIGNAL MMD : STD_LOGIC_VECTOR(1 DOWNTO 0);-- 方式选择SIGNAL FS : STD_LOGIC_VECTOR (3 DOWNTO 0);SIGNAL CC : STD_LOGIC_VECTOR(4 DOWNTO 0); --行同步/横彩条生成SIGNAL LL : STD_LOGIC_VECTOR(8 DOWNTO 0); --场同步/竖彩条生成 SIGNAL GRBX : STD_LOGIC_VECTOR(3 DOWNTO 1);-- X横彩条SIGNAL GRBY : STD_LOGIC_VECTOR(3 DOWNTO 1);-- Y竖彩条SIGNAL GRBP : STD_LOGIC_VECTOR(3 DOWNTO 1);SIGNAL GRB : STD_LOGIC_VECTOR(3 DOWNTO 1);BEGINGRB(2) <= (GRBP(2) XOR MD) AND HS1 AND VS1;GRB(3) <= (GRBP(3) XOR MD) AND HS1 AND VS1;GRB(1) <= (GRBP(1) XOR MD) AND HS1 AND VS1;PROCESS( MD )BEGINIF MD'EVENT AND MD = '0' THENIF MMD = "10" THEN MMD <= "00";ELSE MMD <= MMD + 1; --三种模式END IF;END IF;END PROCESS;PROCESS( MMD )BEGINIF MMD = "00" THEN GRBP <= GRBX; -- 选择横彩条ELSIF MMD = "01" THEN GRBP <= GRBY; -- 选择竖彩条ELSIF MMD = "10" THEN GRBP <= GRBX XOR GRBY; --产生棋盘格ELSEGRBP <= "000";END IF;END PROCESS;PROCESS( CLK )BEGINIF CLK'EVENT AND CLK = '1' THEN -- 12MHz 13分频IF FS = 12 THEN FS <= "0000";ELSEFS <= (FS + 1);END IF;END IF;END PROCESS;FCLK <= FS(3);PROCESS( FCLK )BEGINIF FCLK'EVENT AND FCLK = '1' THENIF CC = 29 THEN CC <= "00000";ELSECC <= CC + 1;END IF;END IF;END PROCESS;CCLK <= CC(4);PROCESS( CCLK )BEGINIF CCLK'EVENT AND CCLK = '0' THENIF LL = 481 THEN LL <= "000000000";ELSELL <= LL + 1;END IF;END IF;END PROCESS;PROCESS( CC,LL )BEGINIF CC > 23 THEN HS1 <= '0'; --行同步ELSEHS1 <= '1';END IF;IF LL > 479 THEN VS1 <= '0'; --场同步ELSEVS1 <= '1';END IF;END PROCESS;PROCESS(CC, LL)BEGINIF CC < 3 THEN GRBX <= "111"; -- 横彩条ELSIF CC < 6 THEN GRBX <= "110";ELSIF CC < 9 THEN GRBX <= "101";ELSIF CC < 12 THEN GRBX <= "100";ELSIF CC < 15 THEN GRBX <= "011";ELSIF CC < 18 THEN GRBX <= "010";ELSIF CC < 21 THEN GRBX <= "001";ELSE GRBX <= "000";END IF;IF LL < 60 THEN GRBY <= "111"; -- 竖彩条ELSIF LL < 120 THEN GRBY <= "110";ELSIF LL < 180 THEN GRBY <= "101";ELSIF LL < 240 THEN GRBY <= "100";ELSIF LL < 300 THEN GRBY <= "011";ELSIF LL < 360 THEN GRBY <= "010";ELSIF LL < 420 THEN GRBY <= "001";ELSE GRBY <= "000";END IF;END PROCESS;HS <= HS1 ; VS <= VS1 ;R <= GRB(2) ;G <= GRB(3) ; B <= GRB(1);END behav;选择模式5CLK 选CLOCK0 ,对应引脚PIN_89 选用12MHzMD 选PIN48 ,对应引脚PIN_8. 键1R 选PIN40 ,对应引脚PIN_99.G 选PIN41 ,对应引脚PIN_100 .B 选PIN42 ,对应引脚PIN_101.HS 选PIN43 ,对应引脚PIN_103VS 选PIN44 ,对应引脚PIN_104.由于本次实验要用到两台显示器,请1号机房的同学将编译成功仿真成功的代码拷贝到第21台电脑上运行。

VGA控制显示实验说明文档

VGA控制显示实验本实验是在VGA基本控制之上的更进一步的对VGA显示进行控制的。

1.VGA显示原理常见的彩色显示器一般由CRT(阴极射线管)构成,彩色是由R(红),G(绿),B(蓝)3基色组成。

显示采用逐行扫描的方式,阴极射线枪发出的电子束打在涂有荧光粉的荧光屏上,产生RGB三色基,最后合成一个彩色图像。

从屏幕的左上方开始自左向右的扫描,每扫完一行电子束回到下一行的最左端,每行结束后电子枪回扫的过程中进行消隐。

然后从新开始行扫描,消隐,直到扫描到屏幕的右下方,电子书回到屏幕的左上方重新开始新的图像扫描,并且在回到屏幕的左上方过程中进行消隐,在消隐的过程中不发射电子束。

每一行扫描结束时,用HS(行同步)信号进行同步;扫描完所有的行后用VS(场同步)信号进行同步。

2.VGA实验功能说明本实验设计是基于FPGA的VGA接口控制器,通过对FPGA硬件编程实现显示驱动,通过VGA接口在显示器上显示彩条,圆环和动态方块信号。

实现显示驱动需要5个信号:R,G,B,hsyncb,vsyncb,其中R,G,B分别为红,绿,蓝颜色的强度信号,hsyncb和vsyncb 为行同步和场同步信号,均为模拟信号。

由实验板将FPGA输出直接与VGA接口相连,中间没有D/A转换电路,因此这五个信号实际上均为数字信号。

hsyncb和vsyncb可用数字信号等效;R,G,B分别用3位数字信号表示。

用于显示驱动的行,场同步信号利用实验板的50MHz系统时钟产生。

VGA接口控制器由三个模块组成,即产生行场同步信号和消隐信号的VGASig模块,产生内容和位置信息的ColorMap模块,产生动态时序信号的count16以及顶层模块VGACore,模块之间的信号连接如图:本设计的整体思想是:首先由系统时钟二分频后作为VGASig模块的时钟输入信号;VGASig 模块的hsyncb信号和vsyncb信号形成顶层模块的hsyncb(行同步)和vsyncb(场同步)信号;VGASig模块的hcnt和vcnt信号作为ColorMap模块的地址控制输入,ColorMap模块根据该信号的值输出相应的RGB颜色信息rgbx,rgby,rgbz和rgbw。

5.3VGA显示实践

第五章FPGA基本实践5.1流水灯实践流水灯的关键设计流水灯工程的vivado 实现5.2数码管动态显示实践数码管动态显示原理分析数码管动态显示设计数码管动态显示工程的vivado 实现数码管动态显示IP 核设计与实现调用IP 核实现动态显示5.3 VGA 显示的实现VGA 显示基本原理VGA 显示设计与实现补充按键行列按键原理行列按键实践⏹驱动普通的液晶显示器显示图形,就可以实现诸如监控系统、示波器视频显示。

本节将构建VIVADO 工程实现基本的VGA 显示。

⏹5.3.1 VGA显示基本原理⏹图中所示,使用到了VGA接口除地之外,包括1脚红色,2脚绿色,3脚蓝色。

以及13脚的水平同步(扫描)Hsync和14脚的垂直同步(扫描)Vsync。

⏹进一步分析该图,红色信号使用了VGA R0通过4K 电阻、VGA R1通过2K电阻、VGA R2通过1K电阻、VGA R2通过510欧姆的电阻后,进行线或后加载。

出于实验的目的对颜色的精度要求不高,电阻的取值510欧姆近似于500欧姆。

那么这种设计R3R2R1R0的权重分别为8421,因此符合二进制数值设计。

当R3R2R1R0为1111是红色最强。

红色的数字范围为0000-1111。

同理,绿色和蓝色也是四位颜色。

因此是12位色(4096色)。

⏹基于欧姆定律进行计算⏹液晶显示驱动电路管脚分配⏹VGA的扫描过程⏹要显示整个图像,一行扫描完成后要进行回扫,然后开始下一行的扫描。

所有行扫描完成后,需要进行垂直回扫完成扫描过程。

垂直扫描的周期长,完成整个屏幕的显示,也称为场或帧。

回扫过程需要消隐。

⏹VGA 的时序主要分为行和场两种数据时序⏹VGA显示器是由一个一个的像素点组成的,如果有x行y列,就有x*y个像素点。

按照规则,要一行一行地显示直到所有行显示完。

这种方式也称为扫描。

行数据时序就是一行数据的显示时序。

由VGA 行数据时序图可以看出,显示一行数据需要做好两件事情。

VGA显示原理与控制资料讲解

图6 VGA接口定义图

Planning and task

Establish a powerPC405 system with EDK Write a boot loader program

Write a VGA driver and control program

VGA display success

图2 通用VGA显示卡控制电路

Timing analysis

Vsync : 场同步信号 tWV : 场同步脉冲(宽度为2行) tHV : 场消隐前沿(13行) tVH :场消隐后沿(30行) Hsync : 行同步信号 tWH : 行同步脉冲(96个DCLK) tHC : 行消隐前沿(19个DCLK) tCH : 行消隐后沿(45个DCLK) BLANK : 复合消隐信号(行消隐信号和场消隐信号的逻辑 与,有效显示区域为高电平,无效显示区域为低电平)

此课件下载可自行编辑修改,仅供参考! 感谢您的支持,我们努力做得更好!谢谢

754

658

图4 行同步状态机状态转移图

Timing implementation

场同步状态机有v_video,v_front,v_sync, v_back四 种状态,它根据场行数计数器的计数值来进行 场同步状态机状态转移图

Interface definition

1红基色 red 2 绿基色 green 3 蓝基色 blue 4 地址码 ID Bit 5 自测试 (各家定义不同 ) 6 红地 7 绿地 8 蓝地 9 保留 (各家定义不同 ) 10 数字地 11 地址码 12 地址码 13 行同步 14 场同步 15 地址码 (各家定义不同 )

图3 VGA(640X480,60Hz)图像格式信号时序图

尝试五vga图象显示控制

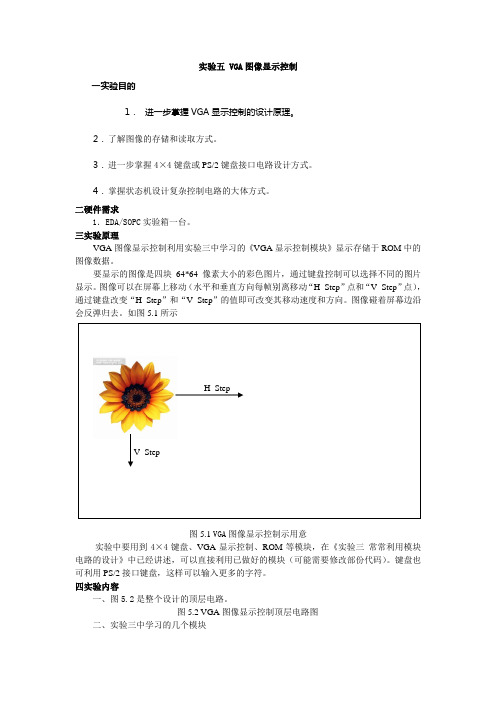

实验五 VGA图像显示控制一实验目的1.进一步掌握VGA显示控制的设计原理。

2.了解图像的存储和读取方式。

3.进一步掌握4×4键盘或PS/2键盘接口电路设计方式。

4.掌握状态机设计复杂控制电路的大体方式。

二硬件需求1.EDA/SOPC实验箱一台。

三实验原理VGA图像显示控制利用实验三中学习的《VGA显示控制模块》显示存储于ROM中的图像数据。

要显示的图像是四块64*64像素大小的彩色图片,通过键盘控制可以选择不同的图片显示。

图像可以在屏幕上移动(水平和垂直方向每帧别离移动“H_Step”点和“V_Step”点),通过键盘改变“H_Step”和“V_Step”的值即可改变其移动速度和方向。

图像碰着屏幕边沿会反弹归去。

如图5.1所示H_StepV_Step图5.1 VGA图像显示控制示用意实验中要用到4×4键盘、VGA显示控制、ROM等模块,在《实验三常常利用模块电路的设计》中已经讲述,可以直接利用已做好的模块(可能需要修改部份代码)。

键盘也可利用PS/2接口键盘,这样可以输入更多的字符。

四实验内容一、图5.2是整个设计的顶层电路。

图5.2 VGA图像显示控制顶层电路图二、实验三中学习的几个模块①“Read_Keyboard”模块与实验三中的4×4键盘模块一致;②四个ROM模块利用宏功能模块实现,并设置其内存初始化文件别离为“FBB.mif”、“dog.mif”、“cat.mif”、“flower.mif”,如图5.3所示。

固然也可以用其他图片(大小为64*64)利用“BmpToMif”软件生成对应的“mif”文件,如图5.4所示。

图5.3 内存初始化文件设置图5.4 获取内存初始化文件(mif文件)③“VGA”模块与实验三中大体一致,只需要在端口中屏蔽“key”端口,并加入“imag_rgb: in std_logic_vector(2 downto 0);”用于从外部输入图像数据。

VHDL语言VGA显示控制

EDA大作业实验报告基于VHDL语言的VGA显示与控制1111000079 田宇1111000081 王坤目录1.VGA显示原理 (3)1. 1 VGA逐行扫描显示 (3)1. 2 VGA时序分析 (3)2.时序部分的代码实现 (3)2.1时序部分主要代码 (3)2.2时序部分的实现 (4)2.2. 1 行时序 (4)2.2.2场时序 (5)3.控制部分的代码实现 (5)3.1控制部分主要代码 (5)3.2控制部分的实现 (12)3.2.1彩条与彩格 (12)3.2.2字体显示 (12)4.硬件平台实验 (12)1- VGA显示原理1.1 VGA逐行扫描显示逐行扫描是扫描从屏幕左上角一点开始,从左像右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信号进行同步:当扫描完所有的行,形成一帧,用场同步信号进行场同步,并使扫描回到屏幕左上方,同时进行场消隐,开始下一帧。

1.2 VGA时序分析9.水-麻------------ f荷同步r_ IVGA的行时序\同歩1同步~1牀冲8睐冲.| ------场消(ft何隔VGA的场时序0-1)2.时序部分的代码实现2.1时序部分主要代码if eve nt and ck=,T then H<=H+1 oif H>15 and H<110 then Hs<=> T。

elsif H>=110 then Hs<= 0J。

if H>=160 and H<800 then Hen<=, T。

elsif H=800 then Hen<=,O'。

H<=Ooend ifoend ifoend ifoif Hs' event and Hs=,T then V<=V+1oif V>11 and V<14 then Vs<=, 1'。

VGA显示驱动原理及其实现

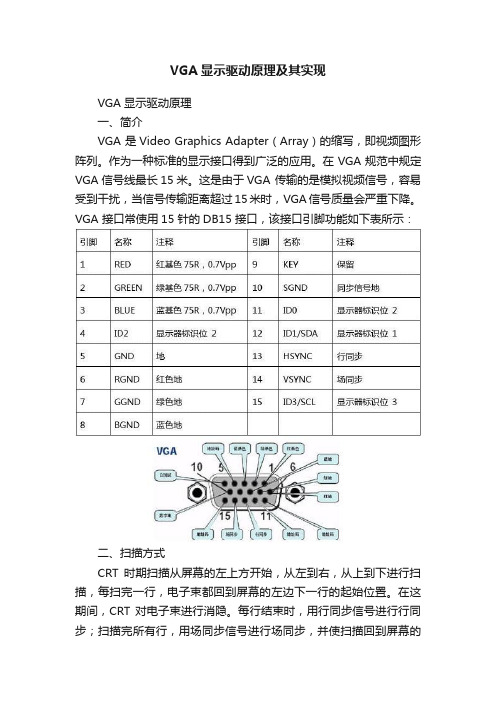

VGA显示驱动原理及其实现VGA显示驱动原理一、简介VGA 是Video Graphics Adapter(Array)的缩写,即视频图形阵列。

作为一种标准的显示接口得到广泛的应用。

在VGA规范中规定VGA信号线最长15米。

这是由于VGA 传输的是模拟视频信号,容易受到干扰,当信号传输距离超过15米时,VGA信号质量会严重下降。

VGA 接口常使用15 针的DB15 接口,该接口引脚功能如下表所示:二、扫描方式CRT时期扫描从屏幕的左上方开始,从左到右,从上到下进行扫描,每扫完一行,电子束都回到屏幕的左边下一行的起始位置。

在这期间,CRT 对电子束进行消隐。

每行结束时,用行同步信号进行行同步;扫描完所有行,用场同步信号进行场同步,并使扫描回到屏幕的左上方。

同时进行场消隐,预备下一场的扫描。

随着显示器发展,液晶显示开始流行,虽然液晶与CRT成像模式不一样,但是同样支持兼容传统接口,因此,我们在使用显示器时,只要该显示器带有标准的VGA 接口,我们就不用去关系其成像原理,直接使用标准的VGA 时序即可驱动。

对于普通的显示器(无论是液晶还是CRT),共有5 个信号:R、G、B 三基色信号,行同步信号HS,场同步信号VS。

对于时序驱动,VGA 显示器要严格遵循“VGA 工业标准”,即640*480*60Hz 模式四、标准时序具体时序可查看VESA_Monitor_Timing_Standard-Version,本文以640*480*60HZ 时序为例将以上图实例化640*480*60HZ消隐区内需送出黑场信号。

像素时钟=Htotal * Vtotal * rame =800*525*59.94=25.175MHz五、接口电路芯片能接收、发送均为数字信号,但VGA传输为模拟信号,故在传输,发送时候需要进行数模转换。

VGA发送原理图:VGA接收原理图本篇幅主要涉及VGA信号发送部分,该VGA接口三基色信号R、G、B共专用8位(分别是R 3位、G 3位、B 2位)。

VGA显示的控制器

VGA显示的控制器1 VGA显示接口原理计算机显示器的显示有许多接口标准,常见的有 VGA、SVGA等。

VGA接口,也叫D-Sub接口,是15针的梯形插头,分成 3排,每排 5个,传输模拟信号。

VGA接口采用非对称分布的 15针连接方式,其工作原理是:将显存内以数字格式存储的图像(帧)信号在RAMDAC 里经过模拟调制成模拟高频信号,然后再输出到显示设备成像。

VGA 支持在640×480的较高分辨率下同时显示16种色彩或256种灰度,同时在 320 × 240 分辨率下可以同时显示 256种颜色。

VGA显示器的显示是采用逐行扫描的方式解决。

扫描从屏幕的左上方开始,从左到右, 从上到下,逐行扫描,每扫完一行,电子束回到屏幕的左边下一行的起始位置,在这期间对电子束进行行消隐,每行结束时,用行同步信号进行行同步,扫描完所有行,用场同步信号进行场同步,并使扫描回到屏幕的左上方,同时进行场消隐,并预备进行下一次的扫描。

2 VGA显示控制器的设计实现系统硬件框图如图所示通常VGA显示器显示的图像数据量较大,而 FPGA 内置 ROM 很难满足这么大的存储量,FPGA需要外接SDRAM来存储这些数据。

VGA显示器的输入的是模拟信号,所以由 VGA显示控制器产生的 RGB信号在进入VGA 接口之前要经过一个 D/A 转换器。

2.VGA时序控制信号VGA显示器的时序控制要严格遵循“VGA工业标准”,即640×480×60Hz模式,否则会导致VGA显示器无法正常工作。

图2-1所示为行扫描时序,图2-2所示为场扫描时序。

(1)行扫描信号时序:图2-1给出了行视频时序示意图。

在行扫描时序中,包括以下几个时序参数:HSYNC Signal是用来控制“列填充”,而一个HSYNC Signal可以分为4个段,也就是a(同步段),b(后沿段),c(激活段),d(前沿段)。

HSYNC Signal的a是拉低的128个列像素,b是拉高的61个列像素,c是拉高的806个列像素,最后的d是拉高的53个列像素。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

作业:

利用9 利用9条控制线输出多种颜色

Lines 480 10 2 33 525

Time [ms] 15.253227408143 0.31777557100298 0.06355511420059 6 1.0486593843098 16.683217477656

Vertical timing (frame)

Polarity of vertical sync pulse is negative.

实验原理:

3.VGA信号的时序关系 3.VGA信号的时序关系 显示器要正常工作就要求有VGA端口输出的控制信号满足一定的时序关系。时 显示器要正常工作就要求有VGA端口输出的控制信号满足一定的时序关系。时 序如下:

不同分辨率对应的像素及行分布:

实验原理:

4. VGA驱动程序的FPGA实现: 驱动程序主要完成以下任务:按照VGA时序要求产生行/列同步信号,并且在指 定的时间(有效像素期间)将要显示的颜色数据输出到RGB。 不同的显示模式和刷新频率下,具体同步信号前、后、同步信号、有效像素数 是不同的,要根据像素时钟频率来设置。如上表:以800*600,60Hz为例 ,像素时钟为40M,像素时钟=(800+40+128+88)*(600+1+4+23)*60= 1056 * 628*60=40MHz,设计中可根据系统时钟频率来选择合适的显示模 式

General timing Screen refresh rate Vertical refresh Pixel freq. 60 Hz 31.46875 kHz 25.175 MHz

Sync pulse Back porch Whole line

Frame part Visible area Front porch Sync pulse

实验原理:

在通常使用的连接方法里面,15个管脚里面的5个是最重要的,他们 包括3个基本红,绿,蓝三条基本色彩线和水平与垂直两条控制线。由这5 条控制线,我们一共可以在屏幕内显示8种不同的色彩(8种组合)。在开 发板上,红、绿、蓝三条基本色彩线每条都由三条输入线控制,这三条控制 线分别串有不同的电阻,在这样三条输入线的控制下,红、绿、蓝三基色也 都各自被细化为八个等级。理论上开发板的VGA接口一共有9条颜色控制线 ,一共可以显示512种不同的颜色。

Video Monitor

实验原理:

2. CRT显示器的工作原理: 在显示器内部,电流流过线圈产生磁场,控制电子束流过显示器表面,水平是 从左向右流,垂直方向是从上向下流。只有当电子沿正方向流的时候(即从 左向右,从上到下)显示器工作,而当电子返回显示器的左面或上面的时候 显示器不工作。 VGA接口标准 VGA工业标准所要求的频率: • 时钟频率: 25.175MHz(像素输出的频率); • 行频: 31469Hz; • 场频: 59.94Hz。 显示器技术规格提供的行频一般在30kHz~45kHz(保守数据),场频一般在 50Hz~75Hz(保守数据),针对以上保守数据,以30kHz的行频进行扫描时 所需时钟频率为:30kHz×800(行周期)=24MHz,则场频为:30kHz÷525( 场周期)=57.14Hz

Video timing generation

• •

上图中,有四个与垂直场相关的关键时间,分别是: Tvsync:Vertical Synchronization Time,场同步脉冲 时间; • Tvgdel:Vertical Gate Delay Time,场后肩时间; • Tvgate:Vertical Gate Time,场有效时间; • Tvlen:Vertical Length Time,整zonal timing information: Mode name Pixel sync back active front whole line clock pulse porch time porch period (MHz) (us) (pix) (pix) (pix) (pix) (pix) 3.2 128 85 806 37 1056

实验内容:

在VGA的显示器上面按照实验需要显示实验要求的色彩条,通过SW3 VGA的显示器上面按照实验需要显示实验要求的色彩条,通过SW3 来切换水平还是垂直显示

实验结果:

看到VGA的显示器上的彩条显示

实验步骤:

1.新建一个工程 1.新建一个工程 2.在工程目录下创建并输入源程序 2.在工程目录下创建并输入源程序 3.综合,布局布线 3.综合,布局布线 4.下载调试 4.下载调试

Horizontal timing (line)

Polarity of horizontal sync pulse is negative.

Scanline part Visible area Front porch

Pixels 640 16 96 48 800

Time [µs] 25.422045680238 0.63555114200596 3.8133068520357 1.9066534260179 31.777557100298

Interlaced Video

CRT face

1/60 second 262 = 1 field lines

1/30 second 525 lines = 1 frame (525i)

Progressive Video

525p = 1 frame

为了帮助保护您的隐私,PowerPoint 禁止自动下载此外部图片。若要下载并显示此图片,请单击消息栏中的 “选项”,然后单击 “启用外部内容 ”。

VGA 800x600 60Hz 40

Vertical timing information: Mode name Lines line sync back active front whole frame Total width pulse porch time porch period (us) (us)(lin) (us)(lin) (us) (lin) (us)(lin) (us) (lin) VGA 800x600 60Hz 16579 628 628 26.40 106 4 554 21 15945 604 -1*

Back porch Whole frame

Video timing generation

• 根据各显示模块的关键参数产生出对应的输出显示信号,显示 器上的VGA接口就是根据该模块产生的输出显示信号同步输出 的。 • 以下列出与timing产生的关键参数。 • 上图中,有四个与水平行相关的关键时间,分别是: • Thsync:Horizontal Synchronization Time,行同步脉冲时 间; • Thgdel:Horizontal Gate Delay Time,行后肩时间; • Thgate:Horizontal Gate Time,行有效时间; • Thlen:Horizontal Length Time,整行时间;

实验三 VGA显示控制实验 显示控制实验

实验原理:

本次实验要求用VerilogHDL编写一个可以控制实验版上面的VGA端口输出 的程序,并通过实验板控制显示器来显示已经编写好的程序里面的颜色。若 要显示器正常工作,首先要了解VGA端口的结构,其次要知道CRT显示器 的工作原理,另外还要掌握VGA端口输出信号的时序关系。 1.VGA端口的结构: VGA端口是视频输出端口,端口一共包含15个管脚,如下图: