静电放电损伤自修复数字电路模型

【国家自然科学基金】_自修复控制_基金支持热词逐年推荐_【万方软件创新助手】_20140802

2009年 序号 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19

科研热词 醋酸 配置控制 航空航天器 腐蚀 胚胎电子系统 灾害扩散 模型 无标度网络 容错 可调指数 半导体 动态重构 动力学行为 内建自诊断 内建自测试 内建自修复 内建冗余分析 内容可寻址存储器 不锈钢

2011年 序号 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23

2011年 科研热词 自修复 量子控制 自组织 自修复控制 自修复性能 羟基硅酸盐 直升机 激素 润滑油添加剂 模型参考自适应控制 材料物理与化学 故障容错 摩擦学性能 搜索和捕获 扫描电镜 微裂纹 微胶囊 多机器人系统 多智能体系统 多故障 内分泌细胞 任务复制 人工内分泌系统 推荐指数 3 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

推荐指数 2 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

2013年 序号 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29

科研热词 自修复 重布线 遗传算法 超强韧性 自诊断 自组织网(son) 自主容错 级配 生长自组织神经网络 液化 智能交通 故障定位 工作度 容错可重构阵列 容错 在线分布式控制 图论 可靠性 可重构阵列 功率控制 光纤自诊断网络 光纤应变花 人工神经网络 交通流预测 交通信息工程及控制 互连资源 三维集成电路 三维容错路由算法 三维

推荐指数 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

静电放电esd)最常用的三种模型及其防护设计

静电放电(ESD)最常用的三种模型及其防护设计ESD:Electrostatic Discharge,即是静电放电,每个从事硬件设计和生产的工程师都必须掌握?ESD?的相关知识。

为了定量表征 ESD 特性,一般将 ESD 转化成模型表达方式,ESD 的模型有很多种,下面介绍最常用的三种。

1.HBM:Human Body?Model,人体模型:该模型表征人体带电接触器件放电,Rb 为等效人体电阻,Cb 为等效人体电容。

等效电路如下图。

图中同时给出了器件 HBM 模型的 ESD 等级。

ESD人体模型等效电路图及其ESD等级2.MM:Machine Model,机器模型:机器模型的等效电路与人体模型相似,但等效电容(Cb)是?200pF,等效电阻为 0,机器模型与人体模型的差异较大,实际上机器的储电电容变化较大,但为了描述的统一,取 200pF。

由于机器模型放电时没有电阻,且储电电容大于人体模式,同等电压对器件的损害,机器模式远大于人体模型。

ESD机器模型等效电路图及其ESD等级3.CDM:Charged?Device?Model,充电器件模型:半导体器件主要采用三种封装型式(金属、陶瓷、塑料)。

它们在装配、传递、试验、测试、运输及存贮过程中,由于管壳与其它绝缘材料(如包装用的塑料袋、传递用的塑料容器等)相互磨擦,就会使管壳带电。

器件本身作为电容器的一个极板而存贮电荷。

CDM 模型就是基于已带电的器件通过管脚与地接触时,发生对地放电引起器件失效而建立的,器件带电模型如下:ESD充电器件模型等效电路图及其ESD等级器件的 ESD 等级一般按以上三种模型测试,大部分 ESD 敏感器件手册上都有器件的 ESD数据,一般给出的是 HBM 和 MM。

通过器件的 ESD 数据可以了解器件的 ESD 特性,但要注意,器件的每个管脚的 ESD 特性差异较大,某些管脚的 ESD 电压会特别低,一般来说,高速端口,高阻输入端口,模拟端口 ESD电压会比较低。

ESD放电模型

♦

--

♦

♦

♦

♦

--

BMM)

“

”

ESD

, --

IEC801-2(1984) IEC801-2(1991)

IEC1000-4-2 1995

GB17626.2 EN61000-2-4 ECMA

ISO10605E ISO10605E IEC61000-4-2 2001

/pF / Ω

/ns

150 150 5ns±30

r

铺

CB=Cs+Cg=253pF

♦ 1962 22

398pF

100 4000Ω

520 90

♦ 1976 Kirk V

C=270pF

10MΩ 1kΩ

RB

=

1000(I0 IP

−

Ip)

RB=87~190Ω

CB

=

RB

τ

+ 1000

CB=132~190pF

♦ Enoch-Shaw

♦

200V; 5 500pF 1

IC DUT

CDM ESDS

C1 C2 C3 C4 C5 C6 C7

(V) <125 125~< 250 250<=500 500~<=1000 1000~<=1500 1500~<=2000 =>2000

“

”

环脱状

静电放电模拟器

环脱状 环脱状 环脱状

必电的z

静电放电模拟器

环脱状 环脱状

IEC61340-3-1

HBM ESDS

0 1A 1B 1C 2 3A 3B

(V) <250 250~<500 500~<1000 1000~<2000 2000~<4000 4000~<8000 ≥8000

ESD引起集成电路损坏原理模式及实例

ESD引起集成电路损坏原理模式及实例一.ESD引起集成电路损伤的三种途径(1)人体活动引起的摩擦起电是重要的静电来源,带静电的操作者与器件接触并通过器件放电。

(2)器件与用绝缘材料制作的包装袋、传递盒和传送带等摩擦,使器件本身带静电,它与人体或地接触时发生的静电放电。

(3)当器件处在很强的静电场中时,因静电感应在器件内部的芯片上将感应出很高的电位差,从而引起芯片内部薄氧化层的击穿。

或者某一管脚与地相碰也会发生静电放电。

根据上述三种ESD的损伤途径,建立了三种ESD损伤模型:人体带电模型、器件带电模型和场感应模型。

其中人体模型是主要的。

二.ESD损伤的失效模式(1)双极型数字电路a.输入端漏电流增加b.参数退化c.失去功能,其中对带有肖特基管的STTL和LSTTL电路更为敏感。

(2)双极型线性电路a.输入失调电压增大b.输入失调电流增大c.MOS电容(补偿电容)漏电或短路d.失去功能(3)MOS集成电路a.输入端漏电流增大b.输出端漏电流增大c.静态功耗电流增大d.失去功能(4)双极型单稳电路和振荡器电路a.单稳电路的单稳时间发生变化b.振荡器的振荡频率发生变化c.R.C连接端对地出现反向漏电。

三.ESD对集成电路的损坏形式a.MOS电路输入端保护电路的二极管出现反向漏电流增大b.输入端MOS管发生栅穿c.MOS电路输入保护电路中的保护电阻或接触孔发生烧毁d.引起ROM电路或PAL电路中的熔断丝熔断e.集成电路内部的MOS电容器发生栅穿f.运算放大器输入端(对管)小电流放大系数减小g.集成电路内部的精密电阻的阻值发生漂移h.与外接端子相连的铝条被熔断i.引起多层布线间的介质击穿(例如:输入端铝条与n+、间的介质击穿)四.ESD损伤机理(1)电压型损伤a.栅氧化层击穿(MOS电路输入端、MOS电容)b.气体电弧放电引起的损坏(芯片上键合根部、金属化条的最窄间距处、声表面波器件的梳状电极条间)c.输入端多晶硅电阻与铝金属化条间的介质击穿d.输入/输出端n+扩区与铝金属化条间的介质击穿。

ESD(静电放电)原理、模型及防护

料、防静电涂料等,以降低设备表面静电电荷的积累。

设备接地

Байду номын сангаас

02

将设备与大地连接,使设备上积累的静电电荷能够迅速泄放到

大地,避免静电放电对设备造成损害。

静电消除器

03

在关键部位安装静电消除器,通过产生相反电荷来中和设备表

面的静电电荷,达到消除静电的目的。

系统级防护策略

系统接地

将整个系统与大地连接,确保系统内各部分电位一致,减少静电放 电的可能性。

ESD(静电放电)原理、模型及防护

目录

• 静电放电(ESD)基本概念与原理 • ESD模型与特性分析 • ESD防护措施与方法 • ESD测试与评估方法 • ESD在工业生产中应用案例分享 • 总结与展望

01

静电放电(ESD)基本概念与原 理

静电产生及危害

静电产生原因

物质接触、摩擦、分离等过程导 致电荷不平衡,形成静电。

规范操作培训

制定详细的设备操作规范,对操作人员进行培训,确保其在操作 过程中能够遵循规范,减少静电放电的风险。

静电防护装备使用

要求操作人员佩戴防静电手环、防静电鞋等静电防护装备,降低 人体静电对设备的影响。

04

ESD测试与评估方法

测试标准介绍

这是国际电工委员会制定的静电放电抗扰度测试标准,它规定了 测试等级、测试方法、测试环境和设备要求等。

特性

HBM放电电流具有较快的上升时间和较短的持 续时间,通常持续几百纳秒。放电能量较低,但 足以对敏感器件造成损坏。

应用场景

HBM模型常用于评估手持设备、可穿戴设备等 便携式电子产品的ESD防护能力。

机器模型(MM)

描述

应用场景

静电放电电路 -回复

静电放电电路-回复静电放电电路是一种常见的电路设计,用于控制和释放静电能量,以防止设备或者电子元件受到静电损害。

在本文中,我们将一步一步地介绍静电放电电路的原理、组成部分、工作原理以及实际应用。

一、静电放电电路的原理静电放电电路的原理是基于静电的产生和释放。

静电是指电荷在物体表面积聚而产生的一种现象。

当物体表面电荷积聚到一定程度时,静电就会产生,当电荷得不到及时释放,则会造成静电放电。

静电放电可以引发火花、电击以及设备损坏等危险,因此需要通过静电放电电路来控制和释放静电能量,以保护设备和人员的安全。

二、静电放电电路的组成部分静电放电电路通常由以下几个主要组成部分组成:1. 静电感应电极:用于感应和收集周围的静电能量,并将其导入电路中。

静电感应电极通常由导电材料制成,如金属或者导电塑料。

2. 静电电容器:用于储存和释放静电能量。

静电电容器的选择取决于电路的需要,通常以电容量和额定电压为基准。

3. 静电放电电阻:用于限制静电能量的释放速度,避免过大的放电电流对设备造成损坏。

静电放电电阻的阻值通常根据电路的需求和静电放电速度确定。

4. 静电放电开关:用于控制静电放电电路的开关状态。

静电放电开关通常是电子开关,能够快速响应并关闭电路,以防止静电释放。

三、静电放电电路的工作原理静电放电电路的工作原理可以简述如下:1. 当静电感应电极感应到周围的静电能量时,会产生电压和电荷。

2. 静电感应电极将感应到的静电能量导入静电电容器。

3. 当静电电容器电荷达到一定程度时,静电放电开关会检测到电容器的电荷状态。

4. 当静电放电开关检测到静电电容器电荷达到指定阈值时,开关会打开,启动静电放电电路。

5. 静电电容器通过静电放电电路释放静电能量,将其导入静电放电电阻。

6. 静电放电电阻限制静电能量的释放速度,防止过大的放电电流引发危险。

7. 静电放电电路工作完成后,静电放电开关会关闭,电路恢复到初始状态。

四、静电放电电路的实际应用静电放电电路在许多领域中有着广泛的应用,下面列举几个典型的应用场景:1. 电子设备保护:在电子设备制造和使用过程中,静电放电是一个常见的问题。

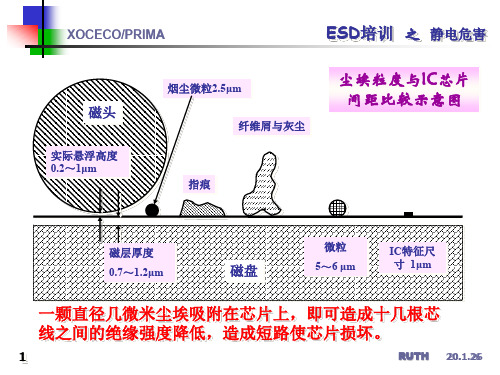

静电放电造成器件损伤

6

RUTH 2200.1.2266

XOCECO/PRIMA

ESD培训 之 静电危害

3.2 潜在性:有些电子器件受静电放电损伤后,仅表现出某 些性能参数的下降,但未达到安全失效程度,若没有进行全 面地检测往往无法发现。如有的IC在静电放电损伤后,仅表 现出输入电流增加,一般在功能检测时不会被发现,或者静 电放电使产品出现可自愈的击穿,或者其他非致命的损害。 但随工作时间延长,这种效应在累加继续使用下,最终发生 致命失效。

目前,半导体内有PN结,它的介电层 SiO2,膜厚度 0.007~0.15μm,再考虑工艺偏差,能承受的耐压值很低。

目前,半导体器件安全阀门限电压≤100V。

3

RUTH 2200.1.2266

XOCECO/PRIMA

ESD培训 之 静电危害

2. ESD造成电子元器件失效的主要机理

(1) 热二次击穿 (2) 金属镀层融熔

硬失效 10% 静电源(如人体或物体放电、静电场或静电高压尖峰放电) 放电,超过ESDS器件允许工作电压或电流值。造成击穿或烧 毁,使ESDS器件内部开路或短路产生完全失效。

9

RUTH 2200.1.2266

XOCECO/PRIMA

ESD培训 之 静电危害

电压击穿开始时往往先在 某一电压下在介质个别点 上出现所谓网点击穿,以 后只要在较低的电压下即 可出现大片区域的雪崩式 击穿,造成器件永久性损 毁。

5

RUTH 2200.1.2266

XOCECO/PRIMA

ESD培训 之 静电危害

人体带电和电击感应程度的关系

人体带电电位

1.0 (KV) 2.0 (KV) 2.5 (KV) 3.0 (KV) 4.0 (KV) 5.0 (KV) 6.0 (KV) 7.0 (KV) 8.0 (KV) 9.0 (KV) 10.0 (KV) 11.0 (KV) 12.0 (KV)

esd电路原理

esd电路原理

ESD电路原理是指防静电保护电路的设计和工作原理。

在电子设备中,静电放电(ESD)是一种常见的故障和损坏原因。

为了防止设备受到静电的损害,需要采用一些电路来保护电子设备。

ESD电路的原理涉及三个方面:静电感应、静电放电和保护措施。

首先是静电感应,当人体或其他物体带有静电时,周围的电子设备可能会受到感应而受到电磁干扰。

这种电磁干扰可能引起设备的故障或损坏。

因此,ESD电路需要具备感应静电的能力,以提前发现和处理这种干扰。

其次是静电放电,当带电物体接触到电子设备时,可能会发生静电放电。

静电放电会产生高压脉冲,可能对设备的敏感元器件造成破坏。

ESD电路需要具备快速响应的能力,能够在静电放电事件发生时迅速将电压限制到安全范围内。

最后是保护措施,ESD电路需要采用一系列的保护措施来保护电子设备。

常见的保护措施包括使用TVS二极管、MOV等元器件,这些元器件具备快速响应和较高的耐压能力,能够有效地吸收和限制静电放电的能量。

综上所述,ESD电路原理涉及静电感应、静电放电和保护措施三个方面。

通过合理设计和应用ESD电路,可以有效地保护电子设备免受静电损害。

静电放电最常用的三种放电模型是什么?

静电放电最常用的三种放电模型是什么?1、ESD简介ESD:ESD是当具有累积正负电荷的物体(电介质)接触或接近时发生的放电现象,通常为高达几KV的纳秒级短脉冲。

目前根据ESD 产生的原因及其对集成电路放电的方式不同,常见的ESD 被分类为下列三类(还有一些模式并不常用),分别是:人体放电模式(HBM, Human Body Model), 机器放电模式(MM, Machine Model)以及充电设备模式(CDM, Charge Device Model)。

1.1 HBM-人体模型HBM(Human Body Model),人体模型。

静电放电损害最常见的原因是,人体或带电材料将静电荷直接移转至静电放电敏感物体(ESDS)上。

在地板上行走时,身体便开始累积静电荷。

手指轻触(或靠近)ESDS 或组件的导电引线时,身体便会放电,且可能使器件受损。

这种放电模式称为「人体模型」(HBM)。

在各种ESD器件敏感度分级模型中,人体模型是最早也最普遍使用的。

HBM测试模型是指当个体站立时,其指尖的放电传递至器件上。

该模型通过一个开关组件,以电阻器(通常为兆欧级)将100pF电容器充电后,在待测器件和与之相串联的一个1500电阻器上放电,器件最后接地或到达低电位。

1.2 MM-机器模型MM(Machine Model),机器模型;是指带电的导电物体也会发生放电,如金属工具或自动化设备、夹具等。

「机器模型」最初是为了尝试建立HBM事件的最坏情况。

这个ESD模型是一个200 pF电容直接对组件放电,输出电路中没有直流串联电阻。

放电波形可以振荡,上升时间和脉冲宽度与HBM类似。

机器模型通常会有与人体模型同样的物理性故障模式,但在明显较低的水平。

MM主要模拟可能从带电机器(如制造系统)释放的静电。

esd保护电路原理

esd保护电路原理

ESD(静电放电)保护电路是一种用于保护电子设备免受外部静电放电损害的电路设计。

静电放电是指由于电荷的不平衡而产生的短暂的高电压放电现象,会对敏感的电子器件造成不可逆转的损坏。

ESD保护电路的设计目标是将外部静电放电的能量引导到安

全地方,避免其对电子设备造成伤害。

为了实现这一目标,ESD保护电路通常由以下几个关键部分组成:

1. 静电放电探测器:用于检测外部静电放电事件的发生。

一旦探测到静电放电,它会发送一个信号给保护电路。

2. 充电泵:用于将ESD保护电路与电源之间建立一个高电压差。

这个高电压差是为了将静电放电的能量引导到地。

3. 电压限制器:用于限制引导过来的静电放电能量的电压,并防止其超过设备耐受的最大电压。

4. 可重复使用的保护元件:用于吸收和分散静电放电的能量。

这些元件可以多次使用,因为它们在处理静电放电时可以自愈。

5. 地引线:用于将引导过来的静电放电能量导入地。

地是一个电势为零的点,可以安全地对外部静电放电进行耗散。

综上所述,ESD保护电路的原理是通过静电放电探测器检测

外部静电放电事件,然后利用充电泵建立高电压差将静电放电

能量引导到地引线,并通过电压限制器和可重复使用的保护元件保护电子设备免受损害。

复位电路esd防护设计

复位电路esd防护设计

复位电路是电子设备中非常重要的一部分,它用于在设备出现故障或异常情况时将设备恢复到正常工作状态。

ESD(静电放电)防护设计则是为了防止静电放电对电子设备造成损坏。

在设计复位电路的时候,需要考虑如何保护电路免受ESD的影响。

首先,针对ESD防护,可以采取以下措施:

1. 使用ESD保护器件,选择适当的ESD保护器件,如TVS二极管、ESD二极管等,来限制静电放电对电路的影响。

2. 地线设计,合理设计地线,确保设备的外壳和地线之间有良好的连接,以便将静电放电迅速引导至地。

对于复位电路的设计,建议考虑以下几点:

1. 稳定性,确保复位电路能够稳定可靠地工作,不会因为外界干扰或噪声而误触发。

2. 延迟,在设计复位电路时,需要考虑延迟的问题,确保在需

要复位时能够有足够的延迟时间来完成相应的操作,避免误操作或者频繁复位。

3. 电源管理,复位电路通常与电源管理相关,需要考虑电源的稳定性和可靠性,以确保复位电路能够正常工作。

在实际设计中,可以采用多种技术来实现ESD防护和复位电路设计,比如使用滤波器、保护二极管、电容器等 passives 元件,以及专门的复位集成电路(IC)来实现复位功能。

此外,还需要通过模拟和数字仿真来验证设计的可靠性和稳定性。

总之,复位电路的ESD防护设计需要综合考虑电路稳定性、延迟、电源管理等多个因素,以确保设备在面对静电放电时能够正常工作并且不受损坏。

ESD保护电路的模拟仿真

ESD保护电路的模拟仿真ESD(电静电放电)是现代集成电路领域面临的一个严重问题。

在电子设备使用过程中,由于静电的产生和积累,可能会导致电子器件受到损坏,甚至无法正常工作。

因此,为了保护集成电路免受ESD的影响,设计并模拟仿真ESD保护电路成为一项重要的工作。

一、ESD保护电路的功能与原理ESD保护电路主要功能是在ESD事件发生时,吸收静电放电的能量并将其传播到地线,维持被保护器件的工作电压稳定。

ESD保护电路主要由两个部分组成:ESD保护电路的前端和ESD保护电路的后端。

ESD保护电路的前端通常由一个或多个元件组成,如TVS二极管、Metal Oxide Varistor(MOV)、Spark Gap等。

这些元件主要用来吸收ESD产生的高能量放电,并将其传递到地线。

其中,TVS二极管是最常见的前端ESD保护元件,因其结构简单且响应速度快被广泛应用。

ESD保护电路的后端主要由驱动器、限流电阻等组成,用来控制ESD事件的过程,确保ESD电流在允许范围内。

限流电阻的作用是限制ESD电流的大小,避免对保护器件造成二次损害。

驱动器的作用是使保护电路能够快速响应ESD放电,并迅速传递ESD能量到地线。

二、ESD保护电路的模拟仿真方法在设计ESD保护电路之前,进行模拟仿真是非常必要的。

通过模拟仿真可以预测ESD保护电路的性能和响应,有助于优化保护电路的设计。

下面给出了ESD保护电路模拟仿真的几种常见方法。

1. SPICE仿真SPICE(Simulation Program with Integrated Circuit Emphasis)是一种常用的电路仿真工具,可以用于模拟和分析电路的性能。

在设计ESD保护电路时,可以使用SPICE软件进行电路结构和参数的仿真,以实现对保护电路的性能进行评估。

2. 有限元仿真有限元仿真是一种基于数值方法的电磁场仿真技术,可以用于分析电路中的电磁场分布和ESD放电的传播路径。

ESD静电放电分析整改方法

ESD应该是EMC中最常见也是遇到问题最多的测试项,许多硬件工程师遇到试验Fail 时,无从下手,今天就来谈谈ESD分析与整改的理论基础,不涉及实际案例应用。

█ESD干扰方式地弹根据静电放电电流波形可知,其电流具有较宽的频率范围。

如此高频率电流通过参考地平面时,理想情况下参考地平面阻抗处处相等,地电平抬升或者降落对系统信号以及电源无明显影响。

但是由于参考地电位受静电电流冲击产生的现象,即所谓的〝地弹〞现象。

容性耦合容性耦合是指电磁骚扰源通过电路或系统之间的电场并以耦合电容作用于敏感对象的电磁耦合方式。

静电放电产生容性耦合的机理是:静电电流流过阻抗变化的参考地平面时,会在参考地平面上产生变化电压。

平行于静电电流泄放路径参考地平面的导线,会因为容性耦合产生骚扰电压,当骚扰电压幅值超过芯片容错电压时则会引起芯片误动作,严重情况下会导致芯片内部半导体器件过压击穿而彻底损坏。

感性耦合感性耦合是指电磁骚扰源通过电路或系统之间的磁场并以耦合电感形式作用于敏感对象的电磁耦合方式。

静电放电产生感性耦合的机理是:静电放电变化电流流过参考地平面时,当遇到阻抗较低的信号布线(互感耦合到信号线上面,此时电压突变),会沿着阻抗较低的信号布线流进芯片,在芯片内部产生骚扰电压或者以电流形式冲击芯片,严重时会造成芯片内部半导体器件因过流烧毁。

辐射如上图所示,静电枪充电开关1接通时,充电电阻Rc与Cd电容构成充电回路,给电容充电;放电开关2接通时,Cd电容与Rd电阻构成放电回路。

当放电开关接通瞬间通过放电枪头对DUT放电,此时瞬间的高压脉冲流过放电电阻Rd产生变化的电流,变化的电流产生变化的磁场,从而形成丰富的电磁场干扰。

█ESD电流泄放路径静电电流会选择阻抗最低的路径返回到源端。

ESD整改简单来说就是找出静电电流泄放路径中的敏感信号,并对其进行ESD防护,提高其抗静电能力。

如果产品已经DV/PV,无法改变PCBA,则想办法设计一条阻抗最低路径,使电流返回源端。

5放电和静电放电模型

静电放电和静电放电模型♦静电放电的特点♦静电放电的类型♦静电放电模型♦静电放电模拟器♦静电放电产生的辐射场静电放电的特点♦静电放电(ESD)是指带电体周围的场强超过周围介质的绝缘击穿场强时,因介质电离而使带电体上的静电荷部分或全部消失的现象。

♦静电放电是高电位,强电场,瞬时大电流的过程。

♦静电放电会产生强烈的电磁辐射形成电磁脉冲(EMP)。

静电放电类型♦电晕放电♦火花放电♦刷形放电♦沿面放电静电放电的类型电晕放电(corona discharge)电晕放电以电晕为特点的一种放电,当某气体中的两个电极中有一个的形状导致其表面的电场明显大于两个电极之间电场的时候所发生放电现象。

电晕放电危害♦射频干扰飞机、航天器的通讯或导弹在飞行过程中,机壳或弹体上会因摩擦而产生静电,当静电电位足够高时可引发电晕放电,形成的电磁干扰会对飞机、航天器或导弹的制导系统产生干扰,造成通讯中断或制导失灵,引发事故。

♦浪费电能高压输电线上的电晕放电会造成电力浪费。

电晕放电的利用♦静电除尘♦脱硫脱硝♦静电喷涂静电火花放电(spark discharge )♦当静电电位比较高的带电导体或人体靠近其它导体、人体或接地导体时,便会引发静电火花放电。

♦静电火花放电是一个瞬变的过程,放电时两放电体之间的空气被击穿,形成“快如闪电”的火花通道,与此同时还伴随着噼啪的爆裂声,爆裂声是由火花通道内空气温度的急骤上升形成的气压冲击波造成的。

♦在发生静电火花放电时,静电能量瞬时集中释放,其引燃、引爆能力较强。

另外静电火花放电产生的放电电流及电磁脉冲具有较大的破坏力,它可对一些敏感的电子器件和设备造成危害。

刷形放电(brush discharge)♦刷形放电电往往发生在导体与带电绝缘体之间,带电绝缘体可以是固体、气体或低电导率的液体。

♦产生刷形放电时形成的放电通道在导体一端集中在某一点上,而在绝缘体一端有较多分叉,分布在一定空间范围内。

根据其放电通道的形状,这种放电被称为刷形放电。

电容esd简化等效模型

电容esd简化等效模型电容ESD简化等效模型ESD(静电放电)是指在不同电势下,由于静电累积所导致的突然放电现象。

在电子设备中,ESD问题是非常重要且需要重视的,因为ESD放电可能对电子元件及系统造成永久性损坏或暂时性故障。

为了更好地理解ESD现象以及其对电容的影响,我们可以使用简化的等效模型来研究。

首先,让我们了解一下电容的基本概念。

电容是一种存储电荷的器件,由两个导体之间的电介质(如空气、塑料等)隔开。

当在电容的两个端口之间施加电压时,正电荷会聚集在一个电极上,而负电荷会聚集在另一个电极上,形成电场。

这个电场储存了电能,当电容器断开电源时,这些电荷会被释放。

在ESD现象中,根据电容的特性,我们可以使用一个简化的等效模型来模拟电容对ESD放电的响应。

这个简化的等效模型主要由电容和电阻组成,它们分别代表电容器本身的电荷储存能力和电导率。

首先,我们可以将电容器视为一个等效的理想电容,其电容值可以通过电容器的尺寸、电介质材料等参数来确定。

然后,我们将一个电阻连接在电容器的两个端口上,这个电阻模拟了电介质的电导率,它与电容器的材料有关。

当一个ESD放电事件发生时,静电能量会通过电容器的电场引导到地面。

在这个过程中,电阻会限制电流的流动,并消散能量。

因此,电阻的值就成为了影响ESD放电过程的关键因素之一。

电阻的大小取决于电介质材料的导电性能以及电容器的尺寸。

较大的电阻值可以减小ESD放电时的电流峰值,从而保护电容器和其他电子元件。

同时,电阻和电容之间的相对值也会影响ESD放电过程的时间特性。

较小的电阻值和较大的电容值会导致较长的ESD放电时间,从而降低放电过程中的瞬态行为。

这对于某些敏感的电子元件来说是非常重要的,因为它可以减小ESD放电对电子元件的损害。

除了电阻和电容的等效模型之外,还有一些其他的因素可能会影响ESD放电过程,如ESD放电路径的几何结构、设备的接地和屏蔽等等。

这些因素一般也需要考虑在内,在进行ESD设计和测试时进行综合分析。

2.静电放电类型和静电放电模型

二、静电放电的特点

高电位,强电场,瞬时大电流的过程。

过去,人们认为静电是一种高电位、强电 场、小电流的过程,其实这种看法并不完全 正确。的确有些静电放电过程产生的放电电 流比较小,如电晕放电,但是在大多数情况 下静电放电过程往往会产生瞬时脉冲大电流, 尤其是带电导体或手持小金属物体(如钥匙 或螺丝刀等)的带电人体对接地导体产生火 花放电时,产生的瞬时脉冲电流的强度可达 到几十安培甚至上百安培。

三、静电放电的类型

电晕放电的特点

电晕放电是一种高电位、小电流、空气被 局部电离的放电过程。在放电中,它产生的电 流很小,约在1A到几百个之间,因此一般不具 备引燃、引爆能力。

电晕放电的形成

对于两极间的静电放电,只有当某一电极或两个 电极本身的尺寸比起极间距离小的多时才会出现电晕 放电。例如,在空气中两平行细线间的静电放电,当 细线的半径r与两线间距d之比d/r>5.85时,才有可能 产生电晕放电。否则,随着极间电压的升高,两极间 直接产生火花放电而不会产生电晕放电;除两平行细 线电极结构之外,其它能产生电晕放电的典型的电极 结构还有圆柱筒与其轴线上的细导线构成的电极,细 线或尖端与平板构成的电极。另外,处在空气中的带 电体当其电位足够高时也会产生电晕放电。

二、静电放电的特点

会产生强烈的电磁辐射形成电磁脉冲

过去人们在研究静电放电的危害时,主要 关心的是静电放电产生的注入电流对电火工 品、电子器件、电子设备及其它一些静电敏 感系统的危害和静电放电的火花对易燃易爆 气体、粉尘等的引燃 、引爆问题,忽视了静 电放电的电磁脉冲效应。

二、静电放电的特点

会产生强烈的电磁辐射形成电磁脉冲

电晕放电机制

当两极间的电压小于某 一 特 定 值 Vc 时 , 极 间 任 何 部分的场强均未超过空气的 击穿场强,两极间任何地方 都不会产生显著的空气电离 现象。但是两极间却有一定 的电流流过,这一电流随外 加电压的升高而增加,最终 达到一饱和值,饱和电流的 量级为10-14A。这一电流是 由宇宙射线和自然界中其它 放射性射线在空气中产生的 电子、离子对形成的。

手机ESD静电放电模型和分析

首先说结论:

1.之所以我们在设计手机电路的时候,总是尽量利用参考地来作为静电释放的通路,根本原 因是参考地与外界的“放电阻抗”很小,最容易与外界发生电荷转移(因为参考地平面很 大,覆盖很广,尖端多,和外界的等效接触很多,对比电路中的其他通路和许多元器件,在 无强带电体靠近时容易对外界释放电荷,而有强带电体靠近时则容易吸附电荷) (这里的 外界定义为电中性,即不带电的所有物体的总和,一般可直接等效为大地)。

放电路径 3:即信号线与参考地之间的通路,假设是由电路之间的各种电子元件、部分 PCB 构成的。所以如果大量的电荷通过这条路径的话,会对电路造成不可预计的干扰,使我们设 计时需要规避的。

按目前的设计规范,手机中的 3 条放电路径,放电路径 1 的放电阻抗远远大于放电路径 2 的放电阻抗(因为信号面的“折合等效”面积远远小于地平面),放电路径 3 的放电阻抗数 量级不好说,我想一般会远小于放电路径 2,所以: 放电阻抗: 放电路径 1 >>> 放电路径 2 > 放电路径 3

图2

综上所述:

1.电子设备中防 ESD 的本质就是:防止积聚的静电电荷在有电子元器件的路径中通过导致打 坏器件,以及防止静电电荷通过路径时导致的系统误操作(瞬间大电流会造成电位变化和磁 场干扰)。 一般,可用 TVS 管钳住高位,防止电压过高,打坏器件。但是对于防止电位的变化,没有太 可靠的办法,只能加电容来缓解。这也是为什么许多 reset 信号常常要保持低电平几 ms 才 开始操作的原因,因为这个时间越长,抗 ESD 导致的电位误操作的能力就越强。

耦合板其实就是为电荷的“扩散”提供一个良好的通路,估计搞 ESD 的人都知道,将手机孤立 在空气中打静电,手机时不容易出问题的,因为电荷没有“扩散”的通路,大部分电荷只是积 聚在手机上,并没有移动。

电路容错与自修复技术

电路容错与自修复技术在现代的信息时代中,电路在各行各业都起着重要的作用。

然而,由于种种原因,如功耗、电压噪声、温度变化和物理损坏等因素的存在,电路往往会出现各种故障。

为了确保电路工作的可靠性和稳定性,电路容错与自修复技术应运而生。

一、电路容错技术电路容错技术旨在提高电路在面对故障时的容错能力,以保持电路的正常运行。

主要的电路容错技术包括:1. 容错编码技术:通过加入冗余信息来检测和纠正数据传输过程中的错误。

常见的容错编码技术包括海明码、卷积码等。

2. 双模容错设计:通过在电路中加入备选模块,当主模块故障时,备选模块会自动接替其工作,保证电路的连续性和可用性。

3. 重配置技术:通过动态重配置电路资源,当电路中出现故障时,可以自动切换到备用电路,以保证电路的正常工作。

二、自修复技术自修复技术旨在在故障发生时,自动对电路进行修复,使电路能够自行恢复正常运行。

主要的自修复技术包括:1. 自动检测与定位:通过引入故障检测机制,可以及时发现电路中的故障,并通过定位技术确定故障的具体位置。

2. 错误分析与诊断:通过对故障进行分析与诊断,找出导致故障的原因,并提供相应的修复方案。

3. 自动修复:根据错误分析与诊断结果,自动进行修复操作,恢复电路的正常工作。

修复策略可以包括引入备用电路、自动补丁生成、替换故障元件等。

三、电路容错与自修复技术的应用电路容错与自修复技术广泛应用于各个领域,其中包括:1. 通信领域:在信号传输过程中,容错技术可以提高通信信号的质量和可靠性,而自修复技术可以自动恢复信号传输中的故障,确保通信的连续性。

2. 电力系统:在电力系统中,容错技术可以提高电网的协调性和稳定性,自修复技术可以及时修复电力设备的故障,降低电力系统的停电风险。

3. 航空航天领域:在航空航天领域中,电路容错与自修复技术可以提高飞行器的安全性和可靠性,尤其是在面临极端环境和飞行故障时。

4. 智能电子设备:在智能电子设备中,容错技术可以提高电子设备的稳定性和可靠性,自修复技术可以修复设备中的软件或硬件故障,延长设备的寿命。

ESD保护版图设计

摘要静电放电(简写为ESD)是集成电路(简写为IC)在制造、运输、以及使用过程中经常发生并导致IC芯片损坏或失效的重要原因之一。

工业调查表明大约有40%的IC失效与ESD/EOS(过强的电应力)有关。

因此,为了获得性能更好更可靠的IC芯片,对ESD开展专门研究并找到控制方法是十分必要的。

随着芯片尺寸的持续缩小,ESD问题表现得更加突出,已成为新一代集成电路芯片在制造和应用过程中需要重视并着力解决的一个重要问题。

论文论述了CMOS集成电路ESD 保护的必要性,研究了在CMOS电路中ESD 保护结构的设计原理,分析了该结构对版图的相关要求,重点讨论了在I/O电路中ESD 保护结构的设计要求。

论文所做的研究工作和取得的结果完全基于GGNMOS的器件物理分析,是在器件物理层次上研究ESD问题的有益尝试;相对于电路层次上的分析结果,这里的结果更加准确和可靠,可望为GGNMOS ESD保护器件的设计和制造提供重要参考。

关键词:静电放电(ESD);接地栅NMOS;保护器件;电源和地AbstractThe electrostatic discharge (ESD) is integrated circuit (IC) in manufacturing, transportation, and use process occurs frequently and cause IC chips damage or failure of one of the important reasons. Industrial survey shows that about 40 percent of IC failure and ESD/EOS (overpowered electrical stress) relevant. Therefore, in order to obtain better performance more reliable IC chips, to carry out special research and find the ESD control method is very necessary. Along with the continuous narrowing, chip size behaved more prominent ESD problems, has become a new generation of integrated circuit chip in the manufacture and application process needed to pay attention to and addressing an important question.This paper discusses the CMOS integrated circuit, the necessity of ESD protection in CMOS circuit was studied in the structure of ESD protection design principle, analyzes the structure on the map the relevant requirements, especially discussed in the I/O circuit ESD protection structure design requirements.Keywords:Electrostatic Discharge, GND gate NMOS, Protected Device, Power and Ground目录摘要 (1)Abstract (2)第1章绪论 (4)1.1 集成电路的发展状况 (4)1.1.1 集成度的提高 (4)1.1.2 摩尔定律 (4)1.2 集成电路中的ESD保护 (5)1.2.1 为何出现ESD (5)1.2.2 ESD保护的必要性 (5)第2章关于版图设计与版图设计环境的介绍 (7)2.1 集成电路版图设计 (7)2.2 版图结构 (7)2.3 版图设计流程与方法 (8)2.4 版图设计环境 (8)2.4.1 Technology file 与Display Resource File 的建立 (9)2.4.2 Virtuoso工具的使用 (9)第3章CMOS电路的ESD保护结构版图设计 (13)3.1 CMOS电路中ESD测试 (13)3.2 ESD保护原理 (14)3.3 CMOS电路ESD保护结构的设计 (14)3.3.1 CMOS电路ESD保护器件 (15)3.4 CMOS电路ESD保护结构的版图设计 (16)3.4.1 版图设计原则 (16)3.4.2 ESD保护结构版图设计 (17)第4章结束语 (18)参考文献 (19)致谢 (20)第1章绪论1.1 集成电路的发展状况1.1.1 集成度的提高真正导致数字集成电路技术发生革命性变化的是半导体存储器和微处理器的引入。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

图1 电机控制系统中电机换相电路自修复实现 Fig.1 Realization of commutation circuit in motor controlling system

电子系统没 有 损 伤 之 前,系 统 的 故 障 可 以 通 过 软件复位或者加入纠错程序恢复。一旦 ESD 等电 磁干扰环境 导 致 电 子 电 路 局 部 损 伤 ,电 路 功 能 的 恢 复 需 要 硬 件 电 路 的 支 持 才 能 实 现。演 化 硬 件 (evolvable hardware,EHW)是模拟自然进化而设计 的一种电路设计技 术。Miller等 人 把 遗 传 算 法 和 重 配置硬件电 路 结 合 在 一 起,实 现 电 路 结 构 的 动 态 改 变[13-16]。在电路的容错运行和故障修复中已经有了 对该技术的相关研究。随着集成电路技术的不断进 步和可编 程 芯 片 的 广 泛 应 用,Ortega等 人 基 于 可 编 程器 件 对 演 化 硬 件 技 术 进 行 了 深 入 的 研 究 。 [17-20] Stoica致力于使电子系统具有适应环境的能力 。 [21-22] 上述研究成果使得数字电路故障自修复和环境自适

Shijiazhuang 050003,China)

Abstract:In order to make the digital circuit to recover from faults and improve the reliability of digital circuit,a new self-repairing digital circuit model was proposed based on evolvable hardware(EHW ).The commutator of brushless direct current motor(BDCM)is implemented with the self-repairing digital circuit model which includes a microprocessor and a reconfigurable circuit.A fault injection-reparation experiment was carried out in the model, and the effect of the presented model on repairing ability of the designed circuit was analyzed.Then,we improved the model to enhance the probability of repairing circuit by introducing key functions.The results show that self- repairing digital circuit model can always recover from fault when ratio of fault units to total units is smaller than 50% .Therefore,the given model can repair circuits successfully when it is subjected to certain faults.It is concluded that the improved model can reduce the time of self-repairing and can raise the probability and speed of the repair. Key words:electrostatic discharge(ESD);faults self-repairing;reconfigurable circuit;key functions;brushless direct current motor;repair probability of faults

重配置电路中每一个 PE 单元的输入,既可接 收前面任意一列 PE单元的输出,也可以接收电路输 入。同样,电路的输出可来自于任意一列 PE 的 输 入。上述连接方式保证了 PE 资源的充分利用,PE 间的互连均 由 多 路 选 择 器 实 现 ,通 过 染 色 体 编 码 对 多路选择器进行配置,进而确定 PE单元的输入。

பைடு நூலகம்

复 ,改 进 的 自 修 复 数 字 电 路 模 型 降 低 了 电 路 生 成 时 间 ,提 高 了 电 路 修 复 概 率 和 速 度 。

关键词:静电放电 (ESD);故障自修复;重配置电路;关键函数;无刷直流电机;故障修复率

DOI:10.3969/j.issn.1003-6520.2012.09.027

高电压技术 第38卷 第9期 2012年9月30日 High Voltage Engineering,Vol.38,No.9,September 30,2012

2329

静电放电损伤自修复数字电路模型的建立与优化

常小龙,刘尚合,满梦华,李川涛,褚 杰 (军 械 工 程 学 院 静 电 与 电 磁 防 护 研 究 所 ,石 家 庄 050003)

文 章 编 号 :1003-6520(2012)09-2329-07

Construction and Improvement of Self-repairing Digital Circuit Model for Electrostatic Discharge Damage

CHANG Xiaolong,LIU Shanghe,MAN Menghua,LI Chuantao,CHU Jie (Research Institute of Electrostatic and Electromagnetive Protection,Mechanical Engineering College,

摘 要:为了使数字电路在产生故障失效后实现功能自动恢复,提高 电 路 可 靠 性,基 于 演 化 硬 件(EHW)原 理 建 立

了 自 修 复 数 字 电 路 模 型 ,该 模 型 主 要 包 括 微 处 理 器 和 重 配 置 电 路 2 个 部 分 。 利 用 自 修 复 数 字 电 路 模 型 实 现 无 刷 直

流电机控制系统中的换相电路,并对换相电路进行了故障注入修复实验。深入分 析 了 自 修 复 数 字 电 路 模 型 对 电 路

演化修复的影响,通过引入关键函数对自修复数字 电 路 模 型 进 行 了 改 进。 实 验 结 果 表 明,当 注 入 故 障 单 元 数 小 于

总单元数的50%时,改进后的自修复数字电路 模 型 修 复 率 达 到 100%。 因 此,该 模 型 能 够 对 部 分 故 障 进 行 成 功 修

Sekanina在文献[19]中给出了一种常用的重配 置电路,其电路节点包含的功能通常是与(AND)、或 (OR)、非(NOT)、异或(XOR)等基本 门 单 元。利 用 上述基本门单元得到 PE 单元结构如图1(b)所示, 包括配置寄 存 器、多 路 选 择 器、基 本 逻 辑 运 算 单 元。 重配置电路中所有 PE单元寄存器的值构成了电路 演化所需的染色体。寄存器中存放的是 PE 单元的 基因,PE单元的基因表示节点的功能以及与其他节 点的连接,Fun表示 PE 单元的功能,Back和 Sel表 示逻辑的输入来自的行和列。

1 ESD 自修复数字电路模型

利用演化硬 件 构 建 电 路 时,电 路 功 能 模 块 由 重 配置电路构成[19]。功能电路受到 ESD 干扰产生故 障时,系统通过演化改变电路结构恢复系统功能。

为了实现电路 ESD故障自动修复,构建了一种 ESD 自修复 数 字 电 路 模 型,如 图 1 所 示。 该 模 型 包 含2部分,一是微处理器,主要用于执行演化算法和 故障检测。演化算法的基因型采用 Cartesian遗传编 程编码方式[23]。这种编码方式染色体编码与重配置 电路的结构 对 应,能 够 实 现 基 因 型 到 表 现 型 的 快 速 映 射;二 是 由 可 编 程 单 元 (programmable element, PE)和内部互联网络 构 成 的 重 配 置 电 路 。 重 配 置 电 路实际上是由 m×n个可编程单元构成的 m 行n 列 矩阵,根据 外 部 环 境 变 化 实 现 电 路 的 动 态 生 成。 电 路中某些 PE单元产生故障,微处理器检测到电路失 效后,重新配置 PE 单元的连接方式,从而实现电路 结构变换,实 现 电 路 的 故 障 自 修 复 功 能。 随 着 可 编 程器件性能 不 断 提 高,在 片 内 同 时 构 建 微 处 理 器 和 重配置电路已经能够实现。因此基于此模型可以根 据电路状态和所处环境动态生成目标电路。

基 金 资 助 项 目 :国 家 自 然 科 学 基 金 专 项 基 金 (10927506)。 Project supported by National Natural Science Foundation of China (10927506).

电子系统具 有 自 我 修 复 的 能 力 ,因 此 一 些 新 的 电 磁 防护技术随之出现 。 [11-12]

实 验 板 核 心 部 件 是 XILINX SPARTAN XC3S500EFPGA 芯片,内部配置了1个微处理器和 1个重配置电路,并按 照 图 1(b)PE 单 元 的 结 构 设 计 重配置电路。微处理器主要运行演化算法成相应电 路结构编码,电 路 结 构 编 码 决 定 了 重 配 置 演 化 模 型 的 PE单元间连接关系和 PE的功能。

的概率。影响自修复概率的主要因素是自修复电路 模型的结构和自修复电路模型中 ESD 引起故障单 元的数目。系统修复时间必须满足实时性。