PCB设计规则检查器1

PCB布线设计规范精选全文

可编辑修改精选全文完整版印制电路板设计规范一、适用范围该设计规范适用于常用的各种数字和模拟电路设计。

对于特殊要求的,尤其射频和特殊模拟电路设计的需量行考虑。

应用设计软件为Protel99SE。

也适用于DXP Design软件或其他设计软件。

二、参考标准GB 4588.3—88 印制电路板设计和使用Q/DKBA—Y004—1999 华为公司内部印制电路板CAD工艺设计规范三、专业术语1.PCB(Print circuit Board): 印制电路板2.原理图(SCH图):电路原理图,用来设计绘制,表达硬件电路之间各种器件之间的连接关系图。

3.网络表(NetList表):由原理图自动生成的,用来表达器件电气连接的关系文件。

四、规范目的1.规范规定了公司PCB的设计流程和设计原则,为后续PCB设计提供了设计参考依据。

2.提高PCB设计质量和设计效率,减小调试中出现的各种问题,增加电路设计的稳定性。

3.提高了PCB设计的管理系统性,增加了设计的可读性,以及后续维护的便捷性。

4.公司正在整体系统设计变革中,后续需要自主研发大量电路板,合理的PCB设计流程和规范对于后续工作的开展具有十分重要的意义。

五、SCH图设计5.1 命名工作命名工作按照下表进行统一命名,以方便后续设计文档构成和网络表的生成。

有些特殊器件,没有归类的,可以根据需求选择其英文首字母作为统一命名。

对于元器件的功能具体描述,可以在Lib Ref中进行描述。

例如:元器件为按键,命名为U100,在Lib Ref中描述为KEY。

这样使得整个原理图更加清晰,功能明确。

5.2 封装确定元器件封装选择的宗旨是1. 常用性。

选择常用封装类型,不要选择同一款不常用封装类型,方便元器件购买,价格也较有优势。

2. 确定性。

封装的确定应该根据原理图上所标示的封装尺寸检查确认,最好是购买实物后确认封装。

3. 需要性。

封装的确定是根据实际需要确定的。

总体来说,贴片器件占空间小,但是价格贵,制板相同面积成本高,某些场合下不适用。

PCB板设计规范检查表

3

工艺边一般以整板(即含拼板)的长边为工艺边,当短边与长边的比≤80%时, 必须以长边为工艺边。

4

工艺边宽度:双面或多层板5mm(MARK点不在工艺边上),双面或多层板10mm± 2mm(MARK点在工艺边上);单面板10mm±2mm;

检查问题点确认描述

第 2 页,共 5 页

对策

责任人

完成 时间

效果 验证

NO

检查项 目

检查内容及参考标准

自检 他检 检查问题点确认描述

4 导锡点的位置是否合理,导锡点与PCB板过炉方向相反,大小合适。 5 过回流焊的IC和排插的焊盘不允许有加拖锡点。

6

过回流焊的与大面积铺铜连接的小电流SMT焊盘应为网状(梅花形)连接(例如: 连接铺铜地线的焊盘),线宽0.3mm,连线数3条。

17 同一个元件的两个焊盘大小必须一致。

18 引脚间距<2mm插件焊盘非焊接面用绿油覆盖,特殊要求除外

19 焊盘不能被丝印覆盖。

20 烧录IC最好设计元件升级的焊盘或可植针的焊点。

1 PCB的拼板尺寸控制在宽100~200mm ×长200~310mm的面积范围内。

2

两面都有SMT元件的而且面积较小的PCB(比如KB板),4拼板,两正两反或正 反正反,一定要对称,正看和镜像都一样。

1 MARK点的直径为1mm。

2 MARK点的外环直径为3mm。

3 MARK点的边缘到PCB板边距离大于5mm。

4

MARK点与周围的元件距离大于4mm,四周5mm范围内不能有元器件、焊盘或测 试点。

5 一块PCB要有4个以上的MARK点,最好是对角,但是不能对称。

【AltiumDesigner】PCB如何用规则检查

【AltiumDesigner】PCB如何⽤规则检查简介在PCB的规则检查时,分3步骤:1、设置规则参数2、使能规则3、检查1、设置规则参数在PCB编辑界⾯,使⽤快捷按键D->R,可以调出PCB规则及约束编辑器如下:⼀些关键的规则介绍和规则的参数设置建议:Design Rules类型名称建议值Electrical 电⽓类型Clearance⾛线之间的间距≥6mil Short-Circuit短路不允许短路Un-routed Net没有⾛线的⽹络-Routing ⾛线Width⾛线宽度5mil~50milRouting Via Style过孔属性类型过孔焊盘外径⽐过孔内径⼤10mil即可。

内径≥8mil,外径≥18milPlane Polygon Connect Style铜⽪连接⽅式⾛线按照⼗字花连接。

过孔via和铜⽪直接连接。

Manufacturing可制造性Hole Size过孔尺⼨8mil~28milHole To Hole Clearance过孔间距≥8milMinimumSolderMaskSliver≥3mil,太⼩在焊接时,容易连焊Silk to Solder mask Clearance≥3mil,间距太⼩,丝印会印刷不上Silk To silk clearance≥1milNet Antennae0mil2、使能规则在PCB界⾯,快捷⽅式T->D,调出如下界⾯:点击Rules To Check,检查的规则的使能与禁⽌。

规则使能建议如下:在线:在编辑PCB时,实时检查的项⽬批量:在⼿动按规则检查时,使能的检查项⽬在默认情况下,有的项⽬没有勾选,需要⼀⼀检查项⽬是否需要勾选。

可以按照下⾯图⽰进⾏勾选,软件可⾃动记录选项。

3检查3.1按规则检查PCB编辑界⾯,快捷⽅式T->D->R,进⾏检查。

例如:按照项⽬⼀⼀审查冲突项,在了解冲突项后果的严重性,可调整规则、可修复冲突、可忽略。

PCB设计检查表-PCB checklist

59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88

3.6 3.7 3.8 3.9

没有锐角和90布线 高速信号线、时钟信号线遵循回路面积最小原则 总体布线均匀,布线尽可能短,且少过孔 布线线宽保持一致,没有跳变

2.10 普通板有大于3mm工艺边 2.11 器件布局间距,IC大于2mm、BGA大于5mm;特殊情况可适当调整。但保证IC大 于1mm,BGA大于3mm

2.12 压接件距其他器件大于5mm,焊接面压接件贯通区域无任何器件 2.13 有极性插装器件第一脚为方焊盘 2.14 坐标原点为板框左、下延伸线交点 2.15 板外框平滑弧度5mm,或者按结构尺寸图设计 2.16 高度≥10mm器件周围3mm内不能放置贴片器件(矮、小器件) 2.17 双列封装数字集成电路有1个或以上滤波电容 2.18 QFP、BGA、PLCC、模拟IC等器件有2个或以上滤波电容 2.19 含贴片器件的PCB,贴片器件所在面的板任选2角各放置一个定位光标 2.20 MOUNTING孔(安装孔)是否镀铜(要镀铜) 2.21 GUIDE PIN孔(定位孔)是否没镀铜(除另有说明,不要镀铜)

29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58

2.22 元器件的1脚是否为方PAD 2.23 POWER PLANE 分割时是否出现瓶颈 2.24 BGA SOCKET 相同的POWER PIN 是否连接起来 2.25 BGA SOCKET相同的GND PIN 是否连接起来 2.26 BGA SOCKET的四圈及四角,是否加上DECOUBLING CAP 的PATTERN 2.27 是否在板上形成了一圈POWER RING(永不要在板上形成了一圈POWER RING,否 则会产生电磁噪音,可把POWER RING 割成两个半圈 )

PCB标准设计规范-1

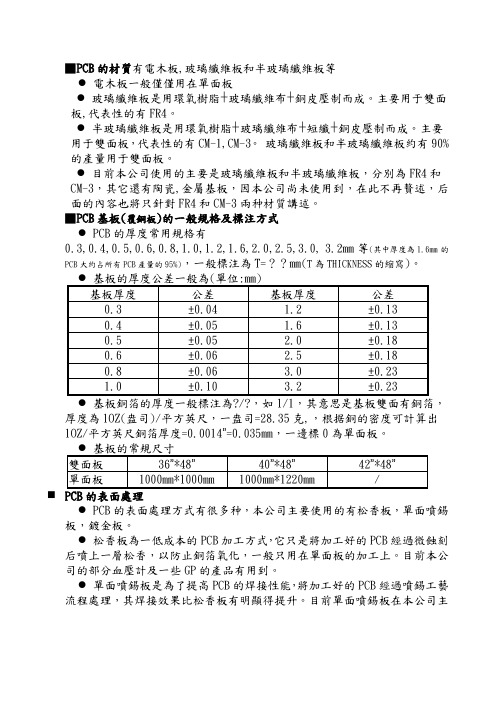

■P CB的材質有電木板,玻璃纖維板和半玻璃纖維板等●電木板一般僅僅用在單面板●玻璃纖維板是用環氧樹脂+玻璃纖維布+銅皮壓制而成。

主要用于雙面板,代表性的有FR4。

●半玻璃纖維板是用環氧樹脂+玻璃纖維布+短纖+銅皮壓制而成。

主要用于雙面板,代表性的有CM-1,CM-3。

玻璃纖維板和半玻璃纖維板約有90%的產量用于雙面板。

●目前本公司使用的主要是玻璃纖維板和半玻璃纖維板,分別為FR4和CM-3,其它還有陶瓷,金屬基板,因本公司尚未使用到,在此不再贅述,后面的內容也將只針對FR4和CM-3兩种材質講述。

■P CB基板(覆銅板)的一般規格及標注方式●PCB的厚度常用規格有0.3,0.4,0.5,0.6,0.8,1.0,1.2,1.6,2.0,2.5,3.0,3.2mm等(其中厚度為1.6mm 的PCB大約占所有PCB產量的95%),一般標注為T=??mm(T為THICKNESS的縮寫)。

厚度為1OZ(盎司)/平方英尺,一盎司=28.35克,,根据銅的密度可計算出1OZ/平方英尺銅箔厚度=0.0014”=0.035mm,一邊標0為單面板。

⏹●PCB的表面處理方式有很多种,本公司主要使用的有松香板,單面噴錫板,鍍金板。

●松香板為一低成本的PCB加工方式,它只是將加工好的PCB經過微蝕刻后噴上一層松香,以防止銅箔氧化,一般只用在單面板的加工上。

目前本公司的部分血壓計及一些GP的產品有用到。

●單面噴錫板是為了提高PCB的焊接性能,將加工好的PCB經過噴錫工藝流程處理,其焊接效果比松香板有明顯得提升。

目前單面噴錫板在本公司主要應用在部分血壓計及一些GP的產品上。

●鍍金板實際上是鍍鎳鍍金板,它又有鍍軟鎳軟金和鍍硬鎳硬金之分。

鍍軟鎳軟金其電鍍用的是氨基磺酸鎳系列電鍍液,鎳的鍍層是塊狀結晶,有無數的孔隙,比較适合打線作業。

鎳的鍍層一般要求150u”(3.8um)以上,金的鍍層一般要求1-3u”(0.025~0.075um)以上。

PCB设计规范1

PCB设计规范北方工业大学电气传动研究室(版权所有,翻版必究)目录1 前言 (3)1.1 目的 (3)2 术语和定义 (3)3 PCB设计的工艺规范 (5)4 PCB设计的布局规范 (8)5 PCB设计的布线规范 (12)6 元件库制作规范: (19)7 可维修性规范 (20)1前言1.1 目的本文档叙述了PCB设计规范,用于指导和规范PCB设计和制作工作。

2术语和定义1、印制电路板:PCB-printed circuit board,在绝缘基材上,按预定设计形成印制器件或印制线路以及两者结合的导电图形的印制板。

2、原理图:schematic diagram,电路原理图,用原理图设计工具绘制的、表达硬件电路中各种器件之间的连接关系的图。

3、网络表:Schematic Netlist,由原理图设计工具自动生成的、表达元器件电气连接关系的文本文件,一般包含元器件封装、网络列表和属性定义三部分。

4、顶层:Top Layer,封装和互连结构的一面,该面在布设总图上就作了规定(通常此面含有最复杂的或多数的元器件。

此面在通孔插装技术中有时称做“元器件面”)5、底层:Bottom Layer,封装及互连结构的一面,它是TOP面的反面。

(在通孔插装技术中此面有时称做“焊接面”)。

6、内层:Inner Layer,多层板除了顶层底层外的电气层。

7、板厚:board thickness,包括导电层在内的包覆金属基材板的厚度。

板厚有时可能包括附加的镀层和涂敷层。

8、金属化孔:Plated through hole,孔壁镀覆金属的孔。

用于内层和外层导电图形之间的连接,同义词:镀覆孔。

具体效果图如下:9、非金属化孔:NPTH-unsupported hole,没有用电镀层或其他导电材料加固的孔。

10、过孔:Via hole,用作贯通连接的金属化通孔,内部不需插装器件引脚或其他加固材料。

11、Solder mask or Solder resist,是用于在焊接过程中及焊接之后提供介质和机械屏蔽的一种覆膜。

PCB图的设计规则检查

北京印刷学院

第四章 PCB图的设计规则检查

电路设计与制版

把需要等长的网络名,放到右边的Member中。

北京印刷学院

第四章 PCB图的设计规则检查

电路设计与制版

把鼠标放在Matched Net Lengths上, 点击鼠标右键, 单击New Rule,新建一个规则。

北京印刷学院

第四章 PCB图的设计规则检查

是否在线检查, 一边绘图,一 边检查

Batch: 执行按钮Run Design Rule Check时,要进行 检查的规则

按钮Run Design Rule Check :进行 规则检查

北京印刷学院

第四章 PCB图的设计规则检查

设计规则检查生成的报告:

电路设计与制版

北京印刷学院

第四章 PCB图的设计规则检查

第四章 PCB图的设计规则检查

电路设计与制版

《电路设计与制版》

主讲教师:董 武 北京印刷学院 信息工程学院

办公室:主校区B楼412 Email: dongwu@

北京印刷学院

第四章 PCB图的设计规则检查

电路设计与制版

第四章PCB图的设计规则检查

一. 设计规则的设置 二、设计规则检查

电路设计与制版

北京印刷学院

第四章 PCB图的设计规则检查

电路设计与制版

Matched Net Lengths :用于进行等长的布线

首先:把需要等长的多个网络名设置为一个网络类。

网络类:包含需要等长的网络名。 菜单 Design / Classes:在弹出的对话框中,在Net Classes上,单击鼠标右键,选择子菜单Add Class

Report Options选项卡:

最新华为PCB设计规范标准

华为PCB设计规范I. 术语1..1 PCB(Print circuit Board):印刷电路板。

1..2 原理图:电路原理图,用原理图设计工具绘制的、表达硬件电路中各种器件之间的连接关系的图。

1..3 网络表:由原理图设计工具自动生成的、表达元器件电气连接关系的文本文件,一般包含元器件封装、网络列表和属性定义等组成部分。

1..4 布局:PCB设计过程中,按照设计要求,把元器件放置到板上的过程。

深圳市华为技术有限公司1999-07-30批准,1999-08-30实施。

1..5 仿真:在器件的IBIS MODEL或SPICE MODEL支持下,利用EDA设计工具对PCB的布局、布线效果进行仿真分析,从而在单板的物理实现之前发现设计中存在的EMC问题、时序问题和信号完整性问题,并找出适当的解决方案。

深圳市华为技术有限公司1999-07-30批准,1999-08-30实施。

II. 目的A. 本规范归定了我司PCB设计的流程和设计原则,主要目的是为PCB设计者提供必须遵循的规则和约定。

B. 提高PCB设计质量和设计效率。

提高PCB的可生产性、可测试、可维护性。

III. 设计任务受理A. PCB设计申请流程当硬件项目人员需要进行PCB设计时,须在《PCB设计投板申请表》中提出投板申请,并经其项目经理和计划处批准后,流程状态到达指定的PCB设计部门审批,此时硬件项目人员须准备好以下资料:⒈经过评审的,完全正确的原理图,包括纸面文件和电子件;⒉带有MRPII元件编码的正式的BOM;⒊PCB结构图,应标明外形尺寸、安装孔大小及定位尺寸、接插件定位尺寸、禁止布线区等相关尺寸;⒋对于新器件,即无MRPII编码的器件,需要提供封装资料;以上资料经指定的PCB设计部门审批合格并指定PCB设计者后方可开始PCB 设计。

B. 理解设计要求并制定设计计划1. 仔细审读原理图,理解电路的工作条件。

如模拟电路的工作频率,数字电路的工作速度等与布线要求相关的要素。

第四章PCB图的设计规则检查

1)Width 设置导线宽度规则 作用: 设定导线的宽度

Min Width: 设置导线的最 小宽度

Max Width:

设置导线的最大宽 度

第四章PCB图的设计规则检查

2)Routing Via Style 过孔规则 作用: 设置过孔的最大值、最小值

Via Diameter: 设置过孔的 外孔径的最大值、最小值

默认:不同网 络相连是短路 不选

第四章PCBBiblioteka 的设计规则检查3)Un-Rounted Net: 布线规则 作用: 检查是否完成一个网络的所有布线

第四章PCB图的设计规则检查

2. Routing 布线规则 作用:设置布线方面的一些规则

Enabled: 设置此规则是不是使用。

第四章PCB图的设计规则检查

把需要等长的网络名,放到右边的Member中。

第四章PCB图的设计规则检查

把鼠标放在Matched Net Lengths上, 点击鼠标右键, 单击New Rule,新建一个规则。

第四章PCB图的设计规则检查

Where The First Object Matches: 选择“Net Class” 下拉框:选择需要等长的网 络类名。 Tolerance:进行等长布线时 所允许的误差,设置为零

Enabled: 设置此规则是不是使用。

第四章PCB图的设计规则检查

1)Clearance 安全间距规则:

作用: 设置走线Track、 过孔Via、 焊盘Pad自身之间 或两两之间的 最小间距

注意:电路板工厂加工的最 小间距一般为4mil

第四章PCB图的设计规则检查

2)Short-Circuit 短路许可规则: 作用: 设定不同网络相连时是否算作短路

pcb元件检查规则

pcb元件检查规则PCB元件检查规则主要包括以下方面:1. 元器件间距和布局:确保元器件之间有足够的空间,以防止短路或干扰。

电源元器件和敏感信号元器件之间的隔离,以减小互相干扰的机会。

2. 方向和朝向:确保极性敏感的元器件被正确放置,并遵守电路原理图中的方向。

元器件方向的一致性,以减少生产错误的机会。

3. 信号完整性:控制信号传输线的长度、走线方式和阻抗,以减少信号传输延迟和失真。

4. 电源供应:使用足够的电源平面/地平面来提供稳定的电源分布。

最小化电源线的电感,以提供更稳定的电源。

5. 散热和热管理:合理布局散热元器件,以确保元器件在高功率应用中不会过热。

不要将热敏感元器件放置在高温元器件附近。

6. EMI控制:布局元器件以减小电磁辐射和敏感性,避免创建回路和天线。

使用地平面和屏蔽层来抑制EMI。

7. 元器件封装检查:元件的封装和实物是否相符。

8. 元器件放置位置检查:元件是否便于安装与拆卸;对温度敏感元件是否距发热元件太近;可产生互感元件距离及方向是否合适;接插件之间的放置是否对应顺畅;便于拔插;输入输出;强电弱电;数字模拟是否交错;上风侧和下风侧元件的安排。

9. 元器件管脚检查:具有方向性的元件是否进行了错误的翻转而不是旋转;元件管脚的安装孔是否合适,能否便于插入。

10. 网络表检查:原理图和PCB图对应检查,防止网络表丢失。

11. 完整性检查:检查每一个元件的空脚是否正常,是否为漏线;检查同一网络表在上下层布线是否有过孔,焊盘通过孔相连,防止断线,确保线路的完整性。

12. 字符放置检查:检查上下层字符放置是否正确合理,不要放上元件盖住字符,以便于焊接。

此外,还可以通过建立详细的元器件布局文档,包括PCB图纸和布局图,来记录和传达元器件布局信息。

以上规则可根据实际需求适当增删或修改。

编写PCB设计规则检查器DRC的系统方法

编写PCB设计规则检查器DRC的系统方法编写属于自己的PCB设计规则检查器具有很多优点,尽管设计检查器并不那么简单,但也并非高不可攀,因为任何熟悉现有编程或脚本语言的设计人员完全能够设计检查器,这项工作的好处是不可估量的,本文介绍编写PCB设计规则检查器的技巧。

本文阐述了一种编写PCB设计规则检查器(DRC)的系统方法。

利用电路图生成工具得到PCB设计后,即可运行DRC以找到任何违反设计规则的故障。

这些操作必须在后续处理开始之前完成,而且开发电路图生成工具的开发商必须提供大多数设计人员都能轻松掌握的DRC工具。

然而,市场销售的通用工具通常不具备足够的灵活性以满足特定的设计需要。

因此,客户必须将新特性需求反映给DRC工具开发商,而这通常需要耗费一定的资金和时间,尤其当需求不断更新时。

幸运的是,大多数工具开发商均可为客户提供编写属于自己的DRC 以满足特定需求的便捷方法。

但是,这种具有强大功能的工具尚未得到广泛认同或使用。

本文提供了利用DRC工具获取最大收益的实用指南。

由于DRC必须遍历PCB设计的整个电路图,包括每个符号、每个引脚、每个网路、每种属性,如有必要还能创建数目不限的“附属”文件。

如4.0节所述,DRC可以标示出任何违反设计规则的细微偏差。

例如其中一个附属文件就可能包含设计用到的全部去耦电容。

如果电容数低于或高于期望值,就将在可能出现电源线dv/dt问题的地方标注红色记号[1]。

这些附属文件或许必不可少,但并非任何商用DRC工具都一定能创建这些文件。

DRC的另一优势是便于更新,以适应新设计特性(如那些可能影响设计规则的新特性)的需要。

而且,一旦在该领域获得充分经验,那么还能实现许多其它功能。

例如,如果能编写属于自己的DRC,那么就能编写属于自己的物料清单(BOM)创建工具,这样就能更好地处理特定用户需求,如如何获取本身不属于电路图数据库一部分的器件“额外硬件”(如插座、散热装置或螺丝刀)。

PCB优先选项设定、设计规则设定

一、PCB 优先选项设定PCB优先选项设定对话框设定和PCB操作相关的参数,可以通过Tools\preferences 命令进入.这些设定会保存在系统环境中,打开不同的PCB 会使用相同的设定项Online DRC: 实时错误检测选择Snap to center: 移动焊盘和过孔时,鼠标定位于中心. 移动元件时定位于参考点.移动走线时定位于顶点Double click Runs Inspector: 双击打开Inspector, 而不是通常的属性对话框Remove duplicates: 在输出数据时移去属性相同的元素Confirm Global edit: 确认全局编辑Protect locked objects: 锁定元素不能移动Click clears selection: 单击鼠标清除选择Shift click to select: Shift+click组合键选择相应元素(建议选择元件,铜皮等较大元素) Smart track Ends: 设定鼠线的显示方式Undo/Redo: 设定次数(建议设定较小数值,大数值对内存要求比较高)Rotation Step: 设定旋转角度Cursor type: 设定鼠标形状Comp Drag: 设定移动元件时连接的走线是否一起拖动Autopan options: 设定平移窗口的类型Polygon repour: 设定重新铺铜的一些属性Use DirectX: 使用6.3 版图形引擎,处理图形速度增加20 倍Convert special String: 转换特殊字符.(如时间,日期等)Redraw layers: 在层切换时重新刷新屏幕Transparent layers: 透明层选项Use alpha blending: 选择该项,当元素重叠时会以半透明方式显示High light in Full: 以高亮方式显示选择的目标Use net color for highlight: 使用网络特有颜色高亮显示网络Use transparent mode when masking: 筛选时使用半透明模式Apply Mask during interactive editing: 布线时灰色显示不活动网络Apply highlight during interactive editing: 布线时高亮显示活动网络(不推荐使用)Draft threshold: 当线宽或字符小于设定值时以外形轮廓显示Plane drawing: 设定平面层显示的方式, 选择“outlined layer control”或“outlined net control”时,以负片格式显示,如一段走线表示这一段没有铜皮. “solid net color”则以半透明的方式显示平面层上的网络Pad and Via display options: 显示焊盘,过孔的网络名和标号等Use smart display color: 智能控制显示的字符大小Net names on Tracks: 网络名在走线上显示的模式Single layer mode: 设定单层的显示模式Display: 设定显示时的各种参数Visible display modes:Cursor location: 当前鼠标位置Last click delta: 鼠标移动变化量. 在绘制边框和放置元件时比较方便其他选项可以按需设定,在下面的图形中可以预览显示效果Interactive routing conflict resolutionNone: 没有反映Stop at first conflicting object: 停止在第一个有冲突的地方Push conflicting object: 推移有冲突的对象Smart connection routing resolutionNone: 没有反映Stop at first confliction object: 停止在第一个有冲突的地方Walk around controlling object: 绕过有冲突的对象Interactive routing optionsRestrict to 90/45: 把拐角模式限制在90/45模式下Auto complete: 在智能布线时自动完成布线Automatically terminate routing: 布完一个网络时自动结束Automatically remove loops: 自动移去网络环路Interactive routing width/via source选择走线宽度和过孔的大小.布线时按shift+W 快捷键可以弹出预设线宽选择框. 放置过孔时按TAB 键可以弹出过孔属性对话框.二、设计规则设定Electrical Clearance选择Electrical\clearance 下clearance 分支,也可以右键点击clearance,在弹出菜单中选择New rules, 新建一个规则. 在右侧可以设定不同对象之间的间距.All: 所有电气元素Net: 指定网络Net class: 网络组Layer: 层Net and Layer: 指定层上的网络Advanced: 高级设定,点击query builder 按钮进入设定框.在左边窗口有不同对象的选项,如选择“Object kind is”, 中间选择“Poly”, 则选中了多边形铺铜的对象. Query 语句中出现相应的语句“IsPolygon”. 再设定另一个对象的范围,如“all”, 则设定了多边形和全部电气元素之间的间距.Routing 规则设定选择Routing\clearance 分支就可以设定走线宽度,过孔大小等规则. 如图4.3,图4.4对不同的网络设定不同的线宽和不同的过孔大小.元件间距设定选择Placement\component clearance, 设定元件之间的间距. 图 4.5 Quick check: 包含所有基本元素的最小多边形Multi layer check: 包含插列元件在对应层的影响.Full check: 使用元件基本元素真实占用的多边形Use component Bodies: 只检测元件的基本元素和其他元件之间的间距。

PCB设计规范(最新版本)

印刷电路板〔PCB〕设计标准一:适用范围:本标准适用于我司CAD设计的所有印刷电路板〔简称:PCB〕二:目的:1. 本标准规定我司PCB设计流程和设计原那么,为PCB设计者提供必须准那么2. 提高PCB设计质量和效率,提高PCB的可生产性,可测性,可维护性。

三:设计任务受理:1. 电子工程师接到上级分配的新产品开发工程时,首先填写?新产品PCB设计进度表?。

然后根据新产品要求完成电路原理图设计,并通过电子组及软件组审核。

2 . 对于设计电路中不常用元件,先通过查公司ERP,如果没有库存,那么需要在第一时间写申购单申请所需元器件,保证新产品开发进度。

3. 要求构造组负责人员提供正确的PCB构造图及3D效果图,在导入构造图过程中须与构造工程师沟通,了解各筋位线分层情况及定位孔位置等等信息。

4. 对于常规产品的设计,那么可根据原有的资料进展LAYOUT,须注意样品单上产品的交期。

四:设计过程:1 创立网络表:1. PCB设计人员根据具体的CAD设计软件创立符合要求的网络表。

2. 确定元器件封装〔PCB FOOTPRINT〕,对于新元件需根据元器件资料制作相应封装。

3. 引入网络表创立PCB板设计文件。

2 元器件布局1. 根据构造图设计板框尺寸,按构造要求定位元器件,并按要求给予尺寸标注。

比方:PCB板厚,PCB的外形尺寸等等。

2. 根据构造图和生产实际要求设计制止布线区。

3. 根据产品要求合理选取板材,定义板层。

4. 布局的根本原那么:a). 按照<先大后小,先难后易,先整体,后局部>的布局原那么,重要的单元电路,核心元器件应优先布局。

b). 布局应参考电原理图,根据信号流向规律按排主要元器件。

c). 布局应尽可能满足:连线尽可能短,高电压,大电流信号线与低电压,小电流信号线完全分开。

d). 板面元器件均匀分布,重心平衡,版面美观的标准优化布局。

5. 布局过程中的元件放置:a). 同类型插装元器件在X或Y方向上应朝一个方向放置,便于生产和检验。

PCB 原理图 Checklist检查表

类别描述检视规则原理图需要进行检视,提交集体检视是需要完成自检,确保没有低级问题。

检视规则原理图要和公司团队和可以邀请的专家一起进行检视。

检视规则第一次原理图发出进行集体检视后所有的修改点都需要进行记录。

检视规则正式版本的原理图在投板前需要经过经理的审判。

差分网络原理图中差分线的网络,芯片管脚处的P 和N 与网络命令的P 和N 应该一一对应。

单网络原理图中所有单网络需要做一一确认。

空网络原理图中所有空网络需要做一一确认。

1、原理图绘制中要确认网格设置是否一致。

2、原理图中没有网格最小值设置不一致造成网络未连接的情况。

网络属性确认网络是全局属性还是本地属性1、原理图中器件的封装与手册一致。

2、原理图器件是否是标准库的symbol 。

绘制要求原理图中器件的封装与手册一致。

指示灯设计默认由电源点亮的指示灯和由MCU 点灭的指示灯,便于故障时直观判断电源问题还是MCU 问题网口连接器确认网口连接器的开口方向、是否带指示灯以及是否带PoE 网口变压器确认变压器选型是否满足需求,比如带PoE 按键确认按键型号是直按键还是侧按键电阻上下拉同一网络避免重复上拉或者下拉OD 门芯片的OD 门或者OC 门的输出管脚需要上拉匹配高速信号的始端和末端需要预留串阻三极管三极管电路需要考虑通流能力可测试性在单板的关键电路和芯片附近增加地孔,便于测试连接器防呆连接器选型时需要选择有防呆设计的型号仿真低速时钟信号,一驱动总线接口下挂器件的驱动能力、匹配方式、接口时序必须经过仿真确认,例如MDC/MDIO 、IIC 、PCI 、Local bus 仿真电路中使用电感、电容使用合适Q 值,可以通过仿真。

时序确认上电时序是否满足芯片手册和推荐电路要求。

时序确认下电时序是否满足芯片手册和推荐电路要求。

时序确认复位时序是否满足芯片手册和推荐电路要求。

复位开关单板按键开关设计,要防止长按按键,单板挂死问题,建议按键开关设计只产生一段短脉宽低电平。

PCB设计 Cadence库检查规则

Cadence 库检查规则1.Symbol检查规则1.1 Symbol必须有pin_ num. 和pin_ name,一般要跟spec相同,但硬件若有特殊要求时应将硬件要求的pin_ name与spec的pin_ name一起写入1.2 User properties 中可包括的信息有(如果采用中心库,可以不用填这些,到时候在数据库填写也可以):a. REF----part reference (visible)b. value (系统默认值hidden)c. real value(只有电阻,电容,电感,晶振有此项visible)d. part number (visible)e. MPN----manufacturer part number (visible)f. PCBFOOTPRINT (hidden)g. Description (hidden)h. Creator name and Date (hidden)以上这些信息须要跟数据库信息保持一致,对应的PCB Footprint 填写正确1.3 外框和pin 必须在格点上HW有推荐原理图样本,当pin定义和spec不一样时,两个pin_ name都要写上去。

若是非金属化孔,非金属化孔就pin_ name定义为NCD (NOT CONNECT DRILL)用来固定的焊盘用MT开头命名。

2.PCB footprint 检查规则2.1 确定封装类型:根据SPEC确认封装的外形。

当spec中有多种封装时,根据description来确定封装类型2.2 焊盘检查一般焊盘包括:PAD ; SOLDER-MASKE ; PASTE-MASKEc.通常焊盘尺寸solder>pad>paste, 单边0.05mm,总共三者两两相差0.1mm。

d.若是大焊盘,面积超过4mm2, solder<pad,而且钢网做特殊处理,钢网面积占焊盘面积55-65%,若是spec有推荐,严格按照spec要求制作。

编写PCB设计规则检查器(DRC)的系统方法

编写PCB设计规则检查器(DRC)的系统方法于此并将保存在联合或全局的程序库目录中,这些符号具有一些不同于本地器件符号的重要特征。

设计人员通常会因为没有采用共同符号取代本地符号而引入设计错误。

legal_lib_path_name 可选,因为对于大多数电路图工具,程序库信息包含在启动工具所需的初始化文件中。

对于ViewDraw 工具,该文件称为viewdraw.ini,当工具启动时,该文件就自动创建(利用脚本程序):目录[r] /corp_lib/pcb/symbol_libraries/viewdraw/fct (fct)。

Fct(快速CMOS 技术)是ViewDraw 众多子库中的一个,也是fct 器件各符号的来源。

如果初始化文件存在,那么DRC 不仅可以而且也应当直接读取该文件,因为设计人员可以及时地添加新程序库。

* 可以创建包含合法上拉电阻的legal_pullup_res 文件以检测那些被终止以及未被使用的输入引脚。

通常,可以限定一组设计人员能使用的电阻,当然电阻值本身也是一个重要因素。

如果上拉了未使用的输入引脚,那么该电阻的阻值将为5K 或更高。

* 可以创建包含合法下拉电阻的legal_pulldown_res 文件以检测那些被终止以及未被使用的输入引脚。

如果下拉了未使用的输入引脚,那么阻值将会很小以阻止任何电流泄漏,从而使引脚电压高于触发阀值。

* 可以创建包含合法去耦电容的legal_decoup_cap 文件,而且公司还可要求设计人员只使用特定的合格器件以满足电源线dv/dt 要求。

* 可以创建一个包含器件符号全部属性的legal_comp_attr 文件,如PART_NO、GEOM、REFDES 和SIM_CLASS。

BOAM 创建工具、Verilog 网表分析器及其它工具都能使用这些属性。

编写PCB设计规则检查器技巧

编写PCB设计规则检查器技巧本文阐述了一种编写设计规章检查器(DRC)系统办法。

利用生成工具得到PCB设计后,即可运行DRC以找到任何违背设计规章故障。

这些操作必需在后续处理开头之前完成,而且开发图生成工具开发商必需提供大多数设计人员都能轻松把握DRC工具。

编写属于自己PCB设计规章检查器具有无数优点,尽管设计检查器并不那么容易,但也并非高不行攀,由于任何认识现有编程或脚本语言设计人员彻低能够设计检查器,这项工作益处是不行估计。

然而,市场销售通用工具通常不具备足够灵便性以满足特定设计需要。

因此,客户必需将新特性需求反映给DRC工具开发商,而这通常需要耗费一定资金和时光,尤其当需求不断更新时。

幸运是,大多数工具开发商均可为客户提供编写属于自己DRC以满足特定需求便捷办法。

但是,这种具有强大功能工具尚未得到广泛认同或用法。

本文提供了利用DRC 工具猎取最大收益有用指南。

因为DRC必需遍历 PCB设计囫囵电路图,包括每个符号、每个引脚、每个网路、每种属性,如有须要还能创建数目不限“附属”文件。

如4.0节所述,DRC可以标示出任何违背设计规章细微偏差。

例如其中一个附属文件就可能包含设计用到所有去耦。

假如电容数低于或高于期望值,就将在可能浮现电源线dv/dt问题地方标注红色记号。

这些附属文件或许必不行少,但并非任何商用DRC工具都一定能创建这些文件。

DRC另一优势是便于更新,以适应新设计特性(如那些可能影响设计规章新特性)需要。

而且,一旦在该领域获得充分阅历,那么还能实现许多其它功能。

例如,假如能编写属于自己DRC,那么就能编写属于自己物料清单(BOM)创建工具,这样就能更好地处理特定用户需求,如如何猎取本身不属于电路图数据库一部分器件“额外硬件”(如插座、散热装置或螺丝刀)。

或者设计人员可以编写属于自己网表分析器,该分析器在设计环境下第1页共3页。

PCB布线及设计规则检查

PCB布线及设计规则检查[提示]PCB中常见错误:(1)网络载入时报告NODE没有找到: a. 原理图中的元件使用了pcb库中没有的封装; b. 原理图中的元件使用了pcb库中名称不一致的封装; c. 原理图中的元件使用了pcb库中pin number不一致的封装。

如三极管:sch中pin number 为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上: a. 创建pcb库时没有在原点; b. 多次移动和旋转了元件,pcb板界外有隐藏的字符。

选择显示所有隐藏的字符,缩小pcb, 然后移动字符到边界内。

(3)DRC报告网络被分成几个部分:表示这个网络没有连通,看报告文件,使用选择CONNECTED COPPER查找。

另外提醒朋友尽量使用WIN2000, 减少蓝屏的机会;多几次导出文件,做成新的DDB文件,减少文件尺寸和PROTEL僵死的机会。

如果作较复杂的设计,尽量不要使用自动布线。

(4)在PCB设计中装入网络表后,提示很多错误,主要是关于封装的错误:这是由于在原理图设计时没有填写FOOtprint一栏。

应回到原理图中,主要是对于电阻、电容等分立元件重新填写这一栏,并且一定要生成新的网络表。

(5)在装入网络表时Action项提示Add nod-1 to NetN00001,Error项提示Component not found的错误:这是由于有的元件的Designator项未填写造成的。

只要在原理图中重新填写此项并重新生成网络表即可。

第九单元第1题样图9-01[操作要求]1、布线设计:●打开Unit9\Y9-01.pcb文件。

●加载Unit9\,用Protel的自动布线功能进行布线。

●设置自动布线线宽为12mil,双层板,Via直径为52mil,,Via Hole直径为28mil;Pad直径为62mil,Pad Hole直径为30mil;Top层垂直布线、BOTTOM层水平布线,最小安全间距为5mil。

PCB板检查项

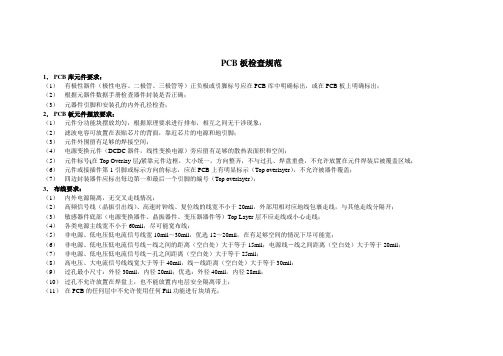

PCB板检查规范1.PCB库元件要求:(1)有极性器件(极性电容、二极管、三极管等)正负极或引脚标号应在PCB库中明确标出,或在PCB板上明确标出;(2)根据元器件数据手册检查器件封装是否正确;(3)元器件引脚和安装孔的内外孔径检查;2.PCB板元件摆放要求:(1)元件分功能块摆放均匀,根据原理要求进行排布,相互之间无干涉现象;(2)滤波电容可放置在表贴芯片的背面,靠近芯片的电源和地引脚;(3)元件外围留有足够的焊接空间;(4)电源变换元件(DCDC器件,线性变换电源)旁应留有足够的散热表面积和空间;(5)元件标号(在Top Overlay层)紧靠元件边框,大小统一,方向整齐,不与过孔、焊盘重叠,不允许放置在元件焊装后被覆盖区域;(6)元件或接插件第1引脚或标示方向的标志,应在PCB上有明显标示(Top overlayer),不允许被器件覆盖;(7)四边封装器件应标出每边第一和最后一个引脚的编号(Top overlayer);3.布线要求:(1)内外电源隔离,无交叉走线情况;(2)高频信号线(晶振引出线)、高速时钟线、复位线的线宽不小于20mil,外部用相对应地线包裹走线,与其他走线分隔开;(3)敏感器件底部(电源变换器件、晶振器件、变压器器件等)Top Layer层不应走线或小心走线;(4)各类电源主线宽不小于60mil,尽可能宽布线;(5)非电源、低电压低电流信号线宽10mil~30mil,优选12~20mil,在有足够空间的情况下尽可能宽;(6)非电源、低电压低电流信号线-线之间的距离(空白处)大于等于15mil;电源线-线之间距离(空白处)大于等于20mil;(7)非电源、低电压低电流信号线-孔之间距离(空白处)大于等于25mil;(8)高电压、大电流信号线线宽大于等于40mil,线-线距离(空白处)大于等于30mil;(9)过孔最小尺寸:外径30mil,内径20mil;优选:外径40mil,内径28mil;(10)过孔不允许放置在焊盘上,也不能放置内电层安全隔离带上;(11)在PCB的任何层中不允许使用任何Fill功能进行块填充;(12)走线采用135度拐角或弧线拐角,不允许有其他任何角度的拐角;(13)走线以90度直接连接到焊盘中心位置,与焊盘连接的线宽不允许超过焊盘大小;(14)布线完毕后做泪滴焊盘处理;(15)金属壳器件和模块外部的接地处理;(16)在PCB内电层不允许走信号线或进行任何填充,内电层不同区域之间的间隔宽度应不小于40mil;(17)在Toplayer和Bottom Layer层上需要铺设Polygen的,采用设置Grid Size:10mil,Track Width:10mil的参数设置,不允许留有死铜区域,并且要求与其他线路的间隔不小于30mils.;(18)“Power Plane Connect style rule”项设置:Conductor width: 20mils, Conductors: 4 , Expansion: 20mils, Gap: 10mil;(19)全面DRC检查通过;(20)布线完毕后放置元件焊接定位焊盘;4.边框处理(1)根据本组件的特殊要求,在PCB内电层的边框上(含外边框和板内工艺孔)添加安全区域,应不小于60mil,避免安装后通过组件外框短路;(2)检查外框大小是否符合标准;。

版图设计规则检查文件的自动生成工具的开题报告

版图设计规则检查文件的自动生成工具的开题报告一、选题的背景和意义在进行版图设计时,设计师需要遵循一定的规则和标准,以确保设计的可靠性和稳定性。

然而,在大多数情况下,这些规则和标准需要手动检查,这是一个繁琐的过程,很容易出现疏漏。

因此,自动化检查有助于减少人为漏洞,提高设计的质量和效率。

针对这个问题,本文拟开发一款自动生成版图设计规则检查文件的工具,其将自动分析版图设计,并生成检查文件,使设计师无需手动检查每一个细节,可以专注于解决一些更加复杂的问题,提高工作效率并减少错误。

二、需求分析本软件的主要功能要求如下:1.实现版图设计规则自动检查:针对常见的设计规则和标准,自动生成相应的检查文件,包括最小线宽和间隙、最小面积和间距等规则;2.提供可视化界面:为用户提供用户友好的界面,支持用户选择特定规则进行检查,并同时提供版本控制和历史记录的功能;3.实现信息关联:能够将检查结果与具体的设计元素关联,并允许设计师快速定位和解决问题;4.支持多种输出格式:可以将检查结果转换为多种格式,包括文本、Excel、PDF 等,以便于分享和展示;5.提供个性化设置:允许用户自定义检查规则和参数,以满足不同的设计要求。

三、研究方案本软件的核心技术包括版图分析和规则检查两个模块。

版图分析模块中,将使用python语言实现一个版图分析引擎。

该引擎将分析设计文件,提取关键信息,如线宽和间距,并将其保存到数据库中。

我们将在数据库中创建专门的数据表来存储版图数据。

通过这种方式,版图分析模块将为下一个模块提供必要的信息。

规则检查模块中,将定制一系列检查规则,并使用Python代码实现。

我们将从规则库中提取规则,这些规则是由PCB行业的专家根据行业标准和最佳实践确定的。

我们将使用规则生成引擎将规则与版图分析模块中保存的信息进行匹配,并输出检查结果。

我们将使用PyQT库开发可视化界面,以增加程序的易用性和可行性。

界面的设计将重点放在用户友好性、易于上手和操作效率上。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

您当前的位置:首页 > 应用 > EDA与PLD编写PCB设计规则检查器(DRC)的系统方法时间:2012-03-09 21:00:30 来源:作者:编写属于自己的PCB设计规则检查器具有很多优点,尽管设计检查器并不那么简单,但也并非高不可攀,因为任何熟悉现有编程或脚本语言的设计人员完全能够设计检查器,这项工作的好处是不可估量的,本文介绍编写PCB设计规则检查器的技巧。

本文阐述了一种编写PCB设计规则检查器(DRC)的系统方法。

利用电路图生成工具得到PCB设计后,即可运行DRC以找到任何违反设计规则的故障。

这些操作必须在后续处理开始之前完成,而且开发电路图生成工具的开发商必须提供大多数设计人员都能轻松掌握的DRC工具。

然而,市场销售的通用工具通常不具备足够的灵活性以满足特定的设计需要。

因此,客户必须将新特性需求反映给DRC工具开发商,而这通常需要耗费一定的资金和时间,尤其当需求不断更新时。

幸运的是,大多数工具开发商均可为客户提供编写属于自己的DRC 以满足特定需求的便捷方法。

但是,这种具有强大功能的工具尚未得到广泛认同或使用。

本文提供了利用DRC工具获取最大收益的实用指南。

由于DRC必须遍历PCB设计的整个电路图,包括每个符号、每个引脚、每个网路、每种属性,如有必要还能创建数目不限的“附属”文件。

如4.0节所述,DRC可以标示出任何违反设计规则的细微偏差。

例如其中一个附属文件就可能包含设计用到的全部去耦电容。

如果电容数低于或高于期望值,就将在可能出现电源线dv/dt问题的地方标注红色记号[1]。

这些附属文件或许必不可少,但并非任何商用DRC工具都一定能创建这些文件。

DRC的另一优势是便于更新,以适应新设计特性(如那些可能影响设计规则的新特性)的需要。

而且,一旦在该领域获得充分经验,那么还能实现许多其它功能。

例如,如果能编写属于自己的DRC,那么就能编写属于自己的物料清单(BOM)创建工具,这样就能更好地处理特定用户需求,如如何获取本身不属于电路图数据库一部分的器件“额外硬件”(如插座、散热装置或螺丝刀)。

或者设计人员可以编写属于自己的Verilog网表分析器,该分析器在设计环境下具有充分的灵活度,如怎样获取适用于特定器件的Verilog 模型或时间文件。

实际上,由于DRC遍历了整个设计电路图,因此可以收集全部有效信息以输出PCB设计Verilog网表分析所需的仿真和/或BOM。

在不提供任何程序代码的前提下讨论这些话题实在有些牵强,为此,我们将以一种电路图获取工具为例进行说明。

本文采用了Mentor Graphics公司开发的附属于PADS-Designer产品线的ViewDraw工具。

此外,我们还采用了ViewBase工具,这是一个可被调用并对ViewDraw数据库进行存取操作的简化C例行程序库。

利用ViewBase工具,设计人员可以轻松地采用C/C++语言为ViewDraw编写完整且高效的DRC工具[2] [3]。

需要注意的是,这里讨论的基本原则同样适用于任何其它的PCB电路图工具。

输入文件除了电路图数据库,DRC还需要一些可以描述特定情况处理的输入文件,如自动连接到电源平面的合法电源网路名称。

例如,如果电源网路名为POWER,那么电源平面将采用后端封装设备(如适用于ViewDraw的pcbfwd)自动连接到电源平面。

下面给出了输入文件列表,这些文件必须放在固定的全局位置,这样DRC就能自动找到并读取,然后在运行时将这些信息保存在DRC内部。

* 文件legal_pwr_net_name可选,该文件包含POWER信号全部合法网路名称,如VCC、V3_3P和VDD。

在PCB布局/路由工具中,需要对名称的大小写进行区分,一般VCC 并不等同于Vcc或vcc。

VCC可以是5.0V的电源,而V3_3P则可以是3.3V的电源。

* 文件legal_pwr_net_name可选,因为后端封装设备的配置文件通常必须包含一组合法电源线网路名称。

如果采用Cadence设计系统公司的Allegro布线工具,那么pcbfwd 的文件名则为allegro.cfg并且具有如下入口参数:接地:VSS CGND GND GROUND电源:VCC VDD VEE V3_3P V2_5P +5V +12V如果DRC可以直接读取allegro.cfg文件,而非legal_pwr_net_name,那么将能得到更好的结果(即引入误差的几率较小)。

电源线引脚通常并不外接到器件符号上,相反,该符号的一个属性(这里称为SIGNAL)描述了哪个引脚是电源引脚或接地引脚并描述引脚应当连接的网络名称。

SIGNAL = VCC:10SIGNAL = GROUND:20DRC可读取该属性并确保网路名称保存在legal_pwr_net_name文件中,如果legal_pwr_net_name中不包含网路名称,那么电源引脚将不会连接到电源平面,而这个问题确实非常严重。

一些符号必须具有外接电源线引脚,因为这些符号并不连接到常规电源线层。

例如,ECL器件的VCC引脚要么连接到VCC,要么连接到GROUND;其VEE引脚则可连接到GROUND或-5.0V平面。

此外,电源线引脚在到达电源线层之前也可连接到滤波器。

引脚与滤波器之间的网路可具有任意名称,而DRC很难检测到这一点。

DRC可以错误形式汇报这一点,而用户则必须将其标示出或在legal_pwr_net_name文件中添加该网路名称。

这就是我们需要类似legal_pwr_net_name文件的一个原因。

最后,DRC将读取legal_pwr_net_name,以1)找到上拉电阻,2)在设计中检查POWER网路名称的大小写,3)检测任何与POWER直接相连但尚未使用的引脚。

* 包含GROUND信号(如GROUND、VSS和F_GND)中所有合法网路名的legal_gnd_net_name文件可以随意创建。

而需要再次注意的是,符号的大小写可能会对一些PCB布线工具产生影响。

而且,如果DRC可以直接读取上述allegro.cfg文件,而非legal_gnd_net_name文件的话,无疑可以得到更好的设计结果。

legal_gnd_net_name不仅具有与legal_pwr_net_name相同的功能,而且DRC还可读取该文件,以1)找到下拉电阻,2)检查POWER网路名称的大小写,3)检测任何与POWER 直接相连但尚未使用的引脚。

* 包含全部合法符号库路径和名称的legal_lib_path_name文件可以随意创建,这一点非常重要。

例如,一个常见的严重错误是使用未授权程序库中的符号。

在PCB设计阶段,根据测试需要,通常要求创建临时器件符号并保存在本地符号库目录中。

最终用到的器件符号来源于此并将保存在联合或全局的程序库目录中,这些符号具有一些不同于本地器件符号的重要特征。

设计人员通常会因为没有采用共同符号取代本地符号而引入设计错误。

legal_lib_path_name可选,因为对于大多数电路图工具,程序库信息包含在启动工具所需的初始化文件中。

对于ViewDraw工具,该文件称为viewdraw.ini,当工具启动时,该文件就自动创建(利用脚本程序):目录[r]/corp_lib/pcb/symbol_libraries/viewdraw/fct (fct)。

Fct(快速CMOS技术)是ViewDraw众多子库中的一个,也是fct器件各符号的来源。

如果初始化文件存在,那么DRC不仅可以而且也应当直接读取该文件,因为设计人员可以及时地添加新程序库。

* 可以创建包含合法上拉电阻的legal_pullup_res文件以检测那些被终止以及未被使用的输入引脚。

通常,可以限定一组设计人员能使用的电阻,当然电阻值本身也是一个重要因素。

如果上拉了未使用的输入引脚,那么该电阻的阻值将为5K或更高。

* 可以创建包含合法下拉电阻的legal_pulldown_res文件以检测那些被终止以及未被使用的输入引脚。

如果下拉了未使用的输入引脚,那么阻值将会很小以阻止任何电流泄漏,从而使引脚电压高于触发阀值。

* 可以创建包含合法去耦电容的legal_decoup_cap文件,而且公司还可要求设计人员只使用特定的合格器件以满足电源线dv/dt要求。

* 可以创建一个包含器件符号全部属性的legal_comp_attr文件,如PART_NO、GEOM、REFDES和SIM_CLASS。

BOAM创建工具、Verilog网表分析器及其它工具都能使用这些属性。

* 可以创建一个包含器件符号全部引脚属性的legal_pin_attr文件,如PIN_NAME、PINTYPE和PIN_NO。

设计目录结构运行DRC必须满足的第二个条件就是需要可被所有PCB设计共享的单独设计目录结构。

没有该目录结构,DRC将难以确定如何找到电路图数据库并存储输出文件。

该架构可以极复杂的分层架构支持全部PCB设计业务,如设计规则检查、BOM创建、Verilog仿真、静态时序分析、信号完整性分析、布线、PAL/FPGA设计(综合与仿真)及文档控制。

但对于DRC本身,如果采用了ViewDraw,那么下述条件就完全充分:pcb_info应最少包含两个文件:design_def和design_type。

design_def应包含PCB器件(组合)数目及其它所需信息,这不仅仅对于DRC,对于其它所有工具也同样如此。

design_type应当包含设计类型信息,即PCB信息。

如果其它类型的设计(如ASIC或FPGA)可以共享该设计目录结构,那么design_type将指定该目录,这样设计自动化工具将能根据不同的设计类型进行适当的操作。

如果没有pcb_info 目录或该目录内容为空,这就意味着设计目录并非标准设计目录。

在这种情况下,DRC应当退出并发送出错信息。

Schem目录包含电路图数据库并可由DRC使用的ViewBase直接存取。

sch子目录包含了在图表上描述符号位置的电路图文件及其它信息,wir子目录则包含设计网表分析及全部符号属性。

ViewBase例程可直接存取这些内容。

drc目录应存储DRC输出文件。