PADK_-_Schematics

NuMicro N9H30系列开发板用户手册说明书

NuMicro®FamilyArm® ARM926EJ-S BasedNuMaker-HMI-N9H30User ManualEvaluation Board for NuMicro® N9H30 SeriesNUMAKER-HMI-N9H30 USER MANUALThe information described in this document is the exclusive intellectual property ofNuvoton Technology Corporation and shall not be reproduced without permission from Nuvoton.Nuvoton is providing this document only for reference purposes of NuMicro microcontroller andmicroprocessor based system design. Nuvoton assumes no responsibility for errors or omissions.All data and specifications are subject to change without notice.For additional information or questions, please contact: Nuvoton Technology Corporation.Table of Contents1OVERVIEW (5)1.1Features (7)1.1.1NuMaker-N9H30 Main Board Features (7)1.1.2NuDesign-TFT-LCD7 Extension Board Features (7)1.2Supporting Resources (8)2NUMAKER-HMI-N9H30 HARDWARE CONFIGURATION (9)2.1NuMaker-N9H30 Board - Front View (9)2.2NuMaker-N9H30 Board - Rear View (14)2.3NuDesign-TFT-LCD7 - Front View (20)2.4NuDesign-TFT-LCD7 - Rear View (21)2.5NuMaker-N9H30 and NuDesign-TFT-LCD7 PCB Placement (22)3NUMAKER-N9H30 AND NUDESIGN-TFT-LCD7 SCHEMATICS (24)3.1NuMaker-N9H30 - GPIO List Circuit (24)3.2NuMaker-N9H30 - System Block Circuit (25)3.3NuMaker-N9H30 - Power Circuit (26)3.4NuMaker-N9H30 - N9H30F61IEC Circuit (27)3.5NuMaker-N9H30 - Setting, ICE, RS-232_0, Key Circuit (28)NUMAKER-HMI-N9H30 USER MANUAL3.6NuMaker-N9H30 - Memory Circuit (29)3.7NuMaker-N9H30 - I2S, I2C_0, RS-485_6 Circuit (30)3.8NuMaker-N9H30 - RS-232_2 Circuit (31)3.9NuMaker-N9H30 - LCD Circuit (32)3.10NuMaker-N9H30 - CMOS Sensor, I2C_1, CAN_0 Circuit (33)3.11NuMaker-N9H30 - RMII_0_PF Circuit (34)3.12NuMaker-N9H30 - RMII_1_PE Circuit (35)3.13NuMaker-N9H30 - USB Circuit (36)3.14NuDesign-TFT-LCD7 - TFT-LCD7 Circuit (37)4REVISION HISTORY (38)List of FiguresFigure 1-1 Front View of NuMaker-HMI-N9H30 Evaluation Board (5)Figure 1-2 Rear View of NuMaker-HMI-N9H30 Evaluation Board (6)Figure 2-1 Front View of NuMaker-N9H30 Board (9)Figure 2-2 Rear View of NuMaker-N9H30 Board (14)Figure 2-3 Front View of NuDesign-TFT-LCD7 Board (20)Figure 2-4 Rear View of NuDesign-TFT-LCD7 Board (21)Figure 2-5 Front View of NuMaker-N9H30 PCB Placement (22)Figure 2-6 Rear View of NuMaker-N9H30 PCB Placement (22)Figure 2-7 Front View of NuDesign-TFT-LCD7 PCB Placement (23)Figure 2-8 Rear View of NuDesign-TFT-LCD7 PCB Placement (23)Figure 3-1 GPIO List Circuit (24)Figure 3-2 System Block Circuit (25)Figure 3-3 Power Circuit (26)Figure 3-4 N9H30F61IEC Circuit (27)Figure 3-5 Setting, ICE, RS-232_0, Key Circuit (28)Figure 3-6 Memory Circuit (29)Figure 3-7 I2S, I2C_0, RS-486_6 Circuit (30)Figure 3-8 RS-232_2 Circuit (31)Figure 3-9 LCD Circuit (32)NUMAKER-HMI-N9H30 USER MANUAL Figure 3-10 CMOS Sensor, I2C_1, CAN_0 Circuit (33)Figure 3-11 RMII_0_PF Circuit (34)Figure 3-12 RMII_1_PE Circuit (35)Figure 3-13 USB Circuit (36)Figure 3-14 TFT-LCD7 Circuit (37)List of TablesTable 2-1 LCD Panel Combination Connector (CON8) Pin Function (11)Table 2-2 Three Sets of Indication LED Functions (12)Table 2-3 Six Sets of User SW, Key Matrix Functions (12)Table 2-4 CMOS Sensor Connector (CON10) Function (13)Table 2-5 JTAG ICE Interface (J2) Function (14)Table 2-6 Expand Port (CON7) Function (16)Table 2-7 UART0 (J3) Function (16)Table 2-8 UART2 (J6) Function (16)Table 2-9 RS-485_6 (SW6~8) Function (17)Table 2-10 Power on Setting (SW4) Function (17)Table 2-11 Power on Setting (S2) Function (17)Table 2-12 Power on Setting (S3) Function (17)Table 2-13 Power on Setting (S4) Function (17)Table 2-14 Power on Setting (S5) Function (17)Table 2-15 Power on Setting (S7/S6) Function (18)Table 2-16 Power on Setting (S9/S8) Function (18)Table 2-17 CMOS Sensor Connector (CON9) Function (19)Table 2-18 CAN_0 (SW9~10) Function (19)NUMAKER-HMI-N9H30 USER MANUAL1 OVERVIEWThe NuMaker-HMI-N9H30 is an evaluation board for GUI application development. The NuMaker-HMI-N9H30 consists of two parts: a NuMaker-N9H30 main board and a NuDesign-TFT-LCD7 extensionboard. The NuMaker-HMI-N9H30 is designed for project evaluation, prototype development andvalidation with HMI (Human Machine Interface) function.The NuMaker-HMI-N9H30 integrates touchscreen display, voice input/output, rich serial port serviceand I/O interface, providing multiple external storage methods.The NuDesign-TFT-LCD7 can be plugged into the main board via the DIN_32x2 extension connector.The NuDesign-TFT-LCD7 includes one 7” LCD which the resolution is 800x480 with RGB-24bits andembedded the 4-wires resistive type touch panel.Figure 1-1 Front View of NuMaker-HMI-N9H30 Evaluation BoardNUMAKER-HMI-N9H30 USER MANUAL Figure 1-2 Rear View of NuMaker-HMI-N9H30 Evaluation Board1.1 Features1.1.1 NuMaker-N9H30 Main Board Features●N9H30F61IEC chip: LQFP216 pin MCP package with DDR (64 MB)●SPI Flash using W25Q256JVEQ (32 MB) booting with quad mode or storage memory●NAND Flash using W29N01HVSINA (128 MB) booting or storage memory●One Micro-SD/TF card slot served either as a SD memory card for data storage or SDIO(Wi-Fi) device●Two sets of COM ports:–One DB9 RS-232 port with UART_0 used 75C3232E transceiver chip can be servedfor function debug and system development.–One DB9 RS-232 port with UART_2 used 75C3232E transceiver chip for userapplication●22 GPIO expansion ports, including seven sets of UART functions●JTAG interface provided for software development●Microphone input and Earphone/Speaker output with 24-bit stereo audio codec(NAU88C22) for I2S interfaces●Six sets of user-configurable push button keys●Three sets of LEDs for status indication●Provides SN65HVD230 transceiver chip for CAN bus communication●Provides MAX3485 transceiver chip for RS-485 device connection●One buzzer device for program applicationNUMAKER-HMI-N9H30 USER MANUAL●Two sets of RJ45 ports with Ethernet 10/100 Mbps MAC used IP101GR PHY chip●USB_0 that can be used as Device/HOST and USB_1 that can be used as HOSTsupports pen drives, keyboards, mouse and printers●Provides over-voltage and over current protection used APL3211A chip●Retain RTC battery socket for CR2032 type and ADC0 detect battery voltage●System power could be supplied by DC-5V adaptor or USB VBUS1.1.2 NuDesign-TFT-LCD7 Extension Board Features●7” resolution 800x480 4-wire resistive touch panel for 24-bits RGB888 interface●DIN_32x2 extension connector1.2 Supporting ResourcesFor sample codes and introduction about NuMaker-N9H30, please refer to N9H30 BSP:https:///products/gui-solution/gui-platform/numaker-hmi-n9h30/?group=Software&tab=2Visit NuForum for further discussion about the NuMaker-HMI-N9H30:/viewforum.php?f=31 NUMAKER-HMI-N9H30 USER MANUALNUMAKER-HMI-N9H30 USER MANUAL2 NUMAKER-HMI-N9H30 HARDWARE CONFIGURATION2.1 NuMaker-N9H30 Board - Front View Combination Connector (CON8)6 set User SWs (K1~6)3set Indication LEDs (LED1~3)Power Supply Switch (SW_POWER1)Audio Codec(U10)Microphone(M1)NAND Flash(U9)RS-232 Transceiver(U6, U12)RS-485 Transceiver(U11)CAN Transceiver (U13)Figure 2-1 Front View of NuMaker-N9H30 BoardFigure 2-1 shows the main components and connectors from the front side of NuMaker-N9H30 board. The following lists components and connectors from the front view:NuMaker-N9H30 board and NuDesign-TFT-LCD7 board combination connector (CON8). This panel connector supports 4-/5-wire resistive touch or capacitance touch panel for 24-bits RGB888 interface.Connector GPIO pin of N9H30 FunctionCON8.1 - Power 3.3VCON8.2 - Power 3.3VCON8.3 GPD7 LCD_CSCON8.4 GPH3 LCD_BLENCON8.5 GPG9 LCD_DENCON8.7 GPG7 LCD_HSYNCCON8.8 GPG6 LCD_CLKCON8.9 GPD15 LCD_D23(R7)CON8.10 GPD14 LCD_D22(R6)CON8.11 GPD13 LCD_D21(R5)CON8.12 GPD12 LCD_D20(R4)CON8.13 GPD11 LCD_D19(R3)CON8.14 GPD10 LCD_D18(R2)CON8.15 GPD9 LCD_D17(R1)CON8.16 GPD8 LCD_D16(R0)CON8.17 GPA15 LCD_D15(G7)CON8.18 GPA14 LCD_D14(G6)CON8.19 GPA13 LCD_D13(G5)CON8.20 GPA12 LCD_D12(G4)CON8.21 GPA11 LCD_D11(G3)CON8.22 GPA10 LCD_D10(G2)CON8.23 GPA9 LCD_D9(G1) NUMAKER-HMI-N9H30 USER MANUALCON8.24 GPA8 LCD_D8(G0)CON8.25 GPA7 LCD_D7(B7)CON8.26 GPA6 LCD_D6(B6)CON8.27 GPA5 LCD_D5(B5)CON8.28 GPA4 LCD_D4(B4)CON8.29 GPA3 LCD_D3(B3)CON8.30 GPA2 LCD_D2(B2)CON8.31 GPA1 LCD_D1(B1)CON8.32 GPA0 LCD_D0(B0)CON8.33 - -CON8.34 - -CON8.35 - -CON8.36 - -CON8.37 GPB2 LCD_PWMCON8.39 - VSSCON8.40 - VSSCON8.41 ADC7 XPCON8.42 ADC3 VsenCON8.43 ADC6 XMCON8.44 ADC4 YMCON8.45 - -CON8.46 ADC5 YPCON8.47 - VSSCON8.48 - VSSCON8.49 GPG0 I2C0_CCON8.50 GPG1 I2C0_DCON8.51 GPG5 TOUCH_INTCON8.52 - -CON8.53 - -CON8.54 - -CON8.55 - -NUMAKER-HMI-N9H30 USER MANUAL CON8.56 - -CON8.57 - -CON8.58 - -CON8.59 - VSSCON8.60 - VSSCON8.61 - -CON8.62 - -CON8.63 - Power 5VCON8.64 - Power 5VTable 2-1 LCD Panel Combination Connector (CON8) Pin Function●Power supply switch (SW_POWER1): System will be powered on if the SW_POWER1button is pressed●Three sets of indication LEDs:LED Color DescriptionsLED1 Red The system power will beterminated and LED1 lightingwhen the input voltage exceeds5.7V or the current exceeds 2A.LED2 Green Power normal state.LED3 Green Controlled by GPH2 pin Table 2-2 Three Sets of Indication LED Functions●Six sets of user SW, Key Matrix for user definitionKey GPIO pin of N9H30 FunctionK1 GPF10 Row0 GPB4 Col0K2 GPF10 Row0 GPB5 Col1K3 GPE15 Row1 GPB4 Col0K4 GPE15 Row1 GPB5 Col1K5 GPE14 Row2 GPB4 Col0K6GPE14 Row2GPB5 Col1 Table 2-3 Six Sets of User SW, Key Matrix Functions●NAND Flash (128 MB) with Winbond W29N01HVS1NA (U9)●Microphone (M1): Through Nuvoton NAU88C22 chip sound input●Audio CODEC chip (U10): Nuvoton NAU88C22 chip connected to N9H30 using I2Sinterface–SW6/SW7/SW8: 1-2 short for RS-485_6 function and connected to 2P terminal (CON5and J5)–SW6/SW7/SW8: 2-3 short for I2S function and connected to NAU88C22 (U10).●CMOS Sensor connector (CON10, SW9~10)–SW9~10: 1-2 short for CAN_0 function and connected to 2P terminal (CON11)–SW9~10: 2-3 short for CMOS sensor function and connected to CMOS sensorconnector (CON10)Connector GPIO pin of N9H30 FunctionCON10.1 - VSSCON10.2 - VSSNUMAKER-HMI-N9H30 USER MANUALCON10.3 - Power 3.3VCON10.4 - Power 3.3VCON10.5 - -CON10.6 - -CON10.7 GPI4 S_PCLKCON10.8 GPI3 S_CLKCON10.9 GPI8 S_D0CON10.10 GPI9 S_D1CON10.11 GPI10 S_D2CON10.12 GPI11 S_D3CON10.13 GPI12 S_D4CON10.14 GPI13 S_D5CON10.15 GPI14 S_D6CON10.16 GPI15 S_D7CON10.17 GPI6 S_VSYNCCON10.18 GPI5 S_HSYNCCON10.19 GPI0 S_PWDNNUMAKER-HMI-N9H30 USER MANUAL CON10.20 GPI7 S_nRSTCON10.21 GPG2 I2C1_CCON10.22 GPG3 I2C1_DCON10.23 - VSSCON10.24 - VSSTable 2-4 CMOS Sensor Connector (CON10) FunctionNUMAKER-HMI-N9H30 USER MANUAL2.2NuMaker-N9H30 Board - Rear View5V In (CON1)RS-232 DB9 (CON2,CON6)Expand Port (CON7)Speaker Output (J4)Earphone Output (CON4)Buzzer (BZ1)System ResetSW (SW5)SPI Flash (U7,U8)JTAG ICE (J2)Power ProtectionIC (U1)N9H30F61IEC (U5)Micro SD Slot (CON3)RJ45 (CON12, CON13)USB1 HOST (CON15)USB0 Device/Host (CON14)CAN_0 Terminal (CON11)CMOS Sensor Connector (CON9)Power On Setting(SW4, S2~S9)RS-485_6 Terminal (CON5)RTC Battery(BT1)RMII PHY (U14,U16)Figure 2-2 Rear View of NuMaker-N9H30 BoardFigure 2-2 shows the main components and connectors from the rear side of NuMaker-N9H30 board. The following lists components and connectors from the rear view:● +5V In (CON1): Power adaptor 5V input ●JTAG ICE interface (J2) ConnectorGPIO pin of N9H30Function J2.1 - Power 3.3V J2.2 GPJ4 nTRST J2.3 GPJ2 TDI J2.4 GPJ1 TMS J2.5 GPJ0 TCK J2.6 - VSS J2.7 GPJ3 TD0 J2.8-RESETTable 2-5 JTAG ICE Interface (J2) Function●SPI Flash (32 MB) with Winbond W25Q256JVEQ (U7); only one (U7 or U8) SPI Flashcan be used●System Reset (SW5): System will be reset if the SW5 button is pressed●Buzzer (BZ1): Control by GPB3 pin of N9H30●Speaker output (J4): Through the NAU88C22 chip sound output●Earphone output (CON4): Through the NAU88C22 chip sound output●Expand port for user use (CON7):Connector GPIO pin of N9H30 FunctionCON7.1 - Power 3.3VCON7.2 - Power 3.3VCON7.3 GPE12 UART3_TXDCON7.4 GPH4 UART1_TXDCON7.5 GPE13 UART3_RXDCON7.6 GPH5 UART1_RXDCON7.7 GPB0 UART5_TXDCON7.8 GPH6 UART1_RTSCON7.9 GPB1 UART5_RXDCON7.10 GPH7 UART1_CTSCON7.11 GPI1 UART7_TXDNUMAKER-HMI-N9H30 USER MANUAL CON7.12 GPH8 UART4_TXDCON7.13 GPI2 UART7_RXDCON7.14 GPH9 UART4_RXDCON7.15 - -CON7.16 GPH10 UART4_RTSCON7.17 - -CON7.18 GPH11 UART4_CTSCON7.19 - VSSCON7.20 - VSSCON7.21 GPB12 UART10_TXDCON7.22 GPH12 UART8_TXDCON7.23 GPB13 UART10_RXDCON7.24 GPH13 UART8_RXDCON7.25 GPB14 UART10_RTSCON7.26 GPH14 UART8_RTSCON7.27 GPB15 UART10_CTSCON7.28 GPH15 UART8_CTSCON7.29 - Power 5VCON7.30 - Power 5VTable 2-6 Expand Port (CON7) Function●UART0 selection (CON2, J3):–RS-232_0 function and connected to DB9 female (CON2) for debug message output.–GPE0/GPE1 connected to 2P terminal (J3).Connector GPIO pin of N9H30 Function J3.1 GPE1 UART0_RXDJ3.2 GPE0 UART0_TXDTable 2-7 UART0 (J3) Function●UART2 selection (CON6, J6):–RS-232_2 function and connected to DB9 female (CON6) for debug message output –GPF11~14 connected to 4P terminal (J6)Connector GPIO pin of N9H30 Function J6.1 GPF11 UART2_TXDJ6.2 GPF12 UART2_RXDJ6.3 GPF13 UART2_RTSJ6.4 GPF14 UART2_CTSTable 2-8 UART2 (J6) Function●RS-485_6 selection (CON5, J5, SW6~8):–SW6~8: 1-2 short for RS-485_6 function and connected to 2P terminal (CON5 and J5) –SW6~8: 2-3 short for I2S function and connected to NAU88C22 (U10)Connector GPIO pin of N9H30 FunctionSW6:1-2 shortGPG11 RS-485_6_DISW6:2-3 short I2S_DOSW7:1-2 shortGPG12 RS-485_6_ROSW7:2-3 short I2S_DISW8:1-2 shortGPG13 RS-485_6_ENBSW8:2-3 short I2S_BCLKNUMAKER-HMI-N9H30 USER MANUALTable 2-9 RS-485_6 (SW6~8) FunctionPower on setting (SW4, S2~9).SW State FunctionSW4.2/SW4.1 ON/ON Boot from USB SW4.2/SW4.1 ON/OFF Boot from eMMC SW4.2/SW4.1 OFF/ON Boot from NAND Flash SW4.2/SW4.1 OFF/OFF Boot from SPI Flash Table 2-10 Power on Setting (SW4) FunctionSW State FunctionS2 Short System clock from 12MHzcrystalS2 Open System clock from UPLL output Table 2-11 Power on Setting (S2) FunctionSW State FunctionS3 Short Watchdog Timer OFFS3 Open Watchdog Timer ON Table 2-12 Power on Setting (S3) FunctionSW State FunctionS4 Short GPJ[4:0] used as GPIO pinS4Open GPJ[4:0] used as JTAG ICEinterfaceTable 2-13 Power on Setting (S4) FunctionSW State FunctionS5 Short UART0 debug message ONS5 Open UART0 debug message OFFTable 2-14 Power on Setting (S5) FunctionSW State FunctionS7/S6 Short/Short NAND Flash page size 2KBS7/S6 Short/Open NAND Flash page size 4KBS7/S6 Open/Short NAND Flash page size 8KBNUMAKER-HMI-N9H30 USER MANUALS7/S6 Open/Open IgnoreTable 2-15 Power on Setting (S7/S6) FunctionSW State FunctionS9/S8 Short/Short NAND Flash ECC type BCH T12S9/S8 Short/Open NAND Flash ECC type BCH T15S9/S8 Open/Short NAND Flash ECC type BCH T24S9/S8 Open/Open IgnoreTable 2-16 Power on Setting (S9/S8) FunctionCMOS Sensor connector (CON9, SW9~10)–SW9~10: 1-2 short for CAN_0 function and connected to 2P terminal (CON11).–SW9~10: 2-3 short for CMOS sensor function and connected to CMOS sensorconnector (CON9).Connector GPIO pin of N9H30 FunctionCON9.1 - VSSCON9.2 - VSSCON9.3 - Power 3.3VCON9.4 - Power 3.3V NUMAKER-HMI-N9H30 USER MANUALCON9.5 - -CON9.6 - -CON9.7 GPI4 S_PCLKCON9.8 GPI3 S_CLKCON9.9 GPI8 S_D0CON9.10 GPI9 S_D1CON9.11 GPI10 S_D2CON9.12 GPI11 S_D3CON9.13 GPI12 S_D4CON9.14 GPI13 S_D5CON9.15 GPI14 S_D6CON9.16 GPI15 S_D7CON9.17 GPI6 S_VSYNCCON9.18 GPI5 S_HSYNCCON9.19 GPI0 S_PWDNCON9.20 GPI7 S_nRSTCON9.21 GPG2 I2C1_CCON9.22 GPG3 I2C1_DCON9.23 - VSSCON9.24 - VSSTable 2-17 CMOS Sensor Connector (CON9) Function●CAN_0 Selection (CON11, SW9~10):–SW9~10: 1-2 short for CAN_0 function and connected to 2P terminal (CON11) –SW9~10: 2-3 short for CMOS sensor function and connected to CMOS sensor connector (CON9, CON10)SW GPIO pin of N9H30 FunctionSW9:1-2 shortGPI3 CAN_0_RXDSW9:2-3 short S_CLKSW10:1-2 shortGPI4 CAN_0_TXDSW10:2-3 short S_PCLKTable 2-18 CAN_0 (SW9~10) Function●USB0 Device/HOST Micro-AB connector (CON14), where CON14 pin4 ID=1 is Device,ID=0 is HOST●USB1 for USB HOST with Type-A connector (CON15)●RJ45_0 connector with LED indicator (CON12), RMII PHY with IP101GR (U14)●RJ45_1 connector with LED indicator (CON13), RMII PHY with IP101GR (U16)●Micro-SD/TF card slot (CON3)●SOC CPU: Nuvoton N9H30F61IEC (U5)●Battery power for RTC 3.3V powered (BT1, J1), can detect voltage by ADC0●RTC power has 3 sources:–Share with 3.3V I/O power–Battery socket for CR2032 (BT1)–External connector (J1)●Board version 2.1NUMAKER-HMI-N9H30 USER MANUAL2.3 NuDesign-TFT-LCD7 -Front ViewFigure 2-3 Front View of NuDesign-TFT-LCD7 BoardFigure 2-3 shows the main components and connectors from the Front side of NuDesign-TFT-LCD7board.7” resolution 800x480 4-W resistive touch panel for 24-bits RGB888 interface2.4 NuDesign-TFT-LCD7 -Rear ViewFigure 2-4 Rear View of NuDesign-TFT-LCD7 BoardFigure 2-4 shows the main components and connectors from the rear side of NuDesign-TFT-LCD7board.NuMaker-N9H30 and NuDesign-TFT-LCD7 combination connector (CON1).NUMAKER-HMI-N9H30 USER MANUAL 2.5 NuMaker-N9H30 and NuDesign-TFT-LCD7 PCB PlacementFigure 2-5 Front View of NuMaker-N9H30 PCB PlacementFigure 2-6 Rear View of NuMaker-N9H30 PCB PlacementNUMAKER-HMI-N9H30 USER MANUALFigure 2-7 Front View of NuDesign-TFT-LCD7 PCB PlacementFigure 2-8 Rear View of NuDesign-TFT-LCD7 PCB Placement3 NUMAKER-N9H30 AND NUDESIGN-TFT-LCD7 SCHEMATICS3.1 NuMaker-N9H30 - GPIO List CircuitFigure 3-1 shows the N9H30F61IEC GPIO list circuit.Figure 3-1 GPIO List Circuit NUMAKER-HMI-N9H30 USER MANUAL3.2 NuMaker-N9H30 - System Block CircuitFigure 3-2 shows the System Block Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-2 System Block Circuit3.3 NuMaker-N9H30 - Power CircuitFigure 3-3 shows the Power Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-3 Power Circuit3.4 NuMaker-N9H30 - N9H30F61IEC CircuitFigure 3-4 shows the N9H30F61IEC Circuit.Figure 3-4 N9H30F61IEC CircuitNUMAKER-HMI-N9H30 USER MANUAL3.5 NuMaker-N9H30 - Setting, ICE, RS-232_0, Key CircuitFigure 3-5 shows the Setting, ICE, RS-232_0, Key Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-5 Setting, ICE, RS-232_0, Key Circuit3.6 NuMaker-N9H30 - Memory CircuitFigure 3-6 shows the Memory Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-6 Memory Circuit3.7 NuMaker-N9H30 - I2S, I2C_0, RS-485_6 CircuitFigure 3-7 shows the I2S, I2C_0, RS-486_6 Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-7 I2S, I2C_0, RS-486_6 Circuit3.8 NuMaker-N9H30 - RS-232_2 CircuitFigure 3-8 shows the RS-232_2 Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-8 RS-232_2 Circuit3.9 NuMaker-N9H30 - LCD CircuitFigure 3-9 shows the LCD Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-9 LCD Circuit3.10 NuMaker-N9H30 - CMOS Sensor, I2C_1, CAN_0 CircuitFigure 3-10 shows the CMOS Sensor,I2C_1, CAN_0 Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-10 CMOS Sensor, I2C_1, CAN_0 Circuit3.11 NuMaker-N9H30 - RMII_0_PF CircuitFigure 3-11 shows the RMII_0_RF Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-11 RMII_0_PF Circuit3.12 NuMaker-N9H30 - RMII_1_PE CircuitFigure 3-12 shows the RMII_1_PE Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-12 RMII_1_PE Circuit3.13 NuMaker-N9H30 - USB CircuitFigure 3-13 shows the USB Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-13 USB Circuit3.14 NuDesign-TFT-LCD7 - TFT-LCD7 CircuitFigure 3-14 shows the TFT-LCD7 Circuit.Figure 3-14 TFT-LCD7 CircuitNUMAKER-HMI-N9H30 USER MANUAL4 REVISION HISTORYDate Revision Description2022.03.24 1.00 Initial version NUMAKER-HMI-N9H30 USER MANUALNUMAKER-HMI-N9H30 USER MANUALImportant NoticeNuvoton Products are neither intended nor warranted for usage in systems or equipment, anymalfunction or failure of which may cause loss of human life, bodily injury or severe propertydamage. Such applications are deemed, “Insecure Usage”.Insecure usage includes, but is not limited to: equipment for surgical implementation, atomicenergy control instruments, airplane or spaceship instruments, the control or operation ofdynamic, brake or safety systems designed for vehicular use, traffic signal instruments, all typesof safety devices, and other applications intended to support or sustain life.All Insecure Usage shall be made at customer’s risk, and in the event that third parties lay claimsto Nuvoton as a result of customer’s Insecure Usage, custome r shall indemnify the damagesand liabilities thus incurred by Nuvoton.。

Power layout guide

Mobile Power Department

六層板

Configuration II. 此方式有較佳之特性,因為在 Ground 及 Power 平面間有較好 之層間 decoupling。(四層佈線層) 第一層,component side,microstrip 信號佈線層 第二層,埋入之 microstrip 佈線層 第三層,Ground plane 第四層,Power plane 第五層,埋入之 microstrip 佈線層 第六層,solder side,microstrip 信號佈線層

Mobile Power Department

六層板

在六層板之應用上有以下三種常用之組態: Configuration I. 對 clock 信號及高頻元件,較常用之方式。(四層佈線層) 第一層,component side,microstrip 信號佈線層 第二層,Ground plane 第三層,Stripline 佈線層 第四層,Stripline 佈線層 第五層,Power plane 第六層,solder side,microstrip 信號佈線層

SI4 33 6 DY_ T1_ E3 SI4 33 6 DY_ T1_ E3 1

3MM_OPEN_5MIL

(17.5A)

1 L8300 1UH Irat=18A

1

JP8301 1

<G>

2

CE8 3 02 1 5 0U F/2 V PANASO NIC/EEFC D0 D1 5 1 ER 2 1

1 2

2

+1.8V

2

3MM_OPEN_5MIL

C8 3 1 3 0 .1 UF/2 5 V ML CC /+/-1 0 %

S32K3X4EVB-Q172 通用汽车应用开发板说明书

Belt-Driven Starter Generator (BSG), Turbo Charger, Fan/Pump ControllerHero SpecsS32K3 FAMILY FEATURESFS26 Safety System Basis Chip[+5 V, +3.3V and +1.5V]MCU Current Monitoring forVDD_HV_A and VDD_HV_B64Mb QSPI Serial NOR FlashMII/RMII Ethernet Interface— SABRE Connector10/100TBase Ethernet— RJ45 ConnectorTJA1043 CAN InterfacesTJA1021 LIN InterfacesMicrocontroller (MCU)32-bit Arm Cortex-M7-based S32K344 (/products/processors-and-microcontrollers/arm-microcontrollers/s32k-automotive-mcus/s32k3-microcoK26 (/products/processors-and-microcontrollers/arm-microcontrollers/general-purpose-mcus/k-series-cortex-m4/k2x-usb/kinetis-k26-180-mhz-Safety System Basis Chip (SBC)FS26 (/products/power-management/pmics-and-sbcs/safety-sbcs/safety-system-basis-chip-sbc-with-low-power-fit-for-asil-d:FS26): Safety syst Transceivers TJA1021 (/products/interfaces/automotive-lin-solutions/lin-2-1-sae-j2602-transceiver:TJA1021): LIN 2.1/SAE J2602 transceiverTJA1043 (/products/interfaces/can-transceivers/can-with-flexible-data-rate/high-speed-can-transceiver-with-standby-and-sleep-mode:TJA1043Hardware Features 64 Mb QSPI NOR flash100 Mbit Ethernet physical LayerPower supply switchMCU voltage/current measurementUser RGB LED2x user push-buttonsADC rotary potentiometer2x touch pad electrodeSoftware Features Free of charge S32 Design Studio IDE (/design/software/development-software/s32-design-studio-ide:S32-DESIGN-STUDIO-IDE) (Eclipse, GFree of charge (/design/automotive-software-and-tools/real-time-drivers-rtd:AUTOMOTIVE-RTD)Real Time Drivers for AUTOSAR and non-AUConfiguration tools for both AUTOSAR and non-AUTOSAR usersFree of charge security firmware: SHE+ compliant NXP supplied, designed for ISO 21434S32 Safety Software Framework (/design/automotive-software-and-tools/s32-safety-software-framework-saf:SAF) (SAF): Six fault detection anFree of charge Safety Peripheral Drivers (SPD)Structural Core Self Test (/docs/en/product-brief/S32K3xx-SCST-PB.pdf) (SCST)Free of charge inter-platform communication framework (/design/automotive-software-and-tools/inter-platform-communication-framework-ipcf:Free of charge Model-Based Design Toolbox (/design/automotive-software-and-tools/model-based-design-toolbox-mbdt:MBDT) for MATLAB :Programing Debug interfaces On-board S32K3 debug interface20-Pin Cortex debug + ETM connectorCompatibility Arduino UNO pint-out compatible with expansion “shield” supportInterfaces On-board HS-CAN2x on-board LINEthernet 100 Mbit Physical Layer with RJ-45 connector for fast prototypingSWD/JTAG debug interface for S32K3 debugger®®BuyS32K3X4EVB-Q172 (/part/S32K3X4EVB-Q172) S32K3X4EVB-Q172 Evaluation and Development Board for General Purpose(/design/automotive-(/design/software/development-(/design/software/development-Design ResourcesGet Started1. Review this Getting Started guide to get familiar with the hardware specifications.Getting StartedGetting Started with the S32K3X4EVB-Q172 Evaluation Board (/document/guide/getting-started-with-the-s32k3x4evb-q172-evaluation-board:GS-S32K3X4EVB-Q172)HTML Oct 6, 2021 GS-S32K3X4EVB-Q1722. Review this user manual to get familiar with the board.User ManualS32K3X4EVB-Q172 Evaluation Board – HW User Manual (/webapp/Download?colCode=S32K3X4EVB-Q172_HW-UM)PDF Rev A Oct 20, 2021 S32K3X4EVB-Q172_HW-UM EnglishDOCUMENTS ( 8 )DESIGN RESOURCES ( 4 )SOFTWARE ( 7 )Reference Manual ( 1 )User Guide ( 1 )Brochure ( 1 )Errata ( 1 )Product Brief ( 4 )Design Tools & Files ( 4 )Embedded Software ( 3 )Development Software ( 4 )DocumentsReference Manual ( 1 )S32K3X4EVB-Q172 Evaluation Board – HW User Manual (/webapp/Download?colCode=S32K3X4EVB-Q172_HW-UM)Hardware User Manual for the S32K3X4EVB-Q172 Evaluation Board.PDF Rev A Oct 20, 2021 S32K3X4EVB-Q172_HW-UM EnglishUser Guide ( 1 )Getting Started with the S32K3X4EVB-Q172 Evaluation Board (/document/guide/getting-started-with-the-s32k3x4evb-q172-evaluation-board:GS-S32K3X4EVB-Q172)This page will help guide you through the process of learning about your S32K3X4EVB-Q172 evaluation boardHTML Oct 6, 2021 GS-S32K3X4EVB-Q172 EnglishBrochure ( 1 )S32K3 Arm Cortex-M7-based Automotive MCUs – Brochure (/docs/en/brochure/S32KBRA4.pdf)The S32K3 family includes scalable 32-bit Arm Cortex-M7 based MCUs in single, dual and Lockstep core configurations supporting up to ASIL D level safety.Features include a hardware security subsystem with NXP firmware, support for firmware over-the-air (FOTA) updates, and ISO 26262 compliant Real-Time Drivers (RTD) software package for AUTOSARTM and non-AUTOSAR.PDF Rev 0 Oct 19, 2021 S32KBRA4 EnglishErrata ( 1 )Mask Set Errata for Mask 0P55A/1P55A - Errata (/webapp/Download?colCode=S32K3X4-0P55A-1P55A-ERRATA)This report applies to mask 0P55A/1P55A for these products S32K344, S32K324 and S32K314PDF Rev 14 Oct 14, 2021 S32K3X4-0P55A-1P55A-ERRATA EnglishProduct Brief ( 4 )S32 Safety Software Framework (SAF) for S32K3xx Microcontrollers - Product Brief (/docs/en/product-brief/S32K3xx-SAF-PB.pdf)The S32 Safety Software Framework (SAF) is a software product containing software components for establishing the safety foundation for customer’s safety applications compliant with ISO 26262 functional safety.PDF Rev 1 Sep 30, 2021 858.4 KB S32K3xx-SAF-PB EnglishStructural Core Self-Test Library (SCST) for S32K3xx Microcontrollers - Product Brief (/docs/en/product-brief/S32K3xx-SCST-PB.pdf)The SCST (Structural Core Self-Test) Library is the software product used for the runtime detection of permanent HW faults in the MCU core.PDF Rev 1 Oct 14, 2021 S32K3xx-SCST-PB EnglishReal-Time Drivers (RTD) for S32K3xx Microcontrollers – Product Brief (/docs/en/product-brief/RTD-S32K3-PB.pdf)S32-based platform products offer Real-Time Drivers (RTD) software supporting both AUTOSAR and non-AUTOSAR (similar to traditional SDKs) applications.PDF Rev 1.5 Nov 11, 2021 397.5 KB RTD-S32K3-PB EnglishInter-Platform Communication Framework (IPCF) - Product Brief (/docs/en/product-brief/IPCFPB.pdf)Inter-Platform Communication Framework (IPCF) is a subsystem which enables applications, running on multiple homogenous or heterogenous processing cores, located on the same chip or different chips, running on different operating systems (AUTOSAR, FreeRTOS etc.), to communicate over various transport interfaces (Shared Memory, etc.).PDF Rev 1 Oct 13, 2021 441.4 KB IPCFPB EnglishDesign ResourcesDesign Tools & Files ( 4 )Printed Circuit Boards and Schematics ( 3 )S32K3X4EVB-Q172 Evaluation Board – REV A Design Files (/webapp/Download?colCode=S32K3X4EVBQ172_CAD_FILES_REVA)Design Files REV A for the S32K3X4EVB-Q172 Evaluation Board.ZIP Rev A Oct 20, 2021 S32K3X4EVBQ172_CAD_FILES_REVAS32K3X4EVB-Q172 Evaluation Board – REV A Schematics (/webapp/Download?colCode=S32K3X4EVB-Q172_SCH)Schematics REV A for the S32K3X4EVB-Q257 Evaluation Board.PDF Rev A Oct 20, 2021 S32K3X4EVB-Q172_SCHDOWNLOAD (/WEBAPP/DOWNLOAD?COLCODE=S32K3X4EVBQ172_CAD_FILES_REVA)DOWNLOAD (/WEBAPP/DOWNLOAD?COLCODE=S32K3X4EVB-Q172_SCH)S32K3 MCUs for General Purpose – REV A Hardware Design Package (/webapp/Download?colCode=S32K3_HW-DesignPackage)Hardware considerations for the S32K3xx MCUs, covering power considerations, bulk/bypass and decoupling required capacitors, reset, crystal, Ethernet and QSPI configurations, and PCB layout recommendations.ZIP Rev A Sep 29, 2021 8.6 MB S32K3_HW-DesignPackageCalculators ( 1 )S32K Power Estimation Tool (PET) (/design/automotive-software-and-tools/s32k-power-estimation-tool-pet:S32K-PET)S32K PET provides a user interface to generate a power profile for an application use case quickly; it also helps calculate a first estimate of the average power consumption for developing automotive battery-operated applicationsDOWNLOAD OPTIONS (/DESIGN/AUTOMOTIVE-SOFTWARE-AND-TOOLS/S32K-POWER-ESTIMATION-TOOL-PET:S32K-PET?TAB=DESIGN_TOOLS_TAB)SoftwareEmbedded Software ( 3 )Embedded Software ( 3 )S32 Safety Software Framework (SAF) (/design/automotive-software-and-tools/s32-safety-software-framework-saf:SAF)The S32 Safety Software Framework (SAF) is a software product containing software components for establishing the safety foundation for customer’s safety applications compliant with ISO 26262 functional safety.DOWNLOAD OPTIONS (/DESIGN/AUTOMOTIVE-SOFTWARE-AND-TOOLS/S32-SAFETY-SOFTWARE-FRAMEWORK-SAF:SAF?TAB=DESIGN_TOOLS_TAB)Automotive Math and Motor Control Library (AMMCLib) (/design/automotive-software-and-tools/automotive-math-and-motor-control-library-ammclib:AMMCLIB)The Automotive Math and Motor Control Library (AMMCLib) set is a collection of production-ready, easy-to-use, software libraries for rapid development of motor control and other real-time embedded systems.DOWNLOAD OPTIONS (/DESIGN/AUTOMOTIVE-SOFTWARE-AND-TOOLS/AUTOMOTIVE-MATH-AND-MOTOR-CONTROL-LIBRARY-AMMCLIB:AMMCLIB?TAB=DESIGN_TOOLS_TAB)Model-Based Design Toolbox (MBDT) (/design/automotive-software-and-tools/model-based-design-toolbox-mbdt:MBDT)The NXP Model-Based Design Toolbox (MBDT) is a comprehensive collection of tools that plug into the MATLAB and Simulink model-based designenvironment to support fast prototyping, verification, and validationDOWNLOAD OPTIONS (/DESIGN/AUTOMOTIVE-SOFTWARE-AND-TOOLS/MODEL-BASED-DESIGN-TOOLBOX-MBDT:MBDT?TAB=DESIGN_TOOLS_TAB)Development Software ( 4 )IDE and Build Tools ( 2 )S32 Design Studio for S32 Platform (/design/software/development-software/s32-design-studio-ide/s32-design-studio-for-s32-platform:S32DS-S32PLATFORM)The S32 Design Studio is a tool suite for developing your applications for NXP Automotive and Ultra-Reliable MicrocontrollersDOWNLOAD OPTIONS (/DESIGN/SOFTWARE/DEVELOPMENT-SOFTWARE/S32-DESIGN-STUDIO-IDE/S32-DESIGN-STUDIO-FOR-S32-PLATFORM:S32DS-S32PLATFORM?TAB=DESIGN_TOOLS_TAB)S32K3 Standard Software (/webapp/swlicensing/sso/downloadSoftware.sp?catid=SW32K3-STDSW-D)S32K3 Standard Software includes Real Time Drivers for AUTOSAR® and non-AUTOSAR operating systems, Standard HSE Security firmware, SafetyPeripheral Drivers, an Inter-Platform Communication Framework (IPCF) for communications between the Cortex-M7 cores. Additionally user also get access to Real Time Driver of FS26 SBC, S32 Design Studio IDE and EB tresos Studio.EXTERNAL Rev 0 Sep 30, 2021 null KB SW32K3-STDSW-DDOWNLOAD (/WEBAPP/SWLICENSING/SSO/DOWNLOADSOFTWARE.SP?CATID=SW32K3-STDSW-D)Test, Debug and Analyzer Software ( 1 )FreeMASTER Run-Time Debugging Tool (/design/software/development-software/freemaster-run-time-debugging-tool:FREEMASTER)Graphical PC host tool to control and debug embedded applications in run-time.DOWNLOAD OPTIONS (/DESIGN/SOFTWARE/DEVELOPMENT-SOFTWARE/FREEMASTER-RUN-TIME-DEBUGGING-TOOL:FREEMASTER?TAB=DESIGN_TOOLS_TAB)Host Device Drivers ( 1 )Inter-Platform Communication Framework (IPCF) (/design/automotive-software-and-tools/inter-platform-communication-framework-ipcf:IPCF)DOWNLOAD (/WEBAPP/DOWNLOAD?COLCODE=S32K3_HW-DESIGNPACKAGE)Get HelpInter-Platform Communication Framework (IPCF) is a subsystem which enables applications, running on multiple homogenous or heterogenous processing cores, located on the same chip or different chips, running on different operating systems (AUTOSAR, FreeRTOS etc.), to communicate over various transport interfaces (Shared Memory, etc.).DOWNLOAD OPTIONS (/DESIGN/AUTOMOTIVE-SOFTWARE-AND-TOOLS/INTER-PLATFORM-COMMUNICATION-FRAMEWORK-IPCF:IPCF?TAB=DESIGN_TOOLS_TAB)RECOMMENDED COMMUNITIESS32K S32 Design Studio MBDT Community Articles FreeMASTERSUGGESTED LINKSFunctional Safety documents AVAILABLE | Require access to the SafeAssure NDA group(//)ABOUT NXP (///COMPANY/OUR-COMPANY/ABOUT-NXP:ABOUT-NXP)CAREERS (///ABOUT/CAREERS-AT-NXP:CAREERS)INVESTORS (///)MEDIA (//)CONTACT (///COMPANY/ABOUT-NXP/CONTACT-US:CONTACTUS)SUBSCRIBE (///SUBSCRIPTION-CENTER)(///NXP)(///company/nxp-semiconductors)(///NXPsemi)Privacy (///about/privacy:PRIVACYPRACTICES)Terms of Use (///about/terms-of-use:TERMSOFUSE)Terms of Sale (///about/our-standard-terms-and-conditions-of-sale-counter-offer:TERMSCONDITIONSSALE)Slavery and Human Trafficking Statement (///company/about-nxp/sustainability/social-responsibility/labor-and-human-rights:LABOR-AND-HUMAN-RIGHTS)Accessibility (///company/our-company/about-nxp/accessibility:ACCESSIBILITY)©2006-2022 NXP Semiconductors. All rights reserved.Search NXP Community SEARCH (HTTPS:///T5/FORUMS/SEARCHPAGE/TAB/MESSAGE?Q=) News Jan 4, 2022 | Read More (https:///news-releases/news-release-details/nxp-advances-iot-connectivity-industrys-first-secure-tri-radio)。

1_schematic

Cadence IC设计实验中国科技大学电子科学与技术系IC教研组黄鲁胡新伟白雪飞2005年10月(实验例题由Cadence 公司提供)致谢!电子科学技术系刘烃海、矫逸书、祝超、梅汪生等同学帮助编写了部分实验章节;信息实验中心屈玉贵主任和方毅、周远远、刘贵英等老师不仅为实验提供了技术支持,准备好EDA软件licence、配置了计算机和软件运行环境,而且热情参与了本实验教学。

对于上述老师和同学们的辛勤工作和所做出的贡献,在此一并表示衷心地感谢!预备知识:UNIX你掌握UNIX操作系统的基本命令吗?下面几条常用命令可能会对你有用处。

提醒一下,UNIX命令是区分大小写的。

查文件:ls (不显示隐含文件)、la (或ls –a,显示所有文件)、ls |mpre(帧显)、la |more删文件:rm 文件名建新目录:mkdir 目录名删目录:\rm –r目录名( 慎用!!!)拷贝:cp 源文件名(含路径)目标文件名(含路径),例将isc用户的abc.suf 文件拷贝到自己的当前目录下:cp ~isc/abc.suf .解.tar打包文件:tar vxf 打包文件名解.tar.Z压缩文件:tar vxfZ 压缩文件名文件改名: mv 原文件名新文件名查命令与参数功能:man 命令***************************************************************************规定:本实验教材中红色为键入命令或字符,兰色为菜单项,紫色为功能键;“单击”指鼠标左键按下一次。

****************************************************************************实验一、Virtuoso Schematic Editor实验目的:掌握电原理图(schematic)设计输入方法。

边学边做[1]启动IC Design 软件:开机后按lab_readme.txt的说明用你的用户名和密码登录至服务器cp /eva01/cdsmgr/ ICDATA/SchemEd.tar . (提醒:最后是个小点,稍等)tar vxf SchemEd.tarcd adelabic5icfb若出现“What’s New”窗口,关掉它。

Analog Devices ADRF5301 产品说明书

Data SheetADRF5301Silicon, SPDT Switch, 37 GHz to 49 GHz FEATURES►Reflective design►Low insertion loss: 1.4 dB typical►High isolation: 30 dB typical►High input linearity:►P0.1dB: 36 dBm►Input IP3: 52 dBm►High RF power handling►28 dBm average►36 dBm peak►Single-supply operation: 3.3V►Internal NVG►RF settling time (0.1 dB final RF output): 50 ns►20-terminal, 3 mm × 3 mm, land grid array (LGA) package APPLICATIONS►Industrial scanner►Test instrumentation►Cellular infrastructure mmWave 5G►Military radios, radars, electronic counter measures (ECMs)►Microwave radios and very small aperture terminals (VSATs)FUNCTIONAL BLOCK DIAGRAMFigure 1. Functional Block DiagramGENERAL DESCRIPTIONThe ADRF5301 is a reflective, SPDT switch manufactured in the silicon process.The ADRF5301 was developed for 5G applications from 37 GHz to 49 GHz. This device has a low insertion loss of 1.4 dB, high isolation of 30 dB, and RF input power handling capability of 28 dBm average and 36 dBm peak.The ADRF5301 incorporates a negative voltage generator (NVG) to operate with a single positive supply of 3.3 V applied to the VDD pin. The device employs complementary metal-oxide semiconduc-tor (CMOS)-/low voltage transistor to transistor logic (LVTTL)-com-patible control.The ADRF5301 comes in a 20-terminal, 3 mm × 3 mm, RoHS-com-pliant, land grid array package and can operate from −40°C to+105°C.TABLE OF CONTENTSFeatures (1)Applications (1)Functional Block Diagram (1)General Description (1)Specifications (3)Timing Specifications (3)Absolute Maximum Ratings (4)Thermal Resistance (4)Power Derating Curve (4)Electrostatic Discharge (ESD) Ratings (4)ESD Caution (4)Pin Configuration and Function Descriptions (5)Interface Schematics (5)Typical Performance Characteristics (6)Insertion Loss, Return Loss, and Isolation (6)Input Power Compression and Third-OrderIntercept (7)Theory of Operation (8)RF Input and Output (8)Power Supply (8)Timing Requirements (8)Applications Information (9)Recommendations for Printed Circuit BoardDesign (9)Outline Dimensions (10)Ordering Guide (10)Evaluation Boards (10)REVISION HISTORY10/2022—Revision 0: Initial VersionSPECIFICATIONSSupply voltage (V DD) = 3.3 V, CTRL voltage (V CTRL) = 0 V or V DD, T CASE = +25°C, 50 Ω system, unless otherwise noted.Table 1. Electrical CharacteristicsParameter Symbol Test Conditions/Comments Min Typ Max Unit FREQUENCY RANGE3749GHz INSERTION LOSSBetween RFC and RF1/RF2 1.4dB ISOLATIONBetween RFC and RF1/RF230dB Between RF1 and RF230dB RETURN LOSSRFC and RF1/RF2 (On)15dB SWITCHING CHARACTERISTICSRise and Fall Time t RISE, t FALL10% to 90% of RF output10ns On and Off Time t ON, t OFF50% V CTL to 90% of RF output45ns RF Settling Time0.1 dB50% V CTL to 0.1 dB of final RF output50ns0.05 dB50% V CTL to 0.05 dB of final RF output55ns INPUT LINEARITY f = 37 GHz to 40 GHz0.1 dB Power Compression P0.1dB36dBm Third-Order Intercept IP3Two-tone input power = 20 dBm per tone, Δf = 1 MHz52dBm SUPPLY CURRENT I DD450µA DIGITAL CONTROL INPUTS CTRL pinVoltageLow V INL00.8V High V INH 1.2 3.3V CurrentLow I INL<1μA High I INH14µA RECOMMENDED OPERATING CONDITONSSupply Voltage V DD 3.15 3.45V Digital Control Voltage V CTRL0V DD V RF Input Power1P IN f = 37 GHz to 40 GHz, T CASE = +85 °C2Average28dBm Peak100 ns pulse width, 2% duty cycle 36dBm Case Temperature T CASE−40+105°C1For power derating over frequency, see Figure 2.2For operation at +105°C, the power handling degrades from the T CASE = +85°C specification by 3 dB.TIMING SPECIFICATIONSSee Figure 13 for the timing diagram.Table 2. Timing SpecificationsParameter Description Min Typ Max Unitt POWERUP1Minimum wait time after power-up50μst HOLD Minimum control switching time40μst SLEW Maximum control rise and fall time10μs1 A maximum of 10 dBm RF input power can be applied during the t POWERUP wait time.ABSOLUTE MAXIMUM RATINGSFor recommended operating conditions, see Table 1.Table 3. Absolute Maximum RatingsParameter RatingSupply Voltage−0.3 V to +3.6 V Digital Control Input VoltageVoltage−0.3 V to VDD + 0.3 V Current 3 mARF Input Power (V DD = 3.3 V, f = 37 GHz to 40 GHz atT CASE = 85°C)Average28.5 dBmPeak36.5 dBmRF Input Power Under Unbiased Condition (V DD = 0 V)Average28 dBmPeak36 dBm TemperatureJunction (T J)135°CStorage−65°C to +150°C Reflow260°CStresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operat-ing conditions for extended periods may affect product reliability. THERMAL RESISTANCEThermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.θJC is the junction-to-case bottom (channel-to-package bottom) thermal resistance.Table 4. Thermal ResistancePackage TypeθJC1UnitCC-20-17, Through Path235°C/W1θJC was determined by simulation under the following conditions: the heat transfer is due solely to the thermal conduction from the channel through the ground pad to the PCB, and the ground pad is held constant at the operating temperature of +85°C.POWER DERATING CURVEFigure 2. Power Derating vs. Frequency, T CASE = +85°C ELECTROSTATIC DISCHARGE (ESD) RATINGSThe following ESD information is provided for handling of ESD-sen-sitive devices in an ESD protected area only.Human body model (HBM) ratings are per ANSI/ESDA/JEDECJS-001.Charged device model (CDM) ratings are per ANSI/ESDA/JEDEC JS-002.ESD Ratings for ADRF5301Table 5. ADRF5301, 20-Terminal LGAESD Model Withstand Threshold (V)HBM±500 for RF Pins±2000 for Supply and Digital Control Pins CDM±1250 for all PinsESD CAUTIONPIN CONFIGURATION AND FUNCTION DESCRIPTIONSFigure 3. Pin Configuration (Top View)Table 6. Pin Function Descriptions Pin No.Mnemonic Description1, 2, 4 to 7, 9 to 11, 13, 15 to 17, 19, 20GND Ground. These pins must be connected to the RF and DC ground of the PCB. See Figure 6 for the interface schematic.3RFCRF Common Port. This pin is DC-coupled to 0 V and AC matched to 50 Ω. No DC blocking capacitor is required when the RF line potential is equal to 0 V DC. See Figure 4 for the interface schematic.8RF1RF Throw Port 1. This pin is DC-coupled to 0 V and AC matched to 50 Ω. No DC blockingcapacitor is required when the RF line potential is equal to 0 V DC. See Figure 4 for the interface schematic.12VDD Positive Supply Voltage Input. See Figure 6 for the interface schematic.14CTRL Control Voltage Input. See Figure 5 for the interface schematic.18RF2RF Throw Port 2. This pin is DC-coupled to 0 V and AC matched to 50 Ω. No DC blockingcapacitor is required when the RF line potential is equal to 0 V DC. See Figure 4 for the interface schematic.EPADExposed Pad. The exposed pad must be connected to the RF and DC ground of the PCB.INTERFACE SCHEMATICSFigure 4. RFC, RF1, and RF2 Pins Interface SchematicFigure 5. CTRL Pin Interface SchematicFigure 6. VDD Pin and GND Pin Interface SchematicINSERTION LOSS, RETURN LOSS, AND ISOLATIONV DD = 3.3 V, V CTRL = 0 V or V DD , T CASE = 25°C, 50 Ω system, unless otherwise noted. Measured on the ADRF5301-EVALZevaluation board.Figure 7. Insertion Loss vs. FrequencyFigure 8. Return Loss vs. FrequencyFigure 9. Insertion Loss vs. Frequency Over TemperatureFigure 10. Isolation vs. FrequencyINPUT POWER COMPRESSION AND THIRD-ORDER INTERCEPTV DD = 3.3 V, V CTRL = 0 V or V DD, T CASE = 25°C, 50 Ω system, unless otherwise noted. All of the large signal performance parameters are measured on the ADRF5301-EVALZ evaluation board.Figure 11. Input P0.1dB vs. Frequency Figure 12. Input IP3 vs. FrequencyTHEORY OF OPERATIONThe ADRF5301 integrates a driver to perform logic functions inter-nally and to provide the user with the advantage of a simplified control interface. The driver features a single digital control input pin, CTRL, which controls the state of the RF paths. The logic level applied to the CTRL pin determines which RF port is in the insertion loss state while the other path is in the isolation state (see Table 7). RF INPUT AND OUTPUTAll of the RF ports (RFC, RF1, and RF2) are DC-coupled to 0 V, and no DC blocking is required at the RF ports when the RF line potential is equal to 0 V.The RF ports are internally matched to 50 Ω. Therefore, external matching networks are not required.The ADRF5301 is bidirectional with equal power handling capabili-ties. The RF input signal can be applied to the RFC port or the selected RF throw port.The insertion loss path conducts the RF signal between the select-ed RF throw port and the RF common port. The isolation paths provide high loss between the insertion loss path and the unselect-ed RF throw port that is reflective.POWER SUPPLYThe ADRF5301 integrates a negative voltage generator (NVG) and requires a single positive supply voltage applied to the VDD pin. Bypassing capacitors are recommended on the supply line to minimize RF coupling.The ideal power-up sequence is as follows:1.Connect GND reference.2.Power-up supply input VDD.3.Apply digital control input CTRL. Applying the CTRL controlbefore applying the VDD supply inadvertently forward biases and damages the internal ESD protection structures. To avoid this damage, use a series 1 kΩ resistor to limit the currentflowing into the control pin. Use pull-up or pull-down resistors if the controller output is in a high-impedance state after VDD is powered up and the control pins are not driven to a valid logic state.4.Apply RF input signal.The ideal power-down sequence is the reverse order of the power-up sequence.TIMING REQUIREMENTSThere are timing requirements for the proper operation of the bias and control circuits. See Table 2 for the timing specifications. See Figure 13 for the timing requirements.After VDD reaches the operating range, t POWERUP defines the wait time before the recommended maximum RF power can be applied. During this time, a maximum of 10 dBm RF input power can be applied.The minimum wait time before switching states is defined by t HOLD. The maximum rise and fall time of the CTRL pulse is defined byt SLEW.Figure 13. Timing RequirementsTable 7. Control Voltage Truth TableDigital Control Input RF PathsCTRL RF1 to RFC RF2 to RFC High Insertion loss (on)Isolation (off) Low Isolation (off)Insertion loss (on)APPLICATIONS INFORMATIONThe ADRF5301 has one power supply pin (VDD) and one con-trol pin (CTRL). Figure 14 shows the external components and connections for the supply pin. The VDD pin is decoupled with a 100pF multilayer ceramic capacitor. The device pin-out allows the placement of the decoupling capacitors close to the device.No other external components are needed for bias and operation,except DC blocking capacitors on the RF pins when the RF lines are biased at a voltage different than 0 V. See the Pin Configuration and Function Descriptionssection for details.Figure 14. Recommended SchematicRECOMMENDATIONS FOR PRINTED CIRCUIT BOARD DESIGNThe RF ports are matched to 50 Ω internally and the pinout isdesigned to mate a coplanar waveguide (CPWG) with 50 Ω charac-teristic impedance on the PCB. Figure 15 shows the referenced CPWG RF trace design for an RF substrate with 8 mil thick Rogers RO4003 dielectric material. RF trace with 14mil width and 7 milclearance is recommended for 2.2 mil finished copper thickness.Figure 15. Example PCB Stack-UpFigure 16 shows the routing of the RF traces, supply, and control signals from the device. The ground planes are connected with as many filled, through vias as allowed for optimal RF, and thermal performance. The primary thermal path for the device is the bottomside.Figure 16. PCB RoutingsFigure 17 shows the recommended layout from the device RF pins to the 50 Ω CPWG on the referenced stack-up. PCB pads are drawn 1:1 to device pads. The ground pads are drawn soldermask defined and the signal pads are drawn as pad defined. The RF trace from the PCB pad is extended with the same width by 2 mils and tapered to RF trace with a 45° angle. The paste mask is also designed to match the pad without any aperture reduction. Thepaste is divided into multiple openings for the paddle.Figure 17. Recommended RF Pin TransitionsFor alternate PCB stack-ups with different dielectric thickness and CPWG design, contact Analog Devices, Inc., Technical Support Request for further recommendations.OUTLINE DIMENSIONSFigure 18. 20-Terminal Land Grid Array [LGA]3 mm × 3 mm Body and 0.75 mm Package Height (CC-20-17)Dimensions Shown in MillimetersORDERING GUIDEModel1Temperature Range Package Description Package Option Marking Code ADRF5301BCCZN−40°C to +105°C20-Terminal Land Grid Array [LGA]CC-20-17S52ADRF5301BCCZN-RL−40°C to +105°C20-Terminal Land Grid Array [LGA]CC-20-17S52ADRF5301BCCZN-R7−40°C to +105°C20-Terminal Land Grid Array [LGA]CC-20-17S521Z = RoHS-Compliant Part.EVALUATION BOARDSTable 8. Evaluation BoardsModels1DescriptionADRF5301-EVALZ ADRF5301 Evaluation Board1Z = RoHS-Compliant Part.。

7370_schematics

Service SchematicsRM-70Exploded view and component disposalIMPORTANT:This document is intended for use by authorized NOKIA service centers only.Introduction“Service Schematics” was created with focus on customer care.The purpose of this document is to provide further technical repair information for NOKIA mobile phones on Level 3/4 service activities.It contains additional information such as e.g. “Component finder”,“Frequency band table” or “Antenna switch table”.The “Signal overview” page gives a good and fast overview about the most important signals and voltages on board.Saving process time and improving the repair quality is the aim of this document.It is to be used additionally to the service manual and other training or service information such as Service Bulletins.All measurements were made using following equipment:Nokia repair SW : Phoenix version 2005.20.7.98 Oscilloscope : Fluke PM 3380A/BSpectrum Analyzer : Advantest R3162 with an analog probe RF-Generator / GSM Tester : Rhode & Schwarz CMU 200Multimeter : Fluke 73 Series IIWhile every endeavour has been made to ensure the accuracy of this document, some errors may exist. If the reader finds any errors, NOKIA should be notified in writing. Please send E-Mail to: training.sace@ training.sace@Copyright © NOKIAThis material, including documentation and any related computer programs is protected by copyright, controlled by NOKIA. All rights are reserved. Copying, including reproducing, modifying, storing, adapting or translating any or all of this material requires the prior written consent of NOKIA. This material also contains companyconfidential information,which may not be disclosed to others without the prior written consent of NOKIA.7370NOKIAR2100GEN_OUT(3:0)CHARGERUSB_ACI(7:0)USB_CMT(8:0)CBUS(3:0)EMINT(1:0)PUSL(7:0)CHSWSTATSETCURR110nPCM(3:0)PUSL(7:0)AUDIO(8:0)FM_CMT(2:0)TXC_CONV(2:0)Customer Care / Service & Support Readiness / Content Creation Management Copyright © 2005 NOKIA Only for training and service purposes Version: 1.003.11.20057370 RM-70Board version: 1lua_50aPage 12(12)Component finder LCD PWB。

DB_PCap01Ax_0301_电容测试芯片

RMS 噪声和精度 vs. 输出数据频率.......................................................................................................... 2-3

2.2.2

RMS 噪声 vs. 供电电压............................................................................................................................... 2-5

1.2 典型应用

湿度传感器 位移传感器 压力传感器 力学传感器 加速度传感器 倾角传感器 角度传感器 无线应用 夜位开关传感器 麦克风 MEMS 传感器

acam-messelectronic gmbh - Am Hasenbiel 27 - D-76297 Stutensee-Blankenloch - Germany - www.acam.de

3 转换器前端

3.1 CDC 测量原理 3.2 重要 CDC 参数 3.3 CDC 外部电路 3.4 连接电容传感器 3.5 选择放电电阻 3.6 补偿测量

4.1 串行通信

4 接口 (串行通信和 Pulse-Density通信) 4.2 PDM/PWM 和 GPIO

5 读 & 写寄存器 6 DSP, 存储 & 固件

1-1

4

1.3 内部结构原理图

图 1-1: 内部结构原理图

PCapØ1Ax-0301

1-2

acam-messelectronic gmbh - Am Hasenbiel 27 - D-76297 Stutensee-Blankenloch - Germany - www.acam.de

caputer生成网表报错原因解析

(1)Warning "No_connect" #1 Warning [ALG0047] "No_connect" property on Pin "P1.8" ignored forP1: SCHEMATICS 13)URAT (7.90, 1.20). Connecting pin to n et "N16811229".&H)K]-hwM$k3D3pd-T$W7heALG0047这个警告基本可以忽略;造成这个问题的原因是,设计之初先对器件相关的管脚上加上'X'(也就是NC符号),更新设计的过程又对管脚做了连接处理;但是后面的连接处理没有去掉管脚的NC 属性,不信的话把那个管脚上的net删掉看看。

RG9f 解决办法很简单,对这些管脚再做一次NC(2)Warning Part Name #5 Warning [ALG0016] Part Name "CAP PN_C100UP-6.3V-SMT- S_100UF/6.3V" is ren amed to "CAPPN_C100UP-6.3V-SMT- S_100UF/"这个警告不可避免,allegro对相关的属性名称进行合并,超过一定数量的字符就截掉;在命名规范的前提下就不考虑这个警告了。

无法根治这个#2 Warnin g [ALG0016] Part Name ”?j#w?rm之类的错误在于你建立元件原理图的时候你的原件Value值太长了超过32个字符,从而使系统在进行命名规范的时候溢出,而出错,很简单的,只写关键元件名,比如A2541P10_HDR2X5-100MIL_2X5 HEADER" is ren amed to "A2541P10_HDR2X5-100MIL_2X5 HEA错误只需要把2X5 HEADER!改为A2541P10去除中间的空格即可二Allegro对一些字符[例如"空格","小数点"等等]很在意,可以参阅相关文档的描述.(3)Error Illegal character "Dot(.)" found in "PCB Footpri nt"#1 Error [ALG0081] Illegal character "Dot(J" found in "PCB Footpri nt" property for comp onent in sta nee C255: PG16_AC97, PG16_AC97 (226.06, 132.08).封装命名不能包含“.”(4)Error Illegal character "Forward Slash(/)" found in "PCB Footpri nt" property#1 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footpri nt" property for comp onent in sta nee C255: PG16_AC97,PG16_AC97 (226.06, 132.08).#2 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footpri nt" property for comp onent in sta nee D3:PG01_LED&Switch&7-Segme nt Disp, PG01_LED&Switch&7-Segme nt Disp (93.98, 33.02).#3 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footpri nt" property for comp onent in sta nee C245: PG16_AC97,PG16_AC97 (205.74, 35.56).封装命名不能包含“ /”(5)比较隐藏的排除法Loadi ng... E:\FPGA\SCH\allegro/pstchip.dat#34 WARNING(SPCODD-34Jxpected ';' character on line 5308.Check the name and value syntax for invalid characters in the primitive definition before the line number.ERROR(SPCODD-47): File ./allegro/pstchip.dat could not be loaded, and the packagi ng operati on did not complete. Check the pxl.log file for the errors caus ing this situati on and package the desig n aga in.*** Done******* #53 ERROR(SPCODD-53): Packaging cannot be completed because packaging has encountered a null object ID. The design may not have been saved correctly. Save the schematic and rerun packaging. #187 Error [ALG0036] Unable to read logical netlist data.Exiting... "D:\Cadence\SPB_16.2\tools\capture\pstswp.exe" - pst -d "E:\FPGA\SCH\motherboard.dsn" -n "E:\FPGA\SCH\allegro" -c"D:\Cadence\SPB_16.2\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"掌握排错方法,查找文件 pstchip.dat ,第 on line 5308 看看错 误,便可以解决 (6)封装命名中不能包含“小数点”、“ / ”、“空格”,把空格 换成下划线或删除,可以解决********************************************************************************** Netlisting the design*********************************************************** ********************** Design Name: E:\FPGA\SCH\basicboard.dsnNetlist Directory:E:\FPGA\SCH\allegroConfiguration File: D:\Cadence\SPB_16.2\tools\capture\allegro.cfg Spawning... "D:\Cadence\SPB_16.2\tools\capture\pstswp.exe" -pst -d "E:\FPGA\SCH\basicboard.dsn" -n"E:\FPGA\SCH\allegro" -c"D:\Cade nce\SPB_16.2\tools\capture\allegro.cfg" -v 3 -j"PCB Footpri nt"#1 Error [ALG0081] Illegal character "White space" fou nd in "PCB Footpr in t" property for comp onent in sta nee MG2: Basic, PG06_Stepmotor (180.34, 83.82).#2 Error [ALG0081] Illegal character "White space" fou nd in "PCBFootprint" property for component instance ISO1: Basic, PG05_DC Motor (134.62, 40.64).#3 Info: PCB Editor does not support Dots(.), Forward Slash(/) and White space in footpri nt n ames. The supported characters in clude Alphabets, Numerics, Un derscore(_) and Hyphe n(-).#4 Aborti ng Netlisti ng... Please correct the above errors and retry.Exiti ng... "D:\Cade nce\SPB_16.2\tools\capture\pstswp.exe"-pst -d "E:\FPGA\SCH\basicboard.dsn" -n"E:\FPGA\SCH\allegro" -c"D:\Cade nce\SPB_16.2\tools\capture\allegro.cfg" -v 3 -j"PCB Footpri nt"*** Done ***封装命名中不能包含“小数点”、“/”、“空格”,把空格换成下划线或删除,可以解决(7)Warning#11 Warning [ALG0051] Pin "GND" is renamed to "GND#A6" after substitut ing illegal characters in Package XC3S1400A- 4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGACONFIG (2.40,3.10) .moretha n#12 Warning [ALG0051] Pin "GND" is renamed to "GND#A11" aftersubstitut ing illegal characters in Package XC3S1400A- 4FG676-C_0FF , U1A: SCHEMATICS PG01_FPGACONFIG (2.40,3.10) .#13 Warning [ALG0051] Pin "GND" is renamed to "GND#A1" aftersubstitut ing illegal characters in Package XC3S1400A- 4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGACONFIG (2.40,3.10) .#14 Warni ng [ALG0051] Pin "GND" is ren amed to "GND#W8" after substitut ing illegal characters in Package XC3S1400A- 4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGACONFIG (2.40,3.10) .这条警告信息,在命名规范的前提下就不考虑这个警告了。

第一章 cadence ic5141教程schematic及其仿真

Open 菜单项打开相应的 Open File 窗口,如图 1-2-3 所示。 在 Library Name 中选择库名,在 Cell Names 中选择需要打开的单元名。Mode 项可以选 择打开方式——可编辑状态或者只读状态。

图 1-2-3 Open File 窗口 Exit 项退出 Cadence 软件包。 二.Tools 菜单 在 Tools 菜单下,主要的菜单项有 Library Manager、Library Path Editor 等。 Library Manager 项打开的是库管理器(Library Manager)窗口,如图 1-2-4 所示。

图 1-4-2 Save State 窗口 参数。如图 1-4-2 所示。窗口中的两项分别为状态名和选择需保存的内容。 Load State 打开相应的窗口,加载已经保存的状态。 Reset 重置 analog artist。相当于重新打开一个模拟窗口。 二.Setup 菜单 包括 Design、Simulator/directory/host、Temperature、Model Path 等菜单项: Design 项选择所要模拟的线路图。 Simulator/directory/host 项选择模拟使用的模型,系统提供的选项有 cdsSpice、hspiceS、 spectreS 等等。我们一般用到的是 cdsSpice 和 spectreS。其中采用 spectreS 进行的模拟更加 精确。下面我们只以这两种工具为例说明。 Temperature 打开如图 1-4-3 的窗口,可以设置模拟时的温度。

PmodBT2 蓝牙接口模块说明书

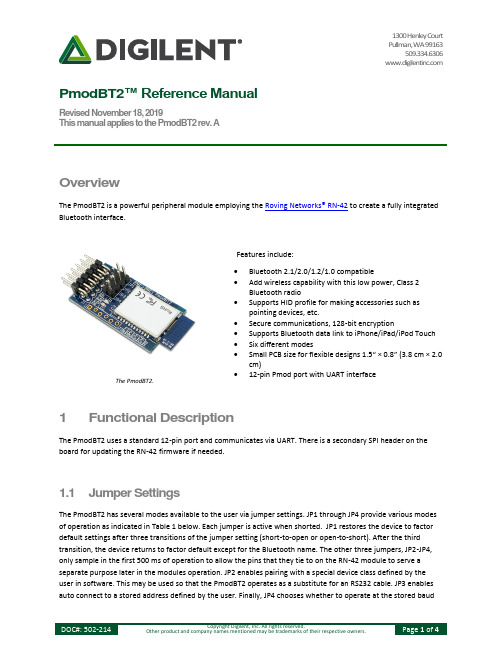

1300 Henley Court Pullman, WA 99163 509.334.6306PmodBT2™ Reference ManualRevised November 18, 2019This manual applies to the PmodBT2 rev. AOverviewThe PmodBT2 is a powerful peripheral module employing the Roving Networks® RN-42 to create a fully integrated Bluetooth interface.1 Functional DescriptionThe PmodBT2 uses a standard 12-pin port and communicates via UART. There is a secondary SPI header on the board for updating the RN-42 firmware if needed.1.1 Jumper SettingsThe PmodBT2 has several modes available to the user via jumper settings. JP1 through JP4 provide various modes of operation as indicated in Table 1 below. Each jumper is active when shorted. JP1 restores the device to factor default settings after three transitions of the jumper setting (short-to-open or open-to-short). After the third transition, the device returns to factor default except for the Bluetooth name. The other three jumpers, JP2-JP4, only sample in the first 500 ms of operation to allow the pins that they tie to on the RN-42 module to serve a separate purpose later in the modules operation. JP2 enables pairing with a special device class defined by the user in software. This may be used so that the PmodBT2 operates as a substitute for an RS232 cable. JP3 enables auto connect to a stored address defined by the user. Finally, JP4 chooses whether to operate at the stored baudThe PmodBT2. • Bluetooth 2.1/2.0/1.2/1.0 compatible • Add wireless capability with this low power, Class 2 Bluetooth radio • Supports HID profile for making accessories such as pointing devices, etc. • Secure communications, 128-bit encryption • Supports Bluetooth data link to iPhone/iPad/iPod Touch • Six different modes • Small PCB size for flexible designs 1.5“ × 0.8” (3.8 cm × 2.0 cm) • 12-pin Pmod port with UART interfaceFeatures include:rate (115.2kbps default) or a baud rate of 9600 regardless of the software selected rate when shorted. For more detailed information on jumper settings and functionality, refer to the RN-42 user manual.Jumper DescriptionJP1 (PIO4) Factory DefaultJP2 (PIO3) Auto Discovery/PairingJP3 (PIO6) Auto ConnectJP4 (PIO7) Baud Rate Setting (9600)Table 1. Set jumper description.Figure 1. PmodBT2 block diagram.1.2 UART InterfaceBy default, the UART interface uses a baud rate of 115.2 kbps, 8 data bits, no parity, and a single stop bit. The startup baud rate may be customized to predefined rates or set to a specific user customized baud rate. Predefined baud rates range from 1200 to 921k.The reset pin (RST) on J1 is active low. If the RST pin is toggled, the device will undergo a hard reset. This hard reset performs similarly to a power cycling of the device. The second interface besides the standard UART signals is the STATUS pin also on J1The STATUS pin directly reflects the connection status of the device. STATUS is driven high by the device when connected and is driven low otherwise.For more information on the devices UART interface and RST and STATUS pins refer to the RN-42 user manual on the Roving Networks website.1.3 Command ModeIn order to enter the command mode, the PmodBT2 must receive "$$$" to which it will respond "CMD". When in command mode, the module will respond to a large number of commands allowing the user to customizing the module for specific applications. In order to exit command mode, send "---<cr>" (three minus signs in a row and where <cr> stands for the carriage return character) to which the device will respond "END". Remote configuration, or configuration over a Bluetooth connection, is possible through the command mode but has several restrictions. The configure time, which defaults to 60 sec, defines the time window in which the PmodBT2 may be configured remotely. Outside of this time, the PmodBT2 will not respond to any remote commands. It is important to note that any of the "set" commands available for the PmodBT2 must be followed by a power cycle to take effect in any design.Connector J1 – UART CommunicationsPin Signal Description1 RTS Ready to Send2 RX Receive3 TX Transmit4 CTS Clear to Send5 GND Power Supply Ground6 VCC Power Supply (3.3V)7 STATUS Connection Status8 ~RST Reset9 NC Not Connected10 NC Not Connected11 GND Power Supply Ground12 VCC Power Supply (3.3V)Connector J2 – SPI Connector (Firmware Update Only)1 MISO Master in/ Slave out2 MOSI Master out/ Slave in3 SCK Serial Clock4 ~CS Chip Select5 VCC Power Supply (3.3V)6 GND Power Supply GroundTable 2. Connector descriptions.The various modes of operation are accessed by using the "SM,<5,4,3,2,1,0>" command while in command mode. The PmodBT2 can be put into one of six available modes of operation. The modes in order, 0 to 5, are: slave, master, trigger master, auto-connect, auto-connect DTR, and auto-connect ANY. For more detailed information onthe different modes of operation, refer to the RN-42 user manual. For the full list of device commands, how to use remote configuration, and more detailed information on the different modes of operation, see the RN-42 data.。

cdl文件转成schematic小结

本文主要是对最近学习的用ic5141将smic035网表转换原理图的总结。

下面是导入cdl的步骤:file-〉import-〉cdl 弹出CDL In界面。

具体解释如下:Parameter File:相当当于模板文件,就是对CDL In界面的各项参数的设置文件。

如果你是在GUI中运行CDL In,则Parameter File 可填可不填。

但是如果你是用命令行运行CDL In则需要指定一个特定的Parameter File。

Load 和Save即Load和Save前面的Parameter File。

CDL Netlist File:你想要import in的CDL文件。

Output Library:要存放schematic的library。

Top Cell:顶层的cell名称,可填可不填。

Reference Library List:列出一下参考链接库,如pdk所提供的库和一些基本的库。

可以填多个库。

Device-Map File:器件的映射转换文件,Device-Map File的格式是:devMap := <primitive_device_name> <mapped_device_name>[ propMatch := list_of_prop_to_match][ termMap :=list_of_terminals_to_map][ propMap :=list_of_properties_to_map][addProp := list_of_additional_properties_to_map] 注:“:=”前后都要有空格。

下面是一个二极管的device-mapdevMap := diode ndio50propMatch := subtype D5propMap := area area perim pjtermMap := PLUS PLUS MINUS MINUSaddProp := model ndio50其中diode是cdl中的管子类型,ndio50是pdk中对应的管子。

SCADA操作员界面硬件 - 第一部分:一般说明书

PART 1: GENERAL

1.01 SECTION INCLUDES

Operator Interface system to be supplied by Contractor. Actual SCADA programming

c. Provide one set of Wonderware SCADAlarm Windows-based autodialer software, or approved equal, for Operator Interface. Software shall be compatible with Wonderware SCADA software for callout on alarms. Autodialer shall have configurable unlimited phone callout list and alarm tagname dictionary, manual or automatic acknowledgment of alarms and provide audible annunciation of analog values. Autodialer software shall be Windows XP compatible. An external voice modem compatible with the software shall be provided for alarm dial-out. Provide microphone and connecting wires between modem and PC for the speaker input.

DLPT05-7-F数据线保护设备产品说明书

DLPT05-7-FFeatures• 300W Peak Pulse Power (tp = 8×20µs)• Transient Protection for Data Line to IEC61000-4-2 Level 4 (ESD), 8kV HBMContact: Discharge – ±30kV Air: Discharge – ±30kV • IEC 61000-4-4 (EFT) • Low Leakage Current• Surface Mount Package Ideally Suited for Automated Insertion • Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2) • Halogen and Antimony Free. “Green” Device (Note 3)Mechanical Data• Case: SOT-23• Case Material: Molded Plastic. UL Flammability Classification Rating 94V-0• Moisture Sensitivity: Level 1 per J-STD-020D• Terminals: Solderable per MIL-STD-202, Method 208• Lead Free Plating (Matte Tin Finish annealed over Alloy 42 Leadframe).• Terminal Connections: See Diagram • Marking Information: See Page 1 • Ordering Information: See Page 1 •Weight: 0.008 grams (Approximate)Ordering Information (Note 4)Part Number Case Packaging DLPT05-7-FSOT23 3000/Tape & ReelNotes:1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant2. See https:///quality/lead-free/ for more information about Diodes Incorporated’s definitions of Halogen- and Antimony-free, "Green" and Lead-free3. Halogen- and Antimony-free "Green” products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds4. For packaging details, go to our website at /datasheets/ap02007.pdf.Marking InformationDate Code KeyYear 1998 1999 2000 2001 … 2019 2020 2021 2022 Code J K L M … GH IJMonth Jan Feb Mar Apr May JunJul Aug Sep Oct Nov Dec Code123456789O NDNotes:5. Product manufactured with Data Code V9 (week 33, 2008) and newer are built with Green Molding Compound. Product manufactured prior to Date Code V9 are built with Non-Green Molding Compound and may contain Halogens or Sb 2O 3 Fire Retardants.Top ViewDevice SchematicCCBE PROTECTEDA01 = Product Type Marking Code YM = Date Code Marking Y = Year (ex: G = 2019)M = Month (ex: 9 = September)A01Y MMaximum Ratings @T A = 25°C unless otherwise specifiedThermal CharacteristicsElectrical Characteristics @T A = 25°C unless otherwise specifiedReverse Standoff Voltage Breakdown VoltageV BR @ I TTestCurrentMax. ReverseLeakage @ V RWM(Note 9)Max. ClampingVoltage @ I pp = 1A(Note 8)Typical PeakPulse Current(Note 7)Typical TotalCapacitance(Note 6)V RWM (V) Min (V)Max (V) I T (mA) I R (µA) V C (V) (A) (pF)5 6.0 1.0 20 9.8 17 1.9 Notes: 6. V R = 0V, f = 1MHz from line to be protected to ground pin.7. tp = 8×20µs.8. Clamping voltage value is based on an 8×20µs peak pulse current (I pp) waveform.9. Short duration pulse test used to minimize self-heating effect.10. Device mounted on FR-4 PCB pad layout (2oz copper) as shown on Diodes, Inc. suggested pad layout AP02001, which can be found on our website at.255075100125150175200T , AMBIENT TEMPERATURE (C)A °P E A K P U L S E D E R A T I N G I N % O F P E A K P O W E R O R C U R R E N TI , P E A K P U L S E C U R R E N T (%I )t, TIME (µs)Figure 2. Pulse WaveformC , T O T A L C A P A C I T A N C E (p F )T V REVERSE VOLTAGE (V)Fig. 3 Typical T otal Capacitance vs. Reverse Voltage R,P , P E A K P U L S E P O W E R (k W )D tp, PULSE WIDTH (µs)Fig. 4 Pulse Rating CurveNotes:11. Measured from line to be protected to ground pin.Typical Application SchematicsVccTransmission LineDriverRgFig. 1 Data Line T erminator VccFig. 2 Data Line ProtectionVccI/O Line 1I/O Line 2VccICPackage Outline DimensionsPlease see /package-outlines.html for the latest version.SOT23SOT23Dim Min Max Typ A 0.37 0.51 0.40 B 1.20 1.40 1.30 C 2.30 2.50 2.40 D 0.89 1.030.915 F 0.45 0.60 0.535 G 1.78 2.05 1.83 H 2.80 3.00 2.90 J 0.013 0.10 0.05 K 0.890 1.00 0.975 K1 0.903 1.101.025 L 0.45 0.61 0.55 L1 0.25 0.55 0.40 M 0.085 0.150 0.110 a 0° 8° -- All Dimensions in mmSuggested Pad LayoutPlease see /package-outlines.html for the latest version.SOT23DLPT05-7-F。

7 Schematic_entry

Schematic EntryZou ZhigeWinter, 2008Schematic Design•Cell Design Flow•Create A Design Library•Create CellSchematic EntryAuto Create Symbol View•Translate to NetlistZou Zhige WHICC2Zou Zhige WHICC 3電路設計Schematic Entry (composer)電路模擬Ckt Simulation(hspice)OK?電路佈局實作Physical Layout (layout editor)佈局驗証Verification(diva,dracula,hspice)是否OK?是否Cell LibraryDesignGuides/RulesCell Design FlowZou Zhige WHICC 4Library Path 可以設定在自己建的目錄下,但是也要配合自己帳號下的.cdsinit 檔設定Library 的Search Path 。

才能每次開啟icfb 時看到已建的Library 。

§每一個新的計畫在選定好technology 及對應的technology file 後,再opus 內open library ,即可將schematic, symbol, layout 等view 全建在固定的design library 內,而不會與其它計畫混淆。

§鍵入icfb& 就可以進入OPUS ,然後配合以下的圖例便可開啟一個Design Library 。

Create A Design Library(I)Zou Zhige WHICC 5注意Technology File 的位置改為/ee10-6/Librarys/Tech-file/cic06-9701.tf (TSMC 0.6um SPDM CMOS 的tech file)按下OK 後不久,在Library Browser 裡應該可找到新建的Library 及其default 內容。

GPS Click产品说明书

1. IntroductionGPS Click is an accessory board in mikroBus™ form factor. It’s a compact solution foradding GPS functionality to your device. It features LEA-6S, high performance u-blox 6 positioning engine. Board can be interfaced with a microcontroller through UART or I2C connection, or data can be acquired using PC application through USB connection. Board features connector compatible with active and passive antennas. It can operate on 3.3V power supply only.Once you have soldered the headers yourboard is ready to be placed into desiredmikroBUS™ socket. Make sure to align thecut in the lower-right part of the boardwith the markings on the silkscreen at themikroBUS™ socket. If all the pins are alignedcorrectly, push the board all the wayinto the socket.3. Plugging the board in232. Soldering the headers14. Features and applicationsGPS Click board with it’s LEA-6S modulefeatures acquisition down to 1s, –147dBmcoldstart sensitivity and 5Hz update rate.You can achive low power consumptiondue to intelligent, user configurable powermanagement. Mentioned features makethis board ideal for asset tracking, roadnavigation devices, public transportationvehicle infor m ation systems and more.Turn the board upward again. Make sureto align the headers so that they areperpendicular to the board, then solder thepins carefully.Turn the board upside down, so thatbottom side is facing you upwards. Placeshorter parts of the header pins in theboth soldering pad locations.GPS click Before using your click board, make sureto solder the provided 1x8 male headersto both sides of the board. Two 1x8 maleheaders are included with the board inthe package.clickBOARDGPS click Manualver. 1.008. SupportMikroElektronika offers Free Tech Support (/esupport) until the end of product lifetime, so if something goes wrong, we are ready and willing to help!7. Code Examples.comOnce you have done all the necessary preparations, it’s time to get your click board up and running. We have provided the examples for mikroC, mikroBasic and mikroPascal compilers on our Libstock website. Just download them and you are ready to start.5. GPS click Board SchematicsUSB_DP USB_DM SDA2SCL2TxD1RxD1SDA2SCL2TxD1RxD1TIMEPULSE DEVICE/OTG CONNECTOR12345678910111213141516171819202122232425262728SDA2SCL2TXD1RXD1RF_IN GND NC VCC GNDVCC_OUT CFG_COM1RESET V_BCKP Reserved GND GND GNDVCC_RF V_ANT AADENT0_NNC TIMEPULSE NC NC VDDUSBUSB_DM USB_DP EXTINT0GPS1LEA6SVCCAN RST CS SCK MOSI MISO +3.3V GNDPWM INT RX TX SCL SDA +5V GNDRESET_NR710VCC_RFVCCC2100nFR3220TIME PULSELED TIMEPULSE RF_INC12.2UFC32.2uF123IN GND OUT 54EN ADJ REG1AP7331-ADJR6180K R2300KR11K12345GND ID D+D-VBUS CN3USB MINIBR5220POWER LEDUSB_DM USB_DPD1BAT43VCCVDD_USBVDD_USBCN4ANTENNARESET_NMikroElektronika assumes no responsibility or liability for any errors or inaccuracies that may appear in the present document.Specification and information contained in the present schematic are subject to change at any time without notice. Copyright © 2012 MikroElektronika. All rights reserved.6. Power supply - 3.3V onlyBoard is designed to use 3.3V power supply only. If you need to add GPS feature to your 5V prototype ordevelopment board, we recommend you to use other boards such as the SmartGPS Accessory Board:/eng/products/view/122/smartgps-board/。

schematics 翻译

schematics 翻译schematics(多用复数形式)是指电气或电子设备的原理图或图纸。

它们用于表示电路的连线、元件的连接方式和工作原理,以便工程师或技术人员能够理解和设计电路。

schematics在工程领域中非常常见,尤其在电子电路设计和电路板布局方面起着重要作用。

通过阅读和理解schematics,工程师可以分析电路的功能、性能和工作原理,并进行必要的修改或优化。

以下是一些关于schematics的常见用法和中英文对照例句:1. 查看schematics(浏览原理图):- Please review the schematics to understand the circuit connections. (请查看原理图以了解电路的连接方式。

)- The schematics clearly show the component values and connections. (原理图清晰地显示了元件的数值和连接方式。

)2. 设计schematics(设计原理图):- The engineer is responsible for designing the schematics of the circuit. (工程师负责设计电路的原理图。

)- The software allows users to easily create and modify schematics. (该软件使用户能够轻松地创建和修改原理图。

)3. 修改schematics(修改原理图):- We need to revise the schematics to improve the circuit's performance. (我们需要修改原理图以提高电路的性能。

)- The technician made some changes to the schematics based on the test results. (技术人员根据测试结果对原理图进行了一些修改。

cadence入门

Cadence 系列软件从schematic到layout入门一.客户端软件使用及icfb启动要使用工作站上的软件,我们必须在PC中使用xwinpro等工具连接到工作站上。

从开始菜单中,运行xwinpro的xSettings,按照下图设置:点击上图的Settings在出现的窗口中按如下设置(connect host选择为192.168.1.137):设置完后,从开始菜单中运行xwinpro的xsessions,应该就可以进入登陆界面,用户名为user1,密码为root。

二、SchematicCadence系列软件包含了电路图工具Schematic,晶体管级电路仿真工具Spectre,以及版图工具Virtuoso等。

一般来说,我们先用Schematic画好电路原理图然后进行仿真,最后用Virtuoso手动画版图或者直接进行版图综合,最后对版图进行LVS,DRC等验证。

在登陆进工作站后,点击鼠标右键,选择tools——>terminal,在弹出的terminal窗口中敲入命令icfb&就可以启动cadence了。

图1 icfb的主界面我们以建立一个反相器电路为例子:在icfb中,任何一个电路,不论是已经存在的可以引用的库,还是用户新建立的一个电路,都是一个library. 一个library一般有若干个Cell(单元电路),每个cell有若干个schematic(电路原理)和若干个layout(版图)。

所以,我们要做的第一步,就是先创建一个自己的“库”,File菜单->new->library图2 新建一个库的界面从这个新建一个library的界面,我们必须输入新建立的库的名称,并且选择好这个库应该存放的目录,然后注意看右边的三个选项,关于新建立的库是否需要链接到Technology File 的问题。

首先,这个Technology File一般是指工艺库,由Foundry提供。

cadence版图使用说明

目录目录 (1)设计环境介绍 (2)工作站常用命令 (2)运行Cadence (6)运行Layout (10)运行schematic的编辑 (15)生成schematic symbol (18)运行Artist的仿真环境 (20)设计示例的简单介绍 (21)设计环境介绍典型的全定制Full-Custom模拟集成电路设计环境1. 集成的设计环境-Cadence Design Framework II是众多Cadence 工具集成在一起的统一的界面,通过这个架构,不用繁琐的数据格式转换,就可以方便的从一个工具转到另一个工具。

其中包括很多软件,如:原理图编辑工具-Composer布局编辑工具-Candence virtuoso布局验证编辑工具-Diva, Dracula2. 电路网表或原理图编辑环境-Text editor / schematic editor3. 电路模拟软件-spice操作系统环境和硬件平台1.SUN工作站;UNIX系统2.运行Linux的PC3.作为终端的PC工作站常用命令一、在terminal窗口键入的基本命令:1. ls:列出目录下所有文件。

2. clear:清除terminal窗口里的内容。

3. pwd:显示目前工作的目录。

4. cd:改变当前目录。

5. rm:刪除文件。

6. cp:复制文件。

7. mv:移动文件。

8. mkdir:建立目录。

9. rmdir:刪除目录。

10. find:寻找文件。

11. passwd:改变当前用户密码。

12. finger:显示当前用户信息。

二、基本操作和命令的使用介绍:1.从PC登录工作站,一般使用exeed或Xmanager。

login :___________(输入username)password:___________(输入密码)2.登出步骤:点击exit3.在线命令说明(以下的example% 表示系统的提示符)example% man [command-name]4. 改变当前目录example% cd [name]Example:example% cd dir1 改变目录位置,至dir1目录下。

经典—PCB设计(高级)试卷A

全国电子专业人才考试(PCB设计高级)试卷考试时间:60分钟姓名:______身份证号:_____________考试日期:____理论部分:一、单选题(共计30题,每题2分,共计60分)1.用于连接各层之间元器件引脚的金属孔称为【B 】。

A. 焊盘B. 过孔C. 安装孔D. 接插件2.下列关于地线设计的原则错误的描述是【B 】。

A. 数字地与模拟地分开B. 低频电路的地应尽量采用单点并联接地,实际布线有困难时可部分串联后再并联接地C. 高频电路宜采用多点串联接地,地线应短而粗,高频元件周围尽量用栅格状大面积地箔D. 接地线构成闭环路3.根据线路板电流的大小,尽量加大电源线宽度,减少环路电阻。

同时使电源线、地线的走向和数据传递的方向一致,这样有助于增强抗噪声能力【 A 】。

A. 对B. 错4.下列不属于电磁兼容性设计措施的是【C 】。

A. 屏蔽B. 密闭C. 接地D. 隔离5.对于传导干扰应采用【D】设计方法。

A. 屏蔽B. 接地C. 隔离D. 滤波6.解决信号完整性问题,最重要的方法是正确的布线,下列布线正确的是【】。

A. (a)(b)(c)B. (b)(c)C. (a)(b)D. (a)(c)7.关于SI解决措施中,下列做法错误的是【D】。

A. 一般在PCB设计中,我们要确保信号的回流路径最小,这样,所形成的电流环路越小,对外的辐射也就越小;B. 差分对可以很好的消除共模干扰,但是两条线必须尽可能靠近布线,长度完全一致;C. 退耦电容时要注意以下几点:电源引脚和地引脚与退耦电容之间的引线要尽量短而粗;D. 尽量避免直角走线。

8.负载电容的增大、负载电阻的增大、地电感的减小、开关器件数目的增加等因素都会导致地弹的增大【B】。

A. 对B. 错9.在PCB布局中不属于电气性能分区的是【D 】。

A. 数字电路区B. 模拟电路区C. 功率驱动区D. 电容电阻区10.原理图编辑系统内编辑出的文件后缀为【D 】。