Integrity-driven Power and Signal Network Codesign

SIGNALINTEGRITY(信号完整性)外文翻译

SIGNAL INTEGRITYRaymond Y. Chen, Sigrid, Inc., Santa Clara, CaliforniaIntroductionIn the realm of high-speed digital design, signal integrity has become a critical issue, and is posing increasing challenges to the design engineers. Many signal integr ity problems are electromagnetic phenomena in nature and hence related to the EMI/EMC discussions in the previous sections of this book. In this chapter, we will discuss what the typical signal integrity problems are, where they come from, why it is important to understand them and how we can analyze and solve these issues. Several software tools available at present for signal integrity analysis and current trends in this area will also be introduced.The term Signal Integrity (SI) addresses two concerns in the electrical design aspects – the timing and the quality of the signal. Does the signal reach its destination when it is supposed to? And also, when it gets there, is it in good condition? The goal of signal integrity analysis is to ensure reliable high-speed data transmission. In a digital system, a signal is transmitted from one component to another in the form of logic 1 or 0, which is actually at certain reference voltage levels. At the input gate of a receiver, voltage above the reference value Vih is considered as logic high, while voltage below the reference value Vil is considered as logic low. Figure 14-1 shows the ideal voltage waveform in the perfect logic world, whereas Figure 14-2 shows how signal will look like in a real system. More complex data, composed of a string of bit 1 and 0s, are actually continuous voltage waveforms. The receiving component needs to sample the waveform in order to obtain the binary encoded information. The data sampling process is usually triggered by the rising edge or the falling edge of a clock signal as shown in the Figure 14-3. It is clear from the diagram that the data must arrive at the receiving gate on time and settle down to a non-ambiguous logic state when the receiving component starts to latch in. Any delay of the data or distortion of the data waveform will result in a failure of the data transmission. Imagine if the signal waveform in Figure 14-2 exhibits excessive ringing into the logic gray zone while the sampling occurs, then the logic level cannot be reliably detected.SI ProblemsT ypical SI Problems“Timing” is everything in a high-speed system. Signal timing depends on the delay caused by the physical length that the signal must propagate. It also depends on the shape of the waveform w hen the threshold is reached. Signal waveform distortions can be caused by different mechanisms. But there are three mostly concerned noise problems:•Reflection Noise Due to impedance mismatch, stubs, visa and other interconnect discontinuities. •Crosstalk Noise Due to electromagnetic coupling between signal traces and visa.•Power/Ground Noise Due to parasitic of the power/ground delivery system during drivers’ simultaneous switching output (SSO). It is sometimes also called Ground Bounce, Delta-I Noise or Simultaneous Switching Noise (SSN).Besides these three kinds of SI problems, there is other Electromagnetic Compatibility or Electromagnetic Interference (EMC/EMI) problems that may contribute to the signal waveform distortions. When SI problems happen and the system noise margin requirements are not satisfied – the input to a switching receiver makes an inflection below Vih minimum or above Vil maximum; the input to a quiet receiver rises above V il maximum or falls below Vih minimum; power/ground voltage fluctuations disturb the data in the latch, then logic error, data drop, false switching, or even system failure may occur. These types of noise faults are extremely difficult to diagnose and solve after the system is built or prototyped. Understanding and solving these problems before they occur will eliminate having to deal with them further into the project cycle,and will in turn cut down the development cycle and reduce the cost[1]. In the later part of thischapter, we will have further investigations on the physical behavior of these noise phenomena, their causes, their electrical models for analysis and simulation, and the ways to avoid them.1. Where SI Problems HappenSince the signals travel through all kinds of interconnections inside a system, any electrical impact happening at the source end, along the path, or at the receiving end, will have great effects on the signal timing and quality. In a typical digital system environment, signals originating from the off-chip drivers on the die (the chip) go through c4 or wire-bond connections to the chip package. The chip package could be single chip carrier or multi-chip module (MCM). Through the solder bumps of the chip package, signals go to the Printed Circuit Board (PCB) level. At this level, typical packaging structures include daughter card, motherboard or backplane. Then signals continue to go to another system component, such as an ASIC (Application Specific Integrated Circuit) chip, a memory module or a termination block. The chip packages, printed circuit boards, as well as the cables and connecters, form the so-called different levels of electronic packaging systems, as illustrated in Figure 14-4. In each level of the packaging structure, there are typical interconnects, such as metal traces, visa, and power/ground planes, which form electrical paths to conduct the signals. It is the packaging interconnection that ultimately influences the signal integrity of a system.2. SI In Electronic PackagingTechnology trends toward higher speed and higher density devices have pushed the package performance to its limits. The clock rate of present personal computers is approaching gigahertz range. As signal rise-time becomes less than 200ps, the significant frequency content of digital signals extends up to at least 10 GHz. This necessitates the fabrication of interconnects and packages to be capable of supporting very fast varying and broadband signals without degrading signal integrity to unacceptable levels. While the chip design and fabrication technology have undergone a tremendous evolution: gate lengths, having scaled from 50 µm in the 1960s to 0.18 µm today, are projected to reach 0.1 µm in the next few years; on-chip clock frequency is doubling every 18 months; and the intrinsic delay of the gate is decreasing exponentially with time to a few tens of Pico-seconds. However, the package design has lagged considerably. With current technology, the package interconnection delay dominates the system timing budget and becomes the bottleneck of the high-speed system design. It is generally accepted today that package performance is one of the major limiting factors of the overall system performance.Advances in high performance sub-micron microprocessors, the arrival of gigabit networks, and the need for broadband Internet access, necessitate the development of high performance packaging structures for reliable high-speed data transmission inside every electronics system.Signal integrity is one of the most important factors to be considered when designing these packages (chip carriers and PCBs) and integrating these packages together.3、SI Analysis3.1. SI Analysis in the Design FlowSignal integrity is not a new phenomenon and it did not always matter in the early days of the digital era. But with the explosion of the information technology and the arrival of Internet age, people need to be connected all the time through various high-speed digital communication/computing systems. In this enormous market, signal integrity analysis will play a more and more critical role to guarantee the reliable system operation of these electronics products. Without pre-layout SI guidelines, prototypes may never leave the bench; without post-layout SI verifications, products may fail in the field. Figure 14-5 shows the role of SI analysis in the high-speed design process. From this chart, we will notice that SI analysis is applied throughout the design flow and tightly integrated into each design stage. It is also very common to categorize SI analysis into two main stages: reroute analysis and post route analysis.In the reroute stage, SI analysis can be used to select technology for I/Os, clock distributions, chip package types, component types, board stickups, pin assignments, net topologies, and termination strategies. With various design parameters considered, batch SI simulations on different corner cases will progressively formulate a set of optimized guidelines for physical designs of later stage. SI analysis at this stage is also called constraint driven SI design because the guidelines developed will be used as constraints for component placement and routing. The objective of constraint driven SI design at the reroute stage is to ensure that the signal integrity of the physical layout, which follows the placement/routing constraints for noise and timing budget, will not exceed the maximum allowable noise levels. Comprehensive and in-depth reroute SI analysis will cut down the redesign efforts and place/route iterations, and eventually reduce design cycle.With an initial physical layout, post route SI analysis verifies the correctness of the SI design guidelines and constraints. It checks SI violations in the current design, such as reflection noise, ringing, crosstalk and ground bounce. It may also uncover SI problems that are overlooked in the reroute stage, because post route analysis works with physical layout data rather than estimated data or models, therefore it should produce more accurate simulation results.When SI analysis is thoroughly implemented throughout the whole design process, a reliable high performance system can be achieved with fast turn-around.In the past, physical designs generated by layout engineers were merely mechanical drawings when very little or no signal integrity issues were concerned. While the trend of higher-speed electronics system design continues, system engineers, responsible for developing a hardware system, are getting involved in SI and most likely employ design guidelines and routing constraints from signal integrity perspectives. Often, they simply do not know the answers to some of the SI problems because most of their knowledge is from the engineers doing previous generations of products. To face this challenge, nowadays, a design team (see Figure 14-6) needs to have SI engineers who are specialized in working in this emerging technology field. When a new technology is under consideration, such as a new device family or a new fabrication process for chip packages or boards, SI engineers will carry out the electrical characterization of the technology from SI perspectives, and develop layout guideline by running SI modeling and simulation software [2]. These SI tools must be accurate enough to model individual interconnections such as visa, traces, and plane stickups. And they also must be very efficient so what-if analysis with alternative driver/load models and termination schemes can be easily performed. In the end, SI engineers will determine a set of design rules and pass them to the design engineers and layout engineers. Then, the design engineers, who are responsible for the overall system design, need to ensure the design rules are successfully employed. They may run some SI simulations on a few critical nets once the board is initially placed and routed. And they may run post-layout verifications as well. The SI analysis they carry out involves many nets. Therefore, the simulation must be fast, though it may not require the kind of accuracy that SI engineers are looking for. Once the layout engineers get the placement and routing rules specified in SI terms, they need to generate an optimized physical design based on these constraints. And they will provide the report on any SI violations in a routed system using SI tools. If any violations are spotted, layout engineers will work closely with design engineers and SI engineers to solve these possible SI problems.3.2.Principles of SI AnalysisA digital system can be examined at three levels of abstraction: log ic, circuit theory, and electromagnetic (EM) fields. The logic level, which is the highest level of those three, is where SI problems can be easily identified. EM fields, located at the lowest level of abstraction, comprise the foundation that the other levels are built upon [3]. Most of the SI problems are EM problems in nature, such as the cases of reflection, crosstalk and ground bounce. Therefore, understanding the physical behavior of SI problems from EM perspective will be very helpful. For instance, in the following multi-layer packaging structure shown in Figure 14-7, a switching current in via a will generate EM waves propagating away from that via in the radial direction between metal planes. The fields developed between metal planes will cause voltage variations between planes (voltage is the integration of the E-field). When the waves reach other visa, they will induce currents in those visa. And the induced currents in that visa will in turn generate EM waves propagating between the planes. When the waves reach the edges of the package, part of them will radiate into the air and part of them will get reflected back. When the waves bounce back and forth inside the packaging structure and superimpose to each other, resonance will occur. Wave propagation, reflection, coupling and resonance are the typical EM phenomena happening inside a packaging structure during signal transients. Even though EM full wave analysis is much more accurate than the circuit analysis in the modeling of packaging structures, currently, common approaches of interconnect modeling are based on circuit theory, and SI analysis is carried out with circuit simulators. This is because field analysis usually requires much more complicated algorithms and much larger computing resources than circuit analysis, and circuit analysis provides good SI solutions at low frequency as an electrostatic approximation.Typical circuit simulators, such as different flavors of SPICE, employ nodal analysis and solve voltages and currents in lumped circuit elements like resistors, capacitors and inductors. In SI analysis, an interconnect sometimes will be modeled as a lumped circuit element. For instance, a piece of trace on the printed circuit board can be simply modeled as a resistor for its finite conductivity. With this lumped circuit model, the voltages along both ends of the trace are assumed to change instantaneously and the travel time for the signal to propagate between the two ends is neglected. However, if the signal propagation time along the trace has to be considered, a distributed circuit model, such as a cascaded R-L-C network, will be adopted to model the trace. To determine whether the distributed circuit model is necessary, the rule of thumb is – if the signal rise time is comparable to the round-trip propagation time, you need to consider using the distributed circuit model.For example, a 3cm long stripling trace in a FR-4 material based printed circuit board will exhibits 200ps propagation delay. For a 33 MHz system, assuming the signal rise time to be 5ns, the trace delay may be safely ignored; however, with a system of 500 MHz and 300ps rise time, the 200ps propagation delay on the trace becomes important and a distributed circuit model has to be used to model the trace. Through this example, it is easy to see that in the high-speed design, with ever-decreasing signal rise time, distributed circuit model must be used in SI analysis.Here is another example. Considering a pair of solid power and ground planes in a printed circuit board with the dimension of 15cm by 15cm, it is very natural to think the planes acting as a large, perfect, lumped capacitor, from the circuit theory point of view. The capacitor model C= erA/d, an electro-static solution, assumes anywhere on the plane the voltages are the same and all the charges stored are available instantaneously anywhere along the plane. This is true at DC and low frequency. However, when the logics switch with a rise time of 300ps, drawing a large amount of transient currents from the power/ground planes, they perceive the power/ground structure as a two-dimensional distributed network with significant delays. Only some portion of the plane charges located within a small radius of the switching logics will be able to supply the demand. And voltages between the power/ground planes will have variations at different locations. In this case, an ideal lumped capacitor model is obviously not going to account for the propagation effects. Two-dimensional distributed R-L-C circuit networks must be used to model the power/ground pair.In summary, as the current high-speed design trend continues, fast rise time reveals the distributed nature of package interconnects. Distributed circuit models need to be adopted to simulate the propagation delay in SI analysis. However, at higher frequencies, even the distributed circuit modeling techniques are not good enough, full wave electromagnetic field analysis based on solving Maxwell’s equations must come to play. As presen ted in later discussions, a trace will not be modeled as a lumped resistor, or a R-L-C ladder; it will be analyzed based upon transmission line theory; and a power/ground plane pair will be treated as a parallel-plate wave guide using radial transmission line theory.Transmission line theory is one of the most useful concepts in today’s SI analysis. And it is a basic topic in many introductory EM textbooks. For more information on the selective reading materials, please refer to the Resource Center in Chapter 16.In the above discussion, it can be noticed that signal rise time is a very important quantity in SI issues. So a little more expanded discussion on rise time will be given in the next section.信号完整性介绍在高速数字设计领域,信号完整性已经成为一个严重的问题,是造成越来越多的挑战的设计工程师。

英语作文-探索集成电路设计的未来趋势与发展方向

英语作文-探索集成电路设计的未来趋势与发展方向Exploring the Future Trends and Development Directions of Integrated Circuit Design。

In recent years, the field of integrated circuit (IC) design has witnessed rapid advancements and breakthroughs. As the backbone of modern technology, ICs are essential components in various electronic devices, ranging from smartphones and computers to medical equipment and automotive systems. In this article, we will explore the future trends and development directions of IC design, focusing on three key aspects: miniaturization, power efficiency, and functional integration.First and foremost, miniaturization is a fundamental trend in IC design. Over the years, the size of ICs has continuously decreased, leading to the development of smaller and more powerful electronic devices. This trend is expected to continue in the future, with the demand for compact and portable devices on the rise. To achieve miniaturization, designers need to overcome various challenges, such as reducing power consumption, improving heat dissipation, and enhancing signal integrity. Advanced fabrication technologies, such as nanoscale lithography and 3D integration, will play a crucial role in enabling further miniaturization of ICs.Secondly, power efficiency is another important aspect of IC design. With the increasing demand for energy-saving devices and the growing concern for environmental sustainability, power efficiency has become a key consideration in IC design. Designers are constantly exploring new techniques to reduce power consumption without compromising performance. This includes the use of low-power design methodologies, such as voltage scaling, clock gating, and power gating, as well as the integration of power management circuits. Additionally, the development of energy harvesting technologies, such as solar cells and wireless charging, presents opportunities for further improving the power efficiency of ICs.Lastly, functional integration is a significant direction for the future of IC design. Traditionally, ICs were designed to perform specific functions, such as processing, memory, or communication. However, the increasing complexity of electronic systems demands higher levels of integration. Designers are now focusing on integrating multiple functions onto a single chip, leading to the development of system-on-chip (SoC) and system-in-package (SiP) solutions. This trend enables the creation of more versatile and compact devices, as well as the realization of emerging technologies like internet of things (IoT) and artificial intelligence (AI). To achieve functional integration, designers need to address challenges related to interconnectivity, power distribution, and thermal management.In conclusion, the future of IC design is characterized by miniaturization, power efficiency, and functional integration. These trends are driven by the demand for smaller, more energy-efficient, and multifunctional electronic devices. To stay at the forefront of IC design, designers need to embrace advanced fabrication technologies, explore innovative power-saving techniques, and focus on integrating multiple functions onto a single chip. By doing so, they can contribute to the development of cutting-edge technologies and shape the future of the electronics industry.。

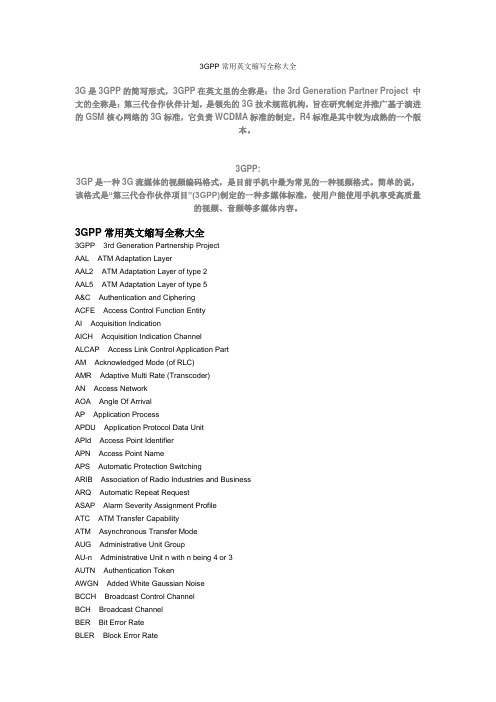

3GPP常用英文缩写全称大全

3GPP常用英文缩写全称大全3G是3GPP的简写形式,3GPP在英文里的全称是:the 3rd Generation Partner Project 中文的全称是:第三代合作伙伴计划,是领先的3G技术规范机构,旨在研究制定并推广基于演进的GSM核心网络的3G标准,它负责WCDMA标准的制定,R4标准是其中较为成熟的一个版本。

3GPP:3GP是一种3G流媒体的视频编码格式,是目前手机中最为常见的一种视频格式。

简单的说,该格式是“第三代合作伙伴项目”(3GPP)制定的一种多媒体标准,使用户能使用手机享受高质量的视频、音频等多媒体内容。

3GPP常用英文缩写全称大全3GPP 3rd Generation Partnership ProjectAAL ATM Adaptation LayerAAL2 ATM Adaptation Layer of type 2AAL5 ATM Adaptation Layer of type 5A&C Authentication and CipheringACFE Access Control Function EntityAI Acquisition IndicationAICH Acquisition Indication ChannelALCAP Access Link Control Application PartAM Acknowledged Mode (of RLC)AMR Adaptive Multi Rate (Transcoder)AN Access NetworkAOA Angle Of ArrivalAP Application ProcessAPDU Application Protocol Data UnitAPId Access Point IdentifierAPN Access Point NameAPS Automatic Protection SwitchingARIB Association of Radio Industries and BusinessARQ Automatic Repeat RequestASAP Alarm Severity Assignment ProfileATC ATM Transfer CapabilityATM Asynchronous Transfer ModeAUG Administrative Unit GroupAU-n Administrative Unit n with n being 4 or 3AUTN Authentication TokenAWGN Added White Gaussian NoiseBCCH Broadcast Control ChannelBCH Broadcast ChannelBER Bit Error RateBLER Block Error RateBMC Broadcast Multicast ControllerBPSK Binary Phase Shift KeyingBS Base StationBSC Base Station ControllerBSS Base Station SystemBTS Base Transceiver StationC- Control-CA Capacity AllocationCAA Capacity Allocation AcknowledgementCAC Connection Admission ControlCAMEL Customized Applications for Mobile network Enhanced Logic CAS Channel Associated SignallingCASC Current Alarm Summary ControlCBR Constant Bit RateCC Call ControlCCBS Call Completion Busy SubscriberCCCH Common Control ChannelCCH Control ChannelCCP Communication Control PortCCPCH Common Control Physical ChannelCCTrCH Coded Composite Transport ChannelCD Capacity Deallocation (radio context)CD Calibration Data (O&M context)CDA Capacity Deallocation AcknowledgementCDMA Code Division Multiple AccessCDR Charging Detail RecordCDV Cell Delay VariationCDVT Cell Delay Variation ToleranceCFN Connection Frame NumberCID Channel IdentifierCk Cipher KeyCLP Cell Loss PriorityCM Configuration ManagementCM Call Management (in e.g. CM Service Request)CmCH Common Transport ChannelCMIP Common Management Information ProtocolCMIS Common Management Information ServiceCMISE Common Management Information Service ElementCN Core NetworkC-n Container-n (n=1-4)COL Collocated EquipmentCP Chip PeriodCPCH Common Packet ChannelCPICH Common Pilot ChannelCPS Common Part SublayerCRC Cyclic Redundancy CheckCRCI CRC IndicatorCRC-N Cyclic Redundancy Check-NCRNC Controlling RNCc-RNTI RNTI allocated by CRNCCS Circuit SwitchedCSES Consecutive Severely Errored SecondCSN Ciphering Sequence NumberCSUM ChecksumCTCH Common Traffic ChannelCTDMA Code Time Division Multiple AccessCTP Connection Termination Point (OAM context)CTP Common Transport Protocol (Protocol context)DBR Deterministic Bit RateDC Dedicated Control (SAP)DCA Dynamic Channel AllocationDCCH Dedicated Control ChannelDCH Dedicated ChannelDCN Data Communication NetworkDL DownLinkDoCoMo Do Communication with MobilesDPCCH Dedicated Physical Control ChannelDPCH Dedicated Physical ChannelDPDCH Dedicated Physical Data ChannelDRAC Dynamic Resource Allocation ControlDRNC Drift RNCDRNS Drift RNSDRX Discontinuous ReceptionDS-CDMA Direct-Sequence Code Division Multiple Access DSCH Downlink Shared ChannelDT Data TransportDTCH Dedicated Traffic ChannelDTX Discontinuous TransmissionEBER Excessive Bit Error RatioECASC Extended Current Summary Alarm ControlEFCI Explicit Forward Congestion IndicationEFD Event Forwarding DiscriminatorEIR Equipment Identity RegisterEIRP Equivalent Isotropic Radiated PowerE-OTD Enhanced OTDES Errored SecondETSI European Telecommunication Standardisation Institute F8 access link encryption functionFACH Forward Access ChannelFAUSCH Fast Uplink Signalling ChannelFBI Feed Back IndicatorFCS Frame Check SequenceFDD Frequency Division DuplexFDMA Frequency Division Multiple AccessFEC Forward Error CorrectionFEEB Far End Errored BlockFEES Far End Errored SecondFER Frame Erasure RateFESES Far End Severely Errored SecondFFS For Further StudyFM Fault ManagementFP Frame ProtocolFTAM File Transfer Access ManagementFTP File Transfer ProtocolGb Gb interface (between SGSN and BSC)GC General Control (SAP)GCRA Generic Cell Rate AlgorithmGFR Guaranteed RateGGSN Gateway GPRS Serving NodeGMM MM for GPRS servicesGMSK Gaussian Minimum Shift KeyingG-PDU T-PDU plus GTP headerGPRS General Packet Radio ServiceGPRS-CSI GPRS CAMEL Subscription InformationGPS Global Positioning SystemGRNC Generic RNCGSM Global System for Mobile communicationsGTP GPRS Tunnelling ProtocolGTP-u GTP user planeHCS Hierarchical Cell StructureHE Home EnvironmentHEC Header Error ControlHFN Hyper Frame NumberHHO Hard HandoverHO HandoverHOP High Order PathHOVC Higher Order Virtual ContainerIBTS uplink Interference signal power level at Node B ICB Inter Carrier BoardICD Interface Control DocumentICH Indicator CHannelICI Inter Carrier InterfaceIE Information ElementIEC Incoming Error CountIETF Internet Engineering Task ForceIK Integrity KeyIMA Inverse Multiplexing for ATMIMEI International Mobile Equipment IdentityIMEISV International Mobile Equipment Identity Software VersionIMSI International Mobile Subscriber Identity (identical for IMUI; used in G SM context)IMUI International Mobile User Identity (identical to IMSI; seems to replace IMSI in UMTS context)INI Inter Network InterfaceIP Internet ProtocolISCP Interference Signal Code PowerISDN Integrated Services Digital NetworkISF Incoming Signal FailureIS-FL Idle Slot Forward LinkISID Idle Signal IdentificationISO International Organisation for StandardizationIT Information TechnologyITU International Telecommunication UnionIu Reference point between Access and Serving Network domainsIub Iub interface (between Node B and RNC)Iu-CS Iu towards the Circuit Switched-Service Domain of the Core NetworkIu-PS Iu towards the Packet Switched-Service Domain of the Core NetworkIur Iur interface (between RNC and RNC)IWF Inter Working FunctionIWU Inter Working UnitJD Joint DetectionKbps kilo-bits per secondKSI Key Set IdentifierKsps kilo-symbols per secondL1 Layer 1 (physical layer)L2 Layer 2 (data link layer)L3 Layer 3 (network layer)L3-CE Layer 3 Compression EntityLAC Link Access ControlLAI Location Area IdentityLAN Local Area NetworkLAPD Link Access Protocol for D-channelLB Laser BiasLCAF Location Client Authorisation FunctionLCCF Location Client Control FunctionLCCTF Location Client Coordinate Transformation FunctionLCD Loss of Cell Delineation (transmission context)LCD Low Constrained Delay (traffic context)LCF Location Client FunctionLCS Localisation Client ServiceLDD Low Delay DataLIR Limited IP Routing entity (in the RNC)LLC Link Layer ControlLMT Local Maintenance TerminalLNA Low Noise AmplifierLOF Loss of FrameLOP Low Order PathLOP Loss of PointerLOS Loss of SignalLPA Linear Power AmplifierLSA Localised Service AreaLSB Least Significant BitLSBF Location System Billing FunctionLSCF Location System Control FunctionLSN Local Sub NetworkLSPF Location Subscriber Privacy FunctionLT Laser TemperatureLTOA Latest Time of ArrivalMA Multiple AccessMAC Medium Access ControlMAC-c MAC entity handling common channels (RACH, FACH)MAC-d MAC entity handling dedicated channels (DCH)MAC-I Message Authentication Code used for data Integrity of signalling mess agesMAC-sh MAC entity handling shared channel (DSCH)MAHO Mobile Assisted HandoverMBS Maximum Burst SizeMCC Mobile Country CodeMCD Manual Configuration DataMcps Mega-chips per secondMD Macro-diversityME Mobile EquipmentMEHO Mobile evaluated handoverMIB Management Information BaseMM Mobility ManagementMNC Mobile Network CodeMNRG Mobile station Not Reachable for GPRS flagMNRR Mobile station Not Reachable ReasonMO Mobile OriginatedMOHO Mobile Originated HandoverMS Multiplex Section (transmission context)MS Mobile Station (GSM or security context)MS-AIS Multiplex Section Alarm Indication SignalMSB Most Significant BitMSC Multi-Slot Cell (MPSR context)MSC Mobile services Switching Centre (Core Network Context) MSID Mobile Station IdentifierMSOH Multiplex Section OverheadMSP Multiplex Section ProtectionMS-RDI Multiplex Section Remote Defect IndicationMS-REI Multiplex Section Remote Error IndicationMSTE Multiplex Section Terminating ElementMT Mobile Terminated (call context)MT Mobile Terminal (equipment context)MTP Message Transfer PartMUI Mobile User IdentifierNAS Non Access StratumNBAP Node B Application PartNCP Node B Control PortNCSES Number of Consecutive Severely Errored SecondNDF New Data FlagNE Network ElementNEHO Network evaluated handoverNEM Network Element ManagerNMC Network Management CentreNNI Network Node Interface (includes INI and ICI interfaces) NP Nectar PilotNPC Network Parameters ControlNRT Non-Real TimeNSS Network Sub SystemNT Nectar TelecomNt Notification (SAP)NW NetworkN-PDU Network PDUO&M Operation and MaintenanceOAM Operation Administration and MaintenanceOCCCH ODMA Common Control ChannelODCCH ODMA Dedicated Control ChannelODCH ODMA Dedicated ChannelODI Outgoing Defect IndicationODMA Opportunity Driven Multiple AccessODTCH ODMA Dedicated Traffic ChannelOEI Outgoing Error IndicationOFS Out of Frame SecondOMC Operation and Maintenance CentreOOF Out of FrameORACH ODMA Random Access ChannelOS Operation SystemOSF Offset FieldOSI Open System InterconnectionOSL Optical Signal LevelOTD Observed Time DifferenceOVSF Orthogonal Variable Spreading FactorPA Power AmplifierPC Power ControlPCCH Paging Control ChannelPCF Positioning Calculation FunctionPCH Paging ChannelPCM Pulse Code ModulationPCR Peak Cell RatePDCP Packet Data Convergence protocolPDH Plesiochronous Digital HierarchyPDN Packet Data NetworkPDP Packet Data ProtocolPDU Protocol Data UnitPG Processing GainPHY Physical layerPhyCH Physical ChannelPI Paging IndicatorPICH Page Indicator ChannelPID Packet IdentificationPJC Pointer Justification CountPJE Pointer Justification EventPkg PackagesPLM Payload MismatchPLMN Public Land Mobile NetworkPM Performance Management/Performance Monitoring PMM MM for PS domainPN Pseudo NoisePOH Path OverheadPPI Plesiochronous Physical InterfacePPM Parts Per MillionPRACH Physical Random Access ChannelPRCF Positioning Radio Co-ordination Function PS Packet SwitchedPSAP Presentation Service Access PointPSC Protection Switch CountPSD Protection Switch DurationPSMF Positioning Signal Measurement FunctionPSN Plane Switch NodePSTN Public Switched Telephone NetworkPTE Path Terminating ElementPVC Permanent Virtual ConnectionP-TMSI Packet TMSI (equivalent to P-TMUI, used in GPRS context)P-TMUI Packet TMUI –(equivalent to P-TMSI, new name for it in the UMTS context)PTR PointerPUF Power Up FunctionQE Quality EstimateQoS Quality of ServiceQPSK Quadrature Phase Shift KeyingRA Routing AreaRAB Radio Access BearerRAC Routing Area CodeRAC Radio Admission ControlRACH Random Access ChannelRAI Routing Area Identity (GPRS or Iu-PS context)RAI Remote Alarm Indication (transmission context)RAID Redundant Array of Independent DisksRAN Radio Access NetworkRANAP Radio Access Network Application PartRAND Random ChallengeRB Radio BearerRDI Remote Defect IndicationRDN Relative Distinguished NameREI Remote Error IndicationRF Radio FrequencyRFC Request For CommentRFN Reference Frame NumberRLC Radio Link ControlRLCP Radio Link Control ProtocolRLS Radio Link SetRLs Radio LinksRNC Radio Network ControllerRNCC Radio Network Connection ControlRNS Radio Network SubsystemRNSAP Radio Network Subsystem Application PartRNTI Radio Network Temporary IdentityRP Radio ProcessingRRC Radio Resource ControlRRM Radio Resource ManagementRS Regenerator sectionRSCP Received Signal Code Power after despreadingRSOH Regenerator Section OverheadRSSI Received Signal Strength IndicatorRT Real TimeRU Resource UnitRX ReceiveSAAL Signalling AAL (equivalent to SSCF over SSCOP over AAL5) SACCH Slow Associated Control ChannelSAP Service Access PointSBR Statistical Bit RateSC Service ControlSCCH Synchronization Control ChannelSCCP Signalling Connection Control PartSCD Selective Cell DiscardSCH Synchronization ChannelSCR Sustainable Cell RateSCTP Simple Control Transmission ProtocolSD Supervision Data (context configuration management)SD Signal Degrade (context SDH)SDCCH Stand-Alone Dedicated Control ChannelSDH Synchronous Digital HierarchySDU Service Data UnitSES Severely Errored SecondSF Signal Fail (transmission context)SF Spreading Factor (radio context)SFN System Frame NumberSG Study GroupSGSN Serving GPRS Support NodeSHO Soft Hand OverSIM Subscriber Information ModuleSIR Signal-to-Interference RatioSLM Signal Label MismatchSMS Short Message ServiceSN Serving NetworkSN Sequence NumberSNMP Simple Network Management ProtocolSOH Section OverheadSONET Synchronous Optical NetworkSP Switching PointSPA Signalling Point AccessibleSPI Signalling Point Inaccessible (SS7 context)SPI Synchronous Physical Interface (SDH context)SPROC System PROCessorSRNC Serving RNCSRNS Serving RNSs-RNTI RNTI allocated by SRNCSSA Signalling Subsystem AccessibleSSADT Service Specific Assured Data TransferSSCF Service Specific Coordination FunctionSSCOP Service Specific Connection-Oriented ProtocolSSP Signalling Subsystem ProhibitedSSSAR Service Specific Segmentation And ReassemblySSTED Service Specific Transmission Error DetectionSTF Start FieldSTM Synchronous Transport ModuleSTM(-N) Synchronous Transport Module (-N)STS(-N) Synchronous Transport Signal (-N)STTD Space Time Transmit DiversityTB Transport BlockTBC To Be ConfirmedTBD To Be DefinedTBF Transport Block FormatTBS Transport Block SetTCH Traffic ChannelTCM Tandem Connection MonitoringTCOH Tandem Connection OverheadTCP Transport Control ProtocolTCP Transport Control ProtocolTC-RDI Tandem Connection Remote Defect IndicationTC-REI Tandem Connection Remote Error IndicationTCT Tandem Connection TraceTCTE Tandem Connection Terminating ElementTDD Time Duplex DivisionTE Terminal EquipmentTEID Tunnel Endpoint IDTFCI Transport Format Combination IndicatorTFCS Transport Format Combination SetTFI Transport Format IndicatorTFS Transport Format SetTFT Traffic Flow TemplateTFTP Trivial File Transfer ProtocolTIM Trace Identifier MismatchTLLI Temporary Logical Link IdentifierTM Transparent Mode (of RLC)TMN Telecommunication Management NetworkTMSI Temporary Mobile Subscriber Identity (used in GSM context, equivalent t o TMUI)TMUI Temporary Mobile User Identity (new name for TMSI in the UMTS context) TN Termination NodeTOA or ToA Time Of ArrivalTOAWE TOA Window End pointTOAWS TOA Window Start pointTP Termination PointTPC Transmit Power ControlT-PDU Original packet, for example an IP datagram, from UE or an externa l PDNTR Threshold ResetTRX Transmitter/ReceiverTSID Test Signal IdentificationTSS Telecommunication Standardization SectorTTC Telecommunication Technology CommitteeTTI Time Transmission Interval (Radio Context)TTI Trail Trace Identifier (O&M context)TTP Trusted Third Party (security context)TTP Trail Termination Point (transmission context)TU Tributary UnitTUG Tributary Unit GroupTUG(-n) Tributary Unit Group (-n)TU-n Tributary Unit-nTX TransmitU- User-UARFCN UTRA Absolute Radio Frequency Channel NumberUAS Unavailable SecondUBR Unspecified Bit RateUDD Unconstrained Delay DataUDP User Datagram ProtocolUE User EquipmentUEA UMTS Encryption AlgorithmUEFN User Equipment Frame NumberUIA UMTS Integrity AlgorithmUL UpLinkUM Unacknowledged Mode (of RLC)UMTS Universal Mobile Telecommunication SystemUNEQ UnequippedUNI User to Network InterfaceUP User PlaneUPC Usage Parameters ControlURA User Registration AreaUSCH Uplink Shared CHannelUSIM UMTS Subscriber Identity ModuleUTRA UMTS Terrestrial Radio AccessUTRAN UMTS Terrestrial Radio Access NetworkUu Reference point between User Equipment and Infrastructure domains, UMTS radio interfaceUUI User to User IndicatorVA Voice Activity (factor)VBR Variable Bit RateVC Virtual ChannelVCC Virtual Channel ConnectionVCI Virtual Channel IdentifierVC-n Virtual Container n (n is 11, 12, 2, 3 or 4)VLR Visitor Location RegisterVP Virtual PathVPC Virtual Path ConnectionVPI Virtual Path IdentifierW-CDMA Wideband CDMAWG Working GroupWG-n Working Group (of 3GPP)WTR Wait-to-RestoreXMAC-I eXpected Message Authentication Code used for data Integrity of signa lling messagesXOR eXclusive ORXPU AuXiliary Processing UnitXRES Expected Response。

英语作文-集成电路设计师需要了解的基础知识与技术要点

英语作文-集成电路设计师需要了解的基础知识与技术要点Integrated Circuit (IC) Designers are professionals responsible for creating and developing the complex electronic circuits found in various electronic devices. To excel in this field, a deep understanding of fundamental knowledge and technical skills is essential. This article aims to provide an overview of the basic knowledge and technical points that IC Designers need to be familiar with.1. Solid Foundation in Electronics:IC Designers must have a solid foundation in electronics, including knowledge of electronic components, circuit theory, and digital logic. They should understand the behavior of different electronic components such as resistors, capacitors, and transistors, and be able to analyze and design basic electronic circuits.2. Semiconductor Physics:Understanding semiconductor physics is crucial for IC Designers. They should be familiar with concepts such as energy bands, carrier concentration, doping, and junctions. Additionally, knowledge of the different semiconductor materials, such as silicon and gallium arsenide, is necessary for designing efficient and reliable integrated circuits.3. Digital Design:IC Designers must have a strong grasp of digital design principles. This includes understanding Boolean algebra, logic gates, flip-flops, and sequential and combinational circuits. They should be able to design and optimize digital circuits using hardware description languages (HDLs) like Verilog or VHDL.4. Analog Design:Analog design is another essential skill for IC Designers. They should be knowledgeable about operational amplifiers, filters, oscillators, and analog-to-digital anddigital-to-analog converters. Proficiency in simulation tools like SPICE (Simulation Program with Integrated Circuit Emphasis) is necessary to analyze and verify the performance of analog circuits.5. Circuit Simulation and Analysis:IC Designers need to be proficient in using circuit simulation tools to verify the functionality and performance of their designs. They should be able to simulate circuits, analyze their behavior, and optimize their performance. Tools like Cadence Virtuoso, Synopsys HSPICE, and Mentor Graphics are commonly used for circuit simulation and analysis.6. Layout Design:Layout design involves the physical placement and routing of transistors, interconnects, and other components on an integrated circuit. IC Designers should be skilled in using layout design tools like Cadence Virtuoso Layout Editor or Mentor Graphics Calibre to create compact and efficient layouts that meet the design specifications and performance requirements.7. Design for Manufacturability (DFM):IC Designers should be aware of Design for Manufacturability principles to ensure that their designs can be manufactured reliably and cost-effectively. They need to consider factors such as process variations, yield optimization, and design rules compliance during the design phase.8. Low Power Design Techniques:With the increasing demand for portable and energy-efficient devices, IC Designers should be familiar with low power design techniques. This includes power management, clock gating, voltage scaling, and optimizing power consumption at both the circuit and system level.9. Signal Integrity and Timing Analysis:IC Designers need to ensure that their designs meet the required signal integrity and timing specifications. They should be skilled in performing signal integrity analysis to minimize noise, crosstalk, and reflections. Timing analysis is also crucial to ensure that the circuit operates within the desired timing constraints.10. Design Verification and Testing:IC Designers should have knowledge of design verification and testing techniques to ensure the correctness and reliability of their designs. This includes functional verification, test pattern generation, and fault simulation. They should be able to perform thorough testing to detect and fix any design flaws or defects.In conclusion, becoming a successful IC Designer requires a strong foundation in electronics, semiconductor physics, digital and analog design, circuit simulation, layout design, DFM, low power design, signal integrity, timing analysis, and design verification. By mastering these fundamental knowledge areas and technical skills, IC Designers can create innovative and efficient integrated circuits that power the ever-advancing world of technology.。

zbc埋入式电容的英文单词

zbc埋入式电容的英文单词The English word for "zbc埋入式电容" is "embedded capacitor".Embedded capacitors, also known as buried capacitors, are an essential component in modern electronic devices and circuits. They are designed to provide capacitance within the circuit board itself, eliminating the need for discrete capacitors. This integration not only saves space but also improves the overall performance and reliability of the electronic system.The concept of embedded capacitors involves incorporating a layer of dielectric material with a high dielectric constant into the printed circuit board (PCB) itself. This dielectric layer acts as a capacitor, capable of storing and releasing electrical energy. The dielectric material used in embedded capacitors is typically a high-performance polymer or ceramic with excellent electrical properties.One of the main advantages of embedded capacitors is their ability to minimize the parasitic inductance and resistance associated with discrete capacitors. In traditional PCB designs, the leads and traces connecting the capacitors introduce parasitic elements that can degrade the performance of the circuit. By integrating the capacitor directly into the PCB, these parasitic elements are significantly reduced, leading to improved signal integrity and faster response times.Embedded capacitors also offer enhanced thermal management capabilities. By distributing the capacitors throughout the PCB, heat generated during operation can be dissipated more efficiently. This reduces the risk of overheating and improves the overall reliability of the electronic device.Furthermore, the integration of capacitors into the PCB simplifies the assembly process and reduces manufacturing costs. The need for manual placement of discrete capacitors is eliminated, saving time and reducing the risk of human error. Additionally, the smaller form factor of embedded capacitors allows for higher-density circuit designs, further optimizing the use of available space on the PCB.The application of embedded capacitors is widespread across various industries, including telecommunications, automotive, aerospace, and consumer electronics. They are commonly used in power management circuits, high-frequency filters, decoupling networks, and signal conditioning circuits. The demand for embedded capacitors continues to grow as electronic devices become more compact and require higher performance levels.In conclusion, "zbc埋入式电容" translates to "embedded capacitor" in English. Embedded capacitors offer numerous benefits, including improved circuit performance, enhanced thermal management, reduced manufacturing costs, and increased design flexibility. As electronic devices continue to evolve, embedded capacitors play a crucial role in enabling smaller, more efficient, and reliable systems.。

英语作文-集成电路设计行业的智能化与数字化转型趋势

英语作文-集成电路设计行业的智能化与数字化转型趋势The semiconductor industry has been witnessing a remarkable transformation driven by the trends of intelligence and digitization. In particular, the field of integrated circuit (IC) design is experiencing a profound shift towards greater automation, intelligence, and digitalization. This transformation is not only reshaping the way ICs are designed but also revolutionizing the entire semiconductor ecosystem.One of the key drivers behind the trend of intelligence in IC design is the growing complexity of modern semiconductor devices. As technology nodes shrink and functionalities increase, traditional design methodologies are becoming inadequate to handle the intricacies involved. In response, design automation tools powered by artificial intelligence (AI) and machine learning (ML) algorithms are being increasingly deployed to streamline the design process. These tools can analyze vast amounts of data, identify patterns, and generate optimized designs with minimal human intervention. By leveraging AI and ML, designers can significantly reduce time-to-market and improve the overall quality and performance of ICs.Moreover, the digitization of IC design workflows is enabling greater collaboration and efficiency across the semiconductor industry. Cloud-based design platforms are becoming more prevalent, allowing geographically dispersed teams to collaborate seamlessly on design projects. This digital transformation also extends to simulation and verification, where advanced simulation tools and methodologies are being adopted to ensure the robustness and reliability of IC designs. Virtual prototyping, for instance, enables designers to simulate the behavior of complex ICs under various operating conditions, thereby reducing the need for physical prototypes and accelerating time-to-market.Furthermore, the integration of advanced manufacturing technologies such as 3D stacking and advanced packaging is driving the digitization of IC design. Thesetechnologies enable the integration of heterogeneous components within a single package, offering higher performance and greater energy efficiency. However, designing such complex systems requires sophisticated design tools capable of addressing multi-domain challenges, including thermal management, signal integrity, and power delivery. Digital twin technology, which creates a virtual replica of the physical system, is proving to be instrumental in optimizing the design of these integrated systems.In addition to enhancing design efficiency and productivity, the trend towards intelligence and digitization in IC design is also enabling new opportunities for innovation. For instance, the rise of edge computing and Internet of Things (IoT) devices is driving demand for ultra-low-power and high-performance ICs tailored for specific applications. Designers are leveraging AI-driven optimization techniques to design energy-efficient circuits capable of meeting stringent performance requirements. Similarly, the emergence of neuromorphic computing and quantum computing is pushing the boundaries of traditional IC design, necessitating new design methodologies and tools.In conclusion, the integration of intelligence and digitization is reshaping the landscape of IC design, driving greater efficiency, collaboration, and innovation. As the semiconductor industry continues to evolve, embracing these trends will be crucial for staying competitive in a rapidly changing market landscape. By leveraging advanced technologies and methodologies, IC designers can unlock new possibilities and accelerate the pace of innovation in semiconductor design.。

Signalintegrity

信号完整性分析平台孙灯亮 Agilent AEO众所周知,当今世界数字技术飞速发展,无论是一位从事有限通信系统,计算机系统,雷达和卫星通信系统,或是高速半导体集成电路设计,高速光电收发模块,高速信号处理,高速互连器件(诸如高速接插件,高速数字传输电缆)等领域的研发及测试工程师都会面临着一个共同的挑战——Signal Integrity ( SI) ——信号完整性。

10 年前我们所提到的数字产品,其时钟或数据频率大多在几十兆之内,信号的上升时间大多在几个纳秒,甚至几十纳秒以上。

那时的数字化产品设计工程师进行的就是“数字设计”――只要掌握布尔代数等数字方面的诸多知识,保证逻辑正确,就能设计出其所期望的性能的产品。

而现在的数字技术已经发展到几千兆,甚至几十千兆的传输速率,信号的上升时间大多在一纳秒以内,诸如串扰,阻抗匹配,EMI(电磁兼容),抖动等射频微波领域才会遇到的问题,如今变成了高速数字设计必须解决的关键性问题。

这就要求我们的工程师不但要具备数字方面的设计知识,同时也要具备射频微波方面的设计知识;不但要掌握时域及逻辑域的测量分析技术,还要掌握频域的测量分析技术。

信号完整性到底是什么?信号完整性这个概念,是针对高速数字信号提出来的,信号的实际波形会与理想波形存在着差别,SI 解决的就是信号传输过程中的信号质量问题。

到底什么样的信号会涉及SI 问题,要从信号的速率以及信号的上升时间两个角度来考虑。

拿PCB来说,当一段PCB 上的连线所造成的信号传输延时远远小于信号的上升时间时,可按简单的电路理论去设计;当一段PCB 上的连线所造成的信号传输延时与信号的上升时间类似时(有说是几倍于上升时间),则必须按传输线的理论去设计,此时的这段连线即是传输线。

举个具体实例,如图1 所示:图1 高速信号的传输假设由驱动器发出的信号是高质量的时钟信号,如图2 中红色波形所示。

但是,在接收机端看到的却是质量变差的信号,如图2 黄色波形所示。

SIGNAL INTEGRITY(信号完整性) 外文翻译

SIGNAL INTEGRITYRaymond Y. Chen, Sigrid, Inc., Santa Clara, CaliforniaIntroductionIn the realm of high-speed digital design, signal integrity has become a critical issue, and is posing increasing challenges to the design engineers. Many signal integrity problems are electromagnetic phenomena in nature and hence related to the EMI/EMC discussions in the previous sections of this book. In this chapter, we will discuss what the typical signal integrity problems are, where they come from, why it is important to understand them and how we can analyze and solve these issues. Several software tools available at present for signal integrity analysis and current trends in this area will also be introduced.The term Signal Integrity (SI) addresses two concerns in the electrical design aspects – the timing and the quality of the signal. Does the signal reach its destination when it is supposed to? And also, when it gets there, is it in good condition? The goal of signal integrity analysis is to ensure reliable high-speed data transmission. In a digital system, a signal is transmitted from one component to another in the form of logic 1 or 0, which is actually at certain reference voltage levels. At the input gate of a receiver, voltage above the reference value Vih is considered as logic high, while voltage below the reference value Vil is considered as logic low. Figure 14-1 shows the ideal voltage waveform in the perfect logic world, whereas Figure 14-2 shows how signal will look like in a real system. More complex data, composed of a string of bit 1 and 0s, are actually continuous voltage waveforms. The receiving component needs to sample the waveform in order to obtain the binary encoded information. The data sampling process is usually triggered by the rising edge or the falling edge of a clock signal as shown in the Figure 14-3. It is clear from the diagram that the data must arrive at the receiving gate on time and settle down to a non-ambiguous logic state when the receiving component starts to latch in. Any delay of the data or distortion of the data waveform will result in a failure of the data transmission. Imagine if the signal waveform in Figure 14-2 exhibits excessive ringing into the logic gray zone while the sampling occurs, then the logic level cannot be reliably detected.SI ProblemsTypical SI Problems“Timing” is everything in a high-speed system. Signal timing depends on the delay caused by the physical length that the signal must propagate. It also depends on the shape of the waveform when the threshold is reached. Signal waveform distortions can be caused by different mechanisms. But there are three mostly concerned noise problems:•Reflection Noise Due to impedance mismatch, stubs, visa and other interconnect discontinuities. •Crosstalk Noise Due to electromagnetic coupling between signal traces and visa.•Power/Ground Noise Due to parasitic of the power/ground delivery system during drivers’ simultaneous switching output (SSO). It is sometimes also called Ground Bounce, Delta-I Noise or Simultaneous Switching Noise (SSN).Besides these three kinds of SI problems, there is other Electromagnetic Compatibility or Electromagnetic Interference (EMC/EMI) problems that may contribute to the signal waveform distortions. When SI problems happen and the system noise margin requirements are not satisfied – the input to a switching receiver makes an inflection below Vih minimum or above Vil maximum; the input to a quiet receiver rises above Vil maximum or falls below Vih minimum; power/ground voltage fluctuations disturb the data in the latch, then logic error, data drop, false switching, or even system failure may occur. These types of noise faults are extremely difficult to diagnose and solve after the system is built or prototyped. Understanding and solving these problems before they occur will eliminate having to deal with them further into the project cycle,and will in turn cut down the development cycle and reduce the cost[1]. In the later part of thischapter, we will have further investigations on the physical behavior of these noise phenomena, their causes, their electrical models for analysis and simulation, and the ways to avoid them.1. Where SI Problems HappenSince the signals travel through all kinds of interconnections inside a system, any electrical impact happening at the source end, along the path, or at the receiving end, will have great effects on the signal timing and quality. In a typical digital system environment, signals originating from the off-chip drivers on the die (the chip) go through c4 or wire-bond connections to the chip package. The chip package could be single chip carrier or multi-chip module (MCM). Through the solder bumps of the chip package, signals go to the Printed Circuit Board (PCB) level. At this level, typical packaging structures include daughter card, motherboard or backplane. Then signals continue to go to another system component, such as an ASIC (Application Specific Integrated Circuit) chip, a memory module or a termination block. The chip packages, printed circuit boards, as well as the cables and connecters, form the so-called different levels of electronic packaging systems, as illustrated in Figure 14-4. In each level of the packaging structure, there are typical interconnects, such as metal traces, visa, and power/ground planes, which form electrical paths to conduct the signals. It is the packaging interconnection that ultimately influences the signal integrity of a system.2. SI In Electronic PackagingTechnology trends toward higher speed and higher density devices have pushed the package performance to its limits. The clock rate of present personal computers is approaching gigahertz range. As signal rise-time becomes less than 200ps, the significant frequency content of digital signals extends up to at least 10 GHz. This necessitates the fabrication of interconnects and packages to be capable of supporting very fast varying and broadband signals without degrading signal integrity to unacceptable levels. While the chip design and fabrication technology have undergone a tremendous evolution: gate lengths, having scaled from 50 µm in the 1960s to 0.18 µm today, are projected to reach 0.1 µm in the next few years; on-chip clock frequency is doubling every 18 months; and the intrinsic delay of the gate is decreasing exponentially with time to a few tens of Pico-seconds. However, the package design has lagged considerably. With current technology, the package interconnection delay dominates the system timing budget and becomes the bottleneck of the high-speed system design. It is generally accepted today that package performance is one of the major limiting factors of the overall system performance.Advances in high performance sub-micron microprocessors, the arrival of gigabit networks, and the need for broadband Internet access, necessitate the development of high performance packaging structures for reliable high-speed data transmission inside every electronics system.Signal integrity is one of the most important factors to be considered when designing these packages (chip carriers and PCBs) and integrating these packages together.3、SI Analysis3.1. SI Analysis in the Design FlowSignal integrity is not a new phenomenon and it did not always matter in the early days of the digital era. But with the explosion of the information technology and the arrival of Internet age, people need to be connected all the time through various high-speed digital communication/computing systems. In this enormous market, signal integrity analysis will play a more and more critical role to guarantee the reliable system operation of these electronics products. Without pre-layout SI guidelines, prototypes may never leave the bench; without post-layout SI verifications, products may fail in the field. Figure 14-5 shows the role of SI analysis in the high-speed design process. From this chart, we will notice that SI analysis is applied throughout the design flow and tightly integrated into each design stage. It is also very common to categorize SI analysis into two main stages: reroute analysis and post route analysis.In the reroute stage, SI analysis can be used to select technology for I/Os, clock distributions, chip package types, component types, board stickups, pin assignments, net topologies, and termination strategies. With various design parameters considered, batch SI simulations on different corner cases will progressively formulate a set of optimized guidelines for physical designs of later stage. SI analysis at this stage is also called constraint driven SI design because the guidelines developed will be used as constraints for component placement and routing. The objective of constraint driven SI design at the reroute stage is to ensure that the signal integrity of the physical layout, which follows the placement/routing constraints for noise and timing budget, will not exceed the maximum allowable noise levels. Comprehensive and in-depth reroute SI analysis will cut down the redesign efforts and place/route iterations, and eventually reduce design cycle.With an initial physical layout, post route SI analysis verifies the correctness of the SI design guidelines and constraints. It checks SI violations in the current design, such as reflection noise, ringing, crosstalk and ground bounce. It may also uncover SI problems that are overlooked in the reroute stage, because post route analysis works with physical layout data rather than estimated data or models, therefore it should produce more accurate simulation results.When SI analysis is thoroughly implemented throughout the whole design process, a reliable high performance system can be achieved with fast turn-around.In the past, physical designs generated by layout engineers were merely mechanical drawings when very little or no signal integrity issues were concerned. While the trend of higher-speed electronics system design continues, system engineers, responsible for developing a hardware system, are getting involved in SI and most likely employ design guidelines and routing constraints from signal integrity perspectives. Often, they simply do not know the answers to some of the SI problems because most of their knowledge is from the engineers doing previous generations of products. To face this challenge, nowadays, a design team (see Figure 14-6) needs to have SI engineers who are specialized in working in this emerging technology field. When a new technology is under consideration, such as a new device family or a new fabrication process for chip packages or boards, SI engineers will carry out the electrical characterization of the technology from SI perspectives, and develop layout guideline by running SI modeling and simulation software [2]. These SI tools must be accurate enough to model individual interconnections such as visa, traces, and plane stickups. And they also must be very efficient so what-if analysis with alternative driver/load models and termination schemes can be easily performed. In the end, SI engineers will determine a set of design rules and pass them to the design engineers and layout engineers. Then, the design engineers, who are responsible for the overall system design, need to ensure the design rules are successfully employed. They may run some SI simulations on a few critical nets once the board is initially placed and routed. And they may run post-layout verifications as well. The SI analysis they carry out involves many nets. Therefore, the simulation must be fast, though it may not require the kind of accuracy that SI engineers are looking for. Once the layout engineers get the placement and routing rules specified in SI terms, they need to generate an optimized physical design based on these constraints. And they will provide the report on any SI violations in a routed system using SI tools. If any violations are spotted, layout engineers will work closely with design engineers and SI engineers to solve these possible SI problems.3.2.Principles of SI AnalysisA digital system can be examined at three levels of abstraction: logic, circuit theory, and electromagnetic (EM) fields. The logic level, which is the highest level of those three, is where SI problems can be easily identified. EM fields, located at the lowest level of abstraction, comprise the foundation that the other levels are built upon [3]. Most of the SI problems are EM problems in nature, such as the cases of reflection, crosstalk and ground bounce. Therefore, understanding the physical behavior of SI problems from EM perspective will be very helpful. For instance, in the following multi-layer packaging structure shown in Figure 14-7, a switching current in via a will generate EM waves propagating away from that via in the radial direction between metal planes. The fields developed between metal planes will cause voltage variations between planes (voltage is the integration of the E-field). When the waves reach other visa, they will induce currents in those visa. And the induced currents in that visa will in turn generate EM waves propagating between the planes. When the waves reach the edges of the package, part of them will radiate into the air and part of them will get reflected back. When the waves bounce back and forth inside the packaging structure and superimpose to each other, resonance will occur. Wave propagation, reflection, coupling and resonance are the typical EM phenomena happening inside a packaging structure during signal transients. Even though EM full wave analysis is much more accurate than the circuit analysis in the modeling of packaging structures, currently, common approaches of interconnect modeling are based on circuit theory, and SI analysis is carried out with circuit simulators. This is because field analysis usually requires much more complicated algorithms and much larger computing resources than circuit analysis, and circuit analysis provides good SI solutions at low frequency as an electrostatic approximation.Typical circuit simulators, such as different flavors of SPICE, employ nodal analysis and solve voltages and currents in lumped circuit elements like resistors, capacitors and inductors. In SI analysis, an interconnect sometimes will be modeled as a lumped circuit element. For instance, a piece of trace on the printed circuit board can be simply modeled as a resistor for its finite conductivity. With this lumped circuit model, the voltages along both ends of the trace are assumed to change instantaneously and the travel time for the signal to propagate between the two ends is neglected. However, if the signal propagation time along the trace has to be considered, a distributed circuit model, such as a cascaded R-L-C network, will be adopted to model the trace. To determine whether the distributed circuit model is necessary, the rule of thumb is – if the signal rise time is comparable to the round-trip propagation time, you need to consider using the distributed circuit model.For example, a 3cm long stripling trace in a FR-4 material based printed circuit board will exhibits 200ps propagation delay. For a 33 MHz system, assuming the signal rise time to be 5ns, the trace delay may be safely ignored; however, with a system of 500 MHz and 300ps rise time, the 200ps propagation delay on the trace becomes important and a distributed circuit model has to be used to model the trace. Through this example, it is easy to see that in the high-speed design, with ever-decreasing signal rise time, distributed circuit model must be used in SI analysis.Here is another example. Considering a pair of solid power and ground planes in a printed circuit board with the dimension of 15cm by 15cm, it is very natural to think the planes acting as a large, perfect, lumped capacitor, from the circuit theory point of view. The capacitor model C= erA/d, an electro-static solution, assumes anywhere on the plane the voltages are the same and all the charges stored are available instantaneously anywhere along the plane. This is true at DC and low frequency. However, when the logics switch with a rise time of 300ps, drawing a large amount of transient currents from the power/ground planes, they perceive the power/ground structure as a two-dimensional distributed network with significant delays. Only some portion of the plane charges located within a small radius of the switching logics will be able to supply the demand. And voltages between the power/ground planes will have variations at different locations. In this case, an ideal lumped capacitor model is obviously not going to account for the propagation effects. Two-dimensional distributed R-L-C circuit networks must be used to model the power/ground pair.In summary, as the current high-speed design trend continues, fast rise time reveals the distributed nature of package interconnects. Distributed circuit models need to be adopted to simulate the propagation delay in SI analysis. However, at higher frequencies, even the distributed circuit modeling techniques are not good enough, full wave electromagnetic field analysis based on solving Maxwell’s equations must come to play. As presen ted in later discussions, a trace will not be modeled as a lumped resistor, or a R-L-C ladder; it will be analyzed based upon transmission line theory; and a power/ground plane pair will be treated as a parallel-plate wave guide using radial transmission line theory.Transmission line theory is one of the most useful concepts in today’s SI analysis. And it is a basic topic in many introductory EM textbooks. For more information on the selective reading materials, please refer to the Resource Center in Chapter 16.In the above discussion, it can be noticed that signal rise time is a very important quantity in SI issues. So a little more expanded discussion on rise time will be given in the next section.信号完整性介绍在高速数字设计领域,信号完整性已经成为一个严重的问题,是造成越来越多的挑战的设计工程师。

英语作文-集成电路设计师需要了解的基础知识与技术要点

英语作文-集成电路设计师需要了解的基础知识与技术要点Integrated circuit (IC) design is a crucial field within electrical engineering, requiring a deep understanding of both foundational principles and advanced technologies. This article explores the essential knowledge and technical aspects that an IC designer needs to master.### Fundamentals of Integrated Circuits。

Integrated circuits are at the heart of modern electronics, encompassing various components such as transistors, diodes, resistors, and capacitors fabricated on a single semiconductor substrate. The design process involves translating circuit requirements into physical layouts that optimize performance, power consumption, and reliability.### Semiconductor Physics and Device Modeling。

A solid grasp of semiconductor physics underpins IC design. Key concepts include the behavior of diodes and transistors under different operating conditions, such as forward and reverse biasing, saturation, and cutoff regions. Device modeling techniques, like SPICE (Simulation Program with Integrated Circuit Emphasis), are essential for predicting circuit behavior accurately.### Circuit Design Techniques。

3GPP常用英文缩写全称大全

3GPP常用英文缩写全称大全3G是3GPP的简写形式,3GPP在英文里的全称是:the 3rd Generation Partner Project 中文的全称是:第三代合作伙伴计划,是领先的3G技术规范机构,旨在研究制定并推广基于演进的GSM核心网络的3G标准,它负责WCDMA标准的制定,R4标准是其中较为成熟的一个版本。

3GPP:3GP是一种3G流媒体的视频编码格式,是目前手机中最为常见的一种视频格式。

简单的说,该格式是“第三代合作伙伴项目”(3GPP)制定的一种多媒体标准,使用户能使用手机享受高质量的视频、音频等多媒体内容。