RT9187-28PQV中文资料

ATTINY28L-4PC,ATTINY28L-4PI,ATTINY28L-4AC,ATTINY28L-4AU,ATTINY28L-4AI,规格书,Datasheet 资料

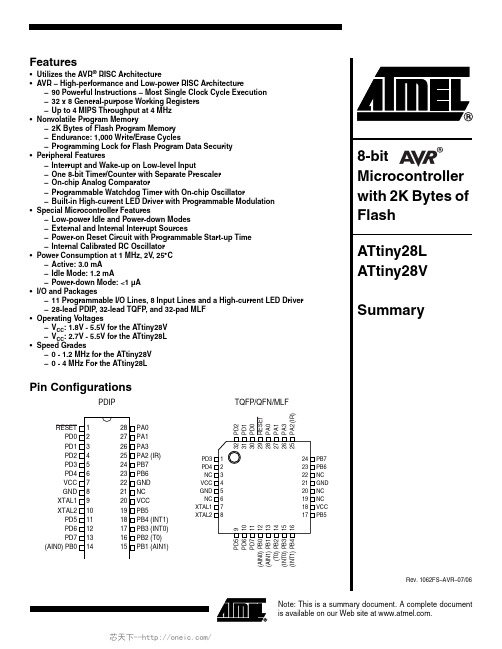

1Features•Utilizes the AVR ® RISC Architecture•AVR – High-performance and Low-power RISC Architecture–90 Powerful Instructions – Most Single Clock Cycle Execution –32 x 8 General-purpose Working Registers –Up to 4 MIPS Throughput at 4 MHz •Nonvolatile Program Memory–2K Bytes of Flash Program Memory –Endurance: 1,000 Write/Erase Cycles–Programming Lock for Flash Program Data Security •Peripheral Features–Interrupt and Wake-up on Low-level Input–One 8-bit Timer/Counter with Separate Prescaler –On-chip Analog Comparator–Programmable Watchdog Timer with On-chip Oscillator–Built-in High-current LED Driver with Programmable Modulation •Special Microcontroller Features–Low-power Idle and Power-down Modes –External and Internal Interrupt Sources–Power-on Reset Circuit with Programmable Start-up Time –Internal Calibrated RC Oscillator •Power Consumption at 1 MHz, 2V , 25°C –Active: 3.0 mA –Idle Mode: 1.2 mA–Power-down Mode: <1 µA •I/O and Packages–11 Programmable I/O Lines, 8 Input Lines and a High-current LED Driver –28-lead PDIP , 32-lead TQFP , and 32-pad MLF •Operating Voltages–V CC : 1.8V - 5.5V for the ATtiny28V –V CC : 2.7V - 5.5V for the ATtiny28L •Speed Grades–0 - 1.2 MHz for the ATtiny28V –0 - 4 MHz For the ATtiny28LPin ConfigurationsPDIPTQFP/QFN/MLF8-bit Microcontroller with 2K Bytes of ATtiny28L ATtiny28V SummaryNote: This is a summary document. A complete documentis available on our Web site at .2ATtiny28L/V1062FS–AVR–07/06DescriptionThe ATtiny28 is a low-power CMOS 8-bit microcontroller based on the AVR RISC archi-tecture. By executing powerful instructions in a single clock cycle, the ATtiny28 achieves throughputs approaching 1 MIPS per MHz, allowing the system designer to optimize power consumption versus processing speed. The AVR core combines a rich instruction set with 32 general-purpose working registers. All the 32 registers are directly con-nected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architec-ture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.Block DiagramFigure 1. The ATtiny28 Block DiagramThe ATtiny28 provides the following features: 2K bytes of Flash, 11 general-purpose I/O lines, 8 input lines, a high-current LED driver, 32 general-purpose working registers, an 8-bit timer/counter, internal and external interrupts, programmable Watchdog Timer with internal oscillator and 2 software-selectable power-saving modes. The Idle Mode stops the CPU while allowing the timer/counter and interrupt system to continue functioning.The Power-down mode saves the register contents but freezes the oscillator, disabling all other chip functions until the next interrupt or hardware reset. The wake-up or inter-3ATtiny28L/V1062FS–AVR–07/06rupt on low-level input feature enables the ATtiny28 to be highly responsive to external events, still featuring the lowest power consumption while in the power-down modes.The device is manufactured using Atmel’s high-density, nonvolatile memory technology.By combining an enhanced RISC 8-bit CPU with Flash on a monolithic chip, the Atmel ATtiny28 is a powerful microcontroller that provides a highly flexible and cost-effective solution to many embedded control applications. The ATtiny28 AVR is supported with a full suite of program and system development tools including: macro assemblers, pro-gram debugger/simulators, in-circuit emulators and evaluation kits.Pin DescriptionsVCC Supply voltage pin.GNDGround pin.Port A (PA3..PA0)Port A is a 4-bit I/O port. PA2 is output-only and can be used as a high-current LED driver. At V CC = 2.0V, the PA2 output buffer can sink 25 mA. PA3, PA1 and PA0 are bi-directional I/O pins with internal pull-ups (selected for each bit). The port pins are tri-stated when a reset condition becomes active, even if the clock is not running.Port B (PB7..PB0)Port B is an 8-bit input port with internal pull-ups (selected for all Port B pins). Port B pins that are externally pulled low will source current if the pull-ups are activated.Port B also serves the functions of various special features of the ATtiny28 as listed on page 27. If any of the special features are enabled, the pull-up(s) on the corresponding pin(s) is automatically disabled. The port pins are tri-stated when a reset condition becomes active, even if the clock is not running.Port D (PD7..PD0)Port D is an 8-bit I/O port. Port pins can provide internal pull-up resistors (selected for each bit). The port pins are tri-stated when a reset condition becomes active, even if the clock is not running.XTAL1Input to the inverting oscillator amplifier and input to the internal clock operating circuit.XTAL2Output from the inverting oscillator amplifier.pulses longer than 50 ns will generate a reset, even if the clock is not running. Shorter pulses are not guaranteed to generate a reset.4ATtiny28L/V1062FS–AVR–07/06Notes:1.For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addressesshould never be written.2.Some of the status flags are cleared by writing a logical “1” to them. Note that the CBI and SBI instructions will operate on allbits in the I/O register, writing a one back into any flag read as set, thus clearing the flag. The CBI and SBI instructions work with registers $00 to $1F only.Register SummaryAddressNameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0Page$3F SREG ITHSVNZCpage 6$3E Reserved ...Reserved $20Reserved $1F Reserved $1E Reserved $1D Reserved $1C Reserved $1B PORTA ----PORTA3PORTA2PORTA1PORTA0page 32$1A PACR ----DDA3PA2HCDDA1DDA0page 32$19PINA ----PINA3-PINA1PINA0page 32$18Reserved $17Reserved $16PINB PINB7PINB6PINB5PINB4PINB3PINB2PINB1PINB0page 32$15Reserved $14Reserved $13Reserved $12PORTD PORTD7PORTD6PORTD5PORTD4PORTD3PORTD2PORTD1PORTD0page 33$11DDRD DDD7DDD6DDD5DDD4DDD3DDD2DDD1DDD0page 33$10PIND PIND7PIND6PIND5PIND4PIND3PIND2PIND1PIND0page 33$0F Reserved $0E Reserved $0D Reserved $0C Reserved $0B Reserved $0A Reserved $09Reserved $08ACSR ACD -ACO ACI ACIE -ACIS1ACIS0page 44$07MCUCS PLUPB -SE SM WDRF -EXTRF PORF page 19$06ICR INT1INT0LLIE TOIE0ISC11ISC10ISC01ISC00page 22$05IFR INTF1INTF0-TOV0----page 23$04TCCR0FOV0--OOM01OOM00CS02CS01CS00page 35$03TCNT0Timer/Counter0 (8-bit)page 36$02MODCR ONTIM4ONTIM3ONTIM2ONTIM1 ONTIM0MCONF2MCONF1MCONF0page 43$01WDTCR ---WDTOEWDEWDP2WDP1WDP0page 37$00OSCCALOscillator Calibration Registerpage 95ATtiny28L/V1062FS–AVR–07/06Instruction Set SummaryMnemonicOperandsDescriptionOperationFlags# ClocksARITHMETIC AND LOGIC INSTRUCTIONSADD Rd, Rr Add Two RegistersRd ← Rd + Rr Z,C,N,V,H 1ADC Rd, Rr Add with Carry Two Registers Rd ← Rd + Rr + C Z,C,N,V,H 1SUB Rd, Rr Subtract Two Registers Rd ← Rd - Rr Z,C,N,V,H 1SUBI Rd, K Subtract Constant from Register Rd ← Rd - K Z,C,N,V,H 1SBC Rd, Rr Subtract with Carry Two Registers Rd ← Rd - Rr - C Z,C,N,V,H 1SBCI Rd, K Subtract with Carry Constant from Reg.Rd ← Rd - K - C Z,C,N,V,H 1AND Rd, Rr Logical AND RegistersRd ← Rd • Rr Z,N,V 1ANDI Rd, K Logical AND Register and Constant Rd ← Rd • K Z,N,V 1OR Rd, Rr Logical OR RegistersRd ← Rd v Rr Z,N,V 1ORI Rd, K Logical OR Register and Constant Rd ← Rd v K Z,N,V 1EOR Rd, Rr Exclusive OR Registers Rd ← Rd ⊕ Rr Z,N,V 1COM Rd One’s Complement Rd ← $FF - Rd Z,C,N,V 1NEG Rd Two’s Complement Rd ← $00 - Rd Z,C,N,V,H 1SBR Rd, K Set Bit(s) in Register Rd ← Rd v K Z,N,V 1CBR Rd, K Clear Bit(s) in Register Rd ← Rd • (FFh - K)Z,N,V 1INC Rd Increment Rd ← Rd + 1Z,N,V 1DEC Rd DecrementRd ← Rd - 1 Z,N,V 1TST Rd Test for Zero or Minus Rd ← Rd • Rd Z,N,V1CLR Rd Clear Register Rd ← Rd ⊕ Rd Z,N,V 1SER Rd Set Register Rd ← $FF None 1BRANCH INSTRUCTIONSRJMP k Relative JumpPC ← PC + k + 1None 2RCALL kRelative Subroutine Call PC ← PC + k + 1None 3RET Subroutine Return PC ← STACK None 4RETI Interrupt Return PC ← STACKI 4CPSE Rd, Rr Compare, Skip if Equal if (Rd = Rr) PC ← PC + 2 or 3None 1/2CP Rd, Rr CompareRd - Rr Z,N,V,C,H 1CPC Rd, Rr Compare with CarryRd - Rr - C Z,N,V,C,H 1CPI Rd, K Compare Register with Immediate Rd - KZ N,V,C,H 1SBRC Rr, b Skip if Bit in Register Cleared if (Rr(b) = 0) PC ← PC + 2 or 3None 1/2SBRS Rr, b Skip if Bit in Register is Set if (Rr(b) = 1) PC ← PC + 2 or 3None 1/2SBIC P, b Skip if Bit in I/O Register Cleared if (P(b) = 0) PC ← PC + 2 or 3None 1/2SBIS P, b Skip if Bit in I/O Register is Set if (P(b) = 1) PC ← PC + 2 or 3None 1/2BRBS s, k Branch if Status Flag Set if (SREG(s) = 1) then PC ← PC + k + 1None 1/2BRBC s, k Branch if Status Flag Cleared if (SREG(s) = 0) then PC ← PC + k + 1None 1/2BREQ k Branch if Equal if (Z = 1) then PC ← PC + k + 1None 1/2BRNE k Branch if Not Equal if (Z = 0) then PC ← PC + k + 1None 1/2BRCS k Branch if Carry Set if (C = 1) then PC ← PC + k + 1None 1/2BRCC k Branch if Carry Cleared if (C = 0) then PC ← PC + k + 1None 1/2BRSH k Branch if Same or Higher if (C = 0) then PC ← PC + k + 1None 1/2BRLO k Branch if Lower if (C = 1) then PC ← PC + k + 1None 1/2BRMI k Branch if Minus if (N = 1) then PC ← PC + k + 1None 1/2BRPL k Branch if Plusif (N = 0) then PC ← PC + k + 1None 1/2BRGE k Branch if Greater or Equal, Signed if (N ⊕ V = 0) then PC ← PC + k + 1None 1/2BRLT k Branch if Less than Zero, Signed if (N ⊕ V = 1) then PC ← PC + k + 1None 1/2BRHS k Branch if Half-carry Flag Set if (H = 1) then PC ← PC + k + 1None 1/2BRHC k Branch if Half-carry Flag Cleared if (H = 0) then PC ← PC + k + 1None 1/2BRTS k Branch if T-flag Set if (T = 1) then PC ← PC + k + 1None 1/2BRTC k Branch if T-flag Cleared if (T = 0) then PC ← PC + k + 1None 1/2BRVS k Branch if Overflow Flag is Set if (V = 1) then PC ← PC + k + 1None 1/2BRVC k Branch if Overflow Flag is Cleared if (V = 0) then PC ← PC + k + 1None 1/2BRIE k Branch if Interrupt Enabled if (I = 1) then PC ← PC + k + 1None 1/2BRIDkBranch if Interrupt Disabledif (I = 0) then PC ← PC + k + 1None1/26ATtiny28L/V1062FS–AVR–07/06DATA TRANSFER INSTRUCTIONSLD Rd, Z Load Register Indirect Rd ← (Z)None 2ST Z, Rr Store Register Indirect (Z) ← Rr None 2MOV Rd, Rr Move between Registers Rd ← Rr None 1LDI Rd, K Load Immediate Rd ←K None 1IN Rd, P In Port Rd ← P None 1OUT P, RrOut PortP ← Rr None 1LPMLoad Program MemoryR0 ← (Z)None3BIT AND BIT-TEST INSTRUCTIONS SBI P, b Set Bit in I/O Register I/O(P,b) ← 1None 2CBI P, b Clear Bit in I/O Register I/O(P,b) ←None 2LSL Rd Logical Shift LeftRd(n+1) ← Rd(n), Rd(0) ← 0Z,C,N,V 1LSR Rd Logical Shift Right Rd(n) ← Rd(n+1), Rd(7) ← 0Z,C,N,V 1ROL Rd Rotate Left through Carry Rd(0) ← C, Rd(n+1) ← Rd(n), C ← Rd(7)Z,C,N,V 1ROR Rd Rotate Right through Carry Rd(7) ← C, Rd(n) ← Rd(n+1), C ← Rd(0)Z,C,N,V 1ASR Rd Arithmetic Shift Right Rd(n) ← Rd(n+1), n = 0..6Z,C,N,V 1SWAP Rd Swap Nibbles Rd(3..0) ← Rd(7..4), Rd(7..4) ← Rd(3..0)None 1BSET s Flag Set SREG(s) ← 1SREG(s)1BCLR s Flag Clear SREG(s) ← 0SREG(s)1BST Rr, b Bit Store from Register to T T ← Rr(b)T 1BLD Rd, bBit Load from T to Register Rd(b) ← T None 1SEC Set Carry C ← 1C 1CLC Clear Carry C ←0C 1SEN Set Negative Flag N ← 1N 1CLN Clear Negative Flag N ← 0N 1SEZ Set Zero Flag Z ←1Z 1CLZ Clear Zero Flag Z ← 0Z1SEI Global Interrupt Enable I ← 1I 1CLI Global Interrupt Disable I ←I 1SES Set Signed Test FlagS ← 1S 1CLS Clear Signed Test Flag S ←0S 1SEV Set Two’s Complement OverflowV ←1V 1CLV Clear Two’s Complement Overflow V ← 0V 1SET Set T in SREG T ← 1T 1CLT Clear T in SREG T ← 0T 1SEH Set Half-carry Flag in SREG H ← 1H 1CLH Clear Half-carry Flag in SREG H ←H 1NOP No Operation None 1SLEEP Sleep(see specific descr. for Sleep function)None 1WDRWatchdog Reset(see specific descr. for WDR/timer)None1Instruction Set Summary (Continued)MnemonicOperandsDescriptionOperationFlags# Clocks7ATtiny28L/V1062FS–AVR–07/06Notes:1.This device can also be supplied in wafer form. Please contact your local Atmel sales office for detailed ordering informationand minimum quantities.2.Pb-free packaging alternative, complies to the European Directive for Restriction of Hazardous Substances (RoHS direc-tive).Also Halide free and fully Green.Ordering InformationSpeed (MHz)Power Supply (Volts)Ordering Code Package (1)Operation Range 42.7 - 5.5A Ttiny28L-4AC A Ttiny28L-4PC A Ttiny28L-4MC32A 28P332M1-A Commercial (0°C to 70°C)A Ttiny28L-4AI A Ttiny28L-4AU (2)A Ttiny28L-4PI A Ttiny28L-4PU (2)A Ttiny28L-4MI A Ttiny28L-4MU (2)32A 32A 28P328P332M1-A 32M1-A Industrial (-40°C to 85°C)1.21.8 - 5.5A Ttiny28V-1AC A Ttiny28V-1PC A Ttiny28V-1MC32A 28P332M1-A Commercial (0°C to 70°C)A Ttiny28V-1AI A Ttiny28V-1AU (2)A Ttiny28V-1PI A Ttiny28V-1PU (2)A Ttiny28V-1MI A Ttiny28V-1MU (2)32A 32A 28P328P332M1-A 32M1-AIndustrial (-40°C to 85°C)Package Type32A 32-lead, Thin (1.0 mm) Plastic Quad Flat Package (TQFP)28P328-lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)32M1-A32-pad, 5x5x1.0 body, Lead Pitch 0.50mm, Quad Flat No-lead/Micro Lead Frame Package (QFN/MLF)8ATtiny28L/V1062FS–AVR–07/06Packaging Information32A9ATtiny28L/V1062FS–AVR–07/0628P310ATtiny28L/V1062FS–AVR–07/0632M1-A11ATtiny28L/V1062FS–AVR–07/06ErrataAll revisionsNo known errata.12ATtiny28L/V1062FS–AVR–07/06Datasheet Revision HistoryPlease note that the referring page numbers in this section are referred to this docu-ment. The referring revision in this section are referring to the document revision.Rev – 01/06G 1.Updated chapter layout.2.Updated “Ordering Information” on page 7.Rev – 01/06G1.Updated description for “Port A” on page 25.2.Added note 6 in “DC Characteristics” on page 54.3.Updated “Ordering Information” on page 7.4.Added “Errata” on page 11.Rev – 03/05F1.Updated “Electrical Characteristics” on page 54.2.MLF-package alternative changed to “Quad Flat No-Lead/Micro Lead Frame PackageQFN/MLF”.3.Updated “Ordering Information” on page 7.1062FS–AVR–07/06© 2006 Atmel Corporation . All rights reserved. ATMEL ®, logo and combinations thereof, Everywhere You Are ®, AVR ®, AVR Studio ®, and oth-ers, are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of oth-ers.Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise,to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL’S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL’S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABIL ITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBIL ITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel’s products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.Atmel CorporationAtmel Operations2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 487-2600Regional HeadquartersEuropeAtmel SarlRoute des Arsenaux 41Case Postale 80CH-1705 Fribourg SwitzerlandTel: (41) 26-426-5555Fax: (41) 26-426-5500AsiaRoom 1219Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong KongTel: (852) 2721-9778Fax: (852) 2722-1369Japan9F, Tonetsu Shinkawa Bldg.1-24-8 ShinkawaChuo-ku, Tokyo 104-0033JapanTel: (81) 3-3523-3551Fax: (81) 3-3523-7581Memory2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 436-4314Microcontrollers2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 436-4314La Chantrerie BP 7060244306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18Fax: (33) 2-40-18-19-60ASIC/ASSP/Smart CardsZone Industrielle13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00Fax: (33) 4-42-53-60-011150 East Cheyenne Mtn. Blvd.Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300Fax: 1(719) 540-1759Scottish Enterprise Technology Park Maxwell BuildingEast Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000Fax: (44) 1355-242-743RF/AutomotiveTheresienstrasse 2Postfach 353574025 Heilbronn, Germany Tel: (49) 71-31-67-0Fax: (49) 71-31-67-23401150 East Cheyenne Mtn. Blvd.Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300Fax: 1(719) 540-1759Biometrics/Imaging/Hi-Rel MPU/High Speed Converters/RF DatacomAvenue de Rochepleine BP 12338521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00Fax: (33) 4-76-58-34-80Literature Requests/literature。

RT9817 产品数据手册说明书

1DS9817-13 April 2022Features●Internally Fixed Threshold 1.2V to 5V in 0.1V Step ●High Accuracy ±1.5%●Low Supply Current 3μA●No External Components Required ●Quick Reset within 20μs●Built-in Recovery Delay Include 0ms, 55ms, 220ms,450ms Options●Low Functional Supply Voltage 0.9V ●CMOS Push-Pull Output●Small SC-82 and SOT-143 Packages●RoHS Compliant and 100% Lead (Pb)-FreePin ConfigurationApplications●Computers ●Controllers●Intelligent Instruments●Critical μP and μC Power Monitoring ●Portable/Battery-Powered EquipmentMicro-Power Voltage Detectors with Manual ResetOrdering InformationGeneral DescriptionThe RT9817 is a micro-power voltage detector with deglitched manual reset input supervising the power supply voltage level for microprocessors (μP) or digital systems. It provides internally fixed threshold levels with 0.1V per step ranging from 1.2V to 5V, which covers most digital applications. It features low supply current of 3μA.The RT9817 performs supervisory function by sending out a reset signal whenever the V DD voltage falls below a preset threshold level. This reset signal will last the whole period before V DD recovering. Once V DD recovered upcrossing the threshold level, the reset signal will be released after a certain delay time. To pull reset signal low manually, just pull the manual reset input (MR) below the specified V IL level. RT9817 is provided in SC-82 and SOT-143 packages.(TOP VIEW)SOT-143Marking Information For marking information, contact our sales representative directly or through a RichTek distributor located in your area, otherwise visit our website for detail.Note :Richtek p roducts are :❝RoHS compliant and compatible with the current require- ments of IPC/JEDEC J-STD-020.❝Suitable for use in SnPb or Pb-free soldering processes.SC-82RESET/RESET MRRESET/RESET MR RT9817A = 0ms (RESET)B = 55ms (RESET)C = 220ms (RESET)D = 450ms (RESET)E = 0ms (RESET)F = 55ms (RESET)G = 220ms (RESET)H = 450ms (RESET)2DS9817-13 April 2022 Functional Block DiagramTypical Application CircuitFunctional Pin DescriptionRESET/RESETMRPart StatusThe part status values are defined as below :Active : Device is in production and is recommended for new designs. Lifebuy : The device will be discontinued, and a lifetime -buy period is in effect. NRND : Not recommended for new designs.Preview : Device has been announced but is not in production. Obsolete : Richtek has discontinued the production of the device.3DS9817-13 April 2022Absolute Maximum Ratings (Note 1)●Terminal Voltage (with Respect to GND)V DD ------------------------------------------------------------------------------------------------------------------------−0.3V to 6.0V●All Other Inputs --------------------------------------------------------------------------------------------------------−0.3V to V DD +0.3V ●Input Current, I VDD -----------------------------------------------------------------------------------------------------20mA ●Power Dissipation, PD @ T A = 25°CSC-82--------------------------------------------------------------------------------------------------------------------0.25W SOT-143-----------------------------------------------------------------------------------------------------------------0.285W ●Package Thermal Resistance (Note 2)SC-82, θJA ---------------------------------------------------------------------------------------------------------------400°C SOT-143, θJA ------------------------------------------------------------------------------------------------------------350°C ●Lead Temperature (Soldering, 10sec.)---------------------------------------------------------------------------- 260°C●Storage T emperature Range ----------------------------------------------------------------------------------------−65°C to 125°C ●ESD Susceptibility (Note 3)HBM (Human Body Mode)------------------------------------------------------------------------------------------2kV MM (Machine Mode)--------------------------------------------------------------------------------------------------200VElectrical Characteristics(V= 3V, T = 25°C, unless otherwise specified)Recommended Operating Conditions (Note 4)●Junction T emperature Range ----------------------------------------------------------------------------------------−40°C to 125°C ●Ambient T emperature Range ----------------------------------------------------------------------------------------−40°C to 85°CTo be continued4DS9817-13 April 2022Note 1. Stresses listed as the above “Absolute Maximum Ratings ” may cause permanent damage to the device. These are forstress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.Note 2. θJA is measured in the natural convection at T A = 25°C on a low effective thermal conductivity test board ofJEDEC 51-3 thermal measurement standard.Note 3. Devices are ESD sensitive. Handling precautions are recommended.Note 4. The device is not guaranteed to function outside its operating conditions.5DS9817-13 April 2022Typical Operating CharacteristicsSupply Current vs. Input Voltage01234123456Input Voltage (V)S u p p l y C u r r e n t I D D (u A )Output Voltage vs. Input Voltage012345670123456Input Voltage (V)O u t p u t V o l t a g e (V)Nch Driver Output Current vs. V DS020*********120012345V DS (V)O u t p u t C u r r e n t(m A )Supply Current vs. Input Voltage01234560123456Input Voltage (V)S u p p l y C u r r e n t (u A )Nch Driver Output Current vs. V DS010********600.511.522.533.5V DS (V)O u t p u t C u r r e n t (m A )Nch Driver Output Current vs. V DS00.40.81.21.622.400.30.60.91.21.5V DS (V)O u t p u t C u r r e n t(m A )6DS9817-13 April 2022 Nch Driver Sink Current vs. Input Voltage0102030400.511.522.533.5Input Voltage (V)S i n k C u r r e n t I S I N K (m A )Supply Current vs. Input Voltage01234123456Input Voltage (V)S u p p l y C u r re n t (u A )Power-Down Reset Delay vs. Temperature051015202530354045-50-25255075100125Temperature P o w e r -D o w n R e s e t D e l a y (u s)(°C)Power-Down Reset Delay vs. Temperature051015202530354045-50-25255075100125Temperature P o w e r -D o w n R e s e t D e l a y (u s )(°C)Power-Down Reset Delay vs. Temperature03691215-50-25255075100125Temperature P o w e r -D o w n R e s e t D e l a y (u s )(°C)Nch Driver Sink Current vs. Input Voltage0102030405012345Input Voltage (V)S i n k C u r r e n t I S I N K (m A )7DS9817-13 April 2022Output Delay Time vs. Load Capacitance0.010.111010010000.00010.00100.01000.1000 1.0000Load Capacitance (uF)O u t p u t D e l a y T i m e (m s )Power-Up Reset Time-Out vs. Temperature0255075100-50-25255075100125Temperature P o w e r -U p R e s e t T im e -O u t (m s )(°C)Reset Threshold Deviation vs. Temperature1.002.003.004.005.006.00-50-25255075100125Temperature R e s e t T h r e s h o l d D e v i a t i on (V )(°C)Pch Driver Output Current vs. Input Voltage0510152025123456Input Voltage (V)O u t p u t C u r r e n t(m A )Nch Driver Output Current vs. V DS204060801001201401600123456V DS (V)N c h D r i v e r O u t p u t C ur r e n t (m A )Power-Up Reset Time-Out vs. Temperature0100200300400500-50-25255075100125Temperature P o w e r -U p R e s e t T i me -O u t (m s )(°C)8DS9817-13 April 2022 Nch Driver Output Current vs. Input Voltage1020304050600123456Input Voltage (V)N c h D r i v e r O u t p u t C u r r e n t (m A )Output Voltage vs. Input Voltage01234567123456Input Voltage (V)O u t p u tV o l t a g e (V )Power-Down Reset Time-Out vs. Temperature051015202530-50-25255075100125Temperature P ow e r -D o w n R e s e t T i m e -O u t (u s )(°C)Power Down Reset Time-Out vs. Temperature0100200300400500-50-25255075100125Temperature P o w e r D o w n R e s e t T i m e -O u t (m s )(°C)9DS9817-13 April 2022Application InformationBenefits of Highly Accurate Reset ThresholdMost μP supervisor ICs have reset threshold voltages between 1% and 1.5% below the value of nominal supply voltages.This ensures a reset will not occur within 1% of the nominal supply, but will occur when the supply is 1.5% below nom inal.10DS9817-13 April 2022SOT-143 Surface Mount Package11DS9817-13 April Richtek Technology CorporationHeadquarter5F, No. 20, Taiyuen Street, Chupei CityHsinchu, Taiwan, R.O.C.Tel: (8863)5526789 Fax: (8863)5526611Information that is provided by Richtek Technology Corporation is believed to be accurate and reliable. Richtek reserves the right to make any change in circuit design,specification or other related things if necessary without notice at any time. No third party intellectual property infringement of the applications should be guaranteed by users when integrating Richtek products into any application. No legal responsibility for any said applications is assumed by Richtek.Richtek Technology Corporation Taipei Office (Marketing)5F, No. 95, Minchiuan Road, Hsintien City Taipei County, Taiwan, R.O.C.Tel: (8862)86672399 Fax: (8862)86672377Email:*********************SC -82 Surface Mount Package。

lm2904中文资料

lm2904中文资料LM2439 视频信号输出集成电路LM2453 视频信号输出集成电路LM2577 稳压集成电路LM2595 直流变换集成电路LM270H 自动增益及静噪控制集成电路LM2808N 伴音中频放大、鉴频及功率放大集成电路LM2904 双运算放大集成电路LM3065N 伴音中频放大、鉴频及前置放大集成电路LM3089 调频中频放大集成电路LM311N 电压比较运放集成电路LM317T 三端电源稳压1.5A集成电路LM324 四运算放大集成电路LM324M 四运算放大集成电路LM3361 解调集成电路LM33T 三端电源稳压-26V集成电路LM358 双运算放大集成电路LM358PS-T1 双运算放大集成电路LM3656 伴音中频放大、鉴频及前置放大集成电路LM377 双声道音频功率放大集成电路LM378 双声道音频功率放大集成电路LM380 场扫描输出集成电路LM381 运算放大集成电路LM382 宽带放大集成电路LM384 音频功率放大集成电路LM386 音频功率放大集成电路LM387 宽带放大集成电路LM3875T 音频功率放大集成电路LM3886 音频功率放大集成电路LM3915 发光二极管十位显示驱动集成电路LM399 基准稳压集成电路LM4500A 调频立体声解码集成电路LM4610 音调、音量、平衡调节集成电路LM4765 双声道音频功率放大30W×2集成电路LM741CN 运算放大集成电路LM79052 三端电源稳压-5.2V/1A集成电路LM8915N 显示驱动集成电路LN5241RA89 显示驱动集成电路LP62S512AX-70LLT 存储集成电路LPUVCP-96 端口功能扩展集成电路LR37632 伺服集成电路LR381641 主轴、字符控制集成电路LS0072 变音集成电路LSC4350 屏幕显示控制集成电路LSC4584P2 屏幕显示控制集成电路LT1074 开关电源稳压集成电路LT1109 升压稳压集成电路LTC1147 直流变换集成电路LTC1148 直流变换集成电路LTV1817 光电耦合集成电路LUKS-5140-M2 微处理集成电路LV1011 人工智能处理集成电路LV1100 音频信号处理集成电路LVA501 视频信号处理集成电路LVA521 制式切换集成电路M11B416256A 存储集成电路M1418VVW 微处理集成电路M2063SP 制式转换集成电路M208 系统控制集成电路M24C08 存储集成电路M24C128-WMN6 存储集成电路M27V201-200N6 中文字库集成电路M28F101AVPAD 存储集成电路M3004LAB1 红外遥控信号发射集成电路M32L1632512A 存储集成电路M34300-012SP 微处理集成电路M34300-628SP 微处理集成电路M34300M4-012SP 微处理集成电路M34300N4-011SP 微处理集成电路M34300N4-012SP 微处理集成电路M34300N4-555SP 微处理集成电路M34300N4-567SP 微处理集成电路M34300N4-584SP 微处理集成电路M34300N4-587SP 微处理集成电路M34300N4-628SP 微处理集成电路M34300N4-629SP 微处理集成电路M34300N4-657SP 微处理集成电路M34302M8-612SP 微处理集成电路M37100M8-616SP 微处理集成电路M37102M8-503SP 微处理集成电路M37103M4-750SP 微处理集成电路M37201M6 微处理集成电路M37204M8-852SP 微处理集成电路M37210M2-609SP 微处理集成电路M37210M3-010SP 微处理集成电路M37210M3-550SP 微处理集成电路M37210M3-603SP 微处理集成电路M37210M3-800SP 微处理集成电路M37210M3-901SP 微处理集成电路M37210M3-902SP 微处理集成电路M37210M4-650SP 微处理集成电路M37210M4-688微处理集成电路M37210M4-705SP 微处理集成电路M37210M4-786SP 微处理集成电路M37211M2-604SP 微处理集成电路M37211M2-609SP 微处理集成电路。

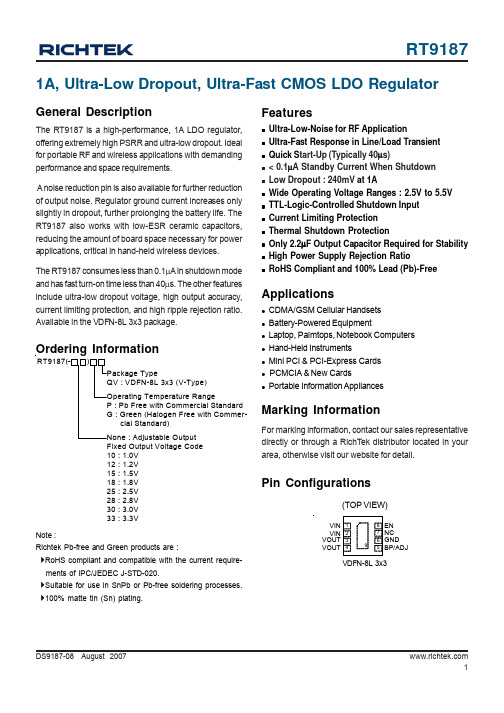

RT9187中文资料

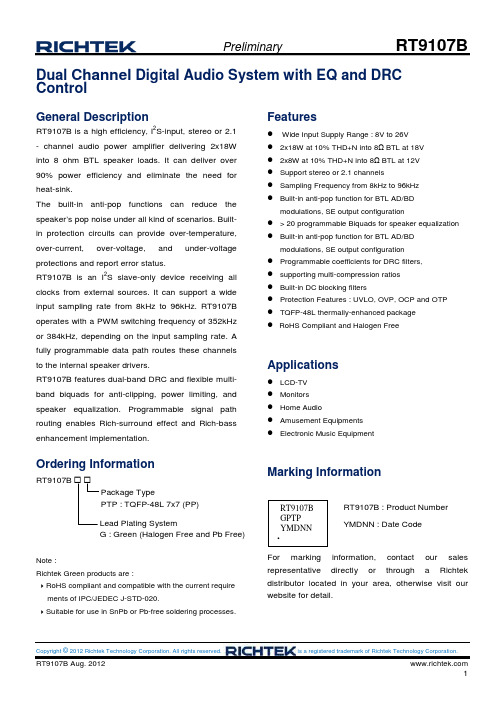

DS9187-08 August 2007Pin ConfigurationsApplicationsCDMA/GSM Cellular Handsets Battery-Powered EquipmentLaptop, Palmtops, Notebook Computers Hand-Held InstrumentsMini PCI & PCI-Express Cards PCMCIA & New CardsPortable Information Appliances1A, Ultra-Low Dropout, Ultra-Fast CMOS LDO RegulatorOrdering InformationMarking InformationFor marking information, contact our sales representative directly or through a RichTek distributor located in your area, otherwise visit our website for detail.General DescriptionThe RT9187 is a high-performance, 1A LDO regulator,offering extremely high PSRR and ultra-low dropout. Ideal for portable RF and wireless applications with demanding performance and space requirements.A noise reduction pin is also available for further reduction of output noise. Regulator ground current increases only slightly in dropout, further prolonging the battery life. The RT9187 also works with low-ESR ceramic capacitors,reducing the amount of board space necessary for power applications, critical in hand-held wireless devices.The RT9187 consumes less than 0.1μA in shutdown mode and has fast turn-on time less than 40μs. The other features include ultra-low dropout voltage, high output accuracy,current limiting protection, and high ripple rejection ratio.Available in the VDFN-8L 3x3 package.(TOP VIEW)VDFN-8L 3x3FeaturesUltra-Low-Noise for RF ApplicationUltra-Fast Response in Line/Load Transient Quick S tart-Up (Typically 40μs)< 0.1μA Standby Current When Shutdown Low Dropout : 240mV at 1AWide Operating Voltage Ranges : 2.5V to 5.5V TTL-Logic-Controlled Shutdown Input Current Limiting Protection Thermal Shutdown ProtectionOnly 2.2μF Output Capacitor Required for Stability High Power Supply Rejection RatioRoHS Compliant and 100% Lead (Pb)-FreeRT9187(Fixed Output Voltage Code 10 : 1.0V 12 : 1.2V 15 : 1.5V 18 : 1.8V 25 : 2.5V 28 : 2.8V 30 : 3.0V 33 : 3.3VVIN VOUTVOUT VIN EN BP/ADJNC GNDNote :Richtek Pb-free and Green products are :`RoHS compliant and compatible with the current require- ments of IPC/JEDEC J-STD-020.`Suitable for use in SnPb or Pb-free soldering processes.`100% matte tin (Sn) plating.Typical Application CircuitFigure 2. Adjustable OperationFigure 1. Fixed Operation Note: The value of R2 should be less than 80k tomaintain regulation.output noise.21R R 1+ VOUT= 0.8 x ( ) VoltsV V OUTV V OUTDS9187-08 August 2007Function Block DiagramENVINAbsolute Maximum Ratings (Note 1)Supply Input Voltage--------------------------------------------------------------------------------------------------6VEN Input Voltage-------------------------------------------------------------------------------------------------------6VPower Dissipation, P D @ T A= 25°CVDFN-8L 3x3-----------------------------------------------------------------------------------------------------------0.923WPackage Thermal Resistance (Note 9)VDFN-8L 3x3, θJC-----------------------------------------------------------------------------------------------------8.2°C/WVDFN-8L 3x3, θJA------------------------------------------------------------------------------------------------------108°C/WLead Temperature (Soldering, 10 sec.)---------------------------------------------------------------------------260°CJunction T emperature-------------------------------------------------------------------------------------------------150°CStorage T emperature Range----------------------------------------------------------------------------------------−65°C to 150°CESD Susceptibility (Note 2)HBM----------------------------------------------------------------------------------------------------------------------2kVMM------------------------------------------------------------------------------------------------------------------------200V Recommended Operating Conditions (Note 3)Supply Input Voltage--------------------------------------------------------------------------------------------------2.5V to 5.5VEN Input Voltage-------------------------------------------------------------------------------------------------------0V to 5.5VJunction T emperature Range----------------------------------------------------------------------------------------−40°C to 125°CAmbient T emperature Range----------------------------------------------------------------------------------------−40°C to 85°C Electrical CharacteristicsTo be continuedDS9187-08 August 2007Note 1. Stresses listed as the above “Absolute Maximum Ratings ” may cause permanent damage to the device. These are forstress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.Note 2. Devices are ESD sensitive. Handling precaution recommended.Note 3. The device is not guaranteed to function outside its operating conditions.Note 4. The dropout voltage is defined as V IN -V OUT , which is measured when V OUT is V OUT(NORMAL) - 100mV.Note 5. Regulation is measured at constant junction temperature by using a 2ms current pulse. Devices are tested for loadregulation in the load range from 10mA to 1.0A.Note 6. Quiescent, or ground current, is the difference between input and output currents. It is defined by I Q = I IN - I OUT under noload condition (I OUT = 0mA). The total current drawn from the supply is the sum of the load current plus the ground pin current.Note 7. Standby current is the input current drawn by a regulator when the output voltage is disabled by a shutdown signal (V EN>1.8V ).Note 8. Performance at -5°C ≤ T A ≤ 85°C is assured by design.Note 9. θJA is measured in the natural convection at T A = 25°C on a low effective thermal conductivity test board ofJEDEC 51-3 thermal measurement standard.Typical Operating Characteristics(C OUT = 2.2μF/x5R, C BP = 10nF, unless otherwise specified )Current LimitTime (1ms/Div)O u t p u t C u r r e n t (A )V IN = 3.3V 451203Quiescent Current vs. Temperature0100200300400500-50-25255075100125Temperature Q u i e s c e n t C u r r e n t (u A )(°C)-40Dropout Voltage vs. Load Current0501001502002503000.00.20.40.60.81.0Load Current (A)D r o p ou t V o l t a g e (m V )Quiescent Current vs. Input Voltage33.544.555.5Input Voltage (V)Q u i e s c e n t C u r r e n t (u A )O u t p u t V o l t a g e (V )E N P i n V o l t a g e (V )Time (100us/Div)EN Pin Shutdown Response V IN = 3.3V, I LOAD : 560mA 510240Start UpO u t p u t V o l t a g e (V )E N P i n V o l t a g e (V )Time (25us/Div)V IN = 3.3VI LOAD : 560mA24120DS9187-08 August 2007Load Transient RegulationTime (100us/Div)O u t p u t V o l t a g e D e v i a t i o n (m V )L o a d C u r r e n t (A )V IN = 3.3V, I LOAD : 50mA to 800mA (1A/Div)(50mV/Div)1 050-50Line Transient RegulationTime (500us/Div)I n p u t V o l t a g e D e v i a t i o n (V )O u t p u t V o l t a g e D e v i a t i o n (m V )V IN = 3.3V to 4.3V, I LOAD : 1A 3.34.3 0100-100Load Transient RegulationTime (100us/Div)O u t p u t V o l t a g e D e v i a t i o n (m V )L o a d C u r r e n t (A )V IN = 3.3V, I LOAD : 50mA to 1A 01 0100-100Line Transient RegulationTime (500us/Div)I n p u t V o l t a g e D e v i a t i o n (V )O u t p u t V o l t a g e D e v i a t i o n (m V )V IN = 3.3V to 4.3V, I LOAD : 800mA3.34.3 010-10PSRR-80-60-40-200200.00.1 1.010.0100.01000.010000.0Frequency (Hz)P S R R (d B )10 100 1k 10k 100k 1M 10MRegion of Stable C OUT ESR vs. Load Current0.0010.010.11101000.20.40.60.81Load Current (A)g i o n o f t a b l e C O UT E S R (Ω)R e g i o n o f S t a b l e C O U T E S R (Ω)Richtek Technology Corporation Headquarter5F, No. 20, Taiyuen Street, Chupei City Hsinchu, Taiwan, R.O.C.Tel: (8863)5526789 Fax: (8863)5526611Richtek Technology CorporationTaipei Office (Marketing)8F, No. 137, Lane 235, Paochiao Road, Hsintien CityTaipei County, Taiwan, R.O.C.Tel: (8862)89191466 Fax: (8862)89191465Email: marketing@V-Type 8L DFN 3x3 Package。

嵌入式系统概述(2)

ARM1ቤተ መጻሕፍቲ ባይዱE系列微处理器

ARM10E系列微处理器具有高性能、低功耗的特点,由于采用了新的体系结构,与同 等的ARM9器件相比较,在同样的时钟频率下,性能提高了近50%,同时,ARM10E系 列微处理器采用了两种先进的节能方式,使其功耗极低。 ARM10E系列微处理器的主要特点如下: 支持DSP指令集,适合于需要高速数字信号处理的场合。 6级整数流水线,指令执行效率更高。 支持32位ARM指令集和16位Thumb指令集。 支持64位的高速AMBA总线接口。 支持VFP10浮点处理协处理器。 全性能的MMU,支持Windows CE、Linux、Palm OS等多种主流嵌入式操作系统。 支持数据Cache和指令Cache,具有更高的指令和数据处理能力 主频最高可达400MIPS。 内嵌并行读/写操作部件。 ARM10E系列微处理器主要应用于下一代无线设备、数字消费品、成像设备、工业控 制、通信和信息系统等领域。 ARM10E系列微处理器包含ARM1020E、ARM1022E和ARM1026EJ-S三种类型,以适 用于不同的应用场合。

目前的ARM7和ARM9内核的芯片最大速度只能到 400MHz。目前最快的嵌入式处理器为Intel的 Xscale,最高主频为500MHz。

SecurCore系列微处理器

SecurCore系列微处理器专为安全需要而设计,提供了完善的32位 RISC技术的安全解决方案,因此,SecurCore系列微处理器除了具 有ARM体系结构的低功耗、高性能的特点外,还具有其独特的优势, 即提供了对安全解决方案的支持。 SecurCore系列微处理器除了具有ARM体系结构各种主要特点外, 还在系统安全方面具有如下的特点: 带有灵活的保护单元,以确保操作系统和应用数据的安全。 采用软内核技术,防止外部对其进行扫描探测。 可集成用户自己的安全特性和其他协处理器。

BQV 系列 军 用 FPGA 产品使用手册说明书

Ver 2.3 B Q V系列军用F P G A产品型号:BQV300/600版本控制页目录一、产品特性 (4)二、产品概述 (2)三、结构图 (2)四、引脚描述 (3)五、引脚定义 (4)六、产品描述 (4)6.1 产品模块描述 (5)6.2 边界扫描 (14)6.3 开发系统 (16)6.4 芯片配置 (22)七、电参数 (31)7.1 电试验要求 (32)7.2 绝对最大额定值 (32)7.3 推荐工作条件 (33)八、封装说明 (34)8.1 BQV300 (34)8.2 BQV600 (37)九、产品应用注意事项 (38)9.1产品应用说明 (38)9.2产品防护 (39)十、研制生产单位联系方式 (39)附录1 BQV系列FPGA电路引出端排列 (41)1. BQV300 PQ240封装引出端排列对应关系 (41)2. BQV300/BQV600 CQFP228封装引出端排列对应关系 (43)3. BQV300 BG352引出端排列对应关系 (45)一、产品特性•高速、高密度FPGA-30万/60万系统门-180MHz系统工作频率-兼容66-MHz PCI 协议-支持Compact PCI 协议热插拔•支持多种I/O接口标准-16种高性能接口标准-可直接与ZBTRAM器件相连接•内置时钟管理电路-4个专用的高级时钟控制延迟锁相环(DLLs)-4个一级low-skew全局时钟分布网络,24个二级局域时钟网络•多级存储系统-可配置为16-bit RAM, 32-bitRAM,16-bit双端口RAM或16-bit移位寄存器的LUTs-多个可配置为同步双端口的4k-bit BRAM-可实现与外部信号高速连接的高性能RAM•结构灵活,可实现速度和密度的平衡-专用的高速算术计算进位逻辑-支持专用乘法器-通过级连可实现多输入函数设计-大量带时钟使能、双重同步/异步set和reset信号的寄存器/锁存器资源-内部三态总线-支持IEEE 1149.1 边界扫描逻辑-芯片温度传感二极管•FPGA Foundation和第三方开发系统支持-完全支持联合库, 关联宏和设计管理-适合大部分PC和工作站平台•SRAM型FPGA, 支持在线系统编程-无限次重复编程-四种配置模式-0.25 μm 5 层金属工艺-100% 的工厂测试•可靠性指标-工作温度:-55℃~ +125℃-抗静电能力(人体模型):2000V-GJB597A和GJB548A-96中规定的B级•BQV系列FPGA兼容性-完全兼容于Xilinx Virtex系列FPGA-可实现管脚到管脚的替换-现有的virtex码流可以直接应用于BQV系列FPGA中,功能完全一致二、 产品概述BQV 系列FPGA 提出了一种高性能、高密度可编程逻辑的解决方案,通过优化布局布线和采用先进的5层金属0.25um 工艺,大大提高了硅片的利用率。

TISP4070H3BJ中文资料

1NOVEMBER 1997 - REVISED MARCH 1999Copyright © 1999, Power Innovations Limited, UKInformation is current as of publication date. Products conform to specifications in accordance with the terms of Power Innovations standard warranty. Production processing does notnecessarily include testing of all parameters.TELECOMMUNICATION SYSTEM 100A 10/1000 OVERVOLTAGE PROTECTORSq 8kV 10/700, 200A 5/310 ITU-T K20/21 rating qIon-Implanted Breakdown Region Precise and Stable VoltageLow Voltage Overshoot under Surgeq Rated for International Surge Wave Shapesq Low Differential Capacitance . . . 67pF max.qUL Recognized, E132482DEVICE V DRM V V (BO)V ‘40705870‘40806580‘40957595‘4125100125‘4145120145‘4165135165‘4180145180‘4200155200‘4240180240‘4265200265‘4300230300‘4350275350‘4400300400WAVE SHAPESTANDARD I TSP A 2/10µs GR-1089-CORE5008/20µs IEC 61000-4-530010/160µs FCC Part 6825010/700µs ITU-T K20/2120010/560µs FCC Part 6816010/1000µsGR-1089-CORE100descriptionThese devices are designed to limit overvoltages on the telephone line. Overvoltages are normally caused by a.c. power system or lightning flash disturbances which are induced or conducted on to the telephone line. A single device provides 2-point protection and is typically used for the protection of 2-wire telecommunication equipment (e.g. between the Ring and Tip wires for telephones and modems). Combinations of devices can be used for multi-point protection (e.g. 3-point protection between Ring, Tip and Ground).The protector consists of a symmetrical voltage-triggered bidirectional thyristor. Overvoltages are initially clipped by breakdown clamping until the voltage rises to the breakover level, which causes the device to crowbar into a low-voltage on state. This low-voltage on state causes the current resulting from the overvoltage to be safely diverted through the device. The high crowbar holding current prevents d.c. latchup as the diverted current subsides.2NOVEMBER 1997 - REVISED MARCH 1999This TISP4xxxH3BJ range consists of thirteen voltage variants to meet various maximum system voltage levels (58V to 275V). They are guaranteed to voltage limit and withstand the listed international lightning surges in both polarities. These high (H) current protection devices are in a plastic package SMBJ (JEDEC DO-214AA with J-bend leads) and supplied in embossed carrier reel pack. For alternative voltage and holding current values, consult the factory. For lower rated impulse currents in the SMB package, the 50A 10/1000TISP4xxxM3BJ series is available.absolute maximum ratings, T A = 25°C (unless otherwise noted)RATINGSYMBOLVALUE UNITRepetitive peak off-state voltage, (see Note 1)‘4070‘4080‘4095‘4125‘4145‘4165‘4180‘4200‘4240‘4265‘4300‘4350‘4400V DRM ± 58± 65± 75±100±120±135±145±155±180±200±230±275±300V Non-repetitive peak on-state pulse current (see Notes 2, 3 and 4)I TSPA2/10µs (GR-1089-CORE, 2/10µs voltage wave shape)5008/20µs (IEC 61000-4-5, 1.2/50µs voltage, 8/20 current combination wave generator)30010/160µs (FCC Part 68, 10/160µs voltage wave shape)2505/200µs (VDE 0433, 10/700µs voltage wave shape)2200.2/310µs (I3124, 0.5/700µs voltage wave shape)2005/310µs (ITU-T K20/21, 10/700µs voltage wave shape)2005/310µs (FTZ R12, 10/700µs voltage wave shape)20010/560µs (FCC Part 68, 10/560µs voltage wave shape)16010/1000µs (GR-1089-CORE, 10/1000µs voltage wave shape)100Non-repetitive peak on-state current (see Notes 2, 3 and 5)I TSM55602.1A20ms (50Hz) full sine wave 16.7ms (60Hz) full sine wave 1000s 50Hz/60Hz a.c.Initial rate of rise of on-state current,Exponential current ramp, Maximum ramp value <200 Adi T /dt 400A/µs Junction temperature T J -40 to +150°C Storage temperature range T stg -65 to +150°C NOTES:1.See Applications Information and Figure 10 for voltage values at lower temperatures.2.Initially the TISP4xxxH3BJ must be in thermal equilibrium with T J =25°C.3.The surge may be repeated after the TISP4xxxH3BJ returns to its initial conditions.4.See Applications Information and Figure 11 for current ratings at other temperatures.5.EIA/JESD51-2 environment and EIA/JESD51-3 PCB with standard footprint dimensions connected with 5A rated printed wiring track widths. See Figure 8 for the current ratings at other durations. Derate current values at -0.61%/°C for ambient temperatures above 25°C3NOVEMBER 1997 - REVISED MARCH 1999electrical characteristics for the T and R terminals, T A = 25°C (unless otherwise noted)P ARAMETERTEST CONDITIONSMINTYPMAX UNIT I DRMRepetitive peak off-state currentV D = V DRMT A = 25°C T A = 85°C±5±10µAV (BO)Breakover voltagedv/dt =±750V/ms,R SOURCE =300Ω‘4070‘4080‘4095‘4125‘4145‘4165‘4180‘4200‘4240‘4265‘4300‘4350‘4400±70±80±95±125±145±165±180±200±240±265±300±350±400V V (BO)Impulse breakover voltagedv/dt ≤±1000V/µs, Linear voltage ramp,Maximum ramp value =±500V di/dt =±20A/µs, Linear current ramp, Maximum ramp value =±10A‘4070‘4080‘4095‘4125‘4145‘4165‘4180‘4200‘4240‘4265‘4300‘4350‘4400±78±88±103±134±154±174±189±210±250±276±311±362±413V I (BO)Breakover current dv/dt =±750V/ms,R SOURCE =300Ω±0.15±0.6A V T On-state voltage I T =±5A,t W =100µs ±3V I H Holding current I T =±5A, di/dt =+/-30mA/ms±0.15±0.6A dv/dt Critical rate of rise of off-state voltage Linear voltage ramp, Maximum ramp value <0.85V DRM ±5kV/µs I DOff-state currentV D =±50V T A = 85°C±10µA C offOff-state capacitancef =100kHz,V d =1V rms,V D =0,f =100kHz,V d =1V rms,V D =-1Vf =100kHz,V d =1V rms,V D =-2Vf =100kHz,V d =1V rms,V D =-50Vf =100kHz,V d =1V rms,V D =-100V(see Note 6)‘4070 thru ‘4095‘4125 thru ‘4200‘4240 thru ‘4400‘4070 thru ‘4095‘4125 thru ‘4200‘4240 thru ‘4400‘4070 thru ‘4095‘4125 thru ‘4200‘4240 thru ‘4400‘4070 thru ‘4095‘4125 thru ‘4200‘4240 thru ‘4400‘4125 thru ‘4200‘4240 thru ‘440014580701307160120655562302428221709084150796714074627335283326pFNOTE6:T o avoid possible voltage clipping, the ‘4125 is tested with V D =-98V .4NOVEMBER 1997 - REVISED MARCH 1999thermal characteristicsPARAMETERTEST CONDITIONSMINTYPMAX UNITR θJAJunction to free air thermal resistanceEIA/JESD51-3 PCB, I T = I TSM(1000),T A = 25°C, (see Note 7)113°C/W 265mm x 210mm populated line card, 4-layer PCB, I T = I TSM(1000), T A = 25°C50NOTE7: EIA/JESD51-2 environment and PCB has standard footprint dimensions connected with 5A rated printed wiring track widths.PARAMETER MEASUREMENT INFORMATIONFigure 1. VOLTAGE-CURRENT CHARACTERISTIC FOR T AND R TERMINALSALL MEASUREMENTS ARE REFERENCED TO THE R TERMINAL-vV DRM I DRMV D I HI T V TI TSMI TSPV (BO)I (BO)I DQuadrant ISwitching Characteristic+v+i V (BO)I (BO)V DI DI HI TV TI TSMI TSP-iQuadrant IIISwitching CharacteristicPMXXAABV DRMI DRM56NOVEMBER 1997 - REVISED MARCH 1999 RATING AND THERMAL INFORMATION78NOVEMBER 1997 - REVISED MARCH 1999APPLICATIONS INFORMATIONdeploymentThese devices are two terminal overvoltage protectors. They may be used either singly to limit the voltage between two conductors (Figure 12) or in multiples to limit the voltage at several points in a circuit (Figure 13).In Figure 12, protector Th1 limits the maximum voltage between the two conductors to ±V (BO). This configuration is normally used to protect circuits without a ground reference, such as modems. In Figure 13,protectors Th2 and Th3 limit the maximum voltage between each conductor and ground to the ±V (BO) of the individual protector. Protector Th1 limits the maximum voltage between the two conductors to its ±V (BO)value. If the equipment being protected has all its vulnerable components connected between the conductors and ground, then protector Th1 is not required.impulse testingT o verify the withstand capability and safety of the equipment, standards require that the equipment is tested with various impulse wave forms. The table below shows some common values.If the impulse generator current exceeds the protectors current rating then a series resistance can be used to reduce the current to the protectors rated value and so prevent possible failure. The required value of series resistance for a given waveform is given by the following calculations. First, the minimum total circuit impedance is found by dividing the impulse generators peak voltage by the protectors rated current. The impulse generators fictive impedance (generators peak voltage divided by peak short circuit current) is then subtracted from the minimum total circuit impedance to give the required value of series resistance. In some cases the equipment will require verification over a temperature range. By using the rated waveform values from Figure 11, the appropriate series resistor value can be calculated for ambient temperatures in the range of -40°C to 85°C.Figure 12. TWO POINT PROTECTION Figure 13. MULTI-POINT PROTECTIONSTANDARDPEAK VOLTAGESETTINGVVOLTAGE WAVE FORMµs PEAK CURRENTVALUE A CURRENT WAVE FORMµs TISP4xxxH325°C RATINGA SERIES RESISTANCEΩGR-1089-CORE25002/105002/105000100010/100010010/1000100FCC Part 68(March 1998)150010/16020010/160250080010/56010010/560160015009/720†37.55/320†200010009/720†255/320†2000I312415000.5/70037.50.2/3102000ITU-T K20/K211500400010/70037.51005/310200† FCC Part 68 terminology for the waveforms produced by the ITU-T recommendation K21 10/700 impulse generatorTh1Th3Th2Th19NOVEMBER 1997 - REVISED MARCH 1999a.c. power testingThe protector can withstand currents applied for times not exceeding those shown in Figure 8. Currents that exceed these times must be terminated or reduced to avoid protector failure. Fuses, PTC (Positive T emperature Coefficient) resistors and fusible resistors are overcurrent protection devices which can be used to reduce the current flow. Protective fuses may range from a few hundred milliamperes to one ampere. In some cases it may be necessary to add some extra series resistance to prevent the fuse opening during impulse testing. The current versus time characteristic of the overcurrent protector must be below the line shown in Figure 8. In some cases there may be a further time limit imposed by the test standard (e.g. UL 1459 wiring simulator failure).capacitanceThe protector characteristic off-state capacitance values are given for d.c. bias voltage, V D , values of 0, -1V , -2V and -50V . Where possible values are also given for -100V . Values for other voltages may be calculated by multiplying the V D =0 capacitance value by the factor given in Figure 6. Up to 10MHz the capacitance is essentially independent of frequency. Above 10MHz the effective capacitance is strongly dependent on connection inductance. In many applications, such as Figure 15 and Figure 17, the typical conductor bias voltages will be about -2V and -50V . Figure 7 shows the differential (line unbalance) capacitance caused by biasing one protector at -2V and the other at -50V .normal system voltage levelsThe protector should not clip or limit the voltages that occur in normal system operation. For unusual conditions, such as ringing without the line connected, some degree of clipping is permissible. Under this condition about 10V of clipping is normally possible without activating the ring trip circuit.Figure 10 allows the calculation of the protector V DRM value at temperatures below 25°C. The calculated value should not be less than the maximum normal system voltages. The TISP4265H3BJ, with a V DRM of 200V , can be used for the protection of ring generators producing 100V rms of ring on a battery voltage of -58V (Th2 and Th3 in Figure 17). The peak ring voltage will be 58+1.414*100 = 199.4V . However, this is the open circuit voltage and the connection of the line and its equipment will reduce the peak voltage. In the extreme case of an unconnected line, clipping the peak voltage to 190V should not activate the ring trip. This level of clipping would occur at the temperature when the V DRM has reduced to 190/200 = 0.95 of its 25°C value. Figure 10 shows that this condition will occur at an ambient temperature of -22°C. In this example, the TISP4265H3BJ will allow normal equipment operation provided that the minimum expected ambient temperature does not fall below -22°C.JESD51 thermal measurement methodT o standardise thermal measurements, the EIA (Electronic Industries Alliance) has created the JESD51standard. Part 2 of the standard (JESD51-2, 1995) describes the test environment. This is a 0.0283m 3 (1ft 3)cube which contains the test PCB (Printed Circuit Board) horizontally mounted at the centre. Part 3 of the standard (JESD51-3, 1996) defines two test PCBs for surface mount components; one for packages smaller than 27mm on a side and the other for packages up to 48mm. The SMBJ measurements used the smaller 76.2mm x 114.3mm (3.0“x 4.5“) PCB. The JESD51-3 PCBs are designed to have low effective thermal conductivity (high thermal resistance) and represent a worse case condition. The PCBs used in the majority of applications will achieve lower values of thermal resistance and so can dissipate higher power levels than indicated by the JESD51 values.10NOVEMBER 1997 - REVISED MARCH 1999typical circuitsFigure 14. MODEM INTER-WIRE PROTECTION Figure 15. PROTECTION MODULEFigure 16. ISDN PROTECTIONFigure 17. LINE CARD RING/TEST PROTECTIONFUSETISP4350AI6XBMA RING DETECTOR HOOK SWITCHD.C. SINK SIGNALMODEMRINGTIPR1aR1bRING WIRETIP WIRETh3Th2Th1PROTECTED EQUIPMENT E.G. LINE CARDAI6XBKR1aR1bTh3Th2Th1AI6XBLSIGNALD.C.MECHANICAL DATASMBJ (DO-214AA)plastic surface mount diode packageThis surface mount package consists of a circuit mounted on a lead frame and encapsulated within a plastic compound. The compound will withstand soldering temperature with no deformation, and circuit performance characteristics will remain stable when operated in high humidity conditions. Leads require no additional cleaning or processing when used in soldered assembly.MECHANICAL DATAdevice symbolization codeDevices will be coded as below. As the device parameters are symmetrical, terminal 1 is not identified.carrier informationDevices are shipped in one of the carriers below. Unless a specific method of shipment is specified by the customer, devices will be shipped in the most practical carrier. For production quantities the carrier will be embossed tape reel pack. Evaluation quantities may be shipped in bulk pack or embossed tape.DEVICE SYMOBLIZATIONCODE TISP4070H3BJ 4070H3TISP4080H3BJ 4080H3TISP4095H3BJ 4095H3TISP4125H3BJ 4125H3TISP4145H3BJ 4145H3TISP4165H3BJ 4165H3TISP4180H3BJ 4180H3TISP4200H3BJ 4200H3TISP4240H3BJ 4240H3TISP4265H3BJ 4265H3TISP4300H3BJ 4300H3TISP4350H3BJ 4350H3TISP4400H3BJ4400H3CARRIERORDER #Embossed T ape Reel PackTISP4xxxH3BJR Bulk PackTISP4xxxH3BJMECHANICAL DATAIMPORTANT NOTICEPower Innovations Limited (PI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to verify, before placing orders, that the information being relied on is current.PI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with PI's standard warranty. T esting and other quality control techniques are utilized to the extent PI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.PI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor is any license, either express or implied, granted under any patent right, copyright, design right, or other intellectual property right of PI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.PI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORISED, OR WARRANTED TO BE SUIT ABLE FOR USE IN LIFE-SUPPORT APPLICA TIONS, DEVICES OR SYSTEMS.Copyright © 1999, Power Innovations Limited。

66572资料

April 1996NEC Electronics Inc.A10616EU1V0DS00CMOS-8LHD3.3-Volt, 0.5-Micron CMOS Gate ArraysPreliminary DescriptionNEC's CMOS-8LHD gate-array family combines cell-based-level densities with the fast time-to-market and low development costs of gate arrays. With a unique heterogeneous cell architecture, CMOS-8LHD provides the very dense logic and RAM capabilities required to build devices for fast computer and communications systems.NEC delivers high-speed, 0.5-micron, drawn gate length (Leff=0.35-micron), three-level metal, CMOS technology with an extensive family of macros. I/O macros include GTL, HSTL, and pECL. TTL CMOS I/Os are provided with 5-V tolerance for applications requiring interface to 5-V logic. PCI signaling standards are also supported,including 3.3-V, 66 MHz PCI. The technology is enhanced by a set of advanced features, including phase-locked loops, clock tree synthesis, and high-speed memory. The CMOS-8LHD gate-array family of 3.3-V devices consists of 12 masters, offered in densities of 75K raw gates to 1.123 million raw gates. Usable gates range from 45K to 674K used gates.The gate-array family is supported by NEC's OpenCAD ®design system, a mixture of popular third-party EDA tools,and proprietary NEC tools. NEC proprietary tools include the GALET floorplanner, which helps to reduce design time and improve design speed, and a clock tree synthesis tool that automatically builds a balanced-buffer clock tree to minimize on-chip clock skew.Figure 1. CMOS-8LHD Package Options: BGA & QFPTable 1. CMOS-8LHD Family Features and BenefitsCMOS-8LHD ApplicationsThe CMOS-8LHD family is ideal for use in personal computer systems, engineering workstations, and telecommunications switching and transmission systems, where extensive integration and high speeds are primary design goals. With power dissipation of 0.21 µW/MHz/gate, CMOS-8LHD is also suited for lower-power applications where high performance is required.OpenCAD is a registered trademark of NEC Electronics Inc.CMOS-8LHD2Cell-Based Array ArchitectureThe CMOS-8LHD gate-array family is built with the Cell-Based Array (CBA) architecture licensed from the Silicon Architects Group of Synopsys. CBA architecture uses two types of cells: compute cells and drive cells.This heterogeneous cell architecture enables very high-density design. Compute cells are used to optimize intramacro logic. Drive cells are optimized for intermacro interconnect. The two cell types are also used to build macros with up to three different power/performance/area points.CBA has a rich macrocell library that is optimized for synthesis. RAM blocks are efficiently created from the CBA architecture, using compute cells as memory cores, and sense amplifiers and drive cells as word and address predecoder drivers.As shown in Figure 2, CBA is divided into I/O and array regions. The I/O region contains input and output buffers. The array region contains the gates used to build logic, RAM blocks, and other design features.Power Rail ArchitectureCMOS-8LHD provides additional flexibility for mixedvoltage system designs. As shown in Figure 2, the arrays contain two power rails: a 3.3-V rail, and V DD2.The V DD2 rail is used for interfaces such as 5-V PCI buffers where a clamping diode allows protection for up to an 11-V voltage spike, per the PCI revision 2.1specification.Figure 2. CBA Layout and Cell ConfigurationThe V DD2 rail is separated into sections to give flexibility for including two or more buses requiring special I/O voltage on one device. Each section can operate as an independent voltage zone, and sections can be linked together to form common voltage zones.Packaging and TestNEC utilizes BIST test structures for RAM testing. NEC also offers advanced packaging solutions including Plastic Ball Grid Arrays (PBGA), Plastic Quad Flat Packs (PQFP), and Pin Grid Arrays (PGA). Please call your local NEC ASIC design center representative for a listing of available master/package combinations.PublicationsThis data sheet contains preliminary specifications for the CMOS-8LHD gate-array family. Additional infor-mation will be available in NEC's CMOS-8LHD Block Library and CMOS-8LHD Design Manual . Call your local NEC ASIC design center representative or the NEC literature line for additional ASIC design information; see the back of this data sheet for locations and phone numbers.Table 2. CMOS-8LHD Base Array Line-upDevice Raw Gates Used Gates (1)Total Pads66562750404502416466563997925987518866565125216751292126656617963210777925266568202400121440268665692681281608763086657029792017875232466571359744215845356665725008643005184206657362054437232646866575802240481344532(1) Actual gate utilization varies depending on circuit implementation.Utilization is 60% for 3LM.3CMOS-8LHDInput/Output CapacitanceV DD =V I =0-V; f =1 MHzTerminal Symbol Typ Max Unit Input C IN 1020pF Output C OUT 1020pF I/OC I/O1020pF(1)Values include package pin capacitancePower ConsumptionDescription Limits Unit Internal gate (1)0.21µW/MHz Input buffer 2.546µW/MHz Output buffer10.60µW/MHzAbsolute Maximum RatingsPower supply voltage, V DD –0.5 to +4.6-VInput voltage, V I3.3-V input buffer (at V I < V DD + 0.5-V)–0.5 to +4.6-V 3.3-V fail-safe input buffer (at V I < V DD + 0.5-V)–0.5 to +4.6-V 5 V-tolerant (at V I < V DD + 3.0-V)–0.5 to +4.6-V Output Voltage, V O3.3-V output buffer (at V O < V DD + 0.5-V)–0.5 to +4.6-V 5-V-tolerant output buffer (at V O < V DD + 3.0-V)–0.5 to +4.6-V 5-V open-drain output buffer (at V O < V DD + 3.0-V)–0.5 to +4.6-VLatch-up current, I LATCH >1 A (typ)Operating temperature, T OPT –40 to +85°C Storage temperature, T STG–65 to +150°C (1) Assumes 30% internal gate switching at one timeCaution: Exposure to absolute maximum ratings for extended periods may affect device reliability; exceeding the ratings could cause permanent damage. The device should not be operated outside the recommended operating conditions.Recommended Operating ConditionsV DD = 3.3-V ±0.165-V; T j = 0 to +100°C3.3-V Interface 5-V Interface5-V PCI 3.3-V PCIBlock BlockLevel LevelParameterSymbol Min Max Min Max Min Max Min Max Unit I/O power supply voltage V DD 3.0 3.6 3.0 3.6 3.0 5.5 3.0 3.6V Junction temperature T J 0+1000+1000+1000+100°C High-level input voltage V IH 2.0V DD 2.0 5.5 2.0V CC 0.5 V CCV CC V Low-level input voltage V IL 00.800.800.800.3 V CCV Positive trigger voltage V P 1.50 2.70 1.50 2.70————V Negative trigger voltage V N 0.60 1.60.60 1.6————V Hysteresis voltage V H 1.10 1.3 1.10 1.3————V Input rise/fall time t R , t F 0200020002000200ns Input rise/fall time, Schmittt R , t F1010————nsAC CharacteristicsV DD = 3.3-V ±0.3-V; T j = –40 to +125°C ParameterSymbol MinTypMax Unit Conditions Toggle frequency (F611)f TOG356MHzD-F/F; F/O = 2 mmDelay time2-input NAND (F322)t PD181ps F/O = 1; L = 0 mmt PD 186ps F/O = 2; L = typ (0.42 mm)Flip-flop (F611)t PD 573ps F/O = 1; L = 0 mm t PD 688ps F/O = 2; L = typ t SETUP 410ps —t HOLD 540ps —Input buffer (FI01)t PD 268ps F/O = 1; L = 0 mm t PD 312ps F/O = 2; L = typ Output buffer (9 mA) 3.3-V (FO01)t PD 1.316ns C L = 15 pF Output buffer (9 mA) 5-V-tolerant (FV01)t PD 1.228ns C L = 15 pF Output buffer (9 mA) 5-V-swing (FY01)t PD 1.517ns C L = 15 pF Output rise time (9 mA) (FO01)t R 1.347ns C L = 15 pF Output fall time (9 mA) (FO01)t F1.284nsC L = 15 pFCMOS-8LHD4(3)Rating is for only one output operating in this mode for less than 1 second.(4)Normal type buffer: I OH < I OL .(5)Balanced buffer: I OH = I OL .(6)Resistor is called 50ký to maintain consistency with previous families.Notes:(1)Static current consumption increases if an I/O block with on-chip pull-up/pull-down resistor or an oscillator is used. Call an NEC ASIC design center repre-sentative for assistance in calculation.(2)Leakage current is limited by tester capabilities. Specification listed representsthis measurement limitation. Actual values will be significantly lower.DC CharacteristicsV DD = 3.3-V ±0.165-V; T j = 0 to +100°C ParameterSymbol Min Typ Max Unit Conditions Quiescent current (1)µPD66578I DDS 2.0300µA V I = V DD or GND µPD66575, 66573, 66572I DDS 1.0300µA V I = V DD or GND Remaining mastersI DDS 0.5200µA V I = V DD or GND Off-state output leakage current3.3-V buffers, 3.3-V PCII OZ ±10µA V O = V DD or GND 5-V-tolerant buffers, 5-V PCI I OZ ±14µA V O = V DD or GND 5-V open-drainI OZ ±14µA V O = V DD or GND Output short circuit current (3)I OS –250mA V O = GND Input leakage current (2)5-V PCI I IH +70, –70µA V IN = 2.7-V, 0.5-V 3.3-V PCI I I ±10µA V IN = V DD or GND RegularI I ±10–5±10µA V I = V DD or GND 50 k Ω pull-up I I –180–40µA V I = GND 5 k Ω pull-up I I –1400–350mA V I = GND 50 k Ω pull-down I I 30160µA V I = V DDResistor values50 k Ω pull-up (6)R pu 2075k Ω5 k Ω pull-upR pu 2.68.6k Ω50 k Ω pull-down (6)R pu 22.5100k ΩInput clamp voltageV IC –1.2V I I = 18 mA Low-level output current (ALL buffer types)3 mA I OL 3mA V OL = 0.4-V 6 mA I OL 6mA V OL = 0.4-V 9 mA I OL 9mA V OL = 0.4-V 12 mA I OL 12mA V OL = 0.4-V 18 mA I OL 18mA V OL = 0.4-V 24 mAI OL 24mA V OL = 0.4-V High-level output current (5-V-tolerant block)3 mA I OH –3mA V OH = V DD –0.4-V 6 mA I OH –3mA V OH = V DD –0.4-V 9 mA I OH –3mA V OH = V DD –0.4-V 12 mA I OH –3mA V OH = V DD –0.4-V 18 mA I OH –4mA V OH = V DD –0.4-V 24 mAI OH –4mA V OH = V DD –0.4-V High-level output current (3.3-V interface block)3 mA I OH –3mA V OH = V DD –0.4-V 6 mA I OH –6mA V OH = V DD –0.4-V 9 mA I OH –9mA V OH = V DD –0.4-V 12 mA I OH –12mA V OH = V DD –0.4-V 18 mA I OH -18mA V OH = V DD –0.4-V 24 mAI OH -24mA V OH = V DD –0.4-V Output voltage (5-V PCI)High-level output voltage V OH 2.4mA I OH = 2 mALow-level output voltage V OL 0.55mA I OL = 3 mA, 6 mA Output voltage (3.3-V PCI)High-level output voltage V OH 0.9 V DDmA I OH = 500 µA Low-level output voltage V OL 0.1 V DDmA I OL = 1500 µA Low-level output voltageV OL 0.1V I OL = 0 mA High-level output voltage, 5-V TTL V OH V DD –0.2V I OL = 0 mA High-level output voltage, 3.3-VV OHV DD –0.1VI OH = 0 mACMOS-8LHD5CMOS-8LHD6Document No. A10616EU1V0DS00For literature, call toll-free 7 a.m. to 6 p.m. Pacific time: 1-800-366-9782or FAX your request to: 1-800-729-9288©1996 NEC Electronics Inc./Printed in U.S.A.NEC ASIC DESIGN CENTERSWEST•3033 Scott Boulevard Santa Clara, CA 95054TEL 408-588-5008FAX 408-588-5017•One Embassy Centre9020 S.W. Washington Square Road,Suite 400Tigard, OR 97223TEL 503-671-0177FAX 503-643-5911THIRD-PARTY DESIGN CENTERSSOUTH CENTRAL/SOUTHEAST•Koos Technical Services, Inc.385 Commerce Way, Suite 101Longwood, FL 32750TEL 407-260-8727FAX 407-260-6227•Integrated Silicon Systems Inc.2222 Chapel Hill Nelson Highway Durham, NC 27713TEL 919-361-5814FAX 919-361-2019•Applied Systems, Inc.1761 W. Hillsboro Blvd., Suite 328Deerfield Beach, FL 33442TEL 305-428-0534FAX 305-428-5906NEC Electronics Inc.CORPORATE HEADQUARTERS2880 Scott Boulevard P.O. Box 58062Santa Clara, CA 95052TEL 408-588-6000No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics Inc. (NECEL). The information in this document is subject to change without notice. ALL DEVICES SOLD BY NECEL ARE COVERED BY THE PROVISIONS APPEARING IN NECEL TERMS AND CONDITIONS OF SALES ONLY. INCLUDING THE LIMITATION OF LIABILITY,WARRANTY, AND PATENT PROVISIONS. NECEL makes no warranty, express, statutory, implied or by description, regarding informa-tion set forth herein or regarding the freedom of the described devices from patent infringement. NECEL assumes no responsibility for any errors that may appear in this document. NECEL makes no commitments to update or to keep current information contained in this document. The devices listed in this document are not suitable for use in applications such as, but not limited to, aircraft control systems,aerospace equipment, submarine cables, nuclear reactor control systems and life support systems. “Standard” quality grade devices are recommended for computers, office equipment, communication equipment, test and measurement equipment, machine tools,industrial robots, audio and visual equipment, and other consumer products. For automotive and transportation equipment, traffic control systems, anti-disaster and anti-crime systems, it is recommended that the customer contact the responsible NECEL salesperson to determine the reliabilty requirements for any such application and any cost adder. NECEL does not recommend or approve use of any of its products in life support devices or systems or in any application where failure could result in injury or death.If customers wish to use NECEL devices in applications not intended by NECEL, customer must contact the responsible NECEL sales people to determine NECEL’s willingness to support a given application.SOUTH CENTRAL/SOUTHEAST•16475 Dallas Parkway, Suite 380Dallas, TX 75248TEL 972-735-7444FAX 972-931-8680•Research Triangle Park2000 Regency Parkway, Suite 455Cary, NC 27511TEL 919-460-1890FAX 919-469-5926•Two Chasewood Park 20405 SH 249, Suite 580Houston, TX 77070TEL 713-320-0524FAX 713-320-0574NORTH CENTRAL/NORTHEAST•The Meadows, 2nd Floor 161 Worcester Road Framingham, MA 01701TEL 508-935-2200FAX 508-935-2234•Greenspoint Tower2800 W. Higgins Road, Suite 765Hoffman Estates, IL 60195TEL708-519-3945FAX 708-882-7564。

Vigor2920 系

Vigor2920 系列雙WAN安全防護路由器快速安裝手冊版本: 1.0韌體版本: V3.3.3.1日期: 19/07/2010因手冊更新無法及時通知用戶,請隨時連上居易網站,取得最新的手冊內容。

版權資訊版權聲明© 2010版權所有,翻印必究。

此出版物所包含資訊受版權保護。

未經版權所有人書面許可,不得對其進行拷貝、傳播、轉錄、摘錄、儲存到檢索系統或轉譯成其他語言。

交貨以及其他詳細資料的範圍若有變化,恕不預先通知。

商標本手冊內容使用以下商標:z Microsoft為微軟公司註冊商標z Windows視窗系列,包括Windows 95, 98, Me, NT, 2000, XP 以及其Explorer均屬微軟公司商標z Apple以及Mac OS均屬蘋果電腦公司的註冊商標z其他產品則為各自生產廠商之註冊商標安全說明和保障安全說明z在設置前請先閱讀安裝說明。

z由於路由器是複雜的電子產品,請勿自行拆除或是維修本產品。

z請勿自行打開或修復路由器。

z請勿把路由器置於潮濕的環境中,例如浴室。

z請將本產品放置在足以遮風避雨之處,適合溫度在攝氏5度到40度之間。

z請勿將本產品暴露在陽光或是其他熱源下,否則外殼以及零件可能遭到破壞。

z請勿將LAN網線置於戶外,以防電擊危險。

z請將本產品放置在小孩無法觸及之處。

z若您想棄置本產品時,請遵守當地的保護環境的法律法規。

保固自使用者購買日起二年內為保固期限,請將您的購買收據保存二年,因為它可以證明您的購買日期。

當本產品發生故障乃導因於製作及(或)零件上的錯誤,只要使用者在保固期間內出示購買證明,居易科技將採取可使產品恢復正常之修理或更換有瑕疵的產品(或零件),且不收取任何費用。

居易科技可自行決定使用全新的或是同等價值且功能相當的再製產品。

下列狀況不在本產品的保固範圍內:(1)若產品遭修改、錯誤(不當)使用、不可抗力之外力損害,或不正常的使用,而發生的故障;(2) 隨附軟體或是其他供應商提供的授權軟體;(3) 未嚴重影響產品堪用性的瑕疵。

Mellanox 高速低成本 DAC 电缆说明书

Mellanox® MCP1600-E0xxEyy DAC cables are high speed, cost-effective alternatives to fiber optics inInfiniBand 100Gb/s EDR applications.Mellanox QSFP28 passive copper cables(1) contain four high-speed copper pairs, each operating at datarates of up to 25Gb/s. Each QSFP28 port comprises an EEPROM providing product information, which canbe read by the host system.Mellanox’s unique quality passive copper cable solutions provide power-efficient connectivity for shortdistance interconnects. It enables higher port bandwidth, density and configurability at a low cost andreduced power requirement in the data centers.Rigorous cable production testing ensures best out-of-the-box installation experience, performance anddurability.T able 1 - Absolute Maximum RatingsT able 2 - Operational SpecificationsT able 3 - Electrical SpecificationsMCP1600-E0xxEyyINTERCONNECTPRODUCT BRIEF†100Gb/s QSFP28 Direct Attach Copper Cable(1)Raw cables are provided from different sources to ensure supply chain robustness.©2018 Mellanox Technologies. All rights reserved.†For illustration only. Actual products may vary.©2018 Mellanox Technologies. All rights reserved.Table 4 - Cable Mechanical SpecificationsNote 1. The minimum assembly bending radius (close to the connector) is 10x the cable’s outer diameter. The repeated bend (far from the connector) is also 10x the cable’s outer diameter. The single bend (far from the connector) is 5x the cable’s outer diameter.Table 5 - Part Numbers and DescriptionsNote. See Figure 2 for the cable length definition. Note 2. xx = reach; yy = wire gauge.Figure 2.Cable Length DefinitionFigure 1.Assembly Bending Radius350 Oakmead Parkway, Suite 100, Sunnyvale, CA 94085Tel: 408-970-3400 • Fax: © Copyright 2018. Mellanox Technologies. All rights reserved.Mellanox, Mellanox logo and LinkX are registered trademarks of Mellanox Technologies, Ltd. All other trademarks are property of their respective owners.Warranty InformationMellanox LinkX direct attach copper cables include a 1-year limited hardware warranty, which covers parts repair or replacement.Mechanical Schematics60111PBRev 2.5。

CHIMEI 27VH LED Backlit Monitor Quick 说明书

LED Backlit Monitor Quick Guide27VHAUTO MENUThis LED backlit monitor has been already approved by safety certification agencies inright, and you should use it according to the user manual, please.本产品的各项性能均已通过右列各项规范认证,请您依照操作说明安心使用本产品。

本產品各項性能均已通過右列各項規範認證,請您依照操作說明安心使用本產品。

部件名称有毒有害物质或元素铅(Pb)汞(Hg)镉(Cd)六价铬(Cr 6+)多溴联苯(PBB)多溴二苯醚(PBDE)外壳○○○○○○液晶显示屏/灯管×○○○○○电路板组件*×○○○○○电源线/电源适配器×○○○○○液晶面板×○○○○○*:电路板组件包括印刷电路板及其构成的零部件,如电阻、电容、集成电路、连接器等○: 表示该有毒有害物质在该部件所有均质材料中的含量均在SJ/T11363-2006标准规定的限量要求以下×: 表示该有毒有害物质在该部件的某一均质材料中的含量超出SJ/T11363-2006标准规定的限量要求;其含量超出是因为目前业界尚无成熟可替代的技术,但仍然符合欧盟RoHS 指令的豁外条款允许范围Package Contents◆The LED backlit monitor and the stand.AUTO MENUAccessoryAll of accessories have been tested and qualified. Do not use any non-qualified accessories with this LED backlit monitor.◆Power Cord.◆ 15-pin D-Sub Signal Cable.◆Audio Cable.◆ DVI Signal Cable. (Optional)◆HDMI Cable. (Optional)◆User Manual (CD-ROM).◆ Quick Guide.◆ Warranty Card. (Optional)Features◆68.6cm ( 27” ) TFT Color LED backlit monitor.◆Supports Resolutions up to 1920 x 1080.Using the CD-ROMCD-ROM ContentsInsert the CD-ROM into your computer’s CD-ROM drive, and it will display automatically.◆User Manual (3 Languages).◆Acrobat Reader® Installation.Note: Some files are shown as the type of Acrobat® PDF.Safety PrecautionsCaution:This LED backlit monitor must be operated with the original accessories.◆This set must be operated with the correct power supply.◆Do not let children use this LED backlit monitor alone.◆Viewing the User Manual for other safety precautions.Quick SetupThe setup steps are described as following: (Step 2 to 4 are illustrated on the overleaf of the cover.)1. Shutdown your computer and unplug.2. Please combine the LED backlit monitor with the stand tightly.3. Connect the 15-pin D-Sub (or DVI-D, HDMI optional)signal cable and Audio cable to the computer and the LED backlit monitor.4. Connect the LED backlit monitor power cord to AC power input socket firmly and completely.5. Use the cable tie to bind up the power cord and the D-sub signal cable/ DVI-D cable/HDMI cable.6. After installation, please turn on the LED backlit monitor and the computer, respectively.7. About function adjustment and troubleshooting, please refer to the content of the CD-ROM.Service (For European service, please refer to the warranty card.)Please contact the following local service telephone:New Zealand ZCOM COMPUTERS LTD Telephone : +64 9 5800222Website : Heima New Zealand Ltd Telephone : +64 9 535-7067Israel PSDS Enterprises LTD Telephone : +972 5282-81602Website : http://www.ksp.co.il Korea Erecta Co.LTD Telephone : +82 2 707 1240MalaysiaVISMART SENDIRIAN BERHAD Telephone : +60 3 79586688Website : .my BangladeshEJU Audio & VideoTelephone : +880-2-9128293NepalCompany: Sagar InfoSysOm Bahal, Newroad, Kathmandu, Nepal Website: .npTel No.: +977(1)-4233618/4245160/4221157 Support Centre: Sagar Customer Care. Direct Call: +977(1)-4245160/ 6218898 (10:00am – 6:00pm)BENDA MAGNETIC LTD Telephone : +972-9864-4621Website : http://www.benda.co.il Philippines PC Trends,IncTelephone : (632)725-7823 ; 727-6 Website : .ph IndonesiaPT Bintang Mas Razeki Nusantara Telephone : +62 21 6264750产品内容◆ LED背光液晶显示器及底座AUTO MENU配属附件以下所列配件皆经测试且认证核可,未经认可之配件,请勿使用于此LED背光液晶显示器。

HA17393中文资料

Output Sink Current Iosink (mA)

HA17903, HA17393 Series

Output Sink Current vs. Ambient Temperature 20

15

VCC = 36 V

15 V

5V 10

2V

5

0

–20

0

25

50

75

Ambient Temperature Ta (°C)

Ratings

Item

HA17903 HA17903 HA17903 HA17903 HA17903 HA17393 HA17393

Symbol PS

PSJ

FP

FPJ

FPK

F

Unit

Supply

VCC

36

36

36

36

36

36

36

V

voltage

Dfferential

VIN(diff)

VCC

VCC

VCC

Input offset current

Common mode input voltage*3

VIO I IB I IO VCM+

—

2.0 5.0 mV

—

25

—

3

3.5 —

250 nA

50

nA

—

V

IIN (+) or IIN (–) | IIN (+) – IIN (–) |

Supply current

board. Derate by 7.14mW/°C above that temperature.

3. Short circuit between the output and VCC will be a cause to destory the circuit. The maximum output current is about 20mA for any supply voltage.

唯特利HDPE管道连接器905型说明书

请参考本文档末的信息。

1.0 产品描述供货尺寸• 2 – 14英寸 IPS 管道尺寸• 63 – 355 毫米 ISO 管道尺寸管道材料• 符合 ASTM D3035 和 ASTM F714 或 ISO 4427-2 (SDR 7 – 26) 的 HDPE 管道• PE-RT 管道符合 ASTM D3035、单元分类 PE445574C、ASTM F2619 和 ASTM F714 (SDR 7 – 26) 标准• 有关交联聚乙烯(PE-Xa)管道的信息,请参见技术文件 36.01• 有关其他管道材料,请与 Victaulic(唯特利)联系最大工作压力• 达到或超过 HDPE 或 PE-RT 管道的额定压力工作温度• 视管道制造商额定值和密封垫圈选用而定• 有关密封垫圈性能选项,请参阅第 3.0 节• 有关管道材料性能极限,请咨询管道制造商功能• 连接平端HDPE管道• 采用 Installation-Ready™专利技术,无零散部件管道制备• 适用于平端 HDPE 或 PE-RT 管道注• 本文档中对 HDPE 的所有引用都包括 PE-RT2.0 CERTIFICATION/LISTINGS注• 有关详细信息,请参见技术文件 10.01:Victaulic(唯特利)消防认证参考指南。

• 有关详细信息,参见技术文件 02.06:Victaulic(唯特利)饮用水产品认证 – ANSI/NSF 61 和 ANSI/NSF 372。

• W aterMark™认证只适用于带 “E” 级三元乙丙橡胶(EPDM)密封垫圈的熔融粘结环氧树脂涂层卡箍。

有关进一步详细信息,请与 Victaulic(唯特利)联系。

用于HDPE管道的 Victaulic®(唯特利™)平端卡箍905 型19.07-CHI如需产品安装、维护或支持信息,3.0 规格 – 材料壳体:符合 ASTM A536之65-45-12 等级要求的球墨铸铁。

磐启微电子 PAN2418 系列 2.4GHz 宽带无线收发芯片说明书

PAN2418系列产品说明书2.4GHz宽带无线收发芯片概述PAN2418芯片是工作在2.320~2.483GHz的宽带无线收发芯片。

该芯片集成射频收发机、频率发生器、晶体振荡器、调制解调器等功能模块,并且支持一对多组网和带ACK的通信模式。

发射输出功率、工作频道以及通信数据率均可配置。

主要特性6Mbps模式的接收灵敏度为-81dBm;最大输出功率20dBm。

其它特性四线 SPI 接口通信 SPI 接口速率最高支持20MbpsQFN24L 0404封装支持最大数据长度为512字节(两级乒乓FIFO)3M /6Mbps模式,需要晶振精度 ±60ppm 工作电压支持2.2~3.3V工作温度支持-40~+85℃GFSK通信方式 支持自动应答及自动重传支持RSSI检测功能 带自动扰码和CRC校验功能应用方案Babymonitor 无线图像传输玩具可视门铃 监控版本 修订时间 更新内容 相关文档V1.0 2017. 12目录1 命名规则 (4)1.1 PAN2418命名规则 (4)1.2 PAN2418系列产品选择 (4)2 主要电特性 (4)3 极限最大额定值 (3)4 系统结构方框图 (3)5 引脚定义 (4)6 芯片工作状态 (5)6.1 休眠模式 (6)6.2 待机模式-I(STB1) (6)6.3 待机模式-III(STB3) (7)6.4 待机模式-II(STB2) (7)6.5 接收模式 (7)6.6 发射模式 (7)7 数据通信模式 (8)7.1 普通模式 (9)7.2 增强模式 (9)7.3增强发送模式 (10)7.4 增强接收模式 (11)7.5 增强模式下的数据包识别 (11)7.6 增强模式下的PTX和PRX的时序图 (11)7.7 增强模式下的接收端一对多通信 (12)7.8 DATA FIFO (14)7.9 中断引脚 (14)8 SPI控制接口 (14)8.1 SPI指令格式 (15)8.2 SPI 时序 (17)9 控制寄存器 (18)10 数据包格式描述 (43)10.1 普通模式的数据包形式 (43)10.2 增强模式的数据包形式 (43)10.3 增强模式的ACK包形式 (43)11 典型应用电路(参考) (44)12 封装尺寸 (44)13 联系方式 (45)1 命名规则1.1 PAN2418命名规则DR 码率3 6 Mbps M f 6∆调制频偏@6Mbps 1.5 2 MHz M FCH 6频道间隔@6Mbps9 MHz 发射模式指标PRF 典型输出功率 0 17 20 dBm PRFC 输出功率范围-30 20 dBm 1PBW发射带数据调制的20dB 带宽(6Mbps)9MHz接收模式指标(注1)maxRX误码率<0.1%时的最大接收幅度 0 dBm 1RXSENS 接收灵敏度(0.1%BER)@6Mbps-81 dBm 2RXSENS接收灵敏度(0.1%BER)@3Mbps-84dBm接收模式邻道选择性CO C Ι/同频的通道选择性@6Mbps 10 dBc STC 1/Ι第1相邻道选择性@6Mbps 0 dBc ND C 2/Ι第2相邻道选择性@6Mbps -18 dBc RDC 3/Ι第3相邻道选择性@6Mbps -19 dBc 4/TH C Ι 第4相邻道选择性@6Mbps-32 dBc 接收机镜像抑制Image镜像抑制30 dBc 操作条件VDD 供电电压 2.2 3 3.3 V VSS 芯片地 0 V OH V 高电平输出电压 VDD-0.3 VDD V OLV 低电平输出电压 VSS VSS+0.3 V IH V高电平输入电压 VDD-0.3 VDD V IL V低电平输入电压VSSVSS+0.3V3 极限最大额定值表3 PAN2418系列芯片极限最大额定值 特 性条件参数值 单位最小典型最大最大额定值DD V 供电电压 -0.3 3.6 V I V 输入电压 -0.3 3.6 V O V输出电压VSS VDD Pd 总功耗(TA=-40℃~85℃)600 mW OP T 工作温度 -40 85 ℃ STG T存储温度-40125℃* 注1:使用中强行超过一项或多项极限最大额定值会导致器件永久性损坏。

MRF7S18125BHR3;MRF7S18125BHR5;MRF7S18125BHSR3;MRF7S18125BHSR5;中文规格书,Datasheet资料