80390datasheet

zl30109中文资料_数据手册_IC数据表

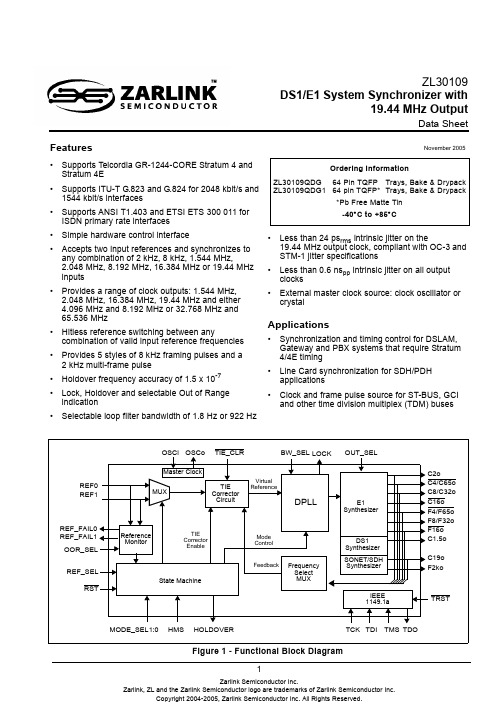

1Features•Supports Telcordia GR-1244-CORE Stratum 4 and Stratum 4E•Supports ITU-T G.823 and G.824 for 2048kbit/s and 1544kbit/s interfaces•Supports ANSI T1.403 and ETSI ETS 300 011 for ISDN primary rate interfaces •Simple hardware control interface•Accepts two input references and synchronizes to any combination of 2kHz, 8kHz, 1.544MHz,2.048MHz, 8.192MHz, 16.384MHz or 19.44MHz inputs•Provides a range of clock outputs: 1.544MHz, 2.048MHz, 16.384MHz, 19.44MHz and either 4.096MHz and 8.192MHz or 32.768MHz and 65.536MHz•Hitless reference switching between anycombination of valid input reference frequencies •Provides 5 styles of 8kHz framing pulses and a 2kHz multi-frame pulse•Holdover frequency accuracy of 1.5 x 10-7•Lock, Holdover and selectable Out of Range indication•Selectable loop filter bandwidth of 1.8Hz or 922Hz•Less than 24 ps rms intrinsic jitter on the19.44MHz output clock, compliant with OC-3 and STM-1 jitter specifications•Less than 0.6ns pp intrinsic jitter on all output clocks•External master clock source: clock oscillator or crystalApplications•Synchronization and timing control for DSLAM, Gateway and PBX systems that require Stratum 4/4E timing•Line Card synchronization for SDH/PDH applications•Clock and frame pulse source for ST-BUS, GCI and other time division multiplex (TDM) busesNovember 2005ZL30109DS1/E1 System Synchronizer with19.44MHz OutputData SheetFigure 1 - Functional Block DiagramReference MonitorMode ControlVirtual ReferenceIEEE 1149.1aFeedbackTIE Corrector EnableState MachineFrequency Select MUXTIE Corrector CircuitMODE_SEL1:0TCK REF1RSTREF_SELTIE_CLROSCo OSCi Master ClockTDOREF0TDI TMS TRSTHOLDOVER BW_SEL HMS LOCK REF_FAIL0REF_FAIL1DPLLOUT_SELMUXOOR_SEL C2oE1SynthesizerDS1SynthesizerSONET/SDH SynthesizerC4/C65o C8/C32o C16o F4/F65o F8/F32o C1.5o C19o F2koF16o Ordering InformationZL30109QDG 64 Pin TQFP Trays, Bake & Drypack ZL30109QDG164 pin TQFP*Trays, Bake & Drypack*Pb Free Matte Tin -40°C to +85°CZL30109Data Sheet DescriptionThe ZL30109 DS1/E1 System Synchronizer contains a digital phase-locked loop (DPLL), which provides timing and synchronization for multi-trunk DS1 and E1 transmission equipment. The 19.44MHz output makes the ZL30109 also suitable for SDH line card applications.The ZL30109 generates a 19.44MHz clock and ST-BUS and TDM bus clocks and framing signals that are phase locked to one of two input references. It helps ensure system reliability by monitoring its references for accuracy and stability and by maintaining stable output clocks during reference switching operations and during short periods when a reference is unavailable.The ZL30109 is intended to be the central timing and synchronization resource for network equipment that complies with Telcordia, ETSI, ITU-T and ANSI network specifications.ZL30109Data SheetTable of Contents1.0 Change Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52.0 Physical Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62.1 Pin Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62.2 Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73.0 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .103.1 Reference Select Multiplexer (MUX). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .103.2 Reference Monitor. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .103.3 Time Interval Error (TIE) Corrector Circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133.4 Digital Phase Lock Loop (DPLL). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.5 Frequency Synthesizers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .173.6 State Machine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .173.7 Master Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .174.0 Control and Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .174.1 Out of Range Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .174.2 Loop Filter Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .184.3 Output Clock and Frame Pulse Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .184.4 Modes of Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .184.4.1 Freerun Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .184.4.2 Holdover Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .194.4.3 Normal Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .194.5 Reference Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .205.0 Measures of Performance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .215.1 Jitter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .215.2 Jitter Generation (Intrinsic Jitter). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .215.3 Jitter Tolerance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .215.4 Jitter Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .215.5 Frequency Accuracy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .225.6 Holdover Accuracy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .225.7 Pull-in Range. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .225.8 Lock Range. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .225.9 Phase Slope . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .225.10 Time Interval Error (TIE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .225.11 Maximum Time Interval Error (MTIE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .225.12 Phase Continuity. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .225.13 Lock Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .226.0 Applications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .236.1 Power Supply Decoupling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .236.2 Master Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .236.2.1 Clock Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .236.2.2 Crystal Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .246.3 Power Up Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .246.4 Reset Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .257.0 Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .267.1 AC and DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .267.2 Performance Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33ZL30109Data SheetList of FiguresFigure 1 - Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Figure 2 - Pin Connections (64 pin TQFP, please see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Figure 3 - Reference Monitor Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 4 - Behaviour of the Dis/Re-qualify Timer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 5 - DS1 Mode Out-of-Range Limits (OOR_SEL=0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 6 - E1 Mode Out-of-Range Limits (OOR_SEL=1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 7 - Timing Diagram of Hitless Reference Switching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Figure 8 - Timing Diagram of Hitless Mode Switching. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Figure 9 - DPLL Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Figure 10 - Mode Switching in Normal Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 Figure 11 - Reference Switching in Normal Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Figure 12 - Clock Oscillator Circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23 Figure 13 - Crystal Oscillator Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 Figure 14 - Power-Up Reset Circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 Figure 15 - Timing Parameter Measurement Voltage Levels. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 Figure 16 - Input to Output Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29 Figure 17 - Output Timing Referenced to F8/F32o . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31 Figure 18 - SONET/SDH Output Timing Referenced to F8/F32o . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32ZL30109Data Sheet1.0 Change SummaryChanges from July 2005 Issue to November 2005 Issue. Page, section, figure and table numbers refer to this current issue.Changes from November 2004 Issue to July 2005 Issue. Page, section, figure and table numbers refer to this current issue.Page Item Change1Features Added description for hitless reference switching.23Section 6.1Removed power supply decoupling circuit and includedreference to synchronizer power supply decoupling application note.Page Item Change8RST pin Specified clock and frame pulse outputs forced to high impedance.10REF0 pinSpecified seven possible reference input frequencies.27Table “DC Electrical Characteristics*“Corrected Schmitt trigger levels.33Table “Performance Characteristics* - Functional“Gave more detail on Lock Time conditions.ZL30109Data Sheet2.0 Physical Description2.1 Pin ConnectionsFigure 2 - Pin Connections (64 pin TQFP, please see Note 1)Note 1: The ZL30109 uses the TQFP shown in the package outline designated with the suffix QD, the ZL30109does not use the e-Pad TQFP .ZL3010934363840424446486462605856525054161412108642OSCo NC GND OUT_SEL C1.5o MODE_SEL1V DD AV DD IC NC RSTNC AGNDF4/F65o V DD REF1NC ICC 8/C 32o F 2k o C 2o A G N DA V D DC 19o F 8/F 32o C 4/C 65o REF_SEL1820222426303228C 16o F16o TIE_CLR OOR_SELICOSCi A V D DA V D DA V D DA V C O R EA G N D A G N D A G N D NC NC IC ICMODE_SEL0NC BW_SELREF0V C O R EL O C K H M ST R S T G N DT D O T M S H O L D O V E R I C T C K T D I V C O R EA V C O R EG N D R E F _F A I L 0R E F _F A I L 1ZL30109Data Sheet2.2 Pin DescriptionPin DescriptionPin # Name Description1GND Ground. 0 V.2V CORE Positive Supply Voltage. +1.8 V DC nominal.3LOCK Lock Indicator (Output). This output goes to a logic high when the PLL is frequencylocked to the selected input reference.4HOLDOVER Holdover (Output). This output goes to a logic high whenever the PLL goes intoholdover mode.5REF_FAIL0Reference 0 Failure Indicator (Output). A logic high at this pin indicates that the REF0 reference frequency has exceeded the out-of-range limit set by the OOR_SEL pin or thatit is exhibiting abrupt phase or frequency changes.6IC Internal bonding Connection. Leave unconnected.7REF_FAIL1Reference 1 Failure Indicator (Output). A logic high at this pin indicates that the REF1 reference frequency has exceeded the out-of-range limit set by the OOR_SEL pin or thatit is exhibiting abrupt phase or frequency changes.8TDO Test Serial Data Out (Output). JTAG serial data is output on this pin on the falling edge of TCK. This pin is held in high impedance state when JTAG scan is not enabled.9TMS Test Mode Select (Input). JTAG signal that controls the state transitions of the TAPcontroller. This pin is internally pulled up to V DD. If this pin is not used then it should beleft unconnected.10TRST Test Reset (Input). Asynchronously initializes the JTAG TAP controller by putting it in the Test-Logic-Reset state. This pin should be pulsed low on power-up to ensure thatthe device is in the normal functional state. This pin is internally pulled up to V DD. Ifthis pin is not used then it should be connected to GND.11TCK Test Clock (Input): Provides the clock to the JTAG test logic. If this pin is not used then it should be pulled down to GND.12V CORE Positive Supply Voltage. +1.8 V DC nominal.13GND Ground. 0 V.14AV CORE Positive Analog Supply Voltage. +1.8 V DC nominal.15TDI Test Serial Data In (Input). JTAG serial test instructions and data are shifted in on this pin. This pin is internally pulled up to V DD. If this pin is not used then it should be leftunconnected.16HMS Hitless Mode Switching (Input). The HMS circuit controls phase accumulation during the transition from Holdover or Freerun mode to Normal mode on the same reference. Alogic low at this pin will cause the ZL30109 to maintain the delay stored in the TIEcorrector circuit when it transitions from Holdover or Freerun mode to Normal mode. Alogic high on this pin will cause the ZL30109 to measure a new delay for its TIE correctorcircuit thereby minimizing the output phase movement when it transitions from Holdoveror Freerun mode to Normal mode.17MODE_SEL0Mode Select 0 (Input). This input combined with MODE_SEL1 determines the mode(Normal, Holdover or Freerun) of operation, see Table4 on page18.18MODE_SEL1Mode Select 1 (Input). See MODE_SEL0 pin description.ZL30109Data Sheet Pin Description (continued)Pin # Name Description19RST Reset (Input). A logic low at this input resets the device. On power up, the RST pin must be held low for a minimum of 300ns after the power supply pins have reachedthe minimum supply voltage. When the RST pin goes high, the device will transitioninto a Reset state for 3ms. In the Reset state all clock and frame pulse outputs will beforced into high impedance.20OSCo Oscillator Master Clock (Output). For crystal operation, a 20MHz crystal is connected from this pin to OSCi. This output is not suitable for driving other devices. For clockoscillator operation, this pin must be left unconnected.21OSCi Oscillator Master Clock (Input). For crystal operation, a 20MHz crystal is connected from this pin to OSCo. For clock oscillator operation, this pin must be connected to aclock source.22IC Internal Connection. Leave unconnected.23GND Ground. 0V.24NC No internal bonding Connection. Leave unconnected.25V DD Positive Supply Voltage. +3.3 V DC nominal.26OUT_SEL Output Selection (Input).This input selects the signals on the combined output clock and frame pulse pins, see Table3 on page18.27IC Internal Connection. Connect this pin to ground.28IC Internal Connection. Connect this pin to ground.29AV DD Positive Analog Supply Voltage. +3.3 V DC nominal.30NC No internal bonding Connection. Leave unconnected.31NC No internal bonding Connection. Leave unconnected.32C1.5o Clock 1.544MHz (Output). This output is used in DS1 applications.This clock output pad includes a Schmitt input which serves as a PLL feedback path;proper transmission-line termination should be applied to maintain reflections belowSchmitt trigger levels.33AGND Analog Ground. 0 V34AGND Analog Ground. 0 V35AV CORE Positive Analog Supply Voltage. +1.8 V DC nominal.36AV DD Positive Analog Supply Voltage. +3.3 V DC nominal.37AV DD Positive Analog Supply Voltage. +3.3 V DC nominal.38F2ko Multi Frame Pulse (Output). This is a 2kHz 51ns active high framing pulse, whichmarks the beginning of a multi frame.This clock output pad includes a Schmitt input which serves as a PLL feedback path;proper transmission-line termination should be applied to maintain reflections belowSchmitt trigger levels.ZL30109Data Sheet Pin Description (continued)Pin # Name Description39C19o Clock 19.44MHz (Output). This output is used in SONET/SDH applications.This clock output pad includes a Schmitt input which serves as a PLL feedback path;proper transmission-line termination should be applied to maintain reflections belowSchmitt trigger levels.40AGND Analog Ground.0V41AGND Analog Ground.0V42C4/C65o Clock 4.096MHz or 65.536MHz (Output). This output is used for ST-BUS operation at2.048Mbps, 4.096Mbps or 65.536MHz (ST-BUS 65.536Mbps). The output frequency isselected via the OUT_SEL pin.43C8/C32o Clock 8.192MHz or 32.768MHz (Output). This output is used for ST-BUS and GCIoperation at 8.192Mbps or for operation with a 32.768MHz clock. The output frequencyis selected via the OUT_SEL pin.44AV DD Positive Analog Supply Voltage. +3.3 V DC nominal.45AV DD Positive Analog Supply Voltage. +3.3 V DC nominal.46C2o Clock 2.048MHz (Output). This output is used for standard E1 interface timing and for ST-BUS operation at 2.048Mbps.This clock output pad includes a Schmitt input which serves as a PLL feedback path;proper transmission-line termination should be applied to maintain reflections belowSchmitt trigger levels.47C16o Clock 16.384MHz (Output). This output is used for ST-BUS operation with a16.384MHz clock.This clock output pad includes a Schmitt input which serves as a PLL feedback path;proper transmission-line termination should be applied to maintain reflections belowSchmitt trigger levels.48F8/F32o Frame Pulse (Output). This is an 8kHz 122ns active high framing pulse (OUT_SEL=0) or it is an 8kHz 31ns active high framing pulse (OUT_SEL=1), which marks thebeginning of a frame.This clock output pad includes a Schmitt input which serves as a PLL feedback path;proper transmission-line termination should be applied to maintain reflections belowSchmitt trigger levels.49F4/F65o Frame Pulse ST-BUS 2.048Mbps or ST-BUS at 65.536MHz clock (Output). Thisoutput is an 8kHz 244ns active low framing pulse (OUT_SEL=0), which marks thebeginning of an ST-BUS frame. This is typically used for ST-BUS operation at2.048Mbps and 4.096Mbps. Or this output is an 8kHz 15ns active low framing pulse(OUT_SEL=1), typically used for ST-BUS operation with a clock rate of 65.536MHz.50F16o Frame Pulse ST-BUS 8.192Mbps (Output). This is an 8kHz 61ns active low framing pulse, which marks the beginning of an ST-BUS frame. This is typically used for ST-BUSoperation at 8.192Mbps.51AGND Analog Ground.0V52IC Internal Connection. Connect this pin to ground.ZL30109Data Sheet Pin Description (continued)Pin # Name Description53REF_SEL Reference Select (Input). This input selects the input reference that is used forsynchronization, see Table5 on page20. This pin is internally pulled down to GND.54NC No internal bonding Connection. Leave unconnected.55REF0Reference (Input). This is one of two (REF0, REF1) input reference sources used forsynchronization. One of seven possible frequencies may be used: 2kHz, 8kHz,1.544MHz,2.048MHz, 8.192MHz, 16.384MHz, or 19.44MHz. This pin is internallypulled down to GND.56NC No internal bonding Connection. Leave unconnected.57REF1Reference (Input). See REF0 pin description.58NC No internal bonding Connection. Leave unconnected.59IC Internal Connection. Connect this pin to ground.60OOR_SEL Out Of Range Selection (Input). This pin selects the out of range reference rejection limits, see Table1 on page17.61V DD Positive Supply Voltage. +3.3 V DC nominal.62NC No internal bonding Connection. Leave unconnected.63TIE_CLR TIE Corrector Circuit Reset (Input). A logic low at this input resets the Time IntervalError (TIE) correction circuit resulting in a realignment of the input phase with the outputphase.64BW_SEL Filter Bandwidth Selection (Input). This pin selects the bandwidth of the DPLL loopfilter, see Table2 on page18. Set continuously high to track jitter on the input referenceclosely or set temporarily high to allow the ZL30109 to quickly lock to the input reference.3.0 Functional DescriptionThe ZL30109 is a DS1/E1 System Synchronizer providing timing (clock) and synchronization (frame) signals to interface circuits for DS1 and E1 Primary Rate Digital Transmission links and OC-3/STM-1 links, as well as a 19.44MHz output for SDH line card applications. Figure 1 is a functional block diagram which is described in the following sections.3.1 Reference Select Multiplexer (MUX)The ZL30109 accepts two simultaneous reference input signals and operates on their rising edges. One of them, the primary reference (REF0) or the secondary reference (REF1) signal can be selected as input to the TIE corrector circuit based on the reference selection (REF_SEL) input.3.2 Reference MonitorThe input references are monitored by two independent reference monitor blocks, one for each reference. The block diagram of a single reference monitor is shown in Figure 3. For each reference clock, the frequency is detected and the clock is continuously monitored for three independent criteria that indicate abnormal behavior of the reference signal, for example; long term drift from its nominal frequency or excessive jitter. To ensure proper operation of the reference monitor circuit, the minimum input pulse width restriction of 15nsec must be observed.ZL30109Data Sheet •Reference Frequency Detector : This detector determines whether the frequency of the reference clock is2kHz, 8kHz, 1.544MHz, 2.048MHz, 8.192MHz, 16.384MHz or 19.44MHz and provides this information to the various monitor circuits and the phase detector circuit of the DPLL.•Precise Frequency Monitor : This circuit determines whether the frequency of the reference clock is within the applicable out-of-range limits selected by the OOR_SEL pin, see Figure 5, Figure 6 and Table 1. It will take the precise frequency monitor up to 10 s to qualify or disqualify the input reference.•Coarse Frequency Monitor (CFM): This circuit monitors the reference frequency over intervals ofapproximately 30 µs to quickly detect large frequency changes.•Single Cycle Monitor (SCM): This detector checks the period of a single clock cycle to detect large phase hits or the complete loss of the clock.Figure 3 - Reference Monitor CircuitExceeding the thresholds of any of the monitors forces the corresponding REF_FAIL pin to go high. The single cycle and coarse frequency failure flags force the DPLL into Holdover mode and feed a timer that disqualifies the reference input signal when the failures are present for more than 2.5s. The single cycle and coarse frequency failures must be absent for 10s to let the timer re-qualify the input reference signal as valid. Multiple failures of less than 2.5s each have an accumulative effect and will disqualify the reference eventually. This is illustrated in Figure 4.Reference Frequency Detector Single Cycle Monitor Precise Frequency MonitorCoarse Frequency Monitor dis/requalify timerREF0 / REF1OR OR REF_DIS= reference disrupted.This is an internal signal.Mode select state machine HOLDOVERREF_DIS REF_FAIL0 / REF_FAIL1ZL30109Data SheetSCM or CFM failurecurrent REFtimer2.5 s10 sREF_FAILHOLDOVERFigure 4 - Behaviour of the Dis/Re-qualify TimerWhen the incoming signal returns to normal (REF_FAIL=0), the DPLL returns to Normal mode with the output signal locked to the input signal. Each of the monitors has a built-in hysteresis to prevent flickering of the REF_FAIL status pin at the threshold boundaries. The precise frequency monitor and the timer do not affect the mode (Holdover/Normal) of the DPLL.Figure 5 - DS1 Mode Out-of-Range Limits (OOR_SEL=0)。

RCP890A03 datasheet

SpecificationForLTCC 3dB Hybrid Coupler Model Name : RCP890A03RN2 Technologies co., Ltd.RN2 Technologies co., Ltd.284-2, Galgot-ri, Jinwe-myeon, Pyeongtaek-si, Kyunggi-do, KOREA Phone : (+82) 31 - 376 - 5400FAX : (+82) 31 - 376 - 9151 Distributor:Shenzhen Jushou electronics Co., Ltd.6F,building3,Sege science park, futian shenzhen Tel: 0086-0755-******** Mobile:0086-136******** Email: Fisher@Contact:Mr yu1. Description1-1. Part number: RCP890A031-2. Features- Hybrid Coupler 3dB, 90˚- Surface mount type- Suitable for operation frequency 815~960MHz- RoHS compliance- High stability in temperature and humidity for LTCC base - Low loss for Silver(Ag) conductor- Miniature size and high power capability- Lead-free alloy solderable- Thermal expansion corresponding with common substrate 2. Electrical SpecificationFreq. (MHz) Amplitude Balancemax (dB)Isolationmin (dB)Insertion Lossmax (dB)815-960 ±0.15 -23 -0.15VSWR MaxPhase(degrees)Power CapacityAvg. (Watt)Operating Temp.(℃)1.2 90 ±2.0 200 -55 to +1253. Mechanical Specification 3-1. Outline Dimension3-2. Weight- 1.35 Grams typical4. Port ConfigurationConfiguration Port 1 Port 2 Port 3 Port 4Case 1. Input Isolated Coupling-3dB, 0˚Output-3dB, -90˚Case 2. Isolated Input Output-3dB, 90˚Coupling -3dB, 0˚Case 3. Coupling-3dB, 0˚Output-3dB, 90˚Input IsolatedCase 4.Output-3dB, 90˚Coupling-3dB, 0˚Isolated Input * Once Port 1 is determined, the other three ports are defined automatically.5. Schematic DrawingPort1P inP cou P out P isoPort3 Port4Port26. Typical Performance Data (25℃)Return Loss [dB]Freq. [MHz]Coupling[dB]Out [dB] IL [dB]Amp.Bal.[dB]Phase[degree]S11 S22 S33 S44815 -3.12 -3.07 -0.09 ±0.02 -90.22 -26.15 -27.56 -26.33 -25.85 820 -3.11 -3.08 -0.08 ±0.02 -90.19 -26.37 -27.85 -26.56 -26.07 830 -3.11 -3.10 -0.09 ±0.00 -90.21 -26.85 -28.42 -27.07 -26.52 840 -3.09 -3.11 -0.09 ±0.01 -90.27 -27.34 -29.01 -27.61 -26.97 850 -3.09 -3.13 -0.10 ±0.02 -90.36 -27.92 -29.68 -28.18 -27.47 860 -3.08 -3.13 -0.09 ±0.03 -90.31 -28.50 -30.34 -28.82 -27.99 870 -3.07 -3.13 -0.09 ±0.03 -90.36 -29.12 -31.06 -29.44 -28.53 880 -3.06 -3.14 -0.09 ±0.04 -90.39 -29.81 -31.71 -30.12 -29.12 890 -3.07 -3.16 -0.11 ±0.05 -90.38 -30.50 -32.40 -30.84 -29.72 900 -3.06 -3.14 -0.09 ±0.04 -90.39 -31.22 -32.98 -31.48 -30.27 910 -3.06 -3.14 -0.09 ±0.04 -90.43 -31.95 -33.45 -32.22 -30.88 920 -3.06 -3.16 -0.10 ±0.05 -90.46 -32.69 -33.70 -32.94 -31.45 930 -3.06 -3.15 -0.09 ±0.04 -90.54 -33.41 -33.71 -33.55 -31.92 940 -3.07 -3.14 -0.10 ±0.04 -90.48 -34.05 -33.48 -34.03 -32.38 950 -3.07 -3.13 -0.09 ±0.03 -90.51 -34.53 -33.00 -34.41 -32.73 960 -3.08 -3.14 -0.10 ±0.03 -90.55 -34.72 -32.38 -34.50 -32.89* Data with PCB and Connector Loss ( 0.89 GHz = 0.03dB )7. Operation Temperature Curve (a)RCP650A03 Return Loss(Port1)M a g n i t u d e [d B ]Frequency[MHz]RCP890A03 Return Loss(Port2)M a g n i t u d e [d B ]Frequency[MHz]70080090010001100RCP890A03 Return Loss(Port3)M a g n i t u d e [d B ]Frequency[MHz]70080090010001100RCP890A03 Return Loss(Port4)M a g n i t u d e [d B ]Frequency[MHz]8. Operation Temperature Curve (b)70080090010001100RCP890A03 Coupling & Transmission LossM a g n i t u d e [d B ]Frequency[MHz]70080090010001100RCP890A03 Insertion LossM a g n i t u d e [d B ]Frequency[MHz]70080090010001100RCP890A03 IsolationM a g n i t u d e [d B ]Frequency[MHz]70080090010001100RCP890A03 Phase BalanceP h a s e [d e g ]Frequency[MHz]9. Test Method- Refer to ‘Case 1’ of ‘4. Port Configuration’ on page 4 - Have the network analyzer calibrated properly.- Measure the data of Coupling through port 1 to port 3. (S31) - Measure the data of Transmission through port 1 to port 4. (S41) - Measure the data of Isolation through port 1 to port 2. (S21)- Calculate the Insertion Loss and Amplitude Balance of coupler on the below power method formula.in out P cou : Power of Coupling Port P iso : Power of Isolated Port10. Measurement board layout11. Recommended PCB layout and Solder mask pattern12. Reflow profilePeakSoakingUpPre-HeatingRamp℃ T1:160±5℃ T2:180±5℃ T4:260±5℃ T3:230±5℃Temp.[]Time [sec] t1:60±5sec t2:100±15sec t3:30±5sec t4:60±10sec13. Using note for LTCC CouplersI.Be careful when transportingA.Excessive stress or shock may make products broken or cracked due to the nature ofceramics structure.B.The products cracked or damaged on terminals may have their property changed.II.Be careful during storageA.Store the products in the temperature of -55 ~ 125℃B.Keep the humidity at 45 ~ 75% around the products.C.Prevent corrosive gas (Cl2, NH3, SO X, NO X, etc.) from contacting the products.D.It is recommended to use the products within 6 months of receipt. If the period exceeds6 months, solderability may need to be verified.III.Be careful when solderingA.All the ground terminals, IN and OUT pad of coupler should be soldered on the groundplane of the PCB.B.Products may be cracked or broken by uneven forces from a claw or suction device.C.Mechanical stress by any other devices may damage products when positioning them onPCB.D. A dropped product is recommended not to be used.E.Soldering must be carried out by the condition of specification sheet.F.Any couplers which are de-soldered from PCB should not be used again.14. Packaging15. Environmental ReliabilityITEM PROCEDURE REQUIREMENTS/RESULTTemperature Cycle (Thermal Shock)1. One cycle : 30 minutesStep 1 : 125 ± 5 for 15 minutesStep 2 : -55 ± 5 for 15 minutes2. Time to approach low or high temperature: 10 seconds3. Number of Cycles : 100 cycles4. Keep normal temperature for 1 hour.1. Meet the electrical Specification after testSolderability1. Solder : 230 ± 5°C for 5± 1 sec. 1. More than 85% of the I/Oelectrode pad shall be covered with solder.Heat Resistance 1. Temperature : 100 ± 2 °C 2. Duration : 96 ± 2 hours 1. Meet the electrical Specification after testLow Temp. Resistance1. Temperature : -55 ± 5 °C2. Duration : 24 ± 2 hours 1. Meet the electrical Specification after testVibration Resistance1. Frequency: 5~ 15MHz2. Acceleration : 10g3. Sweep Time: 0.1 oct/min, 15min/axis4. Axis : X, Y and Z direction 1. No appearance damage 2. Meet the electrical Specification after testHumidity Resistance1. One Cycle :Step1:increase Temperature -25~65°C for 2hours with humidity 85%Step2:Maintain for 4 hour after increasing Humidity 90% to 95%Step3: Decrease Temperature 65°C to 25°C 2. Number of Cycles : 103. Maintain for 3hour after decreasing temperature -10°C 1. Meet the electrical Specification after testDrop Shock 1. Dropped onto hard wood from height of 50 cm for 5 times; each x, y and z direction except I/O direction.1. No appearance damage2. Meet the electrical Specification after test16. RoHS test result-RN2 Technologies warrants and represents as follows.。

APX803D-29SRG-7;APX803D-29SAG-7;中文规格书,Datasheet资料

DescriptionThe APX803/D is used for microprocessor (µP) supervisory circuits to monitor the power supplies in µP and digital systems. They provide excellent circuit reliability and low cost by eliminating external components and adjustments when used with +5V, +3.3V, +3.0V powered circuits.These circuits perform a single function: they assert a reset signal on power up and whenever the V CC supply voltage declines below a preset threshold, keeping it asserted for a fixed period of time after V CC has risen above the reset threshold. For the APX803D this period is a minimum of 1ms while for other APX803 variants it is at least 140ms. The reset comparator is designed to ignore fast transients on V CC, and the outputs are guaranteed to be in the correct logic state for V CC down to 1V.The APX803 is available with different reset thresholds suitable for operation with a variety of supply voltages, however the APX803D is available with a 2.93V threshold voltage.The APX803/D have an open collector active low RESET output and compliment Diodes APX809/10 which have push-pull output stages.. Low supply current makes the APX803/D ideal for use in portable equipment. The APX803/D are available in two pin out variants of the 3-pin SOT23 package. Pin Assignments( Top View )GNDV CC RESETSOT23( Top View )GNDV CC RESETSOT23RFeatures• Precision Monitoring of +2.5V, +3V, +3.3V, and +5V Power-Supply Voltages• Fully Specified Over Temperature• Open-drain RESET Active Low• Power-On/power supply glitch Reset Pulse • APX803D 2ms (Typ)• APX803 200ms (Typ)• 30µA Supply Current (Typ.)• Guaranteed Reset Valid to VCC = +1V• No External Components• SOT23 and SOT23R: Available in “Green” Molding Compound (No Br, Sb)• Lead Free Finish/ RoHS Compliant (Note 1) Applications• Computers• Controllers• Intelligent Instruments• Critical µP and µC Power Monitoring • Portable/Battery Powered EquipmentNotes: 1. EU Directive 2002/95/EC (RoHS). All applicable RoHS exemptions applied. Please visit our website atTypical Application CircuitC INPin DescriptionsFunctional Block DiagramRESETV CCAbsolute Maximum RatingsRecommended Operating ConditionsElectrical Characteristics (T A = 25°C)°3. Final datasheet limits to be determined by characterization and correlation.Typical Performance CharacteristicsFigure 1Figure 2Figure 3Figure 4Typical Performance Characteristics (Continued)Figure 7 Figure 8Figure 9 Figure 10Timing DiagramRESETVccFunctional DescriptionMicroprocessors (µPs) and microcontrollers (µC) have a reset input to ensure that it starts up in a known state. The APX803/D drive the µP’s reset input to prevent code-execution errors during power-up, power-down, or brownout conditions. They assert a reset signal whenever the V CC supply voltage declines below a preset threshold and keep it asserted for a fixed period of time after V CC has risen above the reset threshold. For the APX803D this period is a minimum of 1ms while for other APX803 variants it is at least 140ms. The APX803/D have an open-drain output stage.Ensuring a Valid Reset OutputDown to V CC = 0RESET is guaranteed to be a logic low for V CC > 1V. Once V CC exceeds the reset threshold, an internal timer keeps RESET low for the reset timeout period; after this interval, RESET goes high. If a brownout condition occurs (V CC dips below the RESET reset threshold), RESET goes low. Any time V CC goes below the reset threshold, the internal timer resets to zero, and RESET goes low. The internal timer starts after V CC returns above the reset threshold, and RESET remains low for the reset timeout period.When V CC falls below 1V, the APX803/D RESET output no longer sinks current — it becomes an open circuit. Therefore, high-impedance CMOS logic inputs connected to RESET can drift to undetermined voltages. This presents no problem in most applications since most µP and other circuitry is inoperative with V CC below 1V.Interfacing to µP with Bidirectional Reset Pins Since the RESET output on the APX803/D is open drain, this device interfaces easily with μP/µC that have bidirectional reset pins, such as the Motorola 68HC11. Connecting the μP supervisor’s RESET output directly to the microcontroller’s (μC’s) RESET pin with a single pull-up resistor allows either device to assert reset.Supervising and monitoring Multiple Supplies Generally, the pull-up resistor connected to the APX803/D will connect to the supply voltage that is being monitored at the IC’s V CC pin. However, some systems may use the APX803/D open-drain output to level-shift from the monitored supply to reset the µP powered by a different supply voltage or monitor multiple supplies that will be fed into 1 µC/µP reset input.Ordering InformationAPX 8 03 - XX XX G - 7VoltagePackagePacking7 : Tape & ReelOutput typeGreen G : GreenSA : SOT2346:4.6344:4.3840:4.0031:3.0829:2.9326:2.6323:2.2503 : Active-Low, Open DrainSR : SOT23RAPX 8 03 D - 29 XX G - 7VoltagePackagePacking7 : Tape & ReelOutput typeGreen G : GreenSA : SOT2303 : Active-Low, Open DrainSR : SOT23R29:2.93DevicePackage CodePackaging (Note 4) 7” Tape and ReelQuantity Part Number Suffix APX803-XXSAG-7 SA SOT23 3000/Tape & Reel -7 APX803-XXSRG-7 SR SOT23R 3000/Tape & Reel -7 APX803D-29SAG-7 SA SOT23 3000/Tape & Reel -7 APX803D-29SRG-7SRSOT23R3000/Tape & Reel -7Notes: 4. Pad layout as shown on Diodes Inc. suggested pad layout document AP02001, which can be found on our website at /datasheets/ap02001.pdf.Marking Information(1) SOT23 and SOT23R( Top View )XX : Identification codeW : Week : A~Z : 1~26 week;X : A~Z : GreenY : Year 0~9a~z : 27~52 week; z represents 52 and 53 weekDevice Package Identification Code APX803-46SA SOT23 V3 APX803-44SA SOT23V4 APX803-40SA SOT23V5 APX803-31SA SOT23V6 APX803-29SA SOT23V7 APX803-26SA SOT23V8 APX803-23SA SOT23V9 APX803-46SR SOT23R S3 APX803-44SR SOT23R S4 APX803-40SR SOT23R S5 APX803-31SR SOT23R S6 APX803-29SR SOT23R S7 APX803-26SR SOT23R S8 APX803-23SR SOT23R S9 APX803D-29SA SOT23VN APX803D-29SR SOT23R SNPackage Outline Dimensions (All Dimensions in mm)(1) Package Type: SOT23 and SOT23RNotes: 5. Package outline dimensions as shown on Diodes Inc. package outline dimensions document AP02002, which can be found on our website at /datasheets/ap02002.pdf分销商库存信息:DIODESAPX803D-29SRG-7APX803D-29SAG-7。

IPB09N03_DataSheet

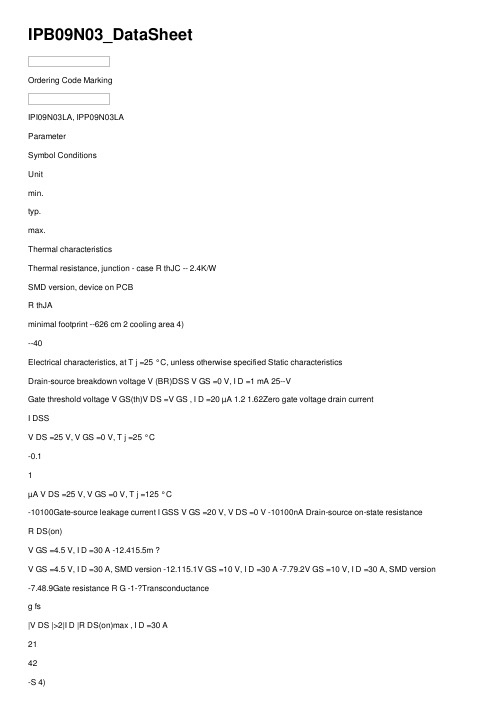

IPB09N03_DataSheetOrdering Code MarkingIPI09N03LA, IPP09N03LAParameterSymbol ConditionsUnitmin.typ.max.Thermal characteristicsThermal resistance, junction - case R thJC -- 2.4K/WSMD version, device on PCBR thJAminimal footprint --626 cm 2 cooling area 4)--40Electrical characteristics, at T j =25 °C, unless otherwise specified Static characteristicsDrain-source breakdown voltage V (BR)DSS V GS =0 V, I D =1 mA 25--VGate threshold voltage V GS(th)V DS =V GS , I D =20 µA 1.2 1.62Zero gate voltage drain currentI DSSV DS =25 V, V GS =0 V, T j =25 °C-0.11µA V DS =25 V, V GS =0 V, T j =125 °C-10100Gate-source leakage current I GSS V GS =20 V, V DS =0 V -10100nA Drain-source on-state resistanceR DS(on)V GS =4.5 V, I D =30 A -12.415.5m ?V GS =4.5 V, I D =30 A, SMD version -12.115.1V GS =10 V, I D =30 A -7.79.2V GS =10 V, I D =30 A, SMD version -7.48.9Gate resistance R G -1-?Transconductanceg fs|V DS |>2|I D |R DS(on)max , I D =30 A2142-S 4)Device on 40 mm x 40 mm x 1.5 mm epoxy PCB FR4 with 6 cm 2 (one layer, 70 µm thick) copper area for drain connection. PCB is vertical in still air.Values 1)Current is limited by bondwire; with an R thJC =2.4 K/W the chip is able to carry 64 A.2) See figure 33) T j,max =150 °C and duty cycle D <0.25 for V GS <-5 VIPI09N03LA, IPP09N03LA Parameter Symbol Conditions Unitmin.typ.max. Dynamic characteristicsInput capacitance C iss-12401649pF Output capacitance C oss-530704 Reverse transfer capacitance C rss-81122Turn-on delay time t d(on)-913ns Rise time t r-88132Turn-off delay time t d(off)-2233Fall time t f- 4.26Gate Charge Characteristics5)Gate to source charge Q gs- 4.4 5.8nC Gate charge at threshold Q g(th)- 2.0 2.6Gate to drain charge Q gd- 3.1 4.7 Switching charge Q sw- 5.57.9Gate charge total Q g-1014Gate plateau voltage V plateau- 3.5-VGate charge total, sync. FET Q g(sync)V DS=0.1 V,V GS=0 to 5 V-912nCOutput charge Q oss V DD=15 V, V GS=0 V-1115 Reverse DiodeDiode continous forward current I S--50A Diode pulse current I S,pulse--350Diode forward voltage V SD V GS=0 V, I F=50 A,T j=25 °C-0.98 1.2VReverse recovery charge Q rr V R=15 V, I F=I S,d i F/d t=400 A/µs--10nC5) See figure 16 for gate charge parameter definition T C=25 °CValuesV GS=0 V, V DS=15 V,f=1 MHzV DD=15 V, V GS=10 V,I D=25 A, R G=2.7 ?V DD=15 V, I D=25 A,V GS=0 to 5 VIPI09N03LA, IPP09N03LA Package OutlineP-TO263-3-2: OutlineFootprint PackagingIPI09N03LA, IPP09N03LA P-TO262-3-1: OutlineP-TO220-3-1: OutlinePackagingIPI09N03LA, IPP09N03LA Published byInfineon Technologies AGBereich KommunikationSt.-Martin-Stra?e 53D-81541 MünchenInfineon Technologies AG 1999All Rights Reserved.Attention please!The information herein is given to describe certain components and shall not be considered aswarranted characteristics.Terms of delivery and rights to technical change reserved.We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts started herein.Infineon Technologies is an approved CECC manufacturer.InformationFor further information on technology, delivery terms and conditions and prices, please contact your nearest Infineon Technologies office in Germany or our Infineon Technologies representatives worldwide (see address list).WarningsDue to technical requirements, components may contain dangerous substances.For information on the types in question, please contact your nearest Infineon Technologies office. Infineon Technologies' components may only be used in life-support devices or systems with the expressed written approval of Infineon Technologies if a failure of such components can reasonablybe expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implantedin the human body, or to support and/or maintain and sustain and/or protect human life. If they fail,it is reasonable to assume that the health of the user or other persons may be endangered.。

UD4803技术稳定datasheet

RatingSymbol Parameter N-Ch P-Ch Units V DS Drain-Source Voltage 40 -40 V V GS Gate-Sou r ce Voltage±20 ±20 V I D @T C =25℃ Continuous Drain Current, V GS @ 10V 1 23 -20 A I D @T C =100℃Continuous Drain Current, V GS @ 10V 118 -16 A I DM Pulsed Drain Current 246 -40 A EAS Single Pulse Avalanche Energy 328 66 mJ I AS Avalanche Current 17.8-27.2 A P D @T C =25℃Total Power Dissipation 425 31.3 W T STG Storage Temperature Range -55 to 150 -55 to 150 ℃ T JOperating Junction Temperature Range-55 to 150-55 to 150℃Symbol ParameterTyp.Max.UnitR θJA Thermal Resistance Junction-Ambient 1 --- 62 ℃/W R θJCThermal Resistance Junction-Case 1 --- 5 ℃/WBVDSS RDSON ID40V 26m Ω 23A -40V 40m Ω -20AThe UD4803 is the highest performance trench N-ch and P-ch MOSFETs with extreme high cell density , which provide excellent RDSON and gate charge for most of the synchronous buck converter applications . The UD4803 meet the RoHS and Green Product requirement 100% EAS guaranteed with full function reliability approved. zAdvanced high cell density Trench technology zSuper Low Gate Charge zExcellent CdV/dt effect decline z100% EAS Guaranteed z Green Device Available Featuresz High Frequency Point-of-Load Synchronous Buck Converter for MB/NB/UMPC/VGA z Networking DC-DC Power System z CCFL Back-light InverterTO252 Pin ConfigurationProduct SummerySymbol ParameterConditionsMin.Typ.Max.UnitBV DSSDrain-Source Breakdown VoltageV GS =0V , I D =250uA 40 --- --- V△BV DSS /△T J BVDSS Temperature Coefficient Reference to 25℃ , I D =1mA--- 0.034 --- V/℃V GS =10V , I D =12A --- 22 26R DS(ON)Static Drain-Source On-Resistance 2V GS =4.5V , I D =10A --- 28 35m ΩV GS(th) Gate Threshold Voltage 1.0 1.5 2.5 V △V GS(th) V GS(th) Temperature Coefficient V GS =V DS , I D =250uA --- -4.56 --- mV/℃V DS =32V , V GS =0V , T J =25℃ --- --- 1 I DSS Drain-Source Leakage Current V DS =32V , V GS =0V , T J =55℃ --- --- 5 uA I GSSGate-Source Leakage CurrentV GS =±20V , V DS =0V --- --- ±100nA gfs Forward Transconductance V DS =5V , I D =12A --- 8 --- S R g Gate Resistance V DS =0V , V GS =0V , f=1MHz --- 2.6 5.2 ΩQ gTotal Gate Charge (4.5V)---5.5---Q gs Gate-Source Charge --- 1.25 --- Q gd Gate-Drain Charge V DS =20V , V GS =4.5V , I D =12A--- 2.5 --- nC T d(on) Turn-On Delay Time --- 8.9 --- T r Rise Time--- 2.2 --- T d(off) Turn-Off Delay Time --- 41 --- T f Fall Time V DD =20V , V GS =10V , R G =3.3Ω I D =1A--- 2.7 --- nsC iss Input Capacitance --- 593 --- C oss Output Capacitance --- 76 --- C rss Reverse Transfer CapacitanceV DS =15V , V GS =0V , f=1MHz --- 56 ---pFSymbol ParameterConditionsMin.Typ.Max.UnitEASSingle Pulse Avalanche Energy 5V DD =25V , L=0.1mH , I AS =10A9 --- --- mJSymbol Parameter Conditions Min. Typ. Max.UnitI S Continuous Source Current 1,6 --- --- 23 AI SM Pulsed Source Current 2,6V G =V D =0V , Force Current --- --- 46 A V SD Diode Forward Voltage 2V GS =0V , I S =1A , T J =25℃ --- --- 1.2 VNote :1.The data tested by surface mounted on a 1 inch 2 FR-4 board with 2OZ copper.2.The data tested by pulsed , pulse width ≦ 300us , duty cycle ≦ 2%3.The EAS data shows Max. rating . The test condition is V DD =25V,V GS =10V,L=0.1mH,I AS =17.8A4.The power dissipation is limited by 150℃ junction temperature5.The Min. value is 100% EAS tested guarantee.6.The data is theoretically the same as I D and I DM , in real applications , should be limited by total power dissipation.Symbol ParameterConditionsMin.Typ.Max.UnitBV DSSDrain-Source Breakdown VoltageV GS =0V , I D =-250uA -40 --- --- V△BV DSS /△T J BV DSS Temperature Coefficient Reference to 25℃ , I D =-1mA--- -0.012 --- V/℃V GS =-10V , I D =-8A --- 32 40R DS(ON)Static Drain-Source On-Resistance 2V GS =-4.5V , I D =-4A ---52 65 m ΩV GS(th) Gate Threshold Voltage -1.0 -1.6 -2.5 V △V GS(th) V GS(th) Temperature Coefficient V GS =V DS , I D =-250uA --- 4.32 --- mV/℃V DS =-32V , V GS =0V , T J =25℃ --- --- 1 I DSS Drain-Source Leakage Current V DS =-32V , V GS =0V , T J =55℃ --- --- 5 uA I GSSGate-Source Leakage CurrentV GS =±20V , V DS =0V --- --- ±100nA gfs Forward Transconductance V DS =-5V , I D =-8A --- 12.6 --- SR g Gate Resistance V DS =0V , V GS =0V , f=1MHz --- 13 16 ΩQ gTotal Gate Charge (-4.5V)---9---Q gs Gate-Source Charge --- 2.54 --- Q gd Gate-Drain Charge V DS =-20V , V GS =-4.5V , I D =-12A--- 3.1 --- nC T d(on) Turn-On Delay Time --- 19.2 ---T r Rise Time --- 12.8 ---T d(off) Turn-Off Delay Time --- 48.6 --- T f Fall Time V DD =-15V , V GS =-10V , R G =3.3Ω, I D =-1A --- 4.6 --- nsC iss Input Capacitance --- 1004 ---C oss Output Capacitance --- 108 --- C rss Reverse Transfer CapacitanceV DS =-15V , V GS =0V , f=1MHz --- 80 ---pFSymbol ParameterConditionsMin.Typ.Max.UnitEASSingle Pulse Avalanche Energy 5V DD =-25V , L=0.1mH , I AS =-15A20 --- --- mJSymbol ParameterConditionsMin.Typ.Max.UnitI S Continuous Source Current 1,6 --- --- -20 AI SM Pulsed Source Current 2,6V G =V D =0V , Force Current --- --- -40 A V SDDiode Forward Voltage 2V GS =0V , I S =-1A , T J =25℃--- --- -1 VNote : 1.The data tested by surface mounted on a 1 inch 2FR-4 board with 2OZ copper. 2.The data tested by pulsed , pulse width ≦ 300us , duty cycle ≦ 2%3.The EAS data shows Max. rating . The test condition is V DD =-25V,V GS =-10V,L=0.1mH,I AS =-27.2A4.The power dissipation is limited by 150℃ junction temperature5.The Min. value is 100% EAS tested guarantee.6.The data is theoretically the same as I D and I DM , in real applications , should be limited by total power dissipation.1212101DSGS12T J ,Junction Temperature ( ℃)T J , Junction Temperature (℃)。

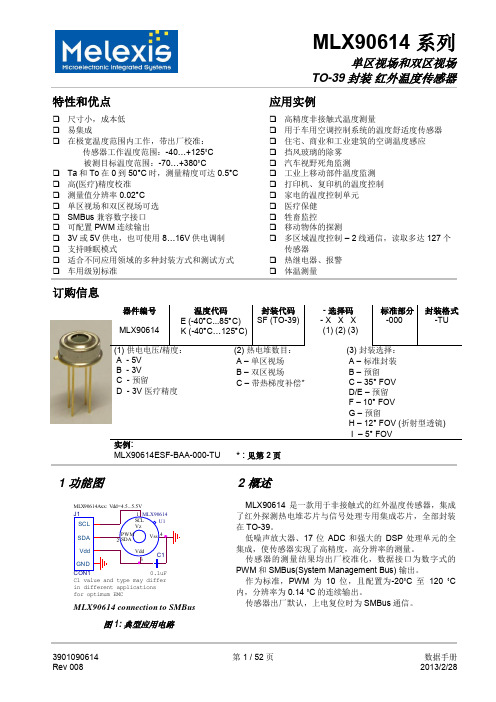

Datasheet MLX90614 中文 数据手册 rev008

10-位 PWM 输出模式是连续输出所测物体温度的标准配置,测量物体的温度范围为-20…120 °C,分辨 率为 0.14 °C。PWM 通过修改 EEPROM 内 2 个单元的值,实际上可以根据需求调整至任何温度范围,而这对 出厂校准结果并无影响。

传感器的测量结果均出厂校准化,数据接口为数字式的 PWM 和 SMBus(System Management Bus) 输出。

作为标准,PWM 为 10 位,且配置为-20˚C 至 120 ˚C 内,分辨率为 0.14 ˚C 的连续输出。

传感器出厂默认,上电复位时为 SMBus 通信。

3901090614 Rev 008

PWM 引脚也可配置为热继电器(输入是 To),这样可以实现简单且性价比高的恒温控制器或温度报警(冰 点/沸点)应用,其中的温度临界值是用户可编程的。在 SMBus 系统里,这个功能可以作为处理器的中断信号, 以此触发读取主线上从动器的值,并确定精度条件。

传感器有两种供电电压选择:5V 或 3V(电池供电)。其中,5V 也可简便的从更高供电电压(例如 8 至 16V)上通过外接元件调制。(具体请参考“应用信息”)

MLX90614 connection to SMBus

图 1: 典型应用电路

2 概述

MLX90614 是一款用于非接触式的红外温度传感器,集成 了红外探测热电堆芯片与信号处理专用集成芯片,全部封装 在 TO-39。

低噪声放大器、17 位 ADC 和强大的 DSP 处理单元的全 集成,使传感器实现了高精度,高分辨率的测量。

6639S-1-103;6639S-1-102;6639S-1-104;6639S-1-202;6639S-1-203;中文规格书,Datasheet资料

22.23 (.875) DIA.

3.18 (.125)

6639

11.25 .38 (.443 .015)

1.57 (.062)

Байду номын сангаас

22.23 (.875) DIA.

.51 (.020) REF

19.81 (.780) DIA.

12.70 .79 (.500 .031)

10.317+.000/-.051 (.4062+.000/-.002)

DIA.

6.342+.000/-.008

(.2497+.0000/-.0003) DIA. SHAFT .25

45 5 (.010) CHAMFER 1.19 1.60

SLOT (.047) X (.063)

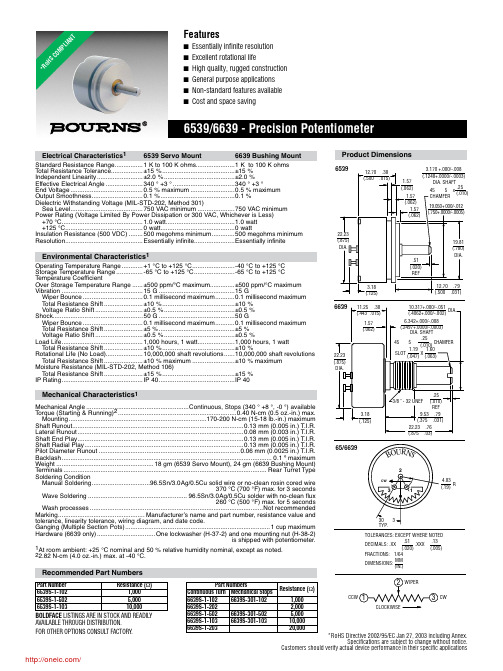

Mechanical Characteristics1

Mechanical Angle ..........................................................Continuous, Stops (340 ° +8 °, -0 °) available Torque (Starting & Running)2 ...................................................................0.40 N-cm (0.5 oz.-in.) max.

Sea Level......................................... 750 VAC minimum .....................750 VAC minimum Power Rating (Voltage Limited By Power Dissipation or 300 VAC, Whichever is Less)

CN803-809-810规格书

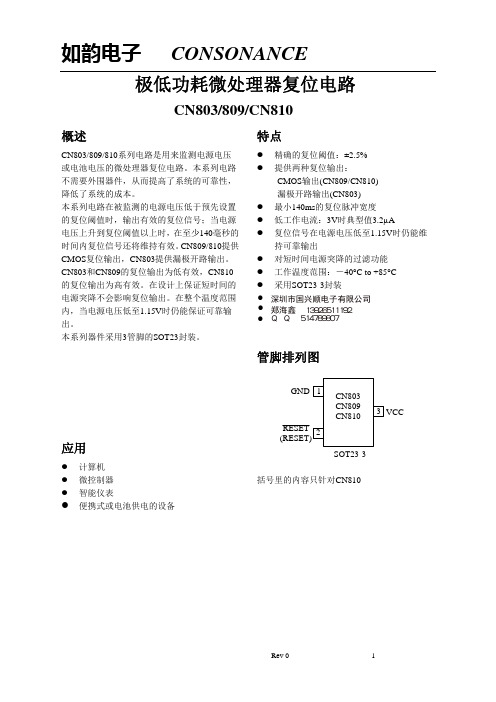

如韵电子CONSONANCE极低功耗微处理器复位电路 CN803/809/CN810概述CN803/809/810系列电路是用来监测电源电压或电池电压的微处理器复位电路。

本系列电路不需要外围器件,从而提高了系统的可靠性,降低了系统的成本。

本系列电路在被监测的电源电压低于预先设置的复位阈值时,输出有效的复位信号;当电源电压上升到复位阈值以上时,在至少140毫秒的时间内复位信号还将维持有效。

CN809/810提供CMOS复位输出,CN803提供漏极开路输出。

CN803和CN809的复位输出为低有效,CN810的复位输出为高有效。

在设计上保证短时间的电源突降不会影响复位输出。

在整个温度范围内,当电源电压低至1.15V时仍能保证可靠输出。

本系列器件采用3管脚的SOT23封装。

应用●计算机●微控制器●智能仪表●便携式或电池供电的设备特点●精确的复位阈值:±2.5%●提供两种复位输出:-CMOS输出(CN809/CN810)-漏极开路输出(CN803)●最小140ms的复位脉冲宽度●低工作电流:3V时典型值3.2µA●复位信号在电源电压低至1.15V时仍能维持可靠输出●对短时间电源突降的过滤功能●工作温度范围:-40°C to +85°C●采用SOT23-3封装管脚排列图GNDRESETVCCSOT23-3括号里的内容只针对CN810深圳市国兴顺电子有限公司郑海鑫 139****1192Q Q 514789807●●器件功能一览表器件型号复位阈值复位电平 高有效或低有效输出类型打印标记CN809L 4.63V 低 CMOS AAAA CN810L 4.63V 高 CMOS AGAA CN809M 4.38V 低 CMOS ABAA CN810M 4.38V 高 CMOS AHAA CN809J 4.00V 低 CMOSCWAA CN809T 3.08V 低 CMOS ACAA CN810T 3.08V 高 CMOS AJAA CN809S 2.93V 低 CMOS ADAA CN810S 2.93V 高 CMOS AKAA CN809R 2.63V 低 CMOS AFAA CN810R 2.63V 高 CMOS ALAA CN803S 2.93V 低 漏极开路 ABC CN803R 2.63V低漏极开路 ABD功能框图D图1 功能框图管脚描述管脚序号 符号 功能描述1 GND 地(CN809)CMOS 复位输出(CN809)。

MLX90393_Datasheet_rev001

Part No. Temperature Code Package Code Silicon Version Option Code Packing Format MLX90393 S (-20°C to 85°C) LQ (QFN16 3x3mm) ABA 011 RE (Reel)1. ScopeThis document serves as a specification for a 3-axis magnetometer targeting low-power applications. The IC is based on the Hall-effect and the patented Triaxis® technology from Melexis. The output signals (raw X, Y, Z Magnetic data and Temperature data) will be provided through the I2C fast mode protocol, or via half-duplex SPI (3- or 4-wire). There is an on-board non-volatile memory to store calibration data on-chip.Figure 1: High-level Block DiagramV DDV SS2.Absolute Maximum RatingsThe MLX90393 can withstand the conditions described in the table below for short periods of time; they do not constitute conditions for normal operation.Parameter Remark Min Nom Max Unit V DD_MAX Analog Supply Voltage Limits -0.3 4 VV DD_IO_MAX Digital IO Supply Limits -0.3 min(4, V DD+0.3) V T STORAGE Storage (idle) temperature range -50 125 °C ESD HBM According to AEC-Q100-002 2.5 kV ESD CDM According to AEC-Q100-011-B (QFN) 750 V3.Thermal SpecificationThe MLX90393 has an on-board temperature sensor which measures the temperature of the MLX90393 sensor. The temperature can be read out via the communication protocol in a digital format.Parameter Remark Min Nom Max Unit T RES Temperature sensor resolution 45.2 LSB/°C T25Temperature sensor output at 25°C 46244 LSB16u T LIN Temperature Linearity(1)+/-3 °CT OPERATING Operating temperature range -20 25 85 °C(1)The linearity is defined as the best fit curve through the digital temperature outputs over the entiretemperature range. It includes ADC non-linearity effects.4.Electrical SpecificationThe specifications are applicable at 25degC, unless specified otherwise, and for the complete supply voltage range.(1)Standby current corresponds to the current consumed in the digital, where not the main oscillator isrunning which is used for analog sequencing, but only the low-power oscillator. This standby current is present in Burst mode; whenever the ASIC is counting down to start a new conversion.(2)Idle current is the current that is drawn by the ASIC in the IDLE mode, where it can only receive newcommands on the communication bus, but all other blocks are disabled. The analog (excluding the power-on-reset block) is disconnected, only the digital IO part allows clocking of a few vital gates.5.Timing SpecificationThe specifications are applicable at 25degC, unless specified otherwise, and for the complete supply voltage range.(1)This conversion time is defined as the time to acquire a single axis of the magnetic flux density.When measuring multiple axes, they are obtained through time-multiplexing, i.e. X(t), Y(t+T CONVM) and Z(t+2*T CONVM). The conversion time is programmable through parameters OSR and DIG_FILT for magnetic conversion time and OSR2 for temperature conversion time. The conversion sequence is always TXYZ, the opposite of the ZYXT argument of the command set.(2)The time T INTERVAL is defined as the time between the end of one set of measurements (anycombination of TXYZ) and the start of the following same set of measurements in BURST and WOC mode. As a result of this, the maximum output data rate is not only a function of T INTERVAL but equals 1/(T CONV_BURSTWOC + T INTERVAL).(3)6.Magnetic SpecificationThe specifications are applicable at 25degC, unless specified otherwise, and for the complete supply voltage range.(1)The offset thermal drift is defined as the deviation at 0Gauss from the output with respect to theoutput at 25°C when sweeping the temperature. The highest gradient (µT/°C) typically occurs at 85°C. The spec value is based on characterization on limited sample size at GAIN_SEL=0x7 and RES_XYZ=0x00.(2)The total axis sensitivity is programmable to support different applications, but has no AutomaticGain control on-chip as do the other angular position sensors from Melexis. The highest gain corresponds to at least the minimum +/-4.8mT magnetic measurement range and the magnetic resolution defined by SENS ii.(3)The sensitivity thermal drift is expressed as a band around the sensitivity at 25°C. It is applicable onwafer level trimming, but can be influenced by packaging (overmolding).,RES Z} X YFigure 2: XY axis RMS noise versus conversion time, expressed in mGauss for GAIN_SEL = 0x7Figure 3: Z axis RMS noise versus conversion time, expressed in mGauss for GAIN_SEL = 0x77.Functional SpecificationThe MLX90393 can operate in 3 modes:∙Burst mode: The ASIC will have a programmable data rate at which it willoperate. This data rate implies auto-wakeup and sequencing of the ASIC,flagging that data is ready on a dedicated pin (INT/DRDY). The maximumdata rate corresponds to continuous burst mode, and is a function of thechosen measurement axes. For non-continuous burst modes, the timeduring which the ASIC has a counter running but is not doing an actualconversion is called the Standby mode (STBY).∙Single Measure mode: The master will ask for data via the correspondingprotocol (I2C or SPI), waking up the ASIC to make a single conversion,immediately followed by an automatic return to sleep mode (IDLE) until thenext polling of the master. This polling can also be done by strobing the TRGpin instead, which has the same effect as sending a protocol command for asingle measurement.∙Wake-Up on Change: This mode is similar to the burst mode in the sensethat the device will be auto-sequencing, with the difference that themeasured component(s) is/are compared with a reference and in case thedifference is bigger than a user-defined threshold, the DRDY signal is set onthe designated pin. The user can select which axes and/or temperature fallunder this cyclic check, and which thresholds are allowed.The user can change the operating mode at all time through a specific command on the bus. The device waits in IDLE mode after power-up, but with a proper user command any mode can be set after power-up. Changing to Burst or WOC mode, coming from Single Measure mode, is always accompanied by a measurement first. The top-level state diagram indicating the different modes and some relevant timing is shown below in Figure 4. In the Measure state, the MDATA flag will define which components will be measured (ZYXT). The order of conversion is defined as TXYZ and can not be modified by the user, only the combination of axes is a degree of freedom.Arrows indicated in grey are the direct result of an Exit command. The main difference between STANDBY and WOC_IDLE is that in STANDBY mode, all analog circuitry is ready to make a conversion, but this is accompanied by a larger current consumption than IDLE mode. For burst mode this extra current consumption is justified because the emphasis is more on accurate timing intervals, avoiding the delay of T STBY before conversion and supporting an efficient continuous burst mode without standby overhead.It is the user’s responsibi lity to read back the measured data, the MLX90393 acts as a pure slave. Even in burst mode and WOC mode when the MLX90393 is auto-sequencing, the master will be responsible for collecting the acquired sensor data.TIMEm*T CONVM + T CONVTT ACTIVET STBYT PORFigure 4: Top-level state diagram with indication of timings7.1 Burst modeWhen the sensor is operating in burst mode, it will make conversions at specific time intervals. The programmability of the user is the following:∙ Burst speed (T INTERVAL ) through parameter BURST_DATA_RATE ∙ Conversion time (T CONV ) through parameters OSR, OSR2 and DIG_FILT∙ Axes/Temperature (MDATA) through parameter BURST_SEL or via the command argument (ZYXT)Whenever the MLX90393 has made the selected conversions (based on MDATA), the DRDY signal will be set (active H) on the INT and/or INT/TRG pin to indicate that the data is ready for readback. It will remain high until the master has sent the command to read out at least one of the converted quantities (ZYXT). Should the master have failed to read out any of them by the time the sensor has made a new conversion, the INT/DRDY pin will be strobed low for 10us, and the next rising edge will indicate a new set of data is ready.7.2 Single Measurement modeWhenever the sensor is set to this mode (or after startup) the MLX90393 goes to the IDLE state where it awaits a command from the master to perform a certain acquisition. The duration of the acquisition will be the concatenation of the T STBY, T ACTIVE, m*T CONVM(with m # of axes) and T CONVT. The conversion time will effectively be programmable by the user (see burst mode), but is equally a function of the required axes/temperature to be measured.Upon reception of such a polling command from the master, the sensor will make the necessary acquisitions, and set the DRDY signal high to flag that the measurement has been performed and the master can read out the data on the bus at his convenience. The INT/DRDY will be cleared either when:∙The master has issued a command to read out at least one of the measured components∙The master issues an Exit (EX) command to cancel the measurement∙The chip is reset, after POR (Power-on reset) or Reset command (RT)7.3Wake-Up on Change modeThe Wake-Up on Change (WOC) functionality can be set by the master with as main purpose to only receive an interrupt when a certain threshold is crossed. The WOC mode will always compare a new burst value with a reference value in order to assess if the difference between both exceeds a user-defined threshold. The reference value is defined as one of the following:∙The first measurement of WOC mode is stored as reference value once, as a result of a measurement. This measurement at “t=0” is then the basis for comparison or,∙The reference for acquisition(t) is always acquisition(t-1), in such a way that the INT signal will only be set if the derivative of any component exceeds a threshold.∙The in-application programmability is the same as for burst mode, but now the thresholds for setting the interrupt are also programmable by the user, as well as the reference, if the latter is data(t=0) or data(t-1).8.Digital SpecificationThe supported protocols are I2C and SPI. The SENB/CS pin is used to define the protocol to be used:∙/CS = 0 for SPI, addressing the MLX90393 slave in SPI mode (3- and 4-wire), but releasing this line in between commands (no permanent addressing allowed)∙/CS = 1 for I2C, addressing the MLX90393 slave when the correct address is transmitted over the bus (permanently kept high)To make sure the activity on the SPI bus can not be accidentally interpreted as I2C protocol, programming bits are available in the memory of the MLX90393 to force the communication mode. It concerns the COMM_MODE[1:0] bits with the following effect:8.1Command ListThe MLX90393 only listens to a specific set of commands. Apart from the Reset command, all commands generate a status byte that can be read out. The table below indicates the 10 different commands that are (conditionally) accepted by the MLX90393. The MLX90393 will always acknowledge a command in I2C, even if the command is not a valid command. Interpreting the associated status byte is the method for verification of command acceptance.The argument for the volatile memory access commands (RR/WR) «abc» should be set to 0x0h, in order to get normal read-out and write of the memory.The argument in all mode-starting commands (SB/SW/SM) is a nibble specifying the conversions to be performed by the sensor in the following order «zyxt». For example, if only Y axis and temperature are to be measured in Single Measurement mode the correct command to be transmitted is 0x35h. The sequence of measurement execution on-chip is inverted to «TXYZ», so T will be measured before X, followed by Y and finally Z. By issuing an all-zero «zyxt» nibble, the BURST_SEL value from RAM will be used instead of the empty argument of the command.8.2Status ByteThe status byte is the first byte transmitted by the MLX90393 in response to a command issued by the master. It is composed of a fixed combination of informative bits:∙MODE bitsthese bits define in which mode the MLX90393 is currently set. Whenever a mode transition command is rejected, the first status byte after this command will have the expected mode bit cleared, which serves as an indication that the command has been rejected, next to the ERROR bit. The SM_MODE flag can be the result of an SM command or from raising the TRG pin when TRG mode is enabled in the volatile memory of the MLX90393.∙ERROR bitthis bit is set in case a command has been rejected or in case an uncorrectable error is detected in the memory, a so called ECC_ERROR. A single error in the memory can be corrected (see SED bit), two errors can be detected and will generate the ECC_ERROR. In such a case all commands but the RT (Reset) command will be rejected. The error bit is equally set when the master is reading back data while the DRDY flag is low.∙SED bitthe single error detection bit simply flags that a bit error in the non-volatile memory has been corrected. It is purely informative and has no impact on the operation of the MLX90393.∙RS bitwhenever the MLX90393 gets out of a reset situation –both hard and soft reset –the RS flag is set to highlight this situation to the master in the first status byte that is read out. As soon as the first status byte is read, the flag is cleared until the next reset occurs.D[1:0] bitsthese bits only have a meaning after the RR and RM commands, when data is expected as a response from the MLX90393. The number of response bytes correspond to 2*D[1:0] + 2, so the expected byte counts are either 2, 4, 6 or 8. For commands where no response is expected, the content of D[1:0] should be ignored.8.3SPI CommunicationThe MLX90393 can handle SPI communication at a bitrate of 10Mhz. The SPI communication is implemented in a half-duplex way, showing high similarities with I2C communication, but addressing through the \CS (Chip Select) pin instead of through bus arbitration. The half-duplex nature is at the basis of the supported 3-wire SPI operation. SPI mode 3 is implemented: CPHA=1 (data changed on leading edge and captured on trailing edge, and CPOL=1 (high level is inactive state). The Chip Select line is active-low.The communication is also bundled in bytes, equally MSB first and MSByte first. A command can of course consist of more than 1 byte (refer to Chapter 8.1) as can the response be from the MLX90393 in the form of multiple bytes after the status byte (not shown in Figure 5)COMMAND[7:0]SCL MOSI 1234567812345678MISO/CS STATUS_BYTE[7:0]X (4-wire SPI) or Z (3-wire SPI)Z (3 & 4-wire SPI)ADDNADDFigure 5: SPI communication example8.4 I 2C CommuncationI 2C AddressThe I 2C address is made up of some hard-coded bits and a memory written value as follows:I2C_ADDR[6:0] = {EE_I2C_ADDR[4:0],A 1,A 0} with A i the user-selectable active-high value of the input pads of the MLX90393, referred to the V DD supply system and EE_I2C_ADDR[4:0] default programmed to 03h, but user accessible for overwrite.I 2C PrincipleThe MLX90393 supports I 2C communication in both Standard Mode and Fast Mode. Bytes are transmitted MSB first, and in order to reconstruct words, the bytes need to be concatenated MSByte first. The general principle of communication is always the same:∙ Initiating the communication is always done by the Master (Start condition S)∙ Addressing the Slave (MLX90393) followed by a cleared bit to indicate the Master intends to writesomething to the specific addressed Slave ∙ Acknowledging by the Slave if the transmitted address corresponds to the Slave’s I 2C address. If thelatter isn’t the case, any further activity on the bus except a Sr (Start Repeat) and P (Stop) condition will be ignored by the MLX90393 ∙ Sending a Command Byte by the Master, as depicted in Figure 6. The Slave will always acknowledgethis, even if it is an unrecognized command. A command such as WR and RR consist of more than 1 byte, which can then be transmitted sequentially over the I 2C bus. Referring to Figure 6 the COMMAND byte should then be a sequence of C OMMAND byte1, byte2, etc… ∙ Issuing a Start Repeat (Sr) condition by the Master in order to restart the addressing phase∙Addressing the Slave (MLX90393) followed by a set bit to indicate the Master intends to read something from the specific addressed Slave∙Acknowledging by the Slave if the transmitted address corresponds to the Slave’s I2C address. If the latter isn’t the case, any further activity on the bus except a Sr (Start Repeat) and P (Stop) condition will be ignored by the MLX90393∙Transmitting the Status Byte by the Slave, who is in control of the bus. Following the RR and RM commands the sensor returns additional data bytes after the status byte.∙Acknowledging by the Master if the data is well received∙Generating a Stop condition (P) by the masterThe Master controlled bus activity is shown in blue, the Slave controlled bus activity is shown in orange. In case a command is longer than a single byte (see Table 6), the bytes are transmitted sequentially before generating the Start Repeat (Sr) condition.I2C_ADDR[6:0]W ACKSCOMMAND[7:0]ACKI2C_ADDR[6:0]R ACK Sr STATUS_BYTE[7:0]ACKSCL SDA SCL SDA 123456789123456789123456789P 123456789Figure 6: Default I2C communication example with status byte readbackThe same applies to the Slave responses: following RR and RM commands, the Slave response is more than just the Status Byte. There as well, the data is partitioned in bytes that are transmitted sequentially by the slave. It is the Master’s responsibility to issue enough clocking p ulses to read back all the data. Finding out how many bytes is possible by decoding the Status Byte information, see Section Status Byte.Finally the master is also free to not read back the status byte when issuing a command. In doing so, he loses the ability to see if the command was received properly by the MLX90393. Moreover, the first SM command issued by the master after power-up or reset should have the status byte read back in order to get valid measurement data back.9. Memory MapThe MLX90393 has 1kbit of non-volatile memory, and the same amount of volatile memory. Each memory consists out of 64 addresses containing 16 bit words. The non-volatile memory has automatic 2-bit error detection and 1-bit error correction capabilities per address. The handling of such corrections & detections is explained in Section Status Byte. The memory is split in 2 areas:∙ Customer area [address 0x00h to 0x1Fh] ∙ Melexis area [address 0x20h to 0x3Fh]The RR and WR commands impact the volatile memory only, there no direct access possible to the non-volatile memory. The customer area of the volatile memory is bidirectionally accessible to the customer; the Melexis area is write-protected. Only modifications in the blue area are allowed with the WR command. The adjustments in the customer area can be stored in the permanent non-volatile memory with the STORE command HS, which copies the entire volatile memory including the Melexis area to the non-volatile one. With the HR command the non-volatile memory content can be recalled to the volatile memory, which can restore any modifications due to prior WR commands. The HR step is performed automatically at start-up of the ASIC, either through cold reset or warm reset with the RT command. The above is graphically shown in Figure 7.Figure 7: The memories of the MLX90393, their areas and the impacting commands.The customer area houses 3 types of data:∙Analog configuration bits∙Digital configuration bits∙Informative (free) bitsThe latter can be filled with customer content freely, and covers the address span from (and including) 0x0Ah to 0x1Fh, a total of 352 bits. The memory mapping of volatile and non-volatile memory on address level is identical. The volatile memory map is given in Figure 8.Figure 8: Customer area memory map.The non-volatile memory can only be written (HS store command) if pin VDD is supplied with 3.3V minimum, otherwise the write sequence can not be performed in a reliable way. Additionally, this HS command was designed to be used as one-time calibration, but not as multi write-cycle memory within the application. In case memory is written within the application, the number of write cycles should be kept to a minimum. There is no limit to the write cycles in the volatile memory (WR write command).9.1Parameter DescriptionThe meaning of each customer accessible parameter is explained in this section. The customer area of both the volatile and the non-volatile memory can be written through standard SPI and I2C communication, within the application. No external high-voltages are needed to perform such operations, nor access to dedicated pins that need to be grounded in the application.ANA_RESERVED_LOW : Reserved IO trimming bitsBIST : Enabled the on-chip coil, applying a Z-field [Built-In Self Test]Z_SERIES : Enable all plates for Z-measurementGAIN_SEL[2:0] : Analog chain gain setting, factor 5 between min and max code HALLCONF[3:0] : Hall plate spinning rate adjustmentTRIG_INT_SEL : Puts TRIG_INT pin in TRIG mode when cleared, INT mode otherwise COMM_MODE[1:0] : Allow only SPI [10b], only I2C [11b] or both [0Xb] according to CS pin WOC_DIFF : Sets the Wake-up On Change based on Δ{sample(t),sample(t-1)} EXT_TRIG : Allows external trigger inputs when set, if TRIG_INT_SEL = 0 TCMP_EN : Enables on-chip sensitivity drift compensationBURST_SEL[3:0] : Defines the MDATA in burst mode if SB command argument = 0 BURST_DATARATE[6:0] : Defines T INTERVAL as BURST_DATA_RATE * 20msOSR2[1:0] : Temperature sensor ADC oversampling ratioRES_XYZ[5:0] : Selects the desired 16-bit output value from the 19-bit ADCDIG_FILT[1:0] : Digital filter applicable to ADCOSR[1:0] : Magnetic sensor ADC oversampling ratioSENS_TC_HT[7:0] : Sensitivity drift compensation factor for T < T REFSENS_TC_LT[7:0] : Sensitivity drift compensation factor for T > T REFOFFSET_i[15:0] : Constant offset correction, independent for i = X, Y, ZWOi_THRESHOLD[15:0] : Wake-up On Change threshold, independent for i = X, Y, Z and T10.Packaging Specification10.1QFN packageThe MLX90393 shall be delivered in a QFN package as shown below in Figure 9.XZYFigure 9: Package Outline DrawingThe sensing elements – Hall plates with the patented IMC technology – are located in the center of the die, which on its turn is located in the center of the package. The pinout (in name and function) is given in Table 7 below.11.Standard information regarding manufacturability of Melexisproducts with different soldering processesOur products are classified and qualified regarding soldering technology, solderability and moisture sensitivity level according to following test methods:Reflow Soldering SMD’s (Surface Mount Devices)IPC/JEDEC J-STD-020Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices (classification reflow profiles according to table 5-2)∙EIA/JEDEC JESD22-A113Preconditioning of Nonhermetic Surface Mount Devices Prior to Reliability Testing (reflow profiles according to table 2)Wave Soldering SMD’s (Surface Mount D evices) and THD’s (Through Hole Devices)∙EN60749-20Resistance of plastic- encapsulated SMD’s to combined effect of moisture and soldering heat∙EIA/JEDEC JESD22-B106 and EN60749-15Resistance to soldering temperature for through-hole mounted devicesIron Soldering THD’s (Through Hole Devices)∙EN60749-15Resistance to soldering temperature for through-hole mounted devicesSolderability SMD’s (Surface Mount D evices) and THD’s (Through Hole Devices)∙EIA/JEDEC JESD22-B102 and EN60749-21SolderabilityFor all soldering technologies deviating from above mentioned standard conditions (regarding peak temperature, temperature gradient, temperature profile etc) additional classification and qualification tests have to be agreed upon with Melexis. The application of Wave Soldering for SMD’s is allowed only after consulting Melexis regarding assurance of adhesive strength between device and board.Melexis recommends reviewing on our web site the General Guidelines soldering recommendation (/Quality_soldering.aspx) as well as trim&form recommendations (/Assets/Trim-and-form-recommendations-5565.aspx).Melexis is contributing to global environmental conservation by promoting lead free solutions. For more information on qualifications of RoHS compliant products (RoHS = European directive on the Restriction Of the use of certain Hazardous Substances) please visit the quality page on our website: /quality.aspx12.ESD PrecautionsElectronic semiconductor products are sensitive to Electro Static Discharge (ESD). Always observe Electro Static Discharge control procedures whenever handling semiconductor products.13.Recommended Application Diagram13.1I2CA1A0 I2C Address13.2SPI14.Table of Contents1.Scope (1)2.Absolute Maximum Ratings (2)3.Thermal Specification (2)4.Electrical Specification (2)5.Timing Specification (3)6.Magnetic Specification (6)7.Functional Specification (9)7.1Burst mode (11)7.2Single Measurement mode (12)7.3Wake-Up on Change mode (12)8.Digital Specification (13)8.1Command List (13)8.2Status Byte (14)8.3SPI Communication (15)8.4I2C Communcation (16)I2C Address (16)I2C Principle (16)9.Memory Map (19)9.1Parameter Description (20)10.Packaging Specification (22)10.1QFN package (22)11.Standard information regarding manufacturability of Melexis products with different soldering processes (23)12.ESD Precautions (24)13.Recommended Application Diagram (25)13.1I2C (25)13.2SPI (25)。

AMP connector