数字信号处理技术2.9串行口

DSP硬件结构.ppt

独立的DMA总线和控制器

有一组或多组独立的DMA总线, 与CPU的程序总线和数据总线并行工 作,在不影响CPU工作的条件下, DMA速度目前已达800 MBps(Millions Bytes/s )

DSP技术讲义,2010

1.0 TMS320C2000系列DSP

• TI公司的TMS320C2000系列DSP控制器,集成了flash存储器、 高速A/D和可靠的CAN模块,主要应用于数字化的控制。

DSP技术讲义,2010

3.在片外围电路(Peripherals on chip)

● 具有软件可编程等待状态发生器 ● 设有可编程分区转换逻辑电路 ● 带有内部振荡器或外部时钟源的片内锁相环(PLL)发 生器 ● 支持全双工操作的串行口,可进行8位或16位串行通信 ● 带4位预定标器的16位可编程定时器 ● 设有与主机通信的并行接口(HPI) ● 具有外部总线判断控制,以断开外部的数据总线、地 址总线和控制信号 ● 数据总线具有总线保持特性

134

135

136

137

138

139

140

141

142

143

144

1

108

2

107

3

106

4

105

5

104

6

103

7

102

8

101

9

100

10

99

11

98

12

97

13

96

14

95

15 16

TMS320VC5402

94 93

17

92

18

91

19

90

20

89

21

dsp

摘要随着数字信号处理技术在通讯、多媒体、信息家电等各个领域得到了广泛的应用,数字信号处理器(DSP)无论从制造工艺、体系结构等方面都取得了巨大的发展。

因此设计有自主产权的DSP处理器IP核具有很高的实用价值及意义。

通过对片上串行接口的模块划分,完成了串口寄存器模块、时钟与帧同步信号控制器模块、接收控制器模块和发送控制器模块的详细设计和FPGA验证。

其中,设计了一种采用一个主控状态机和两个从状态机协同工作的层次化结构方案,规整高效地实现了接收控制器模块和发送控制器模块。

通过对6通道DMA控制器的模块划分,完成了内部寄存器组、优先级编码模块、内部寄存器寻址、地址产生模块和有限状态机等模块的详细设计和FPGA验证。

其中,设计了一种采用模计数和循环比较的结构方案,实现了对6个DMA通道进行分级循环优先级控制的机制。

论文从主机接口(HPI)寄存器、状态机两个方面论述和设计实现一个8位外总线接口。

并完成了内部定时器和可编程等待状态发生器的设计。

目前该兼容DSP处理器的设计已经完成,通过了FPGA验证,能运行基本的功能验证程序,为进一步研发该DSP的可重用IP模块打下了基础。

关键字:数字信号处理器,串行接口,直接寄存器访问控制器,主机接口、定时器、等待状态发生器引言:近年来,我国电子信息产业和市场高速增长,不仅推动了DSP处理器芯片的广泛应用,而且吸引了国内外众多厂商涉足我国DSP处理器产品市场,促使DSP处理器芯片需求量持续增大,市场竞争日渐激烈。

尽管DSP处理器在我国的应用已经有了相当的基础,而且有lO多家集成电路设计企业从事DSP系统及相关产品的开发与应用,但目前在国内芯片市场上还很少见到国内厂商自己的DSP 处理器芯片。

因此研制有自主知识产权的DSP处理器设计技术,以及相应的DSP 系统设计技术与应用能力,仍然是我国科技工作者和IT企业的重大挑战。

1.2.1 DSP处理器的发展史人们对DSP技术的研究兴趣开始于二十世纪七十年代,主要是研究诸如调制解调器和集中转接系统等电信设备。

数字信号处理课程设计

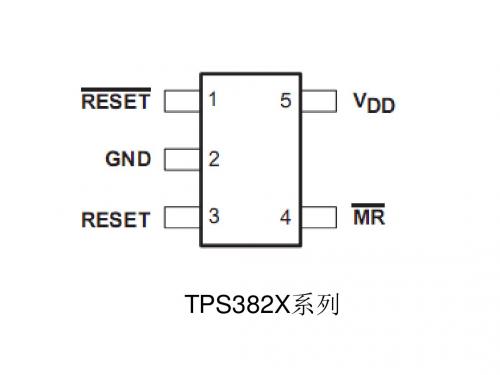

目录一、摘要.................................................................................................................................... - 2 -1、DSP简介 ................................................................................................................... - 2 -2、系统框图...................................................................................................................... - 3 -二、概述.................................................................................................................................... - 4 -1、系统框图描述...................................................................................................................... - 4 -2、设计目的.............................................................................................................................. - 4 -三、系统设计............................................................................................................................ - 4 -1、总体方案设计 ........................................................................................................... - 4 -2、设计原理.................................................................................................................... - 4 -四、硬件设计............................................................................................................................ - 6 -1、系统硬件框图.............................................................................................................. - 6 -2、 TMS320C5402简介....................................................................................................... - 6 -3、电源设计...................................................................................................................... - 7 -4、复位电路设计.............................................................................................................. - 7 -5、时钟电路设计.............................................................................................................. - 8 -6、 D/A数据转换通道....................................................................................................... - 8 -7、独立键盘设计.............................................................................................................. - 9 -五、软件设计.......................................................................................................................... - 10 -1、正弦波形产生原理.................................................................................................... - 10 -2、设计方案.................................................................................................................... - 10 -3、中断程序流程图........................................................................................................ - 11 -4、正弦信号发生器程序清单........................................................................................ - 12 -六、实验结果.......................................................................................................................... - 18 -1、CCS工程项目的调试 ............................................................................................... - 18 -2、仿真结果...................................................................................................................... - 18 -七、总结.................................................................................................................................. - 21 -八、参考文献.......................................................................................................................... - 21 -一、摘要1、DSP简介数字信号处理(Digital Signal Processing,简称DSP)是一门涉及许多学科而又广泛应用于许多领域的新兴学科。

数字信号处理 串行通信接口(SCI)

12

SCI的增强特性

SCIFIFO描述 发送器与接收器各有16级FIFO,有3个专门的寄存器控制; 复位时,SCI工作于标准模式,禁止FIFO功能。

自动波特率检测 自动检测SCI通信的波特率,并刷新BRR寄存器。

(BRR+1)×8

注意:如果BRR=0,则波特率=LSPCLK/16.

SCICLK×8

1≤BRR≤65535,如果BRR=0,等同于BRR=1

BRR

SYSCLKOUT/4

6

SCI多处理器通信

在同一条串行连线上,多处理器通信模式允许一个处理器 (主机)向串行线上其它处理器(从机)发送数据。

一条串行线上每刻只能有一个节点发送数据(发送使能控 制),但可以多个节点同时接收数据。 1、地址字节

13

第7章 DSP片上串行通信外设

7.3 串行通信接口(SCI)

串行通信概述

串行通信:通信线上既传输数据信息,也传输联络信息,因 此收发双方就必须要有通信协议。特点是串行传输成本低, 适用于远距离通信,但传输速度低。 串行通信分类:1)同步通信;2)异步通信。

同步通信:发送器和接收器通常使用同一时钟源来同步。方法是在发送器 发送数据时同时包含了时钟信号,接收器利用该时钟信号进行接收。 异步通信:收发双方的时钟不是同一个时钟,是由双方各自的时钟实现数 据的发送和接收。但要求双方使用同一标称频率,允许有一定偏差。 同步方法:要正确传输字符,准确读取每一位是必须用各自的时钟同步的, 为克服不同时钟的偏差,每个字符都有一个起始位进行同步。

方法二: 利用TXWAKE位产生11位的空闲时间 1)首先置位TXWAKE(SCICTL1.3),控制数据发送特征; 2)写一个数据字节(内容不重要)到SCITXBUF,发送一个

定时器控制寄存器

专用的硬件乘法器

• 在通用的微处理器中,乘法指令是

由一系列加法来实现的,故需许多 个指令周期来完成 • DSP具有专用的硬件乘法器,乘法可 在一个指令周期内完成

1)多总线结构

2)40位算术逻辑单元(ALU)

3)17×17位并行乘法器

4)比较、选择和存储单元(CSSU) 5)指数编码器 6)两个地址发生器

为了快速实现数字信号处理运算,DSP芯片 一般都采用特殊的硬件结构,正是这种针对运算 的特殊的结构和设计,使它区别于通常的CPU或 MCU(微控制器)。 TMS320系列DSP芯片的主要硬件特点包括:哈 佛结构、流水线操作、多总线、多处理单元、硬 件配置强、耗电省。

DSP芯片的基本结构和特征

DSP芯片的基本结构 哈佛结构 流水线操作 专用的硬件乘法器 特殊的DSP指令 快速的指令周期

11

1B 1C 1D

1E 1E~

REA(块重复结束寄存器) PMST ( 处理器 工作 方式 ) XPC(程序计数器扩展) 保留

辅助寄存器(AR0~AR7):这8个16位的辅 助寄存器可以由算术逻辑单元(ALU)访 问,也可以由辅助寄存器算术单元(ARAU) 进行修改。它们主要的功能是产生16位的 数据地址,也可以同来作为通用寄存器和 计数器。

暂存器T

1.

2. 3. 4.

为乘法指令或乘/累加指令存放一个乘数; 为带有移位操作的指令(如:ADD ,LD,SUB 等)存放一个动态的移位数; 为BITT指令存放一个动态位地址; 参与EXP指令和NORM指令的操作。

状态转移寄存器TRN

1. 2.

为计算新的测量值存放中间结果; CMPS(比较、选择、存储单元)指令在累加 器高位和低位比较的基础上会修改TRN的内容

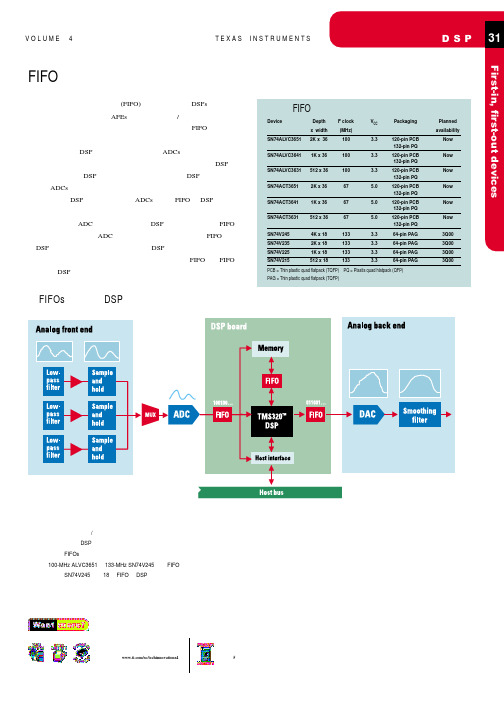

FIFO在速度和特性上优化系统性能

V O L U M E 4T E X A S I FIFO 在速度和特性上优化系统性能德州仪器公司的先进先出(FIFO)使设备能够消除DSPs 、高速处理器、内存设备和模拟前端(AFEs )之间数据输入/输出的瓶颈效应,从而优化系统性能。

采用双端口内存器和内置读写寻址,FIFO 就能按写入的顺序读出数据。

下面所示的DSP 系统中,模数转换器(ADCs )将连续的实值信号转换成离散的整数序列。

因为对模拟信号的采样速率是独立于DSP 的总线速率的,所以向DSP 传递信息需要进行异步缓冲。

DSP 上串行端口提供了与ADCs 相连的异步接口,足够适应相对较低的数据速率,而在较高的速率下,DSP 通过并行端口与ADCs 连接,FIFO 为DSP 提供优化数据缓存,以消除采集数据时的非同步效应。

此外,因为ADC 工作速率通常低于DSP ,所以两者之间的FIFO 还能完成速率匹配任务。

ADC 得到的低位速率数据先存储于FIFO ,然后在DSP 较高处理速度下进行传输。

反之,DSP 输出的高位速率数据在传送到较低处理速度的数模转换器之前,也是先暂存于FIFO 中。

FIFO 还可为作为DSP 内存补充的任何板上存储器提供类似的数据缓冲。

用FIFOs 的增强型DSP 系统产品特点:■消除模拟前端数据输入/输出的瓶颈效应,优化数据采样缓冲■提高高速处理器和DSP 的性能■为工业标准FIFOs 提供快速可靠、成本有效的管脚对管脚等效功能■指定100-MHz ALVC3651和133-MHz SN74V245系列FIFO 的速度和性能标准■提供新一代SN74V245系列18位FIFO 与DSP 之间的无缝连接典型应用■数字信号处理■医学成像■网络和电信系统■高档计算机、复印机和打印机■高速图形系统■工作站在线所有资源可在/sc/techinnovations4上订购或下载。

邮寄请在5处划圈获得数据表。

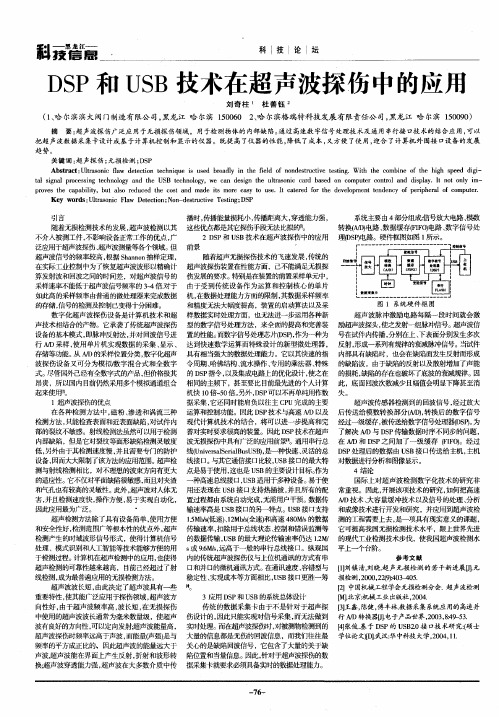

DSP和USB技术在超声波探伤中的应用

播时, 传播能量损耗小 , 传播距离大, 穿透能力强, 系统主要由 4 部分组成信 号放大电路、 模数 这些优点都是其它探伤手段无法比拟的日 。 转换( D 电路、 A ) / 数据缓存( F ) 、 F 0电路 数字信号处 I 2 D P和 U B技术在超声波探伤中的应用 N(S) 路。硬件框图如图 1 S S D P0  ̄ 所示。 前景 随着超声无损探伤技术的飞速发展 , 传统的 超声波探伤装置在性能方面 ,己不能满足无损探 伤发展的要求。 特别是在装置的前置采样单元中, 由于受 到传统设备作为运算和控制核心的单 片 机, 在数据处理能力方面的限制 , 其数据采样频率 图 1 系统 硬 件 框 图 和精度无法大幅度提高 , 装置的启动算法以及采 样数据实时处理方面,也无法进一步运用各种新 超声波脉冲激励电路每隔一段时间就会激 型的数字信号处理方法,来全面的提高和完善装 励超声波探头, 使之发射一组脉冲信号。 超声波信 置的性能。 而数字信号处理芯片(S) D P 作为一种为 号在试件内传播, , 分别在上 、 下表面分别发生多次 达到快速数学运算而特殊设计的新型微处理器, 反射, 形成一系列有规律的衰减脉冲信号。 当试件 具有相当强大的数据处理能力 。它以其 决速的指 内部具有缺陷时, 也会在缺陷面发生反射而形成 令周期、 哈佛结构 、 流水操作 、 专用的乘法器、 特殊 的缺陷波。由于缺陷的反射以及散射增加了声能 的DP S 指令 , 及集成电路上的优化谢 十 使之在 的损耗 , 以 , 缺陷的 存在也破坏了底波的衰减规律。 因 相同的主频下 , 甚至要比目 前最先进的个人计算 此,底面回波次数减少且幅值会明显下降甚至消 机决 l 倍 ̄ 0 另外 , S 可以不再单纯用作数 失 。 0 5 倍。 DP 据采集, 它还同时能肩负以往主 C U完成的主要 P 超声波传感器检测到的回波信号, 经过放大 运算和控制功能。因此 D P S 技术与高速 A / 及 后传送给模数转换部分(D, D以 A) / 转换后的数字信号 现代计算机技术的结合,将可 以 进一步提高和完 经过一级缓存, 被传送给数字信号处理器(S ) D P。 为 善对实时要求很高的装置。因此 D P技术在超声 了解决 AD与 D P S / S 传输数据时序不同步的问题, 波无损探伤中具有广泛的应用前景日 。通用串行总 在 AD和 D P之间加 了一级缓存 (IO。经过 / S FF ) 线(nvra ei B s S ) U iesl r uU B, S a l 是—种快速、 灵活的总 D P S 处理后的数据由 U B 口 S 接 传送给主机, 主机 线接 口 与其它通信接 口比 ,S 接 口的最大特 。 较 UB 点是易于使用, 这也是 U B S 的主要设计目 作为 标。 4结 论 种高速总线接口,S 适用于多种设备。 UB 易于使 国际上对超声波检测数字化技术 的研究非 用还表现在 US B接口支持热插拔 , 并且所有的配 常重视。因此 , 开展该项技术的研究 , 如何把高速 置过程都由系统 自 动完成, 无需用户干预。 数据传 A / D技术 、 大容量缓 冲技术 以 及信号的处理 、 分析 输速率高是 U B接口的另一特 。U B接 口支持 和成像技术进行开发和研究 ,并应用到超声波检 S S lM , 氐 、2 b( 和高速 40 /的数据 测的工程需要上去 , 5 b“ 速) M / ̄速) s 1 s 8Ms 是一项具有现实意义的课题, 传输速率 , 扣除用于总线状态、 控制和错误监测等 它可提高我国无损检测技术水平,跟上世界先进 的数据传输, S 最大理论传输速率仍达 1 M 的现代工业检测技术步伐,使我国超声波检测水 U B的 2 / s 9Ms 或 . / 远高于一般的串行总线接 口。纵观国 平上—个台阶。 6 , 参考 文献 内的传统超声波探伤仪与上位机通讯的方式有串 口 和并 口的 微机通讯方式。 在通讯速度 、 容错型与 【】 1 刘镇清, 刘晓. 超声无损检测的若干新进展明. 无 稳定性、 实现成本等方面相比,S U B接口更胜一筹 损 检 测 ,0 02(: 34 5 2 0 .2 )0 - 0. 94 H I 中国 2 I 机械工程学会无损检测分会. 超声波 检测 3应用 D P和 U B的系统总体设计 S S I . 京: 械工 业 出版 社 ,0 4 M] 北 机 20. 向 性好 , 由于超声波频率高 , 波长短 , 在无损探伤 传统的数据采集卡由于不是针对于超声探 f王鑫, , 3 1 陈健 傅丰林. 数据采集系统应用的高速并 中使用的超声波波长通常为毫米数量级 , 使超声 伤设计的 , 因此只能实现对信号采集, 而无法做到 行 AD转换 器叨_ / 电子产 品世界 ,0 38 9 5. 20 ,A - 3 张俊 . 于 D P的 U B . 口技 术研 究 : 士 基 S S2 0接 ( 硕 波有良好的方向 , 性 可以定向发射超 声波能量高, 实时处理。 而在超声波探伤时, 对被测物检测到的 超声波探伤时频率远高于声波, 而能量庐 强) 大量的信 息 是与 都是无伤的回波信息,而我们往往最 学位论文 . 华中科技大学,0 41. 武汉: 2 0 ,1 频率的平方成正比的 因此超声波的能量远大于 关| 的是缺陷回波信号,它包含了大量的关于缺 声波超 声波能在界面上产生反射 , 折射和波形转 陷位置和当 量信息。 因此, 针对于超声波探伤的数 换; 超声波穿透能力强 , 超声波在大多数介质中传 据采集卡就要求必须具备实时的数据处理能力。

什么是数字信号处理

什么是数字信号处理?有哪些应用?利用数字计算机或专用数字硬件、对数字信号所进行的一切变换或按预定规则所进行的一切加工处理运算。

例如:滤波、检测、参数提取、频谱分析等。

对于DSP:狭义理解可为Digital Signal Processor 数字信号处理器。

广义理解可为Digital Signal Processing 译为数字信号处理技术。

在此我们讨论的DSP的概念是指广义的理解。

数字信号处理是利用计算机或专用处理设备,以数字形式对信号进行采集、变换、滤波、估值、增强、压缩、识别等处理,以得到符合人们需要的信号形式。

信号处理的实质是对信号进行变换。

信号处理的目的是获取信号中包含的有用信息,并用更直观的方式进行表达。

DSP的应用几乎遍及电子学每一个领域。

▲通用数字信号处理器:自适应滤波,卷积,相关,数字滤波,FFT, 希尔伯特变换,波形生成,窗函数等等。

▲语音信号处理:语音增强、识别、合成、编码、信箱等,文字/语音转换▲图形/图像处理:三维动画,图象鉴别/增强/压缩/传输,机器人视觉等等图▲特殊应用数字信号处理:振动和噪声分析与处理,声纳和雷达信号处理,通信信号处理, 地震信号分析与处理,汽车安全及全球定位,生物医学工程等等。

在医疗、军事、汽车等行业,以及通信市场、消费类电子产品等中具有广阔的市场前景。

数字信号处理系统的基本组成:前置预滤波器(PrF)、a/d变换器(ADC)、数字信号处理器(DSP)、d/a变换器(DAC)、模拟滤波器(PoF)数字信号处理特点:1.大量的实时计算(FIR IIR FFT),2.数据具有高度重复(乘积和操作在滤波、卷积和FFT中等常见)数字信号处理技术的意义、内容数字信号处理技术是指数字信号处理理论的应用实现技术,它以数字信号处理理论、硬件技术、软件技术为基础和组成,研究数字信号处理算法及其实现方法。

意义:在21世纪,数字信号处理是影响科学和工程最强大的技术之一它是科研人员和工程师必须掌握的一门技巧DSP芯片及其特点▲采用哈佛结构体系:独立的程序和数据总线,一个机器周期可同时进行程序读出和数据存取。

DSP原理及应用(C54X)

第一章绪论1.1 DSP的基本原理数字信号处理(简称DSP)是一门涉及多门学科并广泛应用于很多科学和工程领域的新兴学科。

数字信号处理是利用计算机或专用处理设备,以数字的形式对信号进行分析、采集、合成、变换、滤波、估算、压缩、识别等加工处理,以便提取有用的信息并进行有效的传输与应用。

数字信号处理是以众多学科为理论基础,它所涉及的范围极其广泛。

如数学领域中的微积分、概率统计、随机过程、数字分析等都是数字信号处理的基础工具。

它与网络理论、信号与系统、控制理论、通信理论、故障诊断等密切相关。

DSP可以代表数字信号处理技术(Digital SignalProcessing),也可以代表数字信号处理器(Digital Signal Processor)。

前者是理论和计算方法上的技术,后者是指实现这些技术的通用或专用可编程微处理器芯片。

数字信号处理包括两个方面的内容:1.法的研究 2.数字信号处理的实现数字信号处理(Digital Signal Processing,简称DSP)是一门涉及许多学科而又广泛应用于许多领域的新兴学科。

20世纪60年代以来,随着计算机和信息技术的飞速发展,数字信号处理技术应运而生并得到迅速的发展。

在过去的二十多年时间里,数字信号处理已经在通信等领域得到极为广泛的应用。

数字信号处理是利用计算机或专用处理设备,以数字形式对信号进行采集、变换、滤波、估值、增强、压缩、识别等处理,以得到符合人们需要的信号形式。

数字信号处理是围绕着数字信号处理的理论、实现和应用等几个方面发展起来的。

数字信号处理在理论上的发展推动了数字信号处理应用的发展。

反过来,数字信号处理的应用又促进了数字信号处理理论的提高。

而数字信号处理的实现则是理论和应用之间的桥梁。

数字信号处理是以众多学科为理论基础的,它所涉及的范围极其广泛。

例如,在数学领域,微积分、概率统计、随机过程、数值分析等都是数字信号处理的基本工具,与网络理论、信号与系统、控制论、通信理论、故障诊断等也密切相关。

数字信号处理第10章数字信号处理的硬件实现

第10章 数0章 数字信号处理的硬件实现 配有专用的硬件乘法-累加器。 为了适应数字信号处理的需要, 当前的DSP芯片都配有专用的 硬件乘法-累加器, 可在一个周期内完成一次乘法和一次累加 操作, 从而可实现数据的乘法和累加操作。例如, 可实现卷 积计算、FIR和IIR滤波、FFT变换等专用信号的处理。 有丰富的片内外设资源。 为了方便数据的读、写及与片外设备的通信, DSP芯片上一般 都集成有DMA控制器, 同时片上还集成有串行通信 口、定时器及中断处理器等。由于DSP通常具有较高的速度, 外设的速度相对较慢, 因此片上还集成有和不同速度存储器 相连接的硬件和软件等待状态发生器。

第10章 数字信号处理的硬件实现 图 10.1.4 数的表示

第10章 数字信号处理的硬件实现

图10.1.4中, s是符号位, 为第31位。s=0表示正数, s=1 表示负数。对定点制, 一个数x可表示为

x=(-1)s×.f f为第0位至第30位, 共31位, 至于小数点在什么位置, 由 使用者指定。例如, 一个正的十六进制数40000000H, 若小数 点在第0位后面, 则x=1 073 741 824, 这时表示的数最大, 但 “分辨率”为1;若小数点在第31位后面, 则x=0.5, 表示 的数最小, “分辨率”为 1/231。若小数点在其它位置, 同 一个十六进数将又会是另一个十进制数。总之, 在定点制 中, 小数点越靠近高位, 能表示的数的范围越小, 但精度越高 ; 反之, 小数点越靠近低位, 能表示的数的范围越大, 但精 度 越低。

第10章 数字信号处理的硬件实现 3. 定点与浮点DSP 按计算机中数的表示方式, DSP可分为定点和浮点两种。早期的 DSP大都为定点的, 一般为16 bit或32 bit。采用定点数来实现 数值运算时, 其操作数大都采用整型数来表示。整 型数的大小 取决于所用的字长, 字的位数越多, 所能表示的 数的范围越大 。例如, 对16 bit字长, 其表示的数的最大范 围是-32 768~ 32 767。在运算过程中, 如果两个数的和或积超过这一范围, 就要产生数据的溢出, 从而带来较大的误差。当然, 定点DSP也 可以实现小数运算, 不过小数点的位置是 由编程人员指定的。一个32 bit定点制格式如图10.1.4(a)所示 与此相对应, IEEE754标准定义的单精度浮点格式如图 10.1.4(b)所示。

DSP芯片原理

◇ 显示模块LM12864 LM12864是内置了HD61202U控制器的128×64点阵式液晶显示 器,LM12864的显示区域被分为左右两个区,均为64×64大小,左 右区的选择由CSA和CSB的组合来决定,当CSA、CSB的组合为01 时,选择左区,当二者的组合为10时,选择右区,二者组合为00或 11时均无效,LM12864内置的HD61202U为一可编程器件,通过对 HD61202U控制器的编程可以实现液晶显示器的各种功能,所有显 示功能均可由指令控制实现,本系统共有7条指令。 ◇ FLASH存储器 串行Flash存储器以其体积小、密度高、功耗低、操作易而备受青 睐,本文简单介绍了MEGAWIN公司生产的Flash存储器 MM36SB020E,MM36SB020E为2M×8BIT串行FLASH,大小为 256KBYTE,接线方式可采用2线和3线制,器件的忙判断可以由内 部的状态寄存器来判断,也可以通过外部引脚BUSY来判断,可以说, 该FLASH不仅操作十分简单,并且可以适用于多个设计方案。

MAX5742可以实现将数字信号转换成模 拟量输出的功能。在实验板使用的 MAX5742是将DIN端送入的十二位数字信 号转换为模拟信号。 Vdd=3.3V,参考输 入允许0~Vdd范围,可以实现同时转换四 路模拟信号输出,并有12位精度。其中 CS是芯片选通输入,SCLK是连续时钟输 入,DIN是连续数据输入。REF是一个参 考值,输出电压与之有对应的关系。 MAX5742与F2812的通信方式采用SPI 。

这个芯片是为快速瞬态响应而设计的,同时在10uF等值串联 电容器下表现稳定。TPS76801将输入电压调节到1.2V-5.5V

OCM12864液晶显示模块概述

1. OCM12864液晶显示模块是128×64点阵型 液晶显示模块,可显示各种字符及图形,可与 CPU直接接口,具有8位标准数据总线、6条控制 线及电源线。采用KS0107控制IC。 2. 外观尺寸:113×65×11mm(ocm12864-1), 93×70×10mm(ocm12864-2) 78×70×10mm(ocm12864-3), 3. 视域尺寸:73.4×38.8mm(ocm128641) 70.7×38mm(ocm12864-2), 64×44mm(ocm12864-3) l 补充说明:外观尺寸可根据用户的要求 进行适度调整。

DSP复习资料

DSP复习资料1、什么是数字信号处理器(DSP)?DSP 可以分为哪两类?a、数字信号处理器是⼀种专门⽤于实现各种数字信号处理算法的微处理器,通常可分为专⽤DSP和通⽤DSP两类。

b、⽤于实现某些特定数字信号处理功能的DSP 属于专⽤DSP。

什么是DSP?DSP:Digtal Signal Processing 数字信号处理技术典型的微处理器系统根据CPU特点,可以分为:1)通⽤单⽚机(Micro-controller) 8/16bit优点:成本低、体积⼩。

缺点:运算与扩展能⼒较弱。

编程:汇编、C语⾔。

2)PC及其兼容机(Micro-processor)缺点:成本⾼、体积⼤、实时性差。

优点:运算与扩展能⼒强,软件资源丰富。

编程:汇编及多种⾼级语⾔。

3)DSP(Digital Signal Processor)16/32bit特点:运算能⼒相当强、实时性、体积⼩、成本较低、功耗较低编程:汇编、C、C++。

4)专⽤微处理器特点:使⽤简单,灵活性差,主要⽤于⼀些批量⽣产的产品。

如家⽤电器的智能控制、⼯业控制。

DSP: Digtal Signal Processor 数字信号处理器TI公司从80代初推出了全球第⼀款“数字信号处理器”TMS320C010,从此引发了⼀场“数字信号处理”⾰命。

我们现在所说的DSP,如果没有特殊说明,⼀般均指“数字信号处理器”。

2、DSP 芯⽚的主要特点有哪些?DSP 从结构上进⾏了优化,使其更适合于哪类运算,从⽽可以⾼速实现多种不同的数字信号处理算法?DSP的特点:在⼀个指令周期内可完成⼀次乘法和⼀次加法运算程序和数据空间分开,可以同时访问指令空间和数据空间⽚内具有快速RAM,通常可通过独⽴的数据总线在两块中同时访问具有低开销或⽆开销循环及跳转的硬件⽀持快速的中断处理和硬件I/O⽀持具有在单周期内操作的多个硬件地址产⽣器可以并⾏执⾏多个操作⽀持流⽔线操作,使取指令、译码、取操作数和执⾏指令等可以重叠执⾏。

DSP在通信系统中的应用与发展

DSP在通信系统中的应用与发展摘要:数字信号处理器(DSP)是一种具有特殊结构的微处理器,特别适合于数字信号处理运算。

它是当今发展最为迅速和前景最为可观的技术之一。

自从20世纪80年代第一片DSP芯片诞生至今。

其性能得到了极大的提高。

应用领域取得了不断的拓展。

日前它己经成为通信、计算机、网络、工业控制以及家用电器等电产品不可或缺的基础器件, 尤其在通信领域,数字信号处理器以其实时快速地实现各种数字信号处理算法的优点从而得到了广泛的应用。

随着超大规模集成电路技术(VLSI)的高速发展。

DSP的性价比也在不断提高。

本文是在本学期学习了《数字信号处理与DSP技术》后,对DSP在通信系统中的应用现状及发展趋势作的简单介绍。

一、DSP器件、厂商简要介绍DSP,也称作数字信号处理器(Digital Signal Processor),是一种具有特殊结构的微处理器,主要对数字信号进行实时处理,以得到相应的处理结果。

DSP 芯片的内部采用程序和数据分开的哈佛结构,具有专门的硬件乘法器,广泛采用流水线操作提供特殊的DSP指令,可以用来快速地实现各种数字信号处理算法。

在DSP出现之前,数字信号处理只能依靠MPU(微处理器)来完成。

但由于MPU处理速度较低,无法满足越来越大的信息量的高速实时要求,因此寻求更快更高效的信号处理方式成了日渐迫切的社会需求。

到了60年代,有人提出了DSP的理论和算法基础,数字信号处理的理论得以迅速发展。

1978年AMI 公司宣布的S2811,标志着世界上第一个DSP的诞生,1979年美国Intel公司推出商用可编程器件2920。

这两种芯片内部都没有现代DSP芯片所必须有的单周期乘法器,其应用领域很局限,但是DSP的问世是个里程碑,它标志着DSP应用系统由大型系统向小型化迈进了一大步。

经过20多年的发展,DSP芯片的性能价格比不断提高,开发手段越来越完善。

DSP芯片的应用已扩大到人们的学习、工作和生活的各个方面,已经在通信与电子系统、信号与信息处理、自动控制、雷达、军事、航空航天、医疗、家用电器在等许多领域得到广泛的应用,并逐渐成为电子产品更新换代的决定因素。

《DSP原理及应用(修订版)》邹彦主编课后答案(个人终极修订版)

第一章1、数字信号处理实现方法一般有几种?答:课本P2(2.数字信号处理实现)2、简要地叙述DSP芯片的发展概况。

答:课本P2(1.2.1 DSP芯片的发展概况)3、可编程DSP芯片有哪些特点?答:课本P3(1.2.2 DSP芯片的特点)4、什么是哈佛结构和冯诺依曼结构?他们有什么区别?答:课本P3-P4(1.采用哈佛结构)5、什么是流水线技术?答:课本P5(3.采用流水线技术)6、什么是定点DSP芯片和浮点DSP芯片?它们各有什么优缺点?答:定点DSP芯片按照定点的数据格式进行工作,其数据长度通常为16位、24位、32位。

定点DSP的特点:体积小、成本低、功耗小、对存储器的要求不高;但数值表示范围较窄,必须使用定点定标的方法,并要防止结果的溢出。

浮点DSP芯片按照浮点的数据格式进行工作,其数据长度通常为32位、40位。

由于浮点数的数据表示动态范围宽,运算中不必顾及小数点的位置,因此开发较容易。

但它的硬件结构相对复杂、功耗较大,且比定点DSP芯片的价格高。

通常,浮点DSP芯片使用在对数据动态范围和精度要求较高的系统中。

7、DSP技术发展趋势主要体现在哪些方面?答:课本P9(3.DSP发展技术趋势)8、简述DSP系统的构成和工作过程。

答:课本P10(1.3.1DSP系统的构成)9、简述DSP系统的设计步骤。

答:课本P12(1.3.3DSP系统的设计过程)10、DSP系统有哪些特点?答:课本P11(1.3.2DSP系统的特点)11、在进行DSP系统设计时,应如何选择合理的DSP芯片?答:课本P13(1.3.4DSP芯片的选择)12、TMS320VC5416-160的指令周期是多少毫秒?它的运算速度是多少MIPS?解:f=160MHz,所以T=1/160M=6.25ns=0.00000625ms;运算速度=160MIPS第二章1、TMS320C54x芯片的基本结构都包括哪些部分?答:课本P17(各个部分功能如下)2、TMS320C54x芯片的CPU主要由几部分组成?答:课本P18(1.CPU)3、处理器工作方式状态寄存器PMST中的MP/MC、OVLY和DROM3个状态位对’C54x 的存储空间结构有何影响?答:课本P34(PMST寄存器各状态位的功能表)4、TMS320C54x芯片的内外设主要包括哪些电路?答:课本P40(’C54x的片内外设电路)5、TMS320C54x芯片的流水线操作共有多少个操作阶段?每个操作阶段执行什么任务?完成一条指令都需要哪些操作周期?答:课本P45(1.流水线操作的概念)6、TMS320C54x芯片的流水线冲突是怎样产生的?有哪些方法可以避免流水线冲突?答:由于CPU的资源有限,当多于一个流水线上的指令同时访问同一资源时,可能产生时序冲突。

DSP概述

1.3 DSP芯片的特点

7.支持多处理器结构 为了满足多处理器系统的设计,许多DSP芯片都采用支

持多处理器的结构。如:TMS320C40提供了6个用于处理器 间高速通信的32位专用通信接口,使处理器之间可直接对通 ,应用灵活、使用方便;

8.省电管理和低功耗 DSP功耗一般为0.5~4W,若采用低功耗技术可使功耗降

T4

时钟

取指令

N

N+1

N+2

N+3

指令译码

N-1

N

N+1

N+2

取操作数

N-2

N-1

N

N+1

执行指令

N-3

N-2

N-1

N

四级流水线操作

1.3 DSP芯片的特点

3. 配有专用的硬件乘法-累加器 为了适应数字信号处理的需要,当前的DSP芯ቤተ መጻሕፍቲ ባይዱ都配有

专用的硬件乘法-累加器,可在一个周期内完成一次乘法和 一次累加操作,从而可实现数据的乘法-累加操作。如矩阵 运算、FIR和IIR滤波、FFT变换等专用信号的处理。 4. 具有特殊的DSP指令

1.2 DSP芯片的发展

DSP芯片诞生于20世纪70年代末,至今已经得到 了突飞猛进的发展,并经历了以下三个阶段。

第一阶段,DSP的雏形阶段(1980年前后) 第二阶段,DSP的成熟阶段(1990年前后) 第三阶段,DSP的完善阶段(2000年以后)

1.2 DSP芯片的发展

第一阶段,DSP的雏形阶段(1980年前后) 1978年AMI公司生产出第一片DSP芯片S2811。 1979年美国Intel公司发布了商用可编程DSP器件Intel2920, 由于内部没有单周期的硬件乘法器,使芯片的运算速度、数据 处理能力和运算精度受到了很大的限制。运算速度大约为单指 令周期200~250ns,应用领域仅局限于军事或航空航天部门。

DSP_2

1

第二章 定点DSP芯片TMS320f2812

2.1 TMS320F2812性能特点

2.2 TMS320F2812硬件结构 2.3 TMS320F2812指令系统简介

2

2.1 TMS320F2812性能特点

(1)采用了高性能的静态CMOS技术,时钟频 率可达150MHZ(6.67ns),其核心电压为1.8V,I/O 口电压3.3V,Flash编程电压也为3.3V。 (2)高性能的32位CPU。能够实现16X16和 32X32乘法操作,哈佛总线结构,快速的中断操作,寻 址程序空间可达4M,寻址数据空间可达4G,在C/C++ 和汇编语言中代码可得到优化,另外还可向下兼容 TMS320F24X/LF240X处理器的代码; (3)片上存储器:闪存128K字,单访问双口 RAM(SARAM)18k字; (4)引导(BOOT)ROM4K字,具有软件启动模 式并包含标准的数学表; (5)时钟和系统控制采用锁相环技术PLL来控 3 制系统各模块所需要的频率;

19

2、TMS320F2812的片内外设简介

由于28lx数字信号处理器集成了很多内核可 以访问和控制的外部设备,28lx内核需要通过 某种方式来读/写外设。为此,处理器将所有的 外设都映射到了数据存储器空间,主要包括配 置寄存器、输入寄存器、输出寄存器和状态寄 存器。每个外设只要通过简单的访问存储器中 的寄存器就可以使用该设备。外设通过外设总 线(PBUS)连接到CPU的内部存储器接口上,如 图2-12 所示。所有的外设(包括看门狗和CPU时 钟)在使用前必须配置相应的控制寄存器。

2.2.3 中央 处理单元 (C28x CPU)

1. CPU结构

11

(1)算术逻辑单元(ALU):32位ALU完成2的补 码的算术运算和布尔运算。通常情况下,中央处 理单元对于用户是透明的。例如,完成一个算术 运算,用户只需要写一个命令和相应的操作数据, 读取相应的结果寄存器的数据就可以了。 (2)乘法器:乘法器完成32x32位的2的补码的 乘法运算,产生64位的补码结果。乘法器能够完 成两个符号数,两个无符号数或一个符号数和一 个无符号数的乘法运算。 (3)移位器:完成数据的左移或右移操作,最 大可移16位。在C28lx的内核中,总计有3个移位 寄存器:输入数据定标移位寄存器,输出数据定标 移位寄存器和乘积定标移位寄存器。

DSP试卷题库(理工版)

DSP原理及应用考试题库凯哥电子技术应用教研室2012.05.20目录一、填空题 (1)二、选择题 (7)三、判断题 (11)四、简答题 (13)五、程序阅读题 (18)六、指令分析 (28)七、程序改错题 (32)八、程序编写 (34)九、程序识读 (35)十、硬件电路分析 (37)一、填空题1.累加器A 分为三个部分,分别为 ; ; 。

2.TMS320VC5402型DSP 的内部采用 条 位的多总线结构。

3.TMS320VC5402型DSP 采用 总线结构对程序存储器和数据存储器进行控制。

4.TMS329VC5402型DSP 有 个辅助工作寄存器。

5.DSP 处理器TMS320VC5402中DARAM 的容量是 字。

6.TI 公司的DSP 处理器TMS320VC5402PGE100有___________个定时器。

7.在链接器命令文件中,PAGE 1通常指________存储空间。

8.C54x 的中断系统的中断源分为 中断和 中断。

9.TI 公司DSP 处理器的软件开发环境是__________________。

10.DSP 处理器TMS320VC5402外部有___________根地址线。

11.直接寻址中从页指针的位置可以偏移寻址 个单元。

12.在链接器命令文件中,PAGE 0通常指________存储空间。

13.C54x 系列DSP 处理器中,实现时钟频率倍频或分频的部件是_____________。

14.TMS320C54x 系列DSP 处理器上电复位后,程序从指定存储地址________单元开始工作。

15.TMS320C54x 系列DSP 处理器有_____个通用I/O 引脚,分别是_________。

16.DSP 处理器按数据格式分为两类,分别是_______;_____。

17.TMS329VC5402型DSP 的ST1寄存器中,INTM 位的功能是 。

18.MS320C54X DSP 主机接口HPI 是________位并行口。

DSP知识点复习

22

TMS320C54x的指令系统符号和意义见P51-53

表3-1

DSP技术及应用

23

寻址方式

C54共有7种基本寻址方式

立即寻址

绝对寻址 累加器寻址

直接寻址

间接寻址 存储器映像寄存器寻址

堆栈寻址

DSP技术及应用

24

寻址方式

• 循环寻址的算法: If 0≤index+step〈BK; Index =index+step; Else if index+step ≥BK; Index =index+step-BK; Else if index+step〈0; Index =index+step+BK;

DSP技术及应用

25

寻址方式

循环寻址

使用循环寻址时,必须遵循以下三个原则:

① 循环缓冲区的长度 R<2N,且地址从一个低N位为0的地址开始; ② 步长小于或等于循环缓冲区的长度; ③ 所使用的辅助寄存器必须指向缓冲区单元。

DSP技术及应用

26

指令系统

TMS320C54X共有129条指令 按功能分为4大类(每大类又分为若干小类) :

DSP技术及应用

5

TMS320C54x硬件结构框图

TMS320C54x内部结构(3大块) (1)CPU:包括算术逻辑运算单元(ALU)、乘法器、 累加器、移位寄存器、各种专门用途的寄存器、地址生 成器及内部总线。 (2)存储器系统:包括片内程序ROM、片内单访问的 数据RAM和双访问的数据RAM、外接存储器接口。 (3)片内外设与专用硬件电路:包括片内定时器、 各种类型的串口、主机接口、片内锁相环(PLL)、时钟 发生器及各种控制电路。

kx数字信号处理器名字对应的通道

kx数字信号处理器名字对应的通道Kx数字信号处理器是一款基于通信原理和数字信号处理技术的高性能处理器。

它主要用于数字信号的采集、处理和分析,并具有较强的实时性和高速性能。

Kx处理器通常具有多通道数据输入和输出接口,可以同时处理多个通道的数据。

通道是指数字信号处理器中用于数据输入和输出的通路。

在Kx数字信号处理器中,通道可以是物理通道或逻辑通道,可以实现对接不同的传感器或数据源。

下面将列举一些常见的Kx数字信号处理器相关通道,并提供相关参考内容,以帮助读者更深入了解Kx数字信号处理器的通道应用。

1. 采集通道(Analog Input Channel):该通道用于采集模拟信号并将其转换为数字信号。

它通常包括一个或多个电压或电流输入端口,将模拟信号转换为数字信号后,可以通过其他处理通道进行进一步处理。

相关参考内容:《数字信号处理技术》- 王志华,讲述了模拟信号采集、数字信号转换和数字信号处理的基本原理。

2. 数字输入通道(Digital Input Channel):该通道用于接收和处理数字信号输入,例如从传感器或外部设备获取的数字信号。

它可以实现数字信号的采集和处理,从而可以用于各种应用中,如通信、图像处理等。

相关参考内容:《数字信号处理导论》- 刘延军,介绍了数字信号的基本概念、数字信号的采样与重构等。

3. 数字输出通道(Digital Output Channel):该通道用于将数字信号输出到外部设备或其他系统。

它可以实现对数字信号的处理和分析,并将处理结果输出给其他设备或系统,实现数据的传递和共享。

相关参考内容:《数字信号处理与MATLAB应用》- 王波,详细介绍了如何使用MATLAB进行数字信号处理,并将处理结果输出。

4. 通信通道(Communication Channel):该通道用于实现与其他设备或系统之间的通信和数据传输。

它通常包括串行通信、并行通信、以太网通信等多种通信方式,可以用于实现数据的传输和共享。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

当缓冲串口和时分串口工作在标准方式下与标准 串口功能相同,下面讨论一下标准串口工作方式:

发送数据过程:

要传送的数据写入DXR XSR

DX

接收数据过程: DR RSR DRR(从此读出)

见下图:

单向串口传送数据的一种接法:DX SX CLKX54x器件0

DR FSR CLKR

54x器件1

2.9 串行口

串行口可以与编码解码器,串行模数(A/D)转 换器以及其他串行系统进行通信。

串行接口分:标准串行接口,带缓冲的串行 接口,时分复用串行接口,多通道带缓冲串 行接口四种。

各型号串口情况和数量。见下表:

带缓冲的串行口(BSP):由标准同步串行口和一个 自动缓冲单元(ABU)组成。ABU的功能是控制串 行接口与内部C54x DSP存储器之间的数据传送,且 不需要CPU的干预。