USB2.0接口EMC防雷设计方案

USB应用中的EMC兼容设计

USB应用中的EMC兼容设计USB端口对PC外设的发展起到了革命性的推动作用,并且正变得越来越流行,比如在采集测量数据或在机器上安装软件更新等应用中就非常常见。

作为用于数据传输的一种总线系统,只要有移动设备连着的地方就有它的身影。

虽然在日常生活中使用的连接器看起来非常结实,但USB应用开发人员仍然必须重视这些接口的保护。

在Intel公司的“高速USB平台设计指南”中,甚至提高了考虑USB端口易感性因素的重要性。

Intel建议用电流补偿型扼流圈抑制 EMI,再用其它元件防止静电放电(ESD)。

电子设备经常会遭受静电放电。

静电放电脉冲电压可能高达30kV,因此对所有类型的集成电路来说都是非常危险的。

目前有些IC对静电放电来说是“安全的”,但这种安全性只是对一小部分潜在威胁来说是有保证的。

日常操作表明:额外保护是必不可少的。

只有采取外部保护措施才能开发出整块电路板不受静电放电影响以及高度可靠的产品来。

专门的抑制措施同样也是必需的。

无线联网的电子设备如今是遍地开花,它们的数量正在与日俱增。

使自己的产品不受辐射干扰的影响非常重要。

只有考虑了预期的干扰形式,才能在设计中及时集成必要的抑制元件,进而缩短开发周期。

我们知道,自身产品的辐射型干扰也必须处于某个电平之下。

这可以通过EMC测试实验室进行很精确的评估。

如果产品没有通过这种测试,那么立马返工的成本将超过抑制元件成本的好几倍。

实际的抗干扰能力在提到干扰对USB的影响时,差分模式数据传输与简单的同轴电缆相比具有很大的优势。

在感性干扰效应(磁场)情况下,导线的绞合可以弥补干扰效应。

鉴于每根双绞线的部分电感的对称性,干扰会彼此影响补偿效果。

这种抗干扰效果在实际应用中会大打折扣。

●USB控制器的输入/输出不是完全对称的,因此USB信号显示出共模干扰。

●Layout与HF/EMC不兼容,寄生电容和缺少波阻匹配会产生共模干扰。

●电路设计(USB滤波器)不充分,滤波器影响信号质量,和/或插损太低。

USB保护电路的EMC设计

USB保护电路的EMC设计1.确定电路布局电路布局是EMC设计中的重要一环。

首先,需要将接地电路的尽可能短。

接地电路是消除电磁串扰的关键,良好的接地是保证设备EMC性能的基础。

其次,将高频信号线与低频信号线分离布局,减少彼此之间的相互干扰。

此外,还需要根据系统需求,合理布局各个电路模块,减少信号线的长度和走线面积。

2.适当选择滤波器滤波器的设计对于EMC起着至关重要的作用。

在USB保护电路中,常常需要使用滤波器来抑制高频噪声和滤除电源线上的电磁干扰。

常用的滤波器包括LC滤波器、Ferrite Beads和EMI滤波器等。

在选择滤波器时,需要根据系统的特点和需求,合理选择滤波器的参数和类型。

3.良好的接地设计良好的接地设计是EMC设计中的重要一环。

首先,需要构建星型接地系统,即将所有的接地点连接在一起,并与外部接地点相连接。

其次,需要采用大面积的接地层来减少环路面积,并且减少共模噪声的辐射和接收。

另外,还要注意将模拟和数字地线分离布局,减少相互之间的干扰。

4.抗干扰设计在USB保护电路的EMC设计中,抗干扰设计是重要的一环。

主要包括以下几个方面:首先,需要合理选择电容和电感元件,以增加抑制干扰的能力。

其次,需要适当加入屏蔽罩或屏蔽层,以减少电磁辐射和电磁感受。

另外,要合理设置地孔和电流回路,在设计中避免环路,减少电磁干扰。

5.可靠的布线设计布线设计也是EMC设计中的关键一环。

在USB保护电路中,需要合理规划信号线和电源线的走线路径,尽量减少信号线的长度和延迟。

此外,还要合理设计PCB板的层压结构,减少信号线的串扰和电磁辐射。

6.使用合适的材料和元件选择合适的材料和元件也是EMC设计中的重要一环。

例如,选择具有良好屏蔽性能的材料和元件,如磁性材料、屏蔽罩等,以减少电磁辐射和电磁感受。

另外,选择高频特性好的元件,如高频滤波器等,以提高系统的EMC性能。

总结起来,USB保护电路的EMC设计是确保设备电磁兼容性和可靠性的重要环节。

USB2.0差分走线要求

USB2.0差分走线要求USB通用串行总线(Universal SerialBus),目前我们所说的USB一般都是指USB2.0,USB2.0接口是目前许多高速数据传输设备的首选接口,从1.1过渡到2.O,作为其重要指标的设备传输速度,从1.5Mbps的低速和12Mbps的全速提高到如今的480Mbps的高速。

USB的特点不用多说大家也知道就是:速度快、功耗低、支持即插即用、使用安装方便。

正是因为其以上优点现在很多视频设备也都采用USB传输。

USB2.0设备高速数据传输PCB板设计。

对于高速数据传输PCB板设计最主要的就是差分信号线设计,设计好坏关乎整个设备能否正常运行。

1、USB2.0接口差分信号线设计USB2.0协议定义由两根差分信号线(D、D-)传输高速数字信号,最高的传输速率为480Mbps。

差分信号线上的差分电压为400mV,理想的差分阻抗(Zdiff)为90(1±O.1)Ω。

在设计PCB板时,控制差分信号线的差分阻抗对高速数字信号的完整性是非常重要的,因为差分阻抗影响差分信号的眼图、信号带宽、信号抖动和信号线上的干扰电压。

由于不同软件测量存在一定偏差,所以一般我们都是要求控制在80Ω至100Ω间。

差分线由两根平行绘制在PCB板表层(顶层或底层)发生边缘耦合效应的微带线(Microstrip)组成的,其阻抗由两根微带线的阻抗与其和决定,而微带线的阻抗(Zo)由微带线线宽(W)、微带线走线的铜皮厚度(T)、微带线到最近参考平面的距离(H)以与PCB板材料的介电常数(Er)决定,其计算公式为:Zo={87/sqrt(Er 1.41)]}ln[5.98H/(0.8WT)]。

影响差分线阻抗的主要参数为微带线阻抗和两根微带线的线间距(S)。

当两根微带线的线间距增加时,差分线的耦合效应减弱,差分阻抗增大;线间距减少时,差分线的耦合效应增强,差分阻抗减小。

差分线阻抗的计算公式为:Zdiff=2Zo(1-0.48exp(-0.96S/H))。

usb防雷击电路工作原理

usb防雷击电路工作原理摘要:B 防雷击电路的背景和重要性B 防雷击电路的工作原理B 防雷击电路的组成部件B 防雷击电路的应用场景B 防雷击电路的优缺点正文:一、USB 防雷击电路的背景和重要性随着电子设备的普及,USB 接口已经成为了日常生活中最常见的电子设备连接方式。

然而,由于雷电等自然现象的影响,USB 电路容易受到电磁干扰,导致设备损坏。

因此,设计一款有效的USB 防雷击电路至关重要。

二、USB 防雷击电路的工作原理USB 防雷击电路的工作原理主要基于防雷芯的特性。

当电路受到感应雷击,产生瞬间巨大电涌时,避雷芯内部电阻值会迅速下降接近零值,对线路电流起泄流作用,避免电流窜入到后端电器设备。

如果感应雷电产生的电涌能量超越避雷芯的承受范围时,避雷芯内部的温度保险丝会自动熔断,以切断电路,阻止电流继续流窜到后端电器设备。

三、USB 防雷击电路的组成部件USB 防雷击电路主要由以下几个部分组成:1.避雷芯:是防雷击电路的核心部件,能够限制瞬间电压波动,保护电路免受雷击损害。

2.温度保险丝:当雷击产生的能量超过避雷芯承受范围时,温度保险丝会自动熔断,切断电路。

3.电容:用于滤除电路中的高频噪声,提高电路的稳定性。

4.电感:限制电路中的电流变化,保护设备免受电流冲击。

四、USB 防雷击电路的应用场景USB 防雷击电路广泛应用于各种电子设备中,如手机、电脑、路由器等。

这些设备在雷电天气中使用时,通过USB 防雷击电路可以有效地保护设备免受雷击损害。

五、USB 防雷击电路的优缺点优点:1.有效保护设备免受雷击损害。

2.结构简单,易于安装和维护。

缺点:1.在防雷击效果上,仍存在一定的局限性。

欧盟统一后的手机USB接口及其EMC测试要求

欧盟统一后的手机USB接口及其EMC测试要求2011-01-28 18:28:09 来源:摩尔实验室浏览次数:615 文字大小:【大】【中】【小】关键字:USB接口统一EMC 测试从2011年1月1日开始,所有在欧盟销售的带usb接口的手机,其接口统一为micro-B USB,手机及配套充电器的接口如下图所示:手机充电器的接口一直以来都是五花八门,从Micro-B USB到MiniUSB,甚至还有专属充电数据接口存在,这样的设计极大的不方便消费者。

很多时候我们急需充电的时候却发现充电接口不一样。

针对这一现象,欧盟委员会已经批准了14家手机品牌大厂商达成的一项协议,统一了手机usb接口为micro-B USB,并采用micro-B USB手机充电器新标准。

目前支持此项决议的手机厂商包括摩托罗拉、诺基亚、华为、LG、三星、索尼爱立信等。

此项协议实施后,消费者就不用再去为充电而烦躁,让生活更加的轻松,同时能减少充电器的产量,换手机造成的丢弃充电器行为也会大大减少,并且能节约消费者的支出,对减轻环境污染与节能减排也是一大利好。

针对以上协议,欧盟对手机充电器制定了一个新法规其标准号为ETSI EN 301 489-34 V1.1.1 (2 010-10),此标准遵从CE指令。

也就是说,带micro-B USB口的手机充电器做CE认证,另外要符合此标准的要求。

现在我们就来了解一下这个新的法规对于micro-B USB口充电器设备在EMC测试方面都有哪些规定。

以方便大家申请欧盟CE认证。

EN301489-34是指关于无线电设备和服务的相关电磁兼容标准的第34部分,即关于移动电话的外部供电设备的特殊规定。

一.标准中规定了对设备进行供电的EPS(外部供电设备)即充电器必需要符合以下条件:设备通过使用一个micro-B的USB插头电缆的充电器进行电源供电;λ●充电电压为:5V±5 % ;λ●最大输出电流限定在500到1500MA;二. 关于EPS的测试需要注意到几个测试条件:λ●进行EPS的测试时它的直流输出端口必需要接一个能够代表它的连接设备的模拟负载。

USB2.0接口EMC防雷设计方案

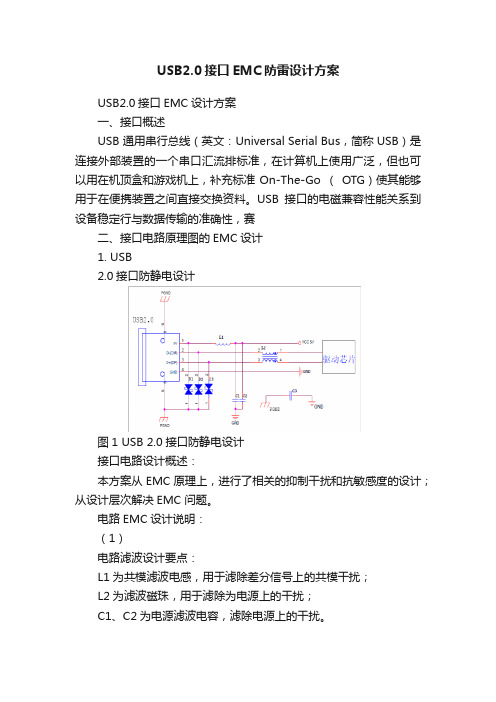

USB2.0接口EMC防雷设计方案USB2.0接口EMC设计方案一、接口概述USB 通用串行总线(英文:Universal Serial Bus,简称USB)是连接外部装置的一个串口汇流排标准,在计算机上使用广泛,但也可以用在机顶盒和游戏机上,补充标准On-The-Go (OTG)使其能够用于在便携装置之间直接交换资料。

USB接口的电磁兼容性能关系到设备稳定行与数据传输的准确性,赛二、接口电路原理图的EMC设计1. USB2.0接口防静电设计图1 USB 2.0接口防静电设计接口电路设计概述:本方案从EMC原理上,进行了相关的抑制干扰和抗敏感度的设计;从设计层次解决EMC 问题。

电路EMC设计说明:(1)电路滤波设计要点:L1为共模滤波电感,用于滤除差分信号上的共模干扰;L2为滤波磁珠,用于滤除为电源上的干扰;C1、C2为电源滤波电容,滤除电源上的干扰。

L1共模电感阻抗选择范围为60Ω/100MHz~120Ω/100MHz,典型值选取90Ω/100MHz;L2磁珠阻抗范围为100Ω/100MHz ~1000Ω/100MHz,典型值选取600Ω/100MHz ;磁珠在选取时通流量应符合电路电流的要求,磁珠推荐使用电源用磁珠;C1、C2两个电容在取值时要相差100倍,典型值为10uF、0.1uF;小电容用滤除电源上的高频干扰,大电容用于滤除电源线上的纹波干扰;C3为接口地和数字地之间的跨接电容,典型取值为1000pF,耐压要求达到2KV以上,C3容值可根据测试情况进行调整;(2)电路防护设计要点D1、D2和D3组成USB接口防护电路,能快速泄放静电干扰,防止在热拔插过程中产生的大量干扰能量对电路进行冲击,导致内部电路工作异常。

D1、D2、D3选用TVS,TVS反向关断电压为5V;TVS管的结电容对信号传输频率有一定的影响,USB2.0的TVS结电容要求小于5pF。

接口电路设计备注:如果设备为金属外壳,同时单板可以独立的划分出接口地,那么金属外壳与接口地直接电气连接,且单板地与接口地通过1000pF电容相连;如果设备为非金属外壳,那么接口地PGND与单板地GND直接电气连接。

USB接口防静电方案列表

USB接口防静电方案列表

作为电脑和电子产品必备接口,USB堪称万能接口。

你的USB接口是2.0还是3.0?不管是使用还是设计接口都要考虑。

各USB接口理论传输速度如下:

USB 1.0:1.5 Mbps(Low Speed)

USB 1.1:12 Mbps(Full Speed)

USB 2.0:480 Mbps(Hi Speed)

USB 3.0:5 Gbps(640 Mbps, Super Speed)

USB3.1:10 Gbps

USB2.0接口静电保护

USB2.0提供500Mbps的传输速度,本方案采用单颗器件防护,节约空间,

保证信号完整性,满足IEC61000-4-2,等级4,接触放电8kV,空气放电15kV

如对Vbus有过流要求,需配PTC保护。

双USB 接口静电保护

USB2.0提供500Mbps的传输速度,本方案采用单颗器件防护2个USB,节约空间,保证信号完整性,满足IEC61000-4-2,等级4,接触放电8kV,空气放电15kV如对Vbus有过

流要求,需配PTC保护。

可以采用单颗器件同时保护高速数据线,满足静电的测试要求。

电子产品的接口防护需用过压保护器件,很多工程师意识到要用保护器件,但由于选型不当或没按照ESD电路PCB设计原则,造成产品静电测试或EMC测试不通过,产品多次验证测试,浪费人力财力,造成产品延迟上市的事情总有发生,或过度设计,造成成本压力。

雷卯电子专业为客户提供电磁兼容EMC的设计服务,提供实验室做摸底测试,从客户高效,控本方便完成设计,希望为更多的客户能快速通过EMC的项目,提高产品可靠性尽力。

雷卯电子电磁兼容实验室,提供免费测试,提供外围静电保护参考电路。

HDMI、USB 2.0等高速端口的ESD保护(一)

HDMI、USB 2.0等高速端口的ESD保护(一)在高速数据率下,低ESD庇护对于保持 2.0、IEEE 1394以及ITV操作中用法的DVI和协议的数据完整性十分关键。

为实现良好的ESD庇护,应当选用具有什么特性的庇护器件呢?布局布线又有什么特别要求呢?本文给出具体分析。

在高速数据率下,低电容ESD庇护对于保持USB 2.0、IEEE 1394以及ITV操作中用法的DVI和HDMI协议的数据完整性是很关键的。

全世界有数百万的家庭都已经在通过卫星电视、有线电视以及陆地广播享用互动式电视(ITV)服务。

借助于计算机技术,ATSCACAP协议正在通过数据广播(PC下载) 以及实时互动应用服务成为富有生命力的广播服务。

通过将计算机装入电视机并为数字式增强嬉戏、运动、互动广告、信箱和因特网接入功能,ITV正在成为电视和家庭消遣的一道风景线。

随着这些行业的汇聚联合,创造商必需对设备需求作出响应,以便容纳更高的数据率以及符合当前和拟议中的通信需求。

另外,庇护昂贵的设备不会受到因用户错误操作、环境危害或电源变幻所引起的致命的损坏也是一项关键的设计课题。

USB2.0、IEEE 1394、ITV应用和操作中用法的数字式可视接口(DVI)和高清楚度多媒体接口(HDMI)协议允许高速数据传输率,并可以支持即插即用热插拔安装和操作。

但这些外部端口很简单受到来自工作环境和周边设备的破坏性的 ESD 脉冲的损害。

ESD抑制器件除了庇护数据传输线路之外,必需保持其信号的完整性。

通常,USB 2.0支持480Mbps(bits per second)的数据传输;DVI和HDMI协议更是分离支持高达 8Gbps和5Gbps的数据传输带宽。

在USB2.0、DVI和HDMI的高速数据率下,传统庇护装置的寄生电容可能破坏信号的完整性或令其失真。

失真表现为由较慢的升高和下降时光所致的高态/低态瞬变的前沿和后沿被修圆。

升高和下降时光较慢会给系统带来一些问题,其中最重要的是时序问题。

硬件设计:接口--USB2.0电路设计

硬件设计:接⼝--USB2.0电路设计参考资料:⼀、USB2.0物理特性 1.1、USB接⼝ USB连接器包含4条线,其中VBUS、GND⽤于提供5V电源,电流可达500mA;⽽D+、D-⽤于USB数据传输。

D+、D-是⼀组差分信号,差分阻抗为90欧,具有极强的抗⼲扰性;若遭受外界强烈⼲扰,两条线路对应的电平会同时出现⼤幅度提升或降低的情况,但⼆者的电平改变⽅向和幅度⼏乎相同,所以两者之间的电压差值可始终保持相对稳定。

扩展:USB OTG(即USB On-The-Go)技术在完全兼容USB2.0标准的基础上,增添了电源管理(节省功耗)功能,它允许设备既可作为主机,也可作为外设操作,实现了在没有主机的情况下,设备与设备之间的数据传输。

例如数码相机直接连接到打印机上,通过OTG技术,连接两台设备间的USB⼝,将拍出的相⽚⽴即打印出来。

USB OTG接⼝中有5条线: 2条⽤来传送数据D+ 、D-; 2条是电源线VBUS、GND; 1条是ID线,⽤于识别不同的电缆端点,mini-A插头(即A外设)中的ID引脚接地,mini-B插头(即B外设)中的ID引脚浮空。

当OTG设备检测到接地的ID引脚时,表⽰默认的是A设备(主机),⽽检测到ID引脚浮空的设备则认为是B设备(外设)。

1.2、反向不归零编码(NRZI) 反向不归零编码(Non Return Zero Inverted Code)的编码⽅式⾮常简单,即⽤信号电平的翻转代表“0”,信号电平保持代表“1”。

这种编码⽅式既可以保证数据传输的完整性,还不需要传输过程中包含独⽴的时钟信号,从⽽可以减少信号线的数量。

但是当数据流中出现长“1”电平时,就会造成数据流长时间⽆法翻转,从⽽导致接收器丢失同步信号,使得读取的时序发⽣严重的错误;所以在反向不归零编码中需要执⾏位填充的⼯作,当数据流中出现连续6个“1”电平就要进⾏强制翻转(即⾃动添加⼀位“0”电平),这样接收器在反向不归零编码中最多每七位就会出现⼀次数据翻转,从⽽保证了接收器的时钟同步,同时接收器端会扔掉⾃动填充的“0”电平,保证了数据的正确性(即使连续6个“1”电平后为“0”电平,NRZI仍然会填充⼀位“0”电平); USB的数据包就是采⽤反向不归零编码⽅式,所以在总线中不需要时钟信号。

USB2.0辐射解决方案

五、思考与启示 为了尽可能在设计早期就考虑 USB 的 EMC 问题,现对 USB 端口 EMC 设计做如下总结:

(一)电路设计

1、电路滤波设计要点: (1)L17 为共模滤波器,用于滤除差分信号上的共模干扰;阻抗选择范围为 60Ω /100MHz

~120Ω /100MHz,典型值选取90Ω /100MHz。 (2)FB13 为滤波磁珠,用于滤除为电源上的干扰;滤除电源上的干扰;FB13 磁珠阻抗范围 为 100Ω /100MHz ~1000Ω /100MHz,典型值选取 600Ω /100MHz ;磁珠在选取时通流量应 符合电路电流的要求,磁珠推荐使用大电流磁珠;

证 缩短 力。

5、如果差分线所在层的信号地需要大面积覆铜,注意信号地与差分线之间要保

35mil 以上的间距,以免覆铜后降低差分线的阻抗。 6、在其他信号层可以放置一些具有信号地属性的过孔,增加信号地的连接性,

信号电流回流路径。 7、在 USB 总线的电源线和 PCB 板的电源线上,可以加磁珠增加电源的抗干扰能

(3)C1、C2 为电源滤波电容,C1、C2 两个电容在取值时要相差 100 倍;典型值为 10UF、 0.1UF,小电容用于滤除电源上的高频干扰,大电容用于滤除电源上的纹波干扰;

(4)FB8 为接口地和数字地之间的跨接电容或磁珠,典型取值为 1000pF 或 600R 磁珠,它 可根据测试情况进行调整;

七、线缆设计

屏蔽电缆的屏蔽层要求与金属连接器进行 360°的搭接;搭接方式如上图。 八、总结

USB 具有速度快、功耗低、支持即插即用、使用安装方便等特点,因此现带很多电子设 备都会使用,而他的 EMC 问题,一直以来也都是工程师设计的难度之一,希望本文对大家会 有所帮助。

USB应用中的电磁兼容保护设计

USB应用中的电磁兼容保护设计

USB端口对PC外设的发展起到了革命性的推动作用,并且正变得越来越流行,比如在采集测量数据或在机器上安装软件更新等应用中就非常常见。

作为用于数据传输的一种总线系统,只要有移动设备连着的地方就有它的身影。

虽然在日常生活中使用的连接器看起来非常结实,但USB应用开发人员仍然必须重视这些接口的保护。

在Intel公司的高速USB平台设计指南中,甚至提高了考虑USB端口易感性因素的重要性。

Intel建议用电流补偿型扼流圈抑制EMI,再用其它元件防止静电放电(ESD)。

电子设备经常会遭受静电放电。

静电放电脉冲电压可能高达30kV,因此对所有类型的集成电路来说都是非常危险的。

目前有些IC对静电放电来说是安全的,但这种安全性只是对一小部分潜在威胁来说是有保证的。

日常操作表明:额外保护是必不可少的。

只有采取外部保护措施才能开发出整块电路板不受静电放电影响以及高度可靠的产品来。

专门的抑制措施同样也是必需的。

无线联网的电子设备如今是遍地开花,它们的数量正在与日俱增。

使自己的产品不受辐射干扰的影响非常重要。

只有考虑了预期的干扰形式,才能在设计中及时集成必要的抑制元件,进而缩短开发周期。

我们知道,自身产品的辐射型干扰也必须处于某个电平之下。

这可以通过EMC测。

SRV05-4在USB2.0接口的静电防护方案

SRV05-4在USB2.0接口的静电防护方案

优恩半导体(UN)

B接口的应用前景

随着计算机等通讯技术的飞速发展,对计算机的外设种类要求增多及PCB上有限的空间之间的矛盾也变的日益突出。

由英特尔等公司联合推出的通用串行总线USB为解决这一问题提供了良好的方案。

同时现在新型的仪器仪表越来越向智能化、模块化等方向发展,而现在的智能化设备要求实现数据的高速传输,通常采用USB技术,同时

USB的即插即用和热插拔功能也为仪器仪表的模块化提供了可能。

2.方案应用背景

USB2.0支持即插即用和热插拔功能

USB2.0接口的数据传输速率高,不容许出现数据缺失

USB2.0接口的集成度较高,且脆弱,较易受到静电损坏

3.应用产品

计算机外设设备

机顶盒

游戏机

便携设备如移动终端手机、平板等

4.应用方案

USB2.0应用方案

产品型号及重要参数

USB2.0方案说明及注意事项

该ESD器件结电容小于1.2pF,可高效的实现USB接口高速的数据传输要求

该器件拥有极低的漏电流,可减少正常工作下的功率损耗

响应速率快,可以在ESD脉冲上升时间内保护USB元件

同时该产品封装为SOT-26,封装体积小,可节约PCB的空间。

EMC对策与雷击防护

EMC对策与雷击防护前言由于IC与LSI高速化与高度积体化,使得IC与LSI本身就成是巨大的噪讯发生源,此外基于低耗电量的要求,即使IC与LSI低耗电化或是低噪讯化,从机器整体的角度观之,机器对外部的噪讯反而变得极端敏感,因此有必要开发可抑制EMC等电磁干扰的技术。

噪讯对策可分为两种方式,一种是直接抑制噪讯,另一种方式是避免外部噪讯造成电磁性结合引发电路误动作,前者必需采取EMI对策,后者则需采取EMS对策。

在电磁噪讯充斥的环境下设计电子电路,除了成本trade off考虑之外,概括性的对策手段摸索与理论的结合成为重要的手法,因此接着要深入探讨EMI与EMS的防护与对策。

IC与LSI高速化与封装时的噪讯对策设计电子电路时选用适合电路动作速度的逻辑IC非常重要,如果IC动作速度超过设计上的要求时,系统与机器的频宽会大幅增加(图1),抑制机器产生的噪讯变得毫无意义,而且更不易进行EMC对策。

最近大部分的电子机器都使用高速低电压CMOS IC,若与以往常用的TTL IC比较,CMOS IC反而更容易因噪讯造成电子电路误动作。

噪讯发生源通常是在电流变化(di/dt)很大的部位。

CMOS IC是在switching产生大电流(过渡电流与充放电电流)变化时动作,此时若流入具有有限阻抗(impedance)的ground line(主要是ind uctance成份),该部位就会发生电压下降现象,而压降造所成电路误动作,会因低电压IC的阀值越低越危险。

相较之下高速IC的场合,即使是数ns的噪讯也会引发电路误动作,因此不论是设计电子电路或是封装设计,噪讯对策时必需注意以下要点:(a).电源与接地层低阻抗化双面电路基板对动作速度较低的数字电路,具有良好的低阻抗效应,因此接地可以采用如图2所示的网状(mesh)导线,如果能缩小电源‧接地(ground)所形成的回路面积(loop area),即使受到外部磁界影响产生诱导电流,由于该电流会相互抵销,因此整体而言双面电路较不易受到外部磁界影响。

USB2.0接口EMC设计方案

USB2.0接口EMC设计方案一、接口概述USB 通用串行总线(英文:Universal Serial Bus,简称USB)是连接外部装置的一个串口汇流排标准,在计算机上使用广泛,但也可以用在机顶盒和游戏机上,补充标准On-The-Go ( OTG)使其能够用于在便携装置之间直接交换资料。

USB接口的电磁兼容性能关系到设备稳定行与数据传输的准确性,赛盛技术应用电磁兼容设计平台(EDP)软件从接口原理图、结构设计,线缆设计三个方面来设计USB2.0接口的EMC设计方案二、接口电路原理图的EMC设计本方案由电磁兼容设计平台(EDP)软件自动生成1. USB2.0接口防静电设计图1 USB 2.0接口防静电设计接口电路设计概述:本方案从EMC原理上,进行了相关的抑制干扰和抗敏感度的设计;从设计层次解决EMC 问题。

电路EMC设计说明:(1)电路滤波设计要点:L1为共模滤波电感,用于滤除差分信号上的共模干扰;L2为滤波磁珠,用于滤除为电源上的干扰;C1、C2为电源滤波电容,滤除电源上的干扰。

L1共模电感阻抗选择范围为60Ω/100MHz ~120Ω/100MHz,典型值选取90Ω/100MHz;L2磁珠阻抗范围为100Ω/100MHz ~1000Ω/100MHz,典型值选取600Ω/100MHz ;磁珠在选取时通流量应符合电路电流的要求,磁珠推荐使用电源用磁珠;C1、C2两个电容在取值时要相差100倍,典型值为10uF、0.1uF;小电容用滤除电源上的高频干扰,大电容用于滤除电源线上的纹波干扰;C3为接口地和数字地之间的跨接电容,典型取值为1000pF,耐压要求达到2KV以上,C3容值可根据测试情况进行调整;(2)电路防护设计要点D1、D2和D3组成USB接口防护电路,能快速泄放静电干扰,防止在热拔插过程中产生的大量干扰能量对电路进行冲击,导致内部电路工作异常。

D1、D2、D3选用TVS,TVS反向关断电压为5V;TVS管的结电容对信号传输频率有一定的影响,USB2.0的TVS结电容要求小于5pF。

汽车充电站防雷系统设计方案

汽车充电站防雷系统设计方案一、引言随着电动汽车的快速普及,汽车充电站的建设也逐渐成为现代城市发展的重要组成部分。

然而,汽车充电站所处的室外环境对防雷系统提出了更高的要求。

本文将针对汽车充电站防雷系统进行设计,确保系统的稳定运行和人员的安全。

二、系统需求1.安全性:保证汽车充电站的设备和人员安全,避免因雷击导致的事故和损失。

2.稳定性:确保汽车充电设备的正常运行,避免因雷击引起的设备损坏和停机。

3.可靠性:设计防雷系统能够有效地抵御各种天气条件下的雷击。

1.天线接地系统在防雷系统设计中,天线接地是非常重要的一部分。

天线应选择合适的接地方式,如垂直接地或水平接地。

同时,接地系统应由专业人员设计和施工,确保接地电阻符合要求。

2.避雷器应用避雷器的应用是防雷系统中必不可少的一环。

避雷器可以有效地吸收和放散雷电能量,防止雷击对设备的伤害。

在汽车充电站防雷系统中,应选择能够满足雷电等级要求的避雷器,并按照规范进行安装和维护。

3.金属屏蔽金属屏蔽是一种常见的防雷手段,可以有效地将雷电能量引导到地下或远离设备的区域。

汽车充电站的金属屏蔽应考虑到建筑结构的特点和周边环境,确保其能够起到预期的防雷效果。

4.接触电阻控制为了保证防雷系统的可靠性,接触电阻的控制是关键。

在设计和施工过程中,要确保接触电阻满足国家标准和规范要求,并定期进行检测和维护。

5.监测和维护防雷系统的监测和维护是确保系统正常运行的重要环节。

应定期进行系统的巡检和维护,检查设备的状态和接地电阻,并及时修复和更换受损的部件。

四、系统实施方案1.由专业的设计院或机构进行防雷系统的设计和论证,确保系统的合理性和可行性。

2.施工过程中,应严格按照设计方案进行,确保安装质量和施工标准。

3.针对系统运行中出现的问题,应及时记录并进行故障排除。

4.定期对防雷系统进行检测和维护,确保系统始终保持良好的工作状态。

五、总结汽车充电站作为现代城市的重要设施,其防雷系统的设计至关重要。

USB 2.0高速端口的ESD保护设计方案

USB 2.0 高速端口的ESD 保护设计方案通用串行总线(USB)高速数据应用也十分普遍,用户在热插拨任何USB 外设时可能会导致ESD 事件。

此外,在离导电表面几英寸的地方也可能发生空气放电,可能损坏USB 接口及芯片。

因此,设计人员必须为USB 元件提供ESD 保护。

业界制定了不少针对不同瞬态干扰的ESD 标准,比如针对系统级ESD 事件的IEC61000-4-2 国际标准。

另外还有一些元器件级的ESD 敏感度测试标准,如人体模型(HBM)和机器模型(MM)等。

USB 2.0 高速数据线路应用的半导体ESD 保护元件应当具备下列重要特性:极低电容:将USB 2.0 高速数据线路(480 Mbps)中的信号衰减减至最小;快速动作响应时间(纳秒级):在ESD 脉冲信号快速上升时保护USB 元件;低泄漏电流:将额定工作条件下的功率消耗减至最低;强固性:能够承受很多次的ESD 事件冲击而不受损伤;小封装:集成型更小封装本文介绍安森美半导体的新的低电容瞬态电压抑制器(TVS)二极管阵列NUP4114UPXV6 的主要特性,并讨论如何为USB 2.0 高速数据线路提供有效的ESD 保护。

NUP4114UPXV6 的特性及配置选择NUP4114UPXV6 是一款非常适合USB 2.0 高速数据线路ESD 保护的TVS 二极管阵列。

该器件具有0.8pF 的极低电容(I/O 线路与地之间的典型电容),能将USB 2.0 高速数据线路中的信号衰减降至最低。

该器件满足13 kV 接触放电的系统级IEC61000-4-2 标准,并能承受人体模型3B 类(超过8 kV)和机器模型C 类(超过400V)的CMOS 器件级ESD 额定脉冲,具有强固的ESD 保护性能。

此。

USB 2.0的EMI和ESD设计

USB 2.0的EMI和ESD设计提供双向、实时数据传输的USB接口,以其即插即用、可热插拔和价格低廉等优点,目前已成为计算机和信息电子产品连接外围设备的首选接口。

时下流行的USB2.0具有高达480Mbps的传输速率,并与传输速率为12Mbps的全速USB1.1和传输速率为1.5Mbps的低速USB1.0完全兼容。

这使得数字图像器、扫描仪、视频会议摄像机等消费类产品可以与计算机进行高速、高性能的数据传输。

另外值得一提的是,USB2.0的加强版USB OTG可以实现没有主机时设备与设备之间的数据传输。

例如。

数码相机可以直接与打印机连接并打印照片,PDA可以与其它品牌的PDA进行数据传输或文件交换。

USB接口的传输速率很高,因此如何提高USB信号的传输质量、减小电磁干扰(EMI)和静电放电(ESD)成为USB设计的关键。

本文以USB2.0为例,从电路设计和PCB设计两个方面对此进行分析。

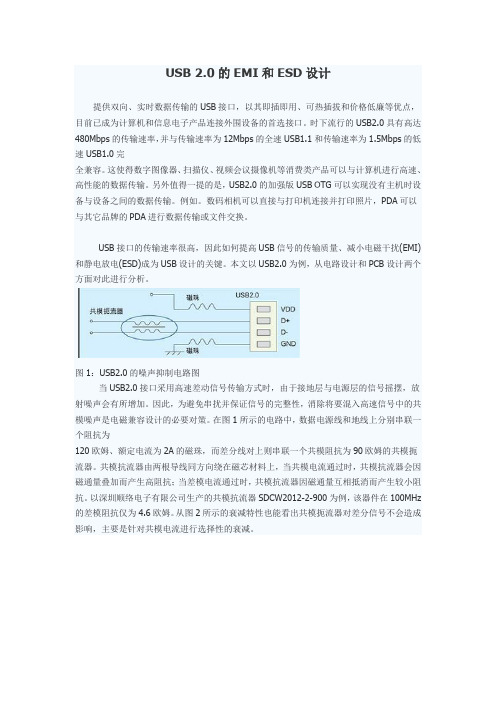

图1:USB2.0的噪声抑制电路图当USB2.0接口采用高速差动信号传输方式时,由于接地层与电源层的信号摇摆,放射噪声会有所增加。

因此,为避免串扰并保证信号的完整性,消除将要混入高速信号中的共模噪声是电磁兼容设计的必要对策。

在图1所示的电路中,数据电源线和地线上分别串联一个阻抗为120欧姆、额定电流为2A的磁珠,而差分线对上则串联一个共模阻抗为90欧姆的共模扼流器。

共模抗流器由两根导线同方向绕在磁芯材料上,当共模电流通过时,共模抗流器会因磁通量叠加而产生高阻抗;当差模电流通过时,共模抗流器因磁通量互相抵消而产生较小阻抗。

以深圳顺络电子有限公司生产的共模抗流器SDCW2012-2-900为例,该器件在100MHz 的差模阻抗仅为4.6欧姆。

从图2所示的衰减特性也能看出共模扼流器对差分信号不会造成影响,主要是针对共模电流进行选择性的衰减。

图2:SDCW2012-2-900的衰减频谱由于USB接口具有可热插拔性,USB接口很容易因不可避免的人为因素而导致静电损坏器件,比如死机、烧板等。

USB2.0标准保护电路设计指南_图文(精)

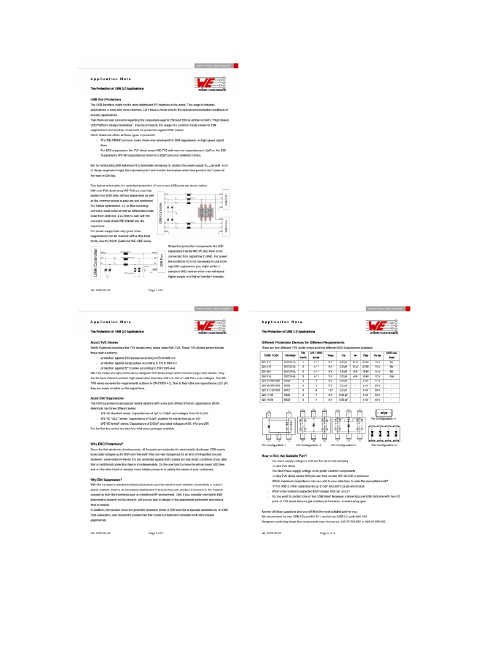

Application Note The Protection of USB 2.0 Applications Order Code 824 015 Competitor S 824 001 Competitor P I/O VRWM VCl,IO VCl,VDD VESD CIN IPP Package SOT23-6L SOT23-6L SOT23-6L SOT23-6L I/O 4 4 4 4 VRWM 5 5 5 5 V Cl,IO 12 22 14 28 VCl,VDD 7,5 15,5 9 19 VESD 12 kV 15 kV 8 kV 8 kV C IN 2 pF 3 pF 1 pF 3 pF IPP 12 A 12 A 5A 6A Number of I/O lines the TVS-Diode can protect Max. reverse working voltage ESD clamping voltage at I/O pin (IEC 61000-4-2, contact mode at 6kV ESD clamping voltage at VDD pin (IEC 61000-4-2, contact mode at 6kV Max. withstanding ESD pulse (IEC 61000-4-2, contact mode Input capacitance at I/O pin via. GND (VIN = 2,5V, VDD=5V Max. Withstanding surge current (8/20µs TLP Curve of different parts for VDD TLP Curve of different parts for I/O lines Recommended Layout for Single Single USB Port The two differential signal lines (D+ and D- are routed from connector to TVS-Diode (p/n 824 011 and via a common mode choke (p/n 744 232 090 to the USB controller as shown on the left picture below. This results in an awesome ESD protection and EMI suppression of both data lines. VBUS is routed like the signal line, but instead of the common mode choke a chip bead ferrite (p/n 742 792 641 is used.After the chip bead you may add a capacitor and a second chip bead as well to get the highest possible EMI suppression effect. For very sensible IC’s and / or high reliable applications you can get an optimized ESD suppression effect if you double contact a four-fold TVS array (p/n 824 015 like shown on right picture. JB, 2009-06-23 Page 6 of 9Application Note The Protection of USB 2.0 Applications Protection of single USB port Double protection of single USB port Designers preferring single channel components can also use the ESD Suppressors WE-VE. The connection has to be carried out from D+ / D- to GND. The other parts are connected in same way as above. Protection of single USB port Recommended Layout for Double USB Port According to single USB port protection the routing is very similar. Use here exactly the same parts as for single port protection and the protection level will also be the same. Protection of double USB port JB, 2009-06-23 Page 7 of 9Application Note The Protection of USB 2.0 Applications Bill of Material: Material: In this application note the following parts are used TVS-Diodes WE-TVS: 824 011: 824 015: Protection of 2 I&O lines and VDD line: Size SOT23-5L | 2pF CI/O | 5V VRWM | 5A IPP Protection of 4 I&O lines and VDD line: Size SOT23-6L | 2pF CI/O | 5V VRWM | 5A IPP ESD Suppressors WE-VE: 823 07 050 029: 823 06 050 029: Size 0402 | 0.2pF Ctyp | 5V VRWM | 17V VCL Size 0603 | 0.2pF Ctyp | 5V VRWM | 30V VCL Common Mode Chokes WE-CNSW: 744 232 090: Size 1206 | 370mA IDC | 300 mΩ RDC | 90Ω Impedance Chip Bead Ferrites WE-CBF: 742 792 641: Size 0603 | 2 000mA IDC | 150mΩ RDC | 300Ω Impedance USB-Connectors WR-COM: 614 008 260 21: 614 004 135 023: USB Typ A Connector | THT | Dual stacked USB Typ A Connector | THT | Vertical JB, 2009-06-23 Page 8 of 9Application Note The Protection of USB 2.0 Applications Interface Design Kit For an easy design of interfaces Würth Elektronik has launched a special Interface Design Kit. This design kit includes a design guide for USB 1.0 to USB 2.0, CAN, Ethernet, VGA, DVI, RS232 and RS485 interfaces and all the components used. These are ESDSuppressors, SMD Common Mode Chokes, Chip Bead Ferrites, LAN Transformers and the corresponding Connectors. In total are 35 different passive components with 235 parts and 4 evaluations boards in. The colour scheme makes it easy to locate the suitable parts for your application. Just follow the specific application colour and arrange your needed parts. For each application you find a simple block schematic where you see how to place the different components to get the best result. Try it - it’s worth each penny pen ny!! ny !! JB, 2009-06-23 Page 9 of 9。

USB 2.0标准保护电路设计指南

About Abo ut ESD Suppressors The ESD suppressors are special raised varistors with a low and defined intrinsic capacitance. Würth Elektronik has three different series: WE-VE standard series: Capacitances of 1pF to 120pF and voltages from 5V to 24V WE-VE “ULC” series: Capacitance of 0.2pF, suitable for signal lines up to 12V WE-VE femtoF series: Capacitance of 0.05pF and rated voltages of 6V, 14V and 26V

Two typical schematics for optimized protection of one or two USB ports are shown below: With one TVS diode array WE-TVS you can fully protect two USB lines. All four signal lines as well as the common power supply are well protected. For further optimization, i.e. to filter incoming common mode noise as well as differential mode noise from USB line, a LC filter is built with the common mode choke WE-CNSW and the capacitors. For power supply lines very good noise suppressions can be reached with a chip bead ferrite, like the Würth Elektronik WE-CBF series. Single line protection components like ESD suppressors series WE-VE also have to be connected from signal line to GND. For power line protection it is not necessary to use a low cap ESD suppressor, you might prefer a standard SMD varistor which can withstand higher surges and higher transient energies.

USB2.0接口EMC设计方案

电磁兼容设计平台(EDP)应用案例——以太网口USB2.0 接口 EMC 设计方案一、接口概述USB 通用串行总线(英文:Universal Serial Bus,简称 USB)是连接外部装置的一个串口汇流排标准,在计算机上使用广泛,但也可以用在机顶盒和游戏机上,补充标准On-The-Go ( OTG)使其能够用于在便携装置之间直接交换资料。

USB 接口的电磁兼容性能关系到设备稳定行与数据传输的准确性,赛盛技术应用电磁兼容设计平台(EDP)软件从接口原理图、结构设计,线缆设计三个方面来设计USB2.0 接口的 EMC 设计方案二、接口电路原理图的EMC设计本方案由电磁兼容设计平台(EDP)软件自动生成B2.0 接口防静电设计图1 USB 2.0接口防静电设计接口电路设计概述:本方案从 EMC 原理上,进行了相关的抑制干扰和抗敏感度的设计;从设计层次解决 EMC 问题。

电路 EMC 设计说明:(1)电路滤波设计要点:L1 为共模滤波电感,用于滤除差分信号上的共模干扰;L2 为滤波磁珠,用于滤除为电源上的干扰;C1、C2 为电源滤波电容,滤除电源上的干扰。

L1共模电感阻抗选择范围为60Ω/100MHz ~120 Ω /100MHz ,典型值选取90Ω/100MHz ;L2 磁珠阻抗范围为 100Ω /100MHz ~1000Ω /100MHz ,典型值选取 600Ω /100MHz ;磁珠在选取时通流量应符合电路电流的要求,磁珠推荐使用电源用磁珠;C1、C2 两个电容在取值时要相差 100 倍,典型值为 10uF、0.1uF;小电容用滤除电源上的高频干扰,大电容用于滤除电源线上的纹波干扰;C3 为接口地和数字地之间的跨接电容,典型取值为1000pF,耐压要求达到2KV 以上,C3 容值可根据测试情况进行调整;( 2)电路防护设计要点D1、 D2 和 D3 组成 USB 接口防护电路,能快速泄放静电干扰,防止在热拔插过程中产生的大量干扰能量对电路进行冲击,导致内部电路工作异常。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

USB2.0接口EMC设计方案

一、接口概述

USB 通用串行总线(英文:Universal Serial Bus,简称USB)是连接外部装置的一个串口汇流排标准,在计算机上使用广泛,但也可以用在机顶盒和游戏机上,补充标准On-The-Go ( OTG)使其能够用于在便携装置之间直接交换资料。

USB接口的电磁兼容性能关系到设备稳定行与数据传输的准确性,赛

二、接口电路原理图的EMC设计

1. USB

2.0接口防静电设计

图1 USB 2.0接口防静电设计

接口电路设计概述:

本方案从EMC原理上,进行了相关的抑制干扰和抗敏感度的设计;从设计层次解决EMC 问题。

电路EMC设计说明:

(1)

电路滤波设计要点:

L1为共模滤波电感,用于滤除差分信号上的共模干扰;

L2为滤波磁珠,用于滤除为电源上的干扰;

C1、C2为电源滤波电容,滤除电源上的干扰。

L1共模电感阻抗选择范围为60Ω/100MHz ~120Ω/100MHz,典型值选取90Ω/100MHz;

L2磁珠阻抗范围为100Ω/100MHz ~1000Ω/100MHz,典型值选取600Ω/100MHz ;磁珠在选取时通流量应符合电路电流的要求,磁珠推荐使用电源用磁珠;

C1、C2两个电容在取值时要相差100倍,典型值为10uF、0.1uF;小电容用滤除电源上的高频干扰,大电容用于滤除电源线上的纹波干扰;

C3为接口地和数字地之间的跨接电容,典型取值为1000pF,耐压要求达到2KV以上,C3容值可根据测试情况进行调整;

(2)电路防护设计要点

D1、D2和D3组成USB接口防护电路,能快速泄放静电干扰,防止在热拔插过程中产生的大量干扰能量对电路进行冲击,导致内部电路工作异常。

D1、D2、D3选用TVS,TVS反向关断电压为5V;TVS管的结电容对信号传输频率有一定的影响,USB2.0的TVS结电容要求小于5pF。

接口电路设计备注:

如果设备为金属外壳,同时单板可以独立的划分出接口地,那么金属外壳与接口地直接电气连接,且单板地与接口地通过1000pF电容相连;

如果设备为非金属外壳,那么接口地PGND与单板地GND直接电气连接。

三、连接器设计

本方案由电磁兼容设计平台(EDP)软件自动生成

USB AF连接器USB信号排序设计

图1 USB连接器结构设计

连接器USB与机体的搭接方式:

(1)面板开孔时采用精密的铣削加工技术,使孔眼的形状更适合连接器的放置,避免孔眼切削不精确的地方出现缝隙,进而降低电磁干扰辐射;经过测试证明,精确的铣削开孔

加工可以提高12~18%的电磁兼容性;

(2)机体与USB金属连接器之间的接合处要增加金属弹片,使两者接合时能够保持良好的导电性能。

具体搭接方式如上图所示:

四、线缆设计

本方案由电磁兼容设计平台(EDP)软件自动生成

USB-2.0接口信号线缆

线缆设计要求:USB2.0 AF连接器普通型

图1 USB金属连接器的搭接

屏蔽层与金属连接器的搭接:

(1)屏蔽电缆的屏蔽层要求与金属连接器进行360°的搭接;搭接方式如上图:

(2)屏蔽电缆屏蔽层要避免出现单独的“尾巴”现象。

五、结束语

电磁兼容设计平台(EDP),依据最专业的EMC专家方案知识库,快速输出符合产品设计要求的指导性的EMC解决方案。

即是工程师身边的产品设计、学习助手,又是企业的EMC 技术方案库,是产品电磁兼容性能的保证。

图2 USB-2.0信号电缆

电缆设计:

(1)USB-2.0信号电缆采用网状编织屏蔽层的屏蔽方式,且网状编织层编织密度要求不小于90%;差分线组采用铝箔屏蔽;

(2)内部组线时,差分电缆采用双绞传输,双绞绞距一般为最小绞距的2倍,(最小绞距= D为电缆的外径);组线方式如上图所示:

(3)电缆两端需要增加磁环处理,磁环内径与电缆的外径要紧密结合,尽量选择厚长型的磁环。

走线设计:

(1)USB-2.0信号电缆走线时要求远离其他强干扰源,如电源模块;

(2)电缆走线最好单独走线或与其他模拟以及功率线缆保持10cm以上距离,切不可与其他线缆一起混合捆扎。