可编程ASCII 第四章课件

四章汇编语言程序设计ppt课件

ENDS,ASSUME,END ,…. 保留字:SEGMENT ENDS OFFSET SIZE DB

DW DD MOV PUSH ADD SUB MUL DIV INC DEC LOOP PROC ENDP CALL RET END

类别名

CODE、DATA、STACK(同名同类别段连续存放)

第4章 汇编语言程序设计

伪操作命令之三:段定义伪指令

段寄存器说明伪指令ASSUME

ASSUME 段寄存器名:段名[段寄存器名:段名[…..]]

例:

CODE SEGMENT ASSUME CS:CODE,DS:DATA,ES:DATA,SS:STACK

MAIN:

……

CODE ENDS ENDS MAIN

;指定第一条要执行的指令标号

注:1、该伪指令用于明确用SEGMENT定义的段的类型, 使编译程序能生成目标代码程序。

2、在源程序中,该伪操作放在可执行程序的前面。 3、该指令没有给段寄存器赋予实际的初值。这项工作要通

过写指令来完成,其中代码段不需要赋值。

+、-、*、/、MOD、SHL、SHR 都可应用于数字运算。 +、- 可以用于表示存储器操作数的地址,或两个存储器

单元(同一段内)的地址偏移量之差。 例:SUM - 2

CYCLE - GO

第4章 汇编语言程序设计

运算符之二:逻辑运算符

AND、OR、XOR、NOT 按位的逻辑运算 例:IN AL,PORT_VAL

DATA2 DB 0C1H,36H,9EH,0D5H,20H;加数

DATA ENDS;数据段结束

CODE SEGMENT;定义代码段

第4章汇编语言程序设计知识PPT课件

┇

(1500H)=72H, (1501H)=34H, (1502H)=00H,

(1503H)=8AH,(1504H)=00H, (1505H)=10H。

(1506H)=00H,(1507H)=48H (H的ASCII值)

第24页/共61页

§4.2 伪指令

7、DS 定义存储空间命 令

格式:DS 表达式 功能:在汇编时,从指定地址开始保留DS之后表达式的值所

第15页/共61页

§4.2 伪指令

1、ORG 汇编起始地址命令

格式:ORG 16位地址

功能:规定该伪指令后面程序的汇编地址,即汇编后生成目

标程序存放的起始地址。

例如:

ORG 2000H

START:MOV A,#64H

┇

规定了START的地址是2000H,又规定了汇编后的第一条指令 码从2000H开始存放。

§4.2 伪指令

例如:

ORG 2000H DB 0A3H

LIST:DB 26H,03H STR: DB ‘ABC’

┇

A3H 26H 03H 41H 42H 43H

2000H 2001H 2002H 2003H 2004H 2005H

经汇编后:(2000H)=A3H, (2001H)=26H, (2002H)=03H, (2003H)=41H, (2004H)=42H, (2005H)=43H,

第31页/共61页

§4.4 汇编语言程序的基本结构

1、顺序程序 2、分支程序 3、循环程序

第32页/共61页

§4.4 汇编语言程序的基本结构

1、顺序程序

顺序程序是最简单的程序结构,也称直线程序。 程序按顺序一条一条地执行指令。这类程序是所有复杂程序的基础。 要写出高质量的程序还是需要掌握一定的技巧,需要熟悉指令系统,正确地选择 指令,最大限度地优化程序。

第4章可编程控制器指令系统1

第四章可编程控制器编程软件和编程语言【主要内容】编程软件WPLSoft的安装 WPLSoft的使用说明程序的建立梯形图编程模式指令表编程模式批注编程通信联机模式 SFC编程说明 通信设置功能 帮助功能介绍 小结思考题与练习题4.1 编程软件WPLSoft的安装WPLSoft为台达DVP系列可编程序控制器在WINDOWS操作系统环境下所使用的程序编程软件,该软件对系统的需求如表4-1所示。

WPLSoft除了一般PLC程序的规划及WINDOWS的一般编辑功能(例如:剪切、粘贴、复制、多窗口……)外,另提供多种中/英文批注编程及其它便利功能(例如:寄存器编程、设置、文件读取、存盘及各接点图标监测与设置等)。

4.2 WPLSoft的使用说明1.初始设置当激活WPLSoft编程软件之后,执行【文件】/【新建】命名,如图所示,即新建文件进行PLC程序设计,在如图所示的机种设置窗口中可以指定程序标题、PLC机种设置、程序容量(请参考所使用PLC主机的机种名称及程序容量规格)及文件名称等有关程序的初始设置。

文件/新建菜单机种选择4.2 WPLSoft的使用说明当完成上述设置后,便会出现二个子窗口:一为梯形图模式窗口,另一为指令模式窗口,如图所示。

读者可根据自身的编程设计习惯选择编程模式,开始编写PLC程序。

梯形图指令表4.2 WPLSoft的使用说明•梯形图模式:完成梯形图编程,必须由编译转换成指令码或SFC图。

•指令模式:完成指令编程,必须由编译转换成梯形图或SFC图。

•SFC编程模式:图示为SFC编程模式。

完成SFC编程,必须由编译转换成指令码,若要转换成梯形图必须再由指令码编译转换。

SFC编程模式4.2 WPLSoft的使用说明2.功能选择栏简介WPLSoft编程软件刚激活时,其功能选择栏中只有五个可点取的选项:文件(F)、视图(V)、通信(C)、设置(O)与帮助(H)。

在【文件(F)】的下拉菜单中执行【新建】指令后,其功能选择栏上会有其它选项:【编程(E)】、【编译(P)】、【批注(M)】、【查找(S)】等,下面将介绍一些主要功能和特殊功能。

第04章 汇编语言程序设计 39页 0.2M PPT版

MOV AL,10100000B OR 00000101B ;(AL)←10100101B

例4-4 关系运算符的应用

MOV AX,5 EQ 101B ;(AX)←0FFFFH

MOV BH,10H GT 16 ;(BH)←0

例4-5 数值返回运算符的应用

K1 DB 30H,31H,32H

K2 DW 4041H,4043H

(4)STACK

(5)MEMORY

(6)AT表达式

4. 类别名

返回

4.2.4 段寻址伪指令

格式:

ASSUME 段寄存器名:段名,段寄存器名:段名,……

例4-15 求从NUM开始的12个无符号字节数的和,结果放在SUM字单元中。

DATA SEGMENT NUM DB 95H,83H,36H,2DH DB 33H,22H,1AH,34H DB 62H,45H,75H,49H SUM DW ?

例4-13

STR1 DB ‘COMPUTER’ ;定义一个字符串,字符串的首地址为STR1 STR2 DW ‘AA’,‘BC’,‘DE’ ;给两个字符组成的字符串分配两个字节存储单元 DATA DW ?,?,? ;为DATA预留6个存储单元

例4-14

DATA1 DB 20 DUP(?) ;为变量DATA1分配20个字节的空间,初值为任意值 DATA2 DW ? ;为变量DATA2分配2个字节的空间,初值为任意值 DATA3 DB 20 DUP(30H) ;为变量DATA3分配20个字节的空间,初值均为30H

K3 DW 20H DUP(0)

K4 DD 50515253H

MOV AL,TYPE K1 ;等效于MOV AL,1

MOV AH,TYPE K2 ;等效于MOV AH,2

第4章汇编语言程序设计3(常见程序设计举例)精品PPT课件

;实际字符数送CL ;第一个字符送AL ;暂存在CH

;第一个字符是负

;不是,转NEXT1 ;字符数减1

;指向第一个数字字符 ;清零AX,存二进制数

;若(CL)=0,转NEXT2 ;取字符 ;转换成BCD码 ;加到中间结果上

10

NEXT2:

NEXT3: CHANGE ; CODE

MOV MUL INC JMP MOV AND ADD CMP JNZ NEG MOV RET ENDP

ENDS END

DX,10 DX BX SHORT LP1 DL,[BX] DL,0FH AX,DX CH,’-’ NEXT3 AX [DI],AX

START

;*10 ;指向下一个字符

;取个位数 ;个位ASCII→未组合BCD ;加个位数,(AX)=001AH

;是’-’? ;该数非负,转NEXT3 ;若为负,求补 ;存二进制结果

16

AGAIN1: NEXT1: AGAIN2: NEXT2:

;计算百位的个数 MOV DL,0 SUB AX,1000 JC NEXT1 INC DL JMP AGAIN1 ADD AX,1000 MOV [BX],DL ;计算百位的个数 MOV DL,0 SUB AX,100 JC NEXT2 INC DL JMP AGAIN2 ADD AX,100 MOV [BX+1],DL

;(SP)=0052H ;(AX)=25AFH ;(DI)=0002H STRING-4;(DI)=0005H ;(DX)=25AFH

BCD→二进制数在本例中采用用以下方法:

((((0+千位数)*10+百位数)*10)+十位数)*10+个位数

第一次中间结果

第四章1-2讲 汇编语言程序设计ppt课件

精选ppt课件2021

25

天津工业大学

(4)带DUP的表达式

• 在表达式中使用重复数据操作符DUP,可以为连 续的存储单元提供重复数据,其格式为:

• N DUP(表达式)

• 其中N为重复因子,只能取正整数,表示定义了N 个重复数据存储单元,其类型由它前面的数据定 义伪指令确定,而每个数据存储单元中的初值由 DUP后面圆括号中的表达式给定。

随机数

DB 3 DUP(22H,11H,?)

精选ppt课件2021

27

天津工业大学

09FF:0000 22 11 ? 22 11 ? 22 11

09FF:0008 ?

0F99:000B

精选ppt课件2021

28

天津工业大学

用?预留存储空间

• MEM1 DB 34H,’A’,?,?,?

•

DW 20 DUP(?)

• LENGTH 变量 * TYPE 变量

精选ppt课件2021

40

天津工业大学

– LENGTH和SIZE运算符的具体运算规则是:如果变量是用重复操 作符DUP定义的,那么运算符LENGTH的运算结果是外层DUP的 给定值 (即外层重复次数),如果没有用DUP定义的变量,运算 结果总是1。

而运算符SIZE是LENGTH和TYPE两个运算结果的乘积。

天津工业大学

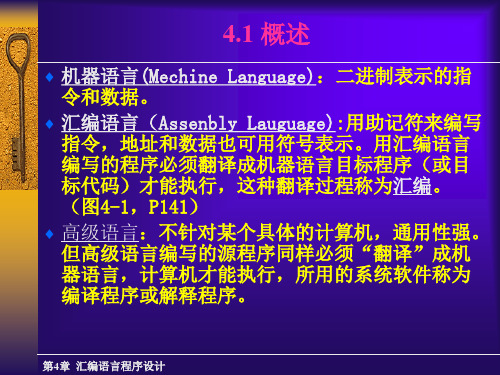

第4章 汇编语言程序设计

4.1 汇编语言源程序 4.2 伪指令 4.3 DOS系统功能调用 4.4 汇编语言程序设计基础 4.5 综合举例

精选ppt课件2021

1

天津工业大学

4.1 汇编语言源程序

了解:

• 计算机的三种语言 • 源程序的结构 • 汇编语言语句格式

第四章 可编程序控制器的编程语言与指令系统课件

5 步、转换和动作是顺序功能图的三

步3

种主要元件。

2020/3/18

动作1 动作2

第四章 可编程序控制器的编程语言和指令系统

4-1 可编程序控制器的编程语言概述

梯形图

X0 X1 X2

Y0

1 与继电器控制系统很相似,直 观易懂,容易掌握;

X3 X4 X5

2 适用于开关量的逻辑控制;

3 由触点、线圈和应用指令等组 成。触点代表逻辑输入条件, 线圈代表逻辑输出结果;

2020/3/18

4-3 FX系列可编程序控制器梯形图中的编程元件

六 、计数器(C)

3、 高速计数器

C235~C255 (X0~X7)

2020/3/18

4-3 FX系列可编程序控制器梯形图中的编程元件

六 、计数器(C)

3、 高速计数器

C235~C255 (X0~X7)

2020/3/18

3、 高速计数器 C235~C255 (X0~X7)

(3)程序执行是一个逻辑解算的过程。根据梯形图中各触 点的状态和逻辑关系,求出各个线圈对应的编程元件的状态

(4) 梯形图中的各编程元件的触点(常开和常闭),都可无限 次使用。

(5)梯形图中的线圈应该放在最右边。 2020/3/18

第四章 可编程序控制器的编程语言和指令系统

4-2 梯形图的主要特点

梯形图的编程特点

4-1 可编程序控制器的编程语言概述 结构文本 PASCAL BASIC C等高级语言

便于实现:

2020/3/18

数学运算 数据处理 图形显示 报表打印

第四章 可编程序控制器的编程语言和指令系统

4-2 梯形图的主要特点

(1)编程元件不是真实的硬件继电器,而是软件继电器。

第4章汇编语言程序设计课件

29

MASTERLI

‘H’‘E’‘L’‘L’‘O’

例2:操作数可以是字符串MASTERLI DB ‘HELLO’汇编后如下:

注意下面的不同DB ‘AB’41 ‘A’ 42 ‘B’

‘AB’‘B’ ‘A’

42

41

DW

30

例3:ABC DB 0, 1, ?, ?, ?LPI DW ?, 54, ? 汇编后如下图示:

第4章 汇编语言程序设计4.1 汇编语言源程序机器语言—用二进制来表示指令和数据。B0 64 什么意思?这就是机器语言。既不直观, 又不易理解和记忆。MOVAL,64H ;大家很清楚,这就是助记符。助记符—反映指令的功能和主要特征,便于人们 理解和记忆。

1

指令除了操作码以外,还有一个操作数问题。操作数可能放在存储器中,这就涉及一个地址问 题。程序中遇到转移指令或调用指令,涉及地址转 移,若采用具体地址就不很方便,一旦有错,改动就 很麻烦。于是人们采用标号或符号来代替地址,例:LP1: …┇LOOP LP1汇编语言 是用助记符、符号地址以及标号等符号 书写的程序。用汇编语言编写的程序叫源程序。

18

(3) 关系运算符EQ(相等),NE(不等),LT(小于),GT(大于), LE(小于或等于),GE(大于或等于)。关系运算符的两个操作数必须都是数字或者是 同一段内的两个存储器地址。关系为真,结果为0FFFFH;关系为假,结果为0。例:MOV BX, PORT_VAL GE 5若PORT_VAL的值大于等于5,则汇编后为:MOV BX, 0FFFFH若PORT_VAL的值小于5,则汇编后为:

(4) 取值运算符和属性运算符:分析和规定存储器的属性。

20

若BUFFER1存储区是用如下伪指令定义的: BUFFER1 DB 100 DUP(?)则 TYPE BUFFER1等于1。

4第四章课件汇编语言程序设计

三、操作数

操作数用于给指令的操作提供数据或地址。在一 条汇编语句中操作数可能是空缺的,也可能包括一 项,还可能包括两项或三项。各操作数间以逗号分 隔。操作数字段的内容可能包括以下几种情况:

(1)工作寄存器名; (2)特殊功能寄存器名; (3)标号名; (4)常数; (5)符号“$”,表示程序计数器PC的当前值; (6)表达式。

2 2019/9/15

二、进行算法的优化

算法是解决具体问题的方法。应用系统经过分 析、研究和明确规定后,对应实现的功能和技术指 标可以利用严密的数学方法或数学模型来描述,从 而把实际问题转化成由计算机进行处理的问题。

同一个问题的算法可以有多种,结果也可能不 尽相同,所以,应对各种算法进行分析比较,并进 行合理的优化。比如,用迭代法解微分方程,需要 考虑收敛速度的快慢(即在一定的时间里能否达到 精度要求)。而有的问题则受内存容量的限制而对 时间要求并不苛刻。对于后一种情况,速度不快但 节省内存的算法则应是首选。

27 2019/9/15

方法二:

CLR A

;1字节,1个机器周期

XCH A,2BH ;2字节,1个机器周期

XCH A,2CH ;2字节,1个机器周期

XCH A,2DH ;2字节,1个机器周期

XCH A,2EH ;2字节,1个机器周期

以上两种方法均可以实现所要求的传送任务。

方法一使用14个字节的指令代码,执行时间为9个机 器周期;方法二仅用了9个字节的代码,执行时间也 减少到了5个机器周期。实际应用中应尽量采用指令

4 2019/9/15

•清晰正确的流程图是编制正确无误的应用程 序的基础和条件。所以,绘制一个好的流程 图,是程序设计的一项重要内容。

汇编语言第4章PPT课件

2. 汇编语言程序设计与执行过程

输入汇编语言源程序(EDIT) 汇编(MASM) 链接(LINK) 调试(TD)

源文件 . ASM 目标文件 .OBJ 可执行文件.EXE 最终程序

4

3. 汇编语言源程序结构

由多个逻辑段组成,包含: 代码段:存放源程序的所有

数据段名 SEGMENT …

数据段名 ENDS

26

一、数据定义伪指令

用途:定义变量类型,给存储器赋初值,或仅给变量分配存储单 元,而不赋予特定的值。

格式: [变量名] DB 操作数;定义字节 [变量名] DW 操作数;定义字 [变量名] DD 操作数;定义双字 [变量名] DQ 操作数;定义8个字节 [变量名] DT 操作数;定义10个字节

操作数——是赋给变量的初始值,可以有一个,也可以有多个, 但不能超出数据类型范围。操作数可以是数值、字 符串、?、或者DUP。

CLC

;CF=0

LPER:MOV AL,DATA2[SI]

ADC DATA1[SI],AL

INC SI

DEC CX

JNZ LPER

MOV AH,4CH

INT 21H

;返回DOS

CODE ENDS

END START

7

二、汇编语言语句类型及格式

1. 汇编语言语句分类

指令性语句

CPU执行的语句, 能够生成目标代码

段 值 变量所在段的段地址 偏移量 变量单元地址与段首地址之

间的位移量。 类 型 字节型、字型和双字型

14

3)表达式

组成:操作数:常量、寄存器名字、存储器操作数 运算符:

算术运算 逻辑运算 关系运算 取值运算和属性运算 其它运算

15

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Net Declarations

s1 0 s2 0 1 X Z

0 X X 0

1

X 1 X 1

X

X X X X

Z

0 1 X Z

s1

wire value

s2

wire net type

14

Wire Values and Timing

Multiplexer built by tri-state buffers

4.1.4 A Simple Testbench

Module Wires

Ports

Interconnections

Wire Values and Timing

A Simple A Simple Testbench Testbench

18

A Simple Testbench

`timescale 1ns/100ps values in this testbench, they are module TriMuxTest; declared as reg and initialized to 0. reg i0=0, i1=0, s=0; wire y; TriMux MUT (i0, i1, s, y); The initial statement is initial begin a procedural construct #15 i1=1’b1; and uses delay control #15 s=1’b1; statements to delay the #15 s=1’b0; program flow in this #15 i0=1’b1; procedural block. #15 i0=1’b0; #15 $finish; The delay before $finish allows the last input change end to have a chance to affect the endmodule

3

4.1

Module Wires

Wires or nets are used for interconnection of substructures together, and interconnection of module ports to appropriate ports of a module’s substructures. By default module ports are wires (net). Wires have delays, can take any of the four values (0, 1, Z and X).

`timescale 1ns/100ps module Anding (input a, b, output y); and (y, a, b); endmodule

Values put into the a and b inputs of Anding are carried through these wires to the inputs of and.

Verilog for a Multiplexer with Tri-state Buffers 16

Wire Values and Timing

Simulation Results of buff1

At time 34 ns, both g1 and g2 conduct. g1 is still conducting because it takes the not gate 5 ns to change the value of sel_ and bufif1 an extra 4 ns to stop g1 from conducting. This causes the value X to appear on y.

A net used for a module port or an internal interconnection can take any of the four Verilog logic values, i.e., 0, 1, Z, and X. Such a value assigned to a net can have a delay, which may be specified by the assignment to the net or as part of its declaration. Multiple simultaneous assignments to a net, or driving a net by multiple sources is legal and the result is defined by the type of the net.

sel

trimux

g0

The symbol of output ports

i0 g1 i1 g2 y

Multiplexer using Tri-state buffers

9

4.1.2 Interconnections

Module Wires

Ports

Interconnections Interconnections

Chapter 4 Combinational Circuit Description

电子科技大学

无线通信与嵌入式系统实验室

通信集成电路与系统工程中心

1

4.1 Module Wires

4.1.1 Ports 4.1.2 Interconnections 4.1.3 Wire values and timing 4.1.4 A simple testbench

A Simple Module

11

4.1.3

Wire Values and Timing

Module Wires

Ports

Interconnections

WireValues Wire Values and Timing and Timing

A Simple Testbench

12

Wire Values and Timing

Wire Values and Timing

A Simple Testbench

10

Interconnections

The and primitive generates its output, which is carried through the y net to the output of Anding.

2

4.5 Behavioral Combinational Descriptions 4.5.1 Simple procedural blocks 4.5.2 Timing control 4.5.3 Intra-assignment delay 4.5.4 Blocking and nonblocking assignments 4.5.5 Procedural if-else 4.5.6 Procedural case statement 4.5.7 Procedural for statement 4.5.8 Procedural while loop 4.5.9 A multilevel description 4.6 Combinational Synthesis 4.6.1 Gate level synthesis 4.6.2 Synthesizing continuous assignments 4.6.3 Behavioral synthesis 4.6.4 Mixed synthesis 4.7 Summary

for the not gate instantiations

not #5 g0 (sel_, sel); bufif1 #4 g1 (y, i0, sel_), g2 (y, i1, sel ); endmodule

Two instances of bufif1 are combined into one gate instantiation construct

Simulation time 45 ns sel becomes 0. At Results of bufif1 Because of the delay Because of this change, after a 4ns of the not gate, this X delay, neither g1 nor g2 conduct, value remains on y for causing a Z (high impedance) to 5 ns. appear on y for a period of 5 ns (inverter17 delay).

4.2 Gate Level Logic

4.2.1 Gate primitives 4.2.2 User defined primitives 4.2.3 Delay formats 4.2.4 Module parameters

4.3 Hierarchical Structures

4.3.1 Simple hierarchies 4.3.2 Vector declarations 4.3.3 Iterative structures 4.3.4 Module path delay

4.4 Describing Expressions with Assign Statements

4.4.1 Bitwise operators 4.4.2 Concatenation operators 4.4.3 Vector operations 4.4.4 Conditional operation 4.4.5 Arithmetic expressions in assignments 4.4.6 Functions in expressions 4.4.7 Bus structures 4.4.8 Net declaration assignment