ARM学习笔记

ARMv8指令学习(1)

如果x0 !=0 , then jumpto label位置处执行

LDUR/LDURB/LDURSB/LDURH/LDURSH/LDURSW/STUR/

STURB / STURH

它们都属于Load-StoreSingle Register(unscaledoffset)

unscaledoffset :指的是”Baseaddr+一个立即数”

w0中的其它字节:用此byte的符号位扩展得到.

(4) ldurh

类似ldurb,不过:这次取halfword(2 bytes)

(5) ldursh

类似ldursb,不过:这次取halfword(2 bytes)

(6) ldursw

类似ldursb,不过:这次取word(4 bytes)

(7) sturx0,[base,#simm9]

把x0保存到[base+#simm9]指向的内存位置

(8) sturb x0,[base,#simm9]

把x0中的一个byte,保存到[base+#simm9]指向的内存位置

(9) sturh x0,[base,#simm9]

把x0中的一个half-word(2 bytes),保存到[base+#simm9]指向的内存位置

(1) ldur x0,[base,#simm9]

x0 = [base+simm9]指向的内容

(2) ldurb w0,[base,#simm9]

从[base+simm9]指向的内容中:取出一个byte,赋给w0.

w0中的其它字节:用0扩展得到.

(3) ldursbw0,[base,#simm9]

ARMCortex-M3学习笔记

ARMCortex-M3学习笔记最近在学ARM Cortex-M3,找了本号称很经典的书“An Definitive Guide to The ARM Cortex-M3”在看。

这个系列学习笔记其实就是在学习这本书的过程中做的读书笔记。

第一章简介这一章的内容主要是介绍Cortex-M3内核是如何的强悍。

还顺带着介绍了ARM系列的发展历史和路线。

ARM公司成立于1990年,ARM公司是Advanced RISC Machines Ltd.的缩写,当然ARM就是Advanced RISC Machines的缩写了,ARM 公司是由Apple,Acorn和VLSI三家共同出资创建的。

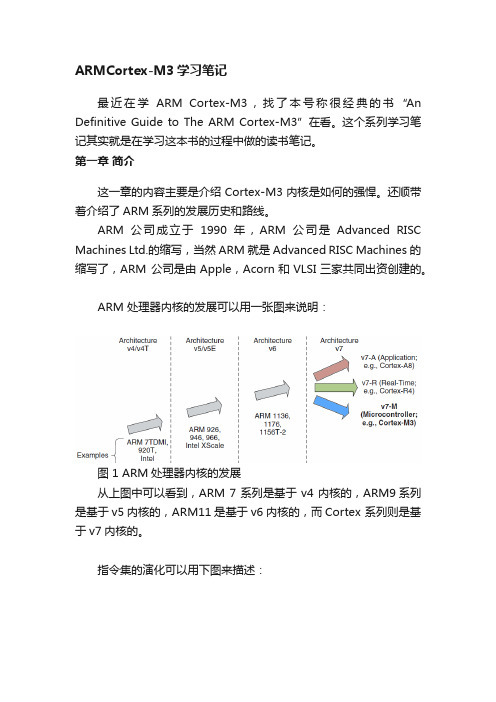

ARM 处理器内核的发展可以用一张图来说明:图 1 ARM处理器内核的发展从上图中可以看到,ARM 7 系列是基于 v4 内核的,ARM9系列是基于v5内核的,ARM11是基于v6内核的,而Cortex 系列则是基于v7内核的。

指令集的演化可以用下图来描述:图 2指令集演进图Cortex-M3 采用Thumb-2指令集,不支持ARM指令集,对Thumb-2指令集其实也只是部分的支持,有很少一部分Thumb-2指令是不支持的。

由于不支持ARM指令集,也就没有了处理器状态在Thumb和ARM之间来回的切换,省去了很多麻烦。

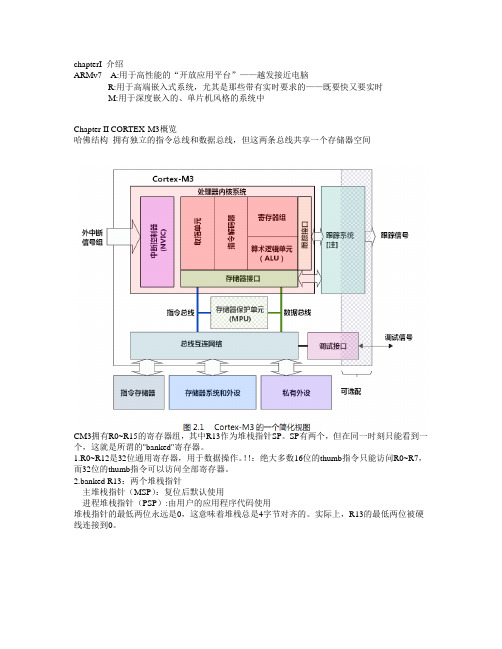

第二章 Cortex-M3 概述Cortex M3 内核的组成可以用一张简图来表示:图 3 Cortex-M3内核简图内核寄存器组包括R0-R15,R0-R12是通用寄存器,部分Thumb 指令只能访问R0-R7。

R13是堆栈指针,实际上有两个,一个是主堆栈指针(MSP)另一个是进程堆栈指针(PSP),堆栈要求4字节对齐。

R14存放程序的返回地址。

R15是PC,记录程序当前的执行地址。

特殊功能寄存器包括:程序状态字寄存器组(PSRs)中断屏蔽寄存器组(PRIMASK, FAULTMASK, BASEPRI)控制寄存器(CONTROL)运行模式和特权级别两种运行模式:handler mode和thread mode。

ARM的异常处理学习笔记转贴

ARM 的异常处理学习笔记转贴ARM的异常处理这部分比较不好理解。

当异常中断发生时,系统执行完当前指令后,将跳转到相应的异常中断处理程序处执行。

当异常中断处理程序执行完成后,程序返回到发生中断指令的下条指令处执行。

在进入异常中断处理程序时,要保存被中断程序的执行现场,从异常中断处理程序退出时,要恢复被中断程序的执行现场。

1、引起异常的原因(1)、指令执行引起的异常软件中断、未定义指令(包括所要求的协处理器不存在是的协处理器指令)、预取址中止(存储器故障)、数据中止。

(2)、外部产生的中断复位、FIQ、IRQ。

2、ARM中异常中断的种类(1)、复位(RESET)a、当处理器复位引脚有效时,系统产生复位异常中断,程序跳转到复位异常中断处理程序处执行,包括系统加电和系统复位。

b、通过设置PC跳转到复位中断向量处执行称为软复位。

(2)、未定义的指令当ARM处理器或者是系统中的协处理器认为当前指令未定义时,产生未定义的指令异常中断,可以通过改异常中断机制仿真浮点向量运算。

(3)、软件中断这是一个由用户定义的中断指令(SWI)。

可用于用户模式下的程序调用特权操作指令。

在实时操作系统中可以通过该机制实现系统功能调用。

(4)、指令与取终止(Prefech Abort)如果处理器预取的指令的地址不存在,或者该地址不允许当前指令访问,当被预取的指令执行时,处理器产生指令预取终止异常中断。

(5)、数据访问终止(DATAABORT)如果数据访问指令的目标地址不存在,或者该地址不允许当前指令访问,处理器产生数据访问终止异常中断。

(6)、外部中断请求(IRQ)当处理器的外部中断请求引脚有效,而且CPSR的寄存器的I控制位被清除时,处理器产生外部中断请求异常中断。

系统中个外设通过该异常中断请求处7)、快速中断请求(FIQ) 理服务。

(当处理器的外部快速中断请求引脚有效,而且CPSR的F控制位被清除时,处理器产生外部中断请求异常中断。

arm实验心得体会

arm实验心得体会在进行arm实验的过程中,我收获了很多知识和经验,也体会到了实验的重要性和意义。

以下是我关于arm实验的心得体会。

首先,在实验中我学习到了关于arm架构的基本知识。

arm架构是一种广泛应用于手机、平板电脑和嵌入式领域的处理器架构。

在实验中,我了解到arm指令集的特点和分类,学会了如何通过汇编语言来编写arm程序。

我能够区分不同的arm寄存器,并熟练运用指令进行数据的读取和存储。

这些知识对于我进一步学习和了解计算机体系结构非常重要。

其次,实验也让我体会到了手动编写程序的乐趣和挑战。

在arm实验中,我需要亲自编写指令并进行调试,这与平时使用高级语言编程的经验完全不同。

手动编写程序需要思考指令的功能和执行顺序,同时需要十分严谨地进行调试和错误修复。

这些挑战锻炼了我的逻辑思维和问题解决能力,同时也为我今后的编程学习打下了良好的基础。

另外,实验还让我深刻认识到了实践的重要性。

光靠理论知识是无法真正掌握一个技能的,必须通过实践来加深理解和应用。

通过亲自编写arm程序,我更加深入地了解了计算机的工作原理和指令执行的过程。

实验也让我意识到了实际操作中可能出现的各种问题和错误,从而提醒我在编程过程中要更加仔细和谨慎。

我在实验中多次因为一小处错误导致程序无法正确执行,这让我更加重视细节和精确性。

此外,实验还提高了我的团队合作能力。

在实验中,我需要与同学们共同研究和解决问题。

通过合作,我们相互帮助、交流意见,并共同进步。

我们互相监督和鼓励,共同完成实验目标。

这锻炼了我的沟通能力和合作能力,也培养了我对团队合作的重视和珍惜。

最后,实验让我对计算机领域的未来充满了信心和热情。

通过亲身参与arm实验,我深刻认识到计算机技术在现代社会中的重要性和广泛应用。

我对于未来计算机技术的发展和创新充满了期待,并希望自己能够为这个领域的进步做出一份贡献。

实验不仅是对知识的检验和巩固,更是对自己兴趣和激情的验证和启发。

总之,通过这次arm实验,我收获了很多知识和经验,也体验到了手动编写程序的乐趣和挑战。

ArmStudy(arm920t个人学习笔记)

Bios->JTAG线->开发板的Nor Flash

开发板的Nor Flash->USB下载线->开发板的Nand Flash

//安装BIOS

H-JTAG(选检测CPU,再检测Nor Flash),无串口,则使用Jlink

SecureCRT.exe串口工具来验证是否已烧写

pathmunge /opt/EmbedSky/4.3.3/bin

//使用source /etc/profile命令使刚刚设置的编译器的环境变量在当前的终端中生效

source /etc/profile

//使用arm-linux-gcc -v命令查看交叉编译器是否安装成功

arm-linux-gcc -v

//打开网络配置文件

gedit /etc/sysconfig/network-scripts/ifcfg-eth0

改后:

HWADDR=00:0C:29:ED:AB:4E

ONBOOT=yes

BOOTPROTO=none

USERCTL=yes

PEERDNS=yes

IPV6INIT=no sou

4.18Note

ps:删除

rm -rf /xxx

(-r为带选择,-rf为不带确认)

chmod -R 777 xxx.txt

(-R后,对子文件也有影响)

1.安装fedora

//打开权限

su root

//进入系统配置文件

gedit /etc/pam.d/gdm

使用#号屏蔽 auth required pam_succeed_if.so user!=root quiet

单片机 arm 学习笔记

Arm学习笔记芯片内BootLoader版本号:2.2RDP除能次数:0RDP使能次数:0芯片PID:00000410 Medium-density芯片FLASH容量为128KB芯片SRAM容量为65535KB(此信息仅供参考,新版本芯片已不包含此信息)96位的芯片唯一序列号:[49FF6B064966505047540887][066BFF49 50506649 87085447]读出的选项字节:A55AFF00FF00FF00FF00FF00FF00FF001.普通IO的的使用首先、通过RCC_APB2PeriphClockCmd()函数是设置外设时钟。

ARM与C51单片机不同的是,不用外设的时候,如IO口、ADC、定时器等等,都是禁止时钟的,以达到节能的目的,只有要用到的外设,才开启它的时钟。

因此在需要用到GPIOB和GPIOD 的时候,我们需要先开启它的时钟,具体用到的是函数库里面的函数:void RCC_APB2PeriphClockCmd(uint32_t RCC_APB2Periph, FunctionalState NewState)其中,第一个参数需要指示要开启什么端口的时钟,RCC_APB2Periph_GPIOx就是开启GPIOx 的时钟,第二个参数需要指示是开启还是关闭,ENABLE/DISABLE。

开启外设时钟之后,然后就开始对GPIO的配置寄存器进行设置了,本文代码为RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOA, ENABLE);然后初始化相关参数,通过命令GPIO_InitTypeDef GPIO_InitStructure; /* Configure the LED0 pin */初始化结构体GPIO_InitStructure.GPIO_Pin = GPIO_Pin_1; //选择管脚,是你想用到的管脚GPIO_InitStructure.GPIO_Mode = GPIO_Mode_Out_PP; //输入输出的8种模式,这要根据外电路和作用选择GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;//选择速度可选2M 10M 50MGPIO_Init(GPIOA, &GPIO_InitStructure);最后,就可以通过io口的相关命令对于io口进行操作。

ARM初学入门

经过一段时间对ARM的学习,在这里跟大家说一些前期的学习经验,另外仅以一个例子说明一下ADS的开发过程,因为这也是初学,可能有的地方说的不太好,望大家谅解,另外可以找其它参考资料来学习。

第一部分:ARM前期学习经验个人认为,要想学好ARM应该首先对ARM的整体框架(包括ARM体系结构,ARM开发过程,及ARM程序框架及执行过程等)有一个了解。

这里这就不多说了,这些东西我也只是刚刚开始学习,还没有很好的掌握,就只说一些个人想法吧。

呵呵,因为时间比较紧张,本来说是一个星期搞定ARM,至少拿着书本可以一点点的做着,可是经过上一个星期,到最后,哇,真的快疯了。

刚开始拿到实验箱,以为和NIOS一样,多跑一些DEMO应该就差不多会玩了,没想到一开始就碰到一个大问题,ARM实验箱里边带了几本教材和实验指导书,拿着实验指导书做了几个DEMO就做不下去了,因为前两个DEMO还比较简单,就只是用汇编语言写了几条对ARM寄存器操作的语句,学过汇编语言的很快就可以理解了。

可是往后就不一样了,因为刚开始学,不太了解ARM程序的框架,实在是看不懂了,为什么每个全程里边都有用到44b.h ,44blib.h ,44blib.c还有一个44binit.s文件?前边三个还容易理解,玩过单片机的很容易就能看出来44b.h 里边定义了一些在S3C44B0X内部的寄存器,44blib.h和44blib.c定义了一些有关初始化的函数,而44binit.s呢?看不懂,到这里我的ARM程序就没法往下做了,只有在网上再找资料,看这个函数到底是干什么用的,原来这就是以前经常听说的“bootloader”或着说是“启动代码”,或着说是“ARM的引导程序”,就是处理器在启动的时候执行的一段代码,主要任务是初始化处理器模式,设置堆栈,初始化变量等等.由于以上的操作均与处理器体系结构和系统配置密切相关,所以一般由汇编来编写(关于这方面的内容大家可以查看相关资料)。

arm cortex m3权威指南读书笔记

chapterI 介绍ARMv7 A:用于高性能的“开放应用平台”——越发接近电脑R:用于高端嵌入式系统,尤其是那些带有实时要求的——既要快又要实时M:用于深度嵌入的、单片机风格的系统中Chapter II CORTEX-M3概览哈佛结构拥有独立的指令总线和数据总线,但这两条总线共享一个存储器空间CM3拥有R0~R15的寄存器组,其中R13作为堆栈指针SP。

SP有两个,但在同一时刻只能看到一个,这就是所谓的"banked"寄存器。

1.R0~R12是32位通用寄存器,用于数据操作。

!!:绝大多数16位的thumb指令只能访问R0~R7,而32位的thumb指令可以访问全部寄存器。

2.banked R13:两个堆栈指针主堆栈指针(MSP):复位后默认使用进程堆栈指针(PSP):由用户的应用程序代码使用堆栈指针的最低两位永远是0,这意味着堆栈总是4字节对齐的。

实际上,R13的最低两位被硬线连接到0。

3.R14:连接寄存器:当调用一个子程序时,由R14存储返回地址4.R15:程序计数寄存器:只向当前程序地址5.特殊功能寄存器:程序状态子寄存器组(PSR)中断屏蔽寄存器组(primask,faultmask,besepri)控制寄存器(control)还支持两级特权操作:特权级和用户级在CM3运行主应用程序时(thread mode),既可以使用用户特权级,也可以使用用户级;但是异常服务例程必须在特权级下执行。

复位后,默认进入thread mode,特权级访问。

在特权级下,程序可以访问所有范围的存储器(如果有MPU,则必须在MPU规定范围之外),并且可以执行所有指令。

一旦进入用户级,想要进入特权级必须:执行一条系统调用指令(SVC),这会出发SVC异常,然后由异常服务例程接管,如果批准进入,则异常服务例程修改control寄存器,才能在用户级的thread mode 下重新进入特权级。

ARM汇编学习笔记

这两天参加了一个编写操作系统的项目,因为要做很多底层的东西,而且这个操作系统是嵌入式的,所以开始学习ARM汇编,发现ARM汇编和一般PC平台上的汇编有很多不同,但主要还是关键字和伪码上的,其编程思想还是相同的。

现将一些学习感悟部分列出来,希望能给有问题的人一点帮助。

1、ARM汇编的格式:在ARM汇编里,有些字符是用来标记行号的,这些字符要求顶格写;有些伪码是需要成对出现的,例如ENTRY和END,就需要对齐出现,也就是说他们要么都顶格,要么都空相等的空,否则编译器将报错。

常量定义需要顶格书写,不然,编译器同样会报错。

2、字符串变量的值是一系列的字符,并且使用双引号作为分界符,如果要在字符串中使用双引号,则必须连续使用两个双引号。

3、在使用LDR时,当格式是LDR r0,=0x022248,则第二个参数表示地址,即0x022248,同样的,当src变量代表一个数组时,需要将r0寄存器指向src 则需要这样赋值:LDR r0,=src 当格式是LDR r0,[r2],则第二个参数表示寄存器,我的理解是[]符号表示取内容,r2本身表示一个寄存器地址,取内容候将其存取r0这个寄存器中。

4、在语句:CMP r0,#numBHS stop书上意思是:如果r0寄存器中的值比num大的话,程序就跳转到stop标记的行。

但是,实际测试的时候,我发现如果r0和num相等也能跳转到stop 标记的行,也就是说只要r0小于num才不会跳转。

下面就两个具体的例子谈谈ARM汇编(这是我昨天好不容易看懂的,呵呵)。

第一个是使用跳转表解决分支转移问题的例程,源代码如下(保存的时候请将文件后缀名改为s):AREA JumpTest,CODE,READONLYCODE32num EQU 4ENTRYstartMOV r0, #4MOV r1, #3MOV r2, #2MOV r3, #0CMP r0, #numBHS stopADR r4, JumpTableCMP r0, #2MOVEQ r3, #0LDREQ pc, [r4,r3,LSL #2]CMP r0, #3MOVEQ r3, #1LDREQ pc, [r4,r3,LSL #2]CMP r0, #4MOVEQ r3, #2LDREQ pc, [r4,r3,LSL #2]CMP r0, #1MOVEQ r3, #3LDREQ pc, [r4,r3,LSL #2]DEFAULTMOVEQ r0, #0SWITCHENDstopMOV r0, #0x18LDR r1, =0x20026SWI 0x123456JumpTableDCD CASE1DCD CASE2DCD CASE3DCD CASE4DCD DEFAULTCASE1ADD r0, r1, r2B SWITCHENDCASE2SUB r0, r1, r2B SWITCHENDCASE3ORR r0, r1, r2B SWITCHENDCASE4AND r0, r1, r2B SWITCHENDEND程序其实很简单,可见我有多愚笨!还是简要介绍一下这段代码吧。

ARM快速入门教程

ARM快速入门教程ARM(Advanced RISC Machines)是一种基于精简指令集计算机(RISC)架构的处理器系列,被广泛应用于嵌入式系统、移动设备和消费类电子产品中。

本文将为您提供一个简单的ARM快速入门教程,帮助您了解ARM的基本概念和使用方法。

第一部分:ARM概述(200字)第二部分:ARM架构(300字)ARM架构采用RISC设计思想,通过简化指令集和优化硬件设计来提高性能和效率。

ARM处理器具有三个基本特征:简洁的指令集、统一的寄存器文件和可变长度的指令长度。

ARM指令集包括数据传输指令(如加载和存储指令)、算术指令(如加法和乘法指令)、控制指令(如分支和跳转指令)等。

这些指令被编码为16位或32位二进制代码,以提高指令执行效率。

ARM处理器的寄存器文件使用统一的32位寄存器,这意味着所有的寄存器都可以用于存储数据或表示内存地址。

该设计简化了指令集编码,并提高了程序的灵活性和扩展性。

与其他处理器架构相比,ARM指令的长度是可变的。

ARM处理器支持16位和32位的指令,根据实际需要进行选择。

这种设计也有利于降低功耗和提高代码密度。

第三部分:ARM开发环境(400字)要开始使用ARM进行开发,您需要一个ARM开发板、一台计算机和适当的开发环境。

ARM开发板是一种嵌入式系统,其中包含一块ARM处理器和各种外围设备(如闪存、RAM、串口等)。

您可以使用开发板来加载和运行您的ARM代码,并与外部设备进行交互。

第四部分:ARM编程(300字)ARM编程可以使用汇编语言或高级语言进行。

汇编语言是一种低级编程语言,直接对应于CPU的指令集。

使用汇编语言编程可以更加深入地了解和控制ARM处理器的操作。

高级语言(如C/C++)编程可以提高开发效率和代码可读性。

您可以使用C/C++编程语言编写ARM应用程序,然后通过交叉编译器将其编译成ARM指令。

在ARM编程中,您可以使用各种库函数和驱动程序来访问外部设备(如闪存、串口、显示屏等)。

arm学习笔记-ARM用到的软件及安装

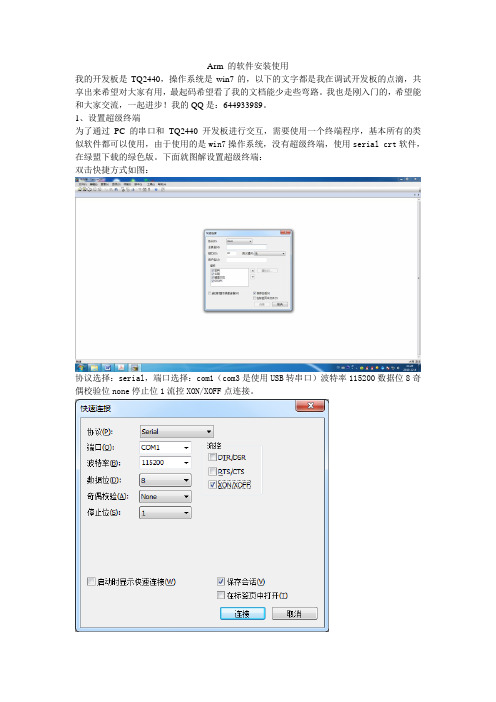

Arm 的软件安装使用我的开发板是TQ2440,操作系统是win7的,以下的文字都是我在调试开发板的点滴,共享出来希望对大家有用,最起码希望看了我的文档能少走些弯路。

我也是刚入门的,希望能和大家交流,一起进步!我的QQ是:644933989。

1、设置超级终端为了通过PC 的串口和TQ2440 开发板进行交互,需要使用一个终端程序,基本所有的类似软件都可以使用,由于使用的是win7操作系统,没有超级终端,使用serial crt软件,在绿盟下载的绿色版。

下面就图解设置超级终端:双击快捷方式如图:协议选择:serial,端口选择:com1(com3是使用USB转串口)波特率115200数据位8奇偶校验位none停止位1流控XON/XOFF点连接。

选项菜单->会话选项选串行将串行中断长度由100改成1300(100特别快,进入不了UBOOT提示!)2、设置DNW 软件在光盘的“Windows 平台工具\DNW”目录下面可以找到DNW 软件,双击即可打开它:Step 1、点击“Configuration”菜单的“Options”选项,出现“UART/USB Options”配置单:设置Download address :0x3020000(下载时候先下载到内存,在由内存拷贝到nand flash 中)。

内存地址从(0x30000000-0x34000000)3、安装GIVEIO 驱动当要使用Jtag 软件SJF2440.exe 烧写u-boot 时,需要安装驱动把并口虚拟成IO 口使用。

下面是图解安装GIVEIO 驱动的步骤:1、找到光盘里面提供的giveio 的驱动,路径是“Windows 平台工具\GIVEIO”,复制giveio.sys 到您的系统盘符的“WINDOWS\system32\drivers”目录下面:2、右键计算机->属性->设备管理3、DVD/CD-ROM驱动器->右键扫描检测硬件改动,IDE ATA/ATAPI 控制器->右键扫描检测硬件改动操作->添加过时硬件下一步安装我手动从列表选择的硬件->下一步在硬件列表中找到“端口(COM 和LPT)”选项,然后点击“下一步”继续:选从磁盘安装->浏览然后定位到刚才的GIVEIO 目录下面,找到“GIVEIO.inf”文件,点击“确定”继续:点型号giveio->下一步出现如下界面,点下一步安装完成后出现如下界面:点完成。

RAM学习笔记

1、Register 14: This register is used as the subroutine link register. This receives a copy of R15 when a Branch and Link (BL) instruction is executed. Rest of the time it may be treated as a general-purpose register. The corresponding banked registers R14_svc, R14_irq, R14_fiq, R14_abt andR14_und are similarly used to hold the return values of R15 when interrupts and exceptions arise, or when Branch and Link instructions are executed within interrupt or exception routines.2、Register 15 :This register holds the Program Counter (PC). In ARM state, bits [1:0] of R15 are zero and bits [31:2] contain the PC. In THUMB state, bit [0] is zero and bits [31:1] contain the PC.3、Register 16 This register is the CPSR (Current Program Status Register). This contains condition code flags and the current mode bits.4、_ISR_STARTADDRESS=0x33FFFF006、#define pISR_EINT4_7 (*(unsigned *)(_ISR_STARTADDRESS+0x30)) 5、__inline void ClearPending(int bit){register i;rSRCPND = bit;rINTPND = bit;i = rINTPND;}Chapter 14Interrupt controllerF-bit and I-bit of Program Status Register (PSR)If the F-bit of PSR is set to 1, the CPU does not accept the Fast Interrupt Request (FIQ) from the interrupt controller.Likewise, If I-bit of the PSR is set to 1, the CPU does not accept the Interrupt Request (IRQ). So, the interrupt controller can receive interrupts by clearing F-bit or I-bit of the PSR to 0 and setting the corresponding bit of INTMSK to 0.ARM寄存器ARM寄存器共有37个寄存器:31个通用寄存器,包括程序寄存器(PC)。

ARM入门学习方法

ARM入门学习方法ARM(Advanced RISC Machines)是一款广泛应用于嵌入式系统的处理器架构。

在现代智能手机、平板电脑和其他嵌入式设备到工控机等各种领域中,ARM处理器都是非常常见的。

对于初学者来说,学习ARM处理器并不是一件容易的事情,因为它涉及到底层计算机体系结构和汇编语言的知识。

以下是一些学习ARM的入门方法,希望能对初学者有所帮助。

1.了解计算机体系结构的基础知识:在学习ARM之前,了解计算机体系结构的基础知识是非常重要的。

了解计算机内部的组成部分,例如中央处理器(CPU)、存储器(内存)和输入输出设备等,对于理解ARM的工作原理和操作方式是必要的。

2.学习汇编语言:学习ARM处理器需要理解其指令集和汇编语言。

汇编语言是一种低级别的语言,用于与计算机硬件进行交互。

学习汇编语言可以帮助你理解ARM指令的功能和操作方式,并且可以更深入地了解ARM处理器的内部工作原理。

3.寻找合适的学习资源:有很多书籍、在线教程和视频教程可以用于学习ARM处理器。

寻找一些适合自己学习风格的资源,并坚持学习。

一些推荐的资源包括《ARM体系结构与编程》、《ARM嵌入式系统开发与应用》等。

5.进行实际项目练习:书本知识只是理论的一部分,实践才是真正掌握ARM的关键。

尝试编写一些简单的ARM汇编程序,并通过模拟器或硬件开发板进行调试和运行。

从简单的程序开始,逐渐挑战更复杂的项目,加深对ARM处理器的理解和掌握。

6.参加社区和论坛讨论:加入ARM相关技术社区和论坛,与其他ARM学习者和专业人士交流和讨论。

这样可以获取更多的学习资源和经验分享,并且可以解决在学习过程中遇到的问题。

7.持续学习和更新:由于技术的发展和更新,ARM处理器的版本和特性也在不断更新。

持续学习和更新自己的知识,关注最新的ARM处理器架构和技术趋势,可以帮助你保持竞争力并适应快速变化的嵌入式行业。

学习ARM处理器需要时间和耐心,但掌握这一技能将为你打开嵌入式系统领域的大门,并为你的职业发展提供更多机会。

ARMv8内存管理架构.学习笔记

ARMv8内存管理架构.学习笔记⽬录第1章分级存储架构. 21.1基础认识 (2)1.1.1从数据通路描述. 21.1.2从数据交换单位描述. 21.1.3 Cache数据⼀致性拓扑结构. 31.2 系统层内存模型 (3)1.2.1内存属性. 31.2.2地址空间. 41.2.3字节编码⽀持. 4第2章虚拟内存系统架构(VMSA) 52.1 VMSAv8-64. 52.1.1地址转换系统. 52.1.2 内存转换粒度. 62.1.3 Address Translation Stage 82.1.4 描述符格式(descriptor format) 92.1.5 描述符内存属性. 112.2 VMSAv8-32. 112.2.1地址转换系统. 112.2.2转换表⽀持. 122.2.3描述符格式. 122.2.4 描述符内存属性. 132.3 TTW(地址转换流程). 142.3.1 VMSAv8-64 142.3.2 VMSAv8-32 16第3章 MMU Fault 193.1故障类型 (19)3.2 Kernel如何处理读取空指针? (19)3.2.1 ARM发⽣了什么?. 193.2.1 Kernel如何处理?. 20第4章 Vmalloc 224.1简介 (22)4.2基本流程 (22)4.3 代码实现分析 (23)第5章 Linux虚拟内存布局. 275.1 User内存布局 (27)5.1.1 Mem mapping内存分配⽅式(64位) 285.2 Kernel内存布局 (29)5.2.1 ARM64内核内存布局. 295.3 各内存域和物理内存映射关系 (31)第1章分级存储架构1.1基础认识通常为了保证计算机的整体性能,内存和CPU之间的通信需保证很⾼的传输速率,然⽽这受限制于内存的⼤⼩和昂贵的硬件实现,传输速率和内存容量⼤⼩的关系遵循“Smaller is faster”原则,使⽤更⼤容量的内存势必会增加传输延迟降低性能。

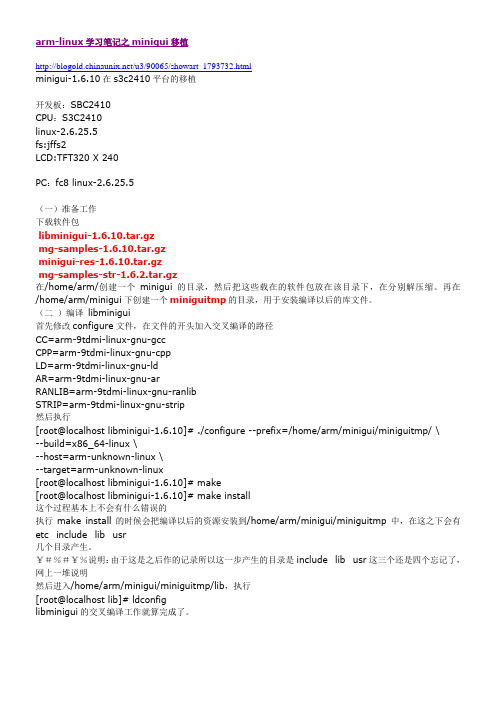

arm-linux学习笔记之minigui移植

arm-linux学习笔记之minigui移植/u3/90065/showart_1793732.htmlminigui-1.6.10在s3c2410平台的移植开发板:SBC2410CPU:S3C2410linux-2.6.25.5fs:jffs2LCD:TFT320 X 240PC:fc8 linux-2.6.25.5(一)准备工作下载软件包libminigui-1.6.10.tar.gzmg-samples-1.6.10.tar.gzminigui-res-1.6.10.tar.gzmg-samples-str-1.6.2.tar.gz在/home/arm/创建一个minigui的目录,然后把这些载在的软件包放在该目录下,在分别解压缩。

再在/home/arm/minigui下创建一个miniguitmp的目录,用于安装编译以后的库文件。

(二)编译libminigui首先修改configure文件,在文件的开头加入交叉编译的路径CC=arm-9tdmi-linux-gnu-gccCPP=arm-9tdmi-linux-gnu-cppLD=arm-9tdmi-linux-gnu-ldAR=arm-9tdmi-linux-gnu-arRANLIB=arm-9tdmi-linux-gnu-ranlibSTRIP=arm-9tdmi-linux-gnu-strip然后执行[root@localhost libminigui-1.6.10]# ./configure --prefix=/home/arm/minigui/miniguitmp/ \--build=x86_64-linux \--host=arm-unknown-linux \--target=arm-unknown-linux[root@localhost libminigui-1.6.10]# make[root@localhost libminigui-1.6.10]# make install这个过程基本上不会有什么错误的执行make install的时候会把编译以后的资源安装到/home/arm/minigui/miniguitmp中,在这之下会有etc include lib usr几个目录产生。

(转)ARM汇编学习笔记——MRS和MSR指令

(转)ARM汇编学习笔记——MRS和MSR指令MRS,状态寄存器传送⾄通⽤寄存器类指令功能:将状态寄存器的内容传送⾄通⽤寄存器。

格式:MRS{<条件码>}Rd,CPSR}SPSR其中:Rd ⽬标寄存器,Rd不允许R15。

R=0 将CPSR中的内容传送⽬的寄存器。

R=1 将SPSR中的内容传送⾄⽬的寄存器。

注释:MRS与MSR配合使⽤,作为更新PSR的读-修改-写序列的⼀部分。

例如:改变处理器或清除标志Q。

注意:当处理器在⽤户模式或系统模式下,⼀定不能试图访问SPSR这条指令不影响条件码标志。

例:MRS R0,CRSR ;将CPSR中的内容传送⾄R0MRS R3,SPSR ;将SPSR中的内容传送⾄R3MSR,通⽤寄存器传送⾄状态寄存器传送指令功能:将通⽤寄存器的内容传送⾄状态寄存器。

格式:MSR{<条件码>CPSR_f|SPSR_f,<#immed_8r>MSR{<条件码>CPSR_<field>|SPSR_<field>,Rm其中:<field>字段可以是以下之⼀或多种:(位从右到左)C:控制域屏蔽字段(PSR中的第0位到第7位);X:扩展域屏蔽字段(PSR中的第8位到第15位);S:状态域屏蔽字段(PSR中的第16位到第32位);F:标志域屏蔽字段(PSR中的第24位到第31位)。

immed_8r 值数字常量的表达式。

常量必须对应8位位图。

该位图在32位字中循环移位偶数数位。

Rm 源寄存器。

注释:同前⼀条指令(MRS)。

例1:设置N、Z、C、V标志。

MSR CPSR_f,#&f0000000 ;仅⾼位有效,其他必须为0例2:仅置位C标志,保留N、Z、V标志。

MRS R0,CPSR ;将CPSR中的内容传送⾄R0ORR R0,R0,#&1f ;置位R0的第29位MSR CPSR_c,R0 ;再将R0中的内容传送⾄CPSR例⼦:设置cpu⼯作在超级保护模式(SVC32)@set the cpu to SVC32 modemrs r0,cpsr@把CPSR内容存⼊r0.使⽤了mrs指令:专⽤寄存器到通过寄存器的存取.@CPSR当前程序状态寄存器格式如下:@ 31 30 29 28 27 26 25 24 ~ ~ ~ 8 7 6 5 4 3 2 1 0@ ___ ___ ___ ___ ___ ___ ___ ___ _ _ _ _ ___ ___ ___ ____ ____ ____ ____ ____@| N | Z | C | V | * | * | * | * | * * * | I | F | T | M4 | M3 | M2 | M1 | M0 |@bic r0,r0,#0x1f@bic指令(bit clear): r0:= r0 and (not op2).上边的指令⽬的是把bit0~bit4清零.orr r0,r0,#0xd3@r0:= r0 or 0xd3 . 以上三条指令执⾏后r0值为:**** **** **** **** **** ***** 11*1 0011msr cpsr,r0@把r0存于cpsr.注意:msr指令是专⽤的通⽤寄存器到特殊功能寄存器的指令与mrs对应说明:通过上边的指令可以看到,实现了两个功能.1,disable 外部中断(IRQ)与快速中断(FIR).2,把系统设为SVC32状态(超级保护)即M4~M1=10011。

ARM9常识知识的笔记

ARM处理器特点:1支持Thumb和ARM双指令集,能很好地兼容8位/16位器件。

Thumb指令集比通常的8位和16位CISC/RISC处理器具有更好代码密度。

2指令采用的3级、5级流水技术。

4支持大端格式和小端格式两种方法存储数据。

5支持字节、半字、和字这3种数据类型。

6 体积小,成本低,性能高ARM工作状态:1、32位ARM状态、2、16位Thumb状态ARM处理器七种运行模式:用户、快中断、中断、管理、(指令预取)中止、系统和未定义(除用户模式外,其余6种模式称为非用户模式,或特权模式;除去用户模式和系统模式外,其余5种模式又称为异常模式)。

R13为堆栈指针SP,R14为链接寄存器LR,R15为程序计数器PC,R16状态寄存器CPSR ARM(嵌入式)系统(从模块结构上看)三大组成部分:硬件、软件、开发平台。

嵌入式系统概念:以应用为中心,以计算机技术为基础,软硬件可裁剪,适应应用系统对功能、可靠性、成本、体积、功耗严格要求的专用计算机系统。

嵌入式开发环境主要组件:●宿主机●目标机●基于JTAG的ICD仿真器、或调试监控软件、或在线仿真器ICE●运行于宿主机的交叉编译器和链接器、以及开发工具链或软件开发环境●嵌入式操作系统常见的嵌入式系统:移动电话、数码照相机、MP4、数字电视的机顶盒、微波炉、汽车内部的喷油控制系统、防抱死制动系统。

4种电源管理模式:1正常模式:正常运行模式2慢速模式:不加PLL的低时钟频率模式3空闲模式:只停止CPU的时钟4掉电模式:切断所有外设和内核的电源RAM=SRAM+DRAM边界对齐方式:字对齐、半字对齐、字节对齐名词解释:ROM:Read Only Memory是只能读出事先所存的数据的固态半导体存储器,其特性是一旦存储资料就无法改变或删除。

ARM:Advanced RISC Machines先进精简指令集。

ARM公司1991年成立于英国剑桥,是专门从事基于RISC技术芯片设计开发公司,主要出售芯片设计技术的授权。

三年级下学期英语学习笔记

三年级下学期英语学习笔记第一课1.clap [klæp](拍)2.hand [hænd](手)3.jump [dʒʌmp] (跳)4.up [ʌp] (向上)5.high [hai] (高高地)6.shake [ʃeik] (摇,摆)7.arm [ɑ:m] (手臂)8.leg [leɡ] (腿)9.bend [bend] (弯曲)10.knee [ni:] (膝盖)11.touch [tʌtʃ] (摸)12.toe [təu] (脚趾)13.nose [nəuz] (鼻子)第二课1.Clap your hands.(拍手。

)2.Jump up high. (高高地跳起来。

)3.Shake your arms. (摆手擘。

)4.Shake your legs. (摆腿。

)5.Touch your toes. (摸你的脚趾。

)6.Bend your knees. (曲膝。

)7.Stand nose to nose. (鼻子对鼻子的站着。

)第三课1.after noon [,ɑ:ftə:'nu:n] (下午)2.evening ['i:vniŋ](晚上)3.night [nait] (夜晚)句子:1.Good afternoon. (下午好。

)2.Good evening. (晚上好。

)3.Good night. (晚安。

)第四课1.pet [pet] (庞物)2.mouse [maus] mice [mais] (老鼠)3.hamster ['hæmstə] (仓鼠)4.fish [fiʃ] (鱼)5.rabbit ['ræbit](兔子)6.bird [bə:d] (鸟)7.frog [frɔɡ] (青蛙)8.budgie ['bʌdʒi] (鹦鹉)9.tiger ['taiɡə] (老虎)第五课1.I have got a pet. (我有一个宠物。

arm学习笔记五(cc++与arm汇编混合编程)

arm学习笔记五(cc++与arm汇编混合编程)混合编程常见⽅式:1 在c/c++程序中嵌⼊汇编指令语法格式:__asm{汇编语⾔程序}2 在汇编程序中访问c/c++定义的全局变量⽰例代码如下:test.c#include <stdio.h>int gVar_1=12;extern asmDouble(void)int main(void){printf("original value of gVar_1 is %d",gVar_1);admDouble();printf("modified value of gVar_1 is %d",gVar_1);return 0;}test.sAREA asmfile,CODE,READONLYEXPORT asmDouble;声明全局引⽤标号IMPORT gVar_1;引⽤asmDoubleldr r0,=gVar_1ldr r1,[r0]mov r2,#2mul r3,r1,r2str r3,[r0]mov pc,lrEND3 在c/c++程序中调⽤汇编函数⽰例代码如下:test1.sAREA asmfile,COCE,READONLYEXPORT asm_strcpy;声明全局引⽤标号asm_strcpy;函数名loop:ldrb r4,[r0],#1cmp r4,#0beq overstrb r4,[r1],#1b loopover:mov pc,lr;⽤于函数返回ENDtest1.c#include <stdio.h>extern void asm_strcpy(const char *src,char *dest);int main(){const char *s ="hello world";char d[32];asm_strcpy(s,d);printf("source:%s",s);printf("destination: %s",d);return 0;}上⾯程序jni的味道有⽊有?4 汇编程序中调⽤c/c++函数⽰例代码如下:test2.cint cFun(int a,int b,int c){return a+b+c;}test2.sEXPORT asmfileAREA asmfile,CODE,READONLY IMPORT cFun;引⽤函数ENTRY;指定应⽤程序⼊⼝mov r0,#11mov r1,#22mov r2,#33BL cFun;返回END。

学习arm的心得体会

学习arm的心得体会篇一:ARM学习心得体会ARM四天学习心得体会1.懂得了如何使用IAR的软件使用,使用前要先进行环境的设置,具体见文档IAR使用说明。

2.第一次是学习点亮LED灯,在点亮LED灯中学习到如果要点亮LED灯必须学会调用已经写好的库函数,对系统进行初始化SystemInit ;对IO口进行初始化GPIOInit ;,还得对GPIO口的设置GPIOSetDir--设置GPIO口为输入为1的IO口,设置完成后就可以对IO口成为输入输出方向,当要点亮LED灯时,要使用到GPIOSetValue();函数,当为确定好某个IO口确定时,后一个为0时可以设置LED灯为点亮了,然后就可以对IO口进行设置了,用法和单片机基本一致,具体可以参考程序《闪灯》。

3.蜂鸣器的鸣响很简单,就是首先对蜂鸣器的IO端口进行设定以驱动蜂鸣器,GPIOSetDir( PORT3, 3, 1 ); 当蜂鸣器需要鸣响时,直接对PORT3_3端口进行赋值0《GPIOSetValue( PORT3, 3, 0 ); 》不让蜂鸣器鸣响则是(GPIOSetValue( PORT3, 3, 01); )就可以了。

4.串口的使用串口开始时要初始化出口,并且通过串口打印前会把数据存在数据缓存区里面,如果我们需要通过输入值来控制ARM板子的功能时,可以读取缓存区(UARTBuffer[UARTCount-1])的内容(缓存区的内的数据都是字符型数据【char】)然后就可以通过输入的值来处理,可以用中断方式,也可以用查询方式,可参考串口中断程序5.中断的使用使用中断时需要初始化中断例如:init_timer32(TEST_TIMER_NUM,TIME_INTERVAL); // 初始化定时器 enable_timer32(TEST_TIMER_NUM); //使能定时器使定时器工作 LPC_SYSCON->SYSAHBCLKCTRL |= (1篇二:学习ARM的心得体会arm四天学习心得体会1.懂得了如何使用iar的软件使用,使用前要先进行环境的设置,具体见文档iar使用说明。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2012-2-9ARM流水线指令集写一些汇编程序.ARM的异样:与中断的区别片内外设,2410ARM9.AT:ARM926E-SAM9645.ARM是一家英国的公司,生产RISC:精简指令集的.(CISC:复杂指令集)对入嵌入式行业来说,主频高不是一切.同样主频下,CISC的执行效率要远远低于RISC,ARM的指令长度是固定的4个字节.而CISC对取来的命令还要进行指令长度的判断(主频不是一切论据1).比较流行的:51,PIC,430,AVR,MIPS,SUN,PPC,ARM的CPU.架构更换:指令集,开发环境.会浪费大量的时间与金钱.ARM后来居上的原因是:指令集完全兼容,但是外设的操作不同,但依然降低了很多公司的前期投入.ARM公司技术研讨会,5月1,10月1,一年两次.ARM约定:Byte: 8bitHALFWORD: 16bit 2ByteWORD: 32bit 4Byte大部分ARMcore提供:ARM指令集 32bitThumb指令集 16bitJazelle cores支持Java bytecode :意味着使用此类CPU之后不再需要JAVA虚拟机,就有更高的效率,(主频不是一切,论据2)7个基本工作模式:划分模式是了资源控制.最主要的资源是寄存器的资源.(牢记) 寄存器是存在与核内:CORE->寄存器->cache->存储器.寄存器的资源很少.而内核访问内存必须通过中间的寄存器 (猜测,若ADD R2,R2,R1指令,如果全写地址没有办法得到32位的指令长度)USER:应用程序90%FIQ:[快速中断]中断是有外设提出的请求,高优先级, (中断的优先级:当低优先级的中断在执行时,高优先级的中断可以打断)而在ARM中则FIQ只能有一个,不允许有一个更高优先级的打断,FIQ里面资源独立,与IRQ不重复,所以进入中断时要置位FIQ禁止.IRQ:[中断]低优先级中断,同上,IRQ也只能有一个,资源独立.Supervison:管理模式,当复位或软件中断指令执行时将会进入这种模式,CPU复位涵盖外设复位与内核复位.复位后CPU内的所有资源全部回到原始状态(管理模式,ARM状态),会引起复位的是:上电复位人为复位欠压/过压复位 CPU的工作电压. 依赖片内外设看门狗复位: 也依赖片内外设,是由看门狗的定时器来产生复位源.软件中断:系统调用是通过软件中断实现的,软件中断是拿SWI实现的,一个系统调用一个SWI,有对应的软件中断号,C库在用户空间,应用程序都在用户模式下工作的,而要陷入内核(LINUX)是切换到管理模式,因为user模式下不能访问到管理模式下的资源,所以要有SWI指令来使得能进入管理模式来做一些必须进入此模式下才能访问的资源,软件中断为用户访问受限资源提供接口.Abort:终止模式,存取异常时进入,是内核存取数据,内核需要的数据有两种,用户数据,指令数据指令数据失败:指令终止模式用户数据失败:用户数据终止模式Undef:未定义指令不等于错误的指令,如2410使用的是V4T的指令集版本,而编写指令是用V5TE的指令集来编写的,或多或少有独有的指令集,在仅支持V4T的内核上跑, System:使用和User模式相同寄存器集的特权模式,虽然共用相同的资源,但能访问在user模式下不能访问的资源异常不能被屏蔽,而中断可以.中断是异常的一种,异常的范围更广,涵盖了中断.异常产生时,必须为ARM状态,由内核自动转换.非特权模式不能由异常(异常包括中断,未定义命令等)进入,特权模式由特定异常产生时进入,1非特权,6特权(5异常,1非异常system)寄存器 R0~R15+CPSR+SPSR,其中R0~R7+R15在物理上与其他模式共享,而R8~R14为SPSR用来保存产生异常前的CPSR(当前程序的状态)SP:堆栈指针LR:链接寄存器,用来保存PC的,为了返回进入异常前状态.Thumb低位寄存器:R0~R7高位寄存器:R8~R14CPSR: USER模式下不具备往CPSR写的权限31:N = 1时,说明ALU结果是一个负数,ALU:算数逻辑单元.30:Z = 1时,说明ALU结果是0.29:C = 1时,说明ALU加法时有进位或减法时有借位,都会置1.28:V = 1时,说明ALU结果溢出时.默认情况下不影响标志位,在命令后加S来让结果影响标志位.27:Q = 1时,表示DSP扩展运算饱和状态 ARM 5TE/J架构支持.24:J = 1时,表示在Jazelle状态. ARM 5TE/J架构支持.7:IRQ = 1时,置1时,屏蔽所有IRQ中断.6:FIQ = 1时,置1时,屏蔽所有FIQ中断.5:T = 1时,ARM处理器的状态,等于0时处理器处于ARM状态,等于1时为Thumb状态,此值不由人为更改.4~0:Mode,表示了处理器处于哪种模式下,编程人员可以读,可以写,USER模式下不具备往CPSR写的权限,只能读,在特权模式下可以通过写此处的值来改变工作模式.程序指针PC:在ARM状态下,所有指令32bits宽,所以指令必须word字对齐,所以PC值由bits[31:2]决定,而bits[1:0]内的值目前无效(因为word对齐,一起跳转1个字长的长度,所以要加4,bits[1:0]里的值无效).0000 0000->0000 0100->0000 1000->0000 1100……在Thumb状态,所有指令16bits宽,所以指令必须halfword半字对齐,所以PC值由[31:1]决定,bits[0]无效在Jazelle状态,所有指令8bits宽.处理器会按字一次去4跳指令异常的处理(第三天的一个重点):以下均在ARM状态下.ARM core实现:内核自动实现,不用自己编写.并发执行,一个周期内完成.拷贝cpsr到spsr_mode设置适当的cpsr位:改变处理器状态进入ARM模式,异常模式内只能在此模式下工作,因为Thumb 没有返回原状态的指令(操作spsr)改变处理器模式进入相应的异常模式设置中断禁止位进制相应中断保存返回地址到LR_mode设置PC为相应的异常向量, 异常向量表是一个公共的入口,(有一部分高端映射没听明白,只有ARM9以上支持,以及ARM720T支持)(一般写的裸机系统从0x0开始放,而有了linux启动过之后用高端映射,到了0xffff0000开始放.)返回时:人为编写操作.也是一个周期内完成,并发执行从SPSP_mode恢复cpsr.从LR_mode恢复PC.字节序:小端:低地址存低位数据.大端:低地址存高位数据.在2006年之后使用了新的命名方法contexA:app,应用处理器.A5,A9都是双核.R:real-time实时.硬盘,M:MCU微控制单元.轻量级CPU.M0,M3,M4,核能跑50MH,而51只能1MH(F ost = 24M/12).高性能方向:TI(德州仪器)DSP出名:非对称式双核(ARM+DSP双核,DSP由ARM分配任务),SMP(对称式双核)Samsung:Freescale:moto原来的半导体部门.Marvell:Qualcomm高通:Nvidia:低功耗低成本的微控制器:M3:STM32系列意法半导体.第一个获得M3授权的公司.实时:R4所有ARM指令均为32bits,大部分为单周期指令,所有指令都可以条件执行,采用Load/Store架构(Load:数据从存储器到寄存器,store:数据从寄存器到存储器).EEPROM与FLASHROM具有通用ROM的特点,掉电不丢失数据,但是还具有可写功能.DMA直接内存访问,不用经过内核,源与目的的数据交流.但是需要DMA设备.B:PC+_32Mbyte,一跳转就不关心返回.BL:保存返回地址到LR,返回地址为当前执行指令的下一条指令的地址.对于非叶子结点的函数,LR必须压栈保存,否则只能返回一次跳转前的状态,而不能多次返回.协处理器:多达16个可定义协处理器,2410上有cp15,是有16个32位的寄存器,常用协处理器来作为ARM cache控制器,高端映射等.协处理器不在核内,属于片内外设.Thumb是16bits指令集:优化代码密度.提高窄内存操作性能.是ARM指令集的一个功能子集.缺点:条件执行不可用.源和目的寄存器相同只有地段寄存器可用常量大小受限制.内嵌的桶形移位不可用.Jazelle:是的ARM cores执行8bits的Java字节码95%的字节码执行使用硬件门电路(说明效率非常高).更高的性能增加的门电路<12KSOC概念,片上系统,是信息系统核心的芯片集成.是一个微小型的系统.BUS:总线,考点:AMBA先进的微处理器架构总线,衍生出了两个分支,AHB(类似北桥)总线,先进的高性能总线,APB(类似南桥)先进的外设总线.绝大部分是按照他们的速度来划分的,由PPT的图知道,APB类似一个AHP的外设.计算机中:北桥:离CPU较近,挂着CPU,内存南桥:键盘鼠标等,对速度要求不高.ARM处理器的内核:尾缀:T:表示支持16为的Thumb指令集.D:支持片上调试测试.M:支持长乘法(两个数相乘结果是64个位).I:支持片上仿真器ICE.J:支持Java字节码.E:支持扩展的DSP指令集.F:支持硬件的浮点指令集(核内有浮点运算器一堆门电路).S:包括以上所有.指令的流水线:PC指向正被取址的指令.预取:PC-8译码:PC-4执行:PC最佳流水线:有一个量化的标准CPI,执行指令的周期数,除以周期内指令了多少条指令,CPI = 1,为最佳.LDR:CPI = 1.5分支流水线:CPI = 1.5中断跳转返回,要把LR的值减4之后再返还给PC,这才是正确的地址.必须自己写代码实现.(因为并不像BL那样会帮你保存好当前PC-4到LR中,因为中断是随机产生的,所以在中断结束后要自动进行这一操作[其实内核做了调整,但是根据流水线的工作,调整后依然少了一条指令,所以要手动-4])存储器访问必须时钟适当的保持地址对齐,ARM7TDMIARM710T有8K的统一的cache,不具体区分指令cache和数据cache,也就是冯诺依曼结构(不分开)与哈佛结构说的是在cache里面是否分开,而不是内存中,哈佛结构分开了两个cache,增加了可用的存储宽度(指令存储器接口,数据存储器接口),并且可以实现指令与数据的同时访问(主频不是一切论据3),ARM92410是哈佛,x86是冯氏.ARM97TDMI采用哈佛结构,采用5级流水线,基本固定CPI在1.5.一般编译器会自动重排,提高效率.(比如两行不相关的代码,重新调整顺序后在流水线工作时就不会有资源锁死,减少时间的消耗,提高效率)LDMIA R13!,{R0-R3} :R13的内容给R0,R13偏移,取内容给R1……3种互锁:时间,空间,时间空间双重.支持V5TE改进ARM/Thumb交互工作新的32*16和16*16乘法指令(优化)新的前导零计数:clz,从符号位后第一位开始数,直到碰到第一个不为0,或末尾则结束,得到有多少个0.新的饱和算术指数:Q位置一,核执行差别单周期32*16乘法器EmbeddedICE逻辑RT,仿真电路的实时性提高.ARM10E系列:采用V5TE64bit存储器接口是核到cache的,CPI≈1.36级流水线为了防止流水线长,碰到了if,else不能正确预读:动态分支预测:(A8与ARM11才有)有动态分支目录.静态分支预测:没有动态分录,只有往前跳或者往后跳.Hit under miss:与cache的刷新算法有关(没注意听)每周期64位的LDM/STM操作EmbeddedICE逻辑RTII,提高仿真电路对中断的优先级有提高.双核与多发射:双核是每个核都有一条流水线,多发射是每个核有两条或多条并行的执行单元,流水线.(X86双核4线程现在是24级流水线).ARM11使用V6体系:提高了多媒体性能,扩展包括了许多新的SIMD指令(单指令流,多数据流),2倍MPEG4编码/解码,更快的音频DSP提高实时性能,更快的异常/中断处理,支持向量中断控制器(不管哪一种异常产生,均会找到对应的响应[异常函数入口地址])ARM公司提供了3种方法1.紧耦合向量中断控制器(很快),2.向量中断控制器(稍慢),3.非向量中断(最慢且视编程水平而定)[外设提出中断到CPU找到对应中断函数入口地址的时间称为中断延迟],所以V6减少了中断响应时间,新的栈和模式转变指令,减少进入和退出异常处理的开销.改进了与非ARM处理器数据共享,增强非ARM处理器的应用程序的移植性,支持混合endian系统(大小端混合使用),2012-2-10伪指令就类似C语言中#define,也不具体生成代码.AREA:定义一个段,代码段code,数据段data,自己定义的段,段名可以自己起,但是不要和原有关键字重名,code段一般readonly,data是可读写.code32/code16:指令类型32位arm,16位thumb.ENTRY:程序的入口,当有多个若干个.s文件时,要有ENTRY来告诉程序从哪开始执行,ENTRY 唯一EXPORT/INPORT:EXPORT声明一个符号可以被其他文件引用,IMPORT在当前文件引用一个其他文件声明的符号.IMPORT类似C语言中的externEQU:常量定义,相当于#definelabel:所有顶格写的为标号,标号就是地址,C语言的函数名.顶格也就是第1列.也就是说除了标号以外,都不能顶格写,并且在汇编里只有行注释,没有/**/,使用”;”进行注释. DCD:连续分配一个字内存单元DCB:分配一个字节的内存单元END:源程序借位xxx.hex→包含地址信息,xxx.bin→没有地址信息,只有指令.功能一样,但hex的文件远大于bin文件.area text, code, readonly //定义一个段,段名为text,是代码段,属性为只读entry //此处为程序入口code32 //指令类型为32位start: //label,函数名……end //源程序结尾STN:俗称的伪彩,在太阳下没办法看到,因为成像原理是电压的击穿使得液晶反转.TFT:真彩液晶.新建工程,选好芯片,target设置好板上flashram,因为片上没有,选片外.output,勾选Create HEX File,若需要生成bin文件,在user选项卡中,Run User Program After Build/Rebulid里,勾选Run #1,并填写如下命令:fromelf.exe –bin –o "L@L.bin" "#L" linker,如果是纯汇编,去掉Use Memory Layout from Target Dialog,并删掉Scatter File 里的文件名.Debug,里可选仿真器.Utilities,keil不支持H-JATGS,只支持ULINK,我们用的是SST39X160XFLASH,增加数据或指令进入内核只有通过前端总线或者寄存器.条件执行:当前这条指令要不要执行,或者如何去执行,取决于上一条执行的影响标志位的结果.ARM指令可以通过添加只当的条件码前缀来达到条件执行的目的,可以提高代码密度,减少分支跳转指令数据,提高性能,默认情况下,数据处理指令不影响条件码标志位但可以选择通过添加S来影响标志位.lsl:逻辑左移MOV R2,R1,LSL #2 →0XE1A021011.什么操作,操作码 24~21→1101 MOV操作2.目的寄存器 15~12→0010 R23.源操作数什么样,寄存器移位数或寄存器数或立即数 25 = 0→是一个寄存器移位数4.源操作寄存器 3~0→0001 第二操作数寄存器R15.移位数多少位 11~7→00010 移2位6.移位类型 6~5→00 逻辑左移7.是不是影响标志位 20→0 不影响标志位8.是什么条件执行 31~28→E1 = AL 无条件执行指令的类型不同格式也不同,不能用同一个格式来分析所有命令ATPCS标准,第一个传参用R0,第二个传参用R1,第三个传参用R2,第四个传参用R3,第5个开始用栈传递. func(a,b,c,d,e…)位清楚 BIC R0,R0,#9 假设R0原来有 1111 1111, #9 = 0000 1001,记住谁为1干掉谁,结果为1111 0110比较指令 CMP R1,#10 CPSR = R1 – 10反值比较+桶形移位器:寄存器,可选择是否增加移位操作逻辑左右移位,无符号数算数右移,保留符号为,高位值填充符号位立即数:以#号开头的是立即数,判断合法立即数的方法:1.若占用连续的1个字节,是则必须为合法.(连续占用是确实的1个字节,而不是2个字节的结合)2.若占用连续的3个半个字节,即1.5个字节,则按二进制位展开,从第一个有效位1开始数,到最后一个有效位1,之间有小于等于8个有效位,并且由于这3个半字节的最低两个位为00,则是合法立即数.i.0x1F8 == 0001 1111 10 00合法ii.0x1FE == 0001 1111 11 10不合法iii.0x7F8 == 0111 1111 10 00 其实依然是不合法的,因为存在有移位只能为偶数的问题(因为老师说过移动位数除以2放到一个存储空间中,然后拿出来乘与2后再开始移位,所以实际上这里就不能把最后的10当作两位来用,因为前边的0111已经占用了半个字节,而不是如0001可以认为占了1/4个字节)iv.因为有MVN命令,所以取反有效,依然合法 0xfffffe07装载32bit常数LDR R0,=0X55555555 此时的LDR是伪指令,类是操作是在某个地方(其实是执行LDR 时,PC应在的地址,即执行地址-8,若LDR之后还有代码,会再自动向后寻址,但是最多只能离LDR这条指令4095个指令,这是LDR的缺陷)存入0x5555 5555,执行LDR时是把这个值拿出来.LDR在装载合法立即数时,会自动变为MOV指令.乘法:32位乘法:MUL{COND}{S} R0,R1,R2 R0=R1*R2MLA{COND}{S} R0,R1,R2,R3 R0=R1*R2+R364位乘法:[U|S]MULL{COND}{S} R0,R1,R2,R3 R0=R2*R3(低32位) R1=R2*R3(高32位)[U|S]MLAL{COND}{S} R0,R1,R2,R3 R0=R2*R3+R0(低32位) R1=R2*R3+R1(高32位) ARM9TDMI比7TDMI多1个周期LDRB LDRHSTRB STRHLDRSB LDRSH带符号位的装载不支持字节与半字存储指令.ARM总共有多少种寻址方式1.立即数寻址:MOV R0,#1 最快的2.寄存器寻址:MOV R0,R13.寄存器移位寻址:MOV R1,R2,LSL #24.寄存器间接寻址:a)LDR R0,[R1] 存储器到寄存器,将R1的内容作为指向存储器的地址,去读地址里的内容保存到R0.b)STR R0,[R1] 寄存器到存储器,………,存储R0内容到R15.基址变址寻址:a)前索引:LDR R0,[R1,#4] R1为基址寄存器,R1的值+4作为地址,将此地址内的值取出放到R0中. STR R0,[R1,#4]b)自动索引:LDR R0,[R1,#4]! R1为基址寄存器,R1的值+4作为新地址,并回写到R1中,将此地址内的值取出放到R0中. STR R0,[R1,#4]!c)后索引:LDR R0,[R1],#4 R1为基址寄存器,将R1的值作为地址,将此地址内的值取出放到R0中,然后将地址值+4回写到R1中STR R0,[R1],#46.多寄存器寻址:什么尾缀存储,完全相反的尾缀取出a)LDM R13!,{R0-R3}b)SRM R13!,{R0-R3}c)I:Inc增加D:Dec减A:After后B:Before先i.IA: 加,后索引,先存,后加,由R0开始ii.IB: 加,先索引,先加,后存,由R0开始iii.DA: 减,后索引,先存,后减,由R3开始iv.DB: 减,先索引,先减,后存,有R3开始7.相对寻址:相对PC,转跳范围+-32MBa) Bb)BL8.堆栈寻址:a)LDMFD:与ATPCS标准有关系, 满full空empty增add减dec,满也就是需要先索引类似B,空则说明后可以后索引,对于堆栈的操作来说,什么尾缀入栈,什么尾缀出栈i.fd:ii.fa:iii.ed:iv.ea:SWP 在寄存器和存储器之间,由一次存储器读和一次存储器写组成的原子操作(一个周期完成两个操作),完成一个字节或字的交换.此指令不能有C语言强制产生,必须使用内列内嵌或C调汇编来实现.用作信号量操作SWP R0,R1,[R2] R2内地址的内容存储R0,R1内容同时存入R2内的地址内C→系统调用→软件中断→SWI(四大步三小步)→PC指向0x08,由SWI内在我们调用它时传入的值来辨别做什么操作.LINUX内核一直运行在ARM的SVC管理模式下PSR指令:CPSR/SPSR的专用访问命令MRS{cond} Rd,<psr> 读*psr的内容到Rd中MSR{cond} <psr[_fields]>,Rm 写Rm内容到*psr中.<psr> = CPSR or SPSR[_fields] 可以为fxcv的任意组合.MSR CPSR_c, R0协处理器指令有3种1.协处理器数据处理指令(少用)2.协处理器寄存器传送指令(有16个寄存器)管理cache,页表,MMUa)MRC:从协处理器寄存器移到ARM寄存器b)MCR:从ARM寄存器移到协处理器寄存器3.写处理器存储器传送指令a)LDC:从存储器装载数据到协处理器寄存器b)STC:从协处理器寄存器存储到存储器Thumb指令集:没有条件执行源,目的寄存器必须相同仅能使用低寄存器常数大小有限制不能使用桶形移位寄存器通过BX指令在ARM与Thumb状态切换,标号位后要加1才能正确跳转到Thumb,而从Thumb跳转到ARM下要把标号位最后一位置0,使用ADR(小范围跳转指令)指令来实现V5TE体系扮酷哦全部的V4T ARM和Thumb指令集更好支持interworking 同时支持ARM/THUMB状态breakpoint指令CLZ指令,前导零计数扩展协处理器指令支持饱和处理Q位封装的带符号的板子乘法指令双字装载/存储指令ARM9TDMI v4T的StrongARM v4的XScale Microachitecture v5TE重点:立即数合法判断,指令的使用,3种基于基址变址的寻址方式,SWP指令的特点,SWI指令2012-2-13异常处理:任何一款CPU都有异常向量表,要记住基本分布,0x00→Reset,0x04→Undefined Instruction,0x08→Software Interrupt,0x0c→Prefetch Abort,0x10→Data Abort,0x14→(Reserved),0x18→IRQ,0x1c→FIQ在ARM7里只有AMR720T可以放到高端地址,ARM9/10均可以PC作为目的寄存器,指令带有S影响的不是标志位,而是回复SPSR到CPSR,同时也依然会更新PC从SWI和Undef异常返回:MOVS PC,LR从FIQ,IRQ和预取异常(Prefect Abort)返回:SUBS PC,LR,#4 [见之前笔记]从数据异常(Data Abort)返回:SUBS PC,LR,#8 [数据在E(执行)时,产生异常,会重新预读此指令,所以需要从原预读地址-8来重新预读此指令] 如果LR之前被压栈的话使用LDM"^":LDMFD SP!,{PC}^中断优先级:数越小中断优先级越高,ISR是中断处理历程的缩写.若有更高中断优先级的请求,会打断之前的中断ISR.若有而比原优先级低的话会等待高优先级的中断完成后再执行.异常优先级:异常在当前(E单元)指令执行完成后才被响应多个异常可以在同一时间产生异常指定了优先级和固定的服务顺序:这个优先级是同时产生是先去服务谁,而不是像中断优先级那样.也就是说在Data Abort异常ISR的过程中,异常可以产生SWI异常来访问一些特定的资源.ResetData AbortFIQIRQPrefetch AbortSWIUndefined instruction异常向量表的跳转指令1.B,优点是灵活,缺点是反问只能+-32MB2.MOV PC,#XXX,缺点是必须要合法立即数3.LDR PC,=32位常数,伪指令,缺点若之后有4095个指令,则不能使用异常进入时必须ARM,退出必须ARM,但是ISR可以是Thumb.异常处理中:与异常发生相关的模式改变移位着所调用的面试题:FIQ的什么特点使它可以快速响应,或者是比IRQ相应更快?1.因为在异常向量表中,FIQ在0x1C,由于FIR位于异常向量表的最末端,所以可以不用像别的那样只有4个字节保存跳转地址,而是可以直接接着写FIQ的ISR代码.2.因为他有5个私有的通用寄存器,不需要特别的保护来恢复这些寄存器. 中断处理:ARM有两级的外部中断FIQ,IRQ.(外部:片只留有两根线nIRQ,nFIQ用于外中断,)SFR:特殊功能寄存器,管理外设.处于4G之内(地址),不属于内核的东西,而是属于外设.大多数的基于ARM的系统有大于2个的中断源因此需要一个中断控制器(地址映射)来控制中断是怎样传递给ARM内核的.在许多系统中,一些中断的优先级比其他中断的优先级高,他们要抢先任何正在处理的的优先级中断.C语言中使用__irq来修饰一个函数,即作为中断程序.纯ubuntu下不支持,只用于keil的IDE环境下.要确保IRQ的堆栈指针已经被设置好在ARER最后有ALIGN=3表示这段空间是字对齐的.SPACE申请连续的字节空间__main是一套宏.宏是没有办法仿真进去的.__main的结束就自动跳转到C的main函数里面中断处理函数具有哪些特点:1.所有的中断的处理函数都不能显式调用2.中断处理函数不能传参(外设中断)3.不能返回值int *s = int * 0x80000000if(*s == 1) int_handler1();………查看属于哪个外设的中断并调用对应的处理函数中断重新使能:中断是可以嵌套的,保存IRQ状态下的LR,SPSR,也就是在使用BL之前改变模式来避免LR_irg被冲掉.通常使用system模式压栈指令必须通过通用寄存器来周转,不能直接使用状态寄存器,__irq不能写可重入中断,要自己写一些处理软中断:用户主动调用才会产生的,是内核已知的一种分支.注意,在汇编中如果SWI调用时处于SVC模式将会冲掉LR_svc.例如在SWI处理程序中的二级调用,解决方法,在SWI调用之前对LR_svc压栈保护.C中使用__swi来定义一个软中断函数.也是在MDK中才能使用的C中__swi允许最多4个参数,使用R0~R3来传递,因为SWI调用将切换到SVC模式,是自己模式的SP,而不是用户模式下的SP,并不通用存取SWI号:用于区分是OPEN,READ,WRITE等操作提取SWI指令中的常数域,要区分ARM/Thumb模式,因为指令长度不同,所以常数域不同,所以由PC-4,-2计算不同.复位处理:执行的动作取决于不同的系统,设置异常向量与调用主应用程序是必须的.ARM优化编译:在设置里面.volatile的作用:1.告诉编译器不要第变量进行优化,是对物理地址的读写,不是对cache里边copy的值,因为存储器里的内容不止内核可以改变,外设也有可能影响着里边的内容,如SFR就是这样映射在存储器中.内嵌函数inline:当调用时间大于运行时间,则推荐使用inline函数.C和C++以及汇编语言的混合编程(重点):可实现在c中无法实现的处理器功能,如swp指令.使用新的或不支持的指令产生更高效的代码ATPCS标准SL=R10SB=R9R12用于存放子程序的返回地址.BX == MOVS PC,LR汇编语言的标号就是C语言里面的函数名c与汇编混合,入口肯定在main函数,在拷贝的文件里可以看到内联汇编不能用物理寄存器void strcpy(des,src){char temp = 0;__asm{loop:ldrb temp,[R0],#1…}}标号不需顶格写,但是要加:号内嵌汇编可以使用物理寄存器,要用__asm来修饰,参考今天的代码PPT上移位的原因是为了把符号位放到对应的位置上.__package字节的对齐对齐访问:sizeof时为什么看到有些自己添加空间,为了快速访问,对齐的最好要小心指针的非对齐.参数传递时,被推荐的最大为4个,R0~R3,为了时间与空间的考虑调库是时间与空间的双重浪费内联,内嵌,C与汇编互调是今天下午的重点2012-2-14电源部分,接入12V的电源,降压到5V的电压,有电感与电容,因为有开关电源,所以用来去波纹,串模干扰.第三个串口在左下角的红外收发上.内部串口是UART口,它逻辑的0和1是TTL/CMOS电平,1≈VDD,接近硅片的供电电压(我们板子是3.3V左右),0≈VSS,接近于电源地.所以PC机要想通过串口进行通信,电平也必须匹配,PC机使用的是232电平,是一种负逻辑的关系,逻辑1 = -3v~-15v(旧主板是-25v),逻辑0 = +3v~+15v(旧主板+25v),此为负逻辑或称为232电平.所以板子上有MAX3232,起电平转换的作用,将传入的232电平与TTL/CMOS电平进行相互转换.MAX3232的工作电压比较大25V 也能复合,MAX232工作电压在5V左右.AT24C02是个EEPROM(电可编程可擦除存储器,有2Kbyte,IIC),XS8900A是一个网卡芯片,有20M的晶振给它时钟源注意液晶屏接口,不要接错了,LCD附近的芯片是为了隔离,不让LCD的电压影响到CPUUSB的A口和B口最近的两个是复用的,只能用一个,所以其实只有两个USB口.UDA1341是做音频输入输出的CPU.矩阵式键盘,异常和中断体系结构.很重要.64M的SDRAM,NOR FLASH有2M,NAND FLASH有64M.1117-S33:电源行骗,输入电压3.3v,是给网卡,SDRAM,FLASH,CPU内部的外设供电的1117-S18:1.8v是给内核供电.32.768khz是给CPU内部的RTC提供时钟源的.主晶振是12M,通过CPU内部的PLL提升到200M核心板的跳线帽,烧写NOR要拔出来,应用工程师:不是很了解内核的工作,多年开发以后对外设使用好了,就更好理解内核.外设:1.看数据手册,中英文两册2.看原理图3.看demo程序。