4046锁相环

锁 相 环 CD4046 应 用 介 绍

锁相环 CD4046 应用介绍锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。

它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

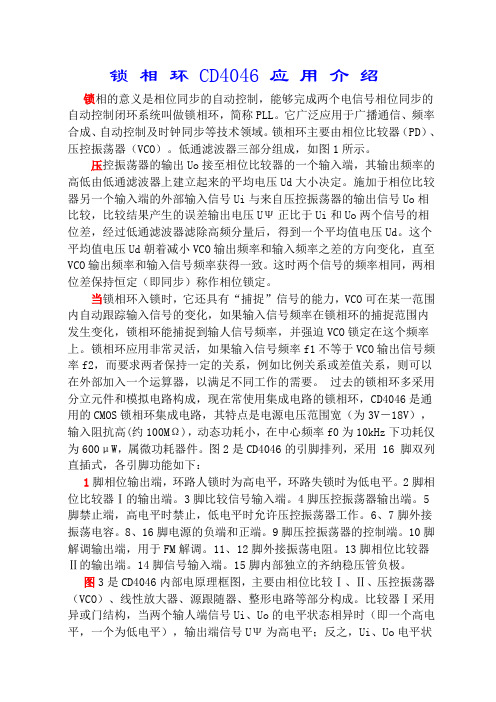

锁相环主要由相位比较器(PD)、压控振荡器(VCO)。

低通滤波器三部分组成,如图1所示。

压控振荡器的输出Uo接至相位比较器的一个输入端,其输出频率的高低由低通滤波器上建立起来的平均电压Ud大小决定。

施加于相位比较器另一个输入端的外部输入信号Ui与来自压控振荡器的输出信号Uo相比较,比较结果产生的误差输出电压UΨ正比于Ui和Uo两个信号的相位差,经过低通滤波器滤除高频分量后,得到一个平均值电压Ud。

这个平均值电压Ud朝着减小VCO输出频率和输入频率之差的方向变化,直至VCO输出频率和输入信号频率获得一致。

这时两个信号的频率相同,两相位差保持恒定(即同步)称作相位锁定。

当锁相环入锁时,它还具有“捕捉”信号的能力,VCO可在某一范围内自动跟踪输入信号的变化,如果输入信号频率在锁相环的捕捉范围内发生变化,锁相环能捕捉到输人信号频率,并强迫VCO锁定在这个频率上。

锁相环应用非常灵活,如果输入信号频率f1不等于VCO输出信号频率f2,而要求两者保持一定的关系,例如比例关系或差值关系,则可以在外部加入一个运算器,以满足不同工作的需要。

过去的锁相环多采用分立元件和模拟电路构成,现在常使用集成电路的锁相环,CD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。

图2是CD4046的引脚排列,采用 16 脚双列直插式,各引脚功能如下:1脚相位输出端,环路人锁时为高电平,环路失锁时为低电平。

2脚相位比较器Ⅰ的输出端。

3脚比较信号输入端。

4脚压控振荡器输出端。

5脚禁止端,高电平时禁止,低电平时允许压控振荡器工作。

MC4046应用

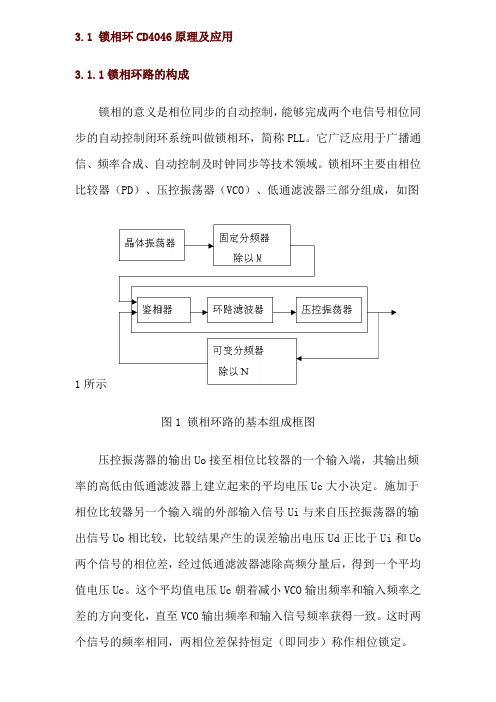

3.1 锁相环CD4046原理及应用3.1.1锁相环路的构成锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。

它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

锁相环主要由相位比较器(PD)、压控振荡器(VCO)、低通滤波器三部分组成,如图1所示图1 锁相环路的基本组成框图压控振荡器的输出Uo接至相位比较器的一个输入端,其输出频率的高低由低通滤波器上建立起来的平均电压Uc大小决定。

施加于相位比较器另一个输入端的外部输入信号Ui与来自压控振荡器的输出信号Uo相比较,比较结果产生的误差输出电压Ud正比于Ui和Uo 两个信号的相位差,经过低通滤波器滤除高频分量后,得到一个平均值电压Uc。

这个平均值电压Uc朝着减小VCO输出频率和输入频率之差的方向变化,直至VCO输出频率和输入信号频率获得一致。

这时两个信号的频率相同,两相位差保持恒定(即同步)称作相位锁定。

当锁相环入锁时,它还具有“捕捉”信号的能力,VCO可在某一范围内自动跟踪输入信号的变化,如果输入信号频率在锁相环的捕捉范围内发生变化,锁相环能捕捉到输人信号频率,并强迫VCO锁定在这个频率上。

锁相环应用非常灵活,如果输入信号频率f1不等于VCO 输出信号频率f2,而要求两者保持一定的关系,例如比例关系或差值关系,则可以在外部加入一个运算器,以满足不同工作的需要。

过去的锁相环多采用分立元件和模拟电路构成,现在常使用集成电路的锁相环,CD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。

3.1.2CD4046的引脚排列,采用 16 脚双列直插式,各引脚功能如下:图1脚相位输出端,环路人锁时为高电平,环路失锁时为低电平。

2脚相位比较器Ⅰ的输出端。

3脚比较信号输入端。

锁相环4046

cD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V -18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz 下功耗仅为600μW,属微功耗器件。

编辑本段功能CD4046的引脚排列,采用16脚双列直插式,各管脚功能:1脚相位输出端,环路入锁时为高电平,环路失锁时为低电平。

2脚相位比较器Ⅰ的输出端。

3脚比较信号输入端。

4脚压控振荡器输出端。

5脚禁止端,高电平时禁止,低电平时允许压控振荡器工作。

6、7脚外接振荡电容。

8、16脚电源的负端和正端。

9脚压控振荡器的控制端。

10脚解调输出端,用于FM解调。

11、12脚外接振荡电阻。

13脚相位比较器Ⅱ的输出端。

14脚信号输入端。

15脚内部独立的齐纳稳压管负极。

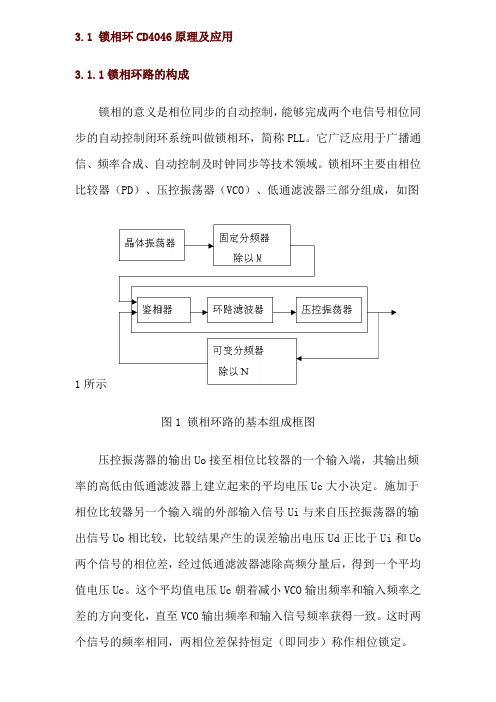

编辑本段图形简介图3图3是CD4046内部电原理框图,主要由相位比较Ⅰ、Ⅱ、压控振荡器(VCO)、线性放大器、源跟随器、整形电路等部分构成。

比较器Ⅰ采用异或门结构,当两个输人端信号Ui、Uo的电平状态相异时(即一个高电平,一个为低电平),输出端信号UΨ为高电平;反之,Ui、Uo电平状态相同时(即两个均为高,或均为低电平),UΨ输出为低电平。

当Ui、Uo的相位差Δφ在0°-180°范围内变化时,UΨ的脉冲宽度m亦随之改变,即占空比亦在改变。

从比较器Ⅰ的输入和输出信号的波形(如图4所示)可知,其输出信号的频率等于输入信号频率的两倍,并且与两个输入信号之间的中心频率保持90°相移。

从图中还可知,fout不一定是对称波形。

对相位比较器Ⅰ,它要求Ui、Uo的占空比均为50%(即方波),这样才能使锁定范围为最大。

相位比较器Ⅱ是一个由信号的上升沿控制的数字存储网络。

它对输入信号占空比的要求不高,允许输入非对称波形,它具有很宽的捕捉频率范围,而且不会锁定在输入信号的谐波。

它提供数字误差信号和锁定信号(相位脉冲)两种输出,当达到锁定时,在相位比较器Ⅱ的两个输人信号之间保持0°相移。

4046芯片

4046芯片4046芯片是一种多功能模拟数字转换器(ADC)和数字模拟转换器(DAC)芯片。

它由一组数字逻辑门和放大器组成,用于实现信号的模拟和数字转换。

4046芯片可用于多种应用,例如锁相环(PLL)电路、频率合成器、频率跟踪器、数码相位锁定环路(DPLL)等。

它能够将模拟信号转换为数字信号,并将数字信号转换为模拟信号。

以下是关于4046芯片的详细介绍。

1. 锁相环(PLL)电路:4046芯片可用作PLL电路的核心部件。

它可以实现频率合成、频率跟踪和相位锁定等功能。

通过调整输入信号和参考信号之间的相位差,4046芯片可以将输入信号锁定到参考信号的相位和频率。

2. 频率合成器:4046芯片可以生成稳定的高频信号。

它可以将低频信号调制到高频,并通过调整振荡器的控制电压来实现频率的调节。

这使得4046芯片非常适合用于射频电路、电视和广播设备等领域。

3. 频率跟踪器:4046芯片可以实现信号的频率跟踪和锁定。

它可以将一个输入信号的频率转换为数字信号,并通过反馈机制来调整输入信号的频率,使其与参考信号的频率保持同步。

4. 数码相位锁定环路(DPLL):4046芯片可以用作数码相位锁定环路的核心元件。

数码相位锁定环路是一种常用的时钟恢复和时钟提取技术,可用于数据通信设备和数字音视频设备中。

4046芯片可以将失真的时钟信号转换为稳定的时钟信号,并通过反馈机制来实现时钟的同步和提取。

除了以上应用,4046芯片还具有以下特点:1. 高精度:4046芯片具有很高的精度和稳定性,可以实现精确的模拟和数字信号转换。

2. 宽电压范围:4046芯片的工作电压范围通常为3V至15V,使其能够适应不同的应用需求。

3. 多功能性:4046芯片支持多种功能,如锁相环、频率合成和频率跟踪等。

这使得它成为设计各种电子设备的理想选择。

总结而言,4046芯片是一种功能强大的模拟数字转换器和数字模拟转换器芯片。

它可以应用于锁相环电路、频率合成器、频率跟踪器和数码相位锁定环路等多种应用领域。

CD4046锁相环

锁相环CD4046应用介绍:频率相等,相位同步也就是相位相差一个固定值锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。

它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

锁相环主要由相位比较器(PC)、压控振荡器(V CO)。

低通滤波器三部分组成,如图1所示。

压控振荡器的输出Uo接至相位比较器的一个输入端,其输出频率的高低由低通滤波器上建立起来的平均电压Ud大小决定。

施加于相位比较器另一个输入端的外部输入信号Ui与来自压控振荡器的输出信号Uo相比较,比较结果产生的误差输出电压UΨ正比于Ui和Uo两个信号的相位差,经过低通滤波器滤除高频分量后,得到一个平均值电压Ud。

这个平均值电压Ud朝着减小VCO输出频率和输入频率之差的方向变化,直至VCO输出频率和输入信号频率获得一致。

这时两个信号的频率相同,两相位差保持恒定(即同步)称作相位锁定。

当锁相环入锁时,它还具有“捕捉”信号的能力,VCO可在某一范围内自动跟踪输入信号的变化,如果输入信号频率在锁相环的捕捉范围内发生变化,锁相环能捕捉到输人信号频率,并强迫VCO锁定在这个频率上。

锁相环应用非常灵活,如果输入信号频率f1不等于VCO输出信号频率f2,而要求两者保持一定的关系,例如比例关系或差值关系,则可以在外部加入一个运算器,以满足不同工作的需要。

过去的锁相环多采用分立元件和模拟电路构成,现在常使用集成电路的锁相环,CD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。

图2是CD4046的引脚排列,采用16 脚双列直插式,各引脚功能如下:1脚相位输出端,环路人锁时为高电平,环路失锁时为低电平。

2脚相位比较器Ⅰ的输出端。

3脚比较信号输入端。

4脚压控振荡器输出端。

5脚禁止端,高电平时禁止,低电平时允许压控振荡器工作。

CD4046中文资料

CD4046中文资料

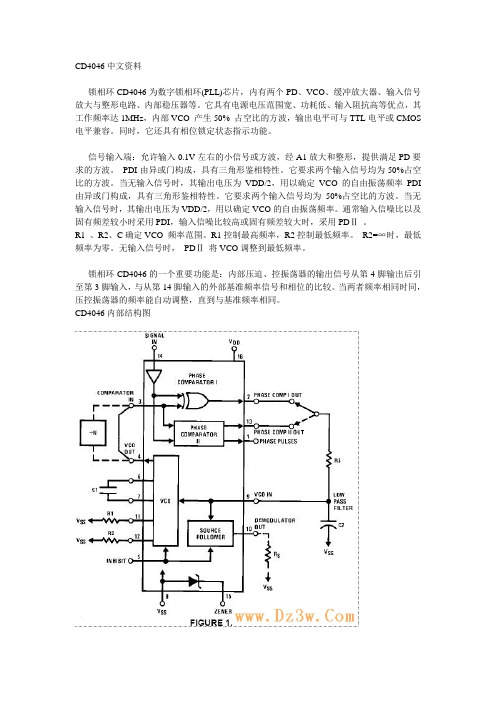

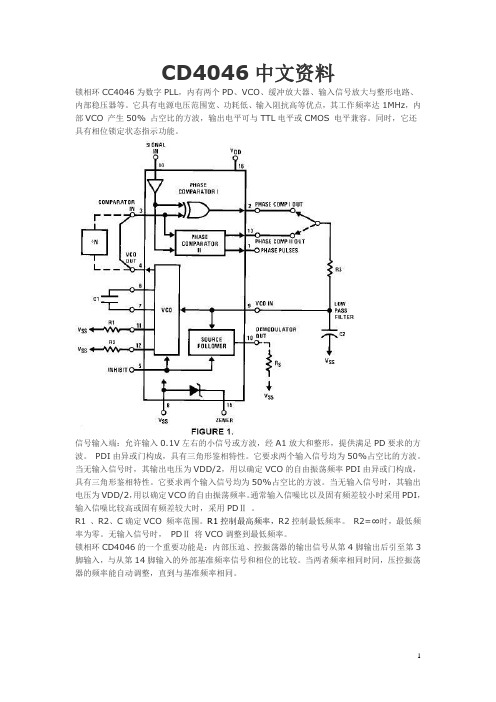

锁相环CD4046为数字锁相环(PLL)芯片,内有两个PD、VCO、缓冲放大器、输入信号放大与整形电路、内部稳压器等。

它具有电源电压范围宽、功耗低、输入阻抗高等优点,其工作频率达1MHz,内部VCO 产生50% 占空比的方波,输出电平可与TTL电平或CMOS 电平兼容。

同时,它还具有相位锁定状态指示功能。

信号输入端:允许输入0.1V左右的小信号或方波,经A1放大和整形,提供满足PD要求的方波。

PDI由异或门构成,具有三角形鉴相特性。

它要求两个输入信号均为50%占空比的方波。

当无输入信号时,其输出电压为VDD/2,用以确定VCO的自由振荡频率PDI 由异或门构成,具有三角形鉴相特性。

它要求两个输入信号均为50%占空比的方波。

当无输入信号时,其输出电压为VDD/2,用以确定VCO的自由振荡频率。

通常输入信噪比以及固有频差较小时采用PDI,输入信噪比较高或固有频差较大时,采用PDⅡ。

R1 、R2、C确定VCO 频率范围。

R1控制最高频率,R2控制最低频率。

R2=∞时,最低频率为零。

无输入信号时,PDⅡ将VCO调整到最低频率。

锁相环CD4046的一个重要功能是:内部压迫、控振荡器的输出信号从第4脚输出后引至第3脚输入,与从第14脚输入的外部基准频率信号和相位的比较。

当两者频率相同时同,压控振荡器的频率能自动调整,直到与基准频率相同。

CD4046内部结构图。

cd4046原理

cd4046原理CD4046是一种常用的集成电路,用于频率锁定环路和相位比较器。

它由一个VCO(Voltage Controlled Oscillator)和两个相位比较器组成。

我们来了解一下CD4046的基本原理。

CD4046是一种锁相环(PLL)电路,它可将输入信号锁定在特定的频率上。

PLL是一种负反馈控制系统,它通过调整输出信号的相位和频率来与输入信号保持一致。

CD4046的输入信号经过一个相位比较器与VCO的输出信号进行比较,然后通过一个滤波器对比较结果进行平滑处理,最后输出给VCO进行频率调整。

CD4046中的相位比较器有两个,分别为相位比较器1和相位比较器2。

相位比较器1用于锁定输入信号的相位,相位比较器2用于锁定输入信号的频率。

相位比较器1的输出信号经过一个低通滤波器来获得一个平均值,然后输入给VCO进行频率调整。

相位比较器2的输出信号则直接输入给VCO进行相位调整。

CD4046中的VCO是一个电压控制的振荡器,它的频率可以通过控制输入信号的电压来调整。

VCO的输出信号经过一个分频器后又反馈给相位比较器1和相位比较器2,形成一个闭环控制系统。

当输入信号的频率与VCO的输出频率不一致时,相位比较器1和相位比较器2会产生不同的输出信号,通过调整VCO的频率和相位,使得两个输入信号保持一致。

CD4046的频率锁定环路具有很多应用。

一种常见的应用是频率合成器,它可以将一个稳定的参考信号通过CD4046锁定在所需的频率上,用于无线电调谐器和通信系统中。

另一种应用是相位比较器,它可以用于数字通信系统中的时钟恢复和数据同步。

总结一下,CD4046是一种用于频率锁定环路和相位比较器的集成电路,它通过相位比较器和VCO的组合来实现输入信号的锁定。

CD4046广泛应用于无线电调谐器、通信系统和数字通信系统等领域。

通过对CD4046的深入了解,我们可以更好地理解和应用这一集成电路。

CD4046应用资料

CD4046中文资料锁相环CC4046为数字PLL,内有两个PD、VCO、缓冲放大器、输入信号放大与整形电路、内部稳压器等。

它具有电源电压范围宽、功耗低、输入阻抗高等优点,其工作频率达1MHz,内部VCO 产生50% 占空比的方波,输出电平可与TTL电平或CMOS 电平兼容。

同时,它还具有相位锁定状态指示功能。

信号输入端:允许输入0.1V左右的小信号或方波,经A1放大和整形,提供满足PD要求的方波。

PDI由异或门构成,具有三角形鉴相特性。

它要求两个输入信号均为50%占空比的方波。

当无输入信号时,其输出电压为VDD/2,用以确定VCO的自由振荡频率PDI由异或门构成,具有三角形鉴相特性。

它要求两个输入信号均为50%占空比的方波。

当无输入信号时,其输出电压为VDD/2,用以确定VCO的自由振荡频率。

通常输入信噪比以及固有频差较小时采用PDI,输入信噪比较高或固有频差较大时,采用PDⅡ。

R1 、R2、C确定VCO 频率范围。

R1控制最高频率,R2控制最低频率。

R2=∞时,最低频率为零。

无输入信号时,PDⅡ将VCO调整到最低频率。

锁相环CD4046的一个重要功能是:内部压迫、控振荡器的输出信号从第4脚输出后引至第3脚输入,与从第14脚输入的外部基准频率信号和相位的比较。

当两者频率相同时同,压控振荡器的频率能自动调整,直到与基准频率相同。

CD4046引脚图DC Supply Voltage 直流供电电压(VDD) −0.5 to +18 VDC Input Voltage输入电压(VIN) −0.5 to VDD +0.5 VDC Storage Temperature Range储存温度范围(TS) −65℃ to +150℃Power Dissipation功耗(PD)Dual-In-Line 普通双列封装700 mWSmall Outline 小外形封装500 mW焊接温度(TL)(焊接10秒)260℃Recommended Operating Conditions 建议操作条件:DC Supply Voltage 直流供电电压(VDD) 3 to 15 VDC Input Voltage输入电压(VIN) 0 to VDD VDC Operating Temperature Range工作温度范围(TA) −55℃ to +125℃符号引脚号名称功能PH1114相位比较器输入端(基准信号输入),相位比较器输入信号,输入允许将0.1V左右的小信号或方波信号在内部放大并再经过整形电路后,输出至相位比较器。

cd4046构成的fsk调制解调电路

cd4046构成的fsk调制解调电路全文共四篇示例,供读者参考第一篇示例:CD4046是一种集成电路,常用于FSK调制和解调电路中。

FSK (Frequency Shift Keying)调制技术是一种数字调制技术,通过改变信号的频率来携带数字信息。

在通信系统中,FSK调制技术被广泛应用于数据传输和调频调制解调。

本文将详细介绍CD4046构成的FSK 调制解调电路的原理和应用。

一、CD4046简介CD4046是一种集成数字数字锁相环PLL(Phase Locked Loop)电路,由德州仪器公司生产。

它由一个相位比较器、一个VCO (Voltage Controlled Oscillator)和一个低通滤波器组成。

CD4046可以将输入信号的频率与VCO的频率进行比较,并自动调节VCO的频率,使得输入信号与VCO的频率同步。

这种锁相环的原理可以用于FSK调制和解调电路中。

二、FSK调制解调电路原理1. FSK调制原理:在FSK调制中,输入的数字信号被转换成两种不同频率的信号,并分别控制两个不同频率的载波信号。

这两种载波信号通过一个开关切换器,使得输出信号在两种频率之间切换,从而携带数字信息。

2. FSK解调原理:在FSK解调中,接收到的信号经过解调器解调,得到两种不同频率的信号。

这两种信号再经过一个比较器比较,得到解调后的数字信号。

CD4046通过其内部的相位比较器和VCO实现了FSK调制解调电路。

其电路连接如下:1. 输入信号经过一个低通滤波器,去除噪声和高频成分,然后输入到CD4046的相位比较器。

2. CD4046的VCO的频率由输入信号的频率控制,当输入信号的频率高于VCO的频率时,VCO的频率会增加;反之,当输入信号的频率低于VCO的频率时,VCO的频率会减小。

3. CD4046的输出信号通过一个比较器进行信号处理,得到FSK调制或解调后的数字信号。

1. 数据传输:FSK调制技术可以将数字信号转换成模拟信号进行传输,提高数据传输效率和可靠性。

基于cd4046锁相环的数字频率合成器电路设计

基于cd4046锁相环的数字频率合成器电路设计1. 介绍在当今的数字电子领域,频率合成器扮演着至关重要的角色,它可以将一个基础频率信号合成出多个频率信号,广泛应用于收音机、数字通信、无线电、雷达等领域。

本文将重点讨论基于cd4046锁相环的数字频率合成器电路设计,以及CD4046的基本工作原理和性能特点。

2. 基础原理CD4046作为一种锁相环集成电路,它由相位比较器、环路滤波器和振荡器组成。

在频率合成器中,CD4046可以将输入信号频率合成成另一个输出频率信号,并且具有较高的信号锁定能力。

其基本工作原理是根据输入信号频率与振荡器输出信号频率之间的差值,不断调节振荡器输出频率,直至二者频率相同,从而实现信号的合成。

3. 设计步骤(1) 确定合成频率范围:根据实际需求确定所需合成频率范围,进而选择合适的分频倍数和振荡器参数。

(2) 选择振荡器电路:根据合成频率范围选择合适的振荡器电路和频率合成器芯片,CD4046是目前较为常用的选择之一。

(3) 进行电路仿真:使用电路仿真软件对设计电路进行仿真和调试,确保电路工作稳定和合成频率准确。

(4) 调节环路参数:根据实际需求调节环路参数,如环路带宽和环路增益,以实现更精准的频率合成效果。

4. 性能分析CD4046锁相环具有较高的抗干扰能力和频率稳定性,能够在一定程度上抵抗外部环境干扰和波动。

其响应速度较快,能够实现快速锁定输入信号频率,并且具有较高的合成精度和稳定性,适用于多种频率合成场景。

5. 个人观点在设计数字频率合成器时,选择合适的频率合成器芯片对电路性能起着至关重要的作用。

CD4046锁相环作为一种可靠的集成电路芯片,具有较高的性能和稳定性,是设计高质量数字频率合成器的重要选择之一。

在实际应用中,需要根据具体需求合理设计振荡器电路和调节环路参数,以实现更加精准和稳定的频率合成效果。

总结:本文对基于CD4046锁相环的数字频率合成器电路设计进行了全面评估和探讨,介绍了其基本工作原理、设计步骤、性能分析和个人观点,并对其在数字频率合成器设计中的重要性进行了强调。

4046锁相环

4。

4 数字锁相环锁相环(PLL)电路是一种反馈控制电路。

图1-37所示是基本锁相环电路的框图。

当相位比较器的两个输入的相位差(θi-θo)不变时,这两个信号的频率一定相等,即fi=fo 从而实现输出信号的频率和相位对输入信号的频率和相位的自动跟踪.图1- 1 基本锁相环电路框图根据实际需要,对基本锁相环电路做相应的改动,增加必要的其他电路,人们设计出了有各种各样用途的锁相环电路。

锁相环电路在通讯、仪器、机电控制的领域有着十分广泛的应用。

在锁相环电路中,若相位比较器的功能是比较两个模拟信号,压控振荡器输出的是正弦波,则称其为模拟锁相环电路;若相位比较器的功能是比较两个方波信号,压控振荡器输出的是方波,则称其为混合型锁相环电路(因为,低通滤波器通常总是模拟电路),亦称其为数字锁相环电路。

4。

4。

1.数字锁相环集成电路74HC4046本实验使用数字锁相环集成电路74HC4046。

图1—38是其的电路原理示意图。

由图可见,它由一个方波压控振荡器(VCO)和三个相位比较器。

三个相位比较器分别是:异或相位比较器(NOR),即PC1,其相位锁定范围为0~180°;相位—频率比较器(PFD),即PC2,其相位锁定范围为—360°~360°;JK触发相位比较器(JK),即PC3,其相位锁定范围为0~360°。

图1- 2 74HC4046的电路原理示意图在使用相位比较器的选择方面,PC1是比较容易锁定的,但要求输入的信号是50%占空比,或者是一个波形较好的小信号正弦波。

如果有条件达到这个要求,尽可能使用PC1。

不对称的大信号如能得到一个比要求输出倍频的基准,用一个触发器分频就可以得到很严格的50%占空比。

如果没有条件得到50%占空比,就要考虑用PC2以得到稳定的锁相。

对照图1—37可知,图1—38所示电路的框图就是图1-37.其使用的相位比较器是PC2,R3、R4、C2组成低通滤波器,其传递函数K f(s)与K p、K o/s、K n将确定环路的动态特性,R1、C1将确定锁相输出的频带范围,R2、C1将确定输出的频率偏移。

74HC4046锁相环电路

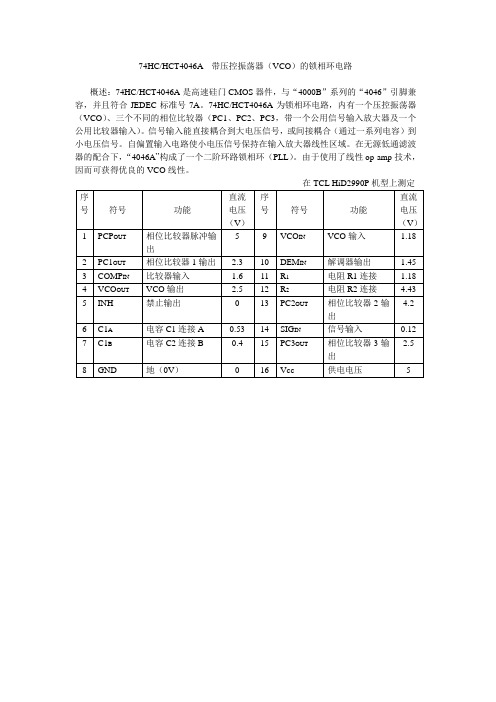

74HC/HCT4046A- -带压控振荡器(VCO)的锁相环电路

概述:74HC/HCT4046A是高速硅门CMOS器件,与“4000B”系列的“4046”引脚兼容,并且符合JEDEC标准号7A。

74HC/HCT4046A为锁相环电路,内有一个压控振荡器(VCO)、三个不同的相位比较器(PC1、PC2、PC3,带一个公用信号输入放大器及一个公用比较器输入)。

信号输入能直接耦合到大电压信号,或间接耦合(通过一系列电容)到小电压信号。

自偏置输入电路使小电压信号保持在输入放大器线性区域。

在无源低通滤波器的配合下,“4046A”构成了一个二阶环路锁相环(PLL)。

由于使用了线性op-amp技术,因而可获得优良的VCO线性。

在TCL HiD2990P机型上测定。

4046中文资料

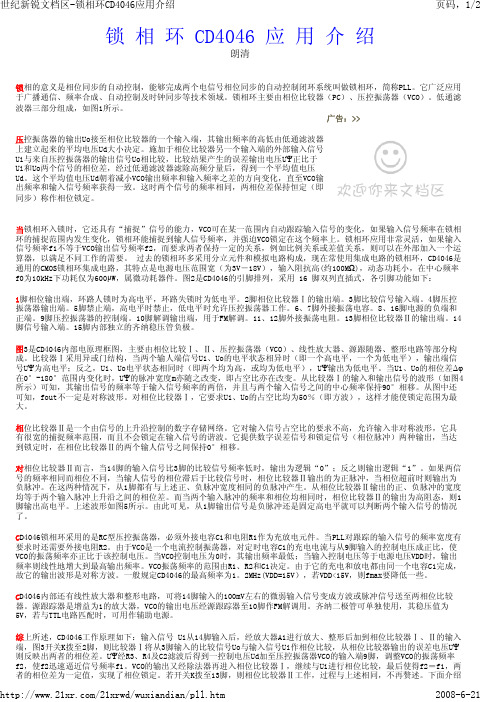

锁 相 环 CD4046 应 用 介 绍朗清锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。

它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

锁相环主要由相位比较器(PC)、压控振荡器(VCO)。

低通滤波器三部分组成,如图1所示。

广告:>>上建立起来的平均电压Ud大小决定。

施加于相位比较器另一个输入端的外部输入信号Ui与来自压控振荡器的输出信号Uo相比较,比较结果产生的误差输出电压UΨ正比于Ui和Uo两个信号的相位差,经过低通滤波器滤除高频分量后,得到一个平均值电压Ud。

这个平均值电压Ud朝着减小VCO输出频率和输入频率之差的方向变化,直至VCO输出频率和输入信号频率获得一致。

这时两个信号的频率相同,两相位差保持恒定(即同步)称作相位锁定。

当锁相环入锁时,它还具有“捕捉”信号的能力,VCO可在某一范围内自动跟踪输入信号的变化,如果输入信号频率在锁相环的捕捉范围内发生变化,锁相环能捕捉到输人信号频率,并强迫VCO锁定在这个频率上。

锁相环应用非常灵活,如果输入信号频率f1不等于VCO输出信号频率f2,而要求两者保持一定的关系,例如比例关系或差值关系,则可以在外部加入一个运算器,以满足不同工作的需要。

过去的锁相环多采用分立元件和模拟电路构成,现在常使用集成电路的锁相环,CD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。

图2是CD4046的引脚排列,采用 16 脚双列直插式,各引脚功能如下:1脚相位输出端,环路人锁时为高电平,环路失锁时为低电平。

2脚相位比较器Ⅰ的输出端。

3脚比较信号输入端。

4脚压控振荡器输出端。

5脚禁止端,高电平时禁止,低电平时允许压控振荡器工作。

6、7脚外接振荡电容。

8、16脚电源的负端和正端。

毕业设计(论文)-数字锁相环4046的锁相和压控振荡原理传感器采集设计

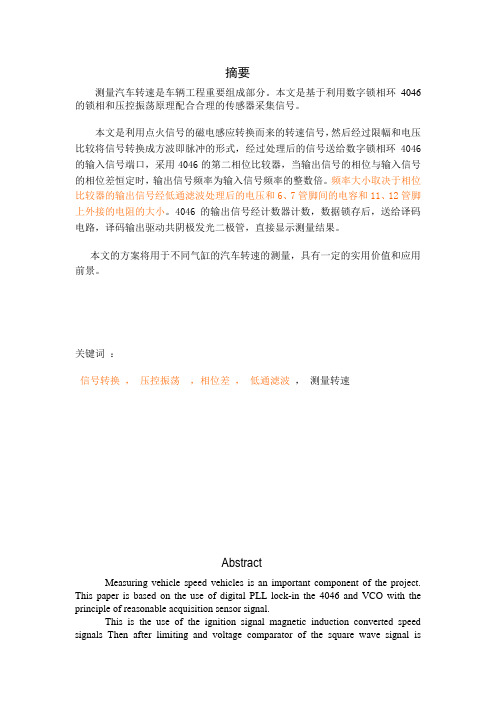

摘要测量汽车转速是车辆工程重要组成部分。

本文是基于利用数字锁相环4046的锁相和压控振荡原理配合合理的传感器采集信号。

本文是利用点火信号的磁电感应转换而来的转速信号,然后经过限幅和电压比较将信号转换成方波即脉冲的形式,经过处理后的信号送给数字锁相环4046的输入信号端口,采用4046的第二相位比较器,当输出信号的相位与输入信号的相位差恒定时,输出信号频率为输入信号频率的整数倍。

频率大小取决于相位比较器的输出信号经低通滤波处理后的电压和6、7管脚间的电容和11、12管脚上外接的电阻的大小。

4046的输出信号经计数器计数,数据锁存后,送给译码电路,译码输出驱动共阴极发光二极管,直接显示测量结果。

本文的方案将用于不同气缸的汽车转速的测量,具有一定的实用价值和应用前景。

关键词:信号转换,压控振荡,相位差,低通滤波,测量转速AbstractMeasuring vehicle speed vehicles is an important component of the project. This paper is based on the use of digital PLL lock-in the 4046 and VCO with the principle of reasonable acquisition sensor signal.This is the use of the ignition signal magnetic induction converted speed signals Then after limiting and voltage comparator of the square wave signal isconverted into the form of pulses, After treatment, the signal given to the 4,046 DPLL input signal ports, The use of 4046 compared with the second phase, when the output signal phase of the input signal with a constant phase difference, output signal frequency of the input signal frequency integer multiples. Frequency depends on the size of phase comparison of the output signal by the low-pass filter after the voltage and 6, 7 pin capacitance between the pin on 11, 12 and the external resistor size. 4046 output signal Counting, data latches, gave decoding circuit, Decoding the total output driving LED cathode direct measurement results show.In this paper, the program will be used for different cylinder motor speed measurement, has some practical value and prospects.第一章 引言1.1锁相环基本原理一个典型的锁相环(PLL )系统,是由鉴相器(PD ),压控荡器(VCO )和低通滤波器(LPF )三个基本电路组成,如图1,Ud = Kd (θi –θo) U F = Ud F (s )θi θo 图11.1.1.鉴相器(PD )构成鉴相器的电路形式很多,这里仅介绍实验中用到的两种鉴相器。

cd4046中文资料

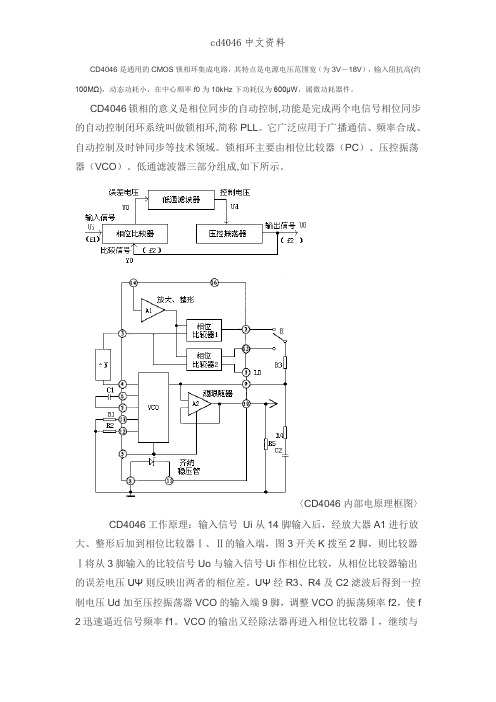

CD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。

CD4046锁相的意义是相位同步的自动控制,功能是完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。

它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

锁相环主要由相位比较器(PC)、压控振荡器(VCO)。

低通滤波器三部分组成,如下所示。

〈CD4046内部电原理框图〉CD4046工作原理:输入信号Ui从14脚输入后,经放大器A1进行放大、整形后加到相位比较器Ⅰ、Ⅱ的输入端,图3开关K拨至2脚,则比较器Ⅰ将从3脚输入的比较信号Uo与输入信号Ui作相位比较,从相位比较器输出的误差电压UΨ则反映出两者的相位差。

UΨ经R3、R4及C2滤波后得到一控制电压Ud加至压控振荡器VCO的输入端9脚,调整VCO的振荡频率f2,使f 2迅速逼近信号频率f1。

VCO的输出又经除法器再进入相位比较器Ⅰ,继续与Ui进行相位比较,最后使得f2=f1,两者的相位差为一定值,实现了相位锁定。

若开关K拨至13脚,则相位比较器Ⅱ工作,过程与上述相同,不再赘述。

下图是CD4046的引脚排列,采用16脚双列直插式,各管脚功能:1脚相位输出端,环路人锁时为高电平,环路失锁时为低电平。

2脚相位比较器Ⅰ的输出端。

3脚比较信号输入端。

4脚压控振荡器输出端。

5脚禁止端,高电平时禁止,低电平时允许压控振荡器工作。

6、7脚外接振荡电容。

8、16脚电源的负端和正端。

9脚压控振荡器的控制端。

10脚解调输出端,用于FM解调。

11、12脚外接振荡电阻。

13脚相位比较器Ⅱ的输出端。

14脚信号输入端。

15脚内部独立的齐纳稳压管负极。

〈CD4046引脚图〉CD4046典型应用电路。

图6是用CD4046的VCO组成的方波发生器,当其9脚输入端固定接电源时,电路即起基本方波振荡器的作用。

锁 相 环 CD4046 应 用 介 绍

锁相环 CD4046 应用介绍锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。

它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

锁相环主要由相位比较器(PC)、压控振荡器(VCO)。

低通滤波器三部分组成,如图1所示。

压控振荡器的输出Uo接至相位比较器的一个输入端,其输出频率的高低由低通滤波器上建立起来的平均电压Ud大小决定。

施加于相位比较器另一个输入端的外部输入信号Ui与来自压控振荡器的输出信号Uo相比较,比较结果产生的误差输出电压UΨ正比于Ui和Uo两个信号的相位差,经过低通滤波器滤除高频分量后,得到一个平均值电压Ud。

这个平均值电压Ud朝着减小VCO输出频率和输入频率之差的方向变化,直至VCO输出频率和输入信号频率获得一致。

这时两个信号的频率相同,两相位差保持恒定(即同步)称作相位锁定。

当锁相环入锁时,它还具有“捕捉”信号的能力,VCO可在某一范围内自动跟踪输入信号的变化,如果输入信号频率在锁相环的捕捉范围内发生变化,锁相环能捕捉到输人信号频率,并强迫VCO锁定在这个频率上。

锁相环应用非常灵活,如果输入信号频率f1不等于VCO输出信号频率f2,而要求两者保持一定的关系,例如比例关系或差值关系,则可以在外部加入一个运算器,以满足不同工作的需要。

过去的锁相环多采用分立元件和模拟电路构成,现在常使用集成电路的锁相环,CD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。

图2是CD4046的引脚排列,采用 16 脚双列直插式,各引脚功能如下:1脚相位输出端,环路人锁时为高电平,环路失锁时为低电平。

2脚相位比较器Ⅰ的输出端。

3脚比较信号输入端。

4脚压控振荡器输出端。

5脚禁止端,高电平时禁止,低电平时允许压控振荡器工作。

CD4046 锁相环原理及应用

CD4046 锁相环原理及应用时间:2008-12-26 来源: 作者: 点击:1560 字体大小:【大中小】锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。

它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

锁相环主要由相位比较器(PC)、压控振荡器(VCO)、低通滤波器三部分组成,如图1所示。

图 1压控振荡器的输出Uo接至相位比较器的一个输入端,其输出频率的高低由低通滤波器上建立起来的平均电压Ud大小决定。

施加于相位比较器另一个输入端的外部输入信号Ui与来自压控振荡器的输出信号Uo相比较,比较结果产生的误差输出电压UΨ正比于Ui和Uo两个信号的相位差,经过低通滤波器滤除高频分量后,得到一个平均值电压Ud。

这个平均值电压Ud 朝着减小CO输出频率和输入频率之差的方向变化,直至VCO输出频率和输入信号频率获得一致。

这时两个信号的频率相同,两相位差保持恒定(即同步)称作相位锁定。

当锁相环入锁时,它还具有“捕捉”信号的能力,VCO可在某一范围内自动跟踪输入信号的变化,如果输入信号频率在锁相环的捕捉范围内发生变化,锁相环能捕捉到输人信号频率,并强迫VCO锁定在这个频率上。

锁相环应用非常灵活,如果输入信号频率f1不等于VCO输出信号频率f2,而要求两者保持一定的关系,例如比例关系或差值关系,则可以在外部加入一个运算器,以满足不同工作的需要。

过去的锁相环多采用分立元件和模拟电路构成,现在常使用集成电路的锁相环,CD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。

图2是CD4046的引脚排列,采用16 脚双列直插式。

图2各引脚功能如下:∙1脚相位输出端,环路人锁时为高电平,环路失锁时为低电平。

∙2脚相位比较器Ⅰ的输出端。

锁相环(史)

RS

QD QC QB QA

74LS90 cBp1 cpA0

RS

被测信号

b

PH I 2 a PH I1

CD4046

c

VCOo

反相器的作用

✓ 左边的反相器:因为74LS374是上升沿触发 ✓ b为什么要为Q3的反相信号?

Q3的特点是高电平持续时间短,低电平时间持续时间 长,如果a为高电平,b为低电平,则锁相环相位器不 好比较,所以将Q3取反。

• 本锁相环电路选择了相位比较器2(PC2), 锁相环路锁定在压控振荡器中型频率处时 输入输出的相位差为0。所以R4是不可以省 去的。

实验内容三 、 用CC4046、74LS90、 74LS00组成一个倍频电路(其倍频数N=1 -10可选)

用锁相环实现倍频的原理

fcoN'fco

实验步骤:

(1)用74LS90设计一个十进制计数器,测绘各关键点的波 形, (注意触发源的选择)。

• 集成数字锁相环内通常至少包含压控振荡器VCO和相位比较器PC。 • 本实验使用HCT4046。

• PIN DESCRIPTION

• PIN NO. SYMBOL NAME AND FUNCTION

MC4046应用

3.1 锁相环CD4046原理及应用3.1.1锁相环路的构成锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。

它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

锁相环主要由相位比较器(PD)、压控振荡器(VCO)、低通滤波器三部分组成,如图1所示图1 锁相环路的基本组成框图压控振荡器的输出Uo接至相位比较器的一个输入端,其输出频率的高低由低通滤波器上建立起来的平均电压Uc大小决定。

施加于相位比较器另一个输入端的外部输入信号Ui与来自压控振荡器的输出信号Uo相比较,比较结果产生的误差输出电压Ud正比于Ui和Uo 两个信号的相位差,经过低通滤波器滤除高频分量后,得到一个平均值电压Uc。

这个平均值电压Uc朝着减小VCO输出频率和输入频率之差的方向变化,直至VCO输出频率和输入信号频率获得一致。

这时两个信号的频率相同,两相位差保持恒定(即同步)称作相位锁定。

当锁相环入锁时,它还具有“捕捉”信号的能力,VCO可在某一范围内自动跟踪输入信号的变化,如果输入信号频率在锁相环的捕捉范围内发生变化,锁相环能捕捉到输人信号频率,并强迫VCO锁定在这个频率上。

锁相环应用非常灵活,如果输入信号频率f1不等于VCO 输出信号频率f2,而要求两者保持一定的关系,例如比例关系或差值关系,则可以在外部加入一个运算器,以满足不同工作的需要。

过去的锁相环多采用分立元件和模拟电路构成,现在常使用集成电路的锁相环,CD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。

3.1.2CD4046的引脚排列,采用 16 脚双列直插式,各引脚功能如下:图1脚相位输出端,环路人锁时为高电平,环路失锁时为低电平。

2脚相位比较器Ⅰ的输出端。

3脚比较信号输入端。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

4.4 数字锁相环锁相环(PLL)电路是一种反馈控制电路。

图1-37所示是基本锁相环电路的框图。

当相位比较器的两个输入的相位差(θi-θo)不变时,这两个信号的频率一定相等,即 fi=fo 从而实现输出信号的频率和相位对输入信号的频率和相位的自动跟踪。

图1- 1 基本锁相环电路框图根据实际需要,对基本锁相环电路做相应的改动,增加必要的其他电路,人们设计出了有各种各样用途的锁相环电路。

锁相环电路在通讯、仪器、机电控制的领域有着十分广泛的应用。

在锁相环电路中,若相位比较器的功能是比较两个模拟信号,压控振荡器输出的是正弦波,则称其为模拟锁相环电路;若相位比较器的功能是比较两个方波信号,压控振荡器输出的是方波,则称其为混合型锁相环电路(因为,低通滤波器通常总是模拟电路),亦称其为数字锁相环电路。

4.4.1.数字锁相环集成电路74HC4046本实验使用数字锁相环集成电路74HC4046。

图1-38是其的电路原理示意图。

由图可见,它由一个方波压控振荡器(VCO)和三个相位比较器。

三个相位比较器分别是:异或相位比较器(NOR),即PC1,其相位锁定范围为0~180°;相位-频率比较器(PFD),即PC2,其相位锁定范围为-360°~360°;JK触发相位比较器(JK),即PC3,其相位锁定范围为0~360°。

图 1- 2 74HC4046的电路原理示意图在使用相位比较器的选择方面,PC1是比较容易锁定的,但要求输入的信号是50%占空比,或者是一个波形较好的小信号正弦波。

如果有条件达到这个要求,尽可能使用PC1。

不对称的大信号如能得到一个比要求输出倍频的基准,用一个触发器分频就可以得到很严格的50%占空比。

如果没有条件得到50%占空比,就要考虑用PC2以得到稳定的锁相。

对照图1-37可知,图1-38所示电路的框图就是图1-37。

其使用的相位比较器是PC2,R3、R4、C2组成低通滤波器,其传递函数K f(s)与K p、K o/s、K n将确定环路的动态特性,R1、C1将确定锁相输出的频带范围,R2、C1将确定输出的频率偏移。

图1-38中虚线部分是相位比较器PC2。

它的两个输入之间可以有三种关系:SIG IN超前COMP IN;SIG IN与COMP IN同相位;SIG IN滞后COMP IN。

若SIG IN超前COMP IN,如图39(b),当SIG IN的上升沿到达时UP置0,P管导通,DOWN依旧为1,N管截止。

PC2OUT输出高电平,记为1。

当COMP IN的上升沿到达时,DOWN也置0,但这时刻,两个D触发器的Q端都为1,与非门输出置低,D触发器被复位,使UP和DOWN都为1,P管和N管都截止,此时为高阻状态,PC2输出为V CC/2,记为0。

若SIG IN与COMP IN同相位,如图1-39(b),当SIG IN、COMP IN的上升沿同时到达时,UP、DOWN 同时置0,但这时刻,两个D触发器的Q端都为1,与非门输出置低,D触发器被复位,使UP和DOWN都为1,P管和N管都截止,此时为高阻状态,PC2输出为V CC/2,记为0。

图 1- 3 PC2相位比较器图 1- 4 VCCS原理电路图 1- 5 74HC4046中的VCO的频率特性若SIG IN滞后COMP IN,如图1-39(b),当COMP IN的上升沿到达时DOWN置0,N管导通,UP 依旧为1,P管截止。

PC2OUT输出低电平,记为-1。

当SIG IN的上升沿到达时,UP也置0,但这时刻,两个D触发器的Q端都为1,与非门输出置低,D触发器被复位,使UP和DOWN都为1,P管和N管都截止,此时为高阻状态,PC2输出为V CC/2,记为0。

PC2的输出经低通滤波器输出直流电压,即图1-39(b)中的V DEMOUT(AV)。

由图1-39(b)可得()()V 4DEMout P COMPin SIGin CC DEMout φφφπK V V =-= 方波VCO 由电压控制电流源(VCCS )和电容交叉充放电式压控振荡器组成。

图1-40为VCCS 的原理电路。

当INH = 1时,T1管截止整个电路不工作。

当INH = 0时,T1导通,电路允许工作。

T2、T3组成镜像电流源。

T4和R2是T2的漏极负载,流过T2的漏源电流受输入电压V VCO 和外接电阻R1、R2控制,2GS2CC 1GS4VCO D2R V V R V V I -+-=图 1- 6 典型的锁相频率范围与R 1C 1的关系流过T3的漏源电流I O 是I D2的镜像电流,两者相等。

至此可见,若选定R1、R2后,输入电压V VCO 与输出电流I O 成线性关系。

电容交叉充放电式压控振荡器的原理示意图如图1-38左侧虚线内的电路。

若设G1输出为1,G2输出为0,则P1、N2导通,P2、N1截止,来自VCCS 的电流经P1、PIN6、C 、N2由左向右给C 充电。

当PIN6点的电压上升到G1的高电平门限时,G1输出1变为0,G2输出由0变为1,这时,P2、N1导通,P1、N2截止,来自VCCS 的电流经P2、PIN7、C 、N1由右向左给C 充电。

当PIN7点的电压上升到G2的高电平门限时,G2输出1变为0,G1输出由0变为1。

在此过程中VCO 输出了一个周期的方波。

若输入电压V VCO 不变,VCO 将不断地重复输出上述周期的方波。

至此可见,电容确定后,若不接R2,I O 小,充电时间长,输出方波频率低,R 2越小,I O 越大,充电时间越短,输出方波的频率越高,且不受VCO 输入电压V VCO 的控制。

R 1越小,I O 越大充电时间越短,输出方波的频率越高,同时受VCO 输入电压V VCO 的控制。

如图1-41,VCO 输出方波的频率的范围为2f L ,中心频率为f o 。

当确定了锁定频率的范围后,就有了2f L ,查对图1-42所示曲线,就可以得到R 1C 1的乘积。

由下式可估算L o off 61f .f f -=查对图1-43所示曲线,可得到C 1、R 2的元件值。

再由R 1C 1的乘积和C 1可得到R 1。

图 1- 7 典型的频率偏移f off 与C 1、R 2的关系4.4.2.数字锁相环倍频器原理数字锁相环电路有着十分广泛的应用。

数字锁相环倍频器原理框图如图1-44。

当环路锁定后,f o =Nf i 。

本实验是用74HC/HCT4046实现数字倍频器。

数字锁相环倍频器是数字频率合成电路的主要组成部分之一。

以例说明数字锁相环倍频器的原理。

要求设计一个数字锁相环倍频器,其输入方波频率为100kHz ,输出锁定频率范围为2MHz ~3MHz ,频率间隔为100kHz ,过渡过程时间不大于1mS ,超调量不大于30%。

取其原理框图如图1-45,对照图1-44可知,本例使用的是PC2,R 3、R 4、C 2组成低通滤波器,其传递函数K f (s )与K p 、K o /s 、K n 将确定环路的动态特性,R 1、C 1将确定锁相输出的中心频率,R 2、C 1将确定输出的频率偏移。

图 1- 8 数字锁相环倍频器框图图 1- 9用74HC4046组成的数字锁相环倍频器数字锁相环倍频器可由以下步骤来设计。

第一步:由要求VCO 输出锁定频率的范围确定R 1、C 1、R 2。

由输出锁定频率范围为2MHz ~3MHz 可得1.7MHz 0.5MHz 1.6MHz 5261MHz52kHz5001MHz2MHz MHz 32L o off o L L =⨯-≈-====-=.f .f f .f f f查图1-42,取V CC =5V 、2f L =1MHz 可得,s C R 611106-⨯≈查图1-43,取R 2=10k Ω、V CC =5V 可得,C 1≈600pF 。

由此可得Ω=⨯⨯=--k /R 10106001061261即R 1=10k Ω,C 1 =600pF ,R 2=10k Ω。

第二步:求相位传递函数H(s)。

先求图1-45所示的各框图的传递函数。

相位比较器PC2输入为相位差φDEMout =θi -θ2,输出是直流电压(在环路中起作用的是PC2out 中的直流分量),由前面的分析和图1-45可知)rad /V (.V K V )s (K CC P DEMout d P 39804≈===πφ 低通滤波器LPF 的输入为电压,输出也为电压,由图1-45可得11212+++==s )(s V V )s (K d C f τττ 其中,τ1=R 3C 2、τ2=R 4C 2。

压控振荡器VCO 输入的是直流电压V C ,输出的是相位θo ,为了将θo 与锁定频率范围建立联系,所以用θo =ωo /s 代入,s.).V (f V s /V )s (K CC L C o C O 19090222--⋅===πωθs)Vs/rad(.sKs.MHzo610963112312⨯≈=⋅=π分频器DIV的输入是相位θo,输出是相位θ2,N)s(KOn12==θθ相位传递函数为2222212122212221111nnnoPoPoPnOfPnOfPiss)s(N/KKN/KKsssNKK)s(K)s(K)s(K)s(K)s(K)s(K)s(K)s(K)s(Hωζωτωττττττττθθ+++=+++++++=⋅⋅⋅+⋅⋅⋅==其中,⎪⎪⎭⎫⎝⎛+=++=+=oPnoPnoPn KKNN/KK,)(NKK2212212121τωτττωζττω前者为系统的固有角频率,后者为系统的阻尼系数。

通常有K P K Oτ2/N>>1,这时有22222nnnnsss)s(Hωζωωζω+++≈这时,22/nτωζ≈。

相位误差传递函数为222221nniiiDEMoute sss)s(H)s(Hωζωθθθθφ++≈-=-==第三步:由对系统的动态特性,即快速性和准确性,求时间常数τ1、τ2,再求低通滤波器的元件值R3、R4、C2。

图1-10 单位阶跃响应的典型曲线图1-11 有零点二阶系统超调量σ与ωn/(-z)的关系通常以单位阶跃响应来描述系统的动态特性,如图1-45,叙述单位阶跃响应的主要指标。

(1)峰值时间t P从t = 0到响应曲线最大值的时刻之间的时间。

(2)超调量σ)()()(σp ∞∞-=y y t y 超调量常用百分数(%)表示。

(3)过渡过程时间t s (亦称调整时间、建立时间)()()()∞⋅∆=∞-y y t y sΔ·y(∞)可取(0.02~0.05)· y(∞)。

最常用的是取Δ=0.05,称为按±5%定义的过渡过程时间,记为t s0.05;取Δ=0.02,称为按±2%定义的过渡过程时间,记为t s0.02。