基于ATE的DSP测试方法

基于ATE的DSP测试方法

中 图 分 类 号 :T 3 9 文 献 标 识 码 :B P 1

M e hod SP e tng on TE t ofD t si A

X ua Ta n o

( eig A tma cTe n eh ooy Istt B On 00 8 C ia B in uo t s g T cn l ntue eig 10 8 hn ) j i i t g i

‘ S SD P55 9A 0

,

t e ho orD SP’ s he m t d f

i tuci nstsi a d t m ehod fw rtn t D S nsr to etng n he t o ii g he P f nci n ’ S ig u to d a noss e ue e nd p nd nt r ATE i s q nc i e e e fom The ag it m nd t ehod en i l or h a he m t sm tone bo ve be n a le he BC31 V50 i e r t d t si yse . d a ve ha e pp id on t 92 nt g ae etng s tm Th eul s w s t ag rt a t e ho a e e e t .S cal,t SP’ Sf tona o l e tn e r s t ho he l o hm i nd he m t ds r f ci ve pe il y he D unci lm du et s g i ag ihm rgi ts fo he bae ofc ve ng alt n i na od e ’ a ti t s l ort o i nae r m t s o r l he f cto lm i u ul s trbu e .The wa e lzn he ysofr aii g t u tona f nci lm od e ts ng ag it ncud rnse rng t sc t s od e e tn l t trbutswi i i n c l ul et or hm i l e ta fri hebai e tm i l ul,t si g al hea t i e t n de t a h i m o l nd t si he e t nd at bu e c o sdfe e o ls nal , t pe ds use t t s pr r a ’ S du e a etng t x e tr t sa r s i r ntm due .Fi ly i hepa r ic s d he e t og m ta s lntton rnpa a i bew e n t e di e e t f r n ATES

基于ATE的LVDS芯片测试技术

加 10 0

24 .

地 靠近

t t isu i i tr a ‘e bt O h . u n t n e v l i iwit ) i .

图2 Asn 的LD 标 NIA Vs 准 厂

LD V S测试 通 常 使用 大 规模 集 成 电路 测 试 机 台 (T ) T A E ,A E的测 试 通道 较多 ,能够产 生 和测 试 多 路 高速 和复 杂 的波形 .芯 片 的功能 测试 、直 流参 数

O U xRi 确 1 u s  ̄F " m “2 0 0 M ̄ s l

们6

5 o s o 2 . 1 . 5

3% o l t 0 |I -

lV mI Iv II n I^ -l - I ● II l l ^ IV mI

V

V m

V咐

I“c I r Ⅲ嘲 l _ I e. Hv a g I so o a e '

电 子 产 品可 靠 性 与 环 境 试 验

21 0 2正

LD V S的特 点 是 电 流 驱 ห้องสมุดไป่ตู้ 模 式 .低 电 压 摆 幅

至少 使用 4层 P B板 ( C 从顶 层 到底 层 ) VD :L S信号

3 0m 可 以提 供 更 高 的信 号传 输 率 .使 用 差 分 传 5 V 输 的方式 .输 入信 号 只与 2个信 号 的差值有 关 ,可 将 共 模 干扰 抑 制 掉 .可 以 使 信 号 的 噪声 和 E 都 MI

Vo o

vs o

翻晌nn Ou .- e 删 叫 g

O s to g n o vb e

27 4

ATE测试原理范文

ATE测试原理范文ATE(Automatic Test Equipment,自动测试设备)是一种用于自动测试和诊断电子元器件、电路板和电子设备的装置,广泛应用于电子制造业。

ATE测试原理是指在ATE系统中进行测试和诊断的基本原理和方法。

本文将从ATE测试的基本流程、测试原理和常见的测试技术等方面进行阐述,介绍ATE测试原理。

在ATE测试中,基本的测试流程通常包括以下几个步骤:1.测试准备:包括测试系统的初始化、测试程序的加载和设备的连接等。

2.测试信号发生:根据测试需求生成测试信号,例如时钟信号、电源信号等,用于驱动被测设备。

3.测量信号采集:采集被测设备在测试信号作用下的响应信号,如输出电压、电流等。

4.数据分析和判断:通过对采集到的信号进行分析和判断,判断被测设备是否符合规格要求。

5.测试结果输出:根据测试判断的结果,输出测试报告或控制设备进行优化和调整。

1.测试目标和测试方法选择:在ATE系统中,根据被测设备的特点和测试需求,选择合适的测试目标和测试方法。

例如,对于数字电路的测试,常采用逻辑测试方法,对模拟电路则采用参数测试方法。

2.测试信号的发生和采集:在ATE系统中,需要根据被测设备的特点生成相应的测试信号,并采集被测设备在测试信号作用下的响应信号。

这一过程通常通过信号发生器和信号采集模块实现。

3.数据分析和判断:在ATE系统中,根据采集到的信号,通过数据分析和判断,判断被测设备是否符合规格要求。

这一过程通常通过数字信号处理和模拟信号处理技术来实现。

4.测试结果输出和记录:根据测试判断的结果,通过输出测试报告或记录测试数据等方式,将测试结果输出。

1.功能测试:用于测试被测设备各个功能模块是否正常工作。

通过输入各种不同的信号,观察输出是否符合预期结果。

2.电气参数测试:用于测试被测设备的电气特性参数,如电压、电流、功率等。

通过对被测设备的输入和输出信号进行测量和分析,判断其电气参数是否在规格范围内。

ate使用手册

ATE使用手册一、简介ATE(Automatic Test Equipment)是一种用于自动测试电子设备的设备。

它能够模拟不同的测试条件,检查设备的功能和性能。

本手册将指导您如何使用ATE进行测试。

二、使用步骤1. 准备工作:在开始测试之前,请确保您已经阅读并理解了ATE 的使用说明。

同时,确保ATE设备已经正确连接并开启。

2. 创建测试配置:根据被测设备的规格和测试需求,创建一个新的测试配置。

测试配置应包括测试项目、测试条件、测试步骤等信息。

3. 加载测试程序:根据被测设备的规格和测试需求,编写测试程序。

然后将测试程序上传到ATE设备中。

4. 执行测试:按照测试配置的步骤,在ATE设备上执行测试。

在测试过程中,请注意观察ATE设备的状态和被测设备的反应。

5. 分析结果:测试完成后,ATE设备将生成测试结果。

请仔细分析测试结果,并根据需要调整测试配置或测试程序。

6. 维护和校准:为了确保ATE设备的准确性和可靠性,定期进行维护和校准是非常重要的。

请参考ATE设备的维护和校准手册,并按照要求进行操作。

三、注意事项1. 在使用ATE设备时,请务必遵守安全规定和操作规程,避免发生意外事故。

2. 在进行测试之前,请确保被测设备已经通过手动测试,以排除任何故障或问题。

3. 在编写测试程序时,请注意遵守编程规范和最佳实践,以提高测试的准确性和可靠性。

4. 在分析测试结果时,请注意识别任何异常或错误,并采取适当的措施进行解决。

5. 在进行ATE设备的维护和校准时,请确保遵循正确的步骤和规程,以确保设备的准确性和可靠性。

ATE自动化测试系统操作手册

ATE自动化测试系统用户手册〔〕一、ATE自动化测试系统简介ATE自动化测试系统是一个简单易用的自动化测试软件,用户可调用通用测试驱动或定制的测试驱动提供的方法来搭建一个测试过程,只需要简洁的设置步骤即可建立一个测试项目。

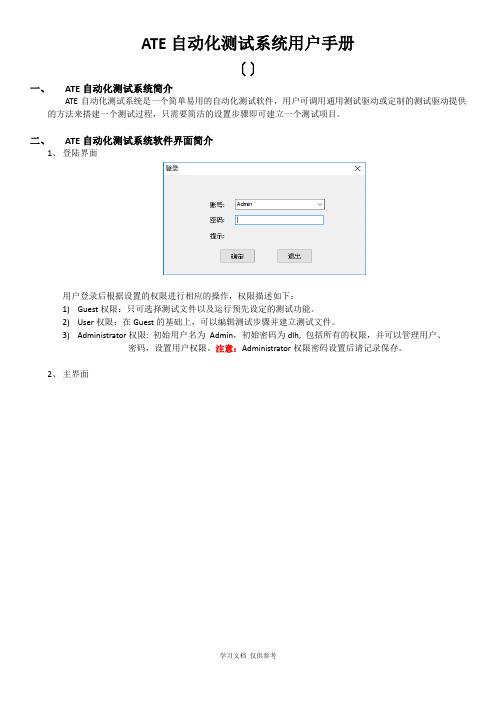

二、ATE自动化测试系统软件界面简介1、登陆界面用户登录后根据设置的权限进行相应的操作,权限描述如下:1)Guest权限:只可选择测试文件以及运行预先设定的测试功能。

2)User权限:在Guest的基础上,可以编辑测试步骤并建立测试文件。

3)Administrator权限: 初始用户名为Admin,初始密码为dlh, 包括所有的权限,并可以管理用户、密码,设置用户权限。

注意:Administrator权限密码设置后请记录保存。

2、主界面2.1 测试项目编辑区用户选择测试步骤和测试参数。

2.2 测试区运行测试程序。

2.3 菜单区测试程序的编辑,运行及系统设置等功能。

2.4 测试结果显示区实时显示测试信息。

三、 菜单说明1. “文件”选项1.1 “新建”创建新的测试文件。

1.2 “打开”打开已存在的测试文件。

1.3 “保存”保存当前测试文件。

1.4 “另存为”测试文件另存为新的文件名。

1.5 “打印”打印测试文件及测试结果。

测试项目编辑区 测试结果显示区菜单区测试区1.6“打印预览”预览测试文件及测试结果。

1.7“打印设置”设置打印测试文件时的页面。

1.8“最近的文件”选择最近打开的测试文件。

1.9“退出”退出软件。

2.“编辑”选项2.1“撤销”撤销当前的操作。

2.2“剪切”剪切选择的测试项目,可用于粘贴。

2.3“复制”复制选择的测试项目,可用于粘贴。

2.4“粘贴”粘贴测试项目。

3.“视图”选项3.1“工具栏”选择是否显示工具栏3.2“状态栏”选择是否显示状态栏4.“运行”选项4.1“开始”开始运行测试文件。

4.2“暂停”暂停运行测试文件。

4.3“停止”停止运行测试文件。

4.4“单步执行”选择此选项可单步运行测试步骤。

ATE测试基本知识

ATE整机组成

PC-控制中心,过 程控制及结果判

断

接口控制电路测试信号的产生,

调制,接收

显示器-显示测 试结果

气缸

测试架-信 号与机芯

接口

.

2、 测试原理

1、CALL ID 测试是依据中华人民共和国通信 行业标准 YND 069-1997制作的。其中FSK 信号是挂机状态、单数据消息格式,DTMF 信号是标准格式。

.

3、建立测试线 测试线建立后,如下图,此时可以选择测试的来电显示号码和 DTFM拨出号码及是否保存测试数据的选项。此时便可开始进行 测试,如果要两个并行测试,可以再建立一条测试线。测试完毕 后,系统显示测试结果“合格”或“不合格”及各项目测试值。

.

4、测试参数设置: 当需要修改测试机芯的参数或新增测试机型时,选择系统菜 单下的<系统参数配置>项,系统出现对话框如下图,在各对 话框中写入相应信息后,选择<Save>按钮保存或依据<Close> 提示进行保存。不需要保存时,选择<Cancel>退出。

.

9、当机芯压板长时间不抬起时,说明正测试机芯 不合格,单按一下“启动1“或”启动2“,压板

会 自动抬起,取出机芯写上故障代码待修理维修。 再放入另一机芯继续测试 。

.

五、ATE测试人员工作要 点

1、每下一种机型,严格按照该种机型的工艺卡操作。 严禁非技术(管理)人员擅自更改已设置好指标参数 的测试程序(文件)。

3、这一部仪器以工控机为基础,内建A/D、I/O卡, 外加自己开发的接口控制电路 ,一台工控机可以 带两个接口控制电路,控制两个测试架,同时测 试两部机芯。

.

二、仪器的连接及各部分说明

一种基于ATE的提高DSP测试覆盖率方法

Computer Science and Application 计算机科学与应用, 2021, 11(5), 1598-1606Published Online May 2021 in Hans. /journal/csahttps:///10.12677/csa.2021.115165一种基于ATE的提高DSP测试覆盖率方法陈培华1,魏领会2*1北京冠中集创科技有限公司,北京2北方工业大学,北京收稿日期:2021年4月28日;录用日期:2021年5月22日;发布日期:2021年5月31日摘要DSP功能高覆盖率的测试是一个比较难的课题。

本文以自主研发CATT-400大规模集成电路测试系统为测试平台,提出一种基于ATE (Automatic Test Equipment)的DSP的高覆盖率的测试方法;通过基于美国TI公司TMS320F28xx系列DSP,实现该测试方法开发验证,并实现自动测试设备与测试向量的自动匹配。

该方法对于有微处理器的芯片测试有很大的推广意义。

关键词CATT-400,TMS320F28xx,ATEA Method of Improving DSP Test CoverageBased on ATEPeihua Chen1, Linghui Wei2*1GZICTEST Technology Co., Ltd., Beijing2North China University of Technology, BeijingReceived: Apr. 28th, 2021; accepted: May 22nd, 2021; published: May 31st, 2021AbstractIt is difficult to test the high coverage of DSP function. In this paper, the CATT-400 large-scale inte-grated circuit test system developed by ourselves is used as the test platform, and a high coverage test method based on ATE (automatic test equipment) DSP is proposed. Through the TMS320F28xx series*通讯作者。

一种用于ATE系统的DPAT测试方法

一种用于ATE系统的DPAT测试方法DPAT(Dynamic Power Analysis Test)是一种用于ATE系统(Automatic Test Equipment,自动测试设备)的测试方法,用于评估芯片的功耗特性。

该方法通过对芯片进行动态功耗分析,可以帮助开发人员了解芯片的功耗情况,从而优化芯片设计和功耗管理策略。

以下是对DPAT测试方法的详细介绍。

1.测试目标:DPAT测试的目标是评估芯片的功耗特性,包括各个功能模块的功耗、功耗的变化情况以及功耗波动的原因等。

2.测试原理:DPAT测试通过对芯片进行动态功耗分析,即对芯片进行正常工作状态下的功耗监测。

测试过程中,通过在芯片上植入功耗监测电路,测量芯片在不同工作状态下的功耗变化,并将数据输入到ATE系统进行分析和统计。

3.测试流程:DPAT测试的流程主要包括以下几个步骤:(1)准备工作:首先,需要准备好测试芯片和ATE系统,包括ATE系统的硬件设备和软件工具。

此外,还需要设计和植入功耗监测电路,并进行芯片的布线和焊接。

(2)设置测试参数:在进行DPAT测试之前,需要设置一些测试参数,例如测试电压、工作频率、测试时间等。

这些参数将影响到测试结果的准确性和全面性。

(3)功耗测试:在测试过程中,通过ATE系统控制芯片的工作状态,例如发送不同的输入信号、改变工作频率等,然后通过功耗监测电路测量芯片的功耗变化,并将测量数据传输到ATE系统进行记录和分析。

(4)数据分析:测试结束后,需要对测得的功耗数据进行分析和统计。

可以通过ATE系统提供的功耗分析工具进行数据处理,例如计算平均功耗、功耗方差、功耗波动等,以及绘制功耗曲线和功耗分布图等。

(5)结果评估:最后,根据测试结果对芯片的功耗特性进行评估。

可以比较不同模块之间的功耗差异,分析功耗的变化趋势以及原因,并从中找出可能存在的问题和改进方向。

4.注意事项:在进行DPAT测试时(1)测试设备:ATE系统需要具备采样速度快、分辨率高的特点,以保证能够准确地测量芯片的功耗变化。

一种基于ate的serdes物理层测试方法

一种基于ate的serdes物理层测试方法基于ATE的SerDes(串行器/解串器)物理层测试方法旨在验证和评估高速串行数据通信链路的可靠性和性能。

这种测试方法可以帮助检测信号完整性、干扰、时钟恢复、数据提取以及串行连接等关键方面的问题。

以下是一种基于ATE的SerDes物理层测试方法的详细介绍。

1.串行器/解串器连接性测试:首先,通过ATE对串行器和解串器进行连接性测试。

这包括验证所有的连接电气和机械规范是否符合要求。

此测试可以确认接口间的正常连接,并消除连接故障可能导致的性能问题。

2.时钟恢复测试:在此测试中,ATE向被测设备发送已知模式的高速数据,并验证解串器是否能正确恢复出数据的时钟。

测试数据可以包括频率和振幅变化的数字信号,以完整覆盖所有潜在时钟恢复问题。

通过分析和比较被测设备接收到的数据和发送的数据,可以评估时钟恢复的性能。

3.数据提取测试:此测试旨在评估解串器的数据提取能力。

通过向被测设备发送包含不同干扰和失真的数据,并使用ATE在解串器端进行数据提取和验证。

此测试可以帮助检测和识别数据提取过程中可能发生的错误或偏差,并评估解串器在不同条件下的性能。

4.信号完整性测试:通过模拟不同电气和环境条件下的信号完整性问题,如反射噪声、串扰、衰减等,来评估接口的信号完整性。

此测试可以使用ATE生成和测量信号,以检测和区分不同信号完整性问题,并确定性能是否符合预期。

5.串行连接测试:利用ATE模拟不同物理层连接条件,如长度、噪声、损耗等,对串行器和解串器进行性能评估。

这些条件可以模拟实际应用中可能遇到的各种连接场景。

通过检测和测量数据时钟、均衡性、眼图开口、误码率等参数,可以评估串行连接的质量和适应性。

6.性能参数测试:最后,通过改变不同的参数和配置,例如数据速率、均衡设置、驱动电平等,测试被测设备在不同条件下的性能。

通过测量和比较接收到的数据质量和信号特性,可以评估设备的性能,并优化物理层连接和配置。

ate测试系统操作规程

ate测试系统操作规程测试系统操作规程一、引言测试系统是指为了保证软件质量,在软件开发过程中进行测试的一套系统。

为了确保测试工作的高效有序进行,提高测试效果,有必要制定测试系统操作规程。

本文档旨在规范测试系统的操作,提供相应的操作指南。

二、测试系统操作规程1. 测试环境准备(1) 确保测试服务器、测试数据库、测试工具等测试所需硬件和软件环境都已搭建完毕。

(2) 确保测试服务器、数据库等已进行初始化和配置,能够正常运行。

(3) 确保测试的软件版本与开发团队使用的软件版本一致。

2. 测试用例编写(1) 根据软件产品需求文档,编写测试用例。

(2) 测试用例应包含详细的测试步骤、预期结果和实际结果。

(3) 测试用例应覆盖软件的各个功能模块,尽可能全面地验证软件的功能和性能。

3. 测试任务安排(1) 根据测试计划,将测试任务分配给不同的测试人员。

(2) 确保测试任务的分配合理,每个测试人员负责的任务应适量,以确保测试的顺利进行。

4. 测试执行(1) 根据测试用例逐个执行测试任务。

(2) 在执行测试任务时,应按照测试用例中的测试步骤进行,记录实际结果。

(3) 在执行过程中,如发现问题或异常,应及时记录并反馈给开发团队。

5. 缺陷管理(1) 对于发现的问题或异常,应及时记录在缺陷管理系统中。

(2) 每个缺陷应包含详细的描述、重现步骤、优先级和严重程度等信息。

(3) 开发团队应及时对缺陷进行修复,并在修复完成后进行复测确认。

6. 测试报告编写(1) 在测试执行完成后,根据测试结果编写测试报告。

(2) 测试报告应包含测试概况、测试结果、缺陷列表以及对测试工作的总结等内容。

(3) 测试报告应及时提交给相关人员,供其参考和决策。

7. 测试数据备份(1) 在测试执行前,应对测试数据进行备份。

(2) 在测试执行后,应对测试数据进行清理,以确保数据不会对系统正式运行造成影响。

8. 测试系统维护(1) 定期对测试系统进行维护和优化,确保其稳定性和可靠性。

基于ATE高效测量射频到基带噪声指数详解

基于ATE高效测量射频到基带噪声指数详解噪声指数(Noise Figure)主要测量的是组件的信噪比(Signal-to-noise RaTIo,SNR)性能,信噪比是误码率(BER)和载波/噪声比(C/N)等大部分数字通信参数的基础。

以往只会针对(RF)到射频的组件,也就是低噪声放大器(LNA),进行噪声指数测量,但在过去几年,低噪声放大器已被整合到接收器中,将信号从天线端带到模拟或数字基带的单元(I和Q),因此,测试射频到基带架构的噪声指数已经变得越来越普遍。

测试射频到基带架构的噪声指数已是射频组件量产测试必经的步骤,为缩短测试时间和降低测试成本,必须在自动化测试设备中导入冷噪声,或使用具任意波形发生能力噪声源的Y系数方法来进行测试。

射频到基带的前端电路包含一个与混频器串接的低噪声放大器,混频器可以将射频信号降频转换为基带信号,这样的组合在今日射频组件的大量生产(HVM)测试中,已经相当普遍。

虽然测量这些组件的噪声指数所使用的方法与到射频组件的方法相同,但台式测试设备与自动化测试设备,以及射频到射频组件与射频到基带组件之间的运用方式还是有些不同。

噪声系数为噪声指数根本噪声指数可测量出组件会带入多少噪声到系统中,在射频到基带的接收器中,通过噪声指数测量,可得知降频转换和放大过程会加入多少的噪声。

噪声指数与信噪比这项基本的参数有关,从最早期的音响设备到最新一代的个人通信装置等各种电子应用中,信噪比都是极为重要的参数。

噪声系数(Noise Factor,F)虽然较少使用,却是噪声指数的根本。

噪声系数是以线性的格式描述因某个组件所造成的信噪比降低程度:噪声系数是在标准化的参考温度T=T0(IEEE订为290K,约17℃)下,将输入端的信噪比与输出端的信噪比相除的结果。

温度之所以成为一项条件,是因为电子电路中的噪声主要是由组件传导媒介中的电子热扰动(Thermal AgitaTIon)所造成的,又称为热噪声。

基于ATE 自动测试设备系统软件测试方法

发现错误与测试用例数量以及新增错误与测试用例数量的关系如图2所示。从图中可以看出,虽然随着测试用例数量的增加,可能会找到更多的软件错误,但是其投入与产出的比率却逐渐下降,当测试用例的数量达到某一程度的时候会极大地降低测试工作的效率。在不影响测试充分性的基础上,要求测试人员从无限的数据组合里提取出最具代表性的部分,充分发现隐藏在软件中的错误。

要测试这一点,需要让测试程序创建一个继承该抽象类的后代类。测试程序将通过测试该后代类来对单元进行测试。通常,采用为类编写源代码的方法使该类可以作为一个抽象或具体类而很容易编译,然而不一定会取得好的结果,还很容易出错。一个好的替代方案是使用指导性检查而不是基于执行的测试。

最后本文以系统级别软件测试为重点,对多种不同类型的软件测试方法进行了深入的探讨和研究,并通过大量的实例探讨了部分方法。在积累一定测试经验的基础上,我们建议,对基于面向过程思想开发的ATE系统(或基于面向对象思想开发的ATE系统中的面向过程部分)的功能测试中采用边界值分析和强健壮等价类结合生成测试用例的方法,其中等价类划分可以根据被测对象的特点在定义域空间或值域空间完成。

ATE是一种非常先进灵活的方案,可以满足多种产品的程序测试要求。微型计算机控制的仪器出现以后,ATE的结构设计直接针对测试需要,ATE包括系统集成、信号连通增值软硬件、面向测试的语言和图形用户界面等。

二、自动测试设备(ATE)系统软件的测试现状

目前很多软件开发机构都面临这样一个问题,那就是开发出来的软件产品的质量一直得不到很好的保证,很多产品在正式交付用户使用后总是存在诸多问题。其中很重要的原因是软件开发的管理水平不高,尤其是忽视了对软件产品进行必要和充分的测试。一直以来,国内对于软件测试的重要性缺乏足够的认识,在对软件测试的理解上也存在一些误区,例如有的企业直到编码阶段后期才开始测试,有的采用谁开发谁测试或者交叉测试的办法,有的甚至连测试这一环节都没有,产品的质量当然无法提高。ISO9000质量体系认证越来越得到软、硬件公司的重视,而测试是ISO9000中质量保证实施的一个重要环节,中国加入WTO后越来越多的企业的产品要面对国际市场优秀产品的竞争,产品质量的保证是生存之本。

基于ATE的FPGA测试方法

基于ATE的FPGA测试方法FPGA(Field-Programmable Gate Array)是一种可编程逻辑设备,它可以在实现之前通过电子设计自动化(EDA)工具编程来实现特定功能。

为了验证FPGA设计的正确性和完整性,需要进行一系列测试。

测试方法的选择直接影响到测试的效率和可靠性。

基于ATE(Automatic Test Equipment)的FPGA测试方法是一种高效且可靠的测试方法,可以有效地验证FPGA的功能和性能。

1.测试计划制定:在开始测试之前,需要制定详细的测试计划,包括测试的目标、测试的范围、测试的方法和测试的时间安排等。

测试计划的制定应充分考虑FPGA设计的特点和需求,并确保测试的全面性和准确性。

2.环境搭建:为了进行FPGA测试,需要搭建测试环境,包括ATE设备、测试夹具、测试工具和测试软件等。

ATE设备是一种专门用于测试电子元件和芯片的硬件设备,可以实现对FPGA的输入输出信号的采集和控制。

测试夹具是一种用来连接FPGA和ATE设备的物理接口,用于传输测试信号和读取测试结果。

测试工具和测试软件则用于配置和控制ATE设备,并对FPGA进行测试。

3.测试程序编写:为了对FPGA进行测试,需要编写相应的测试程序。

测试程序是一种用于验证FPGA功能和性能的代码,可以通过ATE设备对FPGA进行输入输出控制和信号采集。

测试程序应包括对所有输入信号的覆盖测试和对所有输出信号的正确性验证。

4.测试向量生成:在编写测试程序之前,需要生成测试向量。

测试向量是一组输入信号,用于对FPGA进行测试。

测试向量应充分考虑FPGA设计的各个功能,以确保所有功能均得到有效测试。

测试向量的生成可以通过模拟和仿真等方法来实现。

5.测试执行和结果分析:在测试环境搭建和测试程序编写完成后,可以执行测试程序对FPGA进行测试。

测试程序会控制ATE设备对FPGA进行输入输出信号的控制和采集,然后对测试结果进行分析。

ATE测试基本知识

.

ATE整机组成

PC-控制中心,过 程控制及结果判

断

接口控制电路测试信号的产生,

调制,接收

显示器-显示测 试结果

气缸

测试架-信 号与机芯

接口

.

2、 测试原理

1、CALL ID 测试是依据中华人民共和国通信 行业标准 YND 069-1997制作的。其中FSK 信号是挂机状态、单数据消息格式,DTMF 信号是标准格式。

.

4、拿取机芯PCB板,将RING开关拨至右边后,平 稳放入测试架针床上,确认定位良好。

.

5、双手同时按下测试架底座两旁的“启动1”和 “启

动2”按钮,机芯压板自动下压PCB板,到位后 开始测试。

原来这么 简单!

.

6、在前面两声振铃时观察测试架上的LCD显示镜 有无显示设定的FSK及DTMF来电显示号码。

现在

Dtmf、fsk、振铃、各功能的测试由计算 免提发受话、拨 机自动控制和判断, 号、手柄发受话、 操作人员只需拿放机 侧音,一部电话 芯和把测试出的坏机 的功能全部检测。 芯写上代码。

.

三、测试界面及操作说明

1、测试软件界面如下图:

2、选择测试机型界面 在上图中点击测试系统,选择新建,出现如下图的测试型 号选择提示对话框,选择电话机芯的型号,点击<OK>按钮, 系统自动在主画面下建立一条测试线 。

.

3、建立测试线 测试线建立后,如下图,此时可以选择测试的来电显示号码和 DTFM拨出号码及是否保存测试数据的选项。此时便可开始进行 测试,如果要两个并行测试,可以再建立一条测试线。测试完毕 后,系统显示测试结果“合格”或“不合格”及各项目测试值。

.

4、测试参数设置: 当需要修改测试机芯的参数或新增测试机型时,选择系统菜 单下的<系统参数配置>项,系统出现对话框如下图,在各对 话框中写入相应信息后,选择<Save>按钮保存或依据<Close> 提示进行保存。不需要保存时,选择<Cancel>退出。

ate检测标准

ate检测标准ATE测试是应用于电子制造行业的一种检测标准,主要包括了结构测试、功能测试和性能测试三个方面。

以下是ATE检测标准的详细介绍:1.结构测试(Structure Test):结构测试主要检测制造缺陷,以及零件的放置、连接等是否正确。

常见的结构测试包括以下几类:o IO类:主要用JTAG进行覆盖,会进行一些DC参数的测试,如VIH、VIL、VOH、VOL、Leakage等。

o Digital Logic类:主要用SCAN方式进行覆盖,如Stuck-at、Transition等,若存在覆盖率问题可添加功能向量。

o Memory类:主要用BIST方式进行覆盖。

o IP类:内嵌数字电路,用SCAN覆盖;模拟电路,测试功能和性能,辅以BIST。

o功耗类:通常采用IDDQ进行覆盖,亦可进行动态功耗测试。

o特殊类:Die ID、基准trim、加密烧写、SIP、POP、分级筛选等。

2.功能测试(Function Test):功能测试主要针对设备的功能进行检测,以确保设备能够正常工作并产生预期结果。

功能测试通常采用仿真或虚拟测试环境进行,以模拟设备的实际工作条件。

3.性能测试(Performance Test):性能测试主要检测设备的性能指标是否符合设计要求和实际应用需要。

这些指标可能包括设备的响应速度、精度、稳定性等。

性能测试通常需要在真实的设备上进行,以检测实际运行条件下的设备性能。

除了以上三个方面的测试,ATE检测标准还包括对于可靠性和安全性的评估。

这些评估可能包括对于设备的耐久性、环境适应性、电磁兼容性等方面的检测。

这些检测标准旨在确保设备能够在各种条件下正常工作,并且不会对人员或环境造成危害。

在实际应用中,ATE检测标准可能会根据不同的产品类型和实际需求进行调整和修改。

然而,无论采用何种ATE检测标准,其目的都是确保制造的设备能够达到预期的质量和性能水平,以满足客户的需求。

ate的动态试验标准

ate的动态试验标准一、试验目的ATE的动态试验主要目的是评估ATE设备的性能和可靠性。

通过模拟实际运行条件,测试ATE设备的动态响应和稳定性。

此外,动态试验还可以识别设备潜在的问题和瓶颈,以便进行改进和优化。

二、试验原理ATE的动态试验基于设备的工作原理和性能要求进行。

试验中需要模拟各种输入条件,如电压、电流、温度等,并监测设备的输出响应。

通过调整输入条件并观察输出响应,可以评估ATE设备的性能和可靠性。

三、试验步骤1. 准备阶段:选择合适的ATE设备,搭建测试平台,准备所需的测试设备和工具。

2. 测试阶段:按照预定的测试计划,进行各项动态测试。

记录测试数据并观察设备的响应情况。

3. 分析阶段:对测试数据进行整理和分析,评估设备的性能和可靠性。

4. 总结阶段:根据测试结果,撰写测试报告并总结试验结果。

四、试验设备1. ATE设备:选择符合测试要求的ATE设备。

2. 测试平台:搭建稳定的测试平台,确保测试过程中设备运行稳定。

3. 测试工具:准备所需的测试设备和工具,如电源、负载、万用表、示波器等。

五、试验数据记录1. 记录完整的测试数据,包括输入和输出参数。

2. 记录设备的响应时间和稳定性数据。

3. 拍摄设备的运行状态和测试过程,以便后续分析和故障排查。

六、试验结果分析1. 分析测试数据,评估ATE设备的性能指标是否符合要求。

2. 分析设备在各种条件下的响应情况和稳定性表现。

3. 识别设备潜在的问题和瓶颈,提出改进建议。

七、试验结论根据试验结果和分析,得出结论。

总结ATE设备的性能和可靠性表现,指出存在的问题和改进方向。

同时,为后续的设备优化和改进提供参考和建议。

八、试验报告撰写撰写详细的试验报告,包括以下内容:1. 试验目的和背景介绍:简要介绍ATE设备的用途和工作原理,说明进行动态试验的必要性。

2. 试验设备和环境:列出试验所需的设备和工具,描述测试平台的搭建和环境设置。

3. 试验步骤和方法:详细描述试验过程和方法,包括测试计划的制定、数据的记录和分析等。

用于通用ate开关资源测试路径优化的算法

用于通用ate开关资源测试路径优化的算法通用ATE开关资源测试路径优化算法是指将ATE(自动测试设备)资源进行有效利用,通过优化测试路径,提高测试效率和准确性的算法。

ATE测试路径(test path)是指将待测产品或零件连接至ATE,并设置各项参数,然后将产品或零件置入测试室,完成测试的一系列步骤。

优化ATE测试路径可以大大提升测试的效率,并减少缺陷率。

ATE测试路径优化的思路主要是先对实际的测试作业量进行评估,根据测试作业量来合理安排ATE资源,确定测试路径。

具体来说,根据测试设备和产品的特性,进行合理的测试路径优化,缩短测试的耗时,减少重复性的功能测试,减少测试中的消耗,提高测试的效率,达到更客观的测试数据。

在ATE测试路径优化的过程中,我们需要考虑的因素有:1.备的资源配置:可以考虑将ATE资源依据测试作业量进行合理的安排,以减少测试中的消耗,提升测试效率。

2.试数据的准确性:通过优化测试路径,可以使测试数据更加准确,以实现更精确的整体测试质量。

3.能测试的完整性:ATE测试路径的优化,可以使功能测试更加完整,实现高效的测试质量。

4.试的时间维度:ATE测试路径优化可以有效缩短测试的耗时,提高整体的测试效率,节约时间和人力成本。

为了实现ATE测试路径优化,有许多技术可以利用,如:贪心算法、动态规划、粒子群优化算法、遗传算法等。

其中,贪心算法是一种在每一步都作出最优选择,使得最后所有步骤的结果总体最优的算法。

贪心算法可以有效地解决ATE资源优化的问题,但是它的复杂度较高,耗时较长。

因此,为了解决贪心算法的复杂度和耗时问题,研究人员发展出了更简单高效的算法供使用,如动态规划、遗传算法和粒子群优化算法。

动态规划(Dynamic Programming)是一种分析和优化效率的重要方法,它可以用于解决复杂的问题,例如ATE资源优化问题。

在ATE资源测试路径优化中,通常将所有测试作业按序排列,然后求出每个测试作业完成所需要的最小时间。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2010年2月第2期电子测试ELECTRONIC TESTFeb.2010No.2基于ATE的DSP测试方法轩涛(北京自动测试技术研究所 北京 100088)摘要:本文以TI公司的DSP5509A为例,介绍了在ATE上开发DSP芯片的测试程序的思路和方法。

本文论述的DSP功能模块的测试算法,指令测试方法,脱机开发DSP功能诊断程序的方法已经在国产BC3193V50集成电路测试系统上运用,结果表明是有效的。

其中针对DSP功能模块的测试算法以穷举为出发点,具体实现方式包括基本测试模块的反复调用,同模块内所有属性的遍历测试,不同模块间属性的交叉组合测试。

最后本文论述了测试程序在不同测试系统移植中需要注意的问题。

关键词:DSP;集成电路测试系统;测试图形;指令测试;测试程序移植中图分类号:TP319 文献标识码:BMethod of DSP testing on ATEXuan Tao(Beijing Automatic Testing Technology Institute Beijing 100088 China)Abstract: This paper introduced the method of testing DSP chip on ATE by using TI company ‘s DSP5509A chip for instance. The paper discussed the DSP’s functional module testing algorithm, the method for DSP’s instructions testing and the method of writing the DSP function’s diagnosis sequence independent from ATE. The algorithm and the methods mentioned above have been applied on the BC3192V50 integrated testing system. The result shows the algorithm and the methods are effective. Specially, the DSP’s functional module testing algorithm originates from the base of covering all the functional modules’ attributes. The ways of realizing the functional module testing algorithm include transferring the basic test module, testing all the attributes within identical module and testing the extend attributes across different modules. Finally , the paper discussed the test program’s transplantation between different ATES.Keywords: DSP; IC test system; Test figure; Instruction test; The transplantation of the test program0 引言随着DSP芯片在商业,军事,航空航天等领域的越来越广泛的应用,其可靠性和可测试性也显得尤为重要。

DSP芯片内部相当复杂,使用相当灵活,正是这种应用的不确定性和可重复编程性,增加了芯片测试的难度。

其核心问题是建立什么样的测试模型,以及施加什么样的测试激励,能覆盖尽量多的逻辑功能,同时还能在可及端测量出来。

本文研究了在国产测试系统上进行高端的DSP芯片的功能测试的方法。

针对DSP所有功能模块的测试以无限穷举为出发点,测试的算法主要有基本模块的反复调用,属性的遍历测试,属性的交叉测试。

针对DSP指令的测试,本文又提出了既保证覆盖又不增加测试图形开销的详尽的指令测试方案。

最后给出了基于ATE的DSP测试图形的手编复制的生成方法。

本文最后还讨论了测试程序在不同测试系统上的移植中需要注意的问题。

1 被测器件(DUT)和测试系统1.1 被测器件(DUT)本文的测试器件选用TMS320VC5509A 。

TMS320VC5509A DSP是在5000系列DSP CPU核的基础上发展而来的高速低功耗数字信号处理器。

其片上CPU内部总线由一条程序总线,3条读数据总线,2条写数据总线,专门用于外设和DMA功能的总线。

这些总线可以实现一个时钟周期内的3次数据读和2次数据写操作。

此外DMA控制器可以在每个时钟周期内实现2次独立于CPU的数据传输。

片上CPU有2个乘法累加器(MAC),每个累加器都可以实现每时钟周期17位的乘法。

片上CPU还包括一个40位的中心算术逻辑单元(ALU)和一个附加的16位的算术逻辑单元(ALU)。

这些算术逻辑单元(ALU)在指令的控制下,可以实现优化并行处理能力和降低功耗的功能。

这些资源通过片上CPU的地址总线和数据总线调配。

5000系列DSP CPU实现灵活的指令宽度配置,指令单元(IU)从外部或内部存储器上取来32位的指令,在程序单元中将它们排序,程序单元将这些指令解码,然后直接发给地址(AB)和数据总线(DB),实现全保护指令流水线。

可预见的分支处理能力避免了在执行条件指令时可能出现的流水溢出。

通用输入输出端口(GPIO)和10位的A/D转换功能为状态,中断和显示器,键盘以及其它多媒体接口提供了充足的管脚。

并行接口可以有两种工作模式,要么通过HPI端口把芯片作为一个对微控制器的slave;要么通过异步EMIF端口配置为1个多媒体接口。

串行数据通过multimedia card/secure digital 外设和3个MCBSPs完成。

5509A外设的设置通过EMIF接口完成,3个双向的MCBSPs可完成接入符合工业标准的设备,也支持一共128个独立使能通道的多通道通信。

HPI接口是16位的并行接口,提供主处理器对32K 的从片片上存储器的访问。

DMA控制器提供独立于CPU的6个独立通道的数据传输。

DMA的数据传输字长是每时钟周期传输16位。

5509A还包括两个通用定时器,8个专用的GPIO和数字锁相环时钟产生器(DPLL)。

1.2 测试系统介绍BC3192V50 系统是北京自动测试技术研究所研制的基于当前国际先进VXI总线的数字集成电路测试系统,系统的最大优点就是它的软、硬件的开放性和标准化。

可嵌入多家VXI测试模块,使得测试系统易于扩展、升级。

系统符合VXI电、磁兼容标准。

具有测试精度高、速度快等特点。

系统设计采用模块化结构设计,每通道板可提供32路管脚电路,系统最大配置为8块通道板256路测试通道。

最大测试速率为50MHz(非复用),系统具有每16通道一路PMU 的多PMU特性. 本测试系统有较强的失效分析功能,设计有每通道失效存储器,用于失效分析。

系统具有动态定时功能(on the fly),可灵活设置时间参数,具有较强的CAD-CAT自动转换功能。

适用于IC生产厂家进行芯片测试或成品检验,也适用于IC设计公司进行IC功能验证。

该系统适合高端DSP芯片的测试。

2 DSP功能模块的测试算法2.1 基本模块的反复调用在编写测试程序的过程中,有一些对芯片基本操作的模块是要被反复使用的。

如果测试每一个具体的属性,都从头编写每一个测试向量,这个工作量是惊人的,显然这么做也不必要。

这里就涉及到对基本模块的反复调用,以减少编程工作量,增加编程准确性的问题。

这一点很类似于C语言里在每一个大程序开始前定义的若干个要被反复引用的宏。

如在测试EMIF的异步操作时候,CPU的取指,读数据,写数据,这些基本操作是要被反复应用的,而每一个看似简单的基本操作也至少要有5行以上的测试向量开销,这时候在程序开始认真编写好这些基本操作之后,后面就可以反复调用了,不同之处在于只是每一次调用都会视具体情况不同而用不同的相关参数。

ATE中对这些基本模块的调用与C 语言不同,主要采用两种方式,一是复制编好的程序段然后粘贴到指定的地方,之后修改参数,当然小模块可以组成大模块,只要该模块在后面还要被反复应用,都可以如法炮制,反复调用;还有就是为了增加覆盖率和尽量穷尽所有的情况,可以对处于测试程序同一位置的同一个基本模块,反复修改可变参数,然后编译测试。

比如说,有很多与地址有关的指令和操作,在这些模块的操作中,地址是一个可变的参数,这样就可以模块的框架和位置不动,而是反复写入不同的地址,然后编译程序,看程序的执行情况,以增加对DSP不同地址测试的覆盖。

从工程实践里,涉及地址空间的操作中,一般该空间的首,末地址和中间地址都是必测的。

2.2 属性的遍历测试复杂芯片的内部,总是由很多具有不同功能的模块组成的,在这里把每个模块具有的不同功能称之为属性。

显然同一模块的不同功能(属性)之间是相互独立的。

对芯片的逻辑功能测试,首先是对芯片每一个模块功能的测试,虽然每一个模块总是要先收到它上层模块的驱动数据,然后在模块内部把数据进行处理,最后再把处理之后的结果发送给该模块的下层模块,但一个完整的可以覆盖芯片所有逻辑功能的测试程序总是由一次次对每个不同模块的测试组成的。

2.3 属性的交叉组合测试交叉测试是在对每一个模块遍历测试的基础上,针对两个及以上模块的联合测试而言的。

比如模块B可以受模块A驱动(但不仅仅受模块A的驱动),模块A有M种不同的属性,模块B有N种不同的属性。

模块A有M1(显然M1≤M)个属性可以驱动模块B,并且驱动模块B可以完成N1(显然N1≤N)种不同的属性。

那么要实现完整的模块A和模块B的连接测试,就要进行M1*N1次测试(当然这个道理可以推广到3个及以上模块的连接测试)。

比如在DSP5509A中,EMIF可以受到CPU 的驱动,也可以不通过CPU而直接受到片上DMA 控制器的驱动。

EMIF在与DMA的连接中,DMA 有6个不同的channel可以驱动EMIF工作,EMIF 有同步异步2种工作方式,在异步中数据线宽度可以是8也可以是16,片选空间可以是CE 4个中的任何一个,现在为了简化问题,假定同步状态只有一种可以被DMA驱动的工作方式。

那么从上面的情况分析,要完整地测试DMA和EMIF的连接性,就要进行6*2*4+6*1=54次测试。

依据上面所说的测试算法,编写功能诊断程序的步骤如图1所示。