verilog设计 自动售货机

verilog自动售货机课程设计

verilog自动售货机课程设计一、课程目标知识目标:1. 学生理解Verilog硬件描述语言的基本语法和结构;2. 学生掌握利用Verilog设计简单的数字电路,如自动售货机逻辑控制单元;3. 学生了解自动售货机的工作原理及其在数字电路设计中的应用;4. 学生能够识别并描述自动售货机系统的各个模块及其功能。

技能目标:1. 学生能够运用Verilog语言编写自动售货机的基本控制代码;2. 学生通过实际操作,能够模拟自动售货机的运行流程,完成商品选择、支付及出货过程;3. 学生能够利用仿真工具对自动售货机的设计进行验证和调试,解决基本问题。

情感态度价值观目标:1. 学生培养对数字电路设计和Verilog编程的兴趣和热情;2. 学生通过团队协作,培养沟通能力和合作精神;3. 学生在设计过程中,认识到科技对生活的改变,增强创新意识和服务社会的责任感。

课程性质:本课程为电子信息类学科实践课程,结合理论知识,强调学生的动手能力和实际问题解决能力。

学生特点:学生为高中年级,具有一定的电子信息技术基础和编程经验,对新鲜事物充满好奇。

教学要求:注重理论与实践相结合,通过项目驱动的教学方式,引导学生主动探索,提高学生的实践操作能力。

在教学过程中,关注学生的学习反馈,及时调整教学策略,确保课程目标的实现。

将目标分解为具体的学习成果,以便于后续的教学设计和评估。

二、教学内容1. 自动售货机工作原理介绍:分析自动售货机的系统结构,包括投币模块、选择模块、出货模块等,让学生理解各个模块的功能和相互关系。

教材关联章节:第五章 数字电路设计与应用,第3节 自动售货机实例。

2. Verilog基础知识回顾:回顾Verilog的基本语法、数据类型、运算符等,为后续编程打下基础。

教材关联章节:第三章 Verilog语言基础,第1-3节。

3. 自动售货机控制逻辑设计:指导学生利用Verilog编写自动售货机的控制代码,包括投币、选择商品、出货等模块。

自动投币售货机的控制系统设计verilog

工学院二级项目报告二级项目题目:自动投币售货机的控制系统设计指导教师:系别:电子工程系专业:通信工程完成时间:2017年9月目录1. 项目内容与要求 (3)2. 画出投币售货机的控制系统的状态表,状态图,和状态编码方式 (4)3. 用Verilog实现售货机的控制系统描述,并进行仿真 (5)3.1 time.v (5)3.2 state.v (7)3.3 仿真 (10)4. 用C/C++语言实现售货机的有限状态机,并进行测试和仿真 (11)4.1 gcov代码 (11)4.2 仿真 (14)1. 项目内容与要求投币售货机的接收中国的硬币1元和5角,当售货机收到1.5元时出货,无法找零。

(1.5元可以是3个5角,或是1个1元和1个5角)项目以仿真形式完成。

1.画出投币售货机的控制系统的状态表,状态图,和状态编码方式。

2.用Verilog实现售货机的控制系统描述,并进行仿真。

要求仿真测试中给出Code Coverage数据,Code Coverage概念可见PDF 文档。

3.用C/C++语言实现售货机的有限状态机,并进行测试和仿真。

同样要求有测试的Code Coverage数据,具体的工具可用gcc自带的gcov或者是VC的coverage工具4.秋季学期开学前,每个小组需提交一份项目的报告,并作PPT陈述。

2.画出投币售货机的控制系统的状态表,状态图,和状态编码方式3.用Verilog实现售货机的控制系统描述,并进行仿真3.1 time.v`timescale 1ns/1nsmodule times;reg T;reg clk;reg reset;wire A;wire P;state FSM(T,reset,clk,A,P);initial beginreset=0;clk = 0;#80 reset=1;#20 $stop;endalways #10 clk=~clk; initial beginT=1;#20;T=1;#20;T=0;#20;reset=~reset;T=1; #20T=0;#20;endstate uut(.reset(reset),.clk(clk),.T(T),.A(A),.P(P));endmodule3.2 state.vmodule state(T,clk,reset,A,P);input T,clk,reset;output A,P;reg A,P;reg[2:0]y,Y;parameter[2:0] start=2'b000,half=2'b001,one=2'b010,reject=2'b011,paid=2'b100;always @(negedge reset or posedge clk)if(reset==0)y<=start;else y<=Y;//Define the next state always@(T or y) beginY = 3'b000 ;A=0;P=0;case(y)start:beginif(T) Y=one;else if(!T) Y=half;A=1;P=0;endhalf:beginif(T) Y=paid;else if(!T) Y=one;A=1;P=0;endone:beginif(T) Y=reject;else if(!T) Y=paid;A=1;P=0;endreject:beginif(T) Y=reject;else if(!T) Y=paid;A=0;P=0;endpaid:beginif(T) Y=one;else if(!T) Y=half;A=1;P=1;endendcaseendendmodule3.3 仿真4.用C/C++语言实现售货机的有限状态机,并进行测试和仿真4.1 gcov代码-: 0:Source:fsm.c-: 0:Graph:fsm.gcno-: 0:Data:fsm.gcda-: 0:Runs:10-: 0:Programs:1-: 1:#include <stdio.h>-: 2:-: 3:typedef enum //定义状态-: 4:{-: 5: START, //初始-: 6: STATE1, //收入0.5 RMB-: 7: STATE2, //收入1.0 RMB-: 8: REJECT, //找零-: 9: PAID, //出货-: 10:}STATE;-: 11:10: 12:int main()-: 13:{10: 14: int input = 0;10: 15: int input0 = 0; //投入零钱不符合要求时,用于保存原有数据10: 16: int a=1 ;-: 17:10: 18: STATE current_state = START;-: 19:116: 20: while(a<=1)-: 21: {-: 22:96: 23: switch(current_state) //状态转换情况-: 24: {-: 25: case START:-: 26:18: 27: input0 = input;18: 28: printf("accepting\n");18: 29: scanf("%d",&input);-: 30:-: 31:18: 32: if(input == 0)-: 33: {9: 34: current_state = STATE1;9: 35: printf("receive 0.5 RMB\n");-: 36: }9: 37: else if(input == 1)-: 38: {1: 39: current_state = STATE2;1: 40: printf("receive 1.0 RMB\n");-: 41: }-: 42: else-: 43: {8: 44: printf("error,return your money\n");8: 45: input = input0;-: 46: }18: 47: break;-: 48:-: 49: case STATE1:-: 50:23: 51: input0 = input;23: 52: printf("accepting\n");23: 53: scanf("%d",&input);-: 54:23: 55: if(input == 0)-: 56: {#####: 57: current_state = STATE2;#####: 58: printf("receive 1.0 RMB\n");-: 59: }23: 60: else if(input == 1)4.2 仿真输入1元,1元,售货机出货物,且找零输入2元,不符合投币要求,显示错误,退出程序此时代码覆盖率为62.30%,输入不同,代码率也会有所变化所能得到的最高代码覆盖率为95.08%,情况之一如下,输入2 0 1 1 1 1 0 0 2 1 2 最后三行为所生成文件。

基于FPGA自动售货机

摘要本课题是基于Verilog HDL语言的小型自动售货机。

采用Verilog HDL在ModelsimSE6.2B软件平台进行编译和仿真。

在此次设计中,主要采用有限状态机(FSM)的设计,在投币选货状态和找零状态在这两个状态间进行转移。

从而实现货物的选择、货币运算、出货控制、余额显示以及找零等功能。

该售货机系统能够识别两种硬币,两种纸币。

有五种不同价格的商品可供选择,并且通过显示译码电路,可在LED显示器显示余额,同时具备找零、机器存有硬币不足LED 亮起报警、缺货LED亮起报警等功能。

现代的自动售货机有使用方便快捷,可以全天候24小时工作,占地少,成本低,维护简单等优点,有着广阔的前景。

采用FPGA方式用Verilog HDL硬件描述语言,设计简易的自动售货机,其编程简单,开发周期短,硬件运行速度快,开发成本低,稳定性高等优点。

关键词:自动售货机; Verilog HDL;有限状态机;Modelsim;ABSTRACTThis topic design a simple vending machine is based on the FPGA chip. EP2C35 chip, and DE2 development board for the hardware platform, the use of Verilog HDL to compile and simulation in the Quartus Ⅱ software platform, and through the DE2 development achieve the basic functions of a Si mple vending machine.board by to download code to the chip. In this design,it used of finite state machine (FSM) design, choice of goods state, shipment status and give change coin state in the three inter-state transfer, in order to achieve the choice of goods, monetary operations, the cargo control, features such as display and give change. The vending machine system to identify three kinds of coins, there are five kinds of goods at different prices to choose from, and by showing decoding circuit, in DE2 onboard LED display shows the balance, both functions give change. Modern vending machines are convenient, it can work 24 hours a day, covers an area of small, low cost, simple maintenance, there are broad prospects. Manner with the use of FPGA hardware description language Verilog HDL, design simple vending machine, the programming is simple, short development cycles, fast hardware, the development of low cost, high stability.Key words: vending machines; Verilog HDL; Finite state machine; FPGA; DE2 development board;目录绪论..............................................................1 第一章系统方案设计...............................................31.1 人机交换界面设计..........................................31.2 系统方案设计..............................................41.2.1 系统方案确定..........................................5 第二章系统各模块硬件设计.........................................72.1 DE2开发板介绍.............................................72.2 自动售货机各模块设计.....................................82.2.1 自动售货机主体设计...................................82.2.2 LED显示设计方案.....................................92.2.3 货币输入信号设计方案................................102.2.4 出货显示设计方案....................................11 第三章系统的软件设计............................................123.1 EDA工具软件介绍.........................................133.2 软件设计总方案...........................................143.3 售货机主芯片程序设计方案................................153.4 BCD-LED七段数码显示译码器...............................173.5 硬币输入信号程序设计方案................................183.6 出货显示程序设计方案....................................193.7 自动售货机各部分组合连接设计............................20 第四章调试及仿真...............................................214.1 用Quartus Ⅱ完成PFGA设计步骤...........................214.2 自动售货机波形仿真结果..................................214.2.1 自动售货机波形仿真..................................214.2.2 输入信号处理程序波形仿真............................234.2.3 BCD-LED七段数码显示译码器波形仿真..................234.2.4 出货显示译码器波形仿真..............................244.2.5 自动售货机主芯片程序仿真波形.......................254.3 下载、仿真及测试..........................................25 结论..............................................................26 致谢.............................................................27 参考文献..........................................................28 附录1(程序源代码)...............................................29 附录2(整体设计原理图)...........................................35绪论自动售货机最早出现在二十世纪五、六十年代的西欧,英国是较早实行自动售货机售货的国家之一。

SOC设计实验报告

Operating Conditions: cb13fs120_tsmc_max Library: cb13fs120_tsmc_max

Wire Load Model Mode: Inactive.

Startpoint: state_reg[0]

begin

state<=st1;

end

end

end

st2:

begin

if(five==1)

begin

state<=st3;

end

else

begin

if(ten==1)

begin

state<=st3;

end

else

begin

state<=st2;

end

end

end

st3:

begin

state<=st0;

reg five_cents,ten_cents;

wire soda_out;

always #1 clk=~clk;

initial

begin

clk=0;

five_cents=0;

ten_cents=0;

rst_n=1;

#10 rst_n=0;

#10 rst_n=1;

rtl/

#读文件

Link

#连接到目标库

如果通过了偶校验则进入evenblank状态来使pcm30空缺248位,此时进入帧校验的奇校验;

帧校验的奇校验使用三个状态来完成,分别为:oddhold0,oddhold1,oddhold2来校验奇帧的1、2、3位;

Verilog实现自动售货机

东华理工大学EDA课程设计报告课程设计题目:自动售货控制系统设计学院机械与电子工程学院学生姓名王磊班级080612学号********指导老师黄乡生(教授)2011年6月18日摘要本设计是以现场可编程逻辑器件(FPGA)为核心的自动售货机,利用QuartusII软件编写verilog HDL 硬件描述语言程序以实现自动售货功能。

本程序要求能够完成对货物信息的存取,硬币处理,余额计算,取消购物时退款和显示功能。

关键字:FPGA、Verilog HDL、自动售货机、QuartueIIAbstractThis design is an auto-vendingmachine based on field programmavle logic devices(FPGA).We use QuartusII to write procedure in verilog HDL which is a language to describe hardware.The procedure will realize the function of auto-vending machine.Keywords:FPGA、Verilog HDL、auto-vending machine、QuartueII一、设计要求设计一个自动售货控制系统,它能够完成对货物信息的存取,硬币处理余额计算,取消购物时退款和显示等功能。

(1)假定自动售货机可以出售四种货物,每种商品的数量和单价在初始化时设定,并存储在存储器中。

(2)采用模拟开关信号模拟5角和1元硬币购物,并通过按键选择所需商品。

(3)系统能够根据用户输入的硬币,判断累计货物是否足够,当所投硬币累计达到或者超过购买者所选商品价格时,则根据顾客的要求自动售货,并找回剩余的硬币,然后回到初始状态。

当所投硬币不够时,则给出提示,并通过一个复位键退回所有硬币,然后回到初始状态。

二、设计提示系统框图如下:系统按功能可以分为信号输入、控制器、译码显示等模块。

基于VerilogHDL的自动售货机设计

密级:NANCHANG UNIVERSITY学士学位论文THESIS OF BACHELOR(2012 —2016年)题目基于Verilog HDL的自动售货机设计学院:信息工程学院系电子信息工程系专业班级:学生XX:学号:指导教师:职称:教授起讫日期:2016.3.14——2016.6.3基于Verilog HDL的自动售货机设计专业:电子信息工程学号:6100212164学生XX:田启泽指导教师:陶凌摘要自动售货机是商业自动化的常用设备,它不受地点和时间的限制,能够支持线上,线下多种支付方式,出货迅速,并且操作简单方便,因此受到了社会各群体的欢迎。

现目前自动售货机多为单片机设计,常出现因功能单一不能满足顾客需求,性能不稳定带来各种售货出错等现象。

本文将论述采用EDA方法,以QuartusⅡ为软件开发平台,使用Verilog HDL语言设计,经过仿真后,在FPGA器件中实现自动售货机系统的详细流程。

经过仿真验证设计可以实现投币计次,两种售价均为两元的商品选择,购物操作无条件取消,按键消抖,以及投币退币数量显示功能。

硬件电路用一个按键电路实现投币功能,以led的点亮的数量指示投币的数量和商品出货情况,并以七段数码管显示退币的数量。

关键词:自动售货机;Verilog HDL;FPGA;EDA;Quartus ⅡDesign of Vending Machine Based on VHDLAbstractVending machines are monly used as mercial automated equipment, it is not restricted some trouble aspects,such as place,time and so on. It support online, offline payment methods, fast shipping, and easy operation, therefore has been weled by all social groups. Vending machines are currently a mostly single-chip design, often due to a single function can not meet customer needs, bring a variety of sales performance problems due to unstable capability.This article will discusses the selling process of the vending machine by using QuartusⅡas software development platform, with the EDA method and through Verilog HDL language designing, after simulating, plying vending machine system in FPGA devices. After simulation designed it can be achieved coin metering and selection of modities both are priced at two yuan, unconditionally canceled, key debounce and coin-coin number display. Hardware circuit using a function key circuits replays coin-operated,the number of led lights indicates the number of shipments of goods and coin, and using seven-segment LED to display the number of coin return. Keywords: vending machine;Verilog HDL;FPGA;EDA;Quartus Ⅱ目录摘要ⅠAbstract (Ⅱ)第一章绪论错误!未定义书签。

基于Verilog HDL的自动售货机设计与仿真

电子技术Electronic Technology电子技术与软件工程Electronic Technology & Software Engineering 基于Verilog H D L的自动售货机设计与仿真李红科王庆春贾晓菲(安康学院电子与信息工程学院陕西省安康市725000 )摘要:本文应用Verilog H D L语言采用自顶而下的方法设计自动售货机,整个系统包括商品选择、确认、投币、找零和出货等模块。

在Modelsim平台进行功能仿真验证,经过仿真验证设计正确,符合设计要求。

关键词:Verilog H D L;自动售货机;模块设计1引言随着集成电路产业快速发展,电路集成度越来越高,以计算机辅助为基础的电子设计自动化(EDA Electronics Design Automation)技术成为集成电路设计重要工具m,Verilog HDL硬件描述语言是以文字形式描述数字系统硬件电路结构和行为的语言,只需描述电路的功能和电路模块之间的相互关系,设计者更加专注电路设计整体性能,使电路更加优化,提高设计效率|21。

自动售货机是一种常见的智能自动化设备,由于不受人直接参与,所以广泛应用在办公楼、操场、高速服务K等场所,大大降低时间、地点的限制,在节省人力资源方面有着明显优势。

2自动售货机设计思路有限状态机(FSM Finite-state Machine)是•种用来进行对象行为建模的工具,其作用是表示有限个状态以及这些状态之间相互转移和动作等行为的数学模型。

有限状态机广泛应用于建模行为、硬件电路设计、软件工程和网络协议等的设计。

在数字系统设计中,当某一事物发生连续变化时,可以采用有限状态机设计思路提高设计效率,增加程序可读性,降低错误概率,有限状态机设计思路是数字系统中最常用的设计方法之一 [3]。

2.1自动售货机系统总体设计该售货机电路设计要求:(1)每次只能出售一种商品。

(2)所售商品种类:售货机只售4种商品,所售商品编号分 别用四位二进制数从右向左表示为0001、0010、0100、1000,对应价格分别为2元、3元、4元、5元。

基于Verilog HDL自动售货机系统设计

De i n o n i g M a h n y t m s d o rl g HDL n u g sg fVe d n c i e S se Ba e n Ve i o La g a e

ZHANG . r Ke e

( ol eo l t c l n ier g L n D n nvr t , ig a g7 5 0 G nu C l g E e r a gn ei , o g o g U i s y Q n y n 4 0 0, a s ) e f ci E n ei

第2 卷 第5 3 期 21 年 9 02 月

文章编 号 :6 41 3 ( 0 2 0 -0 30 1 7 —7 0 2 1 )50 0 -6

陇东学院学报

J ma o ogog n e i o l f ndn U i rt u L v sy

V0. 3 N . 12 o 5

Ab ta t sr c :Ve io r wa e d s rp in ln u g s u e o i i ls se mo e i rlg Ha d r e c to a g a e i s d frd g t y t m d l i a ng,i l d n lo t m ncu i g a g r h i lv la a e l v la l s s th l v 1 By d b g ig t e h r wa e c rui,we c n r du e h r wae e e nd g t e e swela wic e e . e u gn h a d r ic t a e c a d r d v lp n y l n o t Th a e n r d c st e t r sa d a p iai n o rlg HDL,a d tkig e eo me tc c ea d c s. e p p ri to u e hef au e n p lc t fVe i o o n a n t e in o e d n c n s a x mp e,i u ta e n d ti isd sg r c s ,c d sben ie . he d sg fv n i g ma hie a n e a l l sr ts i e al t e in p o e s o e i g g v n l T e v ld t ft e d sg s p o e y tmi i l t n wa eoT . h a i i o h e in i r v d b i ng smu ai v f In y o

简单自动售货机VerilogHDL程序

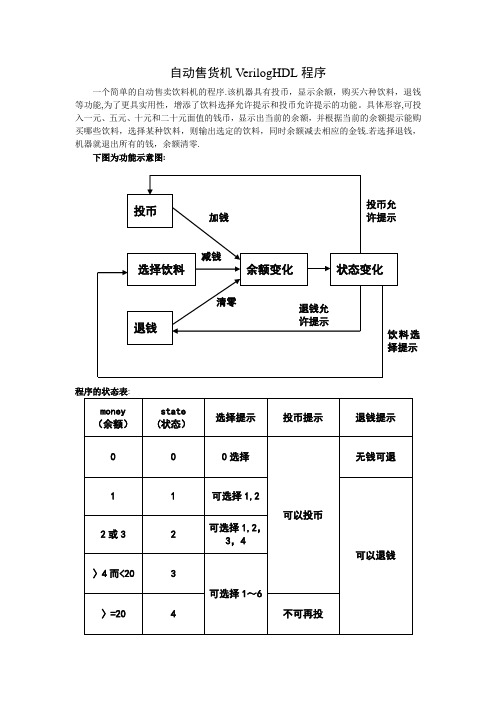

自动售货机VerilogHDL程序一个简单的自动售卖饮料机的程序.该机器具有投币,显示余额,购买六种饮料,退钱等功能,为了更具实用性,增添了饮料选择允许提示和投币允许提示的功能。

具体形容,可投入一元、五元、十元和二十元面值的钱币,显示出当前的余额,并根据当前的余额提示能购买哪些饮料,选择某种饮料,则输出选定的饮料,同时余额减去相应的金钱.若选择退钱,机器就退出所有的钱,余额清零.下图为功能示意图:程序的状态表:程序中包含了一个状态机,定义了一个任务(task)和函数(function),用该任务调用了该函数,使用若干分支语句,详见附后源程序和测试程序。

附上程序编译仿真图:源程序如下:`define one 3'b001`define five 3'b010`define ten 3'b011`define twenty 3’b100module automart(money,state,moneyout,coinable,adrkable,bdrkable,cdrkable,drkout1,drkout2,drkout3,drkout4,drkout5,drkout6,coin,clk,reset,moneyback,choice1,choice2,choice3,choice4,choice5,choice6);input[2:0]coin;//投币输入,分为1、5、10、20元四种输入input clk,reset,moneyback,choice1,choice2,choice3,choice4,choice5,choice6;//moneyback为退钱输入,choice1~6是饮料选择output moneyout,coinable,adrkable,bdrkable,cdrkable,drkout1,drkout2,drkout3,drkout4,drkout5,drkout6;//依次为退钱输出,投币许可提示,饮料选择许可,6种饮料输出output[2:0] state;//状态记录output[7:0] money;//余额显示reg[7:0] money;reg[2:0] state;reg moneyout,coinable,backable,adrkable,bdrkable,cdrkable; parameter A=3'b000,B=3'b001,C=3'b010,D=3'b011,E=4’b100;assign drkout1=choice1&adrkable;assign drkout2=choice2&adrkable;assign drkout3=choice3&bdrkable;assign drkout4=choice4&bdrkable;assign drkout5=choice5&cdrkable;assign drkout6=choice6&cdrkable;always@(posedge clk)repeat(1)@(posedge clk)if (!reset)beginstate<=A;money=0;moneyout=0;endelsebegincase(state)A:begin//初始状态A,可投币进入别的状态coinable=1;backable=0;adrkable=0;bdrkable=0;cdrkable=0;endB: begin//状态B,只能买1元的饮料,可退钱或投币coinable=1;backable=1;adrkable=1;bdrkable=0;cdrkable=0;endC: begin//状态C,可买1或2元的饮料,退钱或投币coinable=1;backable=1;adrkable=1;bdrkable=1;cdrkable=0;endD:begin//状态D,可买三档价格饮料,可退钱或投币coinable=1;backable=1;adrkable=1;bdrkable=1;cdrkable=1;endE:begin//状态E,可买三档价格饮料,可退钱,不可继续投钱coinable=0;backable=1;adrkable=1;bdrkable=1;cdrkable=1;enddefault: state=A;endcasecondition(money,state,coin,coinable);//调用任务endalways@(negedge drkout1 or negedge drkout2)money=money—8’h01;//买1元的饮料,余额减1元always@(negedge drkout3 or negedge drkout4)money=money—8'h02;//买2元的饮料,余额减2元always@(negedge drkout5 or negedge drkout6)money=money—8'h04;//买4元的饮料,余额减4元always@(negedge moneyback)beginif(backable)beginmoneyout=1;money=0;//选择退钱,则推出金钱,余额清零endelsemoney=money+0;endtask condition;//该任务可以判断余额的改变,状态切换inout[7:0] moneycon;inout[2:0] statecon;input[2:0] coincon;input coinablecon;beginif (coinablecon)//允许投币时begincase (coincon)//根据投币面值改变余额,切换状态`one : moneycon=moneycon+8'h01;`five :moneycon=moneycon+8'h05;`ten : moneycon=moneycon+8'h0a;`twenty :moneycon=moneycon+8'h14;default:moneycon=moneycon+0;//无投币则余额不变endcasestatecon=condition_s(moneycon);//调用函数endelse if (moneycon〈8’h14)//不允许投币时,根据余额变化statecon=condition_s(moneycon);//直接切换状态endendtaskfunction [2:0] condition_s;//根据余额的值切换状态的函数input [7:0] money_s;reg [7:0]money_s;beginif (money_s==0)condition_s=A;else if(money_s==8’h01)condition_s=B;else if(money_s==8’h02||money_s==8’h03)condition_s=C;else if(money_s〉=8’h04&&money_s〈8’h14)condition_s=D;else condition_s=E;endendfunctionendmodule测试程序如下:`timescale 100ns/1ns`define clk_cycle 50module test;reg moneyback,choice1,choice2,choice3,choice4,choice5,choice6; reg [2:0] coin;reg clk,reset;wire[7:0] money;wire[2:0]state;wire moneyout,coinable,adrkable,bdrkable,cdrkable,drkout1,drkout2,drkout3,drkout4,drkout5,drkout6;parameter one=3’b001,five=3’b010,ten=3'b011,twenty=3'b100;always #`clk_cycle clk= ~clk;initialbegincoin=0;moneyback=0;clk=0;choice1=0;choice2=0;choice3=0;choice4=0;choice5=0;choice6=0;reset=1;#10 reset=0;#200 reset=1;#400 coin=one;//投币1元,#220 coin=0;#200 coin=one;//投1元,余额2元#220 coin=0;#200 coin=five;//投5元,余额7元#220 coin=0;#200 coin=twenty;//投20元,余27#220 coin=0;#200 choice1=1;//买1元饮料,余26#220 choice1=0;#200 choice3=1;//买2元饮料,余24#220 choice3=0;#200 choice4=1;//买2元饮料,余22#220 choice4=0;#200 choice5=1;//买4元饮料,余18#220 choice5=0;#200 choice6=1;//买4元饮料,余14#220 choice6=0;#200 choice6=1;//买4元饮料,余10#220 choice6=0;#200 choice6=1;//买4元饮料,余6#220 choice6=0;#200 choice6=1;//买4元饮料,余2#220 choice6=0;#200 coin=five;//投5元,余7#220 coin=0;#200 moneyback=1;//退钱#220 moneyback=0;endautomart m(.money(money),。

基于Verilog HDL自动售货机系统设计

基于Verilog HDL自动售货机系统设计

张可儿

【期刊名称】《陇东学院学报》

【年(卷),期】2012(023)005

【摘要】Verilog硬件描述语言用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模,并通过仿真软件完成硬件电路的调试,使得硬件开发周期和成本降低.介绍了Verilog HDL的特点和应用,并以自动售货机的设计为例,详细地说明了它的设计过程,并给出了代码,通过时序仿真波形证明设计的正确性.

【总页数】6页(P3-8)

【作者】张可儿

【作者单位】陇东学院电气工程学院,甘肃庆阳745000

【正文语种】中文

【中图分类】TP311.51

【相关文献】

1.基于Verilog-HDL的现代数字系统设计 [J], 郑汉尚

2.基于Verilog HDL的管道压力自测装置系统设计 [J], 李辉;朱改博

3.基于Verilog HDL的FPGA数字系统设计优化 [J], 李桂林;苗长新

4.基于Verilog HDL的自动售货机设计与仿真 [J], 李红科;王庆春;贾晓菲

5.基于Verilog HDL的电梯系统设计 [J], 吴海生;沈建华

因版权原因,仅展示原文概要,查看原文内容请购买。

用verilog编写16位加法器乘法器自动售货机

Verilog课程实验报告实验1十六位超前进位加法器1.1系统设计要求用超前进位加法器实现一个有符号位的16位加法器,并且考虑溢出的情况2.1详细设计根据超前进位加法器的原理Co = G | ( P & Ci ) S = P ^ Ci 设计出4位加法器的子模块,然后通过4个4位加法器的相连来得到十六位的加法器。

原理如下图所示。

溢出用flag=0表示。

3.1程序//-------------16位超前进位加法器-----------------module cla16(a,b,s,flag); //含有a ,b ,输出s ,进位flag 的模块 input [15:0] a,b;//输入a ,b output [16:0] s; //输出 s output reg flag; //进位FA FA FA FAP 0G 1P 0G 1P 2G 2P 3G 3C o,3C o,2C o,1C o,0C i,0FA FA FA FAP 0G 1P 0G 1P 2G 2P 3G 3C o,2C o,1C o,0C i,0C o,3M u l t i p l e x e rBP=P o P 1P 2P 3Idea: If (P0 and P1 and P2 and P3 = 1)then C o3 = C 0, else “kill” or “generate”.wire pp4,pp3,pp2,pp1;wire gg4,gg3,gg2,gg1;wire [15:0] Cp;wire [15:0] p,g;pg i0 (a[15:0],b[15:0],p[15:0],g[15:0]);add i1 (p[3],p[2],p[1],p[0],g[3],g[2],g[1],g[0],pp1,gg1);add i2 (p[7],p[6],p[5],p[4],g[7],g[6],g[5],g[4],pp2,gg2);add i3 (p[11],p[10],p[9],p[8],g[11],g[10],g[9],g[8],pp3,gg3);add i4 (p[15],p[14],p[13],p[12],g[15],g[14],g[13],g[12],pp4,gg4);add i5 (pp4,pp3,pp2,pp1,gg4,gg3,gg2,gg1,pp5,gg5);//调用四位加法器模块add4 l0 (p[3],p[2],p[1],p[0],g[3],g[2],g[1],g[0],1'b0,Cp[3],Cp[2],Cp[1],Cp[0]);add4 l1 (p[7],p[6],p[5],p[4],g[7],g[6],g[5],g[4],Cp[3],Cp[7],Cp[6],Cp[5],Cp[4]);add4 l2 (p[11],p[10],p[9],p[8],g[11],g[10],g[9],g[8],Cp[7],Cp[11],Cp[10],Cp[9],Cp[8]);add4 l3 (p[15],p[14],p[13],p[12],g[15],g[14],g[13],g[12],Cp[11],Cp[15],Cp[14],Cp[13],Cp[12]); assign s[0]=p[0]^1'b0; //保留位assign s[1]=p[1]^Cp[0];assign s[2]=p[2]^Cp[1];assign s[3]=p[3]^Cp[2];assign s[4]=p[4]^Cp[3];assign s[5]=p[5]^Cp[4];assign s[6]=p[6]^Cp[5];assign s[7]=p[7]^Cp[6];assign s[8]=p[8]^Cp[7];assign s[9]=p[9]^Cp[8];assign s[10]=p[10]^Cp[9];assign s[11]=p[11]^Cp[10];assign s[12]=p[12]^Cp[11];assign s[13]=p[13]^Cp[12];assign s[14]=p[14]^Cp[13];assign s[15]=p[15]^Cp[14];assign s[16]=pp5|gg5;//溢出判断模块always@(a,b,s)beginif ((a[15]==1&&b[15]==1&&s[15]==0)||(a[15]==0&&b[15]==0&&s[15]==1))flag=1'b1;elseflag=1'b0;endendmodule//4位加法器模块module add4(p[3],p[2],p[1],p[0],g[3],g[2],g[1],g[0],Co,Cp[3],Cp[2],Cp[1],Cp[0]);input [3:0]p,g;output [3:0] Cp;assign Cp[0]=g[0]|p[0]&Co;assign Cp[1]=g[1]|p[1]&Cp[0];assign Cp[2]=g[2]|p[2]&Cp[1];assign Cp[3]=g[3]|p[3]&Cp[2];endmodule//模块间的进位module add(p[3],p[2],p[1],p[0],g[3],g[2],g[1],g[0],pp,gg); input [3:0]p,g;output pp,gg;assign pp=p[3]&p[2]&p[1]&p[0];assign gg=g[3]|(p[3]&(g[2]|p[2]&(g[1]|p[1]&g[0]))); endmodule//进位信号的产生module pg(a,b,p,g);input [15:0] a,b;output [15:0] p,g;assign p=a^b;assign g=a&b;endmodule4.1测试程序通过产生一个随机输入a和b,来验证c=a+b。

HDL(Verilog)课程设计报告(自动售货机)

HDL(Verilog)课程设计报告(自动售货机)摘要本设计是以现场可编程逻辑器件(FPGA)为核心的自动售货机,利用QuartusⅡ软件编写verilog HDL 硬件描述语言程序以实现自动售货功能。

本设计主要以程序为主,硬件方面则使用实验箱,将程序各变量端口与实验箱管脚进行相应的配置,用八个开关分别代表商品价格、所投钱币价格及确认付款找零操作。

当选择好商品并投币后,数码管显示所选商品价格及投入钱币价格;按下确认付款开关,数码管显示应找多少钱,蜂鸣器响,对应商品LED灯亮。

若所投钱币不足所选商品价格,对应警告钱币不足的LED灯亮。

关键字:FPGA、Verilog HDL、自动售货机、Quartus ⅡAbstractThis design is an auto-vending machine based on field programmable logic devices (FPGA) . We use QuartusⅡto write procedure in verilog HDL which is a language to describe hardware. The procedure will realize the function of auto-vending machine.This design is mainly about procedure. For the hardware, we use experimental box. We allocate all variable quantities in the procedure to the feet in experimental box. We use eight switch respectively represent commodity prices and throw money price and confirm payment change operation. When choosing good commodities and coin, digital pipe display selected commodity prices and money price. When pressing confirm payment switch, digital pipe display should find how much money, buzzer sounded, corresponding commodity LED lights. If throw money shortage selected commodity prices, corresponding warning money shortage of LED lights.Keywords: FPGA、Verilog HDL、auto-vending machine、QuartusⅡ目录摘要 I第一章系统设计 11.1 系统设计 11.2 系统设计方案比较 11.2.1 总体设计 11.2.1 设计方案比较 1第二章详细设计 22.1 自动售货机状态描述 22.2 详细状态描述 32.2.1 初始状态 32.2.2 选商品状态 32.2.3 投币状态 32.2.4 找零状态 3第三章软件设计 33.1 程序总流程图 33.2 程序 4第四章结果与讨论 74.1 实验调试 74.1.1 调试步骤 74.1.2 实验现象 74.2 结果与分析 8总结 8参考文献 8附录 9第一章系统设计1.1系统设计(1)用四个发光二极管分别模拟售出价值为5角、1元、1.5元和2元的小商品,购买者可以通过开关选择任意一种标价中的小商品。

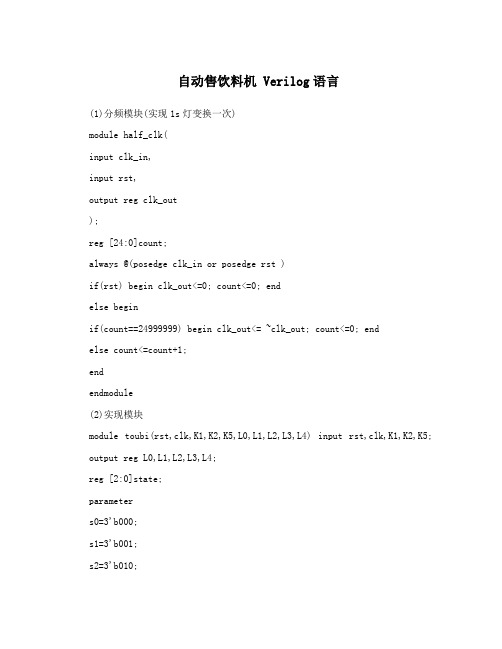

自动售饮料机 Verilog语言

自动售饮料机 Verilog语言(1)分频模块(实现1s灯变换一次)module half_clk(input clk_in,input rst,output reg clk_out);reg [24:0]count;always @(posedge clk_in or posedge rst )if(rst) begin clk_out<=0; count<=0; endelse beginif(count==24999999) begin clk_out<= ~clk_out; count<=0; endelse count<=count+1;endendmodule(2)实现模块module toubi(rst,clk,K1,K2,K5,L0,L1,L2,L3,L4) input rst,clk,K1,K2,K5; output reg L0,L1,L2,L3,L4;reg [2:0]state;parameters0=3'b000;s1=3'b001;s2=3'b010;s3=3'b011;s4=3'b100;always @(posedge clk or posedge rst)if(rst) begin state<=s0;L0<=0;L1<=0;L2<=0;L3<=0;L4<=0; end else case(state)s0:if(k1==1) beginstate<=s1;L0<=0;L1<=0;L2<=0;L3<=0;L4<=0; endelse if(k2==1) beginstate<=s2;L0<=0;L1<=0;L2<=0;L3<=0;L4<=0; endelse if(k5==1) beginstate<=s0;L0<=1;L1<=0;L2<=0;L3<=0;L4<=0; end s1:if(k1==1) begin state<=s2;L0<=0;L1<=0;L2<=0;L3<=0;L4<=0; endelse if(k2==1) beginstate<=s4;L0<=0;L1<=0;L2<=0;L3<=0;L4<=0; endelse if(k5==1) beginstate<=s0;L0<=1;L1<=1;L2<=0;L3<=0;L4<=0; end s2:if(k1==1) begin state<=s3;L0<=0;L1<=0;L2<=0;L3<=0;L4<=0; endelse if(k2==1) beginstate<=s4;L0<=0;L1<=0;L2<=0;L3<=0;L4<=0; endelse if(k5==1) beginstate<=s0;L0<=1;L1<=0;L2<=1;L3<=0;L4<=0; end s3:if(k1==1) begin state<=s4;L0<=0;L1<=0;L2<=0;L3<=0;L4<=0; endelse if(k2==1) beginstate<=s0;L0<=1;L1<=0;L2<=0;L3<=0;L4<=0; endelse if(k5==1) beginstate<=s0;L0<=1;L1<=0;L2<=0;L3<=1;L4<=0; end s4:if(k1==1) begin state<=s0;L0<=1;L1<=0;L2<=0;L3<=0;L4<=0; endelse if(k2==1) beginstate<=s0;L0<=1;L1<=1;L2<=0;L3<=0;L4<=0; endelse if(k5==1) beginstate<=s0;L0<=1;L1<=0;L2<=0;L3<=0;L4<=1; endendcaseendmodule(3)top模块module toubitop(input rst,clk,K1,K2,K5;output reg L0,L1,L2,L3,L4;);wire clk_out;half_clk A1(clk,rst,clk_out);toubi A2(clk_out,rst,K1,K2,K5,L0,L1,L2,L3,L4); endmodule(4)测试模块`timescale 1ms / 1ms//////////////////////////////////////////////////////////////////// ////////////// Company:// Engineer://// Create Date: 15:02:00 12/10/2013// Design Name: toubitop// Module Name: D:/Xilinx/shiyan2/kkk/test.v// Project Name: kkk // Target Device: // Tool versions: // Description: //// Verilog Test Fixture created by ISE for module: toubitop//// Dependencies: //// Revision:// Revision 0.01 - File Created// Additional Comments: ////////////////////////////////////////////////////////////////////// ////////////module test;// Inputsreg clk;reg rst;reg K1;reg K2;reg K5;// Outputswire L0;wire L1;wire L2;wire L3;wire L4;// Instantiate the Unit Under Test (UUT) toubitop uut (.clk(clk),.rst(rst),.K1(K1),.K2(K2),.K5(K5),.L0(L0),.L1(L1),.L2(L2),.L3(L3),.L4(L4));always #500 clk=~clk;initial begin// Initialize Inputsclk = 0;rst = 0;K1 = 0;K2 = 0;K5 = 0;// Wait 100 ns for global reset to finish#100 rst=1;#100 rst=0;#1000 K1=1;#1000 K1=0;#1000 K1=1;#1000 K1=0;#1000 K2=1;#1000 K2=0;#1000 K2=1;#1000 K2=0;// Add stimulus here endendmodule。

自动售货机 verilog

SOPC及EDA技术课程结业报告题目:基于状态机的自动售货机设计院(系)电气工程及其自动化姓名学号班号基于状态机的自动售货机设计一.实验目的1. 学习FPGA入门知识,了解FPGA的编程形式;2. 掌握Quartus II的使用步骤;3. 掌握基于状态机原理的自动售货机设计过程。

二.实验原理自动售货机是可完成无人自动售货,集光、机、电一体化的商业自动化设备。

自动售货机不受任何场地限制,方便快捷,可以每天24小时售货,因此深受上班族的欢迎,很多城市的公共场所里面都放置有自动售货机,出售的商品五花八门,从饮料、零食、香烟、糖果,到牙刷、方便面、自动照相机。

近年来,我国的自动售货机行业突飞猛进:在汽车总站、商厦、医院、小区、学校等地区纷纷涌现出自动售货机的踪迹。

这种方便快捷的购物方式越来越受到人们的青睐,同时也是现代化城市配套设施的需求。

因为自动售货机作为社会上完成商品零售和综合服务的独立设施,所以必须要求它的结构可靠、稳定而且执行效率高。

传统的自动售货机控制系统采用单片机作为控制核心,这样不仅会在输入输出接口上做大量的工作,而且系统的抗干扰性也比较差。

可编程控制器(Programmable Logical Controller,简称PLC)是综合了计算机技术、自动控制技术和通讯技术而发展起来的一种新型的工业控制装置,它具有可靠性高、编程简单、维护方便等优点,已在工业控制领域得到广泛地应用。

PLC是以CPU为核心, 综合了计算机技术和通信技术发展起来的一种通用的工业自动控制装置, 是现代工业控制的三大支柱(PLC、机器人和CAD/CAM) 之一。

PLC的工作原理与计算机的工作原理基本是一致的, 可以简单地表述为在系统程序的管理下, 通过运行应用程序完成用户任务。

但是PLC也有它自己的特点, PLC在确定了工作任务, 装入了专用程序后成为一种专用机, 它采用循环扫描工作方式, 系统工作任务管理及应用程序执行都是用循环扫描方式完成的。

verilog自动售货机资料

齐齐哈尔大学SOPC课程设计(论文)题目:饮料自动提取机的设计院(系):通信与电子工程学院专业班级:电子091学号: **********学生姓名:**指导教师:**起止时间:2011.12.19-2011.12.30摘要饮料自动售货机是台机电一体化的自动化装置,再接收到货币已输入的前提下,靠触摸控制按钮输入信号使控制器启动相关位置的机械装置完成规定动作,将货物输出。

当顾客按下需要买的商品所对应的按键时,数码管上显示出该商品的的价格,然后顾客需要将货币投入投币口,数码管上显示出所投币额。

当按下确认键,则自动售货机将对投入的货币与商品的价格进行比较。

如果投入的币额足够时,则自动送出商品,并且把多余的钱找回,在数码管上显示出来。

本课程设计设想采用专用集成电路芯片实现饮料自动提取机的功能。

在本次设计中,系统开发平台为Quarter2,硬件描述语言是VerilogHDL。

设计方案中,售货机具备硬币识别及找零功能,并能完成四种商品的出售。

依据设计方案和设计平台完成了程序编写和程序调试,通过运行程序及时序波形的仿真有效验证了设计的正确性,初步实现了设计目标。

关键词: 自动售货机 VerilogHDL QuarterⅡ目录第1章绪论 (1)1.1饮料自动提取机概况 (1)1.2本文研究内容 (2)1.3目的与意义 (2)第2章系统设计方案 (3)2.1饮料自动提取机总体设计方案 (3)2.2系统的参数 (4)第3章饮料自动提取机的基本原理 (5)3.1饮料自动提取机功能 (5)3.2饮料自动提取机的基本组成 (5)3.2.1 投币信号产生的设计 (5)3.2.2 时钟电路的设计 (5)3.2.3 数码显示的设计 (6)第4章饮料自动提取机软件设计 (7)4.1软件实现功能综述 (7)4.2计数功能的设计 (7)4.2.1 计数功能接口电路 (7)4.2.2 计数功能程序设计 (7)4.3投币功能的设计 (8)4.3.1 投币功能的接口电路 (8)4.3.2 投币功能程序设计 (8)4.4显示功能的设计 (9)4.4.1 显示功能的接口电路 (9)4.4.2 显示功能程序设计 (9)4.5显示功能的设计 (12)4.5.1 显示功能的接口电路 (12)4.5.2 显示功能程序设计 (12)第5章饮料自动提取机系统的仿真分析 (14)5.1系统原理图 (14)5.2计数功能的仿真分析 (14)5.3投币功能的仿真分析 (15)5.4取货功能的仿真分析 (15)5.5总体功能的仿真分析 (16)第6章课程设计总结 (18)参考文献 (19)第1章绪论1.1饮料自动提取机概况近年来,集成电路技术的迅猛发展,特别是可编程逻辑器件的高速发展,电子设计自动化EDA技术成为电子设计工程师的新宠。

自动售饮料机销售verilog设计

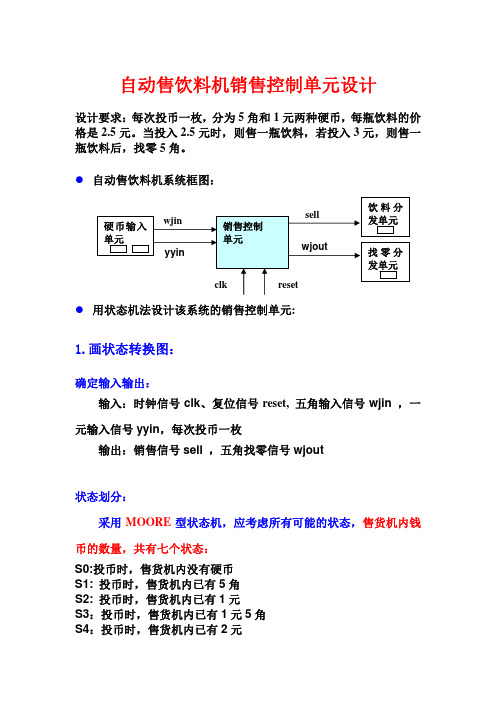

自动售饮料机销售控制单元设计设计要求:每次投币一枚,分为5角和1元两种硬币,每瓶饮料的价格是2.5元。

当投入2.5元时,则售一瓶饮料,若投入3元,则售一瓶饮料后,找零5角。

●自动售饮料机系统框图:●用状态机法设计该系统的销售控制单元:1.画状态转换图:确定输入输出:输入:时钟信号clk、复位信号reset, 五角输入信号wjin ,一元输入信号yyin,每次投币一枚输出:销售信号sell ,五角找零信号wjout状态划分:采用MOORE型状态机,应考虑所有可能的状态,售货机内钱币的数量,共有七个状态:S0:投币时,售货机内没有硬币S1: 投币时,售货机内已有5角S2: 投币时,售货机内已有1元S3:投币时,售货机内已有1元5角S4:投币时,售货机内已有2元S5:投币时,售货机内已有2元5角S6:投币时,售货机内已有3元说明:箭头上的参数表示输入信号:wjin yyin 圈里的参数表示:状态/sell wjout2. 状态编码:S0=3`b000;S1=3`b001;S2=3`b011;S3=3`b010;S4=3`b110;S5=3`b111;S6=3`b101:3.用Verilog_HDL对状态转换图进行描述描述方式:将CS 、NS、OL混合描述。

销售控制单元的Verilog_HDL程序:module auto_sell(wjin,yyin,clk,reset,sell,wjout);input clk,reset; //时钟、复位信号input wjin,yyin; //输入output sell,wjout; //输出reg sell,wjout;reg current_state; //现态寄存器parameter S0=3`b000;S1=3`b001;S2=3`b011;S3=3`b010;S4=3`b110;S5=3`b111;S6=3`b101;//状态编码always @(posedge clk or posedge reset)beginif (reset)s0;current_state=else(current_state)caseS0://0yuanbeginsell=0;wjout =0;if(wjin) current_state = S1;else if(yyin) current_state= S2;endS1://0.5yuanbeginsell=0;wjout =0;if(wjin) current_state= S2;else if(yyin) current_state= S3;endS2://1yuanbeginsell=0;wjout =0;if(wjin) current_state= S3;else if(yyin) current_state=S4;endS3: //1.5yuanbeginsell=0;wjout =0;if(wjin) current_state= S4;else if(yyin) current_state= S5;endS4://2yuanbeginsell=0;wjout =0;if(wjin) current_state= S5;else if(yyin) current_state=S6;endS5://2.5yuanbeginsell=1;wjout =0;if(wjin) current_state= S1;else if(yyin) current_state=S2;endS6://3yuanbeginsell=1; wjout =1;if(wjin) current_state= S1;else if(yyin) current_state=S2;enddefault: begin current_state= S0; sell=0;wjout =0; endendcaseendendmodule若用带流水线的MEALY型状态机实现:状态划分:可划分成五种状态:S0: 投币时,售货机内没有硬币S1: 投币时,售货机内已有5角S2: 投币时,售货机内已有1元S3:投币时,售货机内已有1元5角S4:投币时,售货机内已有2元说明:箭头上的参数表示wjin yyin/sell wjoutS0=0;S1=1;S2=2;S3=3;S4=4;3.用 Verilog_HDL对状态转换图进行描述描述方式:将CS 、NS、OL混合描述。

Verilog语言的自动售货机

完成时间:2010/7/30word格式-可编辑-感谢下载支持一、实验目的1)设计一个自动售货机,此机能出售1元、2元、5元、10元的四种商品。

出售哪种商品可有顾客按动相应的一个按键即可,并同时用数码管显示出此商品的价格。

2)顾客投入硬币的钱数也是有1元、2元、5元、10元四种,但每次只能投入其中的一种硬币,此操作通过按动相应的一个按键来模拟,并同时用数码管将投币额显示出来。

3)顾客投币后,按一次确认键,如果投币额不足时则报警,报警时间3秒(可用点阵模拟报警)。

如果投币额足够时自动送出货物(送出的货物用相应不同的指示灯显示来模拟),同时多余的钱应找回,找回的钱数用数码管显示出来。

4)顾客一旦按动确认键3秒后,自动售货机即可自动恢复到初始状态,此时才允许顾客进行下一次购货操作。

5)售货机还应具有供商家使用的累加卖货额的功能,累加的钱数要用数码管显示,显示2位即可。

此累加器只有商家可以控制清零。

6)此售货机要设有一个由商家控制的整体复位控制。

二、实验原理首先应搭建识别模块,将代表每种硬币的拨码开关信号转变为BCD码进行累加。

当累加完成后,将累加结果与代表商品的BCD码相比较。

如果大于售出商品并对两个BCD码求差,求差的结果作为找钱信号;如果等于直接售出商品;小于则报警。

至于统计卖钱额,则是对售出的商品进行累加。

三、分析与设计思路可分为以下模块1)分频模块。

2)计时模块。

用于控制确认键后到恢复初始化的3秒计时。

3)识别模块。

将每种硬币、货品的拨码开关信号转变为编码。

4)清零模块。

用于销售总额的清零。

5)初始化模块6)控制模块。

用于数据读入、投币不足、交易成功状态的控制及转化。

7)显示模块四、程序代码段moduleautoseller(clk,g,m,yes,read,zero,led_dig,led_seg,led_c,led_r,led);inputclk,yes,read,zero;〃确定键,商家读取键,清零键word格式-可编辑-感谢下载支持input[3:0]g,m;//货品及投币选择键outputled_dig,led_seg,led_c,led_r,led;//数码管输出及点阵输出regf_100;〃分频时钟regf_1;reg[3:0]goods,money,led,change,g_c;integerr,a,b,a_tmp2,a_tmp1;integerret=0;〃用于控制各状态间的转换reg[9:0]count;reg[7:0]led_c,led_r,led_dig,led_seg;reg[1:0]state;integeri;regx;always@(posedgeclk)//分频模块beginif(a_tmp2==999)beginf_100=~f_100;a_tmp2<=0;endelsea_tmp2<=a_tmp2+1;endalways@(posedgeclk)beginif(a_tmp1==9999999)beginf_1=~f_1;a_tmp1<=0;endelsea_tmp1<=a_tmp1+1;endalways@(posedgef_1)beginif(ret!=0)//用于按确认键后的计时begina=a+1;endelsebegina=0;endendalways@(posedgef_100)beginif(zero==0)//清零word格式-可编辑-感谢下载支持begincount=0;endif(read!=0)//非商家读取模式(普通读写模式)begin//识别模块case(g)//表每种货品的拨码开关信号转变为编码4'b0001:begingoods=1;end4'b0010:begingoods=2;end4'b0100:begingoods=5;end4'b1000:begingoods=10;enddefault:begingoods=0;endendcasecase(m)//表每种硬币的拨码开关信号转变为编码4'b0001:beginmoney=1;end4'b0010:beginmoney=2;end4'b0100:beginmoney=5;end4'b1000:beginmoney=10;enddefault:beginmoney=0;endendcase if(a==3)//初始化beginret=0;led=4'b0000;led_c=8'b0000_0000;led_r=8'b1111_1111;x=0;endif(yes==0)//按确定键beginif(money<goods)//金钱不足beginchange=0;ret=1;endelsebegin//金钱足够change=money-goods;ret=2;if(x==0)//交易成功销售总额增加begincount=count+goods;x=1;endendendg_c=goods;//显示模块word格式-可编辑-感谢下载支持if(ret==1)//金额不足,数码管报警begin led_c=8'b1111_1111;led_r=8'b0000_0000;endif(ret==2)〃交易成功begincase(goods)//LED灯显示货物1:beginled=4'b0001;end2:beginled=4'b0010;end5:beginled=4'b0100;end10:beginled=4'b1000;endendcaseg_c=change;endcase(state)//显示选择的货物0:beginr=g_c%10;led_dig=8'b1111_1011;case(r)0:beginled_seg=8'b1111_1100;end1:beginled_seg=8'b0110_0000;end2:beginled_seg=8'b1101_1010;end3:beginled_seg=8'b1111_0010;end4:beginled_seg=8'b0110_0110;end5:beginled_seg=8'b1011_0110;end6:beginled_seg=8'b1011_1110;end7:beginled_seg=8'b1110_0000;end8:beginled_seg=8'b1111_1110;end9:beginled_seg=8'b1111_0110;endendcaseend1:beginr=g_c/10;led_dig=8'b0111_1111;case(r)0:beginled_seg=8'b1111_1100;end1:beginled_seg=8'b0110_0000;end2:beginled_seg=8'b1101_1010;end3:beginled_seg=8'b1111_0010;end4:beginled_seg=8'b0110_0110;end5:beginled_seg=8'b1011_0110;end6:beginled_seg=8'b1011_1110;end7:beginled_seg=8'b1110_0000;end8:beginled_seg=8'b1111_1110;end9:beginled_seg=8'b1111_0110;endendcaseend//显示投入的钱数及余额2:beginr=money%10;led_dig=8'b1110_1111;case(r)0:beginled_seg=8'b1111_1100;end1:beginled_seg=8'b0110_0000;end2:beginled_seg=8'b1101_1010;end3:beginled_seg=8'b1111_0010;end4:beginled_seg=8'b0110_0110;end5:beginled_seg=8'b1011_0110;end6:beginled_seg=8'b1011_1110;end7:beginled_seg=8'b1110_0000;end8:beginled_seg=8'b1111_1110;end9:beginled_seg=8'b1111_0110;endendcase end3:beginr=money/10;led_dig=8'b1111_0111;case(r)0:beginled_seg=8'b1111_1100;end1:beginled_seg=8'b0110_0000;end2:beginled_seg=8'b1101_1010;end3:beginled_seg=8'b1111_0010;end4:beginled_seg=8'b0110_0110;end5:beginled_seg=8'b1011_0110;end6:beginled_seg=8'b1011_1110;end7:beginled_seg=8'b1110_0000;end8:beginled_seg=8'b1111_1110;end9:beginled_seg=8'b1111_0110;endendcase endendcasestate=state+1;endif(read==O)〃商家读取模式begincase(i)//显示销售总额0:beginb=count/10;led_dig=8'b1111_1110;case(b)0:beginled_seg=8'b1111_1100;end1:beginled_seg=8'b0110_0000;end2:beginled_seg=8'b1101_1010;end3:beginled_seg=8'b1111_0010;end4:beginled_seg=8'b0110_0110;end5:beginled_seg=8'b1011_0110;end6:beginled_seg=8'b1011_1110;end7:beginled_seg=8'b1110_0000;end8:beginled_seg=8'b1111_1110;end9:beginled_seg=8'b1111_0110;endendcase end1:beginb=count%10;led_dig=8'b1111_1101;case(b)0:beginled_seg=8'b1111_1100;end1:beginled_seg=8'b0110_0000;end2:beginled_seg=8'b1101_1010;end3:beginled_seg=8'b1111_0010;end4:beginled_seg=8'b0110_0110;end5:beginled_seg=8'b1011_0110;end6:beginled_seg=8'b1011_1110;end7:beginled_seg=8'b1110_0000;end8:beginled_seg=8'b1111_1110;end9:beginled_seg=8'b1111_0110;endendcase endendcasei=i+1;if(i==2)begini=0;endendendendmodule五、对应变量的管脚配置表Named:NodeName Direction Location1/elk Input PIN732/g[o:Input PIN1873/g[i Input PIN18?4Input:PIN1905g[习Input:PIN179尸D led[3]Output PIML6S7■/led[Z Output PIN1678・/led[f Output PIN163/led[0:Output PIN160号・10・/Output PIN3111■/led.®Output PIM3012 1心5]Output PIHZ913■/ledcL4:Output PINZ814・/led15]Output PIN2415・/ledcE2:Output PDN2516・led.cLi:Output PIN2617■_Z ledc[(J]Output PIN27IS•—hdd g[7]Output PIH37四■/leddig[&]Output PIN3920■/leddig[5;Output PIM6021leddig[4;Output PIN57・222ledd g[j]Output PIN5523■_Z ledcig[2]Output PIN5624g[l"Output PIH53Z5■/leddig[a;Output PIN6136■/lecijLT]Output PIM3627・2ledjL6]Output PIN3828・1刨」囚Output PIN1029■/ledjK Output PI卜L15301曲」[割Output PIN」斗Output PINL2 31■/lecijtr32■/1罚」[1]Output PIN1^・/ledjLO]Output PINL7兰兰・/ledr[0]Output PIM1734、丄ledseg[7]Output PIM6735■_Z ledseg[6]Output PIM6536sclfieg[5'Output PIM6457■/leds亡Output PIN6338・/led£eg[5[]Output PIM6839l£dseg[2;Output PIM6940■_Z ledseg[l]Output PIM7041sd-fiegpj]Output PIM7142/rri[Ci Input PIM17743/m[l:Input FIN」764+rri[2]In叫t PIM17545E[3Input PIM174-46read Input PIM19647/yes Input PIM151书/2ero Input PIM202书。

verilog设计 自动售货机

自动售货机1、设计说明本设计是以现场可编程逻辑器件(FPGA)为核心的自动售货机,利用Modesim 软件编写verilog硬件描述语言程序以实现自动售货功能。

1.1、系统设计描述(1)用四个发光二极管分别模拟售出价值为2元、5元、7元和10元的商品,购买者可以通过开关选择任意一种标价中的小商品;(2)灯亮时表示该小商品售出;(3)用开关分别模拟1元、5元,10元和20元货币投入,用四支发光二极管代表投入的货币的面值;(4)每次只能售出一种小商品,当所投硬币达到或超过购买者所选面值时,售出货物并找回剩余的硬币,回到初始状态;(5)当所投硬币值不足面值时,可通过一个复位键退回所投硬币,回到初始状态。

系统框图如图1.1所示:图1.1 系统框图2、详细状态描述2.1 初始状态rst为复位键,低电平有效,实现系统复位。

2.2 选商品状态分别有价格为2元、5元、7元和10元的商品,每次选择商品前,设置一个标志位btn_sel_goods表示选择商品状态。

此自动售货机每一次售货时只能一次选择一种商品,当同时选择两种以上时,选择商品无效,数码管显示清零,重新进行商品选择。

选择商品后,数码管显示所选商品价格。

2.3 投币状态当选好商品后,开始投币。

同样有一标志位btn_price表示投币金额。

投币口只接受面值为1元、5元10元和20元的货币,可以同时投入多种面值钱币。

投完币后,先有一个确认买商品的过程,若投了币但又不购买商品了,就将全部投币金额退回;若确认购买商品,则进入下一状态。

2.4 找零状态投完币,并确认购买商品后,进入找零状态。

首先要将所投的金额与所选商品的价格做比较,若所投金额小于商品价格,则退回所投钱币;若大于等于商品价格,则两者做差,得到需要找零的钱。

3、仿真结果分析设置测试程序各参数,运行tb文件,仿真结果如下图3.1、3.2所示。

图3.1图3.1所示,商品价格选择为7元,即btn_sel_goods=2'b10,投币总额大于商品价格的情况,上图中btn_mony从右到左依次代表投币1元、10元、20元、10元、20元、1元、20元和10元,共92元。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

自动售货机1、设计说明本设计是以现场可编程逻辑器件(FPGA)为核心的自动售货机,利用Modesim 软件编写verilog硬件描述语言程序以实现自动售货功能。

1.1、系统设计描述(1)用四个发光二极管分别模拟售出价值为2元、5元、7元和10元的商品,购买者可以通过开关选择任意一种标价中的小商品;(2)灯亮时表示该小商品售出;(3)用开关分别模拟1元、5元,10元和20元货币投入,用四支发光二极管代表投入的货币的面值;(4)每次只能售出一种小商品,当所投硬币达到或超过购买者所选面值时,售出货物并找回剩余的硬币,回到初始状态;(5)当所投硬币值不足面值时,可通过一个复位键退回所投硬币,回到初始状态。

系统框图如图1.1所示:图1.1 系统框图2、详细状态描述2.1 初始状态rst为复位键,低电平有效,实现系统复位。

2.2 选商品状态分别有价格为2元、5元、7元和10元的商品,每次选择商品前,设置一个标志位btn_sel_goods表示选择商品状态。

此自动售货机每一次售货时只能一次选择一种商品,当同时选择两种以上时,选择商品无效,数码管显示清零,重新进行商品选择。

选择商品后,数码管显示所选商品价格。

2.3 投币状态当选好商品后,开始投币。

同样有一标志位btn_price表示投币金额。

投币口只接受面值为1元、5元10元和20元的货币,可以同时投入多种面值钱币。

投完币后,先有一个确认买商品的过程,若投了币但又不购买商品了,就将全部投币金额退回;若确认购买商品,则进入下一状态。

2.4 找零状态投完币,并确认购买商品后,进入找零状态。

首先要将所投的金额与所选商品的价格做比较,若所投金额小于商品价格,则退回所投钱币;若大于等于商品价格,则两者做差,得到需要找零的钱。

3、仿真结果分析设置测试程序各参数,运行tb文件,仿真结果如下图3.1、3.2所示。

图3.1图3.1所示,商品价格选择为7元,即btn_sel_goods=2'b10,投币总额大于商品价格的情况,上图中btn_mony从右到左依次代表投币1元、10元、20元、10元、20元、1元、20元和10元,共92元。

red灯实时显示所投货币的面值。

dis_price显示为0000001_0001111,对应数码管显示数字为07,即7元。

dis_mony为0000000_0100100,对应数码管显示数字为85。

可以看出,实验结果很理想,说明代码符合设计要求。

图3.2图3.2所示,商品价格选择为7元,即btn_sel_goods=2'b10,投币总额小于商品价格的情况,上图中btn_mony从右到左依次代表投币1元、5元,共6元。

red灯实时显示所投货币的面值。

dis_price显示为0000001_0001111,对应数码管显示数字为07,即7元。

dis_mony为0000001_0100000,对应数码管显示数字为06,即6元,可以看出,实验结果很理想,说明代码符合设计要求。

4、总结与展望通过本次课程设计,我对Verilog HDL语言有了更深刻的了解,能够比较灵活地运用它来实现我们所想要要其实现的功能。

试验中,由于实验条件的限制本实验只实现了一些自动售货机最基本的功能,如果允许的话,后续工作还可以加一些像刷卡消费,折扣消费之类的功能进去。

总的来说该试验还是很成功的,在实验中也确实遇到了不少问题,不过在老师和同学的帮助下一一克服了,使我明白了和他人共同合作的重要性。

在以后的道路上我们也必须深刻认识到团队合作的精神,投入今后的发展之中。

附录:///////////////////////////////////////////////////自动售货机//btn_sel_goods 为所选商品,由于实验条件的限制,本实验中只给出4种价格的商品//btn_ok 购买确认键//led[3:0] 客户单次投币币值//beep 客户所投金额或购买商品后剩余金额大于所选商品价格时,该灯亮,表示可以继续购买//led_warn 客户所投金额或购买商品后剩余金额小于所选商品价格时,该灯亮,表示不可以继续购买//charge 找零按键,按下后找零/////////////////////////////////////////////////`timescale 1ns / 1psmodule auto_machine(rst,clk,charge,dis_mony,dis_price,btn_ok,btn_mony,btn_sel_goods,led_warn,led,beep);input clk,rst;input charge,btn_ok; //找零/确定input [3:0] btn_mony; //选择放入的钱1元5元10元20元input [1:0] btn_sel_goods; //选择2元5元7元10元商品output [3:0] led; //分别显示投入的是1元5元10元还是20元货币output led_warn; //钱不足,指示灯output [13:0] dis_mony; //数码管显示投入总金额output [13:0] dis_price; //数码管显示价钱output beep; //交易完成提醒reg [3:0] led;reg led_warn;//投入钱币不够时警告reg [13:0] dis_mony;reg [13:0] dis_price;reg beep;parameter S2=2'b00,S5=2'b01,S7=2'b10,S10=2'b11;parameter M1=4'b0001,M5=4'b0010,M10=4'b0100,M20=4'b1000;wire[3:0] btn_mony_buf0;wire[3:0] btn_mony_buf1;wire btn_ok_b0;wire btn_ok_b1;wire[1:0] btn_sel_goods_b;wire charge_buf;reg [6:0] price,price_all;key_downuut4(.rst(rst),.clk(clk),.det(btn_mony[0]),.key_don(btn_mony_buf0[0]));key_downuut5(.rst(rst),.clk(clk),.det(btn_mony[1]),.key_don(btn_mony_buf0[1]));key_downuut6(.rst(rst),.clk(clk),.det(btn_mony[2]),.key_don(btn_mony_buf0[2]));key_downuut7(.rst(rst),.clk(clk),.det(btn_mony[3]),.key_don(btn_mony_buf0[3]));edge_detuut0(.rst(rst),.clk(clk),.det(btn_mony_buf0[0]),.pos_edge(btn_mony_buf1[0])); edge_detuut1(.rst(rst),.clk(clk),.det(btn_mony_buf0[1]),.pos_edge(btn_mony_buf1[1])); edge_detuut2(.rst(rst),.clk(clk),.det(btn_mony_buf0[2]),.pos_edge(btn_mony_buf1[2])); edge_detuut3(.rst(rst),.clk(clk),.det(btn_mony_buf0[3]),.pos_edge(btn_mony_buf1[3]));key_down uut8(.rst(rst),.clk(clk),.det(btn_ok),.key_don(btn_ok_b0));edge_det uut9(.rst(rst),.clk(clk),.det(btn_ok_b0),.pos_edge(btn_ok_b1));key_downuut10(.rst(rst),.clk(clk),.det(btn_sel_goods[0]),.key_don(btn_sel_goods_b[0]));key_downuut11(.rst(rst),.clk(clk),.det(btn_sel_goods[1]),.key_don(btn_sel_goods_b[1]));key_down uut12(.rst(rst),.clk(clk),.det(charge),.key_don(charge_buf));always @(negedge rst or posedge clk)beginif(!rst)beginled <= 4'b0;led_warn <=1'b0;beep <=1'b0;price_all =7'd0;price <= 7'd0;dis_mony <=14'h3fff;dis_price <=14'h3fff;endelsebegincase(btn_mony_buf1)M1: //所投钱币+1price_all =price_all + 7'd1;M5: //所投钱币+5price_all =price_all + 7'd5;M10: //所投钱币+10price_all =price_all+ 7'd10;M20: //所投钱币+20price_all =price_all + 7'd20;default: led <= 4'b0;endcasecase(btn_mony)M1: //显示所投钱币币值led <= M1;M5:led <= M5;M10:led <= M10;M20:led <= M20;default:led <= 4'b0;endcasecase(btn_sel_goods_b)S2:begin price <= 7'd2;endS5:begin price <= 7'd5;endS7:begin price <= 7'd7;endS10:begin price <= 7'd10;enddefault:begin price <= 7'd0; endendcaseif(!charge_buf)price_all = 7'd0; //退回零钱elsebeginif(btn_ok_b1)beginif(price_all < price)led_warn = 1'b1;elseprice_all = price_all-price;endelsebeginled_warn <= 1'b0;beep <= 1'b0;endendif(price_all<price)led_warn <= 1'b1; //投币差额小于商品价格时警告elsebeginled_warn <= 1'b0;beep <= 1'b1; //所投金额大于商品价格时,亮灯表示可以购买 enddis_mony[6:0] <= led7(price_all%10);//找零金额个位显示dis_mony[13:7] <= led7(price_all/10);//找零金额十位显示dis_price[6:0] <= led7(price%10);//商品价格个位显示dis_price[13:7] <= led7(price/10);//商品价格十位显示endend/*数码管段码表*/function [6:0] led7;input [6:0] dis_input;begincase (dis_input)0 : led7 = 7'b1000000;1 : led7 = 7'b1111001;2 : led7 = 7'b0100100;3 : led7 = 7'b0110000;4 : led7 = 7'b0011001;5 : led7 = 7'b0010010;6 : led7 = 7'b0000011;7 : led7 = 7'b1111000;8 : led7 = 7'b0000000;9 : led7 = 7'b0011000;default : led7 = 7'b111_1111; endcaseendendfunctionendmodule///////////////////////////////////////实现边沿检测的功能//det为原输入需检测信号//pos_edge为输出的一个脉冲长度的上升沿信号/////////////////////////////////////// module edge_det(rst,clk,det,pos_edge); input rst,clk;input det;output pos_edge;wire pos_edge;reg p_edge1;reg p_edge2;assign pos_edge = (!p_edge1 & p_edge2);always @(negedge rst or posedge clk) beginif (!rst)beginp_edge1<=1'b0;p_edge2<=1'b0;endelsebeginp_edge1<= det;p_edge2<=p_edge1;endendendmodule///////////////////////////////////// //实现按键消抖工功能//det为原输入信号//key_don为输出确认信号////CONT实现计数,经过CONT个脉冲的延时/////////////////////////////////////// module key_down(rst,clk,det,key_don); input rst,clk;input det; //output key_don; //reg p_edge1;reg p_edge2;reg[24:0] cont;parameter CONT = 25'd050;assign key_don = (det & p_edge1 & p_edge2);always @(negedge rst or posedge clk)beginif (!rst)beginp_edge1<=1'b0;p_edge2<=1'b0;cont<=25'b0;endelsebeginif(cont==CONT)begincont<=0;p_edge1 <= det;p_edge2 <=p_edge1;endelsecont<=cont+1'b1;endendendmodule/////////////////////////////////////////////////////////////////////// //tb文件/////////////////////////////////////////////////////////////////////// `timescale 1ns / 1psmodule tb_mb;reg clk,rst,btn_ok;reg [3:0] btn_mony; //选择放入的钱1元5元10元20元reg [1:0] btn_sel_goods; //选择商品2、5、7、10元wire [3:0] led; //led_5,led_10,led_15,led_20wire led_warn; //钱不足,指示灯wire [6:0] dis_mony; //数码管显示投入面值wire [6:0] dis_price; //数码管显示价钱wire beep;auto_machine uut(.clk,.rst,.dis_mony,.dis_price,.btn_ok,.btn_mony,.btn_sel_goods,.led_warn,.led,.beep);initial beginclk = 1'b0;rst = 1'b0;btn_ok=1'b0;#20 rst=1;#10 btn_sel_goods=2'b10;#20 btn_mony=4'b0001;#30 btn_mony=4'b0100;#50 btn_mony=4'b0010;#100 btn_ok=1'b1;endalways #2 clk=~clk; endmodule。