基于FPGA数据通信接口的设计与实现

基于FPGA的千兆以太网端口通信的设计

设计思路

设计需求:本次演示旨在设计一个具有十个端口的千兆以太网接口,以满足 高数据传输速率和多任务处理的需求。

设计原理:基于FPGA的十端口千兆以太网接口的设计原理是利用FPGA的并行 处理能力,将十个千兆以太网物理层(PHY)芯片与FPGA集成在一起,实现高速 数据传输。

逻辑实现:通过FPGA编程语言(如VHDL或Verilog)实现逻辑设计,完成十 个端口的千兆以太网接口的配置和管理。

另外,我们还需要定义一个以太网帧的发送模块。该模块包括一个外部存储 器接口、一个封装模块和一个曼彻斯特编码器。当需要发送一个数据帧时,外部 存储器接口会从存储器中读取数据并将其传递给封装模块。封装模块会将数据封 装成一个以太网

帧,然后将其传递给曼彻斯特编码器。曼彻斯特编码器会将数字信号转换为 模拟信号,以便在物理层上进行传输。

结论

基于FPGA的十端口千兆以太网接口的设计与实现具有重要的应用价值和优势。 在硬件设计中,通过选用高性能的PHY芯片和优化信号完整性分析等措施,提高 了数据传输的稳定性和可靠性。在软件设计中,实现了以太网协议栈和TCP/IP协 议,

并添加了异常处理机制。经过严格的测试和验证,设计的接口具有高性能、 高稳定性、高可靠性等特点,适用于各种需要多端口千兆以太网连接的应用场景。

我们将FPGA中的数据通过SGMII接口传输到以太网控制器中,或者将从以太 网控制器中接收到的数据传递给FPGA处理。

五、SPI接口设计

SPI接口用于在FPGA和外部存储器之间进行数据传输。在设计中,我们使用 了一种同步串行通信协议来实现数据传输。该协议使用一根时钟线和多根数据线 来传输数据,具有简单、高速和可靠等优点。我们将需要保存的数据通过SPI接 口存储到一个外部存储

《2024年基于FPGA的PCIE总线接口和光纤通信模块设计》范文

《基于FPGA的PCIE总线接口和光纤通信模块设计》篇一一、引言随着信息技术的飞速发展,数据传输的速度和效率成为了系统性能的关键因素。

FPGA(现场可编程门阵列)以其强大的并行处理能力和灵活的编程特性,在高速数据传输和处理中发挥着重要作用。

本文将详细介绍基于FPGA的PCIE总线接口和光纤通信模块设计,探讨其设计原理、实现方法和应用优势。

二、PCIE总线接口设计1. PCIE总线概述PCIE(Peripheral Component Interconnect Express)总线是一种高速串行计算机扩展总线标准,具有高带宽、低延迟、支持热插拔等优点。

在FPGA中实现PCIE总线接口,可以有效地提高系统数据传输速度和扩展性。

2. 设计原理PCIE总线接口设计主要包括物理层设计和协议层设计。

物理层设计负责实现PCIe信号的发送和接收,包括差分信号的编码、解码、时钟恢复等。

协议层设计则负责实现PCIe协议的握手、数据传输、流控制等。

3. 实现方法在FPGA中实现PCIE总线接口,需要使用硬件描述语言(如VHDL或Verilog)编写代码,定义PCIe信号的时序、数据宽度、地址空间等参数。

同时,还需要使用FPGA的开发工具进行仿真、综合、布局布线等步骤,生成可在FPGA上运行的二进制文件。

三、光纤通信模块设计1. 光纤通信概述光纤通信是一种基于光信号的传输方式,具有传输距离远、传输速度快、抗干扰能力强等优点。

在高速数据传输系统中,光纤通信模块扮演着至关重要的角色。

2. 设计原理光纤通信模块的设计主要包括光信号的发送和接收两部分。

发送端将电信号转换为光信号,通过光纤传输;接收端则将光信号转换为电信号,供系统处理。

在FPGA中实现光纤通信模块,需要使用高速串行通信接口(如SerDes)进行光电转换和信号处理。

3. 实现方法在FPGA中实现光纤通信模块,需要使用专门的IP核(智能产权核)或第三方芯片,完成光电转换和信号处理功能。

基于FPGA的串口通信设计与实现

置和输人数据计算出响应

的奇偶校验位,它是通过

纯组合逻辑来实现的。

2.6总线选择模块

总线选择模块用于

选择奇偶校验器的输入是

数据发送总线还是数据接

收总线。

2.7计数器模块

计数器模块的功能

是记录串行数据发送或者

接收的数日,在计数到某

数值时通知UART内核模

块。 3 UART程序设计 UART完整的工作流程可以分为接收过程

关键词:FPGA:UART:RS232

引言 串行接口的应用非常广泛,为实现串口通 信功能一般使用专用串行接口芯片,但是这种 接口芯片存在体积较大、接口复杂以及成本较 高的缺点,使得硬件设计更加复杂,并且结构与 功能相对固定,无法根据设计的需要对其逻辑 控制进行灵活的修改。介绍了一种采用FPGA 实现串口通信的方法。 1串口通信协议 对一个设备的处理器来说,要接收和发送 串行通信的数据,需要一个器件将串行的数据 转换为并行的数据以便于处理器进行处理,这 种器件就是UART(Universal Asynchronous Re— ceiver/Transmitter)通用异步收发器。作为接iSl的 一部分,UART提供以下功能: 1.1将由计算机内部传送过来的并行数据 转换为输出的串行数据流; 1.2将计算机外部来的串行数据转换为字 节,供计算机内部使用并行数据的器件使用; 1.3在输出的串行数据流中加入奇偶校验 位,并对从外部接收的数据流进行奇偶校验: 1.4在输出数据流中加入启停标记,并从 接收数据流中删除启停标记。 2 UART模块设计 UART主要由UART内核、信号检测器、移 位寄存器、波特率发生器、计数器、总线选择器 和奇偶校验器7个模块组成。(见图1) 2.1 UART内核模块 UART内核模块是整个设计的核心。在数 据接收时,UART内核模块负责控制波特率发 生器和移位寄存器同步的接收并且保存 RS一232接收端口上的串行数据。在数据发送 时,UART内核模块首先产生完整的发送序列, 之后控制移位寄存器将序列加载到移位寄存器 的内部寄存器里,最后再控制波特率发生器驱 动移位寄存器将数据串行输出。 2_2信号检测模块 信号检测器用于对RS一232的输入信号进 行实时检测,一旦发现新的数据则立即通知 UART内核。需要注意的是,这里所说的 RS一232输入输出信号都指经过电平转换后的 逻辑信号,而不是RS一232总线上的电平信号。 2_3移位寄存器模块 移位寄存器的作用是存储输入或者输出 的数据。 2.4波特率发生器模块 由于RS一232传输必定是工作在某种波特 率下,比如9600,为了便于和RS一232总线进行 同步,需要产生符合RS一232传输波特率的时 钟。 2.5奇偶校验器模块 奇偶校验器的功能是根据奇偶校验的设

基于FPGA的多通道HDLC通信系统设计与实现

一

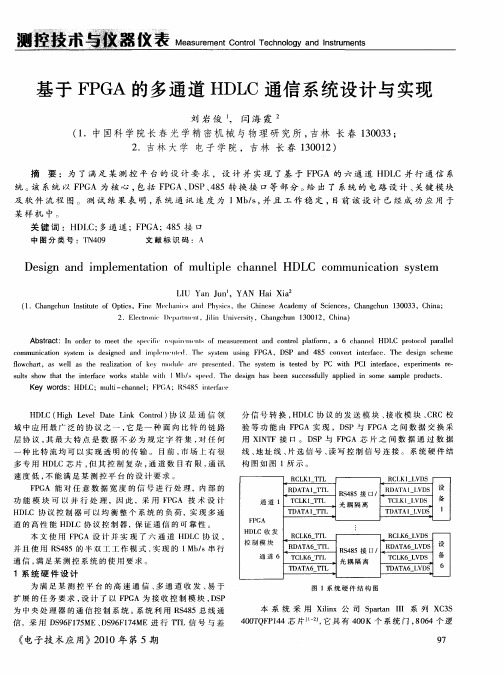

分 信 号 转 换 , DL H C协 议 的 发 送 模 块 、 收 模 块 、 R 接 C C校

验 等 功 能 由 F G 实 现 ,D P与 F GA 之 间 数 据 交 换 采 P A S P 用 X N F接 口 。 D P 与 F GA 芯 片 之 间 数 据 通 过 数 据 IT S P 线 、 址 线 、 选 信 号 、 写 控 制 信 号 连 接 。 系 统 硬 件 结 地 片 读

c mmu i ai n y tm i e in d n i hI1 l t. 1e y t m sn F G o n c t s s o e s d s e a d mp 1i (1 g I l 1l s se u ig P A. DS n 4 5 o v l i tr c P a d 8 c n e  ̄ n e a e.T e e in c e f h d sg s h me l f wc a t s wel s t e r a iai n f k y ld h l r s n e o h r ,a l a h e l t o e no u a t z o ,p e e td.T e y t m i e td y C h s se s se b P wi P I n e a e,e p rme t e t t h C i tr c f x ei ns r— s i h w t a h i tr c o k tb e wi 1Mh s s'eI h e in h s b e s c e su l p l d i o a l r d cs u t s o h t t e n e a e w r s sa l t / l ( s f h .T e d s a e n u c sf l a p i n s me s mp e p o u t . g y e

基于FPGA数据通信接口的设计与实现

胡 应 洪 ( 阳职业 技术 学院信 息工程 系 绵 四川 绵阳 6 1 0 ) 2 0 0

摘 要 : 羞 信 息化 、 字 化 技 术 的 不 断 发展 , 字 集 成 电路 的 应 用越 来 越 广泛 , 鳊 程 逻 辑 器 件也 由早 期 的 储 存 少量 的 数 据 发展 如今 随 数 数 可 超 大规 模 复 杂 组 合 逻 辑 与 时 序 逻 辑 的 现 场 可 编 程 逻 辑 器 件 , P  ̄F 6A。 文 就 对 基 于 F GA 据 通 信 接 口 的设 计 与 实 现 做 出研 究 。 本 P 数

图1 FG P A设 计 流 程 图

组 接 收 到 一祯 数 据 , 就会 在 触 发 中断 的状 态 下 设 定 其 为有 效 状 态 , 这 时 中 断 进 程就 会 征 下 一时 钟 触 发Pc 核 内I T— I NT N信 号 处于 有

科技资 讯 S E CE & T CH OLO IF CIN E N GY N ORMATI ON

明显 的 成 本 较 低 、 带宽 高 且 可以 扩 展 的 特 点 , 用 于 点 对 点 串行 链 适 路的 数 据 传输 。 Aur a 路 层协 议 为标 准的 诸 如I or 链 CP/I P或者 以 太 网等 上 层 协 议 , 何分 据 分 组 都 能 通 过 AU o a 路 层协 议 进 行封 任 rr链 装 , 及 在 各 电路 板 或者 芯 片 之 间 进 行 高 速 数 据 传 输 。 以 SCI 点 模 型 的 模 组 设 汁 中 , 节 中断 进 程 是 相 对 重 要 的 设 计 部 分, 它是 连 接SCI 口两 个 模 块 的 重要 环 节 。 旦Au o a 接 一 r r 的接 收 模

基于FPGA的通信接口模块设计与实现

c mmu iain. icu ig t ec nr lc mma d whc h e ta o to c ie s n st h o tc n rle d o nct o n l d n h o to o n ih te c nr lc n r1ma hn e d o t ef n o told mo . r

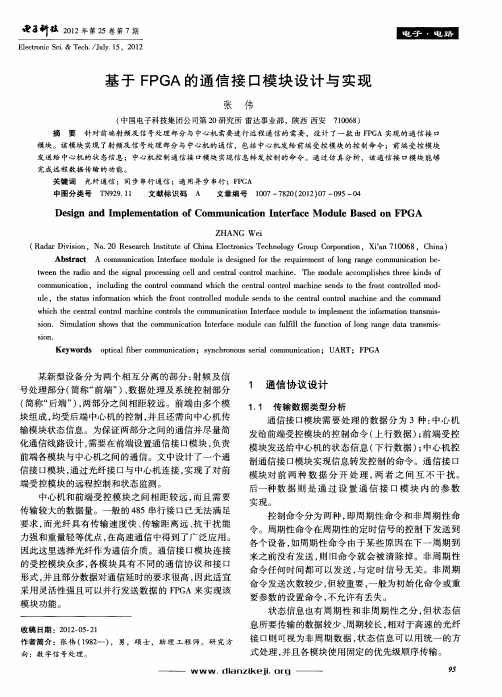

完 成远 程 数 据 传 输 的 功 能 。

关键 词

光 纤 通信 ; 同步 串行 通 信 ;通 用异 步 串行 ;F G PA T 99 1 N 2.1 文 献标 识 码 A 文章编号 10 7 2 (0 2 0 0 5— 4 0 7— 80 2 1 )7— 9 0 中 Nhomakorabea分 类 号

端受 控模 块 的远程 控制 和状态 监测 。 中心 机 和前端 受 控模 块 之 间相距 较 远 , 而且 需 要 传输 较大 的数 据量 。一般 的 4 5串行 接 口已无法 满 足 8

De i n n I plm e a i n o mm un c to n e f c o l s d n FPGA sg a d m e nt to fCo i a i n I t ra e M du e Ba e o

ZHANG e W i

( a a iiin o 2 sac nt ueo hn lcrnc e h ooyG o pC roain R d rD vs ,N . 0 Ree rh Is tt fC iaEe t isT c n lg ru op rt ,Xi n7 0 6 o i o o ’ 1 0 8,C ia a hn )

a 叶技22 第5 第 期 0 年 2卷 7 1

E e to i c. T c . J l. 5. 2 1 l cr nc S i & e h / u y 1 02

基于FPGA的通信系统设计

基于FPGA的通信系统设计随着信息技术的发展,通信系统的应用已经渗透到了我们生活的方方面面,从智能手机到物联网,从基站到卫星通信,通信系统无处不在。

如何设计高效、可靠的通信系统成为了通信领域的重要研究方向之一。

本文将探讨基于FPGA的通信系统设计,介绍FPGA的基本概念和通信系统的基础知识,同时结合实际案例,深入分析FPGA的在通信系统中的应用。

一、FPGA的基本概念FPGA是可编程逻辑门阵列(Field-Programmable Gate Array,简称FPGA)的缩写,是由可编程逻辑器件和可编程时钟、存储器等辅助电路组成的可编程集成电路。

与传统的专用集成电路相比,FPGA可以根据需要重复编程,适应不同的应用场景。

FPGA的优点在于其可以完成高速、高精度的数据处理和控制操作,同时具有较强的可靠性和抗干扰能力。

二、通信系统的基础知识通信系统是在信道传输介质上进行信息传输和交换的一种系统,包括发送端、接收端和传输介质。

通信系统的基本要素包括信号源、调制解调器、信道、接收器和信号处理器。

其中,调制解调器是将数字信号转换为模拟信号或者将模拟信号转换为数字信号的重要组成部分。

三、FPGA在通信系统中的应用FPGA在通信系统中的应用非常广泛,从通信协议的实现到信号处理的优化都有涉及。

下面将以LTE无线通信系统为例,介绍其FPGA在通信系统中的应用。

1. 通信协议的实现LTE是一种4G无线通信标准,其通信协议的实现需要高效、稳定的硬件支持。

FPGAs与硬件描述语言(HDL)结合可以实现高度定制化的硬件设计,并且可以通过高层次综合工具转化为可编程逻辑块和可编程时序。

FPGA实现的通信协议处理器可在保证性能和效率的同时保持灵活性,使其适应不同的协议标准。

2. 信号处理的优化FPGA可以对一些通信信号处理算法进行硬件实现,从而提高信号处理的效率和速度。

例如,在LTE中,可以采用FPGA实现高速傅里叶变换(FFT)算法,从而大大提高了LTE信号处理的速度,并且能够保证处理时间的稳定性和可靠性。

(完整word版)基于FPGA的数字通信系统报告

基于FPGA的数字通信系统设计指导老师:李东明项目负责人:何兴凯项目成员:杜川王光辉李莉玲摘要:设计并实现了了一种基于FPGA的片上数字通信系统。

系统主要由编译码模块,调制解调模块,频率合成模块,FIR数字滤波模块,位同步模块以及加密解密模块组成,由这些模块组成一个完整的通信系统片上系统。

一、项目背景在通信领域,尤其是无线通信方面,随着技术的不断更新和新标准的发布,通信系统也在朝着高速率,高质量,高可靠性等方向不断发展着。

但可以清楚地看到,当今动辄成百上千兆的数据流一股脑的涌进,任何一个高速数据传输系统的稳定性和安全性等方方面面都面临着极大的挑战,稍有考虑不周之处就会引起各种各样的问题,为了提高通信系统的稳定性,将系统构建在一个芯片的内部,即构建所谓的片上系统,应该可以大幅度提高系统的稳定性。

借助于通信原理以及EDA技术等课程的专业知识,设计了一个基于FPGA的数字通信系统,主要目的是在片上系统的设计思想指导下,设计并实现一个片上数字通信系统。

二、系统总体方案设计鉴于当前高速数字通信系统的设计方案大多是现场可编程门阵列(FPGA)加片外存储介质(SDRAM、SRAM、DDR等)的组合,本次设计方案同样采用这种组合方式,具体为一片FPGA、三片静态存储器(SRAM)和一片高速数据传输芯片。

FPGA具有管脚多、内部逻辑资源丰富、足够的可用IP核等优点,用作整个高速数字通信系统的控制核心极为合适,本方案中选用Altera公司的高性价比CycloneII系列FPGA芯片;静态存储用具有的一大优点就是数据读取速度快,且控制信号简单,易操纵,适用作高速数据存储介质,其处理速度和存储容量均满足系统设计的需要。

与传统的DSP(数据信号处理器)或DPP(通用处理器)相比,FPGA在某些信号处理任务中表现出非常强的性能,而单片机的处理也显然逊色很多。

以下为整体的系统流程图:图1 系统设计框图三、程序运行平台Quartus II 9.0;Nios II 9.0 IDE ;Alter SOPC Builder 等四、系统模块具体实现1、编译码模块:信源编码有两个基本功能:一是提高信息传输的有效性,二是模拟信号完成AD转换后,可以实现数字化传输。

基于FPGA的多接口转换研究与实现

基于FPGA的多接口转换研究与实现随着现代通信技术的迅速发展,多种接口标准的同时存在给通信设备的设计、开发和应用带来了一定的挑战。

因此,研究和实现基于FPGA的多接口转换技术变得非常重要。

本文将从多接口转换的背景和需求、研究目标、研究方法以及实现过程等方面详细介绍基于FPGA的多接口转换的研究与实现。

一、多接口转换的背景和需求如今,各种通信设备和接口标准正日益多样化,如USB、HDMI、VGA、以太网等。

然而,不同设备之间的相互连接往往需要进行接口转换,这给设备的设计、开发和应用带来了一定的复杂性和困难。

因此,基于FPGA的多接口转换技术应运而生。

多接口转换的需求主要表现在以下几个方面:1.不同设备之间的接口不匹配。

例如,一些旧型设备使用VGA接口,而现代设备多采用HDMI接口,二者之间需要进行转换才能连接。

2. 不同接口的数据传输速率不同。

例如,USB 2.0接口的数据传输速率为480Mbps,而USB 3.0接口的数据传输速率可达到5Gbps,需要进行速率的转换。

3.不同接口的数据格式不同。

例如,HDMI接口传输的视频数据是数字信号,而VGA接口传输的视频数据是模拟信号,需要进行信号格式的转换。

二、研究目标1.不同接口标准之间的物理层信号转换。

例如,将HDMI的数字信号转换为VGA的模拟信号,或将USB3.0的高速数字信号转换为USB2.0的低速数字信号。

2.不同接口标准之间的数据格式转换。

例如,将HDMI接口传输的视频数据转换为VGA接口所需的模拟信号格式。

3.不同接口标准之间的数据速率转换。

例如,将USB3.0接口的高速数据转换为USB2.0接口所支持的低速数据传输。

三、研究方法1.确定转换的接口标准及其特性。

通过对接口标准的研究和了解,确定转换的接口类型、信号特性、数据格式以及数据传输速率等。

2.设计接口转换的硬件电路。

根据接口类型和特性,设计适当的电路结构和物理层接口电路,实现信号的转换和传输。

基于fpga的pci接口dma传输的设计与实现

基于fpga的pci接口dma传输的设计与实现文章标题:深度探讨:基于FPGA的PCI接口DMA传输的设计与实现在当今数字化世界中,高速数据传输和处理已成为各行各业的重要需求。

随着FPGA(现场可编程门阵列)技术的发展,基于FPGA的PCI 接口DMA传输的设计与实现成为了研究和应用的热点之一。

本文将从深度和广度的角度对这一主题进行全面评估,并共享个人观点和理解。

一、概述1.1 传统数据传输方式的局限性传统的数据传输方式在面对高速、大容量数据传输时存在着吞吐量低、延时大等问题,已不能满足实际需求。

1.2 FPGA技术与PCI接口FPGA作为一种灵活可编程的硬件评台,结合PCI接口技术可实现高速数据传输和处理。

1.3 DMA传输的重要性DMA(直接内存存取)技术能在不依赖CPU的情况下实现高速数据传输,为FPGA的应用提供了可能。

二、基于FPGA的PCI接口DMA传输的设计2.1 PCI接口的设计与实现通过对PCI规范的理解和掌握,可以实现FPGA与PCI接口的良好连接和通信。

2.2 DMA控制器的设计设计DMA控制器需要考虑数据分块、传输方向、时序控制等关键问题,以实现高效可靠的数据传输。

三、基于FPGA的PCI接口DMA传输的实现3.1 硬件设计基于FPGA的PCI接口DMA传输需要进行硬件电路设计,包括数据通路、控制逻辑等。

3.2 软件编程针对DMA传输的应用场景,需要进行相应的软件编程,包括驱动程序、应用程序等。

四、总结与展望4.1 总结本文内容本文从PCI接口、DMA传输的设计与实现等方面对基于FPGA的高速数据传输进行了全面探讨。

4.2 个人观点和理解基于FPGA的PCI接口DMA传输技术有着广泛的应用前景,但在实际应用中还存在一些挑战和待解决的问题。

4.3 展望未来发展随着FPGA技术的不断进步和PCI接口标准的升级,基于FPGA的PCI接口DMA传输技术将会更加成熟和普及,为高速数据传输和处理提供更多可能性。

基于FPGA的以太网MII接口扩展设计与实现

基于FPGA的以太网MII接口扩展设计与实现电脑知识2009-01-10 11:09:49 阅读80 评论0 字号:大中小引言传统以PC为中心的互联网应用现已开始转向以嵌入式设备为中心。

据网络专家预测,将来在互联网上传输的信息中,有70%来自小型嵌入式系统,因此,对嵌入式系统接入因特网的研究是有必要的。

目前有两种方法可以实现单片机系统接入因特网:一种方法是利用NIC (网络控制/网卡)实现网络接口,由单片机来提供所需的网络协议;另外一种方法是利用具有网络协议栈结构的芯片和PHY(物理层的接收器)来实现网络接口,主控制器只负责往协议栈结构芯片的某个寄存器里放上适当的数据。

与此同时,用FPGA实现单片机系统接入因特网的方法也日益受到人们的重视。

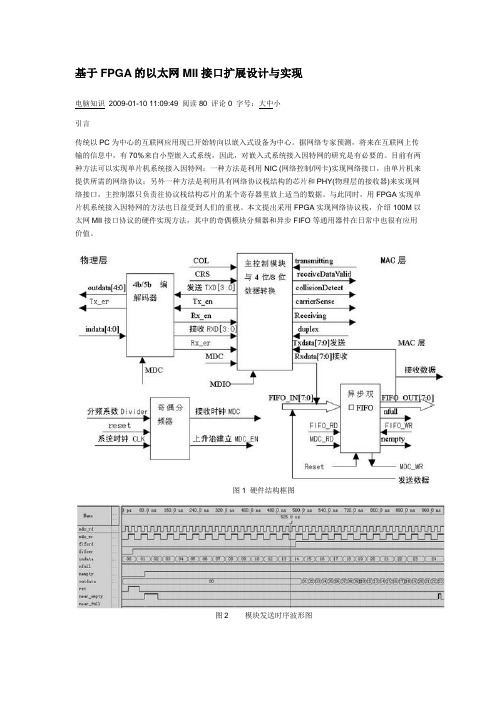

本文提出采用FPGA实现网络协议栈,介绍100M以太网MII接口协议的硬件实现方法,其中的奇偶模块分频器和异步FIFO等通用器件在日常中也很有应用价值。

图1 硬件结构框图图2 模块发送时序波形图以太网MII接口协议IEEE802协议标准系列中,数据链路层包括LLC (逻辑链路控制)子层和MAC (媒体访问控制)子层。

其中MAC单独作为一个子层,完成数据帧的封装、解封、发送和接收功能。

物理层PHY的结构随着传输速率的不同而有一定差异,在100M和1000M以太网中,依次为PCS子层、PMA子层和PMD子层。

MII接口是连接数据链路层和物理层的接口,因为本设计中以太网速率采用100Mb/s,所以MII接口实际连接的是MAC子层和PCS子层。

根据协议,要求MII接口具有的功能有:数据和帧分隔符的读写时钟同步,提供独立的读写数据通道,为MAC层和PCS层提供相应的管理信号,以及支持全双工模式。

扩展MII接口功能及其FPGA实现由于100M以太网的物理层采用4b/5b编码,为了扩展MII接口的功能,要求其能够实现直接物理层5位数据和MAC层8位数据的发送接收传输转换。

即把从MAC子层用于发送的数据和从PHY用于接收的数据存入数据缓冲FIFO,同时要求MII接口将从PHY传来的信号COL、CRS转为信号Carrier和Collision,并提供给MAC子层用于载波监听和冲突检测,以及发送和接收时的时钟、使能、错误位信号的传送。

基于国产FPGA的高速SRIO接口设计与实现

基于国产FPGA的高速SRIO接口设计与实现于东英;陈俊;康令州【摘要】针对具有高速接口的芯片国产化的迫切需求,进行了基于自主研发的国产FPGA平台SRIO接口的设计和验证.首先介绍国产FPGA平台资源和SRIO接口体系结构,结合FPGA厂家提供的IP core进行FPGA内部功能模块设计.其次,重点讨论用户侧接口数据流向方式,对应开发SRIO接口数据流向控制时序代码,并通过软件仿真实现2.5 Gb/s速率的1X SRIO接口逻辑.最后,与xilinx开发板SP605的SRIO接口进行互联互通测试,验证国产FPGA平台上SRIO接口设计的正确性和稳定性.【期刊名称】《通信技术》【年(卷),期】2019(052)001【总页数】4页(P255-258)【关键词】国产FPGA;SRIO;IPCORE;高速数据处理【作者】于东英;陈俊;康令州【作者单位】中国电子科技集团公司第三十研究所,四川成都 610041;中国电子科技集团公司第三十研究所,四川成都 610041;中国电子科技集团公司第三十研究所,四川成都 610041【正文语种】中文【中图分类】TN913.30 引言2015年5月国务院印发《中国制造2025》,是中国政府实施制造强国战略第一个十年行动纲领。

在该行动纲领的指导下,为了提高国家综合国力,成功实现各个产业升级转型,创新与自主发展成为其核心理念之一。

2018年上半年,美国商务部发布对中兴通信的禁止出口令。

该消息一石激起千层浪,对所有国人敲响了警钟,同时明白在很多高科技行业尤其在有“工业石油”之称的芯片方面,必须拥有自主研发的产品,否则将会受制于人。

如果不是在中国自主研发的芯片上进行开发和应用,取得的一切成果就如一座建立在沙子上的城堡。

在提倡创新和自主发展的大背景下,在外部环境瞬息万变的情况下,为了行业长远和健康的发展,必须在芯片领域坚持自主研发和应用。

本文主要是在国产自主研发的FPGA平台上实现高速数据通信接口SRIO的设计与验证。

基于FPGA的串行通信接口设计

模块的实现

1.数据缓冲单元

电源复位后,如果WR_EN是有效 的,则在WR_CLK时钟边沿的作用下数 据被写WR_ADDR相应的数据单元;如果 WR_EN是无效的,则写端口是关闭的。 当RD_EN是有效的,在RD_CLK时钟边 沿的作用下,RD_ADDR地址空间中的数 据读出作为并行到串行转换单元的初始数 据。

基于FPGA的串行通信接口设计

摘要

作为综合任务处理系统的关键处理设备,任务管 理计算机需要与各种设备交联,通信接口的类型 不同。在本文中设计了基于FPGA(现场可编程门 阵列)的串行通信接口,用于与其它设备的数据 通信。它保证了在没有任何硬件资源增加的条件 下串行通信功能实现。它符合硬件设备的标准化 原则。该设计采用Xilinx公司的Virtex-4系列 FPGA芯片,仿真结果表明它满足协议要求。

2.时钟产生单元

ቤተ መጻሕፍቲ ባይዱ.并行到串行的转换单元

并行到串行转换单位主要实现并行数据到串 行数据的转换.Virtex-4提供大量的并行到串行转 换的资源,所以可以实现2倍频到8频率加倍的并 行到串行的转换,适合高速连续转换情况。此模 块的转换率是相当低的,数据量很小。采用将数 据缓冲器和移位寄存器组合以实现并行数据到串 行数据转换。这个方法很简单,适合低速和数据 很少的情况,它可以移植到控制串行接口AD / DA 的实现。

仿真结果

设计完成后,我们进行功能仿真。并行输入数据依次是 “11111111”,“00001111”,“01010101”,“10101010”,图8 示出的波形图,从该波形图中我们可以看出,此程序实现了输入数据 的有效数据位提取,并根据一定的波特率进行串行输出。数据传输是 稳定的,数据输出满足协议要求,具有特定的功能和能力已经通过测 试系统验证。

基于FPGA的1553B总线接口技术研究与实现

基于FPGA的1553B总线接口技术研究与实现FPGA是一种可编程逻辑器件,其内部包含了大量的可配置的逻辑门和存储单元,可以根据需要进行编程,实现各种功能。

1553B总线是一种数据通信协议,用于飞行器和航空航天系统中的数据传输。

基于FPGA的1553B总线接口技术研究与实现是指利用FPGA来实现1553B总线接口的技术和方法。

本文将介绍基于FPGA的1553B总线接口技术的研究与实现。

为了实现基于FPGA的1553B总线接口,需要了解1553B总线的工作原理和通信协议。

1553B总线是一种异步串行通信协议,采用双绞线进行数据传输。

通信包括命令、数据和状态信息。

主机发送命令到从机,然后从机返回响应数据和状态信息。

在数据传输过程中,主机和从机之间需要进行时序控制、错误检测和恢复等操作。

1. 硬件设计:根据1553B总线的通信协议,设计FPGA内部的逻辑电路和数据通路。

逻辑电路主要包括时序控制模块、数据交换模块和错误检测模块等。

数据通路用于完成数据的传输和处理,包括数据解析、校验和错误纠正等功能。

还需要设计与外部设备的接口电路,用于连接外部设备。

2. 软件编程:通过FPGA开发工具进行软件编程,将硬件设计中的逻辑电路和数据通路等功能转化为硬件描述语言,如Verilog或VHDL。

编程过程中,需要考虑时序控制、状态机设计和中断处理等问题,并进行相应的代码优化和测试。

3. 性能优化:在设计和实现的过程中,需要考虑FPGA资源利用率、数据传输速度和电路信号稳定性等问题。

可以通过性能仿真和综合工具进行优化,提高系统的性能和可靠性。

4. 硬件调试和验证:在完成硬件设计和软件编程后,需要进行硬件调试和验证工作。

通过使用测试设备和仿真器等工具,进行信号检测、错误诊断和性能测试等工作,确保系统能够正常工作。

基于FPGA的1553B总线接口技术的研究与实现具有很高的应用价值,在飞行器和航空航天系统中有着广泛的应用。

本文所介绍的技术只是一个基础框架,具体的实现和应用还需要根据具体的需求进行进一步的开发和完善。

基于FPGA的高速以太网接口设计和实现共3篇

基于FPGA的高速以太网接口设计和实现共3篇基于FPGA的高速以太网接口设计和实现1以太网是广泛使用的局域网(LAN)标准,其速度和带宽都非常高,不断发展和改进以满足用户需求。

在现代数据中心和云计算环境中,以太网已变得更加重要,因为它可以提供高速、低延迟和灵活性,使得多个系统之间的通信更加容易和高效。

为了满足这些需求,FPGA成为了一种重要的硬件平台,通过实现高速以太网接口,提供灵活的网络连接。

FPGA是一种可编程的硬件平台,集成了大量的可编程逻辑单元和DSP 资源,可以快速实现各种电路和系统。

基于FPGA的高速以太网接口设计具有以下优点:1. 速度高:基于FPGA的以太网接口可以支持高达40Gbps的数据传输速度,远远快于传统的以太网接口。

2. 低延迟:FPGA内部的可编程逻辑单元可以实现更快的数据处理,并且可以在硬件层面提供更快的响应时间,从而降低网络延迟。

3. 灵活性:FPGA具有可编程性和可重构性,可以根据需要进行实时调整和修改。

此外,FPGA可以通过工具链进行设计和优化,可适应各种硬件需求。

基于FPGA的高速以太网接口设计和实现需要经过以下步骤:1. 设计FPGA电路:使用Verilog或VHDL等硬件描述语言实现电路设计和仿真。

2. 选取以太网MAC:选择适合特定应用场景的以太网MAC,例如10G、25G、40G等。

3. 实现FPGA电路:在FPGA开发板中实现电路设计,FPGA的GPIO口可以与物理层器件、MAC等进行连接,形成完整的以太网接口。

4. 调试和测试:通过网络测试,验证以太网接口的工作状态和性能指标是否达标。

FPGA的以太网接口可以应用于许多领域,例如数据中心、高性能计算、视频监控等,提供高速、可靠的连接。

随着云计算和物联网的迅猛发展,基于FPGA的高速以太网接口设计将变得越来越重要,这将在未来的发展中起到至关重要的作用。

基于FPGA的高速以太网接口设计和实现2以太网是一种最常见的局域网(LAN)技术,它通过使用协议和设备实现计算机和其他设备之间的数据通信。

基于FPGA的SSI通信模块设计

基于FPGA的SSI通信模块设计引言:SSI(Synchronous Serial Interface)是一种高速串行同步通信接口,广泛应用于数据传输、通信和控制系统中。

本文将介绍基于FPGA的SSI通信模块的设计原理、功能设计和硬件实现流程。

一、设计原理SSI通信模块使用基于FPGA的串行通信协议,通过使用FPGA的并行输入输出引脚,将输入并行数据转换成串行数据流,并通过通信线路将数据发送到接收端。

接收端将串行数据流反转回并行数据,并输出到引脚上。

通过这种方式,可以实现高速、可靠的数据通信。

二、功能设计1.并行串行转换:设计一个并行串行转换器,将输入的并行数据转换成串行数据,并通过SSI接口发送。

2.串行并行转换:设计一个串行并行转换器,将接收到的串行数据流转换成并行数据,并输出到引脚上。

3.帧同步:设计一个帧同步模块,通过检测特定的帧同步信号,将数据从串行流中分割成帧,方便后续处理。

4.数据校验:设计一个数据校验模块,对传输的数据进行校验,确保数据的正确性和完整性。

5.时序控制:设计一个时序控制模块,控制数据的传输速率和时序,保证数据的稳定性和可靠性。

三、硬件实现流程1.确定通信协议:根据应用场景和需要传输的数据类型,选择合适的通信协议,并了解其通信格式和时序。

2.FPGA引脚规划:根据通信协议和需要传输的数据位宽,分配FPGA 的引脚,并进行引脚规划。

3.搭建电路结构:根据引脚规划,搭建电路结构,包括并行串行转换器、串行并行转换器、帧同步模块、数据校验模块和时序控制模块。

4.时序优化:根据设计的电路结构,进行时序优化,确保数据的稳定性和可靠性。

5.静态时序分析:对设计的电路进行静态时序分析,以检测和解决时序冲突。

6.功能验证:通过实际测试,验证设计的功能和性能是否满足要求,并对设计进行调优和优化。

总结:本文介绍了基于FPGA的SSI通信模块的设计原理、功能设计和硬件实现流程。

通过使用FPGA的并行输入输出引脚,将输入并行数据转换成串行数据流,并通过通信线路传输数据。

基于FPGA的多串口通信设计与实现

Ke y Wo  ̄S : s e r i a l p o r t ; AS I C; F P GA; UAl k T; i n t e =u p t c o n t r o l l e r ; VHDL

串行通信 因为具有传输线少、 成本低、 配置灵活等特 点, 得到了 广泛应用 , 通用异步收发传 输器 ( Un i v e r s a l As y n c h r o n o u s Re — c e i v e r / Tr a n s mi t t e r ) , 是一种 比较常用的接 口电路 , 主要用于 串行数 据和并行数据的转换。 一般该接 口由专用的UAR T 芯片完成 , 例如 S Cl 6 C 5 5 4 B I B 6 4 , 该接 口芯片具有4 路独立 的通道 , 同时提供多种控 制功能 , 但在实际使用 中往往只使用一种特定控制方式 , 这 不仅造 成 电路复杂和浪费 , 而且会使P C B 面积增 大, 布线复杂 。 [ 1 1 F P G A( F i e l d - P r o g r a mma b l e G a t e Ar r a y ) , 即现场可编程 门 阵列 , 它是作为专用集成电路领域中一种 半定制电路出现 的 , 既解 决了定制 电路的不足, 又克服了原有可编程器件 门电路数有 限的缺 点。 F P G A中具有 丰富的触发器和I / O口, 采用描述语言(ቤተ መጻሕፍቲ ባይዱVHD L 和 V e r i l o g HD L )  ̄行设计 , 用户可以根据需要, 描述 出具有各种功 能的

基于FPGA的光纤通信系统的设计与实现

3 直流平衡 8B/10B 编/解码的 FPGA 实现

8B/10B 编 码 (以 下 简 称 8B/10B)作 为 一 种 高 性 能 的 串 行 数据编码标准,其基本思想就是将一个字节宽度的数据经过 映射机制 (Mapping Rule)转化为 10 为宽度的字符 ,但 是平 衡 了位流中 0 与 1 的个数,也就是所谓的直流平衡特性。 同时 规定位流中 0 或 1 的游程长度 (Run Length)的最大值不能大 于 5,以使得传输过程保持足够高的信号变换频率,这样不仅 确保了时钟恢复也使得信息流的直流频谱分量为零或近乎 为零 , 而 正 是这 些 特 性 使 得 8B/10B 编 码 特 别 适 合 光 纤 等 介 质的连接和信息传输。 3.1 直流平衡 8B/10B 编码

时位同步时钟提取模块提取出同步时钟,为解码模块提供参 考时钟。 最后,接收到的数据经解码后数据输出。

1 光纤通信系统结构设计

光纤通信系统主要由 位 同 步时 钟 提 取模 块 、8B/10B 编 解

码器模块和 NRZI 编解器模块组成, 主要功能框图如图 1 所

示。 数据经 8B/10 编码后,能在很大程度上平衡位流中 0 与 1

(ABCDEFGH)、一个控制信号 (Z)以及一个 时 钟 信号 组 成 ,其 中时钟采样以字节为单位。 控制信号 Z 是数据信号或控制信 号 的 标 示 位 。 输 入 数 据 ABCDEFGH 被 分 成 两 部 分 , 其 中 ABCDE 经 5B/6B 编码生成 6 比特字符 abcdei,而 FGH 经 3B/ 4B 编 码 得 到 fghj, 最 后 组 合 输 出 得 到 10 比 特 的 传 输 字 符 abcdeifghj。

基于FPGA的1553B总线接口技术研究与实现

基于FPGA的1553B总线接口技术研究与实现FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,可以被重新配置以实现不同的功能。

1553B总线是一种广泛应用于军事航空电子系统中的数据传输总线。

本文将介绍基于FPGA的1553B总线接口技术的研究与实现。

需要明确的是,FPGA可以实现1553B总线的接口功能,但并不是所有的FPGA都能够直接与1553B总线进行通信。

一般情况下,需要通过外部接口电路将FPGA与1553B总线进行连接。

这一连接包括数据线、时钟线、控制线等。

本文主要讨论FPGA设计中的接口电路实现。

对于1553B总线接口来说,FPGA需要具备以下功能:1. 接收和发送数据:FPGA需要处理从1553B总线接收到的数据,并将需要发送给1553B总线的数据发送出去。

这包括处理接收到的数据帧、校验数据的合法性,并将需要发送的数据帧组装为符合1553B总线协议的格式。

2. 时序控制:FPGA需要根据1553B总线的时序标准对数据进行采样和发送。

这包括在正确的时机进行数据的读取和写入,以及根据时钟控制数据的传输速率。

3. 错误检测和纠正:FPGA需要实现对数据传输错误的检测和纠正。

这包括校验接收到的数据的合法性,并对错误的数据进行纠正或重新发送。

在实际的设计中,可以使用现有的FPGA开发板或者自定义的FPGA设计板来实现1553B 总线接口。

通过对FPGA的编程,可以实现需要的功能,并与1553B总线进行通信。

实现基于FPGA的1553B总线接口技术的关键是根据1553B总线的协议来设计和实现相应的接口电路。

这包括电路的时序控制、数据处理和错误检测等功能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA数据通信接口的设计与实现

摘要:随着信息化、数字化技术的不断发展,数字集成电路的应用越来越广泛,可编程逻辑器件也由早期的储存少量的数据发展到如今的超大规模复杂组合逻辑与时序逻辑的现场可编程逻辑器件,即FPGA。

本文就对基于FPGA数据通信接口的设计与实现做出研究。

关键词:FPGA 数据通信接口SCI

1 FPGA原理

1.1 FPGA的组成

可编程输入、输出模块、基本可编程逻辑模块、RAM嵌入块、底层嵌入功能ongoing模块以及内嵌专用硬核和线路资源组成了FPGA。

1.2 FPGA设计流程

通常一个完整的FPGA设计流程要包括以下主要步骤:电路的设计、输入—功能仿真—综合优化—验证仿真结果—实现—时序仿真验证—调试加载。

2 通信卡的硬件平台

本系统运用Aurora链路层协议,从而实现SCI节点的高速串行通信,并引入中断机制,以提高SCI通信接口和主机进行数据交换的速

率。

该通信卡利用Virtex-II Pro系列的XC2VP4-FF672C高端FPGA 芯板作为本系统数据处理的主要控制芯片。

通信卡的信号环境为3.3V 的32位CPCI接口和主机进行数据的通信,而各通信卡之间则采用传输速率在1.25Gbps的光纤进行通信。

本系统的通信卡主要由Virtex-II Pro FPGA芯片、时钟产生模组、SFP收发模组、ISP配置PROM以及电源模组和CPCI接口等组成。

3 SCI串行通信接口模型设计与仿真

3.1 SCI整体逻辑划分

FPGA按照功能目的可以分为SCI节点模型模组以及CPCI总线接口模组,其中SCI节点模型包括以下几个部分,即接收和发送RAM、输入及输出旁路FIFO、Address Decode(地址解码器)以及MUX(多路复用)和中断进程、Aurora链路层收发模组(Aurora协议是一个可升级的、小型的链路层协议,可以用来进行点到点的高速串行通路数据传输)等;而CPCI总线接口模组则由PCI内核以及与其相关的配置模组和用户逻辑等三个模组构成,其整体逻辑框图如图2所示。

3.2 SCI的主要功能以及部件原理

Aruoral协议是一个小型但可升级的链路层协议,可以通过它实现点对点的高速串行通路数据的传输。

Aurora链路层协议具有明显的成本较低、带宽高且可以扩展的特点,适用于点对点串行链路的数据传输。

Aurora链路层协议为标准的诸如ICP/IP或者以太网等上层协议,任何分据分组都能通过Aurora链路层协议进行封装,以及在各电路板或者芯片之间进行高速数据传输。

SCI节点模型的模组设计中,中断进程是相对重要的设计部分,它是连接SCI接口两个模块的重要环节。

一旦Aurora的接收模组接收到一祯数据,就会在触发中断的状态下设定其为有效状态,这时中断进程就会在下一时钟触发PCI核内INTT-N信号处于有效状态,此时就表示向PCI核提交中断请求成功。

3.2.1 旁路FIFO

如果SCI节点地址译码结果显示出其传输的目标地址非本机,则数据就会传输到旁路FIFO再由旁路FIFO向另一SCI节点发送。

FIFO 是先进先出堆栈,一般包括读、写指针控制器;存储模块;空信号、满信号输出等部分组成。

FIFO的设计难点在于对空信号输出以及满信号输出信号生成的控制。

旁路FIFO的设计是在同一时间点只允许处于读或写其中一种状态,而读和写状态所采用的相同时钟,所以使用同步旁路FIFO即可。

3.2.2 接收、发送存储器

本系统中采用片上块RAM来实现接收和发送存储器。

块RAM 为双口RAM,其参数可以做调整,存储大小由2KB至128KB不等,A、B两个端口可以同时使用或者单独使用。

在该设计中,PCI总线数据的交互通过块RAM的A口实现,而与Aurora模组的连接则由B口来实现,本设计中FIFO设定4KB,因此对应块RAM的数据线应为32位,地址线则为12位。

RAMBI6seS18_518的主要端口信号定义如下:

.DOA:A端口输出数据线,16位

.ADDRA:A端口地址线,12位

.ADDRB:B端口地址线,12位

.DIA:A端口输入数据线,16位

读写状态机通过控制这些信号线实现对块RAM的数据存取。

3.3 SCI节点工作流程

3.3.1 测试地址

在数据被传输出去以前,主机需要知道本机的地址与环上某机地址是否有冲突,一旦存在冲突则主机就要对地址做相应的修改。

用户要对地址进行修改,并做进一步的测试,直至无地址冲突为止。

3.3.2 寻找接收方

当主机对地址测试完毕后,就可以进行文件的传输,如果找到和主机地址以及开始地址帧中目的地址段相符的的某个机子,那么开始地址帧就会停止传输并被遗弃,那么该对应机子就处于一个允许进行数据接收的状态。

3.3.3 数据的发送

找到相应的机子后就开始发送数据,主机先利用PCI总线读取发送存储器的偏移地址的内容。

在进行数据传输时,主机要先把所要传输的数据长度X写入至发送存储器的偏移地址,然后把需要发送的数据写入发送存储器由偏移地址开始的X个位置,直至数据全部写入。

3.3.4 数据的转发

站在环的角度看,中间主机在进行转发的过程中,由上一个主机传输至该中间主机的数据被接收到以后,是储存在旁路FIFO中的,接着再由旁路FIFO向着下一个中间主机转发,直至达到最后的发送方。

3.3.5 数据的接收

一旦数据被传输至接收方,那么接收方就开始做接收。

因为Aurora的收发模组内并没有设置数据的缓存区,所以主机接收到数据时,要将该数据立刻写入接收缓冲器,不然该数据就会全部丢掉。

所以如果Aurora的收发模块在接收对应主机传输的帧头数据时,要先对接收存储器偏移地址中的内容进行读取。

3.3.6 发送结束传输帧

当发送主机将数据传输完毕后,会接着再发送一个相应的结束地址帧,以通知接收主机当前的数据传送已经结束。

4 结语

本文研究了基于FPGA的SCI通信接口的设计与实现,在FPGA 芯片构建SCI节点,应用Aurora链路层协议实现SCI节点的串行通信。

参考文献

[1] 孙航.Xilinx可编程逻辑器件的高级应用与设计技巧[M].北京:电子工业出版社,2004.

[2] 夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2003.

[3] 姜震.熊华钢.邵定蓉.SCI环平均消息延迟的初步研究[J].遥测遥控,2002(9).

[4] 王诚.薛小刚.FPGA/CPLD设计工具——Xilinx ISE使用详解[M].北京:人民邮电出版社,2005.

[5] 路锦文.基于FPGA的CPCI卡的研究与设计[D].天津工业大学硕士学位论文,2003.。