XILINX Zynq UltraScale+ MPSoC 数据手册概述(中文)

Xilinx Zynq UltraScale+ MPSoC多核异构架构设计详解

Xilinx Zynq UltraScale+ MPSoC多核异构架构设计详解随着人们对计算性能需求的增加以及数据量的显著提升,嵌入式领域传统的微处理器和外设的系统架构设计显得越来越微不足道,除此之外很多应用还要求系统在满足相关行业标准的同时还需要具有可靠性和安全性。

目前在单一的处理器上同时满足处理高带宽数据、执行系统应用程序、响应实时任务请求并满足行业安全标准似乎很难,因此多核异构处理器架构应运而生。

一个多核异构处理系统一般由不同类型的多个单核心或多核心处理器组成,最简单的形式是由一个多核处理器和GPU组成。

图1:异构多核处理器的时代已经到来作为行业的领导者Xilinx正在从产品、工具和理念上来推动从传统可编程逻辑器件向“All Programmable(全可编程)”的转变。

Zynq UltraScale+ MPSoC是Xilinx推出的第二代多处理器SoC器件,采用了16nm FinFET+工艺技术,共分为CG、EG和EV三个系列,都集成了多核应用处理器(四核ARM Cortex-A53应用处理器)、多核图形处理器(双核ARM Mali-400图形处理器)、多核实时处理器(双核ARM Cortex-R5实时处理器)、平台管理单元(电源管理、错误管理、配置管理以及安全管理)和可编程逻辑资源(高性能计算和丰富I/O扩展等)。

与上一代ZYNQ-7000系列相比,其在加密、安全、电源管理和性能方面都得到了显著的增强。

图2:传统系统架构设计向现代一体式整合方式的转变传统的嵌入式系统设计一般都会采用一个或者多个微处理器来实现数据采集、数据处理、人机界面、系统控制等功能,这种方式明显使得系统变得复杂,需要设计生产多块PCB 板卡,增加系统成本。

采用异构多核处理器所有功能都可以用一个处理器来实现,降低了系统PCB设计成本和系统复杂度,但是这对工程师则提出了更高的要求。

对于Zynq UltraScale+ MPSoC的开发,Xilinx为工程师提供了丰富的软硬件设计工具和参考设计产品组合,Vivado设计工具与NI matlab工具相结合实现IP的抽象设计与自动化,。

嵌入式开发之zynqMp---ZynqUltraScale+MPSoC图像编码板zcu102

嵌⼊式开发之zynqMp---ZynqUltraScale+MPSoC图像编码板zcu1021.1 xilinx zynqMp 架构1.1.1 16nm 级别⼯艺 Zynq UltraScale+ MPSoC架构Xilinx新⼀代Zynq针对控制、图像和⽹络应⽤推出了差异化的产品系,这在Xilinx早期的宣传和现在已经发布的⽂档⾥已经说得很清楚了。

她的产品系如图2所⽰。

图2 产品表从图2看到,这个系列的Zynq算是8核(或9核)异构产品:四核的ARM-CortexA53 CPU、双核的Cortex-R5 RPU、Mali-400 GPU(⼀个Geometry核,两个像素核)、PL 逻辑以及视频编解码器Codec核。

在表2中,ZU2E、ZU3E为针对控制类应⽤,逻辑和Block RAM资源较少,没有Video Codec和⾼速收发器。

ZU4E、ZU2E和ZU7E针对视频类应⽤,有内部的UltraRAM资源、Video Codec和GTH⾼速收发器。

其他型号针对⽹络应⽤,除了Video Code没有外,其它⾼⼤上的东西都有,⽐如更⾼速的收发器GTY,还有150G Interlaken和100G Ethernet MAC/PCS/RS-FEC等。

熊猫君是做图像的,下⾯的描述都是针对图像版的Zynq UltraScale+⽽⾔的。

因为PS部分的资源是固定的,⼤家都⼀样,在后⾯⼀起说就⾏。

PL部分因为有这三个东西,将使设计如虎添翼:a)⼤量的Block RAM和Ultra RAM资源,⼩20Mb的内部RAM资源,对分块处理图像,那应该会带来不少的便捷;b)Video Code:这个东西是集成在PL侧的硬核,有了它,图像压缩和解压缩都不⽤愁了;c)GTH:PL端集成的GTH收发器,对SDI、DP等图像接⼝接⼊那是⼗分的⽅便,当然也可以做PCIe咯。

不多说了,熊猫君从Xilinx官⽅⽂档UG1085上截⼀个图来表⽰这个⾼⼤上通⽤SoC的系统级架构,也就是下⾯的图3啦。

Zynq UltraScale+ MPSoC系列新增新型双核器件,提高了ZynqMPSoC产品组合的可扩展性

Zynq UltraScale+ MPSoC系列新增新型双核器件,

提高了ZynqMPSoC产品组合的可扩展性

赛灵思公司(Xilinx)今天宣布其Zynq UltraScale+ MPSoC系列新增新型双核器件。

全新双核CG系列产品提高了ZynqMPSoC产品组合的可扩展性,包含双应用和实时处理器组合。

目前ZynqUltraScale+系列以较低成本切入点增加了双核器件和处理可扩展性,该系列提供四核ARM Cortex-A53、双核Cortex-R5以及一个图形处理单元和一个视频编解码器单元。

设计人员可在可扩展处理组合的三种器件类型中进行选择,以满足多种不同市场的处理要求,包括马达控制、传感器融合、医学内窥镜和手持无线电等。

赛灵思公司高级SoC产品线经理Sumit Shah表示:新型双核CG系列产品能满足客户对可扩展通用硬件平台的需求,通过双核ARM Cortex-A53处理器解决方案赋予他们高度的灵活性。

新产品能满足更丰富的市场和应用需求,提供低成本切入点,并可与ZynqUltraScale+所有产品组合完全相容。

ARM 公司全球市场营销与战略联盟副总裁Ian Ferguson表示:嵌入式市场包括多种不同的应用,客户正在寻求高效可扩展的技术,希望能部署于多种不同的平台和市场。

此外,Zynq产品组合前所未有地更加丰富,可以支持多种ARM处理器,使用户能在任何应用中重复使用IP和代码,因而将大幅加速客户产品上市进程。

一种基于Zynq UltraScale+的HDMI 4K高清视频会议终端的设计与实现

信息通信INFORMATION & COMMUNICATIONS2020年第8期(总第212期)2020(Sum. No 212)一种基于 Zynq UltraScale+ 的 HDMI4K 高清视频会议终端的设计与实现蹇清平(天地阳光通信科技(北家)有限公司,北京100000)摘要:文章针对高清视频会议系统的视频图像传输应用,基于赛灵思ZCU106开发板设计并实现了 一种嵌入式的多路传 输视频会议终端,该系统实现双路4K2KHDMI 输入输出,一路4KDP 输出的高清视频会议终端,同时可通过千兆网 RTP/UDP 实现远程视频传输,视频編解码算法H.265/H.264采用赛灵思专用的VCU 核实现,編解码速度最高可达到 4K2K60HZ 。

该系统体积小、实时性好、稳定性高,达到预期设计目标,音视频流畅,处理时延小于100ms,能够满足高清视 频会议系统的性能要求。

关键词:高清视频会议;VCU ; H.265/H.264; 4K2K60HZ ;千兆网RTP/UDP 中图分类号:TN919.8 文献标识码:A 文章编号:1673-1131( 2020 )08-0137-03Design and Inqiknientation of H DMI 4K H D Video Conference Tenniiial based on ZynqUMraScale +Jian Qingping(Beijing Tiandi Sunshine Technology Co., Ltd., BeyinglOOOOO)Abstract:This article aims at the video image transmission 皱plication of h igh-definition video conference system, The designand implements of an embedded multi-channel transmission video conference terminal is base on Xilinx ZCU106 develqim^it board, the system realizes the dual 4K2K HDMI input and output, one channel 4K DP The output of the high-definition videoconference terminal. And can also realize remote video transmission through Gigabit network RTP / UDP. The video codec al gorithm H.265 / H.264 is implemented by Xilinx's dedicated VCU core, and the codec speed can reach 4K2K60HZ. The systemhas small size, good real-time performance and high stability. It achieves the expected design goals, smooth audio and video,and processing delay ofless than 100ms, which can meet the performance requirements ofhigh-definition video conference sys tems.KeywordszHD video conference;VCU;H.265/H.264;4K2K60HZ;Gigabit RTP/UDP0引言随着科技的发展,在商业、教育、安防以及人们生活的方 方面面对高清视频的需求越来越旺盛,在远程办公的应用上 尤为突出。

XILINX_zynq_详解(1)

XILINX_zynq_详解(1)Xinlix的FPGA确实做的是⼜⼤⼜强,接触FPGA有5、6年的时间,从没有详细的了解⼀下FPGA是什么?FPGA可以做什么?FPGA的溯源在哪⾥?FPGA的⼚商有哪些?FPGA的选型该怎么进⾏?FPGA在⼈⼯智能上会有什么发展前景?FPGA该如何学习?FPGA的着⼒点该在什么地⽅? 接着新开园的新鲜劲,做⼀下总结,因为涉及内容较多,为了能浅显易懂的介绍好各个问题,有必要也必须拉出⼀条主线来。

稍微⾛个神,为什么写博客?很多⼈在写,我个⼈意见,写博客不是⽬的,⽬的是能够将知识系统的总结⼀下。

在⽹络上泛泛的看来的东西,太杂太不系统,如果不整理⼀下、消化⼀下,可能还是没有⼀点进步,所以要写出来,总结下来。

好,来拉⼀条主线?什么是FPGA【定义】→FPGA的⼚家有哪些【选型】→FPGA是什么、FPGA可以做什么【应⽤】—————————————我是分隔符———————————————————————————①什么是FPGA? FPGA-Field Programmable Gate Array,现场可编程门阵列,它是在其他可编程器件,如PAL\GAL\CPLD的基础上进⼀步发展的产物,也是为ASIC(专⽤集成电路)领域中的⼀种半定制电路⽽出现的,克服了原有可编程器件门电路书有限的缺点,FPGA⼀般来说⽐ASIC(专⽤集成电路)的速度要慢,实现同样的功能⽐ASIC电路⾯积要⼤。

但是他们也有很多的优点⽐如可以快速成品,可以被修改来改正程序中的错误和更便宜的造价。

⼚商也可能会提供便宜的但是编辑能⼒差的FPGA。

因为这些有⽐较差的可编辑能⼒,所以这些设计的开发是在普通的FPGA上完成的,然后将设计转移到⼀个类似于ASIC的芯⽚上。

另外⼀种⽅法是⽤CPLD(Complex Programmable Logic Device,复杂可编程逻辑器件)。

【摘⾃度娘】 看来很成功的产物,发展壮⼤的过程不可避免的会经历艰难困苦,FPGA也不例外,1985年的冬天,全球⾸款FPGA产品⽐我早2年出⽣了,起名:XC2064,诞⽣宣⾔:未来⼗年内每⼀个电⼦设备都将有⼀个可编程逻辑芯⽚!当时呱呱落地的它可能想不到,今天的它确实实现了这个理想。

Zynq UltraScale+开发平台AXU15EG用户手册说明书

Zynq UltraScale+开发平台AXU15EG开发板2 / 56芯驿电子科技(上海)有限公司文档版本控制目录文档版本控制 (2)一、开发板简介 (6)二、ACU15EG核心板 (9)(一)简介 (9)(二)ZYNQ芯片 (10)(三)DDR4 DRAM (11)(四)QSPI Flash (18)(五)eMMC Flash (19)(六)时钟配置 (21)(七)电源 (23)(八)结构图 (24)(九)连接器管脚定义 (24)三、扩展板 (33)(一)简介 (33)(二)M.2接口 (34)(三)DP显示接口 (35)(四)USB3.0接口 (36)(五)千兆以太网接口 (37)(六)USB Uart接口 (39)(七)SD卡槽 (40)(八)光纤接口 (41)(九)CAN通信接口 (42)(十)485通信接口 (42)(十一)MIPI接口 (43)(十二)FMC连接器 (44)(十三)40针扩展口 (48)(十四)JTAG调试口 (49)(十五)RTC实时时钟 (50)(十六)EEPROM和温度传感器 (51)3 / 564 / 56芯驿电子科技(上海)有限公司(十七) LED 灯 .......................................................................................................................... 52 (十八) 按键 .............................................................................................................................. 52 (十九) 拨码开关配置 .............................................................................................................. 53 (二十) 电源 .............................................................................................................................. 54 (二十一) 风扇 ......................................................................................................................... 54 (二十二) 结构尺寸图 (56)5 / 56芯驿电子科技(上海)有限公司 基于XILINX Zynq UltraScale+ MPSoCs 开发平台的开发板(型号:AXU15EG )2020款正式发布了,为了让您对此开发平台可以快速了解,我们编写了此用户手册。

XilinxUltraScale架构-业界首款ASIC级AllProgrammable架构

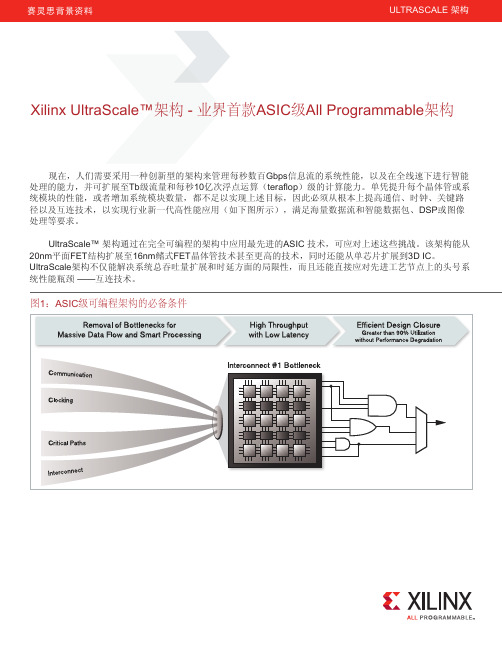

赛灵思背景资料ULTRASCALE 架构Xilinx UltraScale™架构 - 业界首款ASIC级All Programmable架构现在,人们需要采用一种创新型的架构来管理每秒数百Gbps信息流的系统性能,以及在全线速下进行智能处理的能力,并可扩展至Tb级流量和每秒10亿次浮点运算(teraflop)级的计算能力。

单凭提升每个晶体管或系统模块的性能,或者增加系统模块数量,都不足以实现上述目标,因此必须从根本上提高通信、时钟、关键路径以及互连技术,以实现行业新一代高性能应用(如下图所示),满足海量数据流和智能数据包、DSP或图像处理等要求。

UltraScale™ 架构通过在完全可编程的架构中应用最先进的ASIC 技术,可应对上述这些挑战。

该架构能从20nm平面FET结构扩展至16nm鳍式FET晶体管技术甚至更高的技术,同时还能从单芯片扩展到3D IC。

UltraScale架构不仅能解决系统总吞吐量扩展和时延方面的局限性,而且还能直接应对先进工艺节点上的头号系统性能瓶颈 ——互连技术。

图1:ASIC级可编程架构的必备条件• Monolithic to 3D IC • Planar to FinFET • ASIC-class performance图2 :新一代高性能目标应用实图中,高速数据流(Tbps 级的汇聚速率)从左侧进入再从右侧流出。

可通过运行速度为数Gbps 的高速SerDes 收发器进行I/O 传输。

一旦以数Gbps 速度传输的串行数据流进入芯片,就必须扇出(fan out ),以便与片上资源的数据流、路由和处理能力相匹配。

新一代系统要求使用极高的数据速率,因此时钟歪斜、大量总线布置以及系统功耗管理方面的挑战会达到令人生畏的程度。

图3:为您量身定做的新一代架构UltraScale™架构具有无与伦比的高集成度、高容量和ASIC 级系统性能,可满足最严苛应用的要求。

UltraScale 架构经过精调可提供大规模布线能力并且与Vivado ®设计工具进行了协同优化,因此该架构的利用率达到了空前的高水平(超过90%),而且不会降低性能。

Xilinx扩展ZynqUltraScaleRFSoC系列

94M i c r o c o n t r o l l e r s &E m b e d d e d S ys t e m s 2019年第4期w w w .m e s n e t .c o m .c n下一代A r m v 8.1M 架构为最小型嵌入式设备提供强化的机器学习能力A r m 宣布针对其下一代A r m v 8.1M 架构推出基于MP r o f i l e V e c t o r E x t e n s i o n (MV E )矢量扩充方案的A r m H e l i u m 技术㊂这一全新技术能够帮助开发者简化软件开发流程,并显著提升未来C o r t e x M 系列处理器的机器学习能力与信号处理性能㊂A r m H e l i u m 技术针对A r m C o r t e x M 系列处理器设计,在A r m T r u s t Z o n e 的安全基础上,通过M P r o f i l e V e c t o r E x t e n s i o n 矢量扩展加强A r m v 8.1M 架构的计算性能㊂H e l i u m 将为未来的A r mC o r t e x M 系列处理器提供高达15倍的机器学习性能提升和高达5倍的信号处理性能提升,消除因性能挑战造成的对低成本㊁高能效设备的使用限制,从而为我们的合作伙伴带来全新的市场机遇㊂X i l i n x 扩展Z y n q Ul t r a S c a l e +R F S o C 系列赛灵思宣布,其屡获殊荣的Z y n q Ul t r a S c a l e +射频(R F )片上系统(S o C )产品系列再添新品,具有更高射频(R F )性能及更强可扩展能力㊂新一代器件建立在Z y n qU l t r a S c a l e +R F S o C 基础产品系列在多个市场的成功之上,可支持6G H z 以下所有频段,从而满足新一代5G 部署的关键需求㊂同时,还可支持针对采样率高达5G s /s 的14位模数转换器(A D C )和10G s /s 的14位数模转换器(D A C )进行直接R F 采样,二者的模拟带宽均高达6G H z㊂新产品单芯片集成更高性能的R F 数据转换器,可为部署5G 无线通信系统㊁有线电视接入㊁高级相控阵雷达解决方案,以及包括测量测试和卫星通信在内的其他应用,提供所需的广泛频段覆盖范围㊂通过取代分立式组件,这些器件可将功耗及封装尺寸锐降50%,是电信运营商部署5G 系统实现大规模多输入多输出基站的理想选择㊂最新S T M 32W B 双核无线M C U 实现超低功耗实时性能意法半导体的S T M 32W B x 5双核无线微控制器(M C U )配备B l u e t o o t h 5㊁O p e n T h r e a d 和Z i gB e e 3.0连接技术,同时兼备超低功耗性能㊂通过整合意法半导体的S T M 32L 4A r mC o r t e x M 4M C U 的功能与意法半导体内部开发的由一颗C o r t e x M 0+专用内核管理的射频芯片,S T M 32W B x 5既注重节能降耗,又能同时执行无线协议和实时任务,是远程传感器㊁可穿戴跟踪器㊁楼宇自动化控制器㊁计算机外围设备㊁无人机和其他物联网设备的理想选择㊂数据安全功能强化了S TM 32W B x 5的物联网首选微控制器的美誉度㊂安全功能包括客户密钥存储(C K S )㊁公钥授权(P K A )以及无线MA C 层和顶层的加密引擎㊂C o r t e x M 0+内核管理的安全功能,包括用于应用和射频协议栈的O T A 安全固件更新,可保护设备的完整性和知识产权,并让产品管理变得简单可靠㊂M i c r o c h i p 推出基于Po l a r F i r e F P G A 的解决方案M i c r o c h i p 推出的全新Po l a r F i r e F P G A 图像和视频解决方案支持高达4K 的分辨率,其体积小巧,功耗极低,可广泛用于各种图像和视频应用,相比业界其他技术有着显著的优势,是应对上述挑战的极佳选择㊂M i c r o c h i p 的P o l a r F i r e F P G A 系列解决方案屡获殊荣,最早于2017年2月由M i c r o s e m i C o r p o r a t i o n (美高森美公司,现为M i c r o -c h i p 全资子公司)推出㊂相较基于静态随机存取存储器(S R AM )的同类产品,该解决方案的功耗在最低时只有同类产品的50%,不仅如此,它们还具有较大的存储空间和数字信号处理器(D S P )资源,是中等带宽(4K /2K )图像/视频应用的理想选择㊂最新图像和视频解决方案为客户提供了一套完整的生态系统,包括综合全面的特定应用硬件㊁针对图像处理优化的知识产权套件㊁样本参考设计㊁演示设计和配套材料,为设计人员提供基于P o l a r F i r e F P G A实现4K 分辨率所需的硬件和软件㊂D i a l o g 为华为荣耀F l yP o d s 无线耳机提供音频和可配置混合信号芯片组D i a l o g 半导体公司宣布,其音频和可配置混合信号I C (C M I C )被华为的最新荣耀F l yP o d s 真无线立体声耳机所采用㊂D i a l o g Sm a r t B e a t D A 14195系统级芯片(S o C )被集成到每个F l y P o d 耳机中,并连接到一对语音拾取(V P U )传感器㊂片上音频数字信号处理器(D S P )和A R MC o r t e x M 0微控制器用来提供极低功耗㊁高准确率的语音控制㊂系统通过测量语音经过耳道时产生的振动来检测佩戴者何时发出语音命令,提供了即使在嘈杂环境中也能运行的语音用户界面㊂华为荣耀F l y P o d s 的充电方面配置了D i a l o g 的G r e e n P A K I C ,为充电盒和每个耳机之间提供了低成本的电力线通信解决方案㊂共采用了三颗G r e e n P A K I C ,其中两颗分别用于两个耳机中,还有一颗用于充电盒㊂是德科技推出具有2G H z 带宽的双通道44G H z 矢量信号发生器是德科技推出第一款双通道微波信号发生器,该产品。

zynq-ultrascale-plus-product-selection-guide

Page 4

© Copyright 2016 Xilinx

.

Zynq® UltraScale+™ MPSoCs: EG Block Diagram

Processing System

Application Processing Unit

ARM® Cortex™-A53

32KB I-Cache w/Parity 32KB D-Cache w/ECC

System Functions

Multichannel DMA Timers, WDT, Resets, Clocking & Debug

General Connectivity

GigE USB 2.0 CAN UART SPI Quad SPI NOR NAND SD/eMMC

Programmable Logic

103K–600K System Logic Cells • • • • Sensor Processing & Fusion Motor Control Low-cost Ultrasound Traffic Engineering

103K–1143K System Logic Cells • • • • • • • • • Flight Navigation Missile & Munitions Military Construction Secure Solutions Networking Cloud Computing Security Data Center Machine Vision Medical Endoscopy

Applications

Page 2

© Copyright 2016 Xilinx

Xilinx 16nm UltraScale+器件实现2至5倍的性能功耗比优势

Xilinx 16nm UltraScale+器件实现2至5倍的性能功耗比优势Mike Santarini 赛灵思公司赛灵思杂志发行人*************************台积公司的16nm FinFET工艺与赛灵思最新UltraRAM和SmartConnect技术相结合,使赛灵思能够继续为市场提供超越摩尔定律的价值优势。

赛灵思凭借其28nm 7系列全可编程系列以及率先上市的20nm UltraScale?系列,获得了领先竞争对手整整一代优势,在此基础上,赛灵思刚刚又推出了其16nm UltraScale+?系列器件。

客户采用该器件系列构建的系统相比采用赛灵思28nm器件所设计的类似系统的性能功耗比可提升2至5倍。

这些性能功耗比优势主要取决于三大方面:采用台积电公司16FF+(即16nm FinFET Plus)工艺的器件实现方案、赛灵思的片上UltraRAM存储器以及SmartConnect创新型系统级互联-优化技术。

此外,赛灵思还推出了其第二代Zynq?全可编程SoC。

Zynq UltraScale多处理SoC (MPSoC) 在单个器件中完美集成了四核64位ARM? Cortex?-A53应用处理器、32位ARM Cortex-R5实时处理器、ARM Mali-400MP图形处理器、16nm FPGA逻辑(带UltraRAM)、众多外设、安全性与可靠性特性、以及创新型电源控制技术。

该新型Zynq UltraScale+ MPSoC为用户提供了系统创建所需的一切,而且利用其打造出来的系统相比采用28nm Zynq SoC所设计的系统的性能功耗比提升5倍。

FINFET进一步扩展 ULTRASCALE系列,使其具有额外的节点价值优势赛灵思公司芯片产品管理与营销高级总监Dave Myron指出:“采用16nm UltraScale+系列,我们能够创建出比摩尔定律通常提供给用户的更高的额外节点价值优势。

Zynq UltraScale+ 开发平台 ACU2CG 核心板 ACU2CG 用户手册说明书

Zynq UltraScale+开发平台ACU2CG核心板2 / 25芯驿电子科技(上海)有限公司文档版本控制目录文档版本控制 (2)一、ACU2CG核心板 (4)(一)简介 (4)(二)ZYNQ芯片 (5)(三)DDR4 DRAM (6)(四)QSPI Flash (10)(五)eMMC Flash (11)(六)时钟配置 (13)(七)LED灯 (15)(八)电源 (15)(九)结构图 (17)(十)连接器管脚定义 (17)3 / 254 / 25芯驿电子科技(上海)有限公司一、 ACU2CG 核心板(一) 简介ACU2CG(核心板型号,下同)核心板,ZYNQ 芯片是基于XILINX 公司的Zynq UltraScale+ MPSoCs CG 系列的XCZU2CG-1SFVC784E 。

这款核心板PS 端挂载了4片Micron 的DDR4芯片,组成64位数据总线带宽和2GB 的容量。

DDR4 SDRAM 的最高运行速度可达1200MHz(数据速率2400Mbps)。

另外核心板上也集成了1片256MBit 大小的QSPI FLASH 和8GB 大小的eMMC FLASH 芯片,用于启动存储配置和系统文件。

为了和底板连接,这款核心板的4个板对板连接器扩展出了PS 端的USB2.0接口,千兆以太网接口,SD 卡接口及其它剩余的MIO 口;也扩展出了4对PS MGT 高速收发器接口;以及PL 端的几乎所有IO 口(HP I/O :96个,HD I/O :84个),XCZU2CG芯片到接口之间走线做了等长和差分处理,并且核心板尺寸仅为80*60(mm ),对于二次开发来说,非常适合。

ACU2CG 核心板正面图ACU2CG用户手册(二)ZYNQ芯片XCZU2CG-1SFVC784E芯片的PS系统PS系统集成了2个ARM C ortex™-A53处理器,速度高达1.2Ghz,支持2级Cache; 另外还包含2个Cortex-R5处理器,速度高达500Mhz。

ZynqUltraScaleRFSoC的潜力与局限性

ZynqUltraScaleRFSoC的潜力与局限性Zynq UltraScale+ RFSoC的多功能集成最显著的好处是,内置了模数转换器和数模转换器,与多设备方案相比,降低了材料耗费和成本,且节约了约50%的空间,从而可以将其他功能模块安装到电路板上,此外还降低了设备重量。

Pentek公司举了一个例子说明这些好处。

要具有与RFSoC相同的功能,设计人员需要以下组件:·ARM多核处理器·4个4GS/s速率的模数转换器·4个6.4GS/s速率的数模转换器·UltraScale+数字化射频存储器(与射频系统级芯片的逻辑和数字信号处理密度一样)除了设计和测试电路所需的要求和时间外,分布式组件的成本大约是RFSoC的两倍。

此外,由于模数转换器和数字化射频存储器集成在同一个系统级芯片上,所以可以实现高速并行处理,而不需要精确地在电路板上连接。

RFSoC对直流功率有严格的限制,因为它需要13种不同的电压和电流,所有这些要求信号干净并进行良好的调节。

RFSoC产生的大量数据,需要不止一种方法才能从电路板上获取数据,从第3代PCIe开始,数据传输速率可以达到6.4GB/s。

RFSoC具有8个采样速率为4GS/s的模数转换器,每个芯片的采样速率为8GS/s,当模数转换器在6.4GS/s的采样速率下工作时,输入数据的数据传输速率可达64GB/s。

因此,PCIe和芯片中2个数据传输速率为100GB/s的以太网端口配合,它们一起以24GB/s的数据传输速率,将信号传输到用于存档和分析的交换机或其他子系统。

一些公司交付的基于RFSoC的电路板,将以太网端口转换为VITA 66光链路,这些光链路的优点是电磁干扰和射频干扰为零,且可以在任何环境下保持信号完整性。

尽管RFSoC有巨大的潜力,但它并不是所有应用程序的灵丹妙药,和所有设备一样,它也有局限性。

Abaco公司的Hensen说:“当存在很多通道时,Zynq UltraScale+ RFSoC可以显著缩小系统的尺寸。

ZynqUltraScaleMPSoC的嵌入式最小系统开发

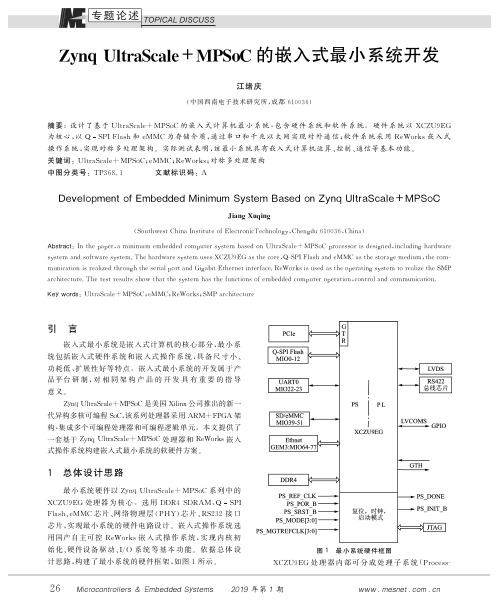

Z y n q Ul t r a S c a l e +M P S o C 的嵌入式最小系统开发江绪庆(中国西南电子技术研究所,成都610036)摘要:设计了基于U l t r a S c a l e +M P S o C 的嵌入式计算机最小系统,包含硬件系统和软件系统㊂硬件系统以X C Z U 9E G为核心,以Q S P I F l a s h 和e MM C 为存储介质,通过串口和千兆以太网实现对外通信;软件系统采用R e W o r k s 嵌入式操作系统,实现对称多处理架构㊂实际测试表明,该最小系统具有嵌入式计算机运算㊁控制㊁通信等基本功能㊂关键词:U l t r a S c a l e +M P S o C ;e MM C ;R e W o r k s;对称多处理架构中图分类号:T P 368.1 文献标识码:AD e v e l o p m e n t o fE m b e d d e d M i n i m u m S y s t e m B a s e d o n Z y n q Ul t r a S c a l e +M P S o C J i a n g X u q i n g(S o u t h w e s t C h i n a I n s t i t u t e o f E l e c t r o n i c T e c h n o l o g y ,C h e n gd u 610036,C h i n a )A b s t r a c t :I n t he p a p e r ,a m i n i m u m e m b e d d e d c o m p u t e r s y s t e m b a s e d o n U l t r a S c a l e +M P S o C p r o c e s s o r i s d e s i g n e d ,i n c l u d i n g ha r d w a r e s y s t e m a n d s o f t w a r e s y s t e m.T h e h a r d w a r e s y s t e m u s e s X C Z U 9E G a s t h e c o r e ,Q -S P I F l a s h a n d e MM C a s t h e s t o r a ge m e d i u m ,t h e c o m -m u n i c a t i o n i s r e a l i z e d t h r o u g h t h e s e r i a l p o r t a n d G i g a b i t E t h e r n e t i n t e rf a c e .R e W o r k s i s u s e d a s t h e o p e r a t i ng s ys t e m t o r e a l i z e t h e S M P a r c h i t e c t u r e .T h e t e s t r e s u l t s s h o w t h a t t h e s y s t e m h a s t h e f u n c t i o n s o f e m b e d d e d c o m p u t e r o pe r a t i o n ,c o n t r o l a n d c o mm u n i c a t i o n .K e y wo r d s :U l t r a S c a l e +M P S o C ;e MM C ;R e W o r k s ;S M P a r c h i t e c t u r e引 言嵌入式最小系统是嵌入式计算机的核心部分,最小系统包括嵌入式硬件系统和嵌入式操作系统,具备尺寸小㊁功耗低㊁扩展性好等特点㊂嵌入式最小系统的开发属于产品平台研制,对相同架构产品的开发具有重要的指导意义㊂Z y n q Ul t r a S c a l e +M P S o C 是美国X i l i n x 公司推出的新一代异构多核可编程S o C ,该系列处理器采用A R M+F P G A 架构,集成多个可编程处理器和可编程逻辑单元㊂本文提供了一套基于Z y n q Ul t r a S c a l e +M P S o C 处理器和R e W o r k s 嵌入式操作系统构建嵌入式最小系统的软硬件方案㊂1 总体设计思路最小系统硬件以Z y n q Ul t r a S c a l e +M P S o C 系列中的X C Z U 9E G 处理器为核心㊂选用D D R 4S D R AM ㊁Q S P IF l a s h ㊁e MM C 芯片㊁网络物理层(P H Y )芯片㊁R S 232接口芯片,实现最小系统的硬件电路设计㊂嵌入式操作系统选用国产自主可控R e W o r k s 嵌入式操作系统,实现内核初始化㊁硬件设备驱动㊁I /O 系统等基本功能㊂依据总体设计思路,构建了最小系统的硬件框架,如图1所示㊂图1 最小系统硬件框图X C Z U 9E G 处理器内部可分成处理子系统(P r o c e s s -i n g S y s t e m ,P S )和可编程逻辑(P r o g r a mm a b l e L o gi c ,P L )[1]㊂P S 集成了多个可编程处理器,包括C o r t e x A 53核㊁C o r t e x R 5核㊁M a l i 400G P U 核以及可编程逻辑单元㊂P S 还集成了O C M ㊁D D R 控制器接口㊁M I O (M u l t i -pl e x e d I O )以及高速串行收发接口㊂P L 提供大规模的可编程逻辑块(C L B )㊁B l o c k R AM ㊁D S P 模块,提供可配置的通用I /O 和高速串行收发接口㊂P S 和P L 通过A X I 总线完成二者间的交互㊂最小系统的设计实现过程分为三个阶段:硬件电路设计㊁处理器硬件平台配置和R e W o r k s 操作系统镜像生成与烧写㊂2 硬件电路设计2.1 电源设计最小系统的电源设计分为两级:第一级转换器选用D C D C 转换器,将5V 输入电压转换为系统需要的各种电压;第二级转换器L D O 将内部电源转换为更加纯净的电压源,满足P L L 等更严苛的电源需求㊂电源设计如图2所示㊂图2 电源设计框图2.2 时钟设计最小系统的参考时钟P S _R E F _C L K 采用频率为33.333MH z ㊁C MO S 电平的时钟信号㊂P S 子系统内需要的所有时钟频率都经过处理器内部锁相环(P L L )倍频和分频得到㊂2.3 启动模式设计处理器支持多种启动模式,可以从多种引导设备获取启动程序镜像㊂芯片上电复位后采样b o o t _m o d e [3:0]引脚,根据采样值决定启动模式[2]㊂本系统通过拨码开关改变b o o t _m o d e [3:0]引脚的值,从而选择不同启动模式,本系统支持的三种启动模式如表1所列㊂表1 处理器启动模式启动模式b o o tm o d e [3:0]使用场景J T A G 0000多用于调试,使用J T A G 仿真器下载调试软件Q S P I 0001启动程序镜像存放在Q S P I F l a s h 中e MM C0110启动程序镜像存放在e MM C 中2.4 D D R 4设计处理器的D D R 接口控制器外接D D R 4芯片㊂芯片选用美国M i c r o n 公司生产的M T 40A 512M 16J Y ,单片位宽为16位,D D R 4接口最高速率为2400M b ps ㊂4片D D R 4芯片并行连接组成的总位宽为64位㊁总容量为4G B 的处理器内存㊂D D R 4的V t t 电压由T P S 51200提供㊂2.5 Q S P I F l a s h 设计处理器的P S 端通过M I O [0:5]挂接一片Q S P IF l a s h ,用于存放启动程序镜像文件㊂F l a s h 选用S p a n s i o n 公司生产的S 25F L 128S A GM F I R 01芯片㊂2.6 e M M C 设计e MM C 芯片是一种内嵌N a n d F l a s h 控制器的新型存储芯片,特点是小尺寸㊁大容量㊁高速度㊂P S 通过M I O [46:51]实现1路e MM C 接口,e M -M C 芯片选用M i c r o n 公司生产的M T F C 32G J D D Q芯片,最大可提供32G B 的非易失性存储空间,用作数据记录和程序存储㊂实现这部分接口的M I O 属于P S 端的b a n k 501,由3.3V 电压供电㊂2.7 异步串口设计P S 通过M I O [18:19]实现1路U A R T 接口㊂U A R T 接口通过外接M A X I M 公司的串口电平转换芯片M A X 3232实现R S 232异步串口㊂异步串口用于与P C 机的通信,实现调试信息的输入与输出㊂2.8 网口电路设计P S 内部集成有3个千兆以太网控制器,本设计应用G E M 3㊂处理器通过M I O [64:77]实现1路MA C接口,连接M a r v e l l 公司生产的88E 1512千兆网P H Y 芯片,引出1路千兆以太网口㊂实现这部分接口的M I O 属于P S 端的b a n k 502,由1.8V 电压供电㊂3 处理器硬件平台配置X C Z U 9E G 处理器的底层硬件架构具有可配置性,配置内容主要包含时钟配置㊁M I O 接口配置㊁D D R 接口配置等方面㊂配置过程使用X i l i n x 公司提供的V i v a d o2017.2软件,通过图形化界面对底层硬件进行配置,实现差异化的硬件架构设计[3]㊂3.1 时钟配置P S 的系统参考时钟频率为33.333MH z㊂配置芯片内部5个P L L ,然后设置各时钟子系统的倍频与分频参数,得到芯片内各控制器需要的时钟㊂最小系统片内时钟子系统最终工作参数设置为:4个A P U 工作频率为1.2G H z ,2个R P U 工作频率为500MH z ,G P U 工作频率为400MH z ,QS P I 接口控制器工作频率为125MH z,U A R T 控制器工作频率为100MH z ,网络接口控制器工作频率为125MH z ,S D I O 控制器工作频率为200MH z㊂3.2 D D R 4接口配置D D R 4硬件设计选用4片16位的D D R 4芯片组成总位宽为64位㊁总容量为4G B 的内存㊂D D R 4接口时钟配置为1067MH z ,行地址为15,列地址为10㊂b a n k 地址位配置为2㊂D D R 4的接口配置如图3所示㊂图3 D D R 4的接口配置3.3 M I O 接口配置X C Z U 9E G 处理器的M I O 是功能复用引脚,每一个M I O 引脚都支持多种备选接口,78个M I O 引脚共分为3个b a n k ㊂根据最小系统硬件电路设计,b a n k 500部分[M I O (0:25)]配置Q S P I 接口㊁U A R T 接口,接口电平配置为3.3V ㊂b a n k 501部分[M I O (26:51)]配置e MM C 接口,接口电平配置为3.3V ㊂b a n k 502部分[M I O(52:77)]配置千兆以太网的MA C 接口,接口电平配置为1.8V ㊂本设计中M I O 的具体配置如表2所列㊂表2 M I O 的配置4 R e W o r k s 操作系统镜像生成与烧写4.1 镜像文件的生成与烧写R e W o r k s 操作系统是中国电子科技集团第三十二研究所推出的嵌入式操作系统,具备高实时性,支持多核处理器㊁多任务管理㊂在本设计中,嵌入式操作系统在4个64位的C o r t e x A 53核上运行㊂采用开发平台R e d e ,将操作系统配置成支持S M P 模式㊁多任务优先级调度㊁文件系统㊁网络协议栈,最终编译得到r e w o r k s .e l f 镜像文件㊂R e W o r k s 操作系统的引导采用X i l i n x 公司S D K 开发平台编译生成f s b l .e f l 镜像文件㊂F S B L 完成对M I O ㊁P L L ㊁时钟㊁D D R 4的初始化,并加载操作R e W o r k s 镜像㊂利用S D K 的C r e a t e B o o t I m a ge 工具将f s b l .e f l 和r e w o r k s .e f l 文件合并生成一个新的b o o t .b i n 的二进制文件,再利用S D K 的P r o gr a m F P G A 工具将b o o t .b i n 文件烧写到X C Z U 9E G 处理器外接的Q S P I F l a s h 中㊂4.2 R e W o r k s 操作系统的启动X C Z U 9E G 处理器加电后启动过程分为三个阶段[4]:①P r e -c o n f i gu r a t i o n 阶段,芯片执行P MU R OM 代码初始化处理器;②C o n f i g u r a t i o n 阶段,芯片将F S B L (f i r s t -s t a ge b o o t l o a d e r )代码从Q S P I F l a s h 搬移到处理器内部O C M 并运行F S B L ;③P o s t -c o n f i gu r a t i o n ,加载并运行R e -W o r k s 操作系统镜像㊂R e W o r k s 镜像在由F S B L 引导成功后,跳转到s t a r t .s文件的s t a r t ()函数中执行㊂从s t a r t ()函数开始执行,整个过程主要完成了以下步骤:处理器㊁内存和目标机初始化;R e W o r k s 核心功能初始化;系统配置初始化;用户配置初始化;执行应用软件入口函数u s r I n i t()[5]㊂经历以上几个阶段,R e W o r k s 操作系统在最小系统硬件平台上建立成功,操作系统建立信息如图4所示,X C Z U 9E G 处理器的4个C o r t e x A 53内核在S M P 对称多处理架构下实现并行工作㊂图4 R e W o r k s 操作系统建立信息5 最小系统测试5.1 测试平台的搭建根据最小系统的设计功能,搭建如图5所示的测试平台㊂最小系统的调试串口和千兆网口直接与P C 机连接,直流稳压电源通过测试板卡给最小系统供电㊂图5 测试平台框图5.2 测试方法为了测试最小系统的指标,制定以下测试方法:①处理器测试㊂通过读取处理器相应的状态寄存器对处理器多核运行状态㊁内核工作频率进行测试㊂②通信测试㊂利用P C 机的网络和串口对最小系统的网口㊁串口功能进行测试㊂③内存测试㊂对D D R 4进行读写测试和容量大小测试㊂④e MM C 测试㊂对e MM C 进行读写速度测试和容量大小测试㊂⑤Q S P I F l a s h 测试㊂对Q S P I F l a s h 进行读写速度测试和容量大小测试㊂⑥操作系统测试㊂硬件功能测试均在R e W o r k s 嵌入式操作系统下进行㊂5.3 测试结论经过测试,最小系统各个指标均通过测试,测试结果如图6所示㊂结果表明,本系统的各项指标均满足设计要求㊂图6 最小系统的测试结果结 语本文立足于硬件电路设计㊁处理器软硬件编程设计㊁R e W o r k s 操作系统移植等关键技术,对基于Z y n q Ul t r a S c a l e +M P S o C 的嵌入式计算机最小系统的实现过程进行了论述㊂经过测试验证,该最小系统完全满足设计要求㊂该最小系统的成功实现为后续基于同一系列处理器研制嵌入式计算机产品提供了参考,对系列化产品的后续研制具有重要的指导意义㊂参考文献[1]X i l i n x .Z y n q U l t r a S c a l e +M P S o C O v e r v i e w ,2016.[2]X i l i n x .Z y n q Ul t r a S c a l e+M P S o C D a t a S h e e t :D C a n d A C S w i t c h i n g Ch a r a c t e r i s t i c s ,2016.[3]X i l i n x .V i v a d o E m b e d d e d P r o c e s s o r H a r d w a r e D e s i gn ,2017.[4]X i l i n x .Z y n q U l t r a S c a l e +M P S o C T e c h n i c a l R e f e r e n c e M a n u -a l ,2017.[5]谢彬.R e W o r k s /R e D e 嵌入式实时操作系统及开发环境产品白皮书,2013.江绪庆(工程师),主要从事嵌入式系统开发方面的研究㊂(责任编辑:薛士然 收稿日期:2018-10-10)。

Zynq UltraScale+ MPSoC的自动驾驶平台MAX介绍

Zynq UltraScale+ MPSoC的自动驾驶平台MAX介

绍

近几年来自动驾驶汽车吸引很多传统汽车制造商以及新型的互联网公司参与竞争,这是传统行业与人工智能的一种结合的探索,比如我们熟悉的特斯拉、百度、福特等公司都完成了自动驾驶技术的测试,尽管自动驾驶在法律法规上的不完善,但是探索的脚步一直在前进。

Perrone Robotics公司则致力于研发自动驾驶控制平台,提供给汽车制造商实现集成各种功能的传感器和控制算法来实现自动驾驶,该公司推出的MAX(Mobile Autonomous X)平台是一个功能全面的模块化具备实时功能的自动化软件软硬件控制平台,在底特律举办的2017 TU-Automotive大会期间Perrone Robotics公司将MAX平台集成到林肯MKZ轿车上并进行了自动驾驶展示。

图1:集成了Perrone Robotics MAX平台的林肯MKZ自动驾驶汽车

为了确保自动驾驶的安全性汽车的不同位置要部署各种各样的传感器,比如摄像头、雷达、超声波、GPS等,这幺多的传感器无疑会生成大量的数据,据Perrone Robotics测试平台显示数据流可达到1Mbyte/sec,我们需要采用不同的处理器进程实时处理不同传感器数据并最终将这些数据进行融合对。

XILINXZynqUltraScale+MPSoC数据手册概述(中文)

XILINXZynqUltraScale+MPSoC数据手册概述(中文)Zynq UltraScale+ MPSoC 数据手册概述一般说明Zynq?UltraScale+?MPSoC系列基于Xilinx?UltraScale?MPSoC 架构。

该系列产品集成了功能丰富的64位四核或双核Arm?Cortex?-A53和基于双核Arm Cortex-R5的处理系统(PS)和Xilinx可编程逻辑(PL)UltraScale架构在单个器件中。

还包括片上存储器,多端口外部存储器接口和丰富的外设连接接口。

处理系统(PS)基于Arm Cortex-A53的应用处理单元(APU)四核或双核CPU频率:高达1.5GHz可扩展的缓存一致性Armv8-A架构o 64位或32位操作模式o TrustZone安全性o 64位模式下的A64指令集,A32 / T32指令设置为32位模式?NEON Advanced SIMD媒体处理引擎单/双精度浮点单元(FPU)CoreSight?和嵌入式跟踪宏单元(ETM)?加速器一致性端口(ACP)AXI一致性扩展(ACE)每个处理器内核的电源岛门控定时器和中断o Arm通用定时器支持o两个系统级三重计时器计数器o一个看门狗定时器o一个全局系统计时器缓存o 32KB 1级,2路组关联指令缓存,带奇偶校验(每个CPU独立)o 32KB 1级,4路组关联数据缓存,带ECC(独立于每个CPU)o带有ECC的1MB 16路组关联2级缓存(在CPU之间共享)基于双核Arm Cortex-R5实时处理单元(RPU)CPU频率:高达600MHzArmv7-R架构o A32 / T32指令集单/双精度浮点单元(FPU)?CoreSight?和嵌入式跟踪宏单元(ETM)锁步或独立操作定时器和中断:o一个看门狗定时器o两个三重计时器计数器缓存和紧耦合存储器(TCM)o 32KB 1级,4路组关联指令和带ECC的数据缓存(每个CPU独立)o带有ECC的128KB TCM(独立于每个CPU),可以在锁步模式下组合成256KB片上存储器带有ECC的PS中的256KB片上RAM (OCM)带有ECC的高达36Mb片上RAM (UltraRAM)带有ECC的PL高达35Mb片上RAM (Block RAM)PL中高达11Mb的片上RAM(分布式RAM)基于ARM Mali-400的GPU支持OpenGL ES 1.1和2.0支持OpenVG 1.1GPU频率:高达667MHz单几何处理器,两个像素处理器像素填充率:2 Mpixels / sec / MHz三角速率:0.11 Mtriangles / sec / MHz64KB二级高速缓存电力岛门控外部存储器接口多协议动态内存控制器DDR4,DDR3,DDR3L或LPDDR3存储器的32位或64位接口,以及32位LPDDR4内存的接口?64位和32位模式下的ECC支持使用单列或双列8位,16位或32位宽存储器,最多32GB的地址空间静态存储器接口o eMMC4.51托管NAND闪存支持o ONFI3.1具有24位ECC的NAND闪存o 1位SPI,2位SPI,4位SPI(Quad-SPI)或2个Quad-SPI(8位)串行NOR闪存8通道DMA控制器两个DMA控制器,每个8通道内存到内存,内存到外设,外设到内存和分散- 收集事务支持串行收发器四个专用PS-GTR接收器和发送器支持高达6.0Gb/ s的数据速率o支持SGMII三速以太网PCIExpress?Gen2,串行ATA(SATA),USB3.0和DisplayPort专用I / O外设和接口PCI Express - 符合PCIe?2.1基本规范o根复合体和端点配置Gen1或Gen2速率下的x1,x2和x4?SATA主机o SATA规范3.1版修订的1.5,3.0和6.0Gb / s数据速率o最多支持两个频道DisplayPort控制器o速率高达5.4Gb / so最多两个TX通道(无RX支持)专用I / O外设和接口PCI Express - 符合PCIe?2.1基本规范o根复合体和端点配置Gen1或Gen2速率下的x1,x2和x4?SATA主机o SATA规范3.1版修订的1.5,3.0和6.0Gb / s数据速率o最多支持两个频道DisplayPort控制器o速率高达5.4Gb / so最多两个TX通道(无RX支持)四个10/100/1000三速以太网MAC外设,支持IEEE Std 802.3和IEEE Std 1588 2.0版o Scatter-gather DMA功能o识别IEEE Std 1588 rev.2 PTP帧o GMII,RGMII和SGMII接口o巨型帧两个USB 3.0 / 2.0设备,主机或OTG外围设备,每个外围设备最多支持12个端点o USB 3.0 / 2.0兼容设备IP核o超高速,高速,全速和低速模式o符合英特尔XHCI标准的USB主机两个完全符合CAN 2.0B标准的CAN总线接口o符合CAN 2.0-A和CAN 2.0-B和ISO 118981-1标准两个兼容SD / SDIO 2.0 / eMMC4.51的控制器?两个全双工SPI 端口,具有三个外设芯片选择?两个高速UART(最高1Mb / s)两个主从I2C接口多达78个灵活多路复用I / O(MIO)(最多三组26个I / O),用于外设引脚分配连接到PL的多达96个EMIO(最多三组32个I / O)互联PS内和PS与PL之间的高带宽连接?ArmAMBA?AXI4为基础QoS支持延迟和带宽控制高速缓存一致性互连(CCI)系统内存管理系统内存管理单元(SMMU)Xilinx存储器保护单元(XMPU)平台管理单元电源门PS外围设备,电源岛和电源域时钟门PS外设用户固件选项配置和安全单元Boots PS并配置PL支持安全和非安全启动模式PS中的系统监视器片内电压和温度检测可编程逻辑(PL)可配置逻辑块(CLB)查找表(LUT)触发器可级联加法器36Kb Block RAM真正的双端口最大72位宽可配置为双18KbUltraRAM288Kb双端口72位宽错误检查和纠正DSP模块27 x 18签名乘法48位加法器/累加器27位预加法器可编程I / O块支持LVCMOS,LVDS和SSTL ?1.0V至3.3V I / O.可编程I / O延迟和SerDesJTAG边界扫描IEEE Std 1149.1兼容测试接口PCI Express支持Root complex和End Point配置支持最高Gen3速度选择设备中最多五个集成块100G以太网MAC / PCS符合IEEE Std 802.3标准CAUI-10(10x 10.3125Gb / s)或CAUI-4(4x 25.78125Gb / s)CAUI-4配置中的RSFEC(IEEE Std 802.3bj)?选定设备中最多有四个集成块Interlaken符合Interlaken规范1.264/67编码12 x 12.5Gb / s或6 x 25Gb / s选定设备中最多有四个集成块视频编码器/解码器(VCU)适用于EV设备可从PS或PL访问同时编码和解码支持H.264和H.265PL中的系统监视器片内电压和温度检测10位200KSPS ADC,最多17个外部输入功能摘要Zynq UltraScale + MPSoCsZynq UltraScale + MPSoC是一款全面的器件系列,提供单芯片,所有可编程异构多处理器,为设计人员提供软件,硬件,互连,电源,安全性和I / O可编程性。

Zynq UltraScale+ MPSoC

Application Note: CoolRunner-II CPLDCoolRunner-II Serial Peripheral InterfaceMasterXAPP386 (v1.0) December 12, 2002Summary This document details the VHDL implementation of a Serial Peripheral Interface (SPI) master ina Xilinx CoolRunner™-II CPLD. CoolRunner-II CPLDs are the lowest power CPLDs available,making this the perfect target device for an SPI Master. To obtain the VHDL code described inthis document, go to section VHDL Code Download and Disclaimer, page81 for instructions.This design fits XC2C256 CoolRunner-II or XCR3256XL CoolRunner XPLA3 CPLDs. Introduction The Serial Peripheral Interface (SPI) is a full-duplex, synchronous, serial data link that isstandard across many microprocessors, microcontrollers, and peripherals. It enablescommunication between microprocessors and peripherals and/or inter-processorcommunication. The SPI system is flexible enough to interface directly with numerouscommercially available peripherals.A SPI Master design has been implemented in a CoolRunner-II CPLD. The CoolRunner-II SPIMaster design can be used to provide a SPI controller to those microcontrollers ormicroprocessors that do not contain a SPI interface. A high-level block diagram is shown inFigure1. The microcontroller (μC) interface chosen in this SPI Master implementation is basedon the popular 8051 microcontroller bus cycles, but can easily be modified to othermicrocontroller interfaces. For more information on the 8051 microcontroller interface, pleaserefer to XAPP388, CoolRunner-II CPLD 8051 Microcontroller Interface.Figure 1: CoolRunner-II SPI MasterSPI Background This section will describe the main protocol of the SPI bus. For more details and timingdiagrams, please refer to the description of the SPI bus in the Motorola 68HC11 ReferenceManual.XAPP386 (v1.0) December 12, 2002CompactFlash Card Interface for CoolRunner-II CPLDshigh enough to meet the V IH value of CoolRunner-II devices, then this CPLD should besufficient. If not, an external buffer with these characteristics must be supplied to satisfy thesystem requirements.I/O configurations OT1 and OT3 require a totem pole type of driver. CoolRunner CPLDs onlyprovide CMOS type output buffers and therefore cannot explicitly meet these requirements.Therefore, an external buffer of totem pole type should be implemented to satisfy the CF+specification. However, CoolRunner-II CPLDs can meet the I/O drive requirements of V OH andV OL at the specified I OH and I OL test conditions respectively, regardless of CMOS or totem poletype configuration. Analysis of the particular application is necessary to determine ifCoolRunner-II CPLD I/Os can be used without the use of external totem pole buffers.Fixed Level and Unused I/OsNomenclature of all signals in the VHDL source code matches that of the CF+ specification forPC Card I/O Mode.The signals -CD1 and -CD2 are card detect pins which indicate to the host that the card is fullyinserted when it detects both signals are low. This application note does not implement thesesignals within the CPLD, but instead relies on the system designer to hold these two signals atGND external to the CPLD.The signal -CSEL is not used by this application as described by the CF+ specification.-SPKR, binary audio, is not used in this reference design, but can be added if required.-VS1 and -VS2, voltage sense signals, are also not used in this implementation, but must behardwired on the PCB so the host system can correctly determine the card’s required voltagelevels. For this reference design, it is assumed that -VS1 is held LOW while -VS2 is left floating.These two signals are held HIGH by the host system, thereby allowing -VS2 to be read as alogic HIGH when the card leaves it in a floating state.Block Diagram CF+ CardFigure1 shows a block diagram of the CF+ card where the major components are theCoolRunner-II CPLD, Intel StrataFlash and the Analog Devices DSP.The CoolRunner-II CPLD implements the direct interface to the CF+ slot, an interface to theCommon Memory space and an interface to the I/O Space. Control logic is included tosynchronize data between the three interfaces. The Attribute memory as a whole is realized inthe CPLD which includes control and status registers as well as the CIS. External ROM is notneeded for the CIS since it has been compactly implemented in the CPLD as a lookup tableconstructed of product terms.The Intel StrataFlash is used for the Common Memory space and is limited to 2 kB due to the11 available address lines of the CF+ interface. To access further memory space, the CF+ cardmust be configured to utilize the I/O Space or redesigned to implement the True IDE mode. TheCommon Memory space is configured with a 16-bit data bus.The I/O Space, for this implementation, consists of an Analog Devices DSP. In Figure1, thereis a reference to Additional Functions. This is included for illustrative purposes and can be anyfunction, such as a GPS device. An 8-bit data bus is used to interface to the DSP.XAPP398 (v1.0) September 23, 2003。

Xilinx Zynq 开发手册

赛灵思最新发布的UltraScale+16nm系列FPGA、3D IC和MPSoC介绍

赛灵思最新发布的UltraScale+16nm系列FPGA、3D IC和MPSoC介绍在 20nm UltraScale MT 系列胜利基础上,赛灵思现又推出了全新的16nm UltraScale+ 系列、3D IC 和 MP,凭借新型存储器、3D-on-3D 和多处理 SoC(M)技术,再次实现了遥遥率先一代的价值优势。

此外,为了实现更高的性能和集成度,UltraScale+ 系列还采纳了全新的互联优化技术——SmartConnect。

这些新的器件进一步扩展了赛灵思的UltraScale 产品系列(现在从 20nm 跨越至 16nm FPGA、SoC 和 3D IC 器件),同时利用台积公司的 16FF+ FinFET 3D 晶体管技术大幅提升了性能功耗比。

因为该系列采纳业阅历证的 20nm UltraScale 架构、Vivado 设计工具以及全球数一数二的服务代工厂台积公司的 16nmFF+ 技术,赛灵思实现了具有最低风险和最大价值的 FinFET 可编程技术。

通过系统级的优化,UltraScale+ 所提供的价值远远超过了传统工艺节点移植所带来的价值,系统级性能功耗比相比 28nm 器件提升了 2 至5 倍,还实现了遥遥率先的系统集成度和智能化,以及最高级别的保密性和平安性。

新扩展的赛灵思 UltraScale+ FPGA 产品组合包含赛灵思市场率先的Kintex UltraScale+ FPGA、Virtex UltraScale+ FPGA 以及 3D IC 系列,而 Zynq UltraScale+ 系列则包含业界首款全可编程MPSoC。

凭借该产品组合,赛灵思能满足各种下一代应用需求,包括 Advanced 与早期 5G无线、Tb 级有线通信、汽车驾驶员辅助系统以及工业(IoT)应用等。

UltraScale+ FPGA 和 3D IC赛灵思选用了业界性能最高的 16nm FinFET+ 技术,并与全球数一数二的服务代工厂台积公司开展通力合作,台积公司预计于 2015 年推出 50 多款 16nmFF+ 流片。

Ti推出面向Zynq UltraScale+ MPSoC的电源参考设计

Ti推出面向Zynq UltraScale+ MPSoC的电源参考设

计

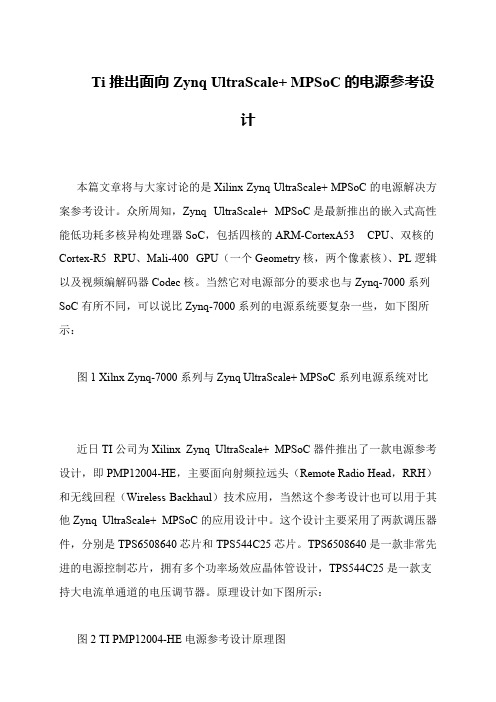

本篇文章将与大家讨论的是Xilinx Zynq UltraScale+ MPSoC的电源解决方案参考设计。

众所周知,Zynq UltraScale+ MPSoC是最新推出的嵌入式高性能低功耗多核异构处理器SoC,包括四核的ARM-CortexA53 CPU、双核的Cortex-R5 RPU、Mali-400 GPU(一个Geometry核,两个像素核)、PL逻辑以及视频编解码器Codec核。

当然它对电源部分的要求也与Zynq-7000系列SoC有所不同,可以说比Zynq-7000系列的电源系统要复杂一些,如下图所示:

图1 Xilnx Zynq-7000系列与Zynq UltraScale+ MPSoC系列电源系统对比

近日TI公司为Xilinx Zynq UltraScale+ MPSoC器件推出了一款电源参考设计,即PMP12004-HE,主要面向射频拉远头(Remote Radio Head,RRH)和无线回程(Wireless Backhaul)技术应用,当然这个参考设计也可以用于其他Zynq UltraScale+ MPSoC的应用设计中。

这个设计主要采用了两款调压器件,分别是TPS6508640芯片和TPS544C25芯片。

TPS6508640是一款非常先进的电源控制芯片,拥有多个功率场效应晶体管设计,TPS544C25是一款支持大电流单通道的电压调节器。

原理设计如下图所示:

图2 TI PMP12004-HE电源参考设计原理图。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Zynq UltraScale+ MPSoC 数据手册概述一般说明Zynq®UltraScale+™MPSoC系列基于Xilinx®UltraScale™MPSoC架构。

该系列产品集成了功能丰富的64位四核或双核Arm®Cortex™-A53和基于双核Arm Cortex-R5的处理系统(PS)和Xilinx可编程逻辑(PL)UltraScale架构在单个器件中。

还包括片上存储器,多端口外部存储器接口和丰富的外设连接接口。

处理系统(PS)基于Arm Cortex-A53的应用处理单元(APU)•四核或双核•CPU频率:高达1.5GHz•可扩展的缓存一致性•Armv8-A架构o 64位或32位操作模式o TrustZone安全性o 64位模式下的A64指令集,A32 / T32指令设置为32位模式•NEON Advanced SIMD媒体处理引擎•单/双精度浮点单元(FPU)•CoreSight™和嵌入式跟踪宏单元(ETM)•加速器一致性端口(ACP)•AXI一致性扩展(ACE)•每个处理器内核的电源岛门控•定时器和中断o Arm通用定时器支持o两个系统级三重计时器计数器o一个看门狗定时器o一个全局系统计时器•缓存o 32KB 1级,2路组关联指令缓存,带奇偶校验(每个CPU独立)o 32KB 1级,4路组关联数据缓存,带ECC(独立于每个CPU)o带有ECC的1MB 16路组关联2级缓存(在CPU之间共享)基于双核Arm Cortex-R5实时处理单元(RPU)•CPU频率:高达600MHz•Armv7-R架构o A32 / T32指令集•单/双精度浮点单元(FPU)•CoreSight™和嵌入式跟踪宏单元(ETM)•锁步或独立操作•定时器和中断:o一个看门狗定时器o两个三重计时器计数器•缓存和紧耦合存储器(TCM)o 32KB 1级,4路组关联指令和带ECC的数据缓存(每个CPU独立)o带有ECC的128KB TCM(独立于每个CPU),可以在锁步模式下组合成256KB片上存储器•带有ECC的PS中的256KB片上RAM (OCM)•带有ECC的高达36Mb片上RAM (UltraRAM)•带有ECC的PL高达35Mb片上RAM (Block RAM)•PL中高达11Mb的片上RAM(分布式RAM)基于ARM Mali-400的GPU•支持OpenGL ES 1.1和2.0•支持OpenVG 1.1•GPU频率:高达667MHz•单几何处理器,两个像素处理器•像素填充率:2 Mpixels / sec / MHz•三角速率:0.11 Mtriangles / sec / MHz•64KB二级高速缓存•电力岛门控外部存储器接口•多协议动态内存控制器•DDR4,DDR3,DDR3L或LPDDR3存储器的32位或64位接口,以及32位LPDDR4内存的接口•64位和32位模式下的ECC支持•使用单列或双列8位,16位或32位宽存储器,最多32GB的地址空间•静态存储器接口o eMMC4.51托管NAND闪存支持o ONFI3.1具有24位ECC的NAND闪存o 1位SPI,2位SPI,4位SPI(Quad-SPI)或2个Quad-SPI(8位)串行NOR闪存8通道DMA控制器•两个DMA控制器,每个8通道•内存到内存,内存到外设,外设到内存和分散- 收集事务支持串行收发器•四个专用PS-GTR接收器和发送器支持高达6.0Gb/ s的数据速率o支持SGMII三速以太网PCIExpress®Gen2,串行ATA(SATA),USB3.0和DisplayPort专用I / O外设和接口•PCI Express - 符合PCIe®2.1基本规范o根复合体和端点配置Gen1或Gen2速率下的x1,x2和x4•SATA主机o SATA规范3.1版修订的1.5,3.0和6.0Gb / s数据速率o最多支持两个频道•DisplayPort控制器o速率高达5.4Gb / so最多两个TX通道(无RX支持)专用I / O外设和接口•PCI Express - 符合PCIe®2.1基本规范o根复合体和端点配置Gen1或Gen2速率下的x1,x2和x4•SATA主机o SATA规范3.1版修订的1.5,3.0和6.0Gb / s数据速率o最多支持两个频道•DisplayPort控制器o速率高达5.4Gb / so最多两个TX通道(无RX支持)•四个10/100/1000三速以太网MAC外设,支持IEEE Std 802.3和IEEE Std 1588 2.0版o Scatter-gather DMA功能o识别IEEE Std 1588 rev.2 PTP帧o GMII,RGMII和SGMII接口o巨型帧•两个USB 3.0 / 2.0设备,主机或OTG外围设备,每个外围设备最多支持12个端点o USB 3.0 / 2.0兼容设备IP核o超高速,高速,全速和低速模式o符合英特尔XHCI标准的USB主机•两个完全符合CAN 2.0B标准的CAN总线接口o符合CAN 2.0-A和CAN 2.0-B和ISO 118981-1标准•两个兼容SD / SDIO 2.0 / eMMC4.51的控制器•两个全双工SPI端口,具有三个外设芯片选择•两个高速UART(最高1Mb / s)•两个主从I2C接口•多达78个灵活多路复用I / O(MIO)(最多三组26个I / O),用于外设引脚分配•连接到PL的多达96个EMIO(最多三组32个I / O)互联•PS内和PS与PL之间的高带宽连接•ArmAMBA®AXI4为基础•QoS支持延迟和带宽控制•高速缓存一致性互连(CCI)系统内存管理•系统内存管理单元(SMMU)•Xilinx存储器保护单元(XMPU)平台管理单元•电源门PS外围设备,电源岛和电源域•时钟门PS外设用户固件选项配置和安全单元•Boots PS并配置PL•支持安全和非安全启动模式PS中的系统监视器•片内电压和温度检测可编程逻辑(PL)可配置逻辑块(CLB)•查找表(LUT)•触发器•可级联加法器36Kb Block RAM•真正的双端口•最大72位宽•可配置为双18KbUltraRAM•288Kb双端口•72位宽•错误检查和纠正DSP模块•27 x 18签名乘法•48位加法器/累加器•27位预加法器可编程I / O块•支持LVCMOS,LVDS和SSTL •1.0V至3.3V I / O.•可编程I / O延迟和SerDesJTAG边界扫描•IEEE Std 1149.1兼容测试接口PCI Express•支持Root complex和End Point配置•支持最高Gen3速度•选择设备中最多五个集成块100G以太网MAC / PCS•符合IEEE Std 802.3标准•CAUI-10(10x 10.3125Gb / s)或CAUI-4(4x 25.78125Gb / s)•CAUI-4配置中的RSFEC(IEEE Std 802.3bj)•选定设备中最多有四个集成块Interlaken•符合Interlaken规范1.2•64/67编码•12 x 12.5Gb / s或6 x 25Gb / s•选定设备中最多有四个集成块视频编码器/解码器(VCU)•适用于EV设备•可从PS或PL访问•同时编码和解码•支持H.264和H.265PL中的系统监视器•片内电压和温度检测•10位200KSPS ADC,最多17个外部输入功能摘要Zynq UltraScale + MPSoCsZynq UltraScale + MPSoC是一款全面的器件系列,提供单芯片,所有可编程异构多处理器,为设计人员提供软件,硬件,互连,电源,安全性和I / O可编程性。

Zynq UltraScale + MPSoC系列中的器件系列允许设计人员使用行业标准工具从单一平台瞄准成本敏感型和高性能应用。

虽然每个Zynq UltraScale + MPSoC包含相同的PS,但PL,视频硬块和I / O资源在不同设备之间有所不同。

Zynq UltraScale + MPSoC能够满足广泛的应用,包括:•汽车:驾驶员辅助,驾驶员信息和信息娱乐•无线通信:支持多光谱波段和智能天线•有线通信:多种有线通信标准和上下文感知网络服务•数据中心:软件定义网络(SDN),数据预处理和分析•更智能的愿景:不断发展的视频处理算法,对象检测和分析•连接控制/ M2M:灵活/适应性强的制造,工厂吞吐量,质量和安全性UltraScale MPSoC架构提供32至64位的处理器可扩展性,支持虚拟化,软硬件组合,用于实时控制,图形/视频处理,波形和数据包处理,下一代互连和存储器,高级电源管理以及提供多级安全性,安全性和可靠性的技术增强功能。

Xilinx为Zynq UltraScale + MPSoC系列提供大量软IP。

独立和Linux设备驱动程序可用于PS和PL中的外围设备。

Xilinx的Vivado®DesignSuite,SDK™和PetaLinux开发环境可为软件,硬件和系统工程师提供快速的产品开发。

基于Arm的PS还将Xilinx现有的PL生态系统与广泛的第三方工具和IP提供商结合在一起。

Zynq UltraScale + MPSoC系列以优化的异构处理引擎组合形式提供前所未有的处理,I / O和存储器带宽,这些引擎嵌入下一代高性能片上互连,并具有适当的片上存储器子系统。

异构处理和可编程引擎针对不同的应用任务进行了优化,使Zynq UltraScale + MPSoC能够提供满足下一代智能系统所需的广泛性能和效率,同时保持与原始Zynq-7000 All Programmable SoC系列的向后兼容性。

UltraScale MPSoC架构还集成了多级安性,更高的安全性和先进的电源管理,这些都是下一代智能系统的关键要求。

Xilinx的嵌入式UltraFast™设计方法充分利用了UltraScale MPSoC架构提供的ASIC级功能,同时支持快速系统开发。

包含应用程序处理器在内均支持高级操作系统,例如Linux。

与Cortex-A53处理器一起使用的其他标准操作系统也可用于Zynq UltraScale + MPSoC系列。

PS和PL位于不同的电源域上,如果需要,用户可以关闭PL以进行电源管理。

PS中的处理器始终首先启动,允许采用以软件为中心的PL配置方法。

PL配置由CPU上运行的软件管理,因此它的启动类似于ASSP。

处理系统应用处理单元(APU)APU的主要功能包括:•64位四核Arm Cortex-A53 MPCores。