ADM1485ARZ

拉雷尔电子有限公司产品说明书

LAUREL ELECTRONICS, ureate™ Rate Meter & Totalizer with Functions A+B, A-B, AxB, A/B, A/B-1Features•Arithmetic functions A+B, A-B, AxB, A/B, A/B-1 applied to rate or total forchannels A & B•Frequencies from 0.005 Hz to 10 kHz•Independent scaling for each channel•Selectable "count by" of 10 or 100 with rounding•6-digit red or green LED display•Universal AC power Input, 85-264 Vac•Isolated 5, 10 or 24 Vdc excitation output•NEMA 4X, 1/8 DIN case•Optional serial I/O: Ethernet, USB, RS232, RS485, Ethernet-to-RS485 converter•Optional relay outputs: dual or quad relays, contact or solid state•Optional isolated analog output: 4-20 mA, 0-20 mA, 0-10V, -10 to +10V•Optional low voltage power: 10-48 Vdc or 12-32 VacDescriptionArithmetic functions A+B, A-B, AxB, A/B, A/B-1 applied tochannels A & B are a capability of Laureates with an Extendedcounter main board and FR dual-channel signal conditionerboard. These functions are applicable to rate or total after scalingto engineering units. The following are application examples:•Add two flows (A+B) for total flow or total volume.•Subtract two flows (A-B) for net flow or net volume.•Take the ratio of two flow rates (A/B) for chemical mixing.•Take the ratio of RPMs or belt speeds (A/B) to synchronizemoving machinery.•Subtract 1 from ratio (A/B-1) to control elongation of materialcompressed by rollers (draw).•Multiply belt speed by weight of material on the belt to for rateor weight of material delivered by the belt. A weighttransducer with frequency output is required.Ratio and draw are similar, except that 1 is subtracted from ratioto obtain draw. The frequency of channels A or B is measuredand converted to rate in engineering units by multiplying it by theappropriate scale factor for that channel. Either rate can bedisplayed. The A/B ratio is taken mathematically by the meter,and 1 is subtracted for draw. The result can be multiplied by amultiple or 10 from 0.0001 to 100000, and the decimal point canbe set to display the result with the desired precision up to sixdigits.Fast, High Resolution Measurements. Laureate countersdetermine frequency by timing an integral number of periods overa programmable gate time. The inverse period approach allowsgreater accuracy and faster update times than conventionalmeters which count signal pulses over a specified time interval.Channel A accepts pulses from 0.005 Hz to 1 MHz, while Chan-nel B accepts pulses from 0.005 Hz to 250 kHz. At the minimumgate time of 10 ms, update rates can be up to 25/second. Suchfast response is ideal for peak capture and for alarm and controlapplications. Variations in the displayed reading can be reducedby selecting a longer gate time. An adaptive digital filter canfurther reduce variations due to noise while rapidly responding toactual changes in the signal.Universal Signal Conditioner. The Laureate dual-channelsignal conditioner accepts inputs from proximity switches withPNP or NPN output, TTL or CMOS logic, magnetic pickups,contact closures, low-level outputs from turbine flow meters downto 12 mV, or high-level AC line inputs to 250 Vac. Jumper selec-tions provide optimum operation for different sensor types andnoise conditions. A built-in isolated 5, 10, or 24 Vdc excitationsupply can power proximity switches or other sensors, andeliminate the need for an external power supply.Designed for system use. Optional plug-in boards includeEthernet and other serial communication boards, dual or quadrelay boards, and an isolated analog output board. Laureatesmay be powered from 85-264 Vac or optionally from 12-32 Vacor 10-48 Vdc. The display is available with red or green LEDs.The 1/8 DIN case meets NEMA 4X (IP65) specifications from thefront when panel mounted. Any setup functions and front panelkeys can be locked out for simplified usage and security. A built-in isolated 5, 10, or 24 Vdc excitation supply can power trans-ducers and eliminate the need for an external power supply.All power and signal connections are via UL / VDE / CSA ratedscrew clamp plugs.SpecificationsDisplayReadout Display Range Zero Adjust Span Adjust Indicators 6 LED digits, 7-segment, 14.2 mm (.56"), red or green LED -999999 to +999999, XXXXEX notation beyond 999999-999999 to +9999990 to 999999Four LED lampsInputsTypesSignal Ground Channel A Frequency Channel B Frequency Minimum Signal Maximum Signal Noise FilterContact Debounce AC, pulses from NPN, PNP transistors, contact closures, magnetic pickups Common ground for channels A & B0.005 Hz to 1 MHz0.005 Hz to 250 kHzNine ranges from (-12 to +12 mV) to (+1.25 to +2.1V)250 Vac1 MHz, 30 kHz, 250 Hz (selectable)0, 3, 50 ms (selectable)Rate AccuracyTime Base Span Tempco Long-term Drift Crystal calibrated to ±2 ppm ±1 ppm/°C (typ)5 ppm/yearPowerVoltage, standard Voltage, optional Power frequency Power consumption (typical, base meter) Power isolation 85-264 Vac or 90-300 Vdc12-32 Vac or 10-48 VdcDC or 47-63 Hz1.2W @ 120 Vac, 1.5W @ 240 Vac, 1.3W @ 10 Vdc, 1.4W @ 20 Vdc, 1.55W @ 30 Vdc, 1.8W @ 40 Vdc,2.15W @ 48 Vdc250V rms working, 2.3 kV rms per 1 min testExcitation Output (standard)5 Vdc10 Vdc24 VdcOutput Isolation 5 Vdc ± 5%, 100 mA10 Vdc ± 5%, 120 mA 24 Vdc ± 5%, 50 mA50 Vdc to meter groundAnalog Output (optional)Output Levels Current compliance Voltage compliance Scaling Resolution Isolation 4-20 mA, 0-20 mA, 0-10V, -10 to +10V (single-output option) 4-20 mA, 0-20 mA, 0-10V (dual-output option)2 mA at 10V ( > 5 kΩ load)12V at 20 mA ( < 600Ω load)Zero and full scale adjustable from -99999 to +9999916 bits (0.0015% of full scale)250V rms working, 2.3 kV rms per 1 min test(dual analog outputs share the same ground)Relay Outputs (optional)Relay Types Current Ratings Output common Isolation 2 Form C contact relays or 4 Form A contact relays (NO)2 or 4 Form A, AC/DC solid state relays (NO)8A at 250 Vac or 24 Vdc for contact relays120 mA at 140 Vac or 180 Vdc for solid state relays Isolated commons for dual relays or each pair of quad relays 250V rms working, 2.3 kV rms per 1 min testSerial Data I/O (optional)Board Selections ProtocolsData Rates Digital Addresses Isolation Ethernet, Ethernet-to-RS485 converter, USB, USB-to-RS485 converter, RS485 (dual RJ11), RS485 Modbus (dual RJ45), RS232.Modbus RTU, Modbus ASCII, Laurel ASCII protocol300 to 19200 baud247 (Modbus), 31 (Laurel ASCII),250V rms working, 2.3 kV rms per 1 min testEnvironmental Operating Temp. Storage Temp.Relative Humidity Protection0°C to 55°C -40°C to 85°C95% at 40°C, non-condensingNEMA-4X (IP-65) when panel mountedSignal ConnectionsMechanicalApplication ExamplesControlling the Mixing Ratio of Two FluidsDisplaying and alarming the input flow rate ratio of two fluids (gas or liquid) allows these to be mixed in a predetermined ratio in continuous processes. The sensing element is normally a turbine flowmeter, which outputs pulses at a frequency proportional to flow rate. The A/B ratio can also be displayed for totalized rate (or delivered volume). Comparing Fluid Inflow & OutflowThe ratio of the inflow and outflow rates of a tank is a measure of the relative filling or emptying rate. The same meter can also be programmed to display the net inflow or outflow rate in flow units, or to display totalized inflow our outflow in volume units. Any of these parameters can be alarmed using the dual relay board and be transmitted via 4-20 mA, RS-232 or RS-485. Controlling Coating Thickness on a FilmIn this application, Channel A measures the rate at which a coating material is applied, as measured by a flow meter, while Channel B measures the speed of the film based on pulses from a proximity switch. Displaying and alarming the A/B ratio assures that an even thickness of coating material is applied as the speed of the film is varies. Synchronizing Two Conveyor LinesThe dual-channel Laureate counter can measure the speed of conveyor lines by using the output of proximity switches which sense gear teeth or spokes of rotating drive wheels. Displaying the speed ratio of two lines allows line speeds to be adjusted so that material arrives at work stations when needed. Measuring Draw for ElongationDraw (Ch A / Ch B - 1) can be used to display the elongation of films compressed between rollers, the shrinkage films, and the RPM difference of rollers whose speed is varied to maintain tension. The six-digit resolution of the Laureate dual channel counter / rate meter is ideal for comparison of rates that are close to each other.Ordering GuideCreate a model number in this format: L70000FR, IPCMain Board L7 Extended Main Board, Green LEDsL8 Extended Main Board, Red LEDsNote: Extended capability is required for arithmetic functions, simultaneous rate and total in thesame counter, phase, stopwatch, batching, and custom curve linearization.Power0 Isolated 85-264 Vac1 Isolated 12-32 Vac or 10-48 VdcRelay Output (isolated) 0 None1 Two 8A Contact Relays2 Two 120 mA Solid State Relays3 Four 8A Contact Relays4 Four 120 mA Solid State RelaysAnalog Output (isolated) 0 None1 Single isolated 4-20 mA, 0-20 mA, 0-10 V, -10 to +10V2 Dual isolated 4-20 mA, 0-20 mA, 0-10VDigital Interface (isolated) 0 None1 RS-2322 RS485 (dual RJ11 connectors)4 RS485 Modbus (dual RJ45 connectors)5 USB6 USB-to-RS485 converter7 Ethernet8 Ethernet-to-RS485 converterInput Type FR Dual-Channel Pulse Input Signal ConditionerAdd-on Options CBL01RJ11-to-DB9 cable. RJ11 to DB9. Connects RS232 ports of meter and PC.CBL02USB-to-DB9 adapter cable. Combination of CBL02 and CBL01 connects meterRS232 port to PC USB port.CBL03-16-wire data cable, RJ11 to RJ11, 1 ft. Used to daisy chain meters via RS485.CBL03-76-wire data cable, RJ11 to RJ11, 7 ft. Used to daisy chain meters via RS485.CBL05USB cable, A-B. Connects USB ports of meter and PC.CBL06USB to RS485 adapter cable, half duplex, RJ11 to USB. Connects meter RS485 portto PC USB port.CASE1Benchtop laboratory case for one 1/8 DIN meterCASE2Benchtop laboratory case for two 1/8 DIN metersIPC Splash-proof coverBOX1NEMA-4 EnclosureBOX2NEMA-4 enclosure plus IPCBL Blank Lens without button padsNL Meter lens without button pads or Laurel logo。

FPGA可编程逻辑器件芯片ADM1485ARZ-REEL中文规格书

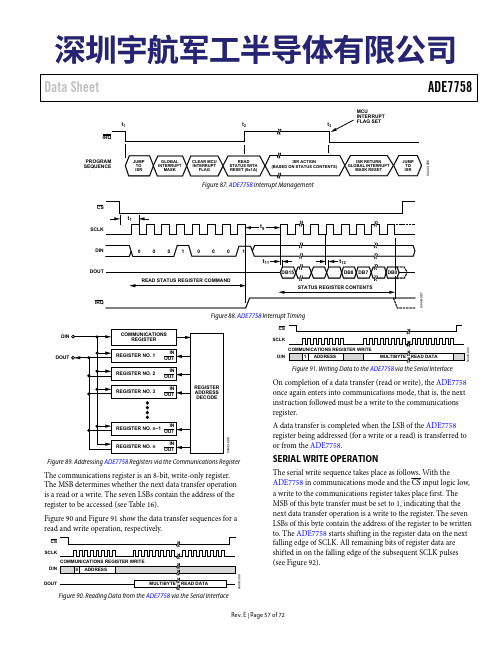

Data SheetADE7758MCU04443-086Figure 87. ADE7758 Interrupt Management04443-087Figure 88. ADE7758Interrupt TimingDINDOUT04443-088Figure 89. Addressing ADE7758 Registers via the Communications RegisterThe communications register is an 8-bit, write-only register. The MSB determines whether the next data transfer operation is a read or a write. The seven LSBs contain the address of the register to be accessed (see Table 16).Figure 90 and Figure 91 show the data transfer sequences for a read and write operation, respectively.MULTIBYTEDIN SCLKDOUTREAD DATACS 04443-089Figure 90. Reading Data from the ADE7758 via the Serial InterfaceDINSCLKCS04443-090Figure 91. Writing Data to the ADE7758 via the Serial InterfaceOn completion of a data transfer (read or write), the ADE7758 once again enters into communications mode, that is, the next instruction followed must be a write to the communications register.A data transfer is completed when the LSB of the ADE7758 register being addressed (for a write or a read) is transferred to or from the ADE7758.SERIAL WRITE OPERATIONThe serial write sequence takes place as follows. With theADE7758 in communications mode and the CS input logic low, a write to the communications register takes place first. The MSB of this byte transfer must be set to 1, indicating that the next data transfer operation is a write to the register. The seven LSBs of this byte contain the address of the register to be written to. The starts shifting in the register data on the next falling edge of SCLK. All remaining bits of register data are shifted in on the falling edge of the subsequent SCLK pulses (see ).ADE7758Figure 92As explained earlier, the data write is initiated by a write to the communications register followed by the data. During a data write operation to the ADE7758, data is transferred to all on-chip registers one byte at a time. After a byte is transferred into the serial port, there is a finite time duration before the content in the serial port buffer is transferred to one of the ADE7758 on-chip registers. Although another byte transfer to the serial port can start while the previous byte is being transferred to the destination register, this second-byte transfer should not finish until at least 900 ns after the end of the previous byte transfer. This functionality is expressed in the timing specification t 6 (see Figure 92). If a write operation is aborted during a byte transfer (CS brought high), then that byte is not written to the destination register.Destination registers can be up to 3 bytes wide (see theAccessing the On-Chip Registers section). Therefore, the first byte shifted into the serial port at DIN is transferred to the most significant byte (MSB) of the destination register. If the destination register is 12 bits wide, for example, a two-byte data transfer must take place. The data is always assumed to be right justified; therefore, in this case, the four MSBs of the first byte would be ignored, and the four LSBs of the first byte written to the ADE7758 would be the four MSBs of the 12-bit word. Figure 93 illustrates this example.COMMAND BYTE MOST SIGNIFICANT BYTE LEAST SIGNIFICANT BYTE04443-091Figure 92. Serial Interface Write Timing DiagramSCLKDIN X X X X DB11DB10DB9DB8DB7DB6DB5DB4DB3DB2DB1DB0MOST SIGNIFICANT BYTE LEAST SIGNIFICANT BYTE04443-092Figure 93. 12-Bit Serial Write OperationSCLKCSDINDOUTCOMMAND BYTE04443-093Figure 94. Serial Interface Read Timing DiagramOPERATIONAL MODE REGISTER (0x13)The general configuration of the ADE7758 is defined by writing to the OPMODE register. Table 18 summarizes the functionality of each bit in the OPMODE register.Table 18. OPMODE RegisterBit Location BitMnemonicDefaultValue Description0 DISHPF 0 The HPFs in all current channel inputs are disabled when this bit is set.1 DISLPF 0 The LPFs after the watt and VAR multipliers are disabled when this bit is set.2 DISCF 1 The frequency outputs APCF and VARCF are disabled when this bit is set.3 to 5 DISMOD 0 By setting these bits, the ADE7758 ADCs can be turned off. In normal operation, these bits shouldbe left at Logic 0.DISMOD[2:0] Description0 0 0 Normal operation.1Redirect the voltage inputs to the signal paths for the current channels andthe current inputs to the signal paths for the voltage channels.0 0 1 Switch off only the current channel ADCs.11Switch off current channel ADCs and redirect the current input signals to thevoltage channel signal paths.0 1 0 Switch off only the voltage channel ADCs.11Switch off voltage channel ADCs and redirect the voltage input signals to thecurrent channel signal paths.11PuttheADE7758 in sleep mode.111PuttheADE7758 in power-down mode (reduces AI DD to 1 mA typ).6 SWRST 0 Software Chip Reset. A data transfer to the ADE7758 should not take place for at least 166 μs aftera software reset.7 Reserved 0 This should be left at 0.MEASUREMENT MODE REGISTER (0x14)The configuration of the PERIOD and peak measurements made by the ADE7758 is defined by writing to the MMODE register. Table 19 summarizes the functionality of each bit in the MMODE register.Table 19. MMODE RegisterBit Location BitMnemonicDefaultValue Description0 to 1 FREQSEL 0 These bits are used to select the source of the measurement of the voltage line frequency.FREQSEL1 FREQSEL0 Source0 0 Phase A0 1 Phase B1 0 Phase C1 1 Reserved2 to 4 PEAKSEL 7 These bits select the phases used for the voltage and current peak registers. Setting Bit 2 switchesthe IPEAK and VPEAK registers to hold the absolute values of the largest current and voltagewaveform (over a fixed number of half-line cycles) from Phase A. The number of half-line cycles isdetermined by the content of the LINECYC register. At the end of the LINECYC number of half-linecycles, the content of the registers is replaced with the new peak values. Similarly, setting Bit 3 turnson the peak detection for Phase B, and Bit 4 for Phase C. Note that if more than one bit is set, theVPEAK and IPEAK registers can hold values from two different phases, that is, the voltage andcurrent peak are independently processed (see the Peak Current Detection section).5 to 7 PKIRQSEL 7 These bits select the phases used for the peak interrupt detection. Setting Bit 5 switches on themonitoring of the absolute current and voltage waveform to Phase A. Similarly, setting Bit 6 turns onthe waveform detection for Phase B, and Bit 7 for Phase C. Note that more than one bit can be set fordetection on multiple phases. If the absolute values of the voltage or current waveform samples inthe selected phases exceeds the preset level specified in the VPINTLVL or IPINTLVL registers thecorresponding bit(s) in the STATUS registers are set (see the Peak Current Detection section).Data Sheet ADE7758ADE7758 Data SheetCOMPUTATIONAL MODE REGISTER (0x16)The computational method of the ADE7758 is defined by writing to the COMPMODE register. Table 21 summarizes the functionality of each bit in the COMPMODE register.。

MM5ZxxxST1G Serie Zener Voltage Regulators 500 mW

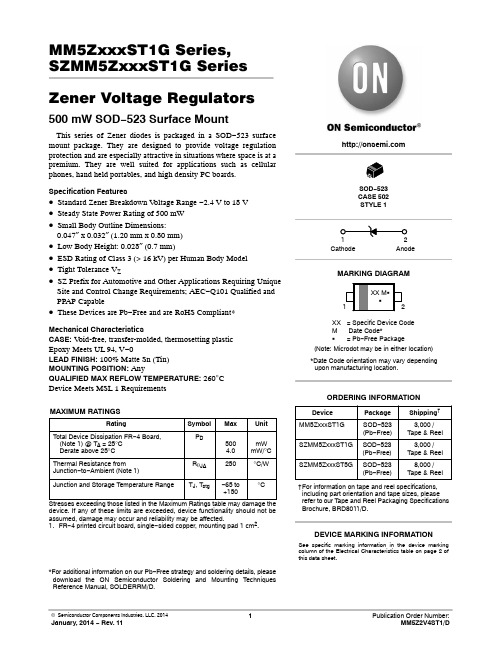

MM5ZxxxST1G Series, SZMM5ZxxxST1G Series Zener Voltage Regulators 500 mW SOD−523 Surface MountThis series of Zener diodes is packaged in a SOD−523 surface mount package. They are designed to provide voltage regulation protection and are especially attractive in situations where space is at a premium. They are well suited for applications such as cellular phones, hand held portables, and high density PC boards. Specification Features•Standard Zener Breakdown V oltage Range −2.4 V to 18 V •Steady State Power Rating of 500 mW•Small Body Outline Dimensions:0.047″ x 0.032″ (1.20 mm x 0.80 mm)•Low Body Height: 0.028″ (0.7 mm)•ESD Rating of Class 3 (> 16 kV) per Human Body Model •Tight Tolerance V Z•SZ Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC−Q101 Qualified and PPAP Capable•These Devices are Pb−Free and are RoHS Compliant*Mechanical CharacteristicsCASE:V oid-free, transfer-molded, thermosetting plasticEpoxy Meets UL 94, V−0LEAD FINISH: 100% Matte Sn (Tin)MOUNTING POSITION:AnyQUALIFIED MAX REFLOW TEMPERATURE: 260°CDevice Meets MSL 1 RequirementsMAXIMUM RATINGSRating Symbol Max UnitTotal Device Dissipation FR−4 Board, (Note 1) @ T A = 25°CDerate above 25°C P D5004.0mWmW/°CThermal Resistance from Junction−to−Ambient (Note 1)R q JA250°C/WJunction and Storage Temperature Range T J, T stg−65 to+150°CStresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.1.FR−4 printed circuit board, single−sided copper, mounting pad 1 cm2.*For additional information on our Pb−Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.Device Package Shipping†ORDERING INFORMATIONCathode AnodeSee specific marking information in the device marking column of the Electrical Characteristics table on page 2 of this data sheet.DEVICE MARKING INFORMATIONSOD−523CASE 502STYLE 1MARKING DIAGRAMXX= Specific Device CodeM Date Code*G= Pb−Free Package(Note: Microdot may be in either location)*Date Code orientation may vary dependingupon manufacturing location.MM5ZxxxST1G SOD−523(Pb−Free)3,000 /Tape & Reel†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our T ape and Reel Packaging Specifications Brochure, BRD8011/D.SOD−523(Pb−Free)SZMM5ZxxxST1G3,000 /Tape & ReelSOD−523(Pb−Free)SZMM5ZxxxST5G8,000 /Tape & ReelELECTRICAL CHARACTERISTICS (T A = 25°C unless otherwise noted,V F = 0.9 V Max. @ I F = 10 mA for all types) Symbol Parameter V Z Reverse Zener Voltage @ I ZTI ZT Reverse CurrentZZT Maximum Zener Impedance @ I ZTI ZK Reverse CurrentZ ZK Maximum Zener Impedance @ I ZKI R Reverse Leakage Current @ V RV R Reverse VoltageI F Forward CurrentV F Forward Voltage @ I FQ V Z Maximum Temperature Coefficient of V Z C Max. Capacitance @V R = 0 and f = 1 MHzV Figure 1. Zener Voltage RegulatorELECTRICAL CHARACTERISTICS (V F = 0.9 Max @ I F = 10 mA for all types)Device*DeviceMarkingTestCurrentIzt mAZener VoltageVZZ ZK I Z= 1.0mA WMaxZ ZTI Z = IZT@ 10%Mod WMaxMaxIR @ VRd VZ/dt (mV/k)@ I ZT1 = 5 mA C pF Max @V R = 0f = 1 MHzMin Max m A V Min MaxMM5Z2V4ST1G T2 5.0 2.43 2.631000100120 1.0−3.50450MM5Z2V7ST1G T3 5.0 2.67 2.911000100100 1.0−3.50450MM5Z3V3ST1G T5 5.0 3.32 3.53100095 5.0 1.0−3.50450MM5Z3V6ST1G T6 5.0 3.60 3.85100090 5.0 1.0−3.50450MM5Z3V9ST1G T7 5.0 3.89 4.16100090 3.0 1.0−3.5−2.5450MM5Z4V3ST1G T8 5.0 4.17 4.43100090 3.0 1.0−3.50450MM5Z4V7ST1G/T5G T9 5.0 4.55 4.7580080 3.0 2.0−3.50.2260MM5Z5V1ST1G TA 5.0 4.98 5.250060 2.0 2.0−2.7 1.2225MM5Z5V6ST1G TC 5.0 5.49 5.7320040 1.0 2.0−2.0 2.5200MM5Z6V2ST1G TE 5.0 6.06 6.3310010 3.0 4.00.4 3.7185MM5Z6V8ST1G TF 5.0 6.65 6.9316015 2.0 4.0 1.2 4.5155MM5Z7V5ST1G TG 5.07.287.616015 1.0 5.0 2.5 5.3140MM5Z8V2ST1G TH 5.08.028.36160150.7 5.0 3.2 6.2135MM5Z9V1ST1G TK 5.08.859.23160150.5 6.0 3.87.0130MM5Z12VST1G TN 5.011.7412.2480250.18.0 6.010130MM5Z16VST1G TU 5.015.8516.5180400.0511.210.414105MM5Z18VST1G TW 5.017.5618.3580450.0512.612.416100 Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.*Include SZ-prefix devices where applicable.TYPICAL CHARACTERISTICSTEMPERATURE (°C)25010040200P O W E R D I S S I P A T I O N (%)50751001251508060Figure 2. Steady State Power DeratingPACKAGE DIMENSIONSSOD −523CASE 502ISSUE ENOTES:1.DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.2.CONTROLLING DIMENSION: MILLIMETERS.3.MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH.MINIMUM LEAD THICKNESS IS THE MINIMUM THICKNESS OF BASE MATERIAL.4.DIMENSIONS D AND E DO NOT INCLUDE MOLD FLASH, PRO-TRUSIONS, OR GATE BURRS.DIM MIN NOM MAX MILLIMETERS D 1.10 1.20 1.30E 0.700.800.90A 0.500.600.70b 0.250.300.35c 0.070.140.20L 0.30 REF H 1.50 1.60 1.70*For additional information on our Pb −Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*E RECOMMENDEDSIDE VIEW2XBOTTOM VIEWL2L2X2XL20.150.200.25STYLE 1:PIN 1.CATHODE (POLARITY BAND)2.ANODEON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

MEMORY存储芯片ADM708ARZ-REEL中文规格书

Data SheetADuM1410/ADuM1411/ADuM1412FEATURESLow power operation 5 V operation1.3 mA per channel maximum at 0 Mbps to 2 Mbps 4.0 mA per channel maximum at 10 Mbps 3 V operation0.8 mA per channel maximum at 0 Mbps to 2 Mbps 1.8 mA per channel maximum at 10 Mbps Bidirectional communication 3 V/5 V level translationHigh temperature operation: 105°C Up to 10 Mbps data rate (NRZ)Programmable default output stateHigh common-mode transient immunity: >25 kV/µs 16-lead, RoHS compliant, SOIC wide body package Safety and regulatory approvalsUL recognition: 3750 V rms for 1 minute per UL 1577 CSA Component Acceptance Notice 5A VDE certificate of conformityDIN V VDE V 0884-10 (VDE V 0884-10): 2006-12 V IORM = 560 V peakTÜV approval: IEC/EN 60950-1V GND V V V V GND DD22OA OB OC OD2206580-001Figure 1. ADuM1410V GND V V V V CTRL GND DD22OA OB OC ID2206580-002Figure 2. ADuM1411V GND V V V V CTRL GNDDD22OA OB IC ID 2206580-003APPLICATIONSGeneral-purpose multichannel isolation SPI interface/data converter isolation RS-232/RS-422/RS-485 transceivers Industrial field bus isolationGENERAL DESCRIPTIONThe ADuM1410/ADuM1411/ADuM14121 are four-channel digital isolators based on Analog Devices, Inc., i Coupler® technology. Combining high speed CMOS and monolithic air core transformer technologies, these isolation components provide outstanding performance characteristics superior to alternatives such as optocoupler devices.By avoiding the use of LEDs and photodiodes, i Coupler devices remove the design difficulties commonly associated with opto-couplers. The usual concerns that arise with optocouplers, such as uncertain current transfer ratios, nonlinear transfer functions, and temperature and lifetime effects, are eliminated with the simple i Coupler digital interfaces and stable performance characteristics. The need for external drivers and other discrete components is eliminated with these i Coupler products. Furthermore, i Coupler1Protected by U.S. Patents 5,952,849; 6,873,065; 6,903,578; and 7,075,329.Figure 3. ADuM1412devices consume one-tenth to one-sixth the power of optocou-plers at comparable signal data rates.The ADuM1410/ADuM1411/ADuM1412 isolators provide four independent isolation channels in a variety of channel configu-rations and data rates (see the Ordering Guide) up to 10 Mbps. All models operate with the supply voltage on either side ranging from 2.7 V to 5.5 V , providing compatibility with lower voltage systems as well as enabling voltage translation functionality across the isolation barrier. All products also have a default output control pin. This allows the user to define the logic state the outputs are to adopt in the absence of the input power. Unlike other optocoupler alternatives, the ADuM1410/ADuM1411/ ADuM1412 isolators have a patented refresh feature that ensures dc correctness in the absence of input logic transitions and during power-up/power-down conditions.Data Sheet ADuM1410/ADuM1411/ADuM1412 SPECIFICATIONSELECTRICAL CHARACTERISTICS—5 V OPERATION4.5 V ≤ V DD1 ≤5.5 V, 4.5 V ≤ V DD2 ≤ 5.5 V; all minimum/maximum specifications apply over the entire recommended operation range, unless otherwise noted; all typical specifications are at T A = 25°C, V DD1 = V DD2 = 5 V. All voltages are relative to their respective ground. Table 1.Parameter Symbol Min Typ Max Unit Test Conditions/CommentsDC SPECIFICATIONSInput Supply Current per Channel,QuiescentI DDI (Q)0.50 0.73 mAOutput Supply Current per Channel,QuiescentI DDO (Q)0.38 0.53 mAADuM1410, Total Supply Current,Four Channels1DC to 2 MbpsV DD1 Supply Current I DD1 (Q) 2.4 3.2 mA DC to 1 MHz logic signal frequency V DD2 Supply Current I DD2 (Q) 1.2 1.6 mA DC to 1 MHz logic signal frequency10 Mbps (BRWZ Version Only)V DD1 Supply Current I DD1 (10)8.8 12 mA 5 MHz logic signal frequency V DD2 Supply Current I DD2 (10) 2.8 4.0 mA 5 MHz logic signal frequency ADuM1411, Total Supply Current,Four Channels1DC to 2 MbpsV DD1 Supply Current I DD1 (Q) 2.2 2.8 mA DC to 1 MHz logic signal frequency V DD2 Supply Current I DD2 (Q) 1.8 2.4 mA DC to 1 MHz logic signal frequency10 Mbps (BRWZ Version Only)V DD1 Supply Current I DD1 (10) 5.4 7.6 mA 5 MHz logic signal frequency V DD2 Supply Current I DD2 (10) 3.8 5.3 mA 5 MHz logic signal frequency ADuM1412, Total Supply Current,Four Channels1DC to 2 MbpsV DD1 or V DD2 Supply Current I DD1 (Q), I DD2(Q)2.0 2.6 mA DC to 1 MHz logic signal frequency10 Mbps (BRWZ Version Only)V DD1 or V DD2 Supply Current I DD1 (10), I DD2 (10) 4.6 6.5 mA 5 MHz logic signal frequencyAll ModelsInput Currents I IA, I IB, I IC,I ID, I CTRL1,I CTRL2, I DISABLE −10 +0.01 +10µA 0 V ≤ V IA, V IB, V IC, V ID ≤ V DD1 or V DD2,0 V ≤ V CTRL1, V CTRL2 ≤ V DD1 or V DD2,0 V ≤ V DISABLE ≤ V DD1Logic High Input Threshold V IH 2.0 V Logic Low Input Threshold V IL 0.8 VLogic High Output Voltages V OAH, V OBH,V OCH, V ODH (V DD1 or V DD2) − 0.1 5.0 V I Ox = −20 µA, V Ix = V IxH (V DD1 or V DD2) − 0.4 4.8 V I Ox = −4 mA, V Ix = V IxHLogic Low Output Voltages V OAL, V OBL,V OCL, V ODL0.0 0.1 V I Ox = 20 µA, V Ix = V IxL0.04 0.1 V I Ox = 400 µA, V Ix = V IxL0.2 0.4 V I Ox = 4 mA, V Ix = V IxL Rev. M | Page of 22ADuM1410/ADuM1411/ADuM1412 Data Sheet Parameter Symbol Min Typ Max Unit Test Conditions/Comments SWITCHING SPECIFICATIONSADuM1410ARWZ/ADuM1411ARWZ/ADuM1412ARWZMinimum Pulse Width2PW 1000 ns C L = 15 pF, CMOS signal levels Maximum Data Rate3 1 Mbps C L = 15 pF, CMOS signal levels Propagation Delay4t PHL, t PLH20 65 100 ns C L = 15 pF, CMOS signal levels Pulse Width Distortion, |t PLH − t PHL|4 PWD 40 ns C L = 15 pF, CMOS signal levels Propagation Delay Skew5t PSK50 ns C L = 15 pF, CMOS signal levels Channel-to-Channel Matching6t PSKCD/OD50 ns C L = 15 pF, CMOS signal levels ADuM1410BRWZ/ADuM1411BRWZ/ADuM1412BRWZMinimum Pulse Width2PW 100 ns C L = 15 pF, CMOS signal levels Maximum Data Rate310 Mbps C L = 15 pF, CMOS signal levels Propagation Delay4t PHL, t PLH20 30 50 ns C L = 15 pF, CMOS signal levels Pulse Width Distortion, |t PLH − t PHL|4 PWD 5 ns C L = 15 pF, CMOS signal levels Change vs. Temperature 5 ps/°C C L = 15 pF, CMOS signal levels Propagation Delay Skew5t PSK30 ns C L = 15 pF, CMOS signal levels Channel-to-Channel Matching,Codirectional Channels6t PSKCD 5 ns C L = 15 pF, CMOS signal levelsChannel-to-Channel Matching,Opposing-Directional Channels6t PSKOD 6 ns C L = 15 pF, CMOS signal levelsAll ModelsOutput Rise/Fall Time (10% to 90%) t R/t F 2.5 ns C L = 15 pF, CMOS signal levelsCommon-Mode Transient Immunity at Logic High Output7|CM H| 25 35 kV/µs V Ix = V DD1 or V DD2, V CM = 1000 V,transient magnitude = 800 VCommon-Mode Transient Immunity at Logic Low Output7 |CM L| 25 35 kV/µs V Ix = 0 V, V CM = 1000 V,transient magnitude = 800 VRefresh Rate f r 1.2 MbpsInput Enable Time8t ENABLE 2.0 µs V IA, V IB, V IC, V ID = 0 V or V DD1 Input Disable Time8t DISABLE 5.0 µs V IA, V IB, V IC, V ID = 0 V or V DD1Input Dynamic Supply Current per Channel9I DDI (D)0.12 mA/MbpsOutput Dynamic Supply Current per Channel9I DDO (D)0.04 mA/Mbps1 The supply current values for all four channels are combined when running at identical data rates. Output supply current values are specified with no output load present. The supply current associated with an individual channel operating at a given data rate can be calculated as described in the Power Consumption section. See Figure 8 through Figure 10 for information on per-channel supply current as a function of data rate for unloaded and loaded conditions. See Figure 11 through Figure 15 for total V DD1 and V DD2 supply currents as a function of data rate for ADuM1410/ADuM1411/ADuM1412 channel configurations.2 The minimum pulse width is the shortest pulse width at which the specified pulse width distortion is guaranteed.3 The maximum data rate is the fastest data rate at which the specified pulse width distortion is guaranteed.4 t PHL propagation delay is measured from the 50% level of the falling edge of the V Ix signal to the 50% level of the falling edge of the V Ox signal. t PLH propagation delay is measured from the 50% level of the rising edge of the V Ix signal to the 50% level of the rising edge of the V Ox signal.5 t PSK is the magnitude of the worst-case difference in t PHL or t PLH that is measured between units at the same operating temperature, supply voltages, and output load within the recommended operating conditions.6 Codirectional channel-to-channel matching is the absolute value of the difference in propagation delays between any two channels with inputs on the same side of the isolation barrier. Opposing-directional channel-to-channel matching is the absolute value of the difference in propagation delays between any two channels with inputs on opposing sides of the isolation barrier.7 |CM H| is the maximum common-mode voltage slew rate that can be sustained while maintaining V O > 0.8 V DD2. |CM L| is the maximum common-mode voltage slew rate that can be sustained while maintaining V O < 0.8 V. The common-mode voltage slew rates apply to both rising and falling common-mode voltage edges. The transient magnitude is the range over which the common mode is slewed.8 Input enable time is the duration from when V DISABLE is set low until the output states are guaranteed to match the input states in the absence of any input data logic transitions. If an input data logic transition within a given channel does occur within this time interval, the output of that channel reaches the correct state within the much shorter duration as determined by the propagation delay specifications within this data sheet. Input disable time is the duration from when V DISABLE is set high until the output states are guaranteed to reach their programmed output levels, as determined by the CTRL2 logic state (see Table 14).9 Dynamic supply current is the incremental amount of supply current required for a 1 Mbps increase in signal data rate. See Figure 8 through Figure 10 for information on per-channel supply current for unloaded and loaded conditions. See the Power Consumption section for guidance on calculating the per-channel supply current for a given data rate.Rev. M | Page of 22Data Sheet ADuM1410/ADuM1411/ADuM1412ELECTRICAL CHARACTERISTICS—3 V OPERATION2.7 V ≤ V DD1 ≤3.6 V, 2.7 V ≤ V DD2 ≤ 3.6 V; all minimum/maximum specifications apply over the entire recommended operation range, unless otherwise noted; all typical specifications are at T A = 25°C, V DD1 = V DD2 = 3.0 V. All voltages are relative to their respective ground. Table 2.Parameter Symbol Min Typ Max Unit Test Conditions/CommentsDC SPECIFICATIONSInput Supply Current per Channel,QuiescentI DDI (Q)0.25 0.38 mAOutput Supply Current per Channel,QuiescentI DDO (Q)0.19 0.33 mAADuM1410, Total Supply Current,Four Channels1DC to 2 MbpsV DD1 Supply Current I DD1 (Q) 1.2 1.6 mA DC to 1 MHz logic signalfrequency V DD2 Supply Current I DD2 (Q)0.8 1.0 mA DC to 1 MHz logic signalfrequency10 Mbps (BRWZ Version Only)V DD1 Supply Current I DD1 (10) 4.5 6.5 mA 5 MHz logic signal frequency V DD2 Supply Current I DD2 (10) 1.4 1.8 mA 5 MHz logic signal frequency ADuM1411, Total Supply Current,Four Channels1DC to 2 MbpsV DD1 Supply Current I DD1 (Q) 1.0 1.9 mA DC to 1 MHz logic signal frequency V DD2 Supply Current I DD2 (Q)0.9 1.7 mA DC to 1 MHz logic signal frequency10 Mbps (BRWZ Version Only)V DD1 Supply Current I DD1 (10) 3.1 4.5 mA 5 MHz logic signal frequency V DD2 Supply Current I DD2 (10) 2.1 3.0 mA 5 MHz logic signal frequency ADuM1412, Total Supply Current,Four Channels1DC to 2 MbpsV DD1 or V DD2 Supply Current I DD1 (Q), I DD2 (Q) 1.0 1.8 mA DC to 1 MHz logic signal frequency10 Mbps (BRWZ Version Only)V DD1 or V DD2 Supply Current I DD1 (10), I DD2 (10) 2.6 3.8 mA 5 MHz logic signal frequencyAll ModelsInput Currents I IA, I IB, I IC, I ID,I CTRL1,I CTRL2, I DISABLE −10 +0.01 +10µA 0 V ≤ V IA, V IB, V IC, V ID ≤ V DD1 or V DD2,0 V ≤ V CTRL1, V CTRL2 ≤ V DD1 or V DD2,0 V ≤ V DISABLE ≤ V DD1Logic High Input Threshold V IH 1.6 V Logic Low Input Threshold V IL 0.4 VLogic High Output Voltages V OAH, V OBH,V OCH, V ODH (V DD1 or V DD2) − 0.1 3.0 V I Ox = −20 µA, V Ix = V IxH (V DD1 or V DD2) − 0.4 2.8 V I Ox = −4 mA, V Ix = V IxHLogic Low Output Voltages V OAL, V OBL,V OCL, V ODL0.0 0.1 V I Ox = 20 µA, V Ix = V IxL0.04 0.1 V I Ox = 400 µA, V Ix = V IxL0.2 0.4 V I Ox = 4 mA, V Ix = V IxL Rev. M | Page of 22ADuM1410/ADuM1411/ADuM1412 Data Sheet。

亚赫英氏SQ-6混音控制台指南说明书

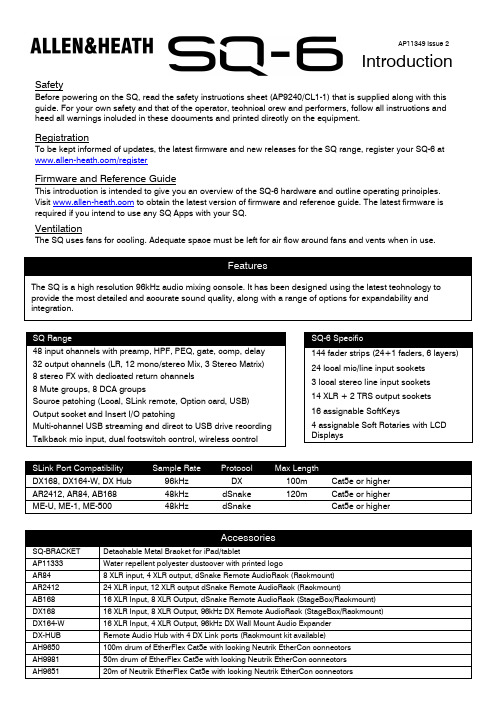

IntroductionSafetyBefore powering on the SQ, read the safety instructions sheet (AP9240/CL1-1) that is supplied along with this guide. For your own safety and that of the operator, technical crew and performers, follow all instructions and heed all warnings included in these documents and printed directly on the equipment. RegistrationTo be kept informed of updates, the latest firmware and new releases for the SQ range, register your SQ-6 at /registerFirmware and Reference GuideThis introduction is intended to give you an overview of the SQ-6 hardware and outline operating principles. Visit to obtain the latest version of firmware and reference guide. The latest firmware is required if you intend to use any SQ Apps with your SQ.VentilationThe SQ uses fans for cooling. Adequate space must be left for air flow around fans and vents when in use.FeaturesThe SQ is a high resolution 96kHz audio mixing console. It has been designed using the latest technology to provide the most detailed and accurate sound quality, along with a range of options for expandability and integration.AP11349 Issue 2AccessoriesSQ-BRACKET Detachable Metal Bracket for iPad/tabletAP11333 Water repellent polyester dustcover with printed logoAR84 8 XLR input, 4 XLR output, dSnake Remote AudioRack (Rackmount) AR2412 24 XLR input, 12 XLR output dSnake Remote AudioRack (Rackmount)AB168 16 XLR Input, 8 XLR Output, dSnake Remote AudioRack (StageBox/Rackmount) DX168 16 XLR Input, 8 XLR Output, 96kHz DX Remote AudioRack (StageBox/Rackmount) DX164-W 16 XLR Input, 4 XLR Output, 96kHz DX Wall Mount Audio Expander DX-HUB Remote Audio Hub with 4 DX Link ports (Rackmount kit available) AH9650 100m drum of EtherFlex Cat5e with locking Neutrik EtherCon connectors AH9981 50m drum of EtherFlex Cat5e with locking Neutrik EtherCon connectors AH965120m of Neutrik EtherFlex Cat5e with locking Neutrik EtherCon connectorsSLink Port Compatibility Sample Rate Protocol Max LengthDX168, DX164-W, DX Hub 96kHz DX 100m Cat5e or higher AR2412, AR84, AB168 48kHz dSnake 120mCat5e or higher ME-U, ME-1, ME-50048kHzdSnakeCat5e or higherSQ Range48 input channels with preamp, HPF, PEQ, gate, comp, delay 32 output channels (LR, 12 mono/stereo Mix, 3 Stereo Matrix) 8 stereo FX with dedicated return channels 8 Mute groups, 8 DCA groupsSource patching (Local, SLink remote, Option card, USB) Output socket and Insert I/O patchingMulti-channel USB streaming and direct to USB drive recording Talkback mic input, dual footswitch control, wireless controlSQ-6 Specific144 fader strips (24+1 faders, 6 layers) 24 local mic/line input sockets 3 local stereo line input sockets 14 XLR + 2 TRS output sockets 16 assignable SoftKeys4 assignable Soft Rotaries with LCD DisplaysLocal Mic/Line Inputs Local Stereo Line Inputs Talkback Mic Input Local XLR OutputsLocal TRS Jack OutputsAES Digital OutputMono/Dual Footswitch Connection Mains Power Input and Switch I/O Port - Option CardMulti-format multi-channel digital audioUSB-B PortConnection to a computer for multi-channel audio and MIDI I/O Network Port Connect to a router for network/wireless controlSLink PortFor connection to Allen&Heath remote audio racks, including AB, AR and DX ranges, as well as the ME personal monitoring systemTouch Screen, Screen Select Keys and Screen EncoderView processing and access the routing and setup menus using keys below. Touch to select a parameter and use the rotary to adjust values.Fader Strips and Layer Select Keys6 layers of 24 faders provide 144 assignable strips for access to any combination of channels, returns,masters and DCAs. Each strip has fader, mute, select and PAFL keys, peak and signal meter.Ident StripLCD displays show channel name and colour for each of the 24 strips. Press the‘View’ key to see secondary information such as input source.Channel(Pre/HPF/Gate/Comp)Physical controls for the selected channel. Preamp, HPF frequency, Gate threshold, Comp threshold.Channel (PEQ/GEQ)Physical controls for the selected channel. EQ band select keys and parametric controls. Use the ‘Fader Flip’ key to present selected mix GEQ on faders. Pan ControlMaster Strip and Mix Select KeysPress a blue ‘Mix’ key to present its sends on the 24 faders and its master on the master fader strip. Select ‘LR’ to work with the main LR mix and channel faders.FX Send Select KeysPress a blue ‘FX’ key to present its sends on the 24 faders and its master send on the master fader strip. Headphone Output and Level Control Main MeterDisplays the LR Mix or selected PAFL signal level.Talk KeyMomentary or latching switch for the talkback microphone.SQ-Drive PortRecord/play audio direct to/from a USB drive. Transfer scene, show and library data using a USB key. Update SQ firmware.ST3 Input3.5mm stereo jack input, can be used for connection to an external background music device.Pre Fade and Assign KeysHold ‘Pre-Fade’ and press ‘Sel’ to toggle channels pre or post fade to the mix. Hold ‘Assign’ and press ‘Sel’ to route channels to the selected mix.CH to All Mix KeyPress and hold to present all sends to mixes for the currently selected channel. The ident strip displays mix names. Copy/Paste/Reset KeysUsed to copy, paste or reset processing blocks or channel parameters.Library KeyOpens different libraries to enable save and recall of presets for channel/mix/FX processing.Assignable SoftKeysUse Setup screen to assign functions such as mutes, tap tempo, scene recall, SQ-Drive control and more.Assignable EncodersUse Setup screen to assign functions for quick access to often used parameters.i. Power off any connected amplifiers or powered speakers. ii. Navigate to the ‘Home’ screen and select ‘Shut Down’ iii.Switch off the unit using the push switch (27).Press a blue ‘LR’, ‘Mix’ or ‘FX’ Key to present send levels for the selected Mix on the 24 Fader Strips. Use the Layer Keys (2) to move through the 6 layers of faders and adjust individual levels. The Master strip (7) controls the master send level of the selected Mix/FX.Select a strip by pressing the green ‘Sel’ Key on a Fader Strip (2) or the Master Strip (7).The physical controls (4), (5) and (6) can now be used to adjust parameters for the selected strip.Go to the ‘Processing’ screen to see an overview of the processing for the selected strip.Tap on any part of the processing to see a detailed view, then touch a parameter on-screen and use the touch screen encoder (1) to adjust.Mute Keys are illuminated when a strip is muted.By default, PAFL (Pre/After Fade Listen) Keys allow you to route one channel at a time to the PAFL bus/Phones output. PAFL settings can be changed in the ‘Setup’ screen.Mix sends set to ‘Post Fade’ follow the LR send levels. To toggle channels between ‘Pre Fade’ and ‘Post Fade’ for the selected Mix, hold the ‘Pre Fade’ Key and use ‘Sel’ Keys.To assign or un-assign a strip from the currently selected mix, hold the ‘Assign’ Key and use ‘Sel’ Keys.Pressing and holding the ‘CH to All Mix’ Key will display the send levels for the currently selected strip across the main fader strips.Press the ‘FX’ Key to see and adjust FX engines.Use the ‘Library’ Key (17) to recall FX types and presets - change parameters by selecting on-screen and using the touch screen encoder.FX busses 1 to 4 (8) send to FX engines 1 to 4 by default.FX Return channels can be routed to Mixes in the same way as stereo input channels.Hold the ‘Copy’ Key and press an ‘In’ Key (4) (5), a ‘Sel’ Key (2) (7), to copy parameters.Hold the ‘Paste’ Key and press a ‘Sel’ Key (2) (7) to paste the copied processing to another channel. Hold the ‘Reset’ Key and press an ‘In’ Key (4) (5), a ‘Sel’ Key (2) (7), or on-screen to reset parameters.A ‘Scene’ is used to store or recall a mix. A ‘Show’ comprises multiple scenes and all settings. Press the ‘Scenes’ Key to access the list of scenes in the current show.Use a combination of scene filters and ‘Safes’ to decide which settings/parameters/strips are affected when a scene is recalled.i. Connect power lead (27).ii. Connect input sources using (20), (21) and (22).iii. Connect outputs (23) and (24) to amplifiers, speakers or line level inputs on other equipment. iv. If required, connect digital I/O such as AudioRacks or Computers using (25), (28), (29) and (31). v. If you are using a footswitch, connect this (26). vi. Switch on the SQ using the push switch (27).vii.Power on any connected amplifiers or powered speakers.To reset all mix, parameter and routing settings go to the ‘Scenes’ screen (1), then press and hold the ‘Reset Mix Settings’ button. This will ‘zero’ the desk without deleting saved scenes or libraries.To check or alter patching, go to the ‘I/O’ screen (1) and use the matrix to patch from Local/Digital Inputs to SQ input channels, and to patch SQ outputs [LR/Mix/Group/Matrix/DirectOut] to Local/Digital Outputs.Balanced mono/stereo inputs Mic or line level XLR 1=Gnd, 2=+, 3= -ST1 and ST2 Inputs Line level ¼” TRS Jack Tip= +, Ring= -, Sleeve=GndST3 Input Line level 3.5mm Jack Tip=Left, Ring=Right, Sleeve=Gnd Balanced XLR Outputs Line level XLR 1=Gnd, 2= +, 3= -Balanced Jack Outputs Line level ¼” TRS Jack Tip= +, Ring= -, Sleeve=GndSLink RJ45/EtherCON. Use Cat5e or higher. Refer to individual expansion unit instructions.AES Stereo Digital Output Digital XLR Use 110Ω AES CableRear USB Connection USB-B, Conforms to USB 2.0 standardNetwork Connection RJ45, Use Cat5e or higherFootswitch ¼” TRS (dual) or TS (mono) JackThere are many support resources available through our website including user guides, knowledgebase articles and access to the Allen & Heath Digital Community.For local language support, please contact the Allen & Heath distributor for your region.Limited One Year Manufacturer’s WarrantyAllen & Heath warrants the Allen & Heath -branded hardware product and accessories contained in the original packaging ("Allen & Heath Product”) against defects in materials and workmanship when used in accordance with Allen & Heath's user manuals, technical specifications and other Allen & Heath product published guidelines for a period of ONE (1) YEAR from the date of original purchase by the end-user purchaser ("Warranty Period").This warranty does not apply to any non-Allen & Heath branded hardware products or any software, even if packaged or sold with Allen & Heath hardware.Please refer to the licensing agreement accompanying the software for details of your rights with respect to the use of software/firmware (“EULA”).Details of the EULA, warranty policy and other useful information can be found on the Allen & Heath website: /legal.Repair or replacement under the terms of the warranty does not provide right to extension or renewal of the warranty period. Repair or direct replacement of the product under the terms of this warranty may be fulfilled with functionally equivalent service exchange units.This warranty is not transferable. This warranty will be the purchaser’s sole and exclusive remedy and neither Allen & Heath nor its approved service centres shall be liable for any incidental or consequential damages or breach of any express or implied warranty of this product.Conditions of WarrantyThe equipment has not been subject to misuse either intended or accidental, neglect, or alteration other than as described in the User Guide or Service Manual, or approved by Allen & Heath. The warranty does not cover fader wear and tear.Any necessary adjustment, alteration or repair has been carried out by an authorised Allen & Heath distributor or agent. The defective unit is to be returned carriage prepaid to the place of purchase, an authorised Allen & Heath distributor or agent with proof of purchase. Please discuss this with the distributor or the agent before shipping. Units returned should be packed in the original carton to avoid transit damage.DISCLAIMER: Allen & Heath shall not be liable for the loss of any saved/stored data in products that are either repaired or replaced.Check with your Allen & Heath distributor or agent for any additional warranty information which may apply. If further assistance is required please contact Allen & Heath Ltd.Any changes or modifications to the equipment not approved by Allen & Heath could void the compliance of the product and therefore the user’s authority to operate it.。

max485esa中文资料

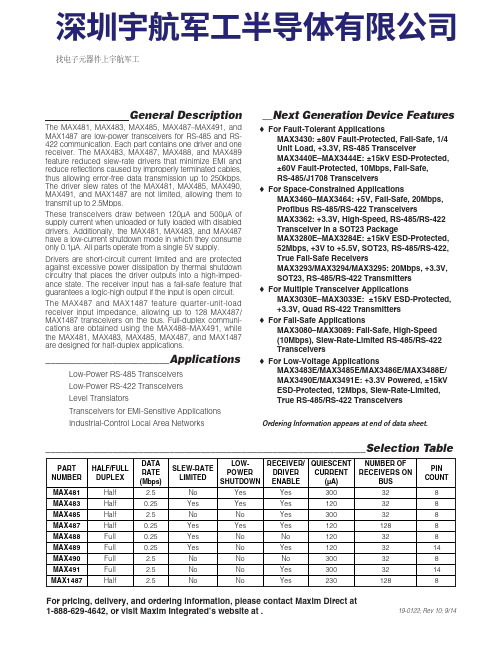

General DescriptionThe MAX481, MAX483, MAX485, MAX487–MAX491, andMAX1487 are low-power transceivers for RS-485 and RS-422 communication. Each part contains one driver and onereceiver. The MAX483, MAX487, MAX488, and MAX489feature reduced slew-rate drivers that minimize E MI andreduce reflections caused by improperly terminated cables,thus allowing error-free data transmission up to 250kbps.The driver slew rates of the MAX481, MAX485, MAX490,MAX491, and MAX1487 are not limited, allowing them totransmit up to 2.5Mbps.These transceivers draw between 120µA and 500µA ofsupply current when unloaded or fully loaded with disableddrivers. Additionally, the MAX481, MAX483, and MAX487have a low-current shutdown mode in which they consumeonly 0.1µA. All parts operate from a single 5V supply.Drivers are short-circuit current limited and are protectedagainst excessive power dissipation by thermal shutdowncircuitry that places the driver outputs into a high-imped-ance state. The receiver input has a fail-safe feature thatguarantees a logic-high output if the input is open circuit.The MAX487 and MAX1487 feature quarter-unit-loadreceiver input impedance, allowing up to 128 MAX487/MAX1487 transceivers on the bus. Full-duplex communi-cations are obtained using the MAX488–MAX491, whilethe MAX481, MAX483, MAX485, MAX487, and MAX1487are designed for half-duplex applications.________________________Applications Low-Power RS-485 Transceivers Low-Power RS-422 Transceivers Level Translators Transceivers for EMI-Sensitive Applications Industrial-Control Local Area Networks__Next Generation Device Features o For Fault-Tolerant Applications MAX3430: ±80V Fault-Protected, Fail-Safe, 1/4Unit Load, +3.3V, RS-485 Transceiver MAX3440E–MAX3444E: ±15kV ESD-Protected,±60V Fault-Protected, 10Mbps, Fail-Safe, RS-485/J1708 Transceivers o For Space-Constrained Applications MAX3460–MAX3464: +5V, Fail-Safe, 20Mbps,Profibus RS-485/RS-422 Transceivers MAX3362: +3.3V, High-Speed, RS-485/RS-422Transceiver in a SOT23 Package MAX3280E–MAX3284E: ±15kV ESD-Protected,52Mbps, +3V to +5.5V, SOT23, RS-485/RS-422,True Fail-Safe Receivers MAX3293/MAX3294/MAX3295: 20Mbps, +3.3V,SOT23, RS-485/RS-422 Transmitters o For Multiple Transceiver Applications MAX3030E–MAX3033E: ±15kV ESD-Protected,+3.3V, Quad RS-422 Transmitters o For Fail-Safe Applications MAX3080–MAX3089: Fail-Safe, High-Speed (10Mbps), Slew-Rate-Limited RS-485/RS-422Transceiverso For Low-Voltage ApplicationsMAX3483E/MAX3485E/MAX3486E/MAX3488E/MAX3490E/MAX3491E: +3.3V Powered, ±15kVESD-Protected, 12Mbps, Slew-Rate-Limited,True RS-485/RS-422 Transceivers For pricing, delivery, and ordering information, please contact Maxim Direct at1-888-629-4642, or visit Maxim Integrated’s website at .______________________________________________________________Selection Table19-0122; Rev 10; 9/14PARTNUMBERHALF/FULL DUPLEX DATA RATE (Mbps) SLEW-RATE LIMITED LOW-POWER SHUTDOWN RECEIVER/DRIVER ENABLE QUIESCENT CURRENT (μA) NUMBER OF RECEIVERS ON BUS PIN COUNT MAX481Half 2.5No Yes Yes 300328MAX483Half 0.25Yes Yes Yes 120328MAX485Half 2.5No No Yes 300328MAX487Half 0.25Yes Yes Yes 1201288MAX488Full 0.25Yes No No 120328MAX489Full 0.25Yes No Yes 1203214MAX490Full 2.5No No No 300328MAX491Full 2.5No No Yes 3003214MAX1487 Half 2.5No No Yes 2301288Ordering Information appears at end of data sheet.找电子元器件上宇航军工MAX481/MAX483/MAX485/MAX487–MAX491/MAX1487Low-Power, Slew-Rate-LimitedRS-485/RS-422 TransceiversPackage Information For the latest package outline information and land patterns, go to . Note that a “+”, “#”, or “-”in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.16Low-Power, Slew-Rate-Limited RS-485/RS-422 TransceiversMAX481/MAX483/MAX485/MAX487–MAX491/MAX1487Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.Maxim Integrated 160 Rio Robles, San Jose, CA 95134 USA 1-408-601-100017©2014 Maxim Integrated Products, Inc.Maxim Integrated and the Maxim Integrated logo are trademarks of Maxim Integrated Products, Inc.。

MEMORY存储芯片ADM485ARZ-REEL中文规格书

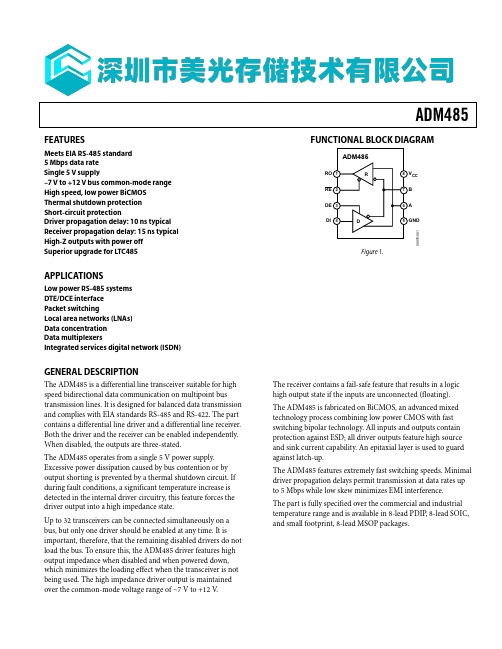

ADM485FUNCTIONAL BLOCK DIAGRAMCC 00078-001FEATURESMeets EIA RS-485 standard 5 Mbps data rateSingle 5 V supply–7 V to +12 V bus common-mode range High speed, low power BiCMOS Thermal shutdown protection Short-circuit protectionDriver propagation delay: 10 ns typical Receiver propagation delay: 15 ns typical High-Z outputs with power off Superior upgrade for LTC485APPLICATIONSLow power RS-485 systems DTE/DCE interface Packet switchingLocal area networks (LNAs) Data concentration Data multiplexersIntegrated services digital network (ISDN)GENERAL DESCRIPTIONThe ADM485 is a differential line transceiver suitable for high speed bidirectional data communication on multipoint bus transmission lines. It is designed for balanced data transmission and complies with EIA standards RS-485 and RS-422. The part contains a differential line driver and a differential line receiver. Both the driver and the receiver can be enabled independently. When disabled, the outputs are three-stated.The ADM485 operates from a single 5 V power supply. Excessive power dissipation caused by bus contention or by output shorting is prevented by a thermal shutdown circuit. If during fault conditions, a significant temperature increase is detected in the internal driver circuitry, this feature forces the driver output into a high impedance state.Up to 32 transceivers can be connected simultaneously on a bus, but only one driver should be enabled at any time. It is important, therefore, that the remaining disabled drivers do not load the bus. To ensure this, the ADM485 driver features high output impedance when disabled and when powered down, which minimizes the loading effect when the transceiver is not being used. The high impedance driver output is maintained over the common-mode voltage range of −7 V to +12 V .Figure 1.The receiver contains a fail-safe feature that results in a logic high output state if the inputs are unconnected (floating). The ADM485 is fabricated on BiCMOS, an advanced mixed technology process combining low power CMOS with fast switching bipolar technology. All inputs and outputs contain protection against ESD; all driver outputs feature high source and sink current capability. An epitaxial layer is used to guard against latch-up.The ADM485 features extremely fast switching speeds. Minimal driver propagation delays permit transmission at data rates up to 5 Mbps while low skew minimizes EMI interference. The part is fully specified over the commercial and industrial temperature range and is available in 8-lead PDIP , 8-lead SOIC, and small footprint, 8-lead MSOP packages.ADM485Rev. F | Page 2 of 16ADM485SPECIFICATIONSV CC = 5 V ± 5%, all specifications T MIN to T MAX, unless otherwise noted.Rev. F | Page 3 of 16ADM485TIMING SPECIFICATIONSV CC = 5 V ± 5%, all specifications T MIN to T MAX, unless otherwise noted.1 Guaranteed by characterization.Rev. F | Page 4 of 16ADM485Rev. F | Page 5 of 16ABSOLUTE MAXIMUM RATINGST A = 25°C, unless otherwise noted.Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operationalsection of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Table 4. TransmittingInputsOutputsDE DIB A 1 1 0 1 1 0 1 0 0X 1Z 2Z 21 X = don’t care.2Z = high impedance.1 X = don’t care.2Z = high impedance.ESD CAUTION。

千兆光猫用户手册说明书

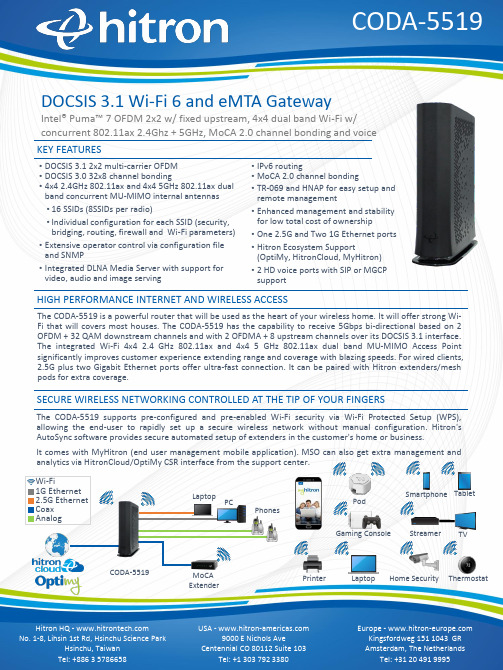

The CODA-5519is a powerful router that will be used as the heart of your wireless home.It will offer strong Wi-Fi that will covers most houses.The CODA-5519has the capability to receive 5Gbps bi-directional based on 2OFDM +32QAM downstream channels and with 2OFDMA +8upstream channels over its DOCSIS 3.1interface.The integrated Wi-Fi 4x42.4GHz 802.11ax and 4x45GHz 802.11ax dual band MU-MIMO Access Point significantly improves customer experience extending range and coverage with blazing speeds.For wired clients,2.5G plus two Gigabit Ethernet ports offer ultra-fast connection.It can be paired with Hitron extenders/mesh pods for extra coverage.•DOCSIS 3.1 2x2 multi-carrier OFDM •DOCSIS 3.0 32x8 channel bonding•4x4 2.4GHz 802.11ax and 4x4 5GHz 802.11ax dual band concurrent MU-MIMO internal antennas •16 SSIDs (8SSIDs per radio)•Individual configuration for each SSID (security, bridging, routing, firewall and Wi-Fi parameters)•Extensive operator control via configuration file and SNMP•Integrated DLNA Media Server with support for video, audio and image servingDOCSIS 3.1 Wi-Fi 6 and eMTA GatewayIntel® Puma™ 7 OFDM 2x2 w / fixed upstream, 4x4 dual band Wi-Fi w/ concurrent 802.11ax 2.4Ghz + 5GHz, MoCA 2.0 channel bonding and voice HIGH PERFORMANCE INTERNET AND WIRELESS ACCESSThe CODA-5519supports pre-configured and pre-enabled Wi-Fi security via Wi-Fi Protected Setup (WPS),allowing the end-user to rapidly set up a secure wireless network without manual configuration.Hitron's AutoSync software provides secure automated setup of extenders in the customer's home or business.It comes with MyHitron (end user management mobile application).MSO can also get extra management and analytics via HitronCloud/OptiMy CSR interface from the support center.SECURE WIRELESS NETWORKING CONTROLLED AT THE TIP OF YOUR FINGERSKEY FEATURES•IPv6 routing•MoCA 2.0 channel bonding•TR-069 and HNAP for easy setup and remote management•Enhanced management and stability for low total cost of ownership•One 2.5G and Two 1G Ethernet ports •Hitron Ecosystem Support (OptiMy, HitronCloud, MyHitron)•2 HD voice ports with SIP or MGCP supportTVStreamer Smartphone TabletThermostatHome Security LaptopCODA-5519Printer PCMoCA ExtenderPhonesWi-Fi1G Ethernet Analog2.5G Ethernet Coax PodLaptop Gaming ConsoleConnectivity•RF F-Type 75Ωfemale connector•2x RJ-45 Ethernet port 10/100/1000Mbps•1x RJ-45 Ethernet port 10/100/1000/2500Mbps•USB 3.0 type A connector with host interface•2x RJ-11 HD voice ports•EBBU jackManagement•Protocol support: TR-069, TFTP, SSHv2, SNMP v2C, v3•Web-based GUI control, configuration and management •Power-on self diagnostic•Hitron proprietary MIBs for extended support onDOCSIS, router management, Wi-Fi managementand MoCA management•app support•and back end supportReception-Demodulation•DOCSIS 3.1/3.0/2.0•DOCSIS 3.1 demodulation: Multi-carrier OFDM 16 to 4096QAM •DOCSIS 3.1 data rate: Up to 5Gps with 2 OFDM 192MHz downstream channels +32 QAM•DOCSIS 3.0 demodulation: 64QAM, 256QAM•DOCSIS 3.0 data rate: Up to 1.2Gbps with 32 bonded downstream channels•Frequency (edge-to-edge): 108-1218MHz and 258-1218 •Channel Bandwidth: 6MHz•Signal level: -15dBmV to 15dBmVTransmitter-Modulation•DOCSIS 3.1/3.0/2.0•DOCSIS 3.1 modulation: Multi-carrier OFDMA BPSK to 4096QAM •DOCSIS 3.1 data rate: Up to 700Mbps with OFDMA 96MHz upstream channels•DOCSIS 3.0 modulation: QPSK, 8QAM, 16QAM, 32QAM, 64QAM, and 128QAM (SCDMA only)•DOCSIS 3.0 data rate: Up to 320Mbps with 8 bonded upstream channels•Frequency: Fixed 5-85MHz•Upstream transmit signal level: +11 to 65dBmVMoCA 2.0 Reception / Transmitter-Modulation •Demodulation/ Modulation: BPSK, QPSK, 8QAM, 16QAM,32QAM, 64QAM, 128QAM, 256QAM, 512QAM, 1024QAM •PHY data rate: 700Mbps (baseline Mode) / 1400Mbps (bonding channel)•Throughput: 400+Mbps (baseline mode) / 500+Mbps (turbo mode, point to point) / 800Mbps (bonding channel)•Frequency (center frequencies): 1400-1625MHz•Channel bandwidth: 100MHz (baseline mode) / 225MHz (bonding channel)Voice•Protocol support: SIP or MGCP•2x 8kHz each HD voice•Audio codecs: G.711 (a-law and mu-law), G.722 (HD codec), G.723.1, G.726, G.728, and G.729Routing Support•Protocol support: IGMP v3 for IPTV service capability•MAC address filtering (IPv4/IPv6)•IP source/destination address filtering (IPv4/IPv6)•DHCP, TFTP and ToD clients (IPv4/IPv6)•DHCP server supports RFC 1541 (IPv4)•DHCPv6 obtains prefix from DHCPv6 server through prefix delegation•Firewall with stateful inspection (IPv4/IPv6)•Hacker intrusion prevention and detection•Application content filtering (IPv4/IPv6)•Complete NAT software implemented as per RFC 1631 with port and address mapping (IPv4)•DSLite support for IPv4 in-home support with IPv6 MSO backbone •6RD support for quick IPv6 deployment over IPv4 backbone •RIPv2 for static IP supportWireless•802.11a/b/g/n/ac/ax•4T4R 2.4GHz 11ax and 4T4R 5GHz 11ax dual band concurrent MU-MIMO with 1Gbps+4.8Gbps PHY rate•20/40/80/160MHz channel bandwidth•Up to 8 SSIDs for each frequency•Security: WPA-PSK/WPA2-PSK (TKIP/AES), WPA3, WAPI •QoS: WMM/WMM-PS•WPS (Wi-Fi Protected Setup) PBC, PIN•Airtime Fairness (ATF), Band Steering (BS)•Dynamic Frequency Selection (DFS)•Wi-Fi output power range: Max permitted by FCC/IC Electrical•Input power: 12VDC, 4A•Power adaptor: 100-240VAC, 50/60Hz•Power consumption: 4.92 (power saving), 22W (typ.), 38W (Max)•Support power outage for 24 hours on Hitron external battery •Surge protection: RF input sustains at least 4KVEthernet RJ-45 sustains at least 4KV Mechanical•Factory default reset button•WPS button•Dimensions: 74.3mm (W) x 251.5mm (H) x 230.8mm (D)•Weight: Weight: 1850 ±10gEnvironmental•Operating temperature: 0°C (32°F) ~ 40°C (104°F)•Operating humidity: 10% ~ 90% (Non-condensing)•Storage temperature: -40°C (-40°F) ~ 60°C (140°F) Compliance Certificates•RoHS compliant•FCC, IC, ULSPECIFICATIONS。

ADI 磁隔离芯片选型表

三通道数字隔离器

型号 通道 3/0 3/0 3/0 2/1 2/1 2/1 3/0 3/0

ADUM1300ARWZ ADUM1300BRWZ ADUM1300CRWZ ADUM1301ARWZ ADUM1301BRWZ ADUM1301CRWZ ADUM1300WSRWZ ADUM1300WTRWZ

单通道数字隔离器型号通道1010101010adum1100arzadum1100brzadum1100urzadum3100arzadum3100brz隔离电压传输速率工作电压工作温度vrmsmbpsv250025305540105250010030554010525001003055401252500253055401052500100305540105封装soic8soic8soic8soic8soic8千片批量价163186279171196双通道数字隔离器型号通道202020111111202020111111202020111120202011111120201111adum1200arzadum1200brzadum1200crzadum1201arzadum1201brzadum1201crzadum1200wsrzadum1200wtrzadum1200wurzadum1201wsrzadum1201wtrzadum1201wurzadum1210brzadum2200arwzadum2200brwzadum2201arwzadum2201brwzadum3200arzadum3200brzadum3200crzadum3201arzadum3201brzadum3201crzadum3210brzadum3210trzadum3211brzadum3211trz隔离电压传输速率工作电压工作温度千片批量价封装vrmsmbpsv25001275540105soic8122250010275540105soic8178250025275540105soic824725001275540105soic8122250010275540105soic8178250025275540105soic824725001305540125soic8215250010305540125soic8314250025305540125soic843525001305540125soic8215250010305540125soic8314250025305540125soic8435250010275540105soic817850001305540105sow16167500010305540105sow1623950001305540105sow16167500010305540105sow162392500127

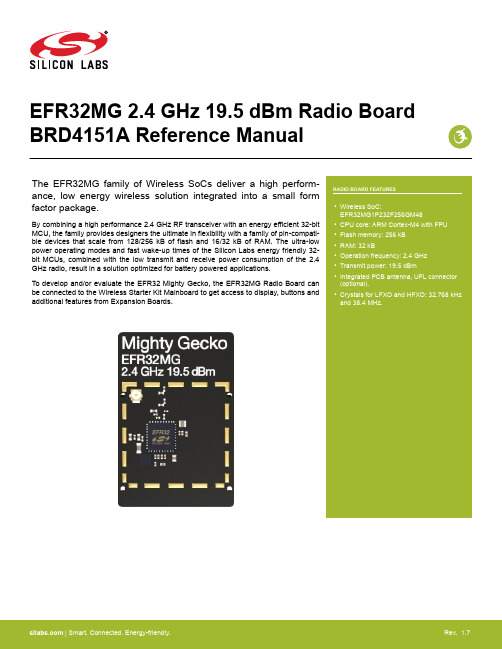

Silicon Labs EFR32MG 2.4 GHz 19.5 dBm 无线模组板参考手册说明书