AT24C02B中文资料

AT24Cxx中文数据手册

AT24C01A/02/04/08A/16A提供1024/2048/4096/8192/16384个连续的可擦除的位,以及由每8位组成一个字节的可编程只读存储器(EEPROM),其分别提供128/256/512/1024/2048个字节。

该设备适用在许多低功耗和低电压操作的工业和商业应用中。

1引脚描述1.1串行时钟(SCL)SCL输入用于正向输出边缘时钟信号到每个EEPROM设备,以及每个设备输出的反向边缘时钟数据。

1.2串行数据(SDA)SDA引脚是用于串行数据双向传输。

该引脚为开漏输出,同时可以与其他开漏极或集电极开路器件进行线或。

1.3设备/页地址(A2,A1,A0)对于AT24C01A和AT24C02,A2、A1和A0引脚是配置器件的硬件地址输入。

一根总线上可以连接多达八个1K / 2K的设备(器件寻址部分详细讨论了器件寻址)。

AT24C04使用A2和A1引脚作为硬件地址输入,在一根总线上有4个4K 的设备可用来寻址。

A0引脚没有连接。

AT24C08A只使用A2引脚作为硬件地址输入,在一根总线上有2个8K 的设备可用来寻址。

A0和A1引脚没有连接。

AT24C16A不使用设备地址引脚,这限制了一根总线上只能挂一个设备。

A0、A1和A2引脚没有连接。

1.4写保护(WP)AT24C01A / 02 / 04 / 08A/ 16A有一个写保护引脚,提供硬件数据保护。

写保护引脚允许正常读/写操作时连接到GND。

当写保护引脚连接到VCC,写保护功能启用和操作如下表所示。

2设备操作2.1时钟和数据转换SDA引脚通常情况下拉高。

SDA引脚上的数据只能在SCL低时间段内更改,而启动条件或停止条件在SCL为高时进行。

2.2启动条件在任何其他指令之前,SDA由高变为低,且SCL为高。

2.3停止条件SDA由低变为高,且SCL为高。

在读取序列之后,执行停止命令后EEPROM进入备用电源模式。

2.4应答所有地址和数据字都是从EEPROM串行发送和接收8位字节。

AT24C02的操作要点中文翻译

A0,A1,A2:器件地址配置引脚

SDA:串行数据线

SCL:串行时钟线

WP:写保护(高电平有效)

VCC:+1.8V~+5.5V

内存组织:

AT24C02:共32页,每页8字节。

所以需要8位(高5位为页地址,低3位为字节地址)的字节地址(共寻址256字节地址)

器件支持的操作:

1、时钟和数据的传输:开始和停止条件,数据在SCL的高电平期间有效,在SCL的低电

平期间改变。

2、开始条件:在SCL高电平期间,SDA产生一个下降沿

3、停止条件:在SCL高电平期间,SDA产生一个上升沿

4、应答:成功接收到数据(地址和数据),产生一个应答位(在第9个时钟周期,将SDA

拉低)

5、待机模式:进入待机模式条件:刚上电后;收到STOP位后且器件内部操作完成

6、内存复位:

写操作:

字节写:(一个字节)

页写:(最多8个字节)

当写到一页的末尾后,如果再写入数据,则从同一页的开始处写入,而覆盖原来的数据。

应答查询:一旦器件内部定时编程数据开始,则EEPROM对输入是不反映的。

发送一个开始信号和器件地址,要是EEPROM内部编写完成,将应答(将SDA拉低),以使下一个读或写操作继续。

读操作:

当前地址读:(一个字节)

内部数据地址计数器保存着最后一次的操作地址(读或写)。

只要芯片一直上电,该地址一直有效。

当读到内存的最后字节后,指针将回到第一页的开始地址,而对于写操作,从当前也的最后返回到同一页的第一个字节处。

任意读:(一个字节)

连续读:(是从当前地址读或任意读开始的)。

AT24C02

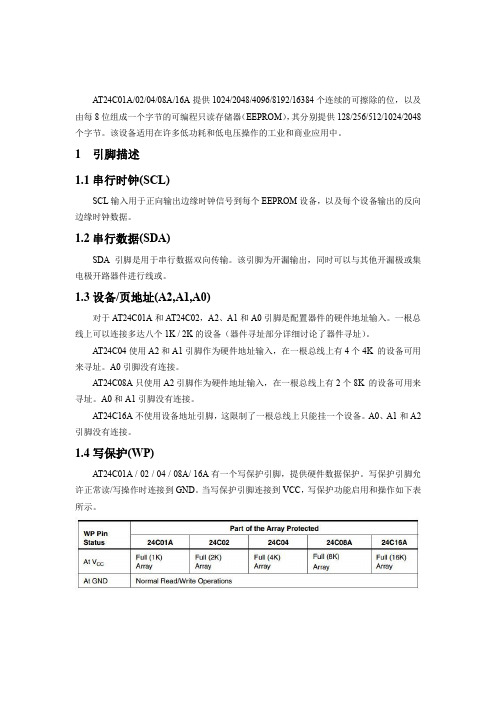

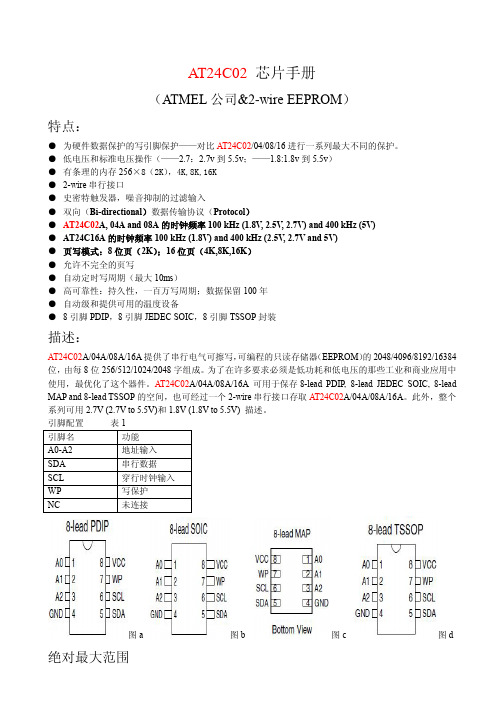

Features•Low Voltage and Standard Voltage Operation5.0 (V CC = 4.5V to 5.5V)2.7 (V CC = 2.7V to 5.5V)2.5 (V CC = 2.5V to 5.5V)1.8 (V CC = 1.8V to 5.5V)•Internally Organized 128 x 8 (1K), 256 x 8 (2K), 512 x 8 (4K),1024 x 8 (8K) or 2048 x 8 (16K)•2-Wire Serial Interface•Bidirectional Data Transfer Protocol•100 kHz (1.8V, 2.5V, 2.7V) and 400 kHz (5V) Compatibility •Write Protect Pin for Hardware Data Protection•8-Byte Page (1K, 2K), 16-Byte Page (4K, 8K, 16K) Write Modes •Partial Page Writes Are Allowed •Self-Timed Write Cycle (10 ms max)•High ReliabilityEndurance: 1 Million Cycles Data Retention: 100 Years•Automotive Grade and Extended Temperature Devices Available •8-Pin and 14-Pin JEDEC SOIC and 8-Pin PDIP PackagesDescriptionThe AT24C01A/02/04/08/16 provides 1024/2048/4096/8192/16384 bits of serial elec-trically erasable and programmable read only memory (EEPROM) organized as 128/256/512/1024/2048 words of 8 bits each. The device is optimized for use in many industrial and commercial applications where low power and low voltage operation are essential. The AT24C01A/02/04/08/16 is available in space saving 8-pin PDIP, 8-pin and 14-pin SOIC packages and is accessed via a 2-wire serial interface. In addition,the entire family is available in 5.0V (4.5V to 5.5V), 2.7V (2.7V to 5.5V), 2.5V (2.5V to5.5V) and 1.8V (1.8V to 5.5V) versions.Pin Configurations8-Pin PDIP8-Pin SOIC14-Pin SOICAT24C01A/02/04/08/16Block Diagram*NOTICE: Stresses beyond those listed under “Absolute Maxi-mum Ratings” may cause permanent damage to the device.This is a stress rating only and functional operation of thedevice at these or any other conditions beyond those indi-cated in the operational sections of this specification is notimplied. Exposure to absolute maximum rating conditionsfor extended periods may affect device reliability. Absolute Maximum Ratings*Pin DescriptionSERIAL CLOCK (SCL): The SCL input is used to positiveedge clock data into each E2PROM device and negativeedge clock data out of each device.SERIAL DATA (SDA): The SDA pin is bidirectional for se-rial data transfer. This pin is open-drain driven and may bewire-ORed with any number of other open-drain or opencollector devices.DEVICE/PAGE ADDRESSES (A2, A1, A0): The A2, A1and A0 pins are device address inputs that are hard wiredfor the AT24C01A and the AT24C02. As many as eight1K/2K devices may be addressed on a single bus system(device addressing is discussed in detail under the DeviceAddressing section).The AT24C04 uses the A2 and A1 inputs for hard wireaddressing and a total of four 4K devices may be ad-dressed on a single bus system. The A0 pin is a no con-nect.The AT24C08 only uses the A2 input for hardwire ad-dressing and a total of two 8K devices may be addressedon a single bus system. The A0 and A1 pins are no con-nects.The AT24C16 does not use the device address pins whichlimits the number of devices on a single bus to one. TheA0, A1 and A2 pins are no connects.(continued)Applicable over recommended operating range from: T AI = -40°C to +85°C, V CC = +1.8V to +5.5V, T AC = 0°C to +70°C,Note:1.V IL min and V IH max are reference only and are not tested.DC CharacteristicsWRITE PROTECT (WP): The AT24C01A/02/04/16 has a Write Protect pin that provides hardware data protection.The Write Protect pin allows normal read/write operations when connected to ground (GND). When the Write Protectpin is connected to V CC , the write protection feature is en-abled and operates as shown in the following table.Pin Description (Continued)Memory OrganizationAT24C01A, 1K SERIAL E 2PROM: Internally organized with 128 pages of 1-byte each, the 1K requires a 7 bit data word address for random word addressing.AT24C02, 2K SERIAL E 2PROM: Internally organized with 256 pages of 1-byte each, the 2K requires an 8 bit data word address for random word addressing.AT24C04, 4K SERIAL E 2PROM: The 4K is internally or-ganized with 256 pages of 2-bytes each. Random word addressing requires a 9 bit data word address.AT24C08, 8K SERIAL E 2PROM:The 8K is internally or-ganized with 4 blocks of 256 pages of 4-bytes each. Ran-dom word addressing requires a 10 bit data word address.AT24C16, 16K SERIAL E 2PROM: The 16K is internally organized with 8 blocks of 256 pages of 8-bytes each.Random word addressing requires an 11 bit data word ad-dress.Pin Capacitance (1)Note:1. This parameter is characterized and is not 100% tested.AT24C01A/02/04/08/16Note:1. This parameter is characterized and is not 100% tested.Applicable over recommended operating range from T A = -40°C to +85°C, V CC = +1.8V to +5.5V, CL = 1 TTL Gate and100 pF (unless otherwise noted).AC CharacteristicsDevice OperationCLOCK and DATA TRANSITIONS: The SDA pin is nor-mally pulled high with an external device. Data on the SDA pin may change only during SCL low time periods (refer to Data Validity timing diagram). Data changes during SCL high periods will indicate a start or stop condition as de-fined below.START CONDITION: A high-to-low transition of SDA with SCL high is a start condition which must precede any other command (refer to Start and Stop Definition timing diagram).STOP CONDITION: A low-to-high transition of SDA with SCL high is a stop condition. After a read sequence, the stop command will place the E 2PROM in a standby power mode (refer to Start and Stop Definition timing diagram).ACKNOWLEDGE: All addresses and data words are se-rially transmitted to and from the E 2PROM in 8 bit words.The E 2PROM sends a zero to acknowledge that it has re-ceived each word. This happens during the ninth clock cy-cle.STANDBY MODE: The AT24C01A/02/04/08/16 features a low power standby mode which is enabled: (a) upon power-up and (b) after the receipt of the STOP bit and thecompletion of any internal operations.Bus Timing SCL: Serial ClockSDA: Serial Data I/OWrite Cycle Timing SCL: Serial Clock SDA: Serial Data I/ONote: 1.The write cycle time t WR is the time from a valid stop condition of a write sequence to the end of the internal clear/write cycle.AT24C01A/02/04/08/16Data ValidityStart and Stop DefinitionOutput AcknowledgeDevice AddressingThe 1K, 2K, 4K, 8K and 16K E2PROM devices all require an 8 bit device address word following a start condition to enable the chip for a read or write operation (refer to Fig-ure 1).The device address word consists of a mandatory one, zero sequence for the first four most significant bits as shown. This is common to all the E2PROM devices.The next 3 bits are the A2, A1 and A0 device address bits for the 1K/2K E2PROM. These 3 bits must compare to their corresponding hard-wired input pins.The 4K E2PROM only uses the A2 and A1 device address bits with the third bit being a memory page address bit. The two device address bits must compare to their corre-sponding hard-wired input pins. The A0 pin is no connect. The 8K E2PROM only uses the A2 device address bit with the next 2 bits being for memory page addressing. The A2 bit must compare to its corresponding hard-wired input pin. The A1 and A0 pins are no connect.The 16K does not use any device address bits but instead the 3 bits are used for memory page addressing. These page addressing bits on the 4K, 8K, and 16K devices should be considered the most significant bits of the data word address which follows. The A0, A1 and A2 pins are no connect.The eighth bit of the device address is the read/write op-eration select bit. A read operation is initiated if this bit is high and a write operation is initiated if this bit is low. Upon a compare of the device address, the E2PROM will output a zero. If a compare is not made, the chip will return to a standby state.Write OperationsBYTE WRITE: A write operation requires an 8 bit data word address following the device address word and ac-knowledgement. Upon receipt of this address, the E2PROM will again respond with a zero and then clock in the first 8 bit data word. Following receipt of the 8 bit data word, the E2PROM will output a zero and the addressing device, such as a microcontroller, must terminate the write sequence with a stop condition. At this time the E2PROM enters an internally-timed write cycle to the nonvolatile memory. All inputs are disabled during this write cycle and the E2PROM will not respond until the write is complete (refer to Figure 2).PAGE WRITE: The 1K/2K E2PROM is capable of an 8-byte page write, and the 4K, 8K and 16K devices are ca-pable of 16-byte page writes.A page write is initiated the same as a byte write, but the microcontroller does not send a stop condition after the first data word is clocked in. Instead, after the E2PROM acknowledges receipt of the first data word, the microcon-troller can transmit up to seven (1K/2K) or fifteen (4K, 8K, 16K) more data words. The E2PROM will respond with a zero after each data word received. The microcontroller must terminate the page write sequence with a stop con-dition (refer to Figure 3).The data word address lower three (1K/2K) or four (4K, 8K, 16K) bits are internally incremented following the re-ceipt of each data word. The higher data word address bits are not incremented, retaining the memory page row loca-tion. If more than eight (1K/2K) or sixteen (4K, 8K, 16K) data words are transmitted to the E2PROM, the data word address will “roll over” and previous data will be overwrit-ten.ACKNOWLEDGE POLLING: Once the internally-timed write cycle has started and the E2PROM inputs are dis-abled, acknowledge polling can be initiated. This involves sending a start condition followed by the device address word. The read/write bit is representative of the operation desired. Only if the internal write cycle has completed will the E2PROM respond with a zero allowing the read or write sequence to continue.Read OperationsRead operations are initiated the same way as write op-erations with the exception that the read/write select bit in the device address word is set to one. There are three read operations: current address read, random address read and sequential read.CURRENT ADDRESS READ: The internal data word ad-dress counter maintains the last address accessed during the last read or write operation, incremented by one. This address stays valid between operations as long as the chip power is maintained. The address “roll over” during read is from the last byte of the last memory page to the first byte of the first page. The address “roll over” during write is from the last byte of the current page to the first byte of the same page.Once the device address with the read/write select bit set to one is clocked in and acknowledged by the E2PROM, the current address data word is serially clocked out. The microcontroller does not respond with an input zero but does generate a following stop condition (refer to Figure 4).RANDOM READ: A random read requires a “dummy”byte write sequence to load in the data word address. Once the device address word and data word address are clocked in and acknowledged by the E2PROM, the micro-(continued) AT24C01A/02/04/08/16Figure 1.Device AddressFigure 2.Byte WriteFigure 3. Page Write(* = DON’T CARE bit for 1K)controller must generate another start condition. The mi-crocontroller now initiates a current address read by send-ing a device address with the read/write select bit high.The E 2PROM acknowledges the device address and seri-ally clocks out the data word. The microcontroller does not respond with a zero but does generate a following stop condition (refer to Figure 5).SEQUENTIAL READ: Sequential reads are initiated by either a current address read or a random address read.After the microcontroller receives a data word, it responds with an acknowledge. As long as the E 2PROM receives an acknowledge, it will continue to increment the data word address and serially clock out sequential data words.When the memory address limit is reached, the data word address will “roll over” and the sequential read will con-tinue. The sequential read operation is terminated when the microcontroller does not respond with a zero but does generate a following stop condition (refer to Figure 6).Read Operations(Continued)Figure 5. Random Read(*= DON’T CARE bit for 1K)Figure 4.Current Address ReadFigure 6. Sequential ReadAT24C01A/02/04/08/16Ordering InformationOrdering InformationOrdering Information。

at24c02中文资料_数据手册_参数

24c02中文官方资料手册pdf

w 址输入脚 A0 A1 A2 可悬空或连接到 Vss 如果只有一个 24WC01 被总线寻址 这三个地址输入

脚 A0 A1 A2 必须连接到 Vss

当使用 24WC04 时最多可连接 4 个器件 该器件仅使用 A1 A2 地址管脚 A0 管脚未用 可以连

符号

参数

最小

典型

最大 单位

测试条件

ICC 电源电流

3

mA

FSCL=100KHz

ISB ILI ILO VIL VIH VOL1 VOL2

备用电流(Vcc=5.0V) 输入漏电流 输出漏电流 输入低电压 输入高电压 输出低电压 输出低电压

1 Vcc 0.7

0

A

10

A

10

A

Vcc 0.3 V

Vcc+0.5 V

s

tHD: DAT

数据输入保持时间

0

0

ns

tSUl: DAT

数据输入建立时间

50

50

ns

tR

SDA 及 SCL 上升时间

1

0.3

s

tF

SDA 及 SCL 下降时间

300

300

ns

tSU: STO

停止信号建立时间

4

0.6

s

tDH

数据输出保持时间

100

100

ns4Biblioteka 海纳电子资讯网: www.fpga-arm.com

上电时序

符号

参数

最大

单位

tPUR

上电到读操作

1

第12章 AT24C02应用

3.数据传送格式

(1)字节传送与应答: 每一个字节必须保证是8位长度。数据传送时,先传送最高位(MSB), 每一个被传送的字节后面都必须跟随一位应答位(即一帧共有9位)。 应答信号由接收设备产生,在SCL信号为高电平期间,接收设备将SDA 拉为低电平,表示数据传输正确,产生应答。

由于某种原因从机不对主机寻址信号应答时(如从机正在进行实时性的处理工 作而无法接收总线上的数据),它必须将数据线置于高电平,而由主机产生一个终 止信号以结束总线的数据传送。

2)应答信号

I2C总线数据传送时,每成功地传送1B数据后,接收器都必须产 生一个应答信号。应答的器件在第9个时钟周期时将SDA线拉低, 表示其已收到1B数据。AT24CXX在接收到起始信号和从器件地 址之后响应一个应答信号,如果器件已选择了写操作,则在每接 收1B之后响应一个应答信号。

2. 写操作方式

内容 DA3

DA2

DA1

DA0

A2

A1

A0

R/W

DA3---DA0:4位是固定位,在器件出厂时就已给定,为 I2C总线器件固有的地址编 码, 如AT24CXX器件地址为1010,4位LED驱动器SAA1064为0111. A2~A0:3位是可编程位,决定了可接入总线该类器件的最大数目,这时仅能寻址8 个同样的器件,即可以有8个同样的器件接入到该I2C总线系统中。由器件的地址引脚 A2—A0在电路中接高电平或低电平决定。 R/W:数据传送方向位,为“0”时表示发送(主机向从机写数据),为“1”时表示主 机由从机读数据。

I2C硬件结构图

连接到I2C总线上的器件的输出级必须是集电极或漏极开路,以实现 “线与”功能,因此SDA及SCL均须通过上拉电阻接正电源。当总线空闲 时,两根线均为高电平。连到总线上的任一器件输出的低电平,都将使总 线的信号变低,即各器件的SDA及SCL都是线“与”关系。

AT24C02B

1.Features•Medium-voltage and Standard-voltage Operation –2.5 (V CC = 2.5V to 5.5V)•Automotive Temperature Range –40°C to 125°C•Internally Organized 128 x 8 (1K), 256 x 8 (2K), 512 x 8 (4K), 1024 x 8 (8K), or 2048 x 8(16K)•Two-wire Serial Interface•Schmitt Trigger, Filtered Inputs for Noise Suppression •Bidirectional Data Transfer Protocol •400 kHz (2.5V) Compatibility•Write Protect Pin for Hardware Data Protection•8-byte Page (1K, 2K) or 16-byte Page (4K, 8K, 16K) Write Modes •Partial Page Writes are Allowed •Self-timed Write Cycle (5 ms max)•High-reliability–Endurance: 1 Million Write Cycles –Data Retention: 100 Years•8-lead JEDEC SOIC and 8-lead TSSOP Packages2.DescriptionThe AT24C01B/02B/04B/08B/16B provides 1024/2048/4096/8192/16384 bits of serial electrically erasable and programmable read-only memory (EEPROM) organized as 128/256/512/1024/2048 words of 8 bits each. The device is optimized for use in many automotive applications where low-power and low-voltage operation are essential.The AT24C01B/02B/04B/08B/16B is available in space-saving 8-lead JEDEC SOIC and 8-lead TSSOP packages and is accessed via a two-wire serial interface. In addi-tion, the entire family is available in 2.5V (2.5V to 5.5V) versions.Table 2-1.Pin ConfigurationsPin Name Function A0 − A2Address Inputs SDA Serial Data SCL Serial Clock Input WPWrite ProtectTwo-wire Automotive Temperature Serial EEPROM1K (128 x 8)2K (256 x 8)4K (512 x 8)8K (1024 x 8)16K (2048 x 8)AT24C01B AT24C02B AT24C04B AT24C08B AT24C16B Preliminary8517B–SEEPR–3/0828517B–SEEPR–3/08AT24C01B/02B/04B/08B/16B [Preliminary]Figure 3-1.Block Diagram3.Absolute Maximum RatingsOperating Temperature...........................−55°C to +125°C *NOTICE:Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent dam-age to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Storage Temperature..............................−65°C to +150°C Voltage on Any Pinwith Respect to Ground..................................−1.0V to +7.0V Maximum Operating Voltage..........................................6.25VDC Output Current........................................................5.0 mA38517B–SEEPR–3/08AT24C01B/02B/04B/08B/16B [Preliminary]4.Pin DescriptionSERIAL CLOCK (SCL): The SCL input is used to positive edge clock data into each EEPROM device and negative edge clock data out of each device.SERIAL DATA (SDA): The SDA pin is bi-directional for serial data transfer. This pin is open-drain driven and may be wire-ORed with any number of other open-drain or open-collector devices.DEVICE/PAGE ADDRESSES (A2, A1, A0): The A2, A1 and A0 pins are device address inputs that are hard wired for the AT24C01B/02B/04B. As many as eight 1K/2K devices may be addressed on a single bus system (device addressing is discussed in detail under the Device Addressing section). The AT24C04B uses the A2 and A1 inputs for hardwire addressing and a total of four 4K devices may be addressed on a single bus system. The A0 pin is a no connect.The AT24C08B only uses the A2 input for hardwire addressing and a total of two 8K devices may be addressed on a single bus system. The A0 and A1 pins are no connect.The AT24C16B does not use the device address pins, which limits the number of devices on a single bus to one. The A0, A1 and A2 pins are no connect.WRITE PROTECT (WP): The AT24C01B/02B/04B/08B/16B has a Write Protect pin that pro-vides hardware data protection. The Write Protect pin allows normal read/write operations when connected to ground (GND). When the Write Protect pin is connected to V CC , the write protec-tion feature is enabled and operates as shown in the following table.5.Memory OrganizationAT24C01B, 1K SERIAL EEPROM: Internally organized with 16 pages of 8 bytes each, the 1K requires a 7-bit data word address for random word addressing.AT24C02B, 2K SERIAL EEPROM : Internally organized with 32 pages of 8 bytes each, the 2K requires an 8-bit data word address for random word addressing.AT24C04B, 4K SERIAL EEPROM : Internally organized with 32 pages of 16 bytes each, the 4K requires a 9-bit data word address for random word addressing.AT24C08B, 8K SERIAL EEPROM : Internally organized with 64 pages of 16 bytes each, the 8K requires a 10-bit data word address for random word addressing.AT24C16B, 16K SERIAL EEPROM : Initially organized with 128 pages of 16 bytes each, the 16K requires an 11-bit data word address for random word addressing.Table 4-1.Write ProtectWP Pin Status Part of the Array Protected AT24C01B/02B/04B/08B/16BAt V CC Full ArrayAt GNDNormal Read/Write Operations48517B–SEEPR–3/08AT24C01B/02B/04B/08B/16B [Preliminary]Note:1.This parameter is characterized and is not 100% tested.Note:1.V IL min and V IH max are reference only and are not tested.Table 5-1.Pin Capacitance (1)Applicable over recommended operating range from T A = 25°C, f = 400 KHz, V CC = +2.5VSymbol Test ConditionMax Units Conditions C I/O Input/Output Capacitance (SDA)8pF V I/O = 0V C IN Input Capacitance (A 0, A 1, A 2, SCL)6pFV IN = 0VTable 5-2.DC CharacteristicsApplicable over recommended operating range from: T A = −40°C to +125°C, V CC = +2.5V to +5.5V (unless otherwise noted)Symbol Parameter Test ConditionMin TypMax Units V CC1Supply Voltage2.55.5V I CC Supply Current V CC = 5.0V Read at 100 kHz 0.4 1.0mA I CC Supply Current V CC = 5.0V Write at 100 kHz 2.0 3.0mA I SB1Standby Current V CC = 2.5V V IN = V CC or V SS 1.6 4.0µA I SB2Standby Current V CC = 5.0V V IN = V CC or V SS 8.018.0µA I LI Input Leakage Current V IN = V CC or V SS 0.10 3.0µA I LO Output Leakage Current V OUT = V CC or V SS0.05 3.0µA V IL Input Low Level (1)−0.6V CC x 0.3V V IH Input High Level (1)V CC x 0.7V CC + 0.5V V OL2Output Low Level V CC = 3.0V I OL = 2.1 mA 0.4V V OL1Output Low Level V CC = 1.8VI OL = 0.15 mA 0.2V58517B–SEEPR–3/08AT24C01B/02B/04B/08B/16B [Preliminary]Notes:1.This parameter is characterized and is not 100% tested (T A = 25°C).2.This parameter is characterized only.Table 5-3.AC CharacteristicsApplicable over recommended operating range from T A = −40°C to +125°C, V CC = +2.5V to +5.5V, CL = 1 TTL Gate and 100 pF (unless otherwise noted)SymbolParameterMinMax Units f SCL Clock Frequency, SCL 400kHz t LOW Clock Pulse Width Low 1.2µs t HIGH Clock Pulse Width High 0.6µs t I Noise Suppression Time (1)50ns t AA Clock Low to Data Out Valid 0.10.9µs t BUF Time the bus must be free before a new transmission can start (2) 1.2µs t HD.STA Start Hold Time 0.6µs t SU.STA Start Set-up Time 0.6µs t HD.DAT Data In Hold Time 0µs t SU.DAT Data In Set-up Time 100ns t R Inputs Rise Time (2)300ns t F Inputs Fall Time (2)300ns t SU.STO Stop Set-up Time 0.6µs t DH Data Out Hold Time 50ns t WRWrite Cycle Time 5ms Endurance (2) 5.0V, 25°C, Page Mode1MWrite Cycles68517B–SEEPR–3/08AT24C01B/02B/04B/08B/16B [Preliminary]6.Device OperationCLOCK and DATA TRANSITIONS: The SDA pin is normally pulled high with an external device. Data on the SDA pin may change only during SCL low time periods (see Figure 8-2 on page 8). Data changes during SCL high periods will indicate a start or stop condition as defined below.START CONDITION: A high-to-low transition of SDA with SCL high is a start condition which must precede any other command (see Figure 8-3 on page 8).STOP CONDITION: A low-to-high transition of SDA with SCL high is a stop condition. After a read sequence, the stop command will place the EEPROM in a standby power mode (see Fig-ure 8-3 on page 8).ACKNOWLEDGE: All addresses and data words are serially transmitted to and from the EEPROM in 8-bit words. The EEPROM sends a “0” to acknowledge that it has received each word. This happens during the ninth clock cycle.STANDBY MODE: The AT24C01B/02B/04B/08B/16B features a low-power standby mode which is enabled: (a) upon power-up and (b) after the receipt of the STOP bit and the completion of any internal operations.2-WIRE SOFTWARE RESET: After an interruption in protocol, power loss or system reset, any 2-wire part can be protocol reset by following these steps: (a) Create a start bit condition, (b)clock 9 cycles, (c) create another start but followed by stop bit condition as shown below. The device is ready for next communication after above steps have been completed.Figure 6-1.Software Reset78517B–SEEPR–3/08AT24C01B/02B/04B/08B/16B [Preliminary]7.Bus TimingFigure 7-1.SCL: Serial Clock, SDA: Serial Data I/O8.Write Cycle TimingFigure 8-1.SCL: Serial Clock, SDA: Serial Data I/ONote:1.The write cycle time t WRis the time from a valid stop condition of a write sequence to the end of the internal clear/write cycle.88517B–SEEPR–3/08AT24C01B/02B/04B/08B/16B [Preliminary]Figure 8-2.Data ValidityFigure 8-3.Start and Stop DefinitionFigure 8-4.Output Acknowledge98517B–SEEPR–3/08AT24C01B/02B/04B/08B/16B [Preliminary]9.Device AddressingThe 1K/2K/4K/8K/16K EEPROM device requires an 8-bit device address word following a start condition to enable the chip for a read or write operation (see Figure 11-1 on page 10).The device address word consists of a mandatory “1”, “0” sequence for the first four most signif-icant bits as shown. This is common to all the Serial EEPROM devices.The next 3 bits are the A2, A1 and A0 device address bits for the 1K/2K EEPROM. These 3 bits must compare to their corresponding hardwired input pins.The 4K EEPROM only uses the A2 and A1 device address bits with the A0 bit being a memory address bit (P0) (see Figure 11-1 on page 10). The two device address bits must compare to their corresponding hardwired input pins. The A0 pin is no connect.The 8K EEPROM only uses the A2 device address bit with the next two bits (P9, P0) being for memory page addressing (See Figure 11-1 on page 10). The A2 bit must compare to its corre-sponding hardwired input pin. The A1 and A0 pins are no connect.The 16K does not use any device address bits but instead the three bits (P2, P1, P0) are used for memory page addressing. These page addressing bits on the 4K, 8K, and 16K devices shall be considered the most significant bits of the data word address which follows. The A0, A1, and A2 pins are no connect (See Figure 11-1 on page 10).The eighth bit of the device address is the read/write operation select bit. A read operation is ini-tiated if this bit is high and a write operation is initiated if this bit is low.Upon a compare of the device address, the EEPROM will output a “0”. If a compare is not made,the chip will return to a standby state.10.Write OperationsBYTE WRITE: A write operation requires an 8-bit data word address following the device address word and acknowledgment. Upon receipt of this address, the EEPROM will again respond with a “0” and then clock in the first 8-bit data word. Following receipt of the 8-bit data word, the EEPROM will output a “0” and the addressing device, such as a microcontroller, must terminate the write sequence with a stop condition. At this time the EEPROM enters an internally timed write cycle, t WR , to the nonvolatile memory. All inputs are disabled during this write cycle and the EEPROM will not respond until the write is complete (see Figure 11-2 on page 11).PAGE WRITE: The 1K/2K EEPROM is capable of an 8-byte page write. The 4K/8K/16K devices are capable of 16-byte page writes.A page write is initiated the same as a byte write, but the microcontroller does not send a stop condition after the first data word is clocked in. Instead, after the EEPROM acknowledges receipt of the first data word, the microcontroller can transmit up to seven (1K/2K) or fifteen (4K/8K/16K) more data words. The EEPROM will respond with a “0” after each data word received.The microcontroller must terminate the page write sequence with a stop condition (see Figure 11-3 on page 11).The data word address lower three (1K/2K) or four (4K/8K/16K) bits are internally incremented following the receipt of each data word. The higher data word address bits are not incremented,retaining the memory page row location. When the word address, internally generated, reaches the page boundary, the following byte is placed at the beginning of the same page. If more than eight (1K/2K) or sixteen (4K/8K/16K) data words are transmitted to the EEPROM, the data word address will “roll over” and previous data will be overwritten.108517B–SEEPR–3/08AT24C01B/02B/04B/08B/16B [Preliminary]ACKNOWLEDGE POLLING: Once the internally timed write cycle has started and the EEPROM inputs are disabled, acknowledge polling can be initiated. This involves sending a start condition followed by the device address word. The read/write bit is representative of the operation desired. Only if the internal write cycle has completed will the EEPROM respond with a “0”, allowing the read or write sequence to continue.11.Read OperationsRead operations are initiated the same way as write operations with the exception that the read/write select bit in the device address word is set to “1”. There are three read operations:current address read, random address read and sequential read.CURRENT ADDRESS READ: The internal data word address counter maintains the last address accessed during the last read or write operation, incremented by one. This address stays valid between operations as long as the chip power is maintained. The address “roll over”during read is from the last byte of the last memory page to the first byte of the first page. The address “roll over” during write is from the last byte of the current page to the first byte of the same page.Once the device address with the read/write select bit set to “1” is clocked in and acknowledged by the EEPROM, the current address data word is serially clocked out. The microcontroller does not respond with an input “0” but does generate a following stop condition (see Figure 11-4 on page 11).RANDOM READ: A random read requires a “dummy” byte write sequence to load in the data word address. Once the device address word and data word address are clocked in and acknowledged by the EEPROM, the microcontroller must generate another start condition. The microcontroller now initiates a current address read by sending a device address with the read/write select bit high. The EEPROM acknowledges the device address and serially clocks out the data word. The microcontroller does not respond with a “0” but does generate a following stop condition (see Figure 11-5 on page 11).SEQUENTIAL READ: Sequential reads are initiated by either a current address read or a ran-dom address read. After the microcontroller receives a data word, it responds with an acknowledge. As long as the EEPROM receives an acknowledge, it will continue to increment the data word address and serially clock out sequential data words. When the memory address limit is reached, the data word address will “roll over” and the sequential read will continue. The sequential read operation is terminated when the microcontroller does not respond with a “0” but does generate a following stop condition (see Figure 11-6 on page 12).Figure 11-1.Device Address118517B–SEEPR–3/08AT24C01B/02B/04B/08B/16B [Preliminary]Figure 11-2.Byte Write(* = DON’T CARE bit for 1K)Figure 11-3.Page Write(* = DON’T CARE bit for 1K)Figure 11-4.Current Address ReadFigure 11-5.Random Read128517B–SEEPR–3/08AT24C01B/02B/04B/08B/16B [Preliminary]Figure 11-6.Sequential Read138517B–SEEPR–3/08AT24C01B/02B/04B/08B/16B [Preliminary]Notes:1.“-B” denotes bulk.2.“-T” denotes tape and reel. SOIC = 4K per reel. TSSOP = 5K per reel.12.AT24C01B Ordering InformationOrdering Code Package Operation RangeAT24C01BN-SP25-B (1) AT24C01BN-SP25-T (2) AT24C01B-TP25-B (1) AT24C01B-TP25-T (2) 8S18S18A28A2Lead-free/Halogen-free/NiPdAu Lead Finish/Automotive Temperature(−40°C to 125°C)Package Type8S18-lead, 0.150” Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)8A28-lead, 4.4 mm Body, Plastic Thin Shrink Small Outline Package (TSSOP)Options−2.5Low-voltage (2.5V to 5.5V)148517B–SEEPR–3/08AT24C01B/02B/04B/08B/16B [Preliminary]13.AT24C02B Ordering InformationNotes:1.“-B” denotes bulk.2.“-T” denotes tape and reel. SOIC = 4K per reel. TSSOP = 5K per reel.Ordering Code Package Operation RangeAT24C02BN-SP25-B (1) AT24C02BN-SP25-T (2) AT24C02B-TP25-B (1) AT24C02B-TP25-T (2) 8S18S18A28A2Lead-free/Halogen-free/NiPdAu Lead Finish/Automotive Temperature(−40°C to 125°C)Package Type8S18-lead, 0.150” Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)8A28-lead, 4.4 mm Body, Plastic Thin Shrink Small Outline Package (TSSOP)Options−2.5Low-voltage (2.5V to 5.5V)158517B–SEEPR–3/08AT24C01B/02B/04B/08B/16B [Preliminary]Notes:1.“-B” denotes bulk.2.“-T” denotes tape and reel. SOIC = 4K per reel. TSSOP = 5K per reel.14.AT24C04B Ordering InformationOrdering Code Package Operation RangeAT24C04BN-SP25-B (1) AT24C04BN-SP25-T (2) AT24C04B-TP25-B (1) AT24C04B-TP25-T (2) 8S18S18A28A2Lead-free/Halogen-free/NiPdAu Lead Finish/Automotive Temperature(−40°C to 125°C)Package Type8S18-lead, 0.150” Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)8A28-lead, 4.4 mm Body, Plastic Thin Shrink Small Outline Package (TSSOP)Options−2.5Low-voltage (2.5V to 5.5V)168517B–SEEPR–3/08AT24C01B/02B/04B/08B/16B [Preliminary]Notes:1.“-B” denotes bulk.2.“-T” denotes tape and reel. SOIC = 4K per reel. TSSOP = 5K per reel.15.AT24C08B Ordering InformationOrdering Code Package Operation RangeAT24C08BN-SP25-B (1) AT24C08BN-SP25-T (2) AT24C08B-TP25-B (1) AT24C08B-TP25-T (2) 8S18S18A28A2Lead-free/Halogen-free/NiPdAu Lead Finish/Automotive Temperature(−40°C to 125°C)Package Type8S18-lead, 0.150” Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)8A28-lead, 4.4 mm Body, Plastic Thin Shrink Small Outline Package (TSSOP)Options−2.5Low-voltage (2.5V to 5.5V)178517B–SEEPR–3/08AT24C01B/02B/04B/08B/16B [Preliminary]Notes:1.“-B” denotes bulk.2.“-T” denotes tape and reel. SOIC = 4K per reel. TSSOP = 5K per reel.16.AT24C16B Ordering InformationOrdering Code Package Operation RangeAT24C16BN-SP25-B (1) AT24C16BN-SP25-T (2) AT24C16B-TP25-B (1) AT24C16B-TP25-T (2) 8S18S18A28A2Lead-free/Halogen-free/NiPdAu Lead Finish/Automotive Temperature(−40°C to 125°C)Package Type8S18-lead, 0.150” Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)8A28-lead, 4.4 mm Body, Plastic Thin Shrink Small Outline Package (TSSOP)Options−2.5Low-voltage (2.5V to 5.5V)188517B–SEEPR–3/08AT24C01B/02B/04B/08B/16B [Preliminary]17.Packaging Information17.18A2 – TSSOP198517B–SEEPR–3/08AT24C01B/02B/04B/08B/16B [Preliminary]17.28S1 – JEDEC SOIC208517B–SEEPR–3/08AT24C01B/02B/04B/08B/16B [Preliminary]18.Revision HistoryDoc. Rev.Date Comments8517B 3/2008Added data for the 8K and 16K parts 8517A1/2008Initial document release.8517B–SEEPR–3/08HeadquartersInternationalAtmel Corporation 2325 Orchard Parkway San Jose, CA 95131USATel: 1(408) 441-0311Fax: 1(408) 487-2600Atmel Asia Room 1219Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong KongTel: (852) 2721-9778Fax: (852) 2722-1369Atmel Europe Le Krebs8, Rue Jean-Pierre Timbaud BP 30978054 Saint-Quentin-en-Yvelines Cedex FranceTel: (33) 1-30-60-70-00 Fax: (33) 1-30-60-71-11Atmel Japan9F, Tonetsu Shinkawa Bldg.1-24-8 ShinkawaChuo-ku, Tokyo 104-0033JapanTel: (81) 3-3523-3551Fax: (81) 3-3523-7581Product ContactWeb SiteTechnical Support s_eeprom@Sales Contact/contactsLiterature Requests /literatureDisclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise,to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL’S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL’S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING , BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel’s products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.© 2008 Atmel Corporation. All rights reserved. Atmel ®, logo and combinations thereof, and others, are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.。

EEPROM---AT24Cxx应用介绍

EEPROM---AT24Cxx应⽤介绍结论:1、读写AT24CXX芯⽚,根据容量有多种⽅式:⼀、容量为AT24C01~AT24C16,⾸先发送设备地址(8位地址),再发送数据地址(8位地址),再发送或者接受数据。

⼆、AT24C32/AT24C64~AT24C512,⾸先发送设备地址(8位地址),再发送⾼位数据地址,再发送地位数据地址,再发送或者接受数据。

三、容量AT24C1024的芯⽚,是把容量⼀和容量⼆的⽅法结合,设备地址中要⽤⼀位作为数据地址位,存储地址长度是17位。

2、它的设备地址根据容量不同有区别: 1)、AT24C01~AT24C16:这⼀类⼜分为两类,分别为AT24C01/AT24C02和AT24C04~AT24C16;他们的设备地址为⾼7位,低1位⽤来作为读写标⽰位,1为读,0为写。

*1*、AT24C01/AT24C02。

AT24C01/AT24C02的A0、A1、A2引脚作为7位设备地址的低三位,⾼4为固定为1010B,低三位A0、A1、A2确定了AT24CXX的设备地址,所以⼀根I2C线上最⼤可以接8个AT24CXX,地址为1010000B~1010111B。

*2*、AT24C04~AT24C16的 A0、A1、A2只使⽤⼀部分,不⽤的悬空或者接地(数据⼿册中写的是悬空不接)。

举例:AT24C04只⽤A2、A1引脚作为设备地址,另外⼀位A0不⽤悬空,发送地址中对应的这位(A0)⽤来写⼊页寻址的页⾯号,⼀根I2C线上最⼤可以接4个,地址为101000xB~101011xB 2)、AT24C32/AT24C64:和AT24C01/AT24C02⼀样,区别是,发送数据地址变成16位。

注意事项:对AT24C32来说,WP置⾼,则只有四分之⼀受保护,即0x0C00-0x0FFF。

也就是说保护区为1KBytes。

对于低地址的四分之三,则不保护。

所以,如果数据较多时,可以有选择地存储。

24C02资料 (2)

一、EPROM与EEPROM:EPROM(Erasable Programmable Read Only Memory),中文含意为“可擦除可编程只读存储器”。

它是一种可重写的存储器芯片,并且其内容在掉电的时候也不会丢失;换句话说,它是非易失性的。

它通过EPROM编程器进行编程,EPROM编程器能够提供比正常工作电压更高的电压对EPROM编程。

一旦经过编程,EPROM只有在强紫外线的照射下才能够进行擦除。

为了进行擦除,EPROM的陶瓷封装上具有一个小的石英窗口,这个石英窗口一般情况下使用不透明的粘带覆盖,当擦除时将这个粘带揭掉,然后放置在强紫外线下大约20分钟。

主要IC有27XX系列和27CXX系列。

EEPROM(electrically erasable, programmable, read-only )是一种电可擦除可编程只读存储器,并且其内容在掉电的时候也不会丢失。

在平常情况下,EEPROM与EPROM一样是只读的,需要写入时,在指定的引脚加上一个高电压即可写入或擦除,而且其擦除的速度极快!通常EEPROM芯片又分为串行EEPROM和并行EEPROM两种,串行EEPROM在读写时数据的输入/输出是通过2线、3线、4线或SPI 总线等接口方式进行的,而并行EEPROM的数据输入/输出则是通过并行总线进行的。

主要IC有28XX系列。

二、24c02芯片硬件介绍:1、引脚说明:A0,A1,A2——地址输入引脚,走位硬件寻址的依据,同种芯片可同时连接8片(2^3);Vcc,Gnd——电源,接地引脚,1.8-5.5vWp——写保护,当Wp接地时,允许对器件的正常读写操作;当Wp接高电平时,写保护,只能进行读操作。

SDA——串行地址/数据输入/输出端口,双向传输,漏极开路,需外接上拉电阻到Vcc(典型阻值为10k)。

SCL——串行时钟输入,高低电平不同状态与SDA配合,执行不同的命令。

2、存储结构:24c02的容量是2k,256字节。

AVR事无巨细系列十二,IIC总线与EEPROM芯片24C02

事无巨细,IIC 协议与EEPROM 24C02在前面的一系列文章中,我们从最简单的开发环境开始到上一节的片外DAC 的使用为止,算是AVR 单片机中比较简单但是绝对是比较全面的内容了。

如果你能够独立掌握了前面的这些内容,我们现在可以开始进入CEPARK AVR 开发板上最后的三个最难的内容:存储芯片AT24C02的IIC 总线协议,时钟芯片DS1302的SPI 总线协议,还有温度传感器DS18B20的单总线协议。

今天我们来讲存储芯片AT24C02的IIC 总线协议。

(也称I 2C 总线协议)IIC 的概念:IIC ,英文全称为Inter -Integrated Circuit ,即内置集成电路。

所以IIC 总线协议,就是指内置集成电路总线协议。

我理解为集成电路直接用以数据传输的线路。

IIC 的发展:IIC 总线产生于在80年代,最初为音频和视频设备开发,如今主要在服务器管理中使用,其中包括单个组件状态的通信。

例如管理员可对各个组件进行查询,以管理系统的配置或掌握组件的功能状态,如电源和系统风扇。

可随时监控内存、硬盘、网络、系统温度等多个参数,增加了系统的安全性,方便了管理。

IIC 的特点:IIC 总线最主要的优点是其简单性和有效性。

由于接口直接在组件之上而且只有两根信号线,因此I2C 总线占用的空间非常小,减少了电路板的空间和芯片管脚的数量,降低了互联成本。

总线的长度可高达25英尺,并且能够以10Kbps 的最大传输速率支持40个组件。

I2C 总线的另一个优点是,它支持多主控(multimastering), 其中任何能够进行发送和接收的设备都可以成为主总线。

一个主控能够控制信号的传输和时钟频率。

当然,在任何时间点上只能有一个主控。

IIC 总线操作方法:IIC 总线在传送数据过程中共有三种类型信号, 它们分别是:开始信号、结束信号和应答信号。

笔者分别配合时序图来说明:1、开始信号与结束信号: B b s .C e p a r k .c o m开始信号:SCL 为高电平时,SDA 由高电平向低电平跳变,开始传送数据。

24C02B中文资料

FEATURES•Single supply with 5.0V operation •Low power CMOS technology - 1 mA active current typical-10 µ A standby current typical at 5.0V - 5 µ A standby current typical at 5.0V•Organized as a single block of 128 bytes (128 x 8) or 256 bytes (256 x 8)•2-wire serial interface bus, I 2 C compatible •100 kHz compatibility•Self-timed write cycle (including auto-erase)•Page-write buffer for up to 8 bytes• 2 ms typical write cycle time for page-write •Hardware write protect for entire memory •Can be operated as a serial ROM •ESD protection > 3,000V•1,000,000 ERASE/WRITE cycles guaranteed Data retention > 200 years •8 pin DIP or SOIC package•Available for extended temperature ranges DESCRIPTIONThe Microchip T echnology Inc. 24C01B and 24C02B are 1K bit and 2K bit Electrically Erasable PROMs. The devices are organized as a single block of 128 x 8 bit or 256 x 8 bit memory with a 2-wire serial interface. The 24C01B and 24C02B also have page-write capability for up to 8 bytes of data. The 24C01B and 24C02B are available in the standard 8-pin DIP and an 8-pin surface mount SOIC package.These devices are for extended temperature applications only. It is recommended that all other applications use Microchip’s 24LC01B/02B.-Automotive (E):-40˚C to +125˚C2元器件交易网24C01B/02B1.0ELECTRICAL CHARACTERISTICS1.1Maximum Ratings*V CC ...................................................................................7.0V All inputs and outputs w.r.t. V SS ................-0.6V to V CC +1.0V Storage temperature.....................................-65˚C to +150˚C Ambient temp. with power applied.................-65˚C to +125˚C Soldering temperature of leads (10 seconds).............+300˚C ESD protection on all pins............................................. ≥ 4 kV*Notice: Stresses above those listed under “Maximum ratings”may cause permanent damage to the device. This is a stress rat-ing only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.TABLE 1-1:PIN FUNCTION TABLEName FunctionV SS SDA SCL WP V CC NCGroundSerial Address/Data I/O Serial ClockWrite Protect Input +5.0V Power Supply No Internal ConnectionTABLE 1-1:DC CHARACTERISTICSAll parameters apply across the speci-fied operating ranges unless otherwise noted.VCC = +4.5V to 5.5VAutomotive (E):Tamb = -40 ° C to 125 ° C ParameterSymbol Min.Max.Units ConditionsWP , SCL and SDA pins:High level input voltageV IH .7 V CCV Low level input voltageV IL .3 V CC V Hysteresis of Schmidt trigger inputs V HYS .05 V CC —V (Note)Low level output voltage V OL .40V I OL = 3.0 mA, V CC = 2.5V Input leakage current ILI -1010 µ A V IN = .1V to 5.5V Output leakage currentILO -1010 µ mA V OUT = .1V to 5.5VPin capacitance (all inputs/outputs)C IN , C OUT —10pF V CC = 5.0V (Note 1)Tamb = 25˚C, F CLK = 1 MHz Operating current I CC Write —3mA V CC = 5.5V , SCL = 100 kHzI CC Read —1mA Standby current ICCS—30 µ A V CC = 3.0V , SDA = SCL = VCC 100 µ AV CC = 5.5V , SDA = SCL = VCC Note:This parameter is periodically sampled and not 100% tested.元器件交易网24C01B/02BTABLE 1-2:AC CHARACTERISTICSAll Parameters apply across thespecified operating ranges unless otherwise notedVcc = 4.5V to 5.5V Automotive (E):Tamb = -40˚C to +125˚C,ParameterSymbol Min.Max.Units RemarksClock frequency F CLK —100kHz Clock high time T HIGH 4000—ns Clock low time T LOW 4700—ns SDA and SCL rise time T R —1000ns (Note 1)SDA and SCL fall time T F —300ns (Note 1)ST ART condition hold time T HD : STA 4000—ns After this period the first clock pulse is generatedST ART condition setup time T SU : STA 4700—ns Only relevant for repeated ST ART condition Data input hold time T HD : DAT 0—ns (Note 2)Data input setup time T SU : DAT 250—ns STOP condition setup time T SU : STO 4000—ns Output valid from clock T AA —3500ns (Note 2)Bus free timeT BUF 4700—ns Time the bus must be free before a new transmission can start Output fall time from V IH minimum to V IL maximum T OF —250ns (Note 1), CB ≤ 100 pF Input filter spike suppression (SDA and SCL pins)T SP —50ns (Note 3)Write cycle time T WR —10ms Byte or Page modeEndurance—1M—cycles25 ° C, Vcc = 5.0V , Block Mode (Note 4)Note 1:Not 100% tested. CB = total capacitance of one bus line in pF .2:As a transmitter, the device must provide an internal minimum delay time to bridge the undefined region(minimum 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.3:The combined T SP and VHYSspecifications are due to Schmitt trigger inputs which provide improved noisespike suppression. This eliminates the need for a TI specification for standard operation.4:This parameter is not tested but guaranteed by characterization. For endurance estimates in a specificapplication, please consult the T otal Endurance Model which can be obtained on our BBS or website.元器件交易网24C01B/02B2.0FUNCTIONAL DESCRIPTION The 24C01B/02B supports a bi-directional two wire bus and data transmission protocol. A device that sends data onto the bus is defined as transmitter, and a device receiving data as receiver. The bus has to be controlled by a master device which generates the serial clock (SCL), controls the bus access, and gener-ates the ST ART and STOP conditions, while the 24C01B/02B works as slave. Both master and slave can operate as transmitter or receiver but the master device determines which mode is activated.3.0BUS CHARACTERISTICSThe following bus protocol has been defined:•Data transfer may be initiated only when the busis not busy.•During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH will be interpreted as a ST ART or STOP condition. Accordingly, the following bus conditions have been defined (Figure 3-1).3.1Bus Not Busy (A)Both data and clock lines remain HIGH.3.2Start Data Transfer (B)A HIGH to LOW transition of the SDA line while the clock (SCL) is HIGH determines a ST ART condition. All commands must be preceded by a ST ART condi-tion.3.3Stop Data Transfer (C)A LOW to HIGH transition of the SDA line while the clock (SCL) is HIGH determines a STOP condition. All operations must be ended with a STOP condition.3.4Data Valid (D)The state of the data line represents valid data when, after a ST ART condition, the data line is stable for the duration of the HIGH period of the clock signal.The data on the line must be changed during the LOW period of the clock signal. There is one clock pulse per bit of data.Each data transfer is initiated with a ST ART condition and terminated with a STOP condition. The number of the data bytes transferred between the ST ART and STOP conditions is determined by the master device and is theoretically unlimited, although only the last six-teen will be stored when doing a write operation. When an overwrite does occur it will replace data in a first in first out fashion.3.5AcknowledgeEach receiving device, when addressed, is obliged to generate an acknowledge after the reception of each byte. The master device must generate an extra clock pulse which is associated with this acknowledge bit. The device that acknowledges has to pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse. Of course, setup and hold times must be taken into account. A master must signal an end of data to the slave by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave must leave the data line HIGH to enable the master to generate the STOP condition.元器件交易网24C01B/02B3.6Device AddressAfter generating a ST ART condition, the bus master transmits the slave address consisting of a 4-bit device code (1010) for the 24C01B/02B, followed by three don't care bits.The eighth bit of slave address determines if the master device wants to read or write to the 24C01B/02B (Figure 3-2).The 24C01B/02B monitors the bus for its correspond-ing slave address all the time. It generates an acknowl-edge bit if the slave address was true and it is not in a programming mode.4.0WRITE OPERATION4.1Byte WriteFollowing the start signal from the master, the device code (4 bits), the don't care bits (3 bits), and the R/W bit which is a logic low is placed onto the bus by the master transmitter. This indicates to the addressed slave receiver that a byte with a word address will follow after it has generated an acknowledge bit during the ninth clock cycle. Therefore the next byte transmitted by the master is the word address and will be written into the address pointer of the 24C01B/02B. After receiving another acknowledge signal from the 24C01B/02B the master device will transmit the data word to be written into the addressed memory location.The 24C01B/02B acknowledges again and the master generates a stop condition. This initiates the internal write cycle, and during this time the 24C01B/02B will not generate acknowledge signals (Figure 4-1).4.2Page WriteThe write control byte, word address and the first data byte are transmitted to the 24C01B/02B in the same way as in a byte write. But instead of generating a stop condition the master transmits up to eight data bytes to the 24C01B/02B which are temporarily stored in the on-chip page buffer and will be written into the memoryafter the master has transmitted a stop condition. After the receipt of each word, the three lower order address pointer bits are internally incremented by one. The higher order five bits of the word address remains con-stant. If the master should transmit more than eight words prior to generating the stop condition, the address counter will roll over and the previously received data will be overwritten. As with the byte write operation, once the stop condition is received an inter-nal write cycle will begin (Figure 4-2).元器件交易网24C01B/02B5.0ACKNOWLEDGE POLLINGSince the device will not acknowledge during a write cycle, this can be used to determine when the cycle is complete (this feature can be used to maximize bus throughput). Once the stop condition for a write com-mand has been issued from the master, the device ini-tiates the internally timed write cycle. ACK polling can be initiated immediately. This involves the master send-ing a start condition followed by the control byte for a write command (R/W = 0). If the device is still busy with the write cycle, then no ACK will be returned. If the cycle is complete, then the device will return the ACK and the master can then proceed with the next read or write command. See Figure 5-1 for flow diagram. FIGURE 5-1:ACKNOWLEDGE POLLING6.0WRITE PROTECTIONThe 24C01B/02B can be used as a serial ROM when the WP pin is connected to V CC. Programming will be inhibited and the entire memory will be write-protected.7.0READ OPERATIONRead operations are initiated in the same way as write operations with the exception that the R/W bit of the slave address is set to one. There are three basic types of read operations: current address read, random read, and sequential read.7.1Current Address ReadThe 24C01B/02B contains an address counter that maintains the address of the last word accessed, inter-nally incremented by one. Therefore, if the previous access (either a read or write operation) was to address n, the next current address read operation would access data from address n + 1. Upon receipt of the slave address with R/W bit set to one, the 24C01B/ 02B issues an acknowledge and transmits the eight bit data word. The master will not acknowledge the trans-fer but does generate a stop condition and the 24C01B/ 02B discontinues transmission (Figure 7-1).7.2Random ReadRandom read operations allow the master to access any memory location in a random manner. T o perform this type of read operation, first the word address must be set. This is done by sending the word address to the 24C01B/02B as part of a write operation. After the word address is sent, the master generates a start condition following the acknowledge. This terminates the write operation, but not before the internal address pointer is set. Then the master issues the control byte again but with the R/W bit set to a one. The 24C01B/02B will then issue an acknowledge and transmits the eight bit data word. The master will not acknowledge the transfer but does generate a stop condition and the 24C01B/02B discontinues transmission (Figure 7-2).7.3Sequential ReadSequential reads are initiated in the same way as a ran-dom read except that after the 24C01B/02B transmits the first data byte, the master issues an acknowledge as opposed to a stop condition in a random read. This directs the 24C01B/02B to transmit the next sequen-tially addressed 8-bit word (Figure 7-3).To provide sequential reads the 24C01B/02B contains an internal address pointer which is incremented by one at the completion of each operation. This address pointer allows the entire memory contents to be serially read during one operation.7.4Noise ProtectionThe 24C01B/02B employs a V CC threshold detector cir-cuit which disables the internal erase/write logic if the V CC is below 1.5 volts at nominal conditions.The SCL and SDA inputs have Schmitt trigger and filter circuits which suppress noise spikes to assure proper device operation even on a noisy bus.元器件交易网24C01B/02B8.0PIN DESCRIPTIONS8.1Serial DataThis is a bi-directional pin used to transfer addresses and data into and data out of the device. It is an open drain terminal, therefore the SDA bus requires a pull-up resistor to V CC (typically 10 KΩ for 100 kHz).For normal data transfer SDA is allowed to change only during SCL low. Changes during SCL high are reserved for indicating the ST ART and STOP condi-tions.8.2SCL Serial ClockThis input is used to synchronize the data transfer from and to the device.8.3WPThis pin must be connected to either V SS or V CC.If tied to V SS, normal memory operation is enabled (read/write the entire memory).If tied to V CC, WRITE operations are inhibited. The entire memory will be write-protected. Read operations are not affected.This feature allows the user to use the 24C01B/02B as a serial ROM when WP is enabled (tied to V CC).元器件交易网元器件交易网24C01B/02B Array NOTES:元器件交易网24C01B/02B Array NOTES:元器件交易网24C01B/02B Array NOTES:24C01B/02BT o order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.Data SheetsProducts supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recom-mended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:1.Y our local Microchip sales office.2.The Microchip Corporate Literature Center U.S. FAX: (602) 786-7277.3.The Microchip’s Bulletin Board, via your local CompuServe number (CompuServe membership NOT required).Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.元器件交易网元器件交易网MAll rights reserved. © 1997, Microchip T echnology Incorporated, USA. 12/97 Printed on recycled paper.。

AT24c02最全的中文资料

CA T24C 161/162(16K),CAT24C081 /082(8K) CAT24C041/042(4K),CAT24C021/022(2K)I2C串行CMOS E2PROM,精确的复位控制器和看门狗定时器控制电路特性•数据线上的看门狗定时器(仅对CA T24Cxxl)籲可编程复位门槛电平籲高数据传送速率为400KHz和I2C总线兼容• 2.7V至6V的工作电压•低功耗CMOS工艺籲16字节页写缓冲区籲片内防误擦除写保护籲高低电平复位信号输出——精确的电源电压监视器——可选择5V、3.3V和3V的复位门槛电平•100万次擦写周期•数据保存可长达100年•8脚DIP或SOIC封装•商业级、工业级和汽车温度范围概述CA T24Cxxx是集E2PROM存储器,复位微控制器和看门狗定时器三种流行功能与一体的芯片。

CAT24C161/162 (16K),CAT24C081/082 (8K),CA T24C041/042 (4K)和CAT24C021/022 (2K)以I2C是串行CMOS E2PROM器件。

釆用CMOS工艺大降低了器件的功耗。

CA T24Cxxx 另一特点是16字节的页写缓冲区,提供8脚DIP和SOIC 封装。

CA T24Cxxx的复位功能和看门狗定时器功能保证系统出现故障的时候能给CPU —个复位信号。

CA T24Cxxx 的2脚输出低电平复位信号,7脚输出高电平复位信号。

CAT24Cxxl看狗溢出信号从SDA脚输出。

CAT24Cxx2不具备看门狗功能。

绝对最大参数工作温度:-55°C〜125°C贮存温度:-65°C〜15°C各管脚承受对地电压:-2.0V〜Vcc+2.0V VCC对地电压范围:-2.0V〜7.0V 最大功耗: 1.0W管脚焊接温度(10S): 300 °C输出短路电流:100mA管脚配置]V C C ]RESET方框图表一直流操作特性表二上电时序管脚介绍WP:写保护将该管脚接Vcc,E2PRON就实现写保护(只读)。

24c02读写--相关资料

24c02读写—相关资料AT24C02是美国Atmel公司的低功耗CMOS型E2PROM,内含256×8位存储空间,具有工作电压宽(2.5~5.5 V)、擦写次数多(大于10 000次)、写入速度快(小于10 ms)、抗干扰能力强、数据不易丢失、体积小等特点。

而且他是采用了I2C总线式进行数据读写的串行器件,占用很少的资源和I/O线,并且支持在线编程,进行数据实时的存取十分方便。

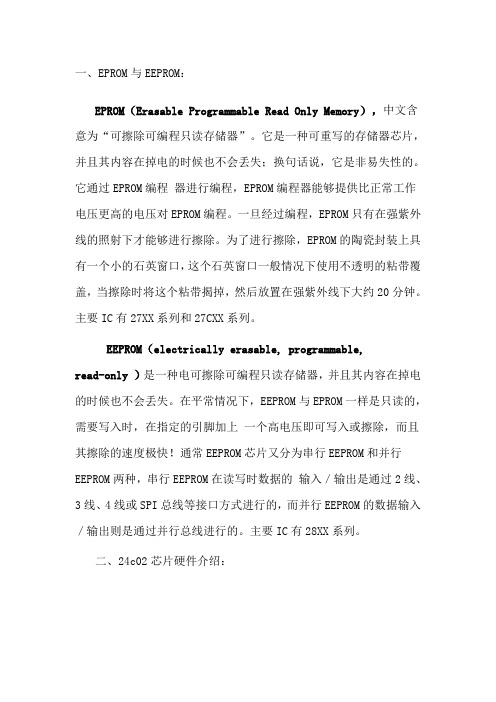

1 AT24C02的引脚功能AT24C02引脚如图1所示。

他的的1、2、3脚是3根地址线,用于确定芯片的硬件地址。

第8脚和第4脚分别为正、负电源。

第5脚SDA为串行数据输入/输出,数据通过这根双向I2C总线串行传送。

第6脚SCL为串行时钟,SDA和SCL为漏极开路端,在实际的应用当中都需要和正电源间各接一个5.1 kΩ的电阻上拉。

第7脚为WP写保护端,接地时允许芯片执行一般的读写操作;接正电源时只允许对器件进行读操作。

2 AT24C02的内部结构图2为AT24C02的内部结构图。

启动、停止逻辑单元 接收数据引脚SDA上的电平信号,判断是否进行启动和停止操作串行控制逻辑单元 根据SCL,SDA电平信号以及“启动、停止逻辑”部件发出的各种信号进行区分,并排列出有关的“寻址”、“读数据”和“写数据”等逻辑,将他们传送到相应的操作单元。

例如:当操作命令为“寻址”时候,他将通知地址计数器加1,并启动“地址比较”器进行工作。

在“读数据”时,他控制“Dout/确认逻辑”单元;在“写数据”时候,他控制“高压泵/定时”电路,以便向E2PROM电路提供编程所需要的高电压。

地址/计数器单元 产生访问E2PROM所需要的存储单元的地址,并将其分别送到X译码器进行字选,送到Y译码器进行位选。

高压泵/定时单元 由于E2PROM数据写入时候需要向电路施加编程高电压,为了解决单一电源电压的供电问题,芯片生产厂家采用了电压的片内提升电路。

电压的提升范围一般可以达12~21.5 V。

24c02中文资料

24C02中文资料1. 介绍24C02是一种串行电子可擦除可编程只读存储器(EEPROM),由美国Microchip Technology公司生产。

它具有2K位存储容量,可用于存储数据。

24C02具有低功耗、高可靠性和可编程性等特点,因此在许多电子设备中得到广泛应用。

2. 24C02的功能特点•存储容量:24C02具有2K位的存储容量,相当于256个字节,每个字节包含8位二进制数据。

•串行接口:24C02采用串行接口进行数据的读写操作,使得它能够与各种微处理器和其他外围设备进行通信。

•可擦除、可编程:24C02采用电子擦除可编程技术,可以对存储的数据进行擦除和编程的操作。

•低功耗:24C02在工作状态下的功耗非常低,使得它适合应用于移动设备和电池供电的设备。

•高可靠性:24C02采用了自动页写技术,具有高可靠性和稳定性,适用于各种工业和消费类电子产品。

3. 24C02的引脚图和功能说明24C02具有8个引脚,每个引脚的功能如下:•VCC:供电引脚,将其连接到供电电源即可。

•GND:地引脚,连接到系统的地线。

•SDA:串行数据输入/输出引脚,与微处理器或其他设备进行数据传输。

•SCL:串行时钟引脚,用于同步传输数据。

•WC:写控制引脚,用于控制写入和擦除操作。

•A0、A1、A2:地址选择引脚,用于选择设备的地址,使得多个设备可以同时使用。

4. 24C02的工作原理24C02采用了I2C总线协议进行数据通信,它的工作原理如下:•开始信号:主设备发出一个开始信号,通知24C02开始进行工作。

•地址传输:主设备发送一个设备地址和操作位(读或写)到24C02。

•对应设备响应:24C02将自己的设备地址进行识别,并发出一个应答信号。

•数据传输:主设备发送要读取或写入的数据到24C02。

•应答信号:24C02接收到数据后,会发出应答信号。

•停止信号:传输完成后,主设备发送一个停止信号,通知24C02本次操作结束。

24c02中文资料 (2)

24C02中文资料1. 简介24C02是一种常用的串行EEPROM(Electrically Erasable Programmable Read-Only Memory)存储器芯片。

它采用I2C 接口进行数据交互,能够以字节为单位读写数据。

24C02广泛应用于各种电子设备中,如计算机、家电、汽车电子设备等。

2. 功能特性•容量:24C02的容量为2Kbit,即256字节。

•输入电压:2.5V至5.5V的工作电压范围。

•I2C接口:24C02采用2线制的I2C接口,支持单主机和多主机模式。

•存储器布局:24C02以字节为单位进行数据存储,每个字节有8位。

•数据保持:24C02具有数据保持能力,即在断电或上电时可以保持数据的完整性。

•写保护功能:24C02提供可编程的写保护功能,可以通过设置相应的寄存器位来保护存储器中的数据免受非授权操作。

3. 存储器结构24C02的存储器由256个字节组成,每个字节有8位数据。

存储器分为多个页面,每个页面包含16个字节。

可以通过I2C接口访问这些页面和字节,实现数据的读写操作。

4. 数据读写4.1 读操作要读取24C02中的数据,首先需发送起始条件,并将器件地址(通常为0xA0)和读命令发送到器件。

然后,按照字节的顺序读取数据。

读取操作的流程如下:1.发送起始条件。

2.发送器件地址和读命令。

3.等待器件确认。

4.读取数据。

5.发送停止条件。

4.2 写操作要向24C02写入数据,也需要发送起始条件,并将器件地址和写命令发送到器件。

然后,写入要存储的数据,并发送停止条件。

写入操作的流程如下:1.发送起始条件。

2.发送器件地址和写命令。

3.等待器件确认。

4.写入数据。

5.发送停止条件。

5. 写保护功能24C02提供了可编程的写保护功能,以保护存储器中的数据免受非授权操作。

通过设置存储器的相应寄存器位,可以开启或关闭写保护功能。

具体的设置方法可以参考24C02的数据手册。

AT24C02A_中文资料(翻译的)

求一个10位数据字的地址。 AT24C016A,16K串行EEPROM:16K是指内部由128页组成,每页含16个字节,随机字寻 址要求一个11位数据字的地址。

引脚电容

推荐工作范围内适用,从TA= 25°C,F =1.0MHzIN 测试条件 输入输出电容(SDA) 输入电容 (A0,A1, A2,SCl) 最大 8 6 表3 单位 pF pF 状态 VI/O=0V VIN=0V

描述:

AT24C02A/04A/08A/16A 提供了串行电气可擦写, 可编程的只读存储器 (EEPROM) 的 2048/4096/8192/16384 位, 由每 8 位 256/512/1024/2048 字组成。 为了在许多要求必须是低功耗和低电压的那些工业和商业应用中 使用,最优化了这个器件。AT24C02A/04A/08A/16A 可用于保存 8-lead PDIP, 8-lead JEDEC SOIC, 8-lead MAP and 8-lead TSSOP 的空间,也可经过一个 2-wire 串行接口存取 AT24C02A/04A/08A/16A。此外,整个 系列可用 2.7V (2.7V to 5.5V)和 1.8V (1.8V to 5.5V) 描述。 引脚配置 表1 引脚名 A0-A2 SDA SCL WP NC 功能 地址输入 串行数据 穿行时钟输入 写保护 未连接

图a

图b

图c

图d

绝对最大范围

操作温度 55℃到+125 贮存温度℃到+150℃ 引脚对地电压 -1.0V 到+7.0V 最大操作电压 6.25V 直流输出电流 5.0mA

注意:强调超出上面“绝对最大范围”列出那些可能促使永 久损毁器件设备。 这只是一个强调范围, 同样在这些情况或 任何别的超出说明书的操作指示下, 设备器件的功能操作不 被限制。 为扩展周期揭露绝对最大范围条件, 这样可能影响 设备的可靠性

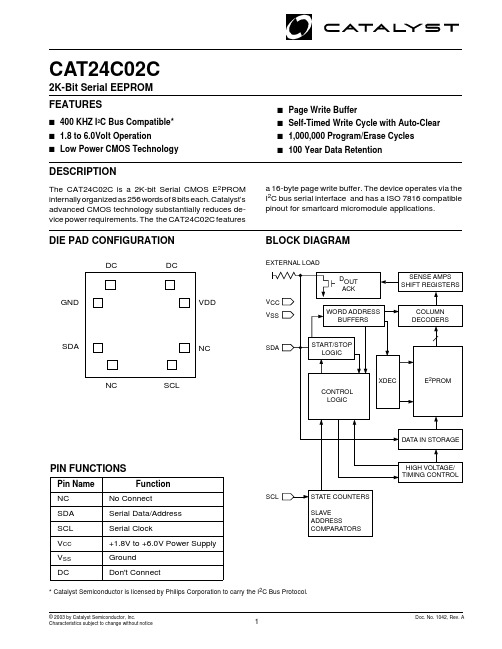

CAT24C02CWA中文资料

© 2003 by Catalyst Semiconductor, Inc. Characteristics subject to change without noticeDoc. No. 1042, Rev. A1CAT24C02C2Doc. No. 1042, Rev. AABSOLUTE MAXIMUM RATINGS*Temperature Under Bias .................–55°C to +125°C Storage Temperature.......................–65°C to +150°C Voltage on Any Pin withRespect to V SS (1).................–2.0V to +V CC + 2.0V V CC with Respect to V SS ................................–2.0V to +7.0V Package Power DissipationCapability (Ta = 25°C)...................................1.0W Lead Soldering Temperature (10 secs)............300°C Output Short Circuit Current (2)........................100mA *COMMENTStresses above those listed under “Absolute Maximum Ratings ” may cause permanent damage to the device.These are stress ratings only, and functional operation of the device at these or any other conditions outside of those listed in the operational sections of this specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability.RELIABILITY CHARACTERISTICS Symbol Parameter Min.Max.Units Reference Test Method N END (3)Endurance 1,000,000Cycles/Byte MIL-STD-883, Test Method 1033T DR (3)Data Retention 100Years MIL-STD-883, Test Method 1008V ZAP (3)ESD Susceptibility 4000Volts MIL-STD-883, Test Method 3015I LTH (3)(4)Latch-up100mAJEDEC Standard 17D.C. OPERATING CHARACTERISTICSV CC = +1.8V to +6.0V, unless otherwise specified.Limits Symbol ParameterMin.Typ.Max.Units Test Conditions I CC Power Supply Current 3mA f SCL = 100 KHz I SB (5)Standby Current (V CC = 5.0V)0µA V IN = GND or V CC I LI Input Leakage Current 10µA V IN = GND to V CC I LO Output Leakage Current 10µA V OUT = GND to V CCV IL Input Low Voltage –1V CC x 0.3V V IH Input High VoltageV CC x 0.7V CC + 0.5V V OL1Output Low Voltage (V CC = 3.0V)0.4V I OL = 3 mA V OL2Output Low Voltage (V CC = 1.8V)0.5VI OL = 1.5 mA Note:(1)The minimum DC input voltage is –0.5V. During transitions, inputs may undershoot to –2.0V for periods of less than 20 ns. Maximum DCvoltage on output pins is V CC +0.5V, which may overshoot to V CC + 2.0V for periods of less than 20ns.(2)Output shorted for no more than one second. No more than one output shorted at a time.(3)This parameter is tested initially and after a design or process change that affects the parameter.(4)Latch-up protection is provided for stresses up to 100 mA on address and data pins from –1V to V CC +1V.(5)Standby Current (I SB ) = 0µA (<900nA).CAPACITANCE T A = 25°C, f = 1.0 MHz, V CC = 5V Symbol TestMax.Units Conditions C I/O (3)Input/Output Capacitance (SDA)8pF V I/O = 0V C IN (3)Input Capacitance (SCL)6pFV IN = 0VCAT24C02C3Doc. No. 1042, Rev. AA.C. CHARACTERISTICSV CC = +1.8V to +6.0V, unless otherwise specified.Read & Write Cycle LimitsNote:(1)This parameter is tested initially and after a design or process change that affects the parameter.(2)t PUR and t PUW are the delays required from the time V CC is stable until the specified operation can be initiated.The write cycle time is the time from a valid stop condition of a write sequence to the end of the internal program/erase cycle. During the write cycle, the bus interface circuits are disabled, SDA is allowed to remain high, and the device does not respond to its slave address.元器件交易网CAT24C02C4Doc. No. 1042, Rev. AFUNCTIONAL DESCRIPTIONThe CAT24C02C supports the I 2C Bus data transmis-sion protocol. This Inter-Integrated Circuit Bus protocol defines any device that sends data to the bus to be a transmitter and any device receiving data to be a re-ceiver. Data transfer is controlled by the Master device which generates the serial clock and all START and STOP conditions for bus access. The CAT24C02C operates as a Slave device. Both the Master and Slave devices can operate as either transmitter or receiver, but the Master device controls which mode is activated.PIN DESCRIPTIONSSCL: Serial ClockThe CAT24C02C serial clock input pin is used to clock all data transfers into or out of the device. This is an input pin.SDA: Serial Data/AddressThe CAT24C02C bidirectional serial data/address pin is used to transfer data into and out of the device. The SDA pin is an open drain output and can be wire-ORed with other open drain or open collector outputs.I 2C BUS PROTOCOLThe following defines the features of the I 2C bus proto-col:(1)Data transfer may be initiated only when the bus isnot busy.(2)During a data transfer, the data line must remainstable whenever the clock line is high. Any changes in the data line while the clock line is high will be interpreted as a START or STOP condition.Figure 3. Start/Stop Timing5020 FHD F055020 FHD F03SCLSDA INSDA OUTSTART BITSDASTOP BITSCL元器件交易网CAT24C02C5Doc. No. 1042, Rev. ASTART ConditionThe START Condition precedes all commands to the device, and is defined as a HIGH to LOW transition of SDA when SCL is HIGH. The CAT24C02C monitor the SDA and SCL lines and will not respond until this condition is met.STOP ConditionA LOW to HIGH transition of SDA when SCL is HIGH determines the STOP condition. All operations must end with a STOP condition.DEVICE ADDRESSINGThe bus Master begins a transmission by sending a START condition. The Master then sends the address of the particular slave device it is requesting. The four most significant bits of the 8-bit slave address are fixed as 1010 for the CAT24C02C (see Fig. 5). The next three significant bits are all zeros. The last bit of the slave address specifies whether a Read or Write operation is to be performed. When this bit is set to 1, a Read operation is selected, and when set to 0, a Write opera-tion is selected.After the Master sends a START condition and the slave address byte, the CAT24C02C monitors the bus and responds with an acknowledge (on the SDA line). The CAT24C02C then performs a Read or Write operation depending on the state of the R/W bit.AcknowledgeAfter a successful data transfer, each receiving device is required to generate an acknowledge. The acknowledg-ing device pulls down the SDA line during the ninth clock cycle, signaling that it received the 8 bits of data.The CAT24C02C responds with an acknowledge after receiving a START condition and its slave address. If the device has been selected along with a write operation,it responds with an acknowledge after receiving each 8-bit byte.When the CAT24C02C is in a READ mode it transmits 8 bits of data, releases the SDA line, and monitors the line for an acknowledge. Once it receives this acknowl-edge, the CAT24C02C will continue to transmit data. If no acknowledge is sent by the Master, the device terminates data transmission and waits for a STOP condition.WRITE OPERATIONSByte WriteIn the Byte Write mode, the Master device sends the START condition and the slave address information (with the R/W bit set to zero) to the Slave device. After the Slave generates an acknowledge, the Master sends the byte address that is to be written into the address pointer of the CAT24C02C. After receiving another acknowledge from the Slave, the Master device trans-mits the data byte to be written into the addressed memory location. The CAT24C02C acknowledge once more and the Master generates the STOP condition, at which time the device begins its internal programming cycle to nonvolatile memory. While this internal cycle is in progress, the device will not respond to any request from the Master device.Page WriteThe CAT24C02C writes up to 16 bytes of data in a single write cycle, using the Page Write operation. The Page Write operation is initiated in the same manner as counter will ‘wrap around ’ to address 0 and continue toFigure 4. Acknowledge Timing5020 FHD F06ACKNOWLEDGESTARTSCL FROM MASTERDATA OUTPUTFROM TRANSMITTERDATA OUTPUT FROM RECEIVER元器件交易网CAT24C02C6Doc. No. 1042, Rev. Athe Byte Write operation, however instead of terminating after the initial word is transmitted, the Master is allowed to send up to 15 additional bytes. After each byte has been transmitted the CAT24C02C will respond with an acknowledge, and internally increment the low order address bits by one. The high order bits remain un-changed.If the Master transmits more than 16 bytes prior to sending the STOP condition, the address counter ‘wraps around ’, and previously transmitted data will be overwrit-ten.Once all 16 bytes are received and the STOP condition has been sent by the Master, the internal programming cycle begins. At this point all received data is written to the CAT24C02C in a single write cycle.Acknowledge PollingThe disabling of the inputs can be used to take advan-tage of the typical write cycle time. Once the stop condition is issued to indicate the end of the host ’s write operation, the CAT24C02C initiates the internal write cycle. ACK polling can be initiated immediately. This involves issuing the start condition followed by the slave address for a write operation. If the CAT24C02C is still busy with the write operation, no ACK will be returned.If the CAT24C02C has completed the write operation,an ACK will be returned and the host can then proceed with thenext read or write operation.Selective ReadSelective READ operations allow the Master device to select at random any memory location for a READ operation. The Master device first performs a ‘dummy ’write operation by sending the START condition, slave address and byte address of the location it wishes to read. After the CAT24C02C acknowledge the word address, the Master device resends the START condi-tion and the slave address, this time with the R/W bit set to one. The CAT24C02C then responds with its ac-knowledge and sends the 8-bit byte requested. The master device does not send an acknowledge but will generate a STOP condition.Sequential ReadThe Sequential READ operation can be initiated by either the immediate Address READ or Selective READ operations. After the 24C02C sends initial 8-bit byte requested, the Master will respond with an acknowledge which tells the device it requires more data. The CAT24C02C will continue to output an 8-bit byte for each acknowledge sent by the Master. The operation is terminated when the Master fails to respond with an acknowledge, thus sending the STOP condition.The data being transmitted from the CAT24C02C is outputted sequentially with data from address N fol-lowed by data from address N+1. The READ operation address counter increments all of the CAT24C02C address bits so that the entire memory array can be read during one operation. If more than 255 bytes are read out, the counter will “wrap around ” and continue to clock out data bytes.Figure 5. Slave Address BitsREAD OPERATIONSThe READ operation for the CAT24C02C is initiated in the same manner as the write operation with the one exception that the R/W bit is set to a one. Three different READ operations are possible: Immediate Address READ, Selective READ and Sequential READ.Immediate Address ReadThe CAT24C02C ’s address counter contains the ad-dress of the last byte accessed, incremented by one. In other words, if the last READ or WRITE access was to address N, the READ immediately following would ac-cess data from address N+1. If N=E (where E = 255 for 24WC02), then the clock out data. After the CAT24C02C receives its slave address information (with the R/W bit set to one), it issues an acknowledge, then transmits the 8-bit byte requested. The master device does not send an acknowledge but will generate a STOP condition.1010000R/W24C02C元器件交易网CAT24C02C7Doc. No. 1042, Rev. AFigure 7. Page Write Timing5020 FHD F08Figure 6. Byte Write TimingBUS ACTIVITY:MASTERSDA LINEDATA n+PBYTE ADDRESS (n)C KC K DATA n C K S T O C KDATA n+1C K S T A R SLAVE ADDRESSNOTE: IN THIS EXAMPLE n = XXXX 0000(B); X = 1 or 0BYTE ADDRESSSLAVE ADDRESS SA C KA C KDATAA C KS T O P PBUS ACTIVITY:MASTERSDA LINES T A R T 5020 FHD F10Figure 8. Immediate Address Read TimingSCL SDA 8TH BIT STOPNO ACKDATA OUT89SLAVE ADDRESSSA C KDATAN O A C KS T O P PBUS ACTIVITY:MASTERSDA LINES T A R T 元器件交易网CAT24C02C8Doc. No. 1042, Rev. AORDERING INFORMATIONFigure 9. Selective Read TimingSLAVE ADDRESSSA C KN O A C K S T O P PBUS ACTIVITY:MASTERSDA LINES T A R T BYTE ADDRESS (n)S A C KDATA nSLAVE ADDRESSA C KS T A R T *Prefix Device #Suffix 元器件交易网Catalyst Semiconductor, Inc.Corporate Headquarters Copyrights, Trademarks and PatentsTrademarks and registered trademarks of Catalyst Semiconductor include each of the following:DPP ™AE 2 ™Catalyst Semiconductor has been issued U.S. and foreign patents and has patent applications pending that protect its products. For a complete list of patents issued to Catalyst Semiconductor contact the Company’s corporate office at 408.542.1000.CATALYST SEMICONDUCTOR MAKES NO WARRANTY, REPRESENTATION OR GUARANTEE, EXPRESS OR IMPLIED, REGARDING THE SUITABILITY OF ITS PRODUCTS FOR ANY PARTICULAR PURPOSE, NOR THAT THE USE OF ITS PRODUCTS WILL NOT INFRINGE ITS INTELLECTUAL PROPERTY RIGHTS OR THE RIGHTS OF THIRD PARTIES WITH RESPECT TO ANY PARTICULAR USE OR APPLICATION AND SPECIFICALLY DISCLAIMS ANY AND ALL LIABILITY ARISING OUT OF ANY SUCH USE OR APPLICATION, INCLUDING BUT NOT LIMITED TO, CONSEQUENTIAL OR INCIDENTAL DAMAGES.Catalyst Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Catalyst Semiconductor product could create a situation where personal injury or death may occur.Catalyst Semiconductor reserves the right to make changes to or discontinue any product or service described herein without notice. Products with data sheets labeled "Advance Information" or "Preliminary" and other products described herein may not be in production or offered for sale.Catalyst Semiconductor advises customers to obtain the current version of the relevant product information before placing orders. Circuit diagrams illustrate typical semiconductor applications and may not be complete.。

S-24C02B中文资料