74HC32A

74hc32芯片参数

74HC32Quad 2−Input OR GateHigh−Performance Silicon−Gate CMOS The 74HC32 is identical in pinout to the LS32. The device inputs are compatible with Standard CMOS outputs; with pullup resistors, they are compatible with LSTTL outputs.Features•Output Drive Capability: 10 LSTTL Loads•Outputs Directly Interface to CMOS, NMOS and TTL •Operating V oltage Range: 2.0 to 6.0 V•Low Input Current: 1.0 m A•High Noise Immunity Characteristic of CMOS Devices•In Compliance With the JEDEC Standard No. 7A Requirements •ESD Performance: HBM > 2000 V; Machine Model > 200 V •Chip Complexity: 48 FETs or 12 Equivalent Gates•These are Pb−Free DevicesMARKINGDIAGRAMSHC32= Device CodeA= Assembly LocationL, WL= Wafer LotY= YearW, WW= Work WeekG or G= Pb−Free PackageTSSOP−14DT SUFFIXCASE 948GSOIC−14D SUFFIXCASE 751AHC32ALYW GG114See detailed ordering and shipping information in the package dimensions section on page 2 of this data sheet.ORDERING INFORMATION(Note: Microdot may be in either location)3Y11A1PIN 14 = V CC PIN 7 = GNDLOGIC DIAGRAM2B16Y24A25B28Y39A310B311Y412A413B4Y = A+BPinout: 14−Lead Packages (Top View)1314121110982134567V CC B4A4Y4B3A3Y3A1B1Y1A2B2Y2GNDL L H HL H L HFUNCTION TABLEInputs Output A B L H H HY ORDERING INFORMATIONDevicePackage Shipping †74HC32DR2G SOIC −14(Pb −Free)2500 / Tape & Reel74HC32DTR2GTSSOP −14*†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.*This package is inherently Pb −Free.MAXIMUM RATINGSSymbol Parameter Value Unit V CC DC Supply Voltage (Referenced to GND)– 0.5 to + 7.0V V in DC Input Voltage (Referenced to GND)– 0.5 to V CC + 0.5V V out DC Output Voltage (Referenced to GND)– 0.5 to V CC + 0.5VI in DC Input Current, per Pin±20mAI out DC Output Current, per Pin±25mAI CC DC Supply Current, V CC and GND Pins±50mAP D Power Dissipation in Still Air,SOIC Package†TSSOP Package†500450mWT stg Storage Temperature– 65 to + 150_CT L Lead Temperature, 1 mm from Case for 10 SecondsSOIC or TSSOP Package260_CStresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stressratings only. Functional operation above the Recommended Operating Conditions is not implied.Extended exposure to stresses above the Recommended Operating Conditions may affectdevice reliability.†Derating—SOIC Package: – 7 mW/_C from 65_ to 125_CTSSOP Package: − 6.1 mW/_C from 65_ to 125_CFor high frequency or heavy load considerations, see Chapter 2 of the ON Semiconductor High−Speed CMOS Data Book (DL129/D). RECOMMENDED OPERATING CONDITIONSSymbol Parameter Min Max UnitV CC DC Supply Voltage (Referenced to GND) 2.0 6.0VV in, V out DC Input Voltage, Output Voltage (Referenced toGND)0V CC VT A Operating Temperature, All Package Types– 55+ 125_Ct r, t f Input Rise and Fall Time V CC = 2.0 V (Figure 1)V CC = 4.5 VV CC = 6.0 V 01000500400nsThis device contains protectioncircuitry to guard against damagedue to high static voltages or electricfields. However, precautions mustbe taken to avoid applications of anyvoltage higher than maximum ratedvoltages to this high−impedance cir-cuit. For proper operation, V in andV out should be constrained to therange GND v (V in or V out) v V CC.Unused inputs must always betied to an appropriate logic voltagelevel (e.g., either GND or V CC).Unused outputs must be left open.DC CHARACTERISTICS(Voltages Referenced to GND)V CC (V)Guaranteed LimitSymbol Parameter Condition−55 to 25°C≤85°C≤125°C UnitV IH Minimum High−Level Input Voltage V out = 0.1V or V CC−0.1V|I out| ≤ 20m A 2.03.04.56.01.502.103.154.201.502.103.154.201.502.103.154.20VV IL Maximum Low−Level Input Voltage V out = 0.1V or V CC− 0.1V|I out| ≤ 20m A 2.03.04.56.00.500.901.351.800.500.901.351.800.500.901.351.80VV OH Minimum High−Level OutputVoltage V in = V IH or V IL|I out| ≤ 20m A2.04.56.01.94.45.91.94.45.91.94.45.9VV in =V IH or V IL|I out| ≤ 2.4mA|I out| ≤ 4.0mA|I out| ≤ 5.2mA3.04.56.02.483.985.482.343.845.342.203.705.20V OL Maximum Low−Level OutputVoltage V in = V IH or V IL|I out| ≤ 20m A2.04.56.00.10.10.10.10.10.10.10.10.1VV in = V IH or V IL|I out| ≤ 2.4mA|I out| ≤ 4.0mA|I out| ≤ 5.2mA3.04.56.00.260.260.260.330.330.330.400.400.40I in Maximum Input Leakage Current V in = V CC or GND 6.0±0.1±1.0±1.0m AI CC Maximum Quiescent SupplyCurrent (per Package)V in = V CC or GNDI out = 0m A6.0 2.02040m ANOTE:Information on typical parametric values can be found in Chapter 2 of the ON Semiconductor High−Speed CMOS Data Book (DL129/D). AC CHARACTERISTICS(C L = 50pF, Input t r = t f = 6ns)V CC (V)Guaranteed LimitSymbol Parameter−55 to 25°C≤85°C≤125°C Unitt PLH, t PHL Maximum Propagation Delay, Input A or B to Output Y(Figures 1 and 2)2.03.04.56.07530151395401916110552219nst TLH, t THL Maximum Output Transition Time, Any Output(Figures 1 and 2)2.03.04.56.07527151395321916110362219nsC in Maximum Input Capacitance101010pF NOTE:For propagation delays with loads other than 50 pF, and information on typical parametric values, see Chapter 2 of the ON Semiconductor High−Speed CMOS Data Book (DL129/D).C PD Power Dissipation Capacitance (Per Buffer)*Typical @ 25°C, V CC = 5.0 V, V EE = 0 VpF20*Used to determine the no−load dynamic power consumption: P D = C PD V CC2f + I CC V CC. For load considerations, see Chapter 2 of the ON Semiconductor High−Speed CMOS Data Book (DL129/D).Figure 1. Switching WaveformsOUTPUT YINPUT A OR BC L **Includes all probe and jig capacitanceTESTFigure 2. Test CircuitYABFigure 3. Expanded Logic Diagram(1/4 of the Device)GNDV CCSOIC −14CASE 751A −03ISSUE HNOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.4.MAXIMUM MOLD PROTRUSION 0.15 (0.006)PER SIDE.5.DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127(0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.DIM MIN MAX MIN MAX INCHESMILLIMETERS A 8.558.750.3370.344B 3.80 4.000.1500.157C 1.35 1.750.0540.068D 0.350.490.0140.019F 0.40 1.250.0160.049G 1.27 BSC 0.050 BSC J 0.190.250.0080.009K 0.100.250.0040.009M 0 7 0 7 P 5.80 6.200.2280.244R0.250.500.0100.019____DIMENSIONS: MILLIMETERS*For additional information on our Pb −Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.TSSOP −14CASE 948G −01ISSUE BDIM MIN MAX MIN MAX INCHESMILLIMETERS A 4.90 5.100.1930.200B 4.30 4.500.1690.177C −−− 1.20−−−0.047D 0.050.150.0020.006F 0.500.750.0200.030G 0.65 BSC 0.026 BSC H 0.500.600.0200.024J 0.090.200.0040.008J10.090.160.0040.006K 0.190.300.0070.012K10.190.250.0070.010L 6.40 BSC 0.252 BSC M0 8 0 8 NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.4.DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE.5.DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08(0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.6.TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY .7.DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE −W −.____14X REF K14X0.360.65PITCHSOLDERING FOOTPRINT**For additional information on our Pb −Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

74HC系列芯片资料

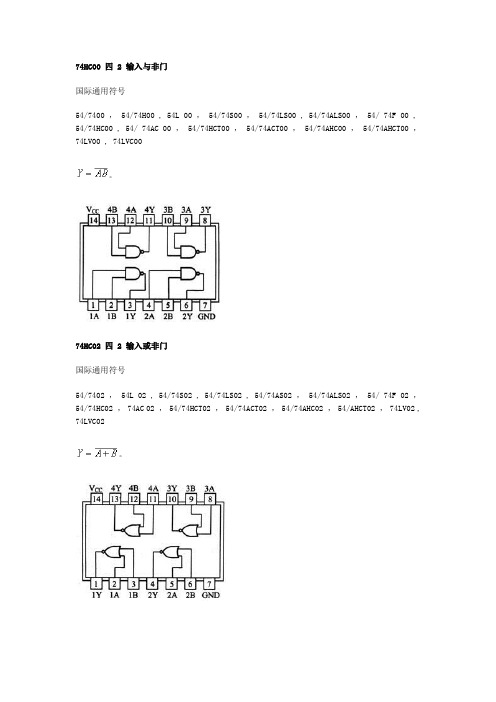

74HC00 四 2 输入与非门国际通用符号54/7400 , 54/74H00 , 54L 00 , 54/74S00 , 54/74LS00 , 54/74ALS00 , 54/ 74F 00 , 54/74HC00 , 54/ 74AC 00 , 54/74HCT00 , 54/74ACT00 , 54/74AHC00 , 54/74AHCT00 ,74LV00 , 74LVC00。

74HC02 四 2 输入或非门国际通用符号54/7402 , 54L 02 , 54/74S02 , 54/74LS02 , 54/74AS02 , 54/74ALS02 , 54/ 74F 02 ,54/74HC02 , 74AC 02 , 54/74HCT02 , 54/74ACT02 , 54/74AHC02 , 54/AHCT02 , 74LV02 , 74LVC02。

74HC04 六反相器国际通用符号54/7404 , 54L 04 , 54/74H04 , 54/74S04 , 54/74LS04 , 54/74AS04 , 54/74ALS04 ,54/ 74F 04 , 54/74HCU04 , 54/74HC04 , 54/ 74AC 04 , 54/74HCT04 , 54/74ACT04 ,54/74AHC04 , 54/74AHCT04 , 74LV04 , 74LVC04 , 54/74AHCU04 , 74LVU04 , 74LVCU04 .74HC08 四 2 输入与门国际通用符号54/7408 , 54/74S08 , 54/74LS08 , 54/74AS08 , 54/74ALS08 , 54/ 74F 08 , 54/74HC08 ,54/74HCT08 , 54/ 74AC 08 , 54/74ACT08 , 54/74AHC08 , 54/74AHCT08 , 74LV08 , 74LVC08。

中波发射机常用数字集成电路工作原理详解

中波发射机常用数字集成电路工作原理详解本节列举了21种数字电路在全固态数字中波发射机单元电路的典型应用,并对其工作原理进行分析。

一、四二输入与非门(74HC00)74HC00是应用广泛的四二输入与非门电路,它内部含有4个独立的2输入与非门,其逻辑功能是:输入全部为“1”时,输出为“0”;输入端只要有“0”,输出端就为“1”。

在发射机本地遥控显示电路中,74HC00(N17)作为导向器使用。

原理分析:S1投向“遥控”时,能产生低电平操作指令,该电平由非门N17B 倒相为高电平驱动遥控指令H28,同时“本地”指示灯H29熄灭。

N17A 输出高电平,用于外部显示。

二、四二输入或非门(74HC02)74HC02为四二输入或非门电路,内部含有4个独立的2输入或非门,其逻辑功能是:A 、B 任意一个或全部为“1”时, 输出为“0”; A=B=0时,输出端为“1”。

在发射机驻波故障检测电路中,74HC02(N43)作为禁止门、合门和倒相器使用。

当输出网络出现反射时,不影响天线系统的调配,而当天线出现反射时会导致输出网络失配,为了避免不必要的误报警,设置了识别禁止门电路。

其原理是:当天线出现反射时,输出网络与天线驻波检测电路分别送出19ms 和14ms 的负脉冲信号,其中前14ms 被禁止门N43B 禁止住,后5ms输出输出正图1 74HC00应用单元图脉冲,使网络驻波显示灯亮0.5s后转为绿色。

当天线不匹配时5ms和14ms正脉冲分别加到N43C的8脚和9脚,经N43C合成19ms的负脉冲,去关功放和驻波自检处理电路。

图2 74HC02应用单元图三、双4输入与非门(74HC20)74HC20为双4输入与非门电路,它内部含有2个独立的4输入与非门,其逻辑功能是:输入全部为“1”时,输出为“0”;输入端只要有“0”,输出端就为“1”。

在发射机功率控制电路中,74HC32(N63、N64、N65)作为功率升、降计数控制门使用。

或门芯片型号

或门芯片型号或门芯片是一种逻辑门电路,常用于数字电路中,其功能是判断输入信号中是否存在至少一个高电平信号。

下面介绍若干种常见的或门芯片型号。

1. 74LS3274LS32是一种四输入或门芯片。

它具有四个输入端口(A、B、C和D)和一个输出端口(Y)。

当其中任意一个输入端口接收到高电平信号时,输出端口Y将置为高电平。

该芯片采用低功耗S型技术,可配合其他TTL逻辑门芯片工作。

2. 74HC3274HC32是一种四输入或门芯片。

与74LS32类似,它可以接受四个输入信号,只要其中一个信号为高电平,输出端口Y就会置为高电平。

不同的是,74HC32采用了CMOS技术,具有低功耗和较高的工作速度。

3. 74HC407574HC4075是一种三输入或门芯片。

它与上述的74LS32和74HC32不同之处在于它只有三个输入端口(A、B和C),但输出端口Y的功能和上述芯片相同。

该芯片采用了低功耗CMOS技术,适合于数字系统中的应用。

4. CD4072CD4072是一种双四输入或门芯片。

它具有两个相互独立的4输入或门电路,每个电路有四个输入端口(A1、B1、C1和D1,A2、B2、C2和D2)和一个输出端口(Y1、Y2)。

当任意一个电路的输入端口接收到高电平信号时,对应的输出端口将置为高电平。

该芯片采用CMOS技术,功耗较低。

以上仅列举了几种常见的或门芯片型号,每种型号都有自己特定的工作电压、逻辑电平和功耗等特性,可以根据具体的应用需求选择适合的型号。

同时,使用这些芯片需要一定的电路设计和连接知识,建议在使用前参考相关的技术文档和数据手册。

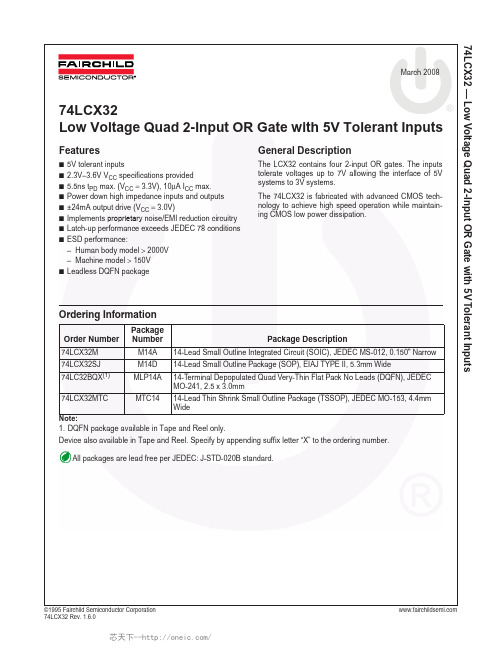

74LCX32MTCX,74LCX32MX,74LCX32BQX, 规格书,Datasheet 资料

74LCX32 — Low Voltage Quad 2-Input OR Gate with 5V Tolerant InputsFeatures■ 5V tolerant inputs■ 2.3V–3.6V V CC specifications provided ■ 5.5ns t PD max. (V CC = 3.3V), 10 µ A I CC max. ■ Power down high impedance inputs and outputs ■ ±24mA output drive (V CC = 3.0V)■ ■ Latch-up performance exceeds JEDEC 78 conditions ■ ESD performance:– Human body model > 2000V – Machine model > 150V ■ Leadless DQFN packageGeneral DescriptionThe LCX32 contains four 2-input OR gates. The inputs tolerate voltages up to 7V allowing the interface of 5V systems to 3V systems.The 74LCX32 is fabricated with advanced CMOS tech-nology to achieve high speed operation while maintain-ing CMOS low power dissipation.Ordering InformationNote:1.DQFN package available in Tape and Reel only.Device also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering number.All packages are lead free per JEDEC: J-STD-020B standard.Order NumberPackage NumberPackage Description74LCX32M M14A 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow 74LCX32SJ M14D 14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide74LC32BQX (1)MLP14A 14-Terminal Depopulated Quad Very-Thin Flat Pack No Leads (DQFN), JEDEC MO-241, 2.5 x 3.0mm74LCX32MTCMTC1414-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm WideImplements proprietary noise/EMI reduction circuitry Low Voltage Quad 2-Input OR Gate with 5V Tolerant Inputs74LCX32 — Low Voltage Quad 2-Input OR Gate with 5V Tolerant Inputs Pad Assignments for DQFN(Top View)Pin DescriptionPin Names DescriptionA n,B n InputsO n Outputs74LCX32 — Low Voltage Quad 2-Input OR Gate with 5V Tolerant InputsNote:2.I O Absolute Maximum Rating must be observed.Recommended Operating Conditions (3)The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to absolute maximum ratings.Note:3.Unused inputs must be held HIGH or LOW. They may not float.V CC Supply Voltage –0.5V to +7.0V V I DC Input Voltage–0.5V to +7.0V V O DC Output Voltage, Output in HIGH or LOW State (2) –0.5V to V CC + 0.5VI IK DC Input Diode Current, V I < GND –50mA I OKDC Output Diode Current V O < GND –50mA V O > V CC+50mA I O DC Output Source/Sink Current ±50mA I CC DC Supply Current per Supply Pin ±100mA I GND DC Ground Current per Ground Pin ±100mAT STGStorage Temperature–65°C to +150°CSymbolParameter Min.Max.UnitsV CCSupply Voltage Operating 2.0 3.6V Data Retention1.5 3.6V I Input Voltage0 5.5V V O Output Voltage, HIGH or LOW State 0V CC V I OH / I OLOutput Current V CC = 3.0V–3.6V ±24mAV CC = 2.7V–3.0V ±12 V CC = 2.3V–2.7V±8T A Free-Air Operating Temperature–4085°C ∆ t / ∆ VInput Edge Rate, V IN = 0.8V–2.0V , V CC = 3.0V10ns /V74LCX32 — Low Voltage Quad 2-Input OR Gate with 5V Tolerant InputsAC Electrical CharacteristicsNote:4.Skew is defined as the absolute value of the difference between the actual propagation delay for any twoseparate outputs of the same device. The specification applies to any outputs switching in the same direction, either HIGH-to-LOW (t OSHL ) or LOW-to-HIGH (t OSLH ).V IL LOW Level Input Voltage 2.3–2.70.7V 2.7–3.60.8V OHHIGH Level Output Voltage2.3–3.6I OH = –100µA V CC – 0.2V2.3I OH = –8mA 1.82.7I OH = –12mA 2.23.0I OH = –18mA 2.4I OH = –24mA 2.2V OLLOW Level Output Voltage 2.3–3.6I OL = 100µA 0.2V2.3I OL = 8mA 0.62.7I OL = 12mA 0.43.0I OL = 16mA 0.4I OL = 24mA 0.55I I Input Leakage Current 2.3–3.60 ≤ V I ≤ 5.5V ±5.0µA I OFF Power-Off Leakage Current 0V I or V O = 5.5V 10µA I CC Quiescent Supply Current 2.3–3.6V I = V CC or GND 10µA 3.6V ≤ V I ≤ 5.5V ±10∆I CCIncrease in I CC per Input2.3–3.6V IH = V CC – 0.6V500µASymbolParameterT A = –40°C to +85°C, R L = 500ΩUnitsV CC = 3.3V ± 0.3V,C L = 50pFV CC = 2.7V,C L = 50pF V CC = 2.5V ± 0.2V,C L = 30pF Min.Max.Min.Max.Min.Max.t PHL , t PLHPropagation Delay1.55.5 1.56.21.56.6ns t OSHL , t OSLH Output to Output Skew (4)1.0ns74LCX32 — Low Voltage Quad 2-Input OR Gate with 5V Tolerant InputsCapacitanceV OLVQuiet Output Dynamic Valley V OL3.3C L = 50pF , V IH = 3.3V , V IL = 0V –0.8V2.5C L = 30pF , V IH = 2.5V , V IL = 0V–0.6SymbolParameterConditionsTypicalUnitsC IN Input Capacitance V CC = Open, V I = 0V or V CC 7pF C OUT Output CapacitanceV CC = 3.3V , V I = 0V or V CC8pF C PDPower Dissipation CapacitanceV CC = 3.3V , V I = 0V or V CC , f = 10MHz25pFPropagation Delay. Pulse Width and t rec Waveforms 3-STATE Output High Enable andDisable Times for Logic Setup Time, Hold Time and Recovery Time for Logict rise and t fallSymbolV CC3.3V ± 0.3V 2.7V 2.5V ± 0.2VV mi 1.5V 1.5V V CC /2 V mo 1.5V 1.5V V CC /2Reel Dimensions inches (millimeters)Tape Size A B C D N W1W2 12mm13.0 (330.0)0.059 (1.50)0.512 (13.00)0.795 (20.20) 2.165 (55.00)0.488 (12.4)0.724 (18.4)Figure 3. 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" NarrowPackage drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions, MS-012,VARIATION AB,ISSUE C,B)ALL DIMENSIONS ARE IN MILLIMETERS.C)DIMENSIONS DO NOT INCLUDE MOLDFLASH OR BURRS.D)LANDPATTERN STANDARD:SOIC127P600X145-14ME)DRAWING CONFORMS TO ASME Y14.5M-1994F)DRAWING FILE NAME:M14AREV138°0°SEATING PLANEDETAIL ASCALE:20:1GAGE PLANE X 45°(1.04)0.900.500.36R0.10R0.100.500.25Figure 4. 14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm WidePackage drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions,Figure 5. 14-Terminal Depopulated Quad Very-Thin Flat Pack No Leads (DQFN), JEDEC MO-241, 2.5 x 3.0mm Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify orFigure 6. 14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm WidePackage drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.C.DIMENSIONS ARE EXCLUSIVE OF BURRS,MOLD FLASH,AND TIE BAR EXTRUSIONSF.DRAWING FILE NAME:MTC14REV61.00D.DIMENSIONING AND TOLERANCES PER ANSI Y14.5M,1982R0.09minNDPATTERN STANDARD:SOP65P640X110-14M A.CONFORMS TO JEDEC REGISTRATION MO-153,VARIATION AB,REF NOTE 6B.DIMENSIONS ARE IN MILLIMETERSsubsidiaries,and is not intended to be an exhaustive list of all such trademarks.ACEx®Build it Now™CorePLUS™CROSSVOLT™CTL™Current Transfer Logic™EcoSPARK®EZSWITCH™*™®Fairchild®Fairchild Semiconductor®FACT Quiet Series™FACT®FAST®FastvCore™FlashWriter®*FPS™FRFET®Global Power Resource SMGreen FPS™Green FPS™e-Series™GTO™i-Lo™IntelliMAX™ISOPLANAR™MegaBuck™MICROCOUPLER™MicroFET™MicroPak™MillerDrive™Motion-SPM™OPTOLOGIC®OPTOPLANAR®®PDP-SPM™Power220®POWEREDGE®Power-SPM™PowerTrench®Programmable Active Droop™QFET®QS™QT Optoelectronics™Quiet Series™RapidConfigure™SMART START™SPM®STEALTH™SuperFET™SuperSOT™-3SuperSOT™-6SuperSOT™-8SupreMOS™SyncFET™®The Power Franchise®TinyBoost™TinyBuck™TinyLogic®TINYOPTO™TinyPower™TinyPWM™TinyWire™µSerDes™UHC®Ultra FRFET™UniFET™VCX™*EZSWITCH™and FlashWriter®are trademarks of System General Corporation,used under license by Fairchild Semiconductor. DISCLAIMERFAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY,FUNCTION,OR DESIGN.FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN;NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS,NOR THE RIGHTS OF OTHERS.THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD’S WORLDWIDE TERMS AND CONDITIONS,SPECIFICALLY THE WARRANTY THEREIN,WHICH COVERS THESE PRODUCTS.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices or systemswhich,(a)are intended for surgical implant into the body or(b)support or sustain life,and(c)whose failure to performwhen properly used in accordance with instructions for use provided in the labeling,can be reasonably expected to result in a significant injury of the user.2.A critical component in any component of a life support,device,or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system,or to affect its safety or effectiveness.PRODUCT STATUS DEFINITIONSDefinition of TermsDatasheet Identification Product Status DefinitionAdvance Information Formative or In Design This datasheet contains the design specifications for product development.Specifications may change in any manner without notice.Preliminary First Production This datasheet contains preliminary data;supplementary data will bepublished at a later date.Fairchild Semiconductor reserves the right tomake changes at any time without notice to improve design. 74LCX32 — Low Voltage Quad 2-Input OR Gate with 5V Tolerant Inputs。

74LS,74HC,CD系列型号功能对照(全)

TTL,CMOS型号内容---------------------------------------------------- 74ls00 2输入四与非门74ls01 2输入四与非门 (oc)74ls02 2输入四或非门74ls03 2输入四与非门 (oc)74ls04 六倒相器74ls05 六倒相器(oc)74ls06 六高压输出反相缓冲器/驱动器(oc,30v)74ls07 六高压输出缓冲器/驱动器(oc,30v)74ls08 2输入四与门74ls09 2输入四与门(oc)74ls10 3输入三与非门74ls11 3输入三与门74ls12 3输入三与非门 (oc)74ls13 4输入双与非门 (斯密特触发)74ls14 六倒相器(斯密特触发)74ls15 3输入三与门 (oc)74ls16 六高压输出反相缓冲器/驱动器(oc,15v)74ls17 六高压输出缓冲器/驱动器(oc,15v)74ls18 4输入双与非门 (斯密特触发)74ls19 六倒相器(斯密特触发)74ls20 4输入双与非门74ls21 4输入双与门74ls22 4输入双与非门(oc)74ls23 双可扩展的输入或非门74ls24 2输入四与非门(斯密特触发)74ls25 4输入双或非门(有选通)74ls26 2输入四高电平接口与非缓冲器(oc,15v)74ls27 3输入三或非门74ls28 2输入四或非缓冲器74ls30 8输入与非门74ls31 延迟电路74ls32 2输入四或门74ls33 2输入四或非缓冲器(集电极开路输出)74ls34 六缓冲器74ls35 六缓冲器(oc)74ls36 2输入四或非门(有选通)74ls37 2输入四与非缓冲器74ls38 2输入四或非缓冲器(集电极开路输出)74ls39 2输入四或非缓冲器(集电极开路输出)74ls40 4输入双与非缓冲器74ls41 bcd-十进制计数器74ls42 4线-10线译码器(bcd输入)74ls43 4线-10线译码器(余3码输入)74ls44 4线-10线译码器(余3葛莱码输入)74ls45 bcd-十进制译码器/驱动器74ls46 bcd-七段译码器/驱动器74ls47 bcd-七段译码器/驱动器74ls48 bcd-七段译码器/驱动器74ls49 bcd-七段译码器/驱动器(oc)74ls50 双二路2-2输入与或非门(一门可扩展)74ls51 双二路2-2输入与或非门74ls51 二路3-3输入,二路2-2输入与或非门74ls52 四路2-3-2-2输入与或门(可扩展)74ls53 四路2-2-2-2输入与或非门(可扩展)74ls53 四路2-2-3-2输入与或非门(可扩展)74ls54 四路2-2-2-2输入与或非门74ls54 四路2-3-3-2输入与或非门74ls54 四路2-2-3-2输入与或非门74ls55 二路4-4输入与或非门(可扩展)74ls60 双四输入与扩展74ls61 三3输入与扩展74ls62 四路2-3-3-2输入与或扩展器74ls63 六电流读出接口门74ls64 四路4-2-3-2输入与或非门74ls65 四路4-2-3-2输入与或非门(oc)74ls70 与门输入上升沿jk触发器74ls71 与输入r-s主从触发器74ls72 与门输入主从jk触发器74ls73 双j-k触发器(带清除端)74ls74 正沿触发双d型触发器(带预置端和清除端)74ls75 4位双稳锁存器74ls76 双j-k触发器(带预置端和清除端)74ls77 4位双稳态锁存器74ls78 双j-k触发器(带预置端,公共清除端和公共时钟端) 74ls80 门控全加器74ls81 16位随机存取存储器74ls82 2位二进制全加器(快速进位)74ls83 4位二进制全加器(快速进位)74ls84 16位随机存取存储器74ls85 4位数字比较器74ls86 2输入四异或门74ls87 四位二进制原码/反码/oi单元74ls89 64位读/写存储器74ls90 十进制计数器74ls91 八位移位寄存器74ls92 12分频计数器(2分频和6分频)74ls93 4位二进制计数器74ls94 4位移位寄存器(异步)74ls95 4位移位寄存器(并行io)74ls96 5位移位寄存器74ls97 六位同步二进制比率乘法器74ls100 八位双稳锁存器74ls103 负沿触发双j-k主从触发器(带清除端)74ls106 负沿触发双j-k主从触发器(带预置,清除,时钟) 74ls107 双j-k主从触发器(带清除端)74ls108 双j-k主从触发器(带预置,清除,时钟)74ls109 双j-k触发器(带置位,清除,正触发)74ls110 与门输入j-k主从触发器(带锁定)74ls111 双j-k主从触发器(带数据锁定)74ls112 负沿触发双j-k触发器(带预置端和清除端)74ls113 负沿触发双j-k触发器(带预置端)74ls114 双j-k触发器(带预置端,共清除端和时钟端)74ls116 双四位锁存器74ls120 双脉冲同步器/驱动器74ls121 单稳态触发器(施密特触发)74ls122 可再触发单稳态多谐振荡器(带清除端)74ls123 可再触发双单稳多谐振荡器74ls125 四总线缓冲门(三态输出)74ls126 四总线缓冲门(三态输出)74ls128 2输入四或非线驱动器74ls131 3-8译码器74ls132 2输入四与非门(斯密特触发)74ls133 13输入端与非门74ls134 12输入端与门(三态输出)74ls135 四异或/异或非门74ls136 2输入四异或门(oc)74ls137 八选1锁存译码器/多路转换器74ls138 3-8线译码器/多路转换器74ls139 双2-4线译码器/多路转换器74ls140 双4输入与非线驱动器74ls141 bcd-十进制译码器/驱动器74ls142 计数器/锁存器/译码器/驱动器74ls145 4-10译码器/驱动器74ls147 10线-4线优先编码器74ls148 8线-3线八进制优先编码器74ls150 16选1数据选择器(反补输出)74ls151 8选1数据选择器(互补输出)74ls152 8选1数据选择器多路开关74ls153 双4选1数据选择器/多路选择器74ls154 4线-16线译码器74ls155 双2-4译码器/分配器(图腾柱输出)74ls156 双2-4译码器/分配器(集电极开路输出)74ls157 四2选1数据选择器/多路选择器74ls158 四2选1数据选择器(反相输出)74ls160 可预置bcd计数器(异步清除)74ls161 可预置四位二进制计数器(并清除异步)74ls162 可预置bcd计数器(异步清除)74ls163 可预置四位二进制计数器(并清除异步)74ls164 8位并行输出串行移位寄存器74ls165 并行输入8位移位寄存器(补码输出)74ls166 8位移位寄存器74ls167 同步十进制比率乘法器(录入编辑:电路图网dzdlt) 74ls168 4位加/减同步计数器(十进制)74ls169 同步二进制可逆计数器74ls170 4*4寄存器堆74ls171 四d触发器(带清除端)74ls172 16位寄存器堆74ls173 4位d型寄存器(带清除端)74ls174 六d触发器74ls175 四d触发器74ls176 十进制可预置计数器74ls177 2-8-16进制可预置计数器74ls178 四位通用移位寄存器74ls179 四位通用移位寄存器74ls180 九位奇偶产生/校验器74ls181 算术逻辑单元/功能发生器74ls182 先行进位发生器74ls183 双保留进位全加器74ls184 bcd-二进制转换器74ls185 二进制-bcd转换器74ls190 同步可逆计数器(bcd,二进制)74ls191 同步可逆计数器(bcd,二进制)74ls192 同步可逆计数器(bcd,二进制)74ls193 同步可逆计数器(bcd,二进制)74ls194 四位双向通用移位寄存器74ls195 四位通用移位寄存器74ls196 可预置计数器/锁存器74ls197 可预置计数器/锁存器(二进制)74ls198 八位双向移位寄存器74ls199 八位移位寄存器74ls210 2-5-10进制计数器74ls213 2-n-10可变进制计数器74ls221 双单稳触发器74ls230 八3态总线驱动器74ls231 八3态总线反向驱动器74ls240 八缓冲器/线驱动器/线接收器(反码三态输出) 74ls241 八缓冲器/线驱动器/线接收器(原码三态输出) 74ls242 八缓冲器/线驱动器/线接收器74ls243 4同相三态总线收发器74ls244 八缓冲器/线驱动器/线接收器74ls245 八双向总线收发器74ls246 4线-七段译码/驱动器(30v)74ls247 4线-七段译码/驱动器(15v)74ls248 4线-七段译码/驱动器74ls249 4线-七段译码/驱动器74ls251 8选1数据选择器(三态输出)74ls253 双四选1数据选择器(三态输出)74ls256 双四位可寻址锁存器74ls257 四2选1数据选择器(三态输出)74ls258 四2选1数据选择器(反码三态输出)74ls259 8为可寻址锁存器74ls260 双5输入或非门74ls261 4*2并行二进制乘法器74ls265 四互补输出元件74ls266 2输入四异或非门(oc)74ls270 2048位rom (512位四字节,oc)74ls271 2048位rom (256位八字节,oc)74ls273 八d触发器74ls274 4*4并行二进制乘法器74ls275 七位片式华莱士树乘法器74ls276 四jk触发器74ls278 四位可级联优先寄存器74ls279 四s-r锁存器74ls280 9位奇数/偶数奇偶发生器/较验器74ls28174ls283 4位二进制全加器74ls290 十进制计数器74ls291 32位可编程模74ls293 4位二进制计数器74ls294 16位可编程模74ls295 四位双向通用移位寄存器74ls298 四-2输入多路转换器(带选通)74ls299 八位通用移位寄存器(三态输出)74ls348 8-3线优先编码器(三态输出)74ls352 双四选1数据选择器/多路转换器74ls353 双4-1线数据选择器(三态输出)74ls354 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls355 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls356 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls357 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls365 6总线驱动器74ls366 六反向三态缓冲器/线驱动器74ls367 六同向三态缓冲器/线驱动器74ls368 六反向三态缓冲器/线驱动器74ls373 八d锁存器74ls374 八d触发器(三态同相)74ls375 4位双稳态锁存器74ls377 带使能的八d触发器74ls378 六d触发器74ls379 四d触发器74ls381 算术逻辑单元/函数发生器74ls382 算术逻辑单元/函数发生器74ls384 8位*1位补码乘法器74ls385 四串行加法器/乘法器74ls386 2输入四异或门74ls390 双十进制计数器74ls391 双四位二进制计数器74ls395 4位通用移位寄存器74ls396 八位存储寄存器74ls398 四2输入端多路开关(双路输出)74ls399 四-2输入多路转换器(带选通)74ls422 单稳态触发器74ls423 双单稳态触发器74ls440 四3方向总线收发器,集电极开路74ls441 四3方向总线收发器,集电极开路74ls442 四3方向总线收发器,三态输出74ls443 四3方向总线收发器,三态输出74ls444 四3方向总线收发器,三态输出74ls445 bcd-十进制译码器/驱动器,三态输出74ls446 有方向控制的双总线收发器74ls448 四3方向总线收发器,三态输出74ls449 有方向控制的双总线收发器74ls465 八三态线缓冲器74ls466 八三态线反向缓冲器74ls467 八三态线缓冲器74ls468 八三态线反向缓冲器74ls490 双十进制计数器74ls540 八位三态总线缓冲器(反向)74ls541 八位三态总线缓冲器74ls589 有输入锁存的并入串出移位寄存器74ls590 带输出寄存器的8位二进制计数器74ls591 带输出寄存器的8位二进制计数器74ls592 带输出寄存器的8位二进制计数器74ls593 带输出寄存器的8位二进制计数器74ls594 带输出锁存的8位串入并出移位寄存器74ls595 8位输出锁存移位寄存器74ls596 带输出锁存的8位串入并出移位寄存器74ls597 8位输出锁存移位寄存器74ls598 带输入锁存的并入串出移位寄存器74ls599 带输出锁存的8位串入并出移位寄存器74ls604 双8位锁存器74ls605 双8位锁存器74ls606 双8位锁存器74ls607 双8位锁存器74ls620 8位三态总线发送接收器(反相)74ls621 8位总线收发器74ls622 8位总线收发器74ls623 8位总线收发器74ls640 反相总线收发器(三态输出)74ls641 同相8总线收发器,集电极开路74ls642 同相8总线收发器,集电极开路74ls643 8位三态总线发送接收器74ls644 真值反相8总线收发器,集电极开路74ls645 三态同相8总线收发器74ls646 八位总线收发器,寄存器74ls647 八位总线收发器,寄存器74ls648 八位总线收发器,寄存器74ls649 八位总线收发器,寄存器74ls651 三态反相8总线收发器(录入编辑:电路图网dzdlt) 74ls652 三态反相8总线收发器74ls653 反相8总线收发器,集电极开路74ls654 同相8总线收发器,集电极开路74ls668 4位同步加/减十进制计数器74ls669 带先行进位的4位同步二进制可逆计数器74ls670 4*4寄存器堆(三态)74ls671 带输出寄存的四位并入并出移位寄存器74ls672 带输出寄存的四位并入并出移位寄存器74ls673 16位并行输出存储器,16位串入串出移位寄存器74ls674 16位并行输入串行输出移位寄存器74ls681 4位并行二进制累加器74ls682 8位数值比较器(图腾柱输出)74ls683 8位数值比较器(集电极开路)74ls684 8位数值比较器(图腾柱输出)74ls685 8位数值比较器(集电极开路)74ls686 8位数值比较器(图腾柱输出)74ls687 8位数值比较器(集电极开路)74ls688 8位数字比较器(oc输出)74ls689 8位数字比较器74ls690 同步十进制计数器/寄存器(带数选,三态输出,直接清除)74ls691 计数器/寄存器(带多转换,三态输出)74ls692 同步十进制计数器(带预置输入,同步清除)74ls693 计数器/寄存器(带多转换,三态输出)74ls696 同步加/减十进制计数器/寄存器(带数选,三态输出,直接清除) 74ls697 计数器/寄存器(带多转换,三态输出)74ls698 计数器/寄存器(带多转换,三态输出)74ls699 计数器/寄存器(带多转换,三态输出)74ls716 可编程模n十进制计数器74ls718 可编程模n十进制计数器CD4001 4二输入或非门CD4002 双4输入或非门CD4006 18位静态移位寄存器CD4007 双互补对加反相器CD4009 六缓冲器/转换-倒相CD4010 六缓冲器/转换-正相CD4011 四2输入与非门CD4012 双4输入与非门CD4013 置/复位双D型触发器CD4014 8位静态同步移位寄存CD4015 双4位静态移位寄存器CD4016 四双向模拟数字开关CD4017 10译码输出十进制计数器CD4018 可预置1/N计数器CD4019 四与或选择门CD4020 14位二进制计数器CD4021 8位静态移位寄存器CD4022 8译码输出8进制计数器CD4023 三3输入与非门CD4024 7位二进制脉冲计数器CD4025 三3输入与非门CD4026 十进制/7段译码/驱动CD4027 置位/复位主从触发器CD4028 BCD十进制译码器CD4029 4位可预置可逆计数器CD4030 四异或门CD4031 64位静态移位寄存器CD4032 三串行加法器CD4033 十进制计数器/7段显示CD4034 8位静态移位寄存器CD4035 4位并入/并出移位寄存器CD4038 3位串行加法器CD4040 12位二进制计数器CD4041 四原码/补码缓冲器CD4042 四时钟D型锁存器CD4043 四或非R/S锁存器CD4044 四与非R/S锁存器CD4046 锁相环CD4047 单非稳态多谐振荡器CD4048 可扩充八输入门CD4049 六反相缓冲/转换器CD4050 六正相缓冲/转换器CD4051 单8通道多路转换/分配CD4052 双4通道多路转换/分配CD4053 三2通道多路转换/分配CD4056 7段液晶显示译码/驱动CD4060 二进制计数/分频/振荡CD4063 四位数值比较器CD4066 四双相模拟开管CD4067 16选1模拟开关CD4068 8输入端与非/与门CD4069 六反相器CD4070 四异或门CD4071 四2输入或门CD4072 双四输入或门CD4073 三3输入与门CD4075 三3输入与门CD4076 4位D型寄存器CD4077 四异或非门CD4078 八输入或/或非门CD4081 四输入与门CD4082 双4输入与门CD4085 双2组2输入与或非门CD4086 可扩展2输入与或非门CD4093 四与非斯密特触发器CD4094 8位移位/贮存总线寄存CD4096 3输入J-K触发器CD4098 双单稳态触发器CD4099 8位可寻址锁存器CD40103 同步可预置减法器CD40106 六斯密特触发器CD40107 双2输入与非缓冲/驱动CD40110 计数/译码/锁存/驱动CD40174 6D触发器CD40175 4D触发器CD40192 BCD可预置可逆计数器CD40193 二进制可预置可逆计数器CD40194 4位双相移位寄存器。

数字电子技术实验指导书(B5)

第一章 数字电子技术基础实验1.1 实验设备认识及门电路功能测试一、实验目的1. 熟悉万用表及电子技术综合实验平台的使用方法;2. 掌握门电路逻辑功能测试方法;3. 了解TTL 器件和CMOS 器件的使用注意事项。

二、实验原理门电路的逻辑功能。

三、实验设备与器件1. 电子技术综合实验平台 一台2. 万用表 一块3. 器件(1) 74LS02 一片(四二输入或非门) (2) 74HC86 一片(四二输入异或门)(3) 74LS03 一片(四二输入与非门(OC)) (4) 74LS00 一片(四二输入与非门)四、实验内容和步骤1. 测试74LS02和74HC86的逻辑功能。

注意CMOS 电路的多余输入端不得悬空,应按需要接成相应的高低电平。

表中V O 为不加负载时的电压,即开路输出电压。

2.OC 门上拉电阻计算及逻辑功能测试 2.1 OC 门上拉电阻的计算OC 门输出端可以并联连接,即OC 门可以实现“线与”逻辑,但必须接一个合适的上拉电阻R L ,计算方法如下:式中:m — 负载门总输入端数 n — OC 门并联的个数 m ' — 负载门个数 I OH — OC 门输出管截止时的漏电流(对于74LS03按I OH =50μA 计算)I LM — OC 门输出管导通时允许的最大灌电流(按V OL ≤0.3V,I LM ≤7.8mA 估算)CC OHL(max)OH IHV V R nI mI -=+CC OL L(min)LM IL V V R I m I -='-I IH — 负载门每个输入端的高电平输入电流(对于74LS00按I IH =0.01 A) I IL — 每个负载门的低电平输入电流(对于74LS00按I IL =-0.25mA 估算) V CC — 电源电压(5V) V OH — 输出高电平(按3V 估算) V OL — 输出低电平(按0.3V 估算)图1.1-12.2 OC 门“线与”应用将各OC 门输入端A 、B 和C 分别接逻辑开关;Z 、Y 1和Y 2分别接LED 指示灯,连接电路图如图1.1-1所示。

74HC系列功能简介

双J—K正沿触发器

74HC123

双可再触发单稳多谐振荡器

74HC125

四总线缓冲门(三态)

74HC126

四总线缓冲门(三态)

3—8线译码器/多路转换器

74HC139

双2—4线译码器/多路转换器

74HC145

BCD—十进制译码器/驱动器

74HC147

10—4线BCD优先编码器

74HC148

8选1数据选择器

74HC151

双4选1数据选择器

74HC153

4—16线多路分配器

74HC154

4—16线多路分配器

74HC155

双2—4线多路分配器

74hc系列功能简介功能双4选1数据选择器三态四2选1数据选择器三态8位可寻址锁存器四2输入异或非门oc八d型触发器带清除端四rs锁存器9位奇偶数产生器校验器4位二进制全加器带超前进位4位2选1数据选择器六缓冲器总线驱动同相六缓冲器总线驱动反相六缓冲器总线驱动同相六缓冲器总线驱动反相八d触发器三态八d触发器三态八d触发器四2输入异或门双4位十进制计数器双4位二进制计数器异步清除八缓冲器总线驱动器八缓冲器总线驱动器八d锁存器三态八d锁存器三态8位输入锁存输出移位寄存器8位输出锁存移位寄存器8位数值比较器等值检测器从4输入或非门双4位串入并出移位寄存器十进制计数器分配器12位二进制串行计数器锁相环六缓冲器电平变换器反相六缓冲器电平变换器同相单8通道模拟开关双4通道摸拟开关三2通道模拟开关14位二进制串行计数器四双向模拟开关双二进制加法计数器型号74hc25374hc25774hc25974hc26674hc27374hc27974hc28074hc28374hc29874hc36574hc36674hc36774hc36874hc37374hc37474hc37774hc38674hc39074hc39374hc54074hc54174hc57374hc57474hc58974hc59574hc68874hc400274hc401574hc401774hc404074hc404674hc404974hc405074hc405174hc405274hc405374hc406074hc406674hc452074hc453874hc454374hc455174hc13274hc13874hc13974hc14574hc14774hc14874hc15174hc15374hc15474hc15574hc15674hc15774hc15874hc16074hc16174hc16274hc16374hc16474hc16574hc16674hc17374hc17474hc17574hc18174hc18274hc19074hc19174hc19274hc19374hc19474hc19574hc22174hc23774hc23874hc24074hc24174hc24274hc24374hc244双精密单稳态触发器7段锁存译码驱动器四2通道模拟开关四2输入与非施密特触发器38线译码器多路转换器双24线译码器多路转换器bcd十进

74hc芯片

74hc芯片74hc芯片是一种常见的数字集成电路芯片,其名称中的74表示“批线”,hc表示“高速CMOS”。

它是基于高速串行CMOS技术制造的数字逻辑芯片,具有高速、低功耗、可靠性高等特点,广泛应用于数字电路设计中。

74hc芯片采用的是CMOS技术,即互补金属氧化物半导体技术。

CMOS技术的特点是电路功耗低、抗干扰能力强、集成度高。

通过CMOS技术的应用,74hc芯片在功能上比较丰富,并且具有很高的可靠性,适用于各种数字电路设计需求。

74hc芯片的引脚数目有多种不同的封装,如DIP、SOP、TSSOP等。

常用的有14引脚、16引脚、20引脚等,不同封装的芯片可以满足不同的应用需求。

74hc芯片提供了许多不同的逻辑功能,如与门、或门、非门、异或门等。

这些逻辑门可以根据不同的输入信号给出相应的输出信号,实现各种数字电路的功能。

74hc芯片的工作电压通常为2V至6V之间,具有较高的抗电源噪声能力和抗振荡能力。

其输入电压逻辑高电平范围为2V至6V,逻辑低电平范围为0V至1V。

输出电压逻辑高电平范围为2.4V至6V,逻辑低电平范围为0V至0.4V。

74hc芯片在数字电路设计中应用广泛。

它可以用于逻辑门电路的设计和实现,如与门、或门、非门等。

它也可以用于时序电路的设计和实现,如时钟电路、计数器电路等。

此外,74hc芯片还可以用于存储器电路的设计和实现,如触发器、巨与门等。

总之,74hc芯片是一种基于高速串行CMOS技术制造的数字集成电路芯片,具有高速、低功耗、可靠性高等特点。

它在数字电路设计中有广泛的应用,可以实现各种逻辑、时序和存储器电路的功能。

74HC系列名词解释

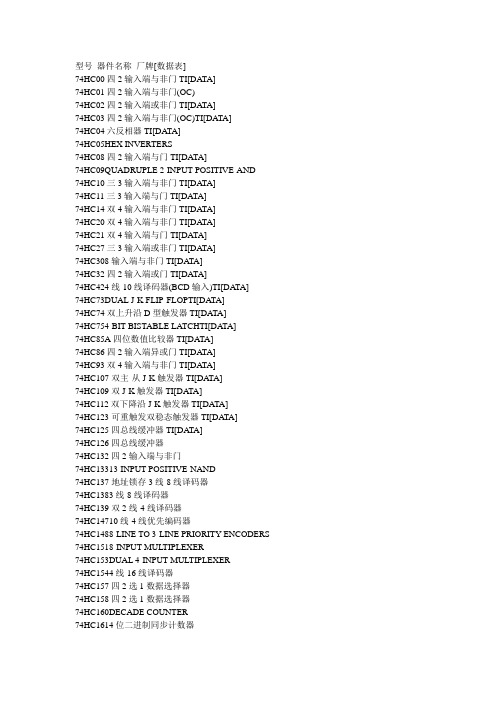

型号器件名称厂牌[数据表]74HC00四2输入端与非门TI[DA TA]74HC01四2输入端与非门(OC)74HC02四2输入端或非门TI[DA TA]74HC03四2输入端与非门(OC)TI[DATA]74HC04六反相器TI[DA TA]74HC05HEX INVERTERS74HC08四2输入端与门TI[DATA]74HC09QUADRUPLE 2-INPUT POSITIVE-AND 74HC10三3输入端与非门TI[DA TA]74HC11三3输入端与门TI[DATA]74HC14双4输入端与非门TI[DA TA]74HC20双4输入端与非门TI[DA TA]74HC21双4输入端与门TI[DATA]74HC27三3输入端或非门TI[DA TA]74HC308输入端与非门TI[DA TA]74HC32四2输入端或门TI[DATA]74HC424线-10线译码器(BCD输入)TI[DATA]74HC73DUAL J-K FLIP-FLOPTI[DATA]74HC74双上升沿D型触发器TI[DATA]74HC754-BIT BISTABLE LATCHTI[DA TA]74HC85A四位数值比较器TI[DATA]74HC86四2输入端异或门TI[DA TA]74HC93双4输入端与非门TI[DA TA]74HC107双主-从J-K触发器TI[DA TA]74HC109双J-K触发器TI[DA TA]74HC112双下降沿J-K触发器TI[DATA]74HC123可重触发双稳态触发器TI[DA TA]74HC125四总线缓冲器TI[DA TA]74HC126四总线缓冲器74HC132四2输入端与非门74HC13313-INPUT POSITIVE-NAND74HC137地址锁存3线-8线译码器74HC1383线-8线译码器74HC139双2线-4线译码器74HC14710线-4线优先编码器74HC1488-LINE TO 3-LINE PRIORITY ENCODERS 74HC1518-INPUT MULTIPLEXER74HC153DUAL 4-INPUT MULTIPLEXER74HC1544线-16线译码器74HC157四2选1数据选择器74HC158四2选1数据选择器74HC160DECADE COUNTER74HC1614位二进制同步计数器74HC162DECADE COUNTER74HC1634-BIT BINARY PRESETTABLE COUNTER 74HC1648位移位寄存器74HC1658位并行输入/串行输出寄存器74HC1668位并行输入/串行输出移位寄存器TI,PHI 74HC1734位D型寄存器TI74HC174HEX D-TYPE FLIP-FLOP WITH RESETTI 74HC175四上升沿D型触发器TI74HC190十进制同步加/减计数器TI74HC1914位二进制同步加/减计数器TI74HC192BCD二进制同步加/减计数器TI74HC193可预置4位二进制加/减计数器TI74HC1944位并入/串入-并出/串出移位寄存TI74HC1954位移位寄存器TI74HC221双单稳态触器TI74HC2373-8线译码器(带地址锁存)TI74HC2383-8线译码器TI74HC239双2-4线译码器74HC240八反相缓冲/线驱动/线接收器TI74HC241八缓冲/线驱动/线接收器TI74HC243四总线收发器TI74HC244八缓冲/线驱动/线接收器TI,FSC74HC245八双向总线发送/接发器TI,FSC74HC2518选1数据选择器74HC253双4选1数据选择器74HC257四2选1数据选择器74HC258四2选1数据选择器74HC2598位可寻址锁存器74HC266QUADRUPLE 2-INPUT EXCLUSIVE-NOR 74HC273八D触发器74HC2809位奇偶产生器/校验器TI74HC2834位二进制超位全加器74HC297DIGITAL PHASE-LOCKED-LOOP74HC2998位双向通用移位/存储寄存器74HC354带锁存三态8-1多路转换开关74HC365六总线驱动器74HC366六反相总线驱动器74HC367六总线驱动器74HC368六反相总线驱动器74HC373六D型锁存器74HC374六上升沿D型触发器74HC3754-BIT BISTABLE LATCH74HC377六上升沿D型触发器74HC3786-BIT D-TYPE FLIP-FLOP74HC379QUADRUPLE D-TYPE FLIP-FLOP74HC390双十进制计数器74HC393双4位二进制计数器74HC4002高速CMOS双4输入端或非门74HC4015高速CMOS双4位串入/并出移位寄存器74HC4016高速CMOS四传输门74HC4017高速CMOS十进制计数/分配器74HC4020高速CMOS14级串行二进制计数/分频器74HC4024高速CMOS7级二进制串行计数/分频器74HC4040高速CMOS12级二进制串行计数/分频器74HC4046A高速CMOS锁相环74HC4049高速CMOS六反相缓冲/变换器74HC4050高速CMOS六同相缓冲/变换器74HC4051高速CMOS八选一模拟开关74HC4052高速CMOS双4选1模拟开关74HC4053高速CMOS三组二路模拟开关74HC4059高速CMOS“N”分频计数器74HC4060高速CMOS14级二进制串行计数/分频器74HC406114-STAGE BINARY COUNTER/OSCILLATOR 74HC4066高速CMOS四传输门74HC4067高速CMOS16选1模拟开关74HC4075高速CMOS三3输入端或门74HC4078A8-INPUT OR/NOR74HC4094高速CMOS8位移位存储总线寄存器74HC40103高速CMOS8位可预置同步二进制减法计数器74HC40105高速CMOS先入先出FI-FD寄存器74HC423 双单稳态振荡器TI[DA TA]74HC4316高速CMOS四模拟开关TI74HC4351ANALOG MULTIPLEXER/DEMULTIPLEXERTI 74HC4352ANALOG MULTIPLEXER/DEMULTIPLEXERTI 74HC4511高速CMOSBCD锁存,7段译码,驱动器74HC4514高速CMOS4位锁存,4线-16线译码器74HC4515高速CMOS4位锁存,4线-16线译码器74HC4518高速CMOS双BCD同步加计数器74HC4520高速CMOS双4位二进制同步加计数器74HC4538高速CMOS精密双单稳TI,INT(HAR)74HC533三态八D锁存器74HC534三态八D锁存器74HC540八路三态收发缓冲器(反相)74HC541八路三态收发缓冲器(同相)74HC563三态八D锁存器74HC564三态八D锁存器74HC573四3选1数据选择器74HC574双4选1数据选择器74HC590A8位二进制计数器TI74HC5948位移位寄存器TI74HC5958位移位三态寄存器TI,ST[DATA],FSC,PHI 74HC5978位移位寄存器74HC651OCTAL BUS TRANSCEIVER/REGISTERTI 74HC652OCTAL BUS TRANSCEIVER/REGISTERTI 74HC664OCTAL BUS TRANSCEIVERTI74HC665OCTAL BUS TRANSCEIVERTI74HC6704-BY-4 REGISTER FILE74HC6828-BIT MAGNITUDE COMPARA TORS74HC6848-BIT MAGNITUDE COMPARA TORSTI74HC6888-BIT MAGNITUDE COMPARA TOR74HC7001QUADRUPLE POSITIVE-ANDTI74HC7002QUADRUPLE POSITIVE-NORTI74HC7032QUADRUPLE POSITIVE-ORTI74HC70746-SECTION MULTIFUNCTION CIRCUITTI 74HC7046A压控锁相环74HC7266QUAD 2-INPUT EXCLUSIVE-NOR GATE 74HCU04HEX INVERTERTI74HC4543高速CMOSBCD七段锁存译码,驱动器74HC47248-BIT ADDRESSABLE LATCHES74HC623OCTAL BUS TRANSCEIVERTI74HC640OCTAL BUS TRANSCEIVER74HC643OCTAL BUS TRANSCEIVERTI74HC645OCTAL BUS TRANSCEIVERTI74HC646OCTAL BUS TRANSCEIVER/REGISTER74HC648OCTAL BUS TRANSCEIVER/REGISTERTI。

74HC系列芯片型号与功能介绍

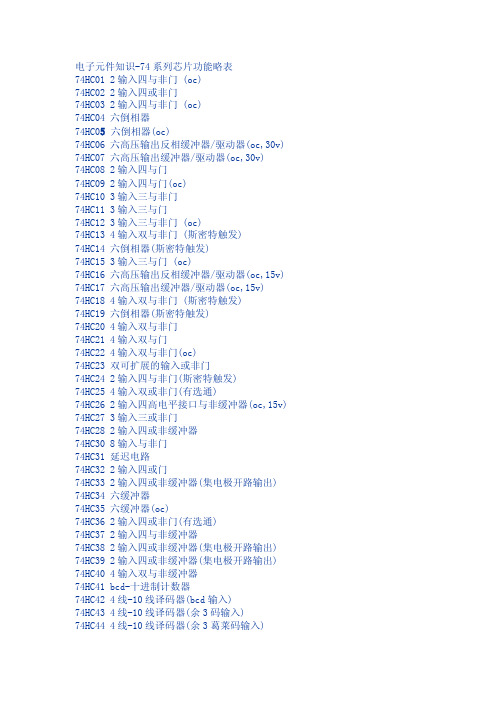

电子元件知识-74系列芯片功能略表74HC01 2输入四与非门 (oc)74HC02 2输入四或非门74HC03 2输入四与非门 (oc)74HC04 六倒相器74HC05六倒相器(oc)74HC06 六高压输出反相缓冲器/驱动器(oc,30v) 74HC07 六高压输出缓冲器/驱动器(oc,30v)74HC08 2输入四与门74HC09 2输入四与门(oc)74HC10 3输入三与非门74HC11 3输入三与门74HC12 3输入三与非门 (oc)74HC13 4输入双与非门 (斯密特触发)74HC14 六倒相器(斯密特触发)74HC15 3输入三与门 (oc)74HC16 六高压输出反相缓冲器/驱动器(oc,15v) 74HC17 六高压输出缓冲器/驱动器(oc,15v)74HC18 4输入双与非门 (斯密特触发)74HC19 六倒相器(斯密特触发)74HC20 4输入双与非门74HC21 4输入双与门74HC22 4输入双与非门(oc)74HC23 双可扩展的输入或非门74HC24 2输入四与非门(斯密特触发)74HC25 4输入双或非门(有选通)74HC26 2输入四高电平接口与非缓冲器(oc,15v) 74HC27 3输入三或非门74HC28 2输入四或非缓冲器74HC30 8输入与非门74HC31 延迟电路74HC32 2输入四或门74HC33 2输入四或非缓冲器(集电极开路输出) 74HC34 六缓冲器74HC35 六缓冲器(oc)74HC36 2输入四或非门(有选通)74HC37 2输入四与非缓冲器74HC38 2输入四或非缓冲器(集电极开路输出) 74HC39 2输入四或非缓冲器(集电极开路输出) 74HC40 4输入双与非缓冲器74HC41 bcd-十进制计数器74HC42 4线-10线译码器(bcd输入)74HC43 4线-10线译码器(余3码输入)74HC44 4线-10线译码器(余3葛莱码输入)74HC45 bcd-十进制译码器/驱动器74HC46 bcd-七段译码器/驱动器74HC47 bcd-七段译码器/驱动器74HC48 bcd-七段译码器/驱动器74HC49 bcd-七段译码器/驱动器(oc)74HC50 双二路2-2输入与或非门(一门可扩展)74HC51 双二路2-2输入与或非门74HC51 二路3-3输入,二路2-2输入与或非门74HC52 四路2-3-2-2输入与或门(可扩展)74HC53 四路2-2-2-2输入与或非门(可扩展)74HC53 四路2-2-3-2输入与或非门(可扩展)74HC54 四路2-2-2-2输入与或非门74HC54 四路2-3-3-2输入与或非门74HC54 四路2-2-3-2输入与或非门74HC55 二路4-4输入与或非门(可扩展)74HC60 双四输入与扩展74HC61 三3输入与扩展74HC62 四路2-3-3-2输入与或扩展器74HC63 六电流读出接口门74HC64 四路4-2-3-2输入与或非门74HC65 四路4-2-3-2输入与或非门(oc)74HC70 与门输入上升沿jk触发器74HC71 与输入r-s主从触发器74HC72 与门输入主从jk触发器74HC73 双j-k触发器(带清除端)74HC74 正沿触发双d型触发器(带预置端和清除端)74HC75 4位双稳锁存器74HC76 双j-k触发器(带预置端和清除端)74HC77 4位双稳态锁存器74HC78 双j-k触发器(带预置端,公共清除端和公共时钟端) 74HC80 门控全加器74HC81 16位随机存取存储器74HC82 2位二进制全加器(快速进位)74HC83 4位二进制全加器(快速进位)74HC84 16位随机存取存储器74HC85 4位数字比较器74HC86 2输入四异或门74HC87 四位二进制原码/反码/oi单元74HC89 64位读/写存储器74HC90 十进制计数器74HC91 八位移位寄存器74HC92 12分频计数器(2分频和6分频)74HC93 4位二进制计数器74HC94 4位移位寄存器(异步)74HC95 4位移位寄存器(并行io)74HC96 5位移位寄存器74HC97 六位同步二进制比率乘法器74HC100 八位双稳锁存器74HC103 负沿触发双j-k主从触发器(带清除端)74HC106 负沿触发双j-k主从触发器(带预置,清除,时钟) 74HC107 双j-k主从触发器(带清除端)74HC108 双j-k主从触发器(带预置,清除,时钟)74HC109 双j-k触发器(带置位,清除,正触发)74HC110 与门输入j-k主从触发器(带锁定)74HC111 双j-k主从触发器(带数据锁定)74HC112 负沿触发双j-k触发器(带预置端和清除端)74HC113 负沿触发双j-k触发器(带预置端)74HC114 双j-k触发器(带预置端,共清除端和时钟端)74HC116 双四位锁存器74HC120 双脉冲同步器/驱动器74HC121 单稳态触发器(施密特触发)74HC122 可再触发单稳态多谐振荡器(带清除端)74HC123 可再触发双单稳多谐振荡器74HC125 四总线缓冲门(三态输出)74HC126 四总线缓冲门(三态输出)74HC128 2输入四或非线驱动器74HC131 3-8译码器74HC132 2输入四与非门(斯密特触发)74HC133 13输入端与非门74HC134 12输入端与门(三态输出)74HC135 四异或/异或非门74HC136 2输入四异或门(oc)74HC137 八选1锁存译码器/多路转换器74HC138 3-8线译码器/多路转换器74HC139 双2-4线译码器/多路转换器74HC140 双4输入与非线驱动器74HC141 bcd-十进制译码器/驱动器74HC142 计数器/锁存器/译码器/驱动器74HC145 4-10译码器/驱动器74HC147 10线-4线优先编码器74HC148 8线-3线八进制优先编码器74HC150 16选1数据选择器(反补输出)74HC151 8选1数据选择器(互补输出)74HC152 8选1数据选择器多路开关74HC153 双4选1数据选择器/多路选择器74HC154 4线-16线译码器74HC155 双2-4译码器/分配器(图腾柱输出)74HC156 双2-4译码器/分配器(集电极开路输出)74HC157 四2选1数据选择器/多路选择器74HC158 四2选1数据选择器(反相输出)74HC160 可预置bcd计数器(异步清除)74HC161 可预置四位二进制计数器(并清除异步)74HC162 可预置bcd计数器(异步清除)74HC163 可预置四位二进制计数器(并清除异步)74HC164 8位并行输出串行移位寄存器74HC165 并行输入8位移位寄存器(补码输出)74HC166 8位移位寄存器74HC167 同步十进制比率乘法器74HC168 4位加/减同步计数器(十进制)74HC169 同步二进制可逆计数器74HC170 4*4寄存器堆74HC171 四d触发器(带清除端)74HC172 16位寄存器堆74HC173 4位d型寄存器(带清除端)74HC174 六d触发器74HC175 四d触发器74HC176 十进制可预置计数器74HC177 2-8-16进制可预置计数器74HC178 四位通用移位寄存器74HC179 四位通用移位寄存器74HC180 九位奇偶产生/校验器74HC181 算术逻辑单元/功能发生器74HC182 先行进位发生器74HC183 双保留进位全加器74HC184 bcd-二进制转换器74HC185 二进制-bcd转换器74HC190 同步可逆计数器(bcd,二进制)74HC191 同步可逆计数器(bcd,二进制)74HC192 同步可逆计数器(bcd,二进制)74HC193 同步可逆计数器(bcd,二进制)74HC199 八位移位寄存器74HC210 2-5-10进制计数器74HC213 2-n-10可变进制计数器74HC221 双单稳触发器74HC230 八3态总线驱动器74HC231 八3态总线反向驱动器74HC240 八缓冲器/线驱动器/线接收器(反码三态输出) 74HC241 八缓冲器/线驱动器/线接收器(原码三态输出) 74HC242 八缓冲器/线驱动器/线接收器74HC243 4同相三态总线收发器74HC244 八缓冲器/线驱动器/线接收器74HC245 八双向总线收发器74HC246 4线-七段译码/驱动器(30v)74HC247 4线-七段译码/驱动器(15v)74HC248 4线-七段译码/驱动器74HC249 4线-七段译码/驱动器74HC251 8选1数据选择器(三态输出)74HC253 双四选1数据选择器(三态输出)74HC256 双四位可寻址锁存器74HC257 四2选1数据选择器(三态输出)74HC258 四2选1数据选择器(反码三态输出)74HC259 8为可寻址锁存器74HC260 双5输入或非门74HC261 4*2并行二进制乘法器74HC265 四互补输出元件74HC266 2输入四异或非门(oc)74HC270 2048位rom (512位四字节,oc)74HC271 2048位rom (256位八字节,oc)74HC273 八d触发器74HC274 4*4并行二进制乘法器74HC275 七位片式华莱士树乘法器74HC276 四jk触发器74HC278 四位可级联优先寄存器74HC279 四s-r锁存器74HC280 9位奇数/偶数奇偶发生器/较验器74HC28174HC283 4位二进制全加器74HC290 十进制计数器74HC291 32位可编程模74HC293 4位二进制计数器74HC294 16位可编程模74HC295 四位双向通用移位寄存器74HC298 四-2输入多路转换器(带选通)74HC299 八位通用移位寄存器(三态输出)74HC348 8-3线优先编码器(三态输出)74HC352 双四选1数据选择器/多路转换器74HC353 双4-1线数据选择器(三态输出)74HC354 8输入端多路转换器/数据选择器/寄存器,三态补码输出74HC355 8输入端多路转换器/数据选择器/寄存器,三态补码输出74HC356 8输入端多路转换器/数据选择器/寄存器,三态补码输出74HC357 8输入端多路转换器/数据选择器/寄存器,三态补码输出74HC365 6总线驱动器74HC366 六反向三态缓冲器/线驱动器74HC367 六同向三态缓冲器/线驱动器74HC368 六反向三态缓冲器/线驱动器74HC373 八d锁存器74HC374 八d触发器(三态同相)74HC375 4位双稳态锁存器74HC377 带使能的八d触发器74HC378 六d触发器74HC379 四d触发器74HC381 算术逻辑单元/函数发生器74HC382 算术逻辑单元/函数发生器74HC384 8位*1位补码乘法器74HC385 四串行加法器/乘法器74HC386 2输入四异或门74HC390 双十进制计数器74HC391 双四位二进制计数器74HC395 4位通用移位寄存器74HC396 八位存储寄存器74HC398 四2输入端多路开关(双路输出)74HC399 四-2输入多路转换器(带选通)74HC422 单稳态触发器74HC423 双单稳态触发器74HC440 四3方向总线收发器,集电极开路74HC441 四3方向总线收发器,集电极开路74HC442 四3方向总线收发器,三态输出74HC443 四3方向总线收发器,三态输出74HC444 四3方向总线收发器,三态输出74HC445 bcd-十进制译码器/驱动器,三态输出74HC446 有方向控制的双总线收发器74HC448 四3方向总线收发器,三态输出74HC449 有方向控制的双总线收发器74HC465 八三态线缓冲器74HC466 八三态线反向缓冲器74HC467 八三态线缓冲器74HC468 八三态线反向缓冲器74HC490 双十进制计数器74HC540 八位三态总线缓冲器(反向)74HC541 八位三态总线缓冲器74HC589 有输入锁存的并入串出移位寄存器74HC590 带输出寄存器的8位二进制计数器74HC591 带输出寄存器的8位二进制计数器74HC592 带输出寄存器的8位二进制计数器74HC593 带输出寄存器的8位二进制计数器74HC594 带输出锁存的8位串入并出移位寄存器74HC595 8位输出锁存移位寄存器74HC596 带输出锁存的8位串入并出移位寄存器74HC597 8位输出锁存移位寄存器74HC598 带输入锁存的并入串出移位寄存器74HC599 带输出锁存的8位串入并出移位寄存器74HC604 双8位锁存器74HC605 双8位锁存器74HC606 双8位锁存器74HC607 双8位锁存器74HC620 8位三态总线发送接收器(反相)74HC621 8位总线收发器74HC622 8位总线收发器74HC623 8位总线收发器74HC640 反相总线收发器(三态输出)74HC641 同相8总线收发器,集电极开路74HC642 同相8总线收发器,集电极开路74HC643 8位三态总线发送接收器74HC644 真值反相8总线收发器,集电极开路74HC645 三态同相8总线收发器74HC646 八位总线收发器,寄存器74HC647 八位总线收发器,寄存器74HC648 八位总线收发器,寄存器74HC649 八位总线收发器,寄存器74HC651 三态反相8总线收发器74HC652 三态反相8总线收发器74HC653 反相8总线收发器,集电极开路74HC654 同相8总线收发器,集电极开路74HC668 4位同步加/减十进制计数器74HC669 带先行进位的4位同步二进制可逆计数器74HC670 4*4寄存器堆(三态)74HC671 带输出寄存的四位并入并出移位寄存器74HC672 带输出寄存的四位并入并出移位寄存器74HC673 16位并行输出存储器,16位串入串出移位寄存器74HC674 16位并行输入串行输出移位寄存器74HC681 4位并行二进制累加器74HC682 8位数值比较器(图腾柱输出)74HC683 8位数值比较器(集电极开路)74HC684 8位数值比较器(图腾柱输出)74HC685 8位数值比较器(集电极开路)74HC686 8位数值比较器(图腾柱输出)74HC687 8位数值比较器(集电极开路)74HC688 8位数字比较器(oc输出)74HC689 8位数字比较器74HC690 同步十进制计数器/寄存器(带数选,三态输出,直接清除。

74hc系列芯片

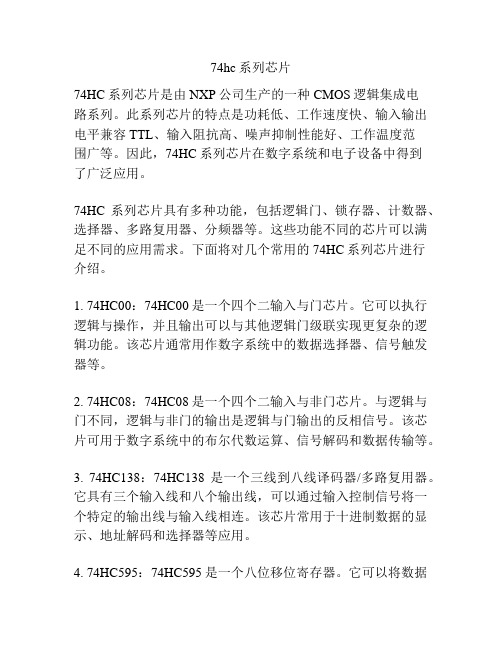

74hc系列芯片74HC系列芯片是由NXP公司生产的一种CMOS逻辑集成电路系列。

此系列芯片的特点是功耗低、工作速度快、输入输出电平兼容TTL、输入阻抗高、噪声抑制性能好、工作温度范围广等。

因此,74HC系列芯片在数字系统和电子设备中得到了广泛应用。

74HC系列芯片具有多种功能,包括逻辑门、锁存器、计数器、选择器、多路复用器、分频器等。

这些功能不同的芯片可以满足不同的应用需求。

下面将对几个常用的74HC系列芯片进行介绍。

1. 74HC00:74HC00是一个四个二输入与门芯片。

它可以执行逻辑与操作,并且输出可以与其他逻辑门级联实现更复杂的逻辑功能。

该芯片通常用作数字系统中的数据选择器、信号触发器等。

2. 74HC08:74HC08是一个四个二输入与非门芯片。

与逻辑与门不同,逻辑与非门的输出是逻辑与门输出的反相信号。

该芯片可用于数字系统中的布尔代数运算、信号解码和数据传输等。

3. 74HC138:74HC138是一个三线到八线译码器/多路复用器。

它具有三个输入线和八个输出线,可以通过输入控制信号将一个特定的输出线与输入线相连。

该芯片常用于十进制数据的显示、地址解码和选择器等应用。

4. 74HC595:74HC595是一个八位移位寄存器。

它可以将数据按照指定的顺序移位存储,并通过串行输入和并行输出的方式与其他逻辑门级联。

该芯片常用于扩展I/O端口、控制LED 显示、驱动数码管等应用。

5. 74HC4040:74HC4040是一个二进制计数器。

它具有十二个计数位和一个异步复位端口,可以按照特定的时钟信号进行二进制计数,并通过输出端口显示计数值。

该芯片广泛应用于时序控制、频率分频器等数字电路中。

除了上述常用的74HC系列芯片,还有许多其他功能的芯片,如74HC04(六个反相器)、74HC14(六个反相器带施密特触发器)等。

这些芯片以其高性能、低功耗、多功能的特点,为数字系统和电子设备的设计者提供了灵活性和便利性。

Verilog基本电路设计逻辑仿真实验报告

实验报告1、基本门电路一、实验目的1、了解基于Verilog的基本门电路的设计及其验证。

2、熟悉利用EDA工具进行设计及仿真的流程。

3、学习针对实际门电路芯片74HC00、74HC02、74HC04、74HC08、74HC32、74HC86进行VerilogHDL设计的方法。

二、实验环境Libero仿真软件。

三、实验内容1、掌握Libero软件的使用方法。

2、进行针对74系列基本门电路的设计,并完成相应的仿真实验。

3、参考教材中相应章节的设计代码、测试平台代码(可自行编程),完成74HC00、74HC02、74HC04、74HC08、74HC32、74HC86相应的设计、综合及仿真。

4、提交针对74HC00、74HC02、74HC04、74HC08、74HC32、74HC86)的综合结果,以及相应的仿真结果。

(任选一个....四、实验结果和数据处理1、所有模块及测试平台代码清单..//74HC00代码-与非// HC00.vmodule HC00(A,B,Y);input [4:1]A,B;output [4:1]Y;assign Y=~(A&B);endmodule//74HC00测试平台代码// test.v`timescale 1ns/1nsmodule test1();reg [4:1]a,b;wire [4:1]y;HC00 u1(a,b,y);initialbegina=4'b0000; b=4'b0001;#10 b=b<<1;#10 b=b<<1;#10 b=b<<1;a=4'b1111; b=4'b0001; #10 b=b<<1;#10 b=b<<1;#10 b=b<<1;endendmodule//74HC02代码-或非// HC02.vmodule HC02(A,B,Y); input [4:1]A,B;output [4:1]Y;assign Y=~(A|B); endmodule//74HC02测试平台代码// test.v`timescale 1ns/1ns module test2();reg [4:1]a,b;wire [4:1]y;HC02 u2(a,b,y);initialbegina=4'b0000; b=4'b0001; #10 b=b<<1;#10 b=b<<1;#10 b=b<<1;a=4'b1111; b=4'b0001; #10 b=b<<1;#10 b=b<<1;#10 b=b<<1;endendmodule//74HC04代码-非// HC04.vmodule HC04(A,Y); input [6:1]A;output [6:1]Y;assign Y=~A; endmodule//74HC04测试平台代码// test.v`timescale 1ns/1ns module test3();reg [6:1]a;wire [6:1]y;HC04 u3(a,y);initialbegina=4'b000001;#10 a=a<<1;#10 a=a<<1;#10 a=a<<1;#10 a=a<<1;#10 a=a<<1;endendmodule//74HC08代码-与// HC08.vmodule HC08(A,B,Y); input [4:1]A,B; output [4:1]Y; assign Y=A&B;endmodule//74HC08测试平台代码// test.v`timescale 1ns/1ns module test4();reg [4:1]a,b;wire [4:1]y;HC08 u4(a,b,y);initialbegina=4'b0000; b=4'b0001; #10 b=b<<1;#10 b=b<<1;#10 b=b<<1;a=4'b1111; b=4'b0001; #10 b=b<<1;#10 b=b<<1;#10 b=b<<1;endendmodule//74HC32代码-或// HC32.vmodule HC32(A,B,Y); input [4:1]A,B;output [4:1]Y;assign Y=A|B; endmodule//74HC32测试平台代码// test.v`timescale 1ns/1ns module test5();reg [4:1]a,b;wire [4:1]y;HC32 u5(a,b,y);initialbegina=4'b0000; b=4'b0001; #10 b=b<<1;#10 b=b<<1;#10 b=b<<1;a=4'b1111; b=4'b0001; #10 b=b<<1;#10 b=b<<1;endendmodule//74HC86代码-异或// HC86.vmodule HC86(A,B,Y); input [4:1]A,B;output [4:1]Y;assign Y=A^B; endmodule//74HC86测试平台代码// test.v`timescale 1ns/1ns module test6();reg [4:1]a,b;wire [4:1]y;HC86 u6(a,b,y);initialbegina=4'b0000; b=4'b0001; #10 b=b<<1;#10 b=b<<1;a=4'b1111; b=4'b0001;#10 b=b<<1;#10 b=b<<1;#10 b=b<<1;endendmodule2、第一次仿真结果(任选一个门,请注明,插入截图,下同.................)。

74HC32-V11

四个双端或门GC74HC32四个双端或门概述GC74HC32或门采用高速硅栅门CMOS工艺研发而成,具有集成电路低功耗的特性,速度可与LS-TTL门电路相媲美。

所有门电路的输出端具有缓冲功能。

该器件具有高噪音容限特性,能驱动10个LS-TTL负载。

74HC系列逻辑门功能管脚与74LS系列相兼容。

所有的输入端均带有箝位幅度在V CC和地之间的保护二极管,以排除静电对芯片的损坏和干扰。

特点◆传输延迟时间典型值为:10ns◆宽电源电压范围:2.0~6.0V◆低静态电流:最大值为20μA(74HC系列)◆低输入电流:最大值为1μA◆能驱动10个LS-TTL负载◆封装形式:DIP14和SOP14;顶示图逻辑框图极限参数四个双端或门GC74HC32推荐工作条件2、除非特殊说明,否则所有电压值均以地为参考点。

3、功耗-温度降级值:塑料“N”封装:-12mW/℃从65℃到125℃; 直流电参数注释:4.当电源电压为5V±10%,HC系列产生最差的输出电压(OH,OL)值为4.5V。

因此,当设计这种供给电源时,4.5V的值被利用。

当V CC分别为5.5V和4.5V时产生最差的V IH和V IL。

当CMOS集成电路为较高电压6.0V时产生最大漏电流(I IN,I CC,I OZ)。

交流电参数一cc A L r f交流电参数二CC,L r f注释:5、PD确定无负载的动态电源消耗,D=PD CC²f+CC CC;无负载动态电流消耗S=PD CC f+CC;封装尺寸图DIP14封装形式SOP14封装形式订货信息四个双端或门GC74HC32文档修改记录文档信息创建日期:2007-8-17VIP customers Mobile Phone&WeChat:138****6225 Company Contact us:************-806。

74vhc123a程序设计

74vhc123a程序设计【原创版】目录1.74vhc123a 概述2.74vhc123a 的逻辑功能3.74vhc123a 的引脚及功能4.74vhc123a 的程序设计方法5.74vhc123a 的应用实例正文一、74vhc123a 概述74vhc123a 是一款高速 cmos 八路数据选择器,具有高速、低功耗、稳定的工作性能。

它内部集成了 8 个独立的数据选择器,用户可以根据需要选择其中一路数据输出。

这款芯片广泛应用于计算机、通信设备、家电等领域的数据选择和控制电路。

二、74vhc123a 的逻辑功能74vhc123a 具有以下逻辑功能:1.当 cs(使能端)为低电平时,数据选择器处于关闭状态,不输出任何数据。

2.当 cs 为高电平时,数据选择器处于工作状态,根据地址端的输入信号选择相应的数据输出。

3.地址端有 3 个输入信号(a0、a1、a2),通过不同组合的输入信号可以选择不同的数据输出。

三、74vhc123a 的引脚及功能1.cs(使能端):低电平有效,控制数据选择器的工作状态。

2.a0、a1、a2(地址端):输入信号,用于选择数据输出。

3.y0、y1、y2、y3、y4、y5、y6、y7(输出端):输出数据,根据地址端的输入信号选择相应的数据输出。

4.vcc(电源端):芯片的工作电源。

5.gnd(地端):芯片的工作地。

四、74vhc123a 的程序设计方法1.根据实际需求,设计地址端的输入信号组合,确定需要选择的数据输出。

2.通过编程设置 cs 端的电平,使数据选择器处于工作状态。

3.根据需要,读取或修改输出端的数据。

五、74vhc123a 的应用实例假设有一个 8 位的数据存储器,其数据分别为 d0、d1、d2、d3、d4、d5、d6、d7,现需要设计一个电路,使得通过 3 位地址信号 a0、a1、a2 可以选择任意一位数据输出。

可以使用 74vhc123a 数据选择器来实现。

具体电路连接如下:1.将数据存储器的 d0、d1、d2、d3、d4、d5、d6、d7 分别连接到74vhc123a 的输入端 y0、y1、y2、y3、y4、y5、y6、y7。

中微爱芯逻辑芯片通用系列AIP74HC,AIP74HCT

中微爱芯逻辑芯片通用系列AIP74HC,AIP74HCTAIP74HC138概述AIP74HC138是高速CMOS电路,管脚与LSTTL系列兼容。

AIP74HC138译码器有3个二进制加权地址输入端(A0,A1,A2),当输入有效时,输出8个互相独立的低电平有效的输出信号(Y0~Y7)。

AIP74HC138 有3个使能输入端:2个低电平有效(E1和E2)和1个高电平有效(E3)。

如果使能输入端无效,每个输出都为高。

芯片的多路使能功能方便AIP74HC138进行并行扩展,扩展成为一个32位译码器仅需要4只AIP74HC138 和一个反向器。

利用AIP74HC138的一个低有效输入作为数据输入,其他使能输入端作为信号输入的关闭闸门,AIP74HC138 可作为8输出的信号分离器。

其主要特点如下:●较宽的工作电压:2~6V●输出能驱动10个LSTTL负载●工作温度分两档:-40℃~+85℃;-40℃~+125℃●可作信号分离●多路使能功能方便扩展●可作为内存芯片的选择解码芯片●互相独立的低电平有效的输出信号●封装形式:DIP16 / SOP162.2、引脚排列图AiP74HC / HCT04概述AiP74HC / HCT04是一个十六进制逆变器。

输入端包括钳位二极管,这些钳位二极管允许使用限流电阻将输入端连接到超过VCC的电压。

主要特点:●输入级别:●对于AiP74HC04:CMOS级别●对于AiP74HCT04:TTL电平●规定温度为-40℃至+ 85℃●包装信息:DIP14 / SOP14 / TSSOP14引脚排列图AiP74HC HCT245概述AiP74HC / HCT245是具有三态输出的8位收发器。

该器件具有一个输出使能OE和用于方向控制的发送/接收(DIR)。

OE上的高电平会导致输出呈现高阻态关断状态。

输入包括钳位二极管。

这样就可以使用限流电阻将输入接口连接到超过VCC的电压。

主要特点:输入级别:对于AiP74HC245:CMOS级别对于AiP74HCT245:TTL电平八路双向总线接口同相三态输出多种包装选择规定温度为-40℃至+ 85℃包装信息:DIP20 / SOP20 / TSSOP20引脚排列图概述AiP74HC164是高速CMOS电路,管脚与低功耗肖特基TTL (LSTTL)系列兼容。

汽车基础电路-逻辑门电路(第一篇)

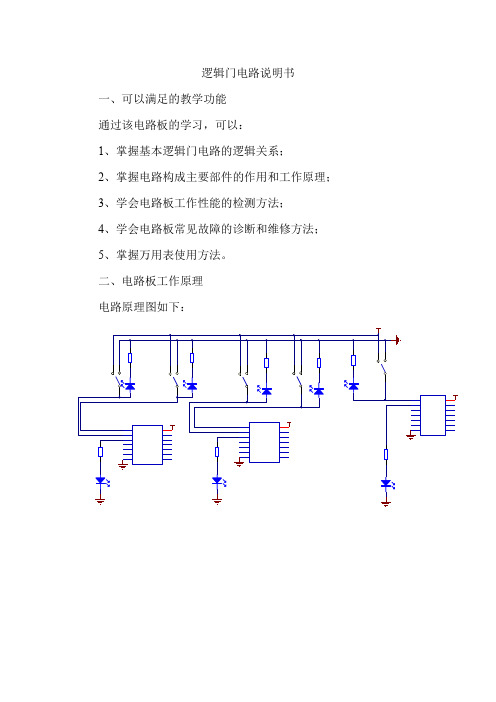

逻辑门电路说明书一、可以满足的教学功能通过该电路板的学习,可以:1、掌握基本逻辑门电路的逻辑关系;2、掌握电路构成主要部件的作用和工作原理;3、学会电路板工作性能的检测方法;4、学会电路板常见故障的诊断和维修方法;5、掌握万用表使用方法。

二、电路板工作原理电路原理图如下:元器件参数表:元件编号元件名称参数R1、R2、R3、R4、R5、R6、R7、R8 电阻300ΩC1、C2 瓷片电容0.1ufCT1、CT2 电解电容22uf D1、D2、D3、D4、D5、D6、D7、D8 LED发光二极管J1 电源接口Q1 稳压电源7805S1、S2、S3、S4、S5 拨动开关U1 非门74HC04U2 与门74HC08U3 或门74HC32 逻辑门电路是数字电路中最基本的逻辑单元,可以实现最基本和常用的逻辑运算功能。

在数字电路中,“门”就是只能进行基本逻辑运算的电路。

基本的逻辑门电路包括非门、与门、或门、与非门、或非门等,本电路可实现基本的非门、与门、或门的逻辑运算,达到对基本逻辑运算的认知。

本电路模块所用芯片74HC04/74HC08/74HC32分别为非门、与门、或门逻辑运算单元,可分别实现非门、与门、或门的逻辑运算。

使学生对逻辑运算有一个基本认识。

74HC04是六位非门逻辑运算单元,A为逻辑输入端,Y为逻辑输出端。

A输入端的高低逻辑电平由拨动开关S1控制,S1开关与电源正极导通时,指示灯D4点亮,同时向74HC04输入高电平,S1开关与电源接地导通时,指示灯D4熄灭,同时向74HC04输入低电平,可直观体现出输入74HC04的是高电平还是低电平。

Y输出端根据A输入端的高低电平可实现输出电平的控制,当输入端为低电平时,输出端为高电平,D1点亮;当输入端为高电平时,输出端为低电平,D1熄灭, Y输出端的电平由指示灯D1的亮灭来表现其高低。

74HC08是四位与门逻辑运算单元,A、B为逻辑输入端,Y为逻辑输出端。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

MC74HC32AQuad 2−Input OR GateHigh−Performance Silicon−Gate CMOS The MC74HC32A is identical in pinout to the LS32. The device inputs are compatible with Standard CMOS outputs; with pullup resistors, they are compatible with LSTTL outputs.Features•Output Drive Capability: 10 LSTTL Loads•Outputs Directly Interface to CMOS, NMOS and TTL •Operating V oltage Range: 2.0 to 6.0 V•Low Input Current: 1m A•High Noise Immunity Characteristic of CMOS Devices•In Compliance With the JEDEC Standard No. 7A Requirements •Chip Complexity: 48 FETs or 12 Equivalent Gates•Pb−Free Packages are AvailableMARKINGDIAGRAMSA= Assembly LocationL, WL= Wafer LotY, YY= YearW, WW= Work WeekG or G= Pb−Free PackageTSSOP−14DT SUFFIXCASE 948G14SOEIAJ−14F SUFFIXCASE 965SOIC−14D SUFFIXCASE 751A11474HC32AALYWGHC32AALYW GG114PDIP−14N SUFFIXCASE 646MC74HC32ANAWLYYWWG114See detailed ordering and shipping information in the package dimensions section on page 2 of this data sheet.ORDERING INFORMATION(Note: Microdot may be in either location)3Y11A1PIN 14 = V CC PIN 7 = GNDLOGIC DIAGRAM2B16Y24A25B28Y39A310B311Y412A413B4Y = A+BPinout: 14−Lead Packages (Top View)1314121110982134567V CC B4A4Y4B3A3Y3A1B1Y1A2B2Y2GNDL L H HL H L HFUNCTION TABLEInputs Output A B L H H HY ORDERING INFORMATIONDevicePackage Shipping †MC74HC32AN PDIP −1425 Units / Rail MC74HC32ANG PDIP −14(Pb −Free)MC74HC32AD SOIC −1455 Units / Rail MC74HC32ADG SOIC −14(Pb −Free)MC74HC32ADR2SOIC −142500 / Tape & Reel MC74HC32ADR2G SOIC −14(Pb −Free)MC74HC32ADTR2TSSOP −14*MC74HC32ADTR2G TSSOP −14*MC74HC32AFEL SOEIAJ −142500 / Tape & Reel MC74HC32AFELGSOEIAJ −14(Pb −Free)†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.*This package is inherently Pb −Free.MAXIMUM RATINGSSymbol Parameter Value Unit V CC DC Supply Voltage (Referenced to GND)– 0.5 to + 7.0V V in DC Input Voltage (Referenced to GND)– 0.5 to V CC + 0.5V V out DC Output Voltage (Referenced to GND)– 0.5 to V CC + 0.5VI in DC Input Current, per Pin± 20mAI out DC Output Current, per Pin± 25mAI CC DC Supply Current, V CC and GND Pins± 50mAP D Power Dissipation in Still Air,Plastic DIP†SOIC Package†TSSOP Package†750500450mWT stg Storage Temperature– 65 to + 150_CT L Lead Temperature, 1 mm from Case for 10 SecondsPlastic DIP, SOIC or TSSOP Package260_CStresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stressratings only. Functional operation above the Recommended Operating Conditions is not implied.Extended exposure to stresses above the Recommended Operating Conditions may affectdevice reliability.†Derating—Plastic DIP: – 10 mW/_C from 65_ to 125_CSOIC Package: – 7 mW/_C from 65_ to 125_CTSSOP Package: − 6.1 mW/_C from 65_ to 125_CFor high frequency or heavy load considerations, see Chapter 2 of the ON Semiconductor High−Speed CMOS Data Book (DL129/D). RECOMMENDED OPERATING CONDITIONSSymbol Parameter Min Max UnitV CC DC Supply Voltage (Referenced to GND) 2.0 6.0VV in, V out DC Input Voltage, Output Voltage (Referenced toGND)0V CC VT A Operating Temperature, All Package Types– 55+ 125_Ct r, t f Input Rise and Fall Time V CC = 2.0 V (Figure 1)V CC = 4.5 VV CC = 6.0 V 01000500400nsThis device contains protectioncircuitry to guard against damagedue to high static voltages or electricfields. However, precautions mustbe taken to avoid applications of anyvoltage higher than maximum ratedvoltages to this high−impedance cir-cuit. For proper operation, V in andV out should be constrained to therange GND v (V in or V out) v V CC.Unused inputs must always betied to an appropriate logic voltagelevel (e.g., either GND or V CC).Unused outputs must be left open.DC CHARACTERISTICS(Voltages Referenced to GND)V CC V Guaranteed LimitSymbol Parameter Condition−55 to 25°C≤85°C≤125°C UnitV IH Minimum High−Level Input Voltage V out = 0.1V or V CC−0.1V|I out| ≤ 20m A 2.03.04.56.01.502.103.154.201.502.103.154.201.502.103.154.20VV IL Maximum Low−Level Input Voltage V out = 0.1V or V CC− 0.1V|I out| ≤ 20m A 2.03.04.56.00.500.901.351.800.500.901.351.800.500.901.351.80VV OH Minimum High−Level OutputVoltage V in = V IH or V IL|I out| ≤ 20m A2.04.56.01.94.45.91.94.45.91.94.45.9VV in =V IH or V IL|I out| ≤ 2.4mA|I out| ≤ 4.0mA|I out| ≤ 5.2mA3.04.56.02.483.985.482.343.845.342.203.705.20V OL Maximum Low−Level OutputVoltage V in = V IH or V IL|I out| ≤ 20m A2.04.56.00.10.10.10.10.10.10.10.10.1VV in = V IH or V IL|I out| ≤ 2.4mA|I out| ≤ 4.0mA|I out| ≤ 5.2mA3.04.56.00.260.260.260.330.330.330.400.400.40I in Maximum Input Leakage Current V in = V CC or GND 6.0±0.1±1.0±1.0m AI CC Maximum Quiescent SupplyCurrent (per Package)V in = V CC or GNDI out = 0m A6.0 1.01040m ANOTE:Information on typical parametric values can be found in Chapter 2 of the ON Semiconductor High−Speed CMOS Data Book (DL129/D). AC CHARACTERISTICS(C L = 50pF, Input t r = t f = 6ns)V CC V Guaranteed LimitSymbol Parameter−55 to 25°C≤85°C≤125°C Unitt PLH, t PHL Maximum Propagation Delay, Input A or B to Output Y(Figures 1 and 2)2.03.04.56.07530151395401916110552219nst TLH, t THL Maximum Output Transition Time, Any Output(Figures 1 and 2)2.03.04.56.07527151395321916110362219nsC in Maximum Input Capacitance101010pF NOTE:For propagation delays with loads other than 50 pF, and information on typical parametric values, see Chapter 2 of the ON Semiconductor High−Speed CMOS Data Book (DL129/D).C PD Power Dissipation Capacitance (Per Buffer)*Typical @ 25°C, V CC = 5.0 V, V EE = 0 VpF20*Used to determine the no−load dynamic power consumption: P D = C PD V CC2f + I CC V CC. For load considerations, see Chapter 2 of the ON Semiconductor High−Speed CMOS Data Book (DL129/D).Figure 1. Switching WaveformsOUTPUT YINPUT A OR BC L **Includes all probe and jig capacitanceTESTFigure 2. Test CircuitYABFigure 3. Expanded Logic Diagram(1/4 of the Device)GNDV CCPACKAGE DIMENSIONSPDIP−14CASE 646−06ISSUE PPACKAGE DIMENSIONSSOIC −14CASE 751A −03ISSUE HNOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.4.MAXIMUM MOLD PROTRUSION 0.15 (0.006)PER SIDE.5.DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127(0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.DIM MIN MAX MIN MAX INCHESMILLIMETERS A 8.558.750.3370.344B 3.80 4.000.1500.157C 1.35 1.750.0540.068D 0.350.490.0140.019F 0.40 1.250.0160.049G 1.27 BSC 0.050 BSC J 0.190.250.0080.009K 0.100.250.0040.009M 0 7 0 7 P 5.80 6.200.2280.244R0.250.500.0100.019____DIMENSIONS: MILLIMETERS*For additional information on our Pb −Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.PACKAGE DIMENSIONSTSSOP −14CASE 948G −01ISSUE BDIM MIN MAX MIN MAX INCHES MILLIMETERS A 4.90 5.100.1930.200B 4.30 4.500.1690.177C −−− 1.20−−−0.047D 0.050.150.0020.006F 0.500.750.0200.030G 0.65 BSC 0.026 BSC H 0.500.600.0200.024J 0.090.200.0040.008J10.090.160.0040.006K 0.190.300.0070.012K10.190.250.0070.010L 6.40 BSC 0.252 BSC M 0 8 0 8 NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.4.DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE.5.DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08(0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.6.TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY .7.DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE −W −.____14X REF 14X0.360.65PITCHSOLDERING FOOTPRINT**For additional information on our Pb −Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.PACKAGE DIMENSIONSSOEIAJ −14CASE 965−01ISSUE ANOTES:1.DIMENSIONING AND TOLERANCING PER ANSIY14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further noticeto any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。