基于FPGA的数字密码锁

基于FPGA的数字密码锁

基于F P G A的数字密码锁LG GROUP system office room 【LGA16H-LGYY-LGUA8Q8-LGA162】CPLD/FPGA课程设计项目名称:基于FPGA的数字密码锁设计专业班级:学生学号:学生姓名:指导老师:2016年6月4日摘要本设计是基于现场可编程门阵列FPGA 器件的电子密码锁的设计。

通过Verilog 语言控制4位二进制数,组成数字排列,形成一个简单的数字密码锁,假设预设密码为4位数:0000,当输入正确时输出为1、输入错误时输出为0。

同时输出输入的次数,当3次以上输入错误时,输出一个报警信号,即使第四、五次输入正确也输出报警信号。

本设计利用Modelsim软件编写Verilog HDL硬件描述语言程序以实现输入密码、开锁、报警功能。

通过仿真调试,利用可编程器件FPGA的电子密码锁的设计基本达到了预期目的。

关键词:现场可编程门阵列;数字密码锁;Verilog HDL;AbstractThis design is the electronic code lock field programmable gate array FPGA devices based design. By Verilog language control 4-bit binary number, composed of figures arranged to form a simple digital lock, assuming that the default password is 4 digits: 0000, correct output when the input is 1, the output of the input error to zero. At the same time the number of input and output, and when more than three times the input error, an alarm signal is output, even if the fourth and fifth also enter the correct output alarm signal.This design uses Modelsim software write Verilog HDL hardware description language program to implement a password lock, alarm function. The simulation debugging, using the programmable device FPGA design basic electronic locks to achieve the desired purpose.Key words: FPGA;The digital combination lock;Verilog HDL;目录摘要 (I)Abstract (II)第1章所选项目的研究意义 (1)概述 (1)数字密码锁的研究现状 (2)数字密码锁的应用 (3)数字密码锁的困难 (3)本文研究意义 (3)设计思路 (4)第2章设计方案 (5)功能定义 (5)模块设计 (5)第3章系统软件设计 (7)设计概括 (7)设计流程 (7)密码存储模块 (7)编码模块 (8)比较模块 (8)主要程序模块 (9)第4章软件仿真 (14)仿真过程 (14)仿真结果 (15)仿真分析 (16)仿真过程 (17)结论 (18)参考文献 (19)附录1 程序代码 (20)项目创新及特色 (26)第1章所选项目的研究意义概述数字密码锁是一个小型的数字系统,与普通机械锁相比, 具有许多独特的优点: 保密性好, 防盗性强, 可以不用钥匙, 记住密码即可开锁等。

基于fpga的aes密码算法设计

基于FPGA的AES密码算法设计一、引言随着信息技术的快速发展,信息安全问题也日益突出,密码算法成为保障信息安全的重要手段之一。

AES(Advanced Encryption Standard)是一种对称密码算法,已经成为当前最流行、最安全的数据加密标准之一。

而FPGA(Field-Programmable Gate Array)作为一种可编程逻辑器件,具有高度的灵活性和可编程性,逐渐成为密码算法设计中的重要工具。

二、AES密码算法概述1. AES密码算法简介AES密码算法是一种对称密码算法,旨在提供快速、高效和安全的数据加密解密功能。

它可以使用128位、192位或256位的密钥,并对固定大小的数据块进行加密处理。

AES算法采用了替代、置换、线性变换等多种复杂运算方法,以实现高度的安全性。

2. AES密码算法的结构AES密码算法主要由四个连续执行的操作组成:字节替代、行移位、列混淆和轮密钥加。

在这些操作的基础上,AES算法通过多轮迭代的方式来实现对数据块的加密处理。

三、FPGA在密码算法设计中的应用1. FPGA的优势FPGA作为一种可编程逻辑器件,具有高度的灵活性和可编程性,能够实现复杂的数字逻辑电路设计。

与传统的固定功能集成电路相比,FPGA可以根据具体需求进行重新配置,同时具有较高的运算速度和并行处理能力。

2. FPGA在密码算法设计中的应用利用FPGA的可编程特性,可以实现对称密码算法的硬件加速和优化设计。

FPGA可以并行处理大量数据,并且能够高效地实现复杂的运算逻辑,从而提高密码算法的加密解密速度和安全性。

四、基于FPGA的AES密码算法设计1. FPGA加速AES算法的优势基于FPGA的AES算法设计可以充分发挥FPGA并行处理和高速运算的优势,实现对数据加密解密过程的加速和优化。

与传统的软件实现相比,FPGA加速的AES算法能够显著提高算法的执行效率和性能表现。

2. FPGA加速AES算法设计的实现步骤(1)针对AES算法的具体特点,对其加密解密过程进行硬件逻辑设计;(2)通过VHDL或Verilog等硬件描述语言对AES算法进行逻辑电路设计和仿真验证;(3)利用FPGA开发板进行算法的实际实现,并进行性能测试和调优。

fpga简易四位密码锁的代码

FPGA简易四位密码锁的代码一、概述在现代社会中,密码锁被广泛应用于各种场合,如家庭、商业和工业等。

密码锁的使用方便、安全性高,受到了人们的青睐。

FPGA (Field Programmable Gate Array)作为一种灵活可编程的硬件设备,可以用来实现各种数字逻辑电路,包括密码锁。

本文将介绍如何使用FPGA实现一个简易的四位密码锁,并提供相应的代码。

二、硬件设计1. 需要的硬件- FPGA开发板- 数字键盘- LED数码管2. 硬件连接- 将数字键盘通过连接线连接到FPGA开发板上的GPIO端口,用于输入密码;- 将LED数码管通过连接线连接到FPGA开发板上的GPIO端口,用于显示密码输入状态。

三、软件设计1. Verilog代码设计```verilog// 模块声明module password_lock (input wire clk, // 时钟信号input wire rst, // 复位信号input wire [3:0] key_in, // 数字键盘输入output reg [3:0] led_out // LED数码管输出);// 代码实现reg [3:0] password = 4'b1101; // 设定密码为1101always (posedge clk or posedge rst) beginif (rst) beginled_out <= 4'b1111; // 置LED数码管输出为1111end else beginif (key_in == password) beginled_out <= 4'b0000; // 如果输入密码正确,则LED数码管输出为0000end else beginled_out <= 4'b1111; // 如果输入密码错误,则LED数码管输出为1111endendendendmodule```2. 实现原理说明- 模块声明中指定了模块的输入和输出端口;- 代码实现中首先设定了一个四位的密码,然后在时钟信号的作用下判断输入的密码是否与设定的密码相匹配,如果匹配则将LED数码管输出为0000,表示密码正确;否则输出为1111,表示密码错误。

基于fpga的数字密码锁设计与实现

一、概述在当今信息技术高度发达的时代,数字密码锁已成为人们生活中常见的安全保障措施之一。

随着FPGA(可编程逻辑门阵列)技术的不断成熟和普及,基于FPGA的数字密码锁设计与实现已经成为一个备受关注的研究方向。

本文将探讨基于FPGA的数字密码锁的设计原理、实现过程以及相关技术细节,为相关领域的研究和应用提供参考。

二、数字密码锁的基本原理1.数字密码锁的基本功能数字密码锁是一种利用密码验证来进行身份识别和门禁控制的设备。

其基本功能包括输入密码、密码验证和门禁控制等。

2.数字密码锁的工作原理数字密码锁通常由键盘、控制单元和执行单元等组成,其工作原理是用户通过键盘输入密码,控制单元接收并验证密码的正确性,然后执行单元根据验证结果控制门禁的开启或关闭。

三、基于FPGA的数字密码锁设计1.基于FPGA的数字密码锁的优势相比传统的基于单片机或嵌入式系统的数字密码锁,基于FPGA的数字密码锁具有更高的灵活性和可扩展性。

FPGA可以根据实际需求进行灵活的硬件逻辑设计,同时兼容多种通信协议和接口,使得其在数字密码锁设计中具有显著的优势。

2.基于FPGA的数字密码锁的设计原理基于FPGA的数字密码锁主要包括密码输入模块、密码验证模块和门禁控制模块。

密码输入模块负责接收用户输入的密码,密码验证模块根据预设的密码进行验证,门禁控制模块根据验证结果控制门禁的开启或关闭。

3.基于FPGA的数字密码锁的设计流程(1)确定需求:明确数字密码锁的功能和性能要求。

(2)硬件设计:设计数字密码锁的硬件逻辑,包括键盘接口、密码验证逻辑和门禁控制逻辑。

(3)软件设计:设计数字密码锁的用户界面和控制逻辑。

(4)综合与实现:将硬件和软件进行综合,实现数字密码锁的功能。

四、基于FPGA的数字密码锁的实现1.硬件设计(1)键盘接口设计:采用矩阵式键盘接口,利用FPGA内部的GPIO 接口进行连接。

(2)密码验证逻辑设计:采用逻辑门设计密码验证逻辑,包括密码存储、密码输入和密码比对等功能。

基于FPGA的数字密码锁

基于F P G A的数字密码锁精选文档TTMS system office room 【TTMS16H-TTMS2A-TTMS8Q8-CPLD/FPGA课程设计项目名称:基于FPGA的数字密码锁设计专业班级:学生学号:学生姓名:指导老师:2016年6月4日摘要本设计是基于现场可编程门阵列FPGA 器件的电子密码锁的设计。

通过Verilog 语言控制4位二进制数,组成数字排列,形成一个简单的数字密码锁,假设预设密码为4位数:0000,当输入正确时输出为1、输入错误时输出为0。

同时输出输入的次数,当3次以上输入错误时,输出一个报警信号,即使第四、五次输入正确也输出报警信号。

本设计利用Modelsim软件编写Verilog HDL硬件描述语言程序以实现输入密码、开锁、报警功能。

通过仿真调试,利用可编程器件FPGA的电子密码锁的设计基本达到了预期目的。

关键词:现场可编程门阵列;数字密码锁;Verilog HDL;AbstractThis design is the electronic code lock field programmable gate array FPGA devices based design. By Verilog language control 4-bit binary number, composed of figures arranged to form a simple digital lock, assuming that the default password is 4 digits: 0000, correct output when the input is 1, the output of the input error to zero. At the same time the number of input and output, and when more than three times the input error, an alarm signal is output, even if the fourth and fifth also enter the correct output alarm signal.This design uses Modelsim software write Verilog HDL hardware description language program to implement a password lock, alarm function. The simulation debugging, using the programmable device FPGA design basic electronic locks to achieve the desired purpose.Key words: FPGA;The digital combination lock;Verilog HDL;目录第1章所选项目的研究意义概述数字密码锁是一个小型的数字系统,与普通机械锁相比, 具有许多独特的优点: 保密性好, 防盗性强, 可以不用钥匙, 记住密码即可开锁等。

基于FPGA的数字密码锁

CPLD/FPGA课程设计项目名称:基于FPGA得数字密码锁设计专业班级:学生学号:学生姓名:指导老师:2016年6月4日摘要本设计就是基于现场可编程门阵列FPGA器件得电子密码锁得设计。

通过Veril og语言控制4位二进制数,组成数字排列,形成一个简单得数字密码锁,假设预设密码为4位数:0000,当输入正确时输出为1、输入错误时输出为0.同时输出输入得次数,当3次以上输入错误时,输出一个报警信号,即使第四、五次输入正确也输出报警信号。

本设计利用Modelsim软件编写Verilog HDL硬件描述语言程序以实现输入密码、开锁、报警功能. 通过仿真调试,利用可编程器件FPGA得电子密码锁得设计基本达到了预期目得.关键词:现场可编程门阵列;数字密码锁;Verilog HDL;AbstractThisdesign is the electroniccodelock fieldprogrammable gatearrayFPGA devices baseddesign、ByVeriloglanguage control 4—bit binary number, posed of figures arranged to form a simple digital lock, assuming that the default password is 4 digits: 0000, correct output when the input is 1,the outputof the inputerror to zero、 At the same time the number of input and output, and when more than three times the input error, an alarm signal is output,evenif thefourth andfifthalso enter thecorrect output alarm signal、Thisdesignuses Modelsim softwarewriteVerilog HDLhardware descriptionlanguage program to implement apasswordlock, alarm function、The simulation debugging, using theprogrammabledevice FPGA design basic electronic locks to achieve the desired purpose、Keywords:FPGA;The digital bination lock;Verilog HDL;目录摘要................................................. 错误!未定义书签。

FPGA课程论文-基于FPGA设计的电子密码锁

FPGA课程论文摘要基于FPGA设计的电子密码锁是一个小型的数字系统,与普通机械锁相比, 具有许多独特的优点: 保密性好, 防盗性强, 可以不用钥匙, 记住密码即可开锁等。

目前使用的电子密码锁大部分是基于单片机技术, 以单片机为主要器件, 其编码器与解码器的生成为软件方式。

在实际应用中, 由于程序容易跑飞, 系统的可靠性能较差。

本文介绍一种基于现场可编程门阵列FPGA 器件的电子密码锁的设计方法采用VHDL语言对系统进行描述,并在FLEX10K10LC84-4上实现。

系统所实现的功能:用户给电子密码锁设定一个密码,当使用本机键盘开锁时,该密码与用户设定的密码比较,如果密码正确,则开锁;如果密码不正确,则允许用户重新输入密码,最多可输入三次,若三次都不正确,则扬声器报警,直到按复位键才允许再次输入代码。

通过仿真调试,利用可编程器件FPGA的电子密码锁的设计基本达到了预期目的。

当然,该系统在一些细节的设计上还需要不断的完善和改进,特别是对系统的扩展有很好的实用和设计的价值。

关键词:现场可编程门阵列, 硬件描述语言, 电子密码锁, 扬声器一绪言系统以利用可编程器件实现电子密码锁的设计为研究背景、现状以及发展方向,明确指出了电子密码锁面临的问题和所解决的方法。

1.1课题背景基于FPGA的电子密码锁是新型现代化安全管理系统,它集微机自动识别技术和现代安全管理措施为一体,它涉及电子,机械,计算机技术,通讯技术,生物技术等诸多新技术。

它是解决重要部门出入口实现安全防范管理的有效措施,适用各种场合,如银行、宾馆、机房、军械库、机要室、办公间、智能化小区、工厂、家庭等。

在数字技术网络技术飞速发展的今天,电子密码锁技术得到了迅猛的发展。

它早已超越了单纯的门道及钥匙管理,逐渐发展成为一套完整的出入管理系统。

它在工作环境安全、人事考勤管理等行政管理工作中发挥着巨大的作用。

在该系统的基础上增加相应的辅助设备可以进行电梯控制、车辆进出控制,物业消防监控、餐饮收费、私家车库管理等,真正实现区域内一卡智能管理。

课程设计报告-基于fpga的电子密码锁的设计

课程设计报告-基于fpga的电子密码锁的设计

一、引言

随着计算机技术的发展,传统的安全锁逐渐淡出人们的视野,取而代之的是一种更加

先进而安全的电子密码锁。

采用FPGA开发的电子密码锁在现代实用锁中变得越来越常见,它能够实现简单易懂、稳定可靠的安全锁功能,从而满足人们对安全问题日益严峻的需求。

本文主要介绍基于FPGA技术设计的电子密码锁的原理及实际应用,旨在为技术研究和产

品设计提供有价值的参考。

二、系统概述

电子密码锁是一种可以根据用户的输入及系统的设置的安全保护锁,它主要由输入接口、控制器、显示屏和锁具电源等组成。

基于FPGA设计的电子密码锁主要分为输入端处

理和控制端处理两部分,其中,输入端利用FPGA控制集成电路(IC)、有源转换器和输入/

输出连接器,实现密码锁的输入模块部分的处理功能;控制端利用FPGA实现温度检测和

按键、加密算法、记录密码信息等功能,满足密码锁的控制要求。

三、工作原理

电子密码锁工作原理主要是建立在输入接口和控制器之间的信息传输上。

当用户通过

输入接口输入密码时,控制器收到输入信号,利用自身中内置的加密算法,将输入的密码

信息和系统设置密码进行比对,如果密码正确,系统会将密码锁打开,从而使得受保护的

物品得到有效的安全保护。

四、总结

基于FPGA技术设计的电子密码锁为现代安全保护提供了一种先进的途径,其安全性

和可靠性得到了极大的提高,使得大多数受保护物品得到有效保护。

电子密码锁以及FPGA 技术的发展正在为我们日常生活与工作提供前所未有的便利,也将带给未来更多安全的思

考与希望。

基于FPGA的高性能数据加密与解密系统设计与实现

基于FPGA的高性能数据加密与解密系统设计与实现随着信息技术的迅猛发展,数据的安全性问题日益突出。

为了保护敏感信息的机密性,数据加密与解密技术成为了当今社会中不可或缺的一部分。

在这篇文章中,我们将探讨基于FPGA(现场可编程门阵列)的高性能数据加密与解密系统的设计与实现。

一、引言数据加密与解密是保护数据安全和隐私的关键技术。

传统的软件实现数据加密与解密在处理大规模数据时会遇到性能瓶颈的问题。

相较于软件实现,FPGA在加密与解密的计算密集型任务上具有显著的优势。

FPGA具备并行计算能力,可以加速加密与解密算法的执行速度。

本文将阐述基于FPGA的高性能数据加密与解密系统设计与实现的方法与步骤。

二、数据加密与解密算法选择在设计数据加密与解密系统之前,我们首先需要选择合适的加密与解密算法。

常见的对称加密算法包括DES(数据加密标准),3DES(Triple DES)和AES(高级加密标准)。

而非对称加密算法包括RSA(Rivest-Shamir-Adleman)和椭圆曲线密码算法等。

对于高性能的加密与解密系统,我们选择了AES算法作为基础。

AES算法使用分组密码,适合在FPGA上进行硬件加速。

其具备较高的安全性和执行速度,因此是许多数据通信和存储系统中使用的主要加密算法。

三、FPGA高性能数据加密与解密系统设计1. 系统架构设计基于FPGA的高性能数据加密与解密系统的设计需要考虑多个模块的协同工作。

该系统的主要模块包括数据缓存模块、加密/解密算法模块、协议控制模块和数据传输接口模块等。

- 数据缓存模块:负责临时存储输入和输出的数据,减少对外部存储器的访问延迟。

- 加密/解密算法模块:实现AES加密/解密算法,包括轮密钥生成、字节代换、行移位、列混淆等操作。

- 协议控制模块:负责控制系统的工作流程,包括输入数据的传输、加密/解密操作的控制和输出数据的传输等。

- 数据传输接口模块:与外部系统进行数据的输入和输出。

《基于VHDL语言和FPGA的电子密码锁》范文

《基于VHDL语言和FPGA的电子密码锁》篇一一、引言随着科技的发展,电子密码锁已逐渐取代传统的锁具,成为了安全领域的重要组成部分。

而作为电子密码锁核心技术之一的FPGA(现场可编程门阵列)技术,以及VHDL语言编程的灵活性,更是对密码锁设计起到了重要的推动作用。

本文旨在详细探讨基于VHDL语言和FPGA的电子密码锁的设计与实现。

二、VHDL语言与FPGA概述VHDL(VHSIC Hardware Description Language)是一种硬件描述语言,用于描述电子系统的结构和行为。

而FPGA则是一种可编程逻辑器件,其内部由许多可配置的逻辑单元组成,通过编程可以实现各种复杂的数字电路功能。

将VHDL语言与FPGA相结合,可以实现电子密码锁的高效、灵活和可定制的设计。

三、电子密码锁的设计要求在基于VHDL语言和FPGA的电子密码锁设计中,首先需要明确设计要求。

这些要求包括:高安全性、易于使用、良好的扩展性以及低成本等。

此外,密码锁应能抵抗各种常见的攻击方式,如暴力破解等。

四、基于VHDL的密码锁设计与实现基于VHDL语言的电子密码锁设计主要分为几个模块:密码输入模块、解码模块、控制模块和输出模块等。

密码输入模块负责接收用户输入的密码;解码模块对输入的密码进行解码,判断其是否正确;控制模块根据解码结果控制输出模块的开关状态;而整个系统则由FPGA实现。

在VHDL编程中,需要详细描述各个模块的功能、接口以及它们之间的通信方式。

例如,密码输入模块应能接收一定长度的密码输入,并将其传递给解码模块。

解码模块则根据预设的算法对密码进行解码,并将结果传递给控制模块。

控制模块根据解码结果控制输出模块的开关状态,以实现密码锁的开启或关闭。

五、FPGA的实现与优化在FPGA上实现电子密码锁时,需要利用FPGA的编程工具进行编程和配置。

首先,将VHDL代码编译成可在FPGA上运行的二进制代码;然后,将二进制代码下载到FPGA中,实现对电子密码锁的硬件配置。

基于fpga的数字密码锁(使用矩阵键盘)

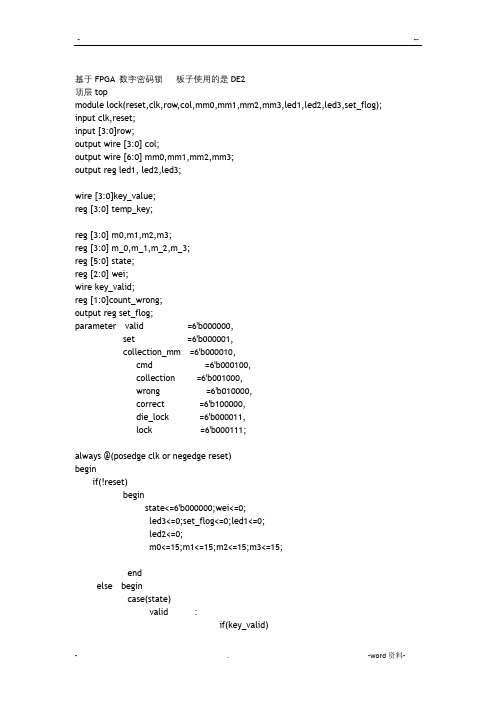

基于FPGA 数字密码锁板子使用的是DE2顶层topmodule lock(reset,clk,row,col,mm0,mm1,mm2,mm3,led1,led2,led3,set_flog); input clk,reset;input [3:0]row;output wire [3:0] col;output wire [6:0] mm0,mm1,mm2,mm3;output reg led1, led2,led3;wire [3:0]key_value;reg [3:0] temp_key;reg [3:0] m0,m1,m2,m3;reg [3:0] m_0,m_1,m_2,m_3;reg [5:0] state;reg [2:0] wei;wire key_valid;reg [1:0]count_wrong;output reg set_flog;parameter valid =6'b000000,set =6'b000001,collection_mm =6'b000010,cmd =6'b000100,collection =6'b001000,wrong =6'b010000,correct =6'b100000,die_lock =6'b000011,lock =6'b000111;always @(posedge clk or negedge reset)beginif(!reset)beginstate<=6'b000000;wei<=0;led3<=0;set_flog<=0;led1<=0;led2<=0;m0<=15;m1<=15;m2<=15;m3<=15;endelse begincase(state)valid :if(key_valid)begintemp_key<=key_value;state<=collection;endelsestate<=valid;collection : beginif(key_value>=0&&key_value<=9)beginif(led1&&(!set_flog))//开启状态不能按数字键state<=valid;else if((!key_valid)&&(wei<5))beginled2<=0;state<=collection_mm;wei<=wei+1'b1;endelsestate<=collection;endelseif(!key_valid)state<=cmd;endcollection_mm: begincase(wei)1:m0<=temp_key;2:m1<=temp_key;3:m2<=temp_key;4:m3<=temp_key;endcasestate<=valid;endcmd : begincase(temp_key)15:if(!led1)beginm0<=15;m1<=15;m2<=15;m3<=15;//*clearstate<= valid;wei<=0;led2<=0;led1<=0;endelsestate<= valid;14:if(led1)state<= valid;else if(wei) //back deletebegincase(wei)1:m0<=15;2:m1<=15;3:m2<=15;4:m3<=15;endcasewei<=wei-1'b1;state<=valid;led2<=0;endelsestate<=valid;13: if(set_flog)//保存密码beginset_flog<=0;led1<=0;m_0<=m0;m_1<=m1;m_2<=m2;m_3<=m3;state<=lock;endelseif((m0==m_0)&&(m1==m_1)&&(m2==m_2)&&(m3==m_3))//comparebeginstate<=correct;m0<=15;m1<=15;m2<=15;m3<=15;endelse beginstate<=wrong;count_wrong<=count_wrong+1;end12: state<=lock;10: if(led1) //setbeginset_flog<=1;wei<=0;m0<=15;m1<=15;m2<=15;m3<=15;state<=valid;enddefault:state<=valid;endcaseendcorrect :begin //openled1<=1;state<=valid;count_wrong<=0;endwrong :beginled2<=1;state<=valid;led1<=0;if(count_wrong==3) //lock diebegincount_wrong<=0;state<=die_lock;endendlock :beginled1<=0;wei<=0;led2<=0;m0<=15;m1<=15;m2<=15;m3<=15;set_flog<=0;state<=valid;enddie_lock:led3<=1;endcaseendendwire [15:0] mm={m3,m2,m1,m0};key key_scan(reset,clk,row,col,key_value,key_valid);display dis_u1(clk,mm,mm3,mm2,mm1,mm0);endmodule键盘扫描模块module key(reset,clk,row,col,key_value,key_flag);input clk,reset;input [3:0] row;//hangoutput reg [3:0] col;//lieoutput reg [3:0] key_value;output reg key_flag;reg [3:0] row_reg;reg [3:0] col_reg;reg [19:0] count;reg [2:0] state;reg clk_500khz;always @(posedge clk or negedge reset)if(!reset) beginclk_500khz<=0;count<=0;endelseif(count>=5000) begin clk_500khz<=~clk_500khz;count<=0;end else count<=count + 1'b1;always @(posedge clk_500khz or negedge reset)beginif(!reset)begin col<=0;state<=0;row_reg<=0;col_reg<=0;end elsebegincase(state)0:begincol<=0;key_flag<=0;if(row[3:0]!=4'b1111)beginstate<=1;col[3:0]<=4'b1110;endelse state<=0;end1: if(row[3:0]!=4'b1111) state<=5;else begin state<=2;col<=4'b1101;end2: if(row[3:0]!=4'b1111) state<=5;else begin state<=3;col<=4'b1011;end3: if(row[3:0]!=4'b1111) state<=5;else begin state<=4;col<=4'b0111;end 4: if(row[3:0]!=4'b1111) state<=5;else state<=0;5: if(row[3:0]!=4'b1111)begincol_reg<=col;row_reg<=row;state<=5;key_flag<=1;endelsestate <=0;endcaseendendalways@(clk or col_reg or row_reg or key_value)beginif(!reset)key_value<=0;else if(key_flag==1'b1)begincase({col_reg,row_reg})8'b1110_1110:key_value<=1;8'b1110_1101:key_value<=2;8'b1110_1011:key_value<=3;8'b1110_0111:key_value<=10;//a8'b1101_1110:key_value<=4;8'b1101_1101:key_value<=5;8'b1101_1011:key_value<=6;8'b1101_0111:key_value<=11;//b8'b1011_1110:key_value<=7;8'b1011_1101:key_value<=8;8'b1011_1011:key_value<=9;8'b1011_0111:key_value<=12;//c8'b0111_1110:key_value<=15;//*8'b0111_1101:key_value<=0;8'b0111_1011:key_value<=14;//#8'b0111_0111:key_value<=13;//d endcaseendendendmodule显示模块module display(clk,mm,wei0,wei1,wei2,wei3); input [15:0]mm;input clk;output reg [6:0] wei0,wei1,wei2,wei3;always @(clk)begincase(mm[3:0])4'b0000:wei0<=7'b 1000000;4'b0001:wei0<=7'b 1111001;4'b0010:wei0<=7'b 0100100;4'b0011:wei0<=7'b 0110000;4'b0100:wei0<=7'b 0011001;4'b0101:wei0<=7'b 0010010;4'b0110:wei0<=7'b 0000010;4'b0111:wei0<=7'b 1111000;4'b1000:wei0<=7'b 0000000;4'b1001:wei0<=7'b 0011000;4'b1010:wei0<=7'b 0001000;4'b1011:wei0<=7'b 0000011;4'b1100:wei0<=7'b 1000110;4'b1101:wei0<=7'b 0100001;4'b1110:wei0<=7'b 0000110;4'b1111:wei0<=~7'b 1000000;//4'b1111:wei0<=7'b 0001110;endcasecase(mm[7:4])4'b0000:wei1<=7'b 1000000;4'b0001:wei1<=7'b 1111001;4'b0010:wei1<=7'b 0100100;4'b0011:wei1<=7'b 0110000;4'b0100:wei1<=7'b 0011001;4'b0101:wei1<=7'b 0010010;4'b0110:wei1<=7'b 0000010;4'b0111:wei1<=7'b 1111000;4'b1000:wei1<=7'b 0000000;4'b1001:wei1<=7'b 0011000;4'b1010:wei1<=7'b 0001000;4'b1011:wei1<=7'b 0000011;4'b1100:wei1<=7'b 1000110; 4'b1101:wei1<=7'b 0100001; 4'b1110:wei1<=7'b 0000110; 4'b1111:wei1<=~7'b 1000000; //4'b1111:wei1<=7'b 0001110; endcasecase(mm[11:8])4'b0000:wei2<=7'b 1000000; 4'b0001:wei2<=7'b 1111001; 4'b0010:wei2<=7'b 0100100; 4'b0011:wei2<=7'b 0110000; 4'b0100:wei2<=7'b 0011001; 4'b0101:wei2<=7'b 0010010; 4'b0110:wei2<=7'b 0000010; 4'b0111:wei2<=7'b 1111000; 4'b1000:wei2<=7'b 0000000; 4'b1001:wei2<=7'b 0011000; 4'b1010:wei2<=7'b 0001000; 4'b1011:wei2<=7'b 0000011; 4'b1100:wei2<=7'b 1000110; 4'b1101:wei2<=7'b 0100001; 4'b1110:wei2<=7'b 0000110; 4'b1111:wei2<=~7'b 1000000; //4'b1111:wei2<=7'b 0001110; endcasecase(mm[15:12])4'b0000:wei3<=7'b 1000000; 4'b0001:wei3<=7'b 1111001; 4'b0010:wei3<=7'b 0100100; 4'b0011:wei3<=7'b 0110000; 4'b0100:wei3<=7'b 0011001; 4'b0101:wei3<=7'b 0010010; 4'b0110:wei3<=7'b 0000010; 4'b0111:wei3<=7'b 1111000; 4'b1000:wei3<=7'b 0000000; 4'b1001:wei3<=7'b 0011000; 4'b1010:wei3<=7'b 0001000; 4'b1011:wei3<=7'b 0000011; 4'b1100:wei3<=7'b 1000110; 4'b1101:wei3<=7'b 0100001; 4'b1110:wei3<=7'b 0000110; 4'b1111:wei3<=~7'b 1000000; //4'b1111:wei3<=7'b 0001110; endcaseend endmodule。

-基于FPGA的电子密码锁的设计

本科毕业设计基于FPGA的电子密码锁的设计摘要随着现代电子技术的迅猛发展,相信电子密码锁将会逐渐取代普通的机械密码锁。

主要是由于电子密码锁拥有几个普通机械密码锁不可能替代的优点:保密系能好、安全度高、即防盗性能强,不需要使用钥匙、即记住密码就可开锁等等。

本文主要阐述了一种基于现场可编程门阵列FPGA器件的电子密码锁的设计方法。

用FPGA器件构造系统,所有算法完全由硬件电路来实现,使得系统的工作可靠性大为提高。

而且由于FPGA具有现场可编程功能,当设计需要更改时,只需更改FPGA中的控制和接口电路,利用EDA 工具将更新后的设计下载到FPGA中即可,无需更改外部电路的设计,大大提高了设计的效率。

因此,采用FPGA开发的数字系统,不仅具有很高的工作可靠性,而且升级也极其方便。

此设计采用EDA技术,利用MAX+PLUSⅡ工作平台和VHDL硬件描述语言,设计了一种电子密码锁,并通过本学院的实验箱FPGA芯片实现。

关键词:电子密码锁FPGA VHDL硬件描述语言EDA MAX+PLUSⅡThe Design of Electronic Locks Based on FPGAWu Yaoxiao(College of Engineering, South China Agricultural University, Guangzhou 510642, China) Abstract:With the rapid development of modern electronic technology, electronic locks will gradually replace the ordinary mechanical locks. Confidential Department has the advantages of several ordinary mechanical locks can not substitute electronic locks, such as high security, anti-theft performance, and does not require the use of a key, Remember password can unlock. This article focuses on the design method which is based on field programmable gate array (FPGA) devices, electronic locks. FPGA device constructed system, all of the algorithms completely realized by a hardware circuit so that the operational reliability of the system can be greatly improved. And with field-programmable function, when it need to change the methods of the design, just change the FPGA control and interface circuit with using EDA tools updated design that is downloaded to the FPGA without the need to change the external circuit design, greatly improving the efficiency of the design. Therefore, the use of digital systems developed by the FPGA, not only has a very high operating reliability, but also extremely easy to upgrade. The design of the system uses the EDA technology, MAX+PLUSⅡsoftware and VHDL hardware description language, designed an electronic lock, and implemented by the Institute of experimental box FPGA chip.Keywords: electronic locks FPGA VHDL hardware description language EDAMAX + PLUS II目录1 前言 01.1 EDA技术及其发展 01.2 电子密码锁的国内外发展状况 01.3 电子密码锁的重要性 (1)2 MAX+PLUSⅡ软件环境概述 (2)2.1 MAX+PLUSⅡ设计流程 (2)2.2 MAX+PLUSⅡ支持的硬件描述语言 (3)2.3 MAX+PLUSⅡ工作过程 (4)3 硬件环境FPGA的工作原理及其结构 (5)3.1 FPGA的基本结构 (5)3.2 FPGA的设计流程 (6)4 基于FPGA电子密码锁系统的基本描述 (8)4.1 电子密码锁的系统的方案比较和选择 (8)4.2 基于FPGA的电子密码锁的设计的思路 (9)4.3 本系统设计的目的和意义 (9)5 基于FPGA电子密码锁系统的仿真和分析 (10)5.1 底层文件仿真和分析 (10)5.1.1 扫描时钟产生模块 (10)5.1.2按键去抖模块 (10)5.1.3键盘扫描模块 (11)5.1.44*4键盘编码及其按键功能的设置模块 (12)5.1.5数码管显示模块 (13)5.1.6 比较判断和功能描述模块 (15)5.2 顶层文件仿真和分析 (16)6 结论 (17)参考文献 (18)附录 (18)致谢 (33)华南农业大学本科生毕业设计成绩评定表1 前言1.1 EDA技术及其发展在计算机技术的推动下,20世纪末,电子技术获得了飞速的发展,现代电子产品几乎渗透于社会的各个领域,有力地推动了社会生产力的发展和社会信息化程度的提高,同时又促使现代电子产品性能的进一步提高,产品更新换代的节奏也越来越快(潘松,等,2005)。

基于FPGA的电子密码锁设计

一、前言电子密码锁的使用体现了人们的消费水平、保安意识和科技水平的提高,而且避免了携带甚至丢失钥匙的麻烦。

目前设计密码锁的方法很多,例如传统的PCB板设计、用PLC设计或者单片机设计等等。

而用VHDL可以更加快速、灵活地设计出符合各种要求的密码锁,优于其他设计方法。

VHDL是一种符合IEEE标准的硬件描述语言,其最大的特点是借鉴高级程序语言的功能特性,对电路的行为与结构进行高度的抽象化、规范化的形式描述,并对设计的不同层次、不同领域的模拟验证与综合优化等处理,使设计过程延到高度自动化。

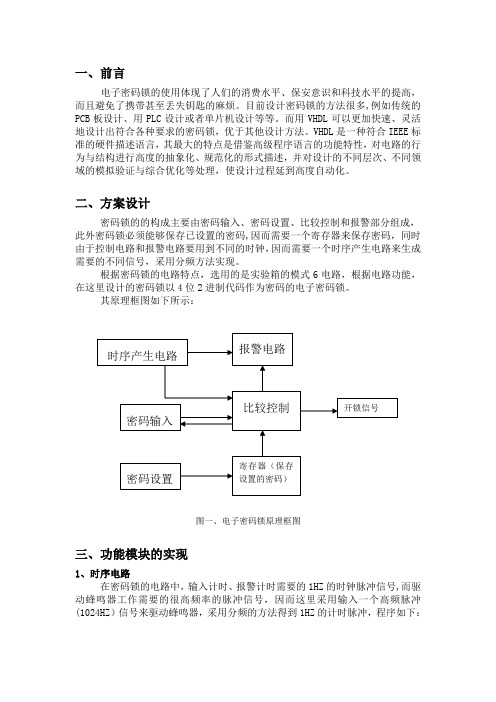

二、方案设计密码锁的的构成主要由密码输入、密码设置、比较控制和报警部分组成,此外密码锁必须能够保存已设置的密码,因而需要一个寄存器来保存密码,同时由于控制电路和报警电路要用到不同的时钟,因而需要一个时序产生电路来生成需要的不同信号,采用分频方法实现。

根据密码锁的电路特点,选用的是实验箱的模式6电路,根据电路功能,在这里设计的密码锁以4位2进制代码作为密码的电子密码锁。

其原理框图如下所示:图一、电子密码锁原理框图三、功能模块的实现1、时序电路在密码锁的电路中,输入计时、报警计时需要的1HZ的时钟脉冲信号,而驱动蜂鸣器工作需要的很高频率的脉冲信号,因而这里采用输入一个高频脉冲(1024HZ)信号来驱动蜂鸣器,采用分频的方法得到1HZ的计时脉冲,程序如下:process(clk_1k)variable cnt1:integer:=0;beginif rising_edge(clk_1k) thenif cnt1=512 thenclk_1〈=not clk_1;cnt1:=0;else cnt1:=cnt1+1;end if;end if;end process;程序说明:clk_1k为输入的1024HZ高频脉冲,cnt为分频得到的1HZ计时脉冲。

2、密码设置为了安全性,密码锁必须能够重复的设定密码,在设定密码锁后,应该设置一个寄存器来存储设定的密码,程序如下:process(rst,password,enter_p) isbeginif rst='0’ thenif enter_p=’1' thenram〈=password;en1<='1';end if;end if;end process;程序说明:rst低电平时所有的模块复位,只有密码设置模块工作;password为设置密码时的输入端,ram就是存储密码的寄存器;enter_p为在这里为密码设置使能端,高电平有效.密码设置的仿真波形如下图,由图中可以清楚地看到在enter_p高电平时寄存器ram中得到了输入的密码1001。

基于FPGA的智能密码锁设计

基于FPGA的智能密码锁设计摘要本文简述了VHDL语言的功能及其特点,介绍一种用EDA技术和VHDL语言,在Quartus Ⅱ环境下,设计一种新型的智能密码锁,该密码锁具有密码预置和误码报警等功能,用一片FPGA(Field Programmable Gate Array)现场可编程门阵列芯片实现,从而大大简化了系统结构,降低成本,提高了系统的保密性和可靠性。

它体积小,功耗低,价格便宜,安全可靠,维护和升级都十分方便,具有较好的应用前景。

关键词:智能密码锁、硬件描述语言、电子设计自动化、Quartus IIAbstractThe paper introduces the function and characteristic of VHDL language. A new type intelligent digital password lock is designed using VHDL language. An FPGA (Field Programmable Gate Array) chips is adopted in this design, thus greatly simplifying the system structure, reduce cost and improve the system of confidentiality and reliability .This new digital intelligent has better application prospect based on its small volume, low power, security and easy maintenance and upgrade.Keywords:intelligent loc k、VHD L、ED A、Quartus II目录引言 (3)1 VHDL语言特点 (3)2 智能密码锁的设计要求 (4)3 智能密码锁的电路组成 (4)3.1密码锁输入电路 (4)3.2密码锁控制电路 (4)3.3 密码锁输出显示电路 (4)4 密码锁输入电路的设计 (5)4.1 时序电路 (5)4.2 键盘扫描电路 (8)4.3 键盘消抖电路 (9)4.4 键盘译码电路 (10)4.5 按键存储电路 (13)4.6 智能密码锁控制电路 (14)5 结论 (23)谢辞 (24)参考文献 (25)引言随着社会物质财富的日益增长,安全防盗已成为全社会问题。

基于FPGA的电子密码锁设计

基于FPGA的电子密码锁设计一、设计要求:1、开锁代码为8位二进制,当输入代码的位数和位值与锁内给定的密码一致,且按规定程序开锁时,方可开锁,并点亮开锁指示灯。

否则,系统进入“错误”状态,并发出报警信号。

2、开锁程序有设计者确定,并要求所内给定的密码可调,且预置方便,保密性好。

3、串行电子密码锁的报警方式是点亮指示灯,并使喇叭鸣叫报警,直到按下复位开关,报警才停止。

此时,电子密码锁又进入等待下一次开锁的状态。

二.设计说明与提示:1.该题目的主要任务是产生一个开锁信号OPEN,而开锁信号的形成条件是,输入代码和已设密码相同。

实现这种功能的电路构思有多种,本题目运用两片8位锁存器,一片存入密码,另一片输入开锁代码,通过比较的方式,若两者相等,则形成开锁信号。

2.在开锁信号产生时,要求输出声,光信号,声音的产生由开锁信号触动扬声器工作,光信号由开锁信号点亮LED指示灯。

3.用按钮开关的第一个动作信号触发一个5秒定时器,若5秒内无开锁信号产生,让扬声器发出特殊音响,以示警告,并输出一个信号推动LED不断闪烁。

三.设计思想:电子密码锁的系统结构框图分成两大部分:控制器和处理器。

整个系统的输入信号有一个时钟脉冲CLK ,输出信号有表示开锁,关锁信号的红灯,绿灯以及报警信号SPEAKER。

控制器中的所有按键按下时均为高电平,即高电平有效。

RW 为“密码设定”信号, OK 为“确定”信号, RED=‘0’GREED=‘1’为开锁信号CNT 表示上一位密码正确时,控制器给出的可进行下一位二进制密码比较的信号,OPEN=‘1’为控制器给出的锁开信号, OPEN=‘0’为控制器给出的密码错误信号。

处理器中有一个计数器,计数器C1用是用来记录从第一个按钮触动后的5秒内若未将锁打开(即输入正确密码时间超过5秒),则电路自动复位并进入自锁状态,使之无法再打开,并由扬声器发出持续20秒的报警信号。

四、设计程序与部分分析:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity lock_m isport(key:in std_logic_vector(7 downto 0);clk,clk1,ok,rw: in std_logic;red,green,speaker,rwled,okrw:out std_logic);end lock_m;architecture behav of lock_m issignal ok1,ok2,ok0,prr,start,pdan,rw1,rin:std_logic :='0';signal sbuf1,sbuf2,keyin:std_logic_vector(7 downto 0):="";signal mmst: std_logic_vector(7 downto 0):="";signal cnt:std_logic_vector(2 downto 0):="000";signal cnt1:std_logic_vector(4 downto 0):="00000";beginprocess(clk) ---定义个存储器将密码存放在keyin中beginif clk'event and clk='1' thenkeyin<=key;end if;end process;prr<=pdan or rw1 or rin or ok;st: process(keyin,prr,ok1) -----第一次修改密码beginif ok1='1' then start<='0';elsif (keyin/="" and prr='0') thenstart<='1';else start<='0';end if;end process;inkey: process(key,start,clk) ----输入密码时间进入记时状态beginif clk'event and clk='1' then ok1<='0';ok2<='0';if start='1' then sbuf1<=keyin; ----将密码放入rom1暂存器中if ok='1' then ok2<='1';elsif cnt="100" then cnt<="000" ;ok1<='1'; --5秒到将cnt值零将ok1值置高else cnt<=cnt+'1';end if ;else cnt<="000";sbuf1<=sbuf1; ----当start=‘1’时cnt永远保持‘0’end if;end if;end process;pandan : process(ok,ok1,ok2,clk,start) ---输入密码用于判断密码是否正确beginif ok2='1' or ok1='1' then pdan<='1'; ------开锁信号elsif clk'event and clk='1' thenif pdan='1' thenif cnt1="10011" thenpdan<='0'; --20秒后判断结束,进入等待外部输入状态elsecnt1<=cnt1+'1';end if;elsecnt1<="00000"; ---等待状态时cnt1一直为‘0’end if;end if;end process;comp: process(pdan,rw1,sbuf1,mmst,rin,clk1) -----显示程序beginif pdan='1' then ------开锁信号密码正确if sbuf1=mmst then -----红灯灭,绿灯亮red<='0';green<='1';rwled<='0';speaker<='0';okrw<='0';else ------密码错误red<='1';green<='0';rwled<='0';speaker<=clk1;okrw<='0';end if; ----红灯亮,绿灯灭,elsif rw1='1' then ----第一次修改密码显示状态red<='1';green<='0';rwled<='1';speaker<='0';okrw<='0';elsif rin='1' thenred<='0';green<='0';rwled<='1';speaker<='0'; okrw<='1';elsered<='1';green<='0';rwled<='0';speaker<='0';okrw<='0';end if;end process;rewrite:process(rw,keyin,ok0,clk,start,pdan,rin)beginif clk'event and clk='1' thenif ok0='1' then rw1<='0';elsif keyin="" and pdan='0' and rin='0' thenif rw='1' thenrw1<='1';end if;end if;end if;end process;process(rw1,ok,keyin,clk)beginif clk'event and clk='1' thenok0<='0';sbuf2<=keyin;if rw1='1' thenif ok='1' thenok0<='1';if mmst=sbuf2 thenrin<='1';elserin<='0';end if;end if;elseif rin='1' thenif ok='1' thenmmst<=sbuf2;rin<='0';else mmst<=mmst;end if;else null;end if;end if;end if;end process;end behav;五、仿真波形:(密码正确)密码锁默认的密码为“”,当我们第一次设置的密码为key=””,然后按OK键盘确认。

基于FPGA的电子密码锁的研究与设计

论文题目:基于FPGA的电子密码锁设计摘要普通的机械锁保密性不好,防盗性差,而且必须使用钥匙。

但是,基于FPGA设计的电子密码锁与普通的机械锁比较来说,就克服了这些不足之处。

该论文主要描述的是一种电子密码锁的设计方法,这种电子密码锁是基于现场可编程门阵列(FPGA)的电子密码锁。

由FPGA构造的电子密码锁系统中,硬件电路可以实现所有的算法,大幅度提高了西戎的工作可靠性。

为了提高设计的效率,可以在更改设计时只更改FPGA中的控制和接口电路,这是因为FPGA的现场可编程功能,也正是利用这一点,可以将更新后的设计下载到FPGA中,省去了更改外部电路设计的麻烦。

所以,这样的系统既可以使工作的可靠性增强也可以更加方便的升级。

系统所实现的功能:用户给电子密码锁设定一个密码,当使用本机键盘开锁时,该密码与用户设定的密码比较,如果密码正确,则开锁;如果密码不正确,用LED灯报警;允许用户重新输入密码。

关键词电子密码锁;FPGA;硬件描述语言;EDAAbstractFPGA-based design of electronic locks is a small digital system,compared with ordinary mechanical locks,has many unique advantages:confidentiality,security and strong,you can not have the keys,remember a password to unlock.This paper describes an approach based on field programmable gate array(FPGA)devices electronic locks design.Construct systems with FPGA devices,all algorithms entirely by hardware circuit to achieve,making the work system reliability greatly improved.As the FPGA with field-programmable function,when you need to change the design,just change the FPGA control and interface circuitry using EDA tools designed updated downloaded to the FPGA without the need to change the external circuit design,greatly improving the design efficiency.Therefore,the use of digital FPGA development system,not only has high reliability,but also extremely easy to upgrade.System implemented features:electronic locks user to set a password when using the keyboard lock,compared with the password set by the user's password,if the password is correct,then unlock;If the password is incorrect,the speaker alarm,allows the user to re- enter the password.Key wordsElectronic locks;FPGA;Hardware Description Language;EDA目录摘要 (I)Abstract (II)前言 (1)第一章概述 (2)1.1 课题背景 (2)1.2 课题研究的目的和意义 (2)1.3 国内外现状 (3)1.4 课题的主要研究工作 (4)第二章相关知识介绍 (5)2.1 FPGA的相关介绍 (6)2.1.1 可编程逻辑器件 (6)2.1.2 FPGA简介 (7)2.1.3 FPGA应用特点 (7)2.1.4 FPGA的设计流程 (9)2.2 硬件描述语言Verilog (11)2.2.1 Verilog语言简介 (11)2.2.2 Verilog语言的优点 (11)2.2.3 Verilog语言的基本结构 (12)2.3 QuartusⅡ软件开发工具 (12)第三章电子密码锁的总体设计 (14)3.1 设计要求 (14)3.2 系统原理框图 (14)3.3 系统主控制流程框图 (15)第四章电子密码锁的软件设计 (17)4.1 主要功能模块设计 (17)4.1.1 输入模块 (18)4.1.2 显示模块 (19)4.3 电子密码锁的仿真 (19)第五章电子密码锁的硬件实现 (24)5.1 电子密码锁的硬件模块实现 (24)5.2 硬件设备 (24)5.3 硬件的实现 (25)结论 (27)参考文献 (28)致谢 (30)前言基于FPGA的电子密码锁是新型现代化安全管理系统,微机自动识别技术和现代安全管理措施技术,包括生物技术、通信技术、电子和机械电等诸多新技术都在其中体现,重要部门出入口安全防范问题因此得到了解决。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

CPLD/FPGA课程设计项目名称:基于FPGA的数字密码锁设计专业班级:学生学号:学生姓名:指导老师:2016年6月4日摘要本设计是基于现场可编程门阵列FPGA 器件的电子密码锁的设计。

通过Verilog语言控制4位二进制数,组成数字排列,形成一个简单的数字密码锁,假设预设密码为4位数:0000,当输入正确时输出为1、输入错误时输出为0。

同时输出输入的次数,当3次以上输入错误时,输出一个报警信号,即使第四、五次输入正确也输出报警信号。

本设计利用Modelsim软件编写Verilog HDL硬件描述语言程序以实现输入密码、开锁、报警功能。

通过仿真调试,利用可编程器件FPGA的电子密码锁的设计基本达到了预期目的。

关键词:现场可编程门阵列;数字密码锁;Verilog HDL;AbstractThis design is the electronic code lock field programmable gate array FPGA devices based design. By Verilog language control 4-bit binary number, composed of figures arranged to form a simple digital lock, assuming that the default password is 4 digits: 0000, correct output when the input is 1, the output of the input error to zero. At the same time the number of input and output, and when more than three times the input error, an alarm signal is output, even if the fourth and fifth also enter the correct output alarm signal.This design uses Modelsim software write Verilog HDL hardware description language program to implement a password lock, alarm function. The simulation debugging, using the programmable device FPGA design basic electronic locks to achieve the desired purpose.Key words: FPGA;The digital combination lock;Verilog HDL;目录摘要 (I)Abstract (II)第1章所选项目的研究意义 (1)1.1 概述 (1)1.2 数字密码锁的研究现状 (2)1.2.1 数字密码锁的应用 (3)1.2.2 数字密码锁的困难 (3)1.3 本文研究意义 (3)1.4 设计思路 (4)第2章设计方案 (5)2.1 功能定义 (5)2.2 模块设计 (5)第3章系统软件设计 (7)3.1 设计概括 (7)3.2 设计流程 (7)3.2.1 密码存储模块 (7)3.2.2 编码模块 (8)3.2.3 比较模块 (8)3.3 主要程序模块 (9)第4章软件仿真 (13)4.1 仿真过程 (13)4.2 仿真结果 (15)4.3 仿真分析 (16)4.3.1 仿真过程 (16)结论 (17)参考文献 (18)附录1 程序代码 (19)项目创新及特色 (25)第1章所选项目的研究意义1.1 概述数字密码锁是一个小型的数字系统,与普通机械锁相比, 具有许多独特的优点: 保密性好, 防盗性强, 可以不用钥匙, 记住密码即可开锁等。

在人们平时生活中,贵重物品或个人信息资料大多数都已加锁的方式进行保管。

如果使用传统的机械锁进行对物品及资料的保管,那么人们要携带很多把钥匙在身上,携带非常不便,而且钥匙丢失将对物品保管的安全性大打折扣,也为人们的生活及心情带来不便。

随着生活质量的不断提高,加强家庭防盗安全变得非常重要,但传统机械锁的构造过于简单,很容易被打开,从而降低了安全性。

数字密码锁因为它的保密性很高,安全系数也非常高,再加上其不需要携带避免了丢失的可能,省去了因钥匙丢失而需要换锁的麻烦,受到了越来越多的人的欢迎。

随着人们对高科技产品也越来越推崇,在当今社会科技的高度集中和创新,人们对日常生活中保护自身及财产安全的物品非常追捧,对其安全性的要求也非常的高。

为了达到人们对锁具安全性的高要求,加强锁具的安全保密性,用密码锁来取代传统机械锁的锁具是必然趋势。

数字密码锁比传统机械锁具更加的安全[1]。

锁具发展到现在已有若干年的历史了,锁是用于保管物品的器件,用来关住某种器物的一种器具。

其必须用钥匙才能打开。

所以在人们的日常生活中离不开锁,这使得我们队锁具的结构和原理也多少有些了解,因此,就有了不借用钥匙就打开锁的方法。

锁具都存在致命的弱点,比如锁芯采用常见的铜、锌、铝等材料容易遭到暴力破坏,还有就是锁具制作工艺的技术落后,从而导致防盗功能缺失,目前,国内市场的锁具,实际上都不具备真正的防盗功能,在惯偷面前用几件简单工具就可以轻松打开这些锁,其实不是他们多么的高明,而是一般锁具的原理过于简单,面对这一社会现状,新时代提出了锁具必须改革的迫切需求[2]。

安全防盗已成为人们所关注的焦点。

然而传统机械弹子锁安全性低,密码量少且需时刻携带钥匙使其无法满足一些特定场合的应用要求,特别是在人员经常变动的公共场所,目前使用的电子密码锁主要有两个方案:一是基于单片机用分立元件实现的,二是通过现代人体生物特征识别技术实现的,前者电路较复杂且灵活性差,无法满足应用要求;后者有其先进性但需考虑成本和安全性等诸多因素。

基于此,本文设计了一种新型电子密码锁,采用FPGA芯片,目前以硬件描述语言(Verilog 或VHDL)所完成的电路设计,可以经过简单的综合与布局,快速的烧录至 FPGA 上进行测试,是现代 IC 设计验证的技术主流[3]。

这些可编辑元件可以被用来实现一些基本的逻辑门电路(比如AND、OR、XOR、NOT)或者更复杂一些的组合功能比如解码器或数学方程式。

在大多数的FPGA里面,这些可编辑的元件里也包含记忆元件例如触发器(Flip-flop)或者其他更加完整的记忆块。

FPGA一般来说比ASIC(专用集成芯片)的速度要慢,无法完成复杂的设计,而且消耗更多的电能。

但是他们也有很多的优点比如可以快速成品,可以被修改来改正程序中的错误和更便宜的造价。

厂商也可能会提供便宜的但是编辑能力差的FPGA。

因为这些芯片有比较差的可编辑能力,所以这些设计的开发是在普通的FPGA上完成的,然后将设计转移到一个类似于ASIC的芯片上。

另外一种方法是用CPLD(复杂可编程逻辑器件备)[4]。

因此,随着电子技术的飞速发展数字密码锁的产生是必然,其在使用的方便性、防盗报警功能、智能管理等方面都是传统机械锁无法比拟的,在对安全性有较高要求的设施及场所中得到了广泛应用。

1.2数字密码锁的研究现状现如今,随着高新技术的涌入,对传统锁具进行了很大的的改进,锁具的防盗性能得到了充分的加强,由传统锁具改进的智能密码锁已成为现如今安防系统中最强大的组成部分,它的作用是每一个传统机械锁具无法取代的。

由于其在市场中巨大的潜力,国内外许多的公司都投入很大的人力、物力来从事智能数字密码锁的研究开发生产。

目前,市场上比较先进的智能电子密码锁分别有:IC卡电子密码锁、射频卡式电子密码锁、红外遥控电子密码锁、指纹识别电子密码锁和瞳孔识别电子密码锁等。

IC 卡电子密码锁成本低,体积小,卡片本身无须电源等优点占领了一定的市场份额,但是由于有机械接触,会产生接触磨损,而且使用不太方便,在一定程度上限制了它的应用;射频卡式电子密码锁是非接触式电子密码锁,成本也不太高,体积跟IC卡密码锁相当,卡片使用感应电源,重量很轻,技术成熟,受到了广泛的欢迎,但是与IC卡电子密码锁相比,成本偏高;指纹识别电子密码锁和瞳孔识别电子密码锁可靠性很高,安全性是目前应用系统中最高的,但是成本高昂,还没进入大众化使用阶段[5]。

在国外,美国、日本、德国的电子密码锁保密性较好,并结合感应卡技术,生物识别技术,使电子密码锁系统得到了飞跃式的发展。

这几个国家的密码锁识别的密码更复杂,并且综合性比较好,已经进入了成熟期,出现了感应卡式密码锁,指纹式密码锁,虹膜密码锁,面部识别密码锁,序列混乱的键盘密码锁等各种技术的系统,它们在安全性,方便性,易管理性等方面都各有特长,新型的电子密码锁系统的应用也越来越广。

1.2.1 数字密码锁的应用密码锁具有安全性高、成本低、功耗低、易操作等优点。

在安全技术防范领域,具有防盗报警功能的电子密码锁逐渐代替传统的机械式密码锁,克服了机械式密码锁密码量少、安全性能差的缺点,使密码锁无论在技术上还是在性能上都大大提高一步[6]。

随着大规模集成电路技术的发展,出现了带微处理器的智能密码锁,它除具有电子密码锁的功能外,还引入了智能化管理、专家分析系统等功能,从而使密码锁具有很高的安全性、可靠性,应用日益广泛[7].随着人们对安全的重视和科技的发展,许多电子智能锁(指纹识别、IC 卡辨认)已在国内外相继面世。

但是这些产品的特点是针对特定的指纹和有效卡,只能适用于保密要求的箱、柜、门等。

而且指纹识识别器若在公共场所使用存在容易机械损坏,IC卡还存在容易丢失、损坏等特点。

加上其成本较高,一定程度上限制了这类产品的普及和推广。

鉴于目前的技术水平与市场的接收程度,电子密码锁是这类电子防盗产品的主流[8]。

1.2.2 数字密码锁的困难1.Verilog HDL语言的程序设计和控制函数的调用编写Verilog HDL语言时,输入4位密码未能和程序预设密码进行比较,无论密码输入正确与否,锁均不打开,而且报警计数器也不进行+1操作。

在程序编译时,函数调未能调用成功。

2.报警程序模块的设计计数器+1操作进行时,系统中断,从而导致系统重置,计数器又从0开始进行+1操作,导致系统不报警。

3.用Modelsim仿真软件波形时,为准确输出正确波形在程序编写时,未考虑初始密码,导致波形错误。

1.3 本文研究意义电子杂志、报刊经常刊登有密码开关、密码锁这样的电路,大多数是使用常用的数字电路,如CD4017,然后通过不同的连接方式实现密码控制功能。

这种电路的特点就是密码修改只能通过改变电路的连接来实现,密码很容易被破解,电路复杂,故障率高。