CPLD流水灯控制器

单片机开发板 SY_03091 说明书

目录第一章:ALTERA_CPLD开发板简介 (3)1-1.SY_03091开发板的特性简介 (3)1-2.SY_03091开发板的构成和工作原理 (4)第二章:开发板使用说明 (5)2-1.系统操作软件安装 (5)2-2.注册授权文件安装 (8)2-3.硬件驱动软件安装 (10)2-4.开发板连接和板上跳线设置 (12)2-5.在线下载功能的使用 (13)第三章:开发板用器件资料及说明 (17)3__1.EPM7128SLC (17)3__2.EPM7032SLC (18)3—3.HT46R47 (19)第四章:开发板器件表附件清单 (20)4—1.调试用源程序 (20)4-2.原理图....................................................附录插页4-3.包装清单.. (26)第五章:其它51类实验板简介 (27)5-1.51DEMO I/O板简介 (27)5-2.A/D89C51数模转换实验板简介 (28)5-3.流水灯控制器(12路) (30)5-4.SY0606开发板 (31)5-5.Atmel_ISP下载线(选配自购件) (32)5-6.Altera_ISP下载线(选配自购件) (33)*********公司其它产品简介见软件盘中电子版文件*********第一章:ALETRA__CPLD开发板简介1-1.SY_03091开发板的特性简介1. 电源适应性强,可随意使用无极性8~15V电源或DC+5V电源供电。

2. CPLD时钟是由单片机“HT46R47”产生,并且可随意改变其时钟频率。

3. 本开发板可直接支持ALTERA的 EPM7128SLC(PLCC84);EPM7064SLC(PLCC68); EPM7064SLC/EPM7032(PLCC44)等芯片為主控元件。

4. 有一组四字节数码管显示器硬件电路。

5. 有2组16位LED发光管连接电路,可作LED跑马灯实习,演示。

EDA流水灯论文(VHDL)

滨江学院课程论文(可编程器件原理与应用)题目基于VHDL语言的流水灯设计学生姓名王秋阳学号20082305047院系滨江学院专业电子与信息工程指导教师刘建成二零一零年十二月三十日一、任务:采用ALTERA 公司的EPM7128SLC84-10芯片,通过VHDL 语言设计一个流水灯电路。

流水灯样式必须大于3种,且可以通过按键调节显示样式;可以通过按键调节流水灯变化快慢;当前流水灯样式和变化速度能够通过数码管显示出来;(附加:具有按键声)二、设计框图(框图说明)1MHZ 周期信号经过2个100分频,得到100HZ ,再经过1个10分频得到10HZ 信号,传给速度控制模块,得到需要的速度周期信号,然后传给样式选择模块,样式选择模块直接输出彩灯样式;控制模块通过接受两个按键信号,同时控制速度控制模块和样式选择模块;译码扫描模块通过判断控制模块,扫描数码管显示当前彩灯样式和彩灯变化速度;按键信号通过延时模块输出按键发生信号。

速度按键 样式按键控制模块速度控制样式选择译码和扫描数码显示彩灯显示1000HZ 信号100HZ 信号蜂鸣器三、原理图(CPLD内部原理说明)从原理图中可以看到,一共有8种模块,D触发器的作用是对按钮进行消抖,除D触发器之外的7个模块功能及作用如下:f100和f10分别是100和10的分频器,speed模块的作用是对彩灯变化速度进行控制,而style_switch模块的作用是对彩灯样式进行调节。

Control 模块接收按键信号对样式和速度进行总的控制。

Show模块是对速度值和样式值进行译码并进行扫描数码管,将当前样式和速度状态显示出来。

Delay模块则是对按键声的延时。

四、各个模块设计(波形仿真)1.f100模块功能:100分频波形仿真:VHDL代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity f100 is --100分频port(clk:in std_logic;sec:out std_logic);end entity f100;architecture getsec of f100 issignal secout : std_logic :='1';beginprocess(clk) isvariable count100: integer range 0 to 50;beginif clk'event and clk='1' thencount100:=count100+1;if count100=50 thensecout<=not secout;count100:=0;end if;end if;end process;sec<=secout;end architecture getsec;2.f10模块功能:10分频波形仿真:VHDL代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity f10 is –-10分频port(clk:in std_logic;sec:out std_logic);end entity f10;architecture getsec of f10 issignal secout : std_logic :='1';beginprocess(clk) isvariable count10: integer range 0 to 5;beginif clk'event and clk='1' thencount10:=count10+1;if count10=5 thensecout<=not secout;count10:=0;end if;end if;end process;sec<=secout;end architecture getsec;3.speed模块功能:根据DATE输入端的数值大小,产生不同频率的周期信号,从而达到控制彩灯变化速率的目的。

cpld原理

cpld原理

CPLD是复杂可编程逻辑器件(Complex Programmable Logic Device)的缩写,它是一种集成电路芯片,通过对其内部的逻

辑门、触发器和可编程互连资源进行编程,实现不同的逻辑功能。

CPLD的原理主要基于可编程逻辑阵列(PAL)和可编程压缩

阵列(GAL)。

它由一个或多个可编程逻辑单元(PLU)或宏单元组成,每个单元包含逻辑门和触发器等基本逻辑元件。

CPLD的内部结构主要由两部分组成:可编程逻辑单元(PLU)和全局输入/输出(IO)资源。

PLU是CPLD的核心部分,它由多个可编程逻辑单元组成,

每个单元接收输入信号并输出相应的逻辑运算结果。

其中每个单元可以实现任意的逻辑功能,并通过互连通道与其他单元进行连接。

全局IO资源用于连接CPLD与外部器件,包括输入输出引脚、时钟信号等。

它提供了与外界通信的接口。

CPLD的编程通常采用硬件描述语言(HDL)或可编程逻辑阶

梯(PLD)语言,如VHDL、Verilog等。

通过编写逻辑描述

代码,并使用专门的软件工具进行综合、布局和布线,可以将逻辑功能转化为CPLD内部资源的配置和连接。

在编程完成后,CPLD可以实现各种逻辑功能,如组合逻辑、

时序逻辑、状态机等。

它还可以实现多个逻辑块之间的通信和控制,具有较高的灵活性和可扩展性。

总而言之,CPLD原理是通过对其内部逻辑资源进行编程,实

现不同的逻辑功能。

它由可编程逻辑单元和全局IO资源组成,通过编写逻辑描述代码并使用专门的软件工具进行编程,可以实现各种逻辑功能,并与外部器件进行通信和控制。

流水灯实验原理

流水灯实验原理

流水灯实验是一种常见的电子原型实验,其原理是利用计时器和移位寄存器来控制一组LED灯的亮灭状态,实现灯光顺序

循环变化的效果。

在流水灯实验中,LED灯的亮灭状态是由移位寄存器控制的。

移位寄存器是一个存储二进制数据的器件,它具有将数据从一个位置移动到另一个位置的功能。

通过这种移位操作,可以实现LED灯的顺序变化。

将多个LED灯连接到移位寄存器的输出引脚上,然后将计时

器的时钟信号连接到移位寄存器的时钟输入引脚上。

计时器的时钟信号用于触发移位寄存器的移位操作。

当计时器的时钟信号输入时,移位寄存器会将存储在其中的数据向移位方向移动一位。

移动之后,每个LED灯的状态就发

生了变化,从而实现了灯光顺序的循环变化。

为了控制LED灯的亮灭状态,可以使用二进制计数器作为移

位寄存器的输入。

二进制计数器的输出可以连接到LED灯的

输入引脚上,根据计数器的计数值决定LED灯的亮灭状态。

通过调节计时器的时钟频率和移位寄存器的移位方式,可以实现不同的流水灯效果。

例如,可以设置较快的时钟频率和循环移位的方式,使LED灯的亮灭状态快速顺序变化;或者设置

较慢的时钟频率和单向移位的方式,使LED灯的亮灭状态缓

慢顺序变化。

通过流水灯实验,可以更好地理解计时器、移位寄存器和LED灯的工作原理,同时也能够培养学生的实验操作能力和创新思维。

PLC控制流水灯系统的设计

目录第一章绪论 (3)1.1 前言 (3)1.1流水灯系统的意义、现状及要求 (4)1.1.2 技术现状 (5)1.2彩灯的发展 (6)1.2.1 彩灯的最初来源 (6)1.2.2 彩灯给城市带来的五彩缤纷 (6)1.3PLC的发展前景及趋势 (7)1.4PLC的定义及特点 (11)第2章硬件电路的设计 (12)2.1流水灯电路的设计 (13)2.2开关电路的设计 (14)第3章软件设计 (15)3.1软件设计的方案 (11)3.2PLC结构 (14)3.3工作原理 (15)3.4编程语言 (16)3.5S7-200的指令系统 (19)3.6流水灯的工作要求 (18)3.7梯形图 (22)结束语 (41)致谢 (42)参考文献 (43)PLC控制流水灯系统的设计[摘要]本次毕业设计是应用S7-200 PLC流水灯设计的硬件电路,并利用OB1的梯形图控制程序设计。

通过控制S7-200 PLC的定时继电器的功能来实现各彩灯按一定的规律点亮和熄灭。

接通延迟定时器SD的特点(如果RLO有正跳沿,则接通延迟定时器启动指令,以设定的时间值启动指令的定时器)。

这种控制电路结构简单,可靠性高,应用性强;软件程序适应范围广,对各彩灯按一定的规律点亮和熄灭的控制,只需要改变相应的定时器的时间接通即可。

第一章绪论前言随着科技的飞速发展,无论在日常生活中,还是在工农业发展中,PLC具有广泛的应用。

PLC的一般特点:抗干扰能力强,可靠性极高、编程简单方便、使用方便、维护方便、设计、施工、调试周期短、易于实现机电一体化。

PLC总的发展趋势是:高功能、高速度、高集成度、大容量、小体积、低成本、通信组网能力强。

本次毕业设计是应用S7-200 PLC流水灯设计的硬件电路,并利用OB1的梯形图控制程序设计。

通过控制S7-200 PLC的定时继电器的功能来实现各彩灯按一定的规律点亮和熄灭。

接通延迟定时器SD的特点(如果RLO有正跳沿,则接通延迟定时器启动指令,以设定的时间值启动指令的定时器)。

cpld工作原理

cpld工作原理什么是CPLD?CPLD(Complex Programmable Logic Device)是一种芯片,它由许多可编程逻辑单元(Programmable Logic Units,PLUs)组成,并具有可编程的互连资源。

CPLD 具有高度的可编程性和灵活性,使得它在数字电路设计中有着广泛的应用。

CPLD的结构和组成CPLD主要由可编程逻辑单元(PLU)、输入输出(I/O)单元、时钟管理单元和互连资源组成。

可编程逻辑单元(PLU)PLU是CPLD的核心部件,它由可编程逻辑门阵列(PLA)、寄存器和触发器等组成。

PLU负责执行逻辑功能,并根据输入信号的状态产生相应的输出信号。

输入输出(I/O)单元I/O单元用于与外部世界进行数据交互,它包括输入引脚和输出引脚。

输入引脚接收外部信号输入到CPLD中,输出引脚将CPLD内部处理后的数据输出到外部。

时钟管理单元时钟管理单元负责生成和管理时钟信号。

时钟信号在数字电路中起到同步和节拍控制的作用,它使得CPLD中的逻辑电路按照特定的时序运行。

互连资源互连资源是CPLD中用于实现逻辑连接的部分,它包括互连开关矩阵和多级互连总线。

互连开关矩阵将PLU、I/O单元和时钟管理单元连接起来,以实现信号的传输和路由。

多级互连总线用于连接不同的互连开关矩阵,以实现更复杂的互连结构。

CPLD的工作原理CPLD的工作原理可以概括为以下几个步骤:1.配置(Configuration)CPLD首先需要进行配置,即将用户设计的逻辑电路加载到CPLD中。

配置通常使用编程器或者其他特定的工具来完成。

配置后,CPLD内部的可编程逻辑单元、互连开关矩阵等部件将按照配置信息进行初始化。

2.输入信号检测和处理一旦CPLD被配置完成,它将开始不断地检测输入信号。

输入信号可以是来自外部引脚的电平变化,也可以是来自内部其他部件的信号。

CPLD根据输入信号的状态和用户预先定义的逻辑电路进行比较,并根据逻辑电路的要求产生相应的输出。

cc2530按键控制流水灯

cc2530按键控制流水灯本次设计用LED1,LED2,LED3 灯及按键S1 为外设。

采用P10、P11、P14 口为输出口,驱动LED1/LED2/LED3,P01 口为输入口,接受按键信号输入(高电平为按键信号)。

1.高性能2.4G 射频模块Q2530RFQ2530RF是丘捷技基于TI公司第二代2.4GHz IEEE 802.15.4 /RF4CE/ZigBee的第二代片上系统解决方案CC2530 F256的全功能模块,集射频收发及MCU控制功能于一体。

外围原件包含一颗32MHz晶振和一颗32.768KHz晶振及其他一些阻容器件。

射频部分采用巴伦匹配和外置高增益SMA天线,接收灵敏度高,发送距离远,空旷环境最大传输距离可达400米。

模块引出CC2530所有IO口,便于功能评估与二次开发。

2.多功能开发板Q2530EB多功能扩展板Q2530EB 可支持多种射频主控模块(例如Q2530RF等),配置有串口液晶显示接口,USB供电接口,DC 5V电源接口,电池接口,RS232接口,DEBUG接口,五向按键及指示灯,红外遥控信号接收/发射等模块。

所有的外设均通过SPI总线/UART /DEBUG等接口与射频模块Q2530RF 相连,并完全受Q2530RF 控制和访问。

多功能仿真扩展板Q2530EB 采用三种电源供电方式:DC 5V供电、USB接口供电、电池供电,可在插座P5设置跳线选择,PIN1-PIN2 为电池供电,PIN2-PIN3 为外接直流电源或者USB接口供电。

电源开关为P4。

Q2530EB 板卡背面的电池盒可放置3节5号干电池,输出电压3.4~4.5V,板载电源电路将其调整到+3.3V 稳定的直流电压输出供后级使用。

当电池电压低于3.4V 时,应更换电池以保持模块正常工作。

Q2530EB 带有1个DC 5V的电源适配器接口P2和一个USB接口P1,输入电压经过稳压器降压为+3.3V输出供后极使用。

基于单片机智能温控流水灯

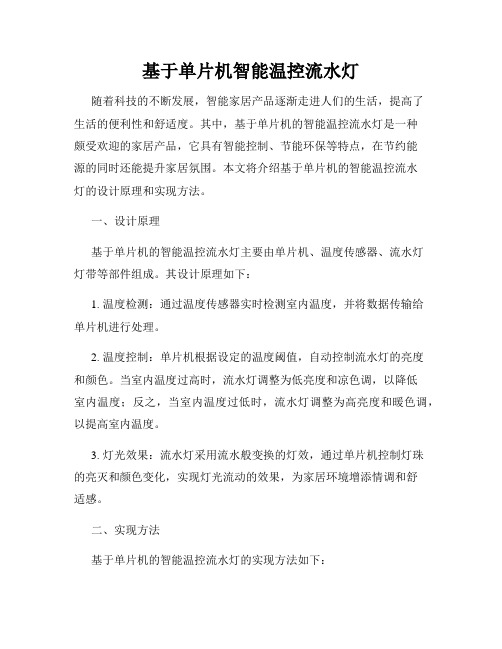

基于单片机智能温控流水灯随着科技的不断发展,智能家居产品逐渐走进人们的生活,提高了生活的便利性和舒适度。

其中,基于单片机的智能温控流水灯是一种颇受欢迎的家居产品,它具有智能控制、节能环保等特点,在节约能源的同时还能提升家居氛围。

本文将介绍基于单片机的智能温控流水灯的设计原理和实现方法。

一、设计原理基于单片机的智能温控流水灯主要由单片机、温度传感器、流水灯灯带等部件组成。

其设计原理如下:1. 温度检测:通过温度传感器实时检测室内温度,并将数据传输给单片机进行处理。

2. 温度控制:单片机根据设定的温度阈值,自动控制流水灯的亮度和颜色。

当室内温度过高时,流水灯调整为低亮度和凉色调,以降低室内温度;反之,当室内温度过低时,流水灯调整为高亮度和暖色调,以提高室内温度。

3. 灯光效果:流水灯采用流水般变换的灯效,通过单片机控制灯珠的亮灭和颜色变化,实现灯光流动的效果,为家居环境增添情调和舒适感。

二、实现方法基于单片机的智能温控流水灯的实现方法如下:1. 硬件设计:选择合适的单片机控制芯片,并连接温度传感器、流水灯灯带等硬件部件,搭建硬件系统。

2. 软件编程:编写单片机的程序,实现对温度传感器数据的读取和处理,以及灯光效果的控制。

通过逻辑判断和控制指令,实现温度检测和灯光调节的功能。

3. 装配调试:将硬件系统组装完善,并进行功能调试和性能优化,确保智能温控流水灯的正常工作和稳定性。

三、应用优势基于单片机的智能温控流水灯具有以下优势:1. 智能化控制:通过单片机程序的设计,实现对室内温度的智能检测和控制,提高了灯光的智能化程度。

2. 节能环保:根据实时温度调节灯光亮度和颜色,避免了灯光长时间高亮度造成的能源浪费,节约了能源资源。

3. 美化家居:流水灯的灯效设计独特,能够为家居环境增添美感和舒适度,营造出温馨浪漫的氛围。

综上所述,基于单片机的智能温控流水灯是一种具有智能化控制和节能环保等特点的家居产品,其设计原理和实现方法都相对简单易行。

几种流水灯程序

几种流水灯程序1. 基础流水灯程序:用来控制1个led灯,使其呈现流水灯的效果,代码如下: int led = 13; // 让led连接到电路的13号引脚void setup(){pinMode(led, OUTPUT); // 设置13号引脚的模式为输出}void loop(){digitalWrite(led, HIGH); // 让led灯亮起来delay(1000); // 等待1秒digitalWrite(led, LOW); // 让led灯熄灭int led1 = 13;int led2 = 12;int led3= 11;int led4 = 10;void setup (){pinMode (led1, OUTPUT);pinMode (led2, OUTPUT);pinMode (led3, OUTPUT);pinMode (led4, OUTPUT);}void loop (){digitalWrite (led1, HIGH);delay (500);digitalWrite (led1, LOW);digitalWrite (led2, HIGH);delay (500);digitalWrite (led2, LOW);digitalWrite (led3, HIGH);delay (500);digitalWrite (led3, LOW);digitalWrite (led4, HIGH);delay (500);digitalWrite (led4, LOW);delay (1000);}3.调节速度的流水灯程序:将第一个流水灯程序增加一个模拟变量,使得可以即时调节灯泡亮度以及闪烁速度,以及可以控制单个led灯或多个led灯,其代码如下:4.设置模式的流水灯程序:将流水灯程序改进,使得应用于不同的场景,可以调节闪烁模式,如快速,慢速,长亮等,其代码如下:。

cpld原理

cpld原理CPLD原理CPLD全称是Complex Programmable Logic Device,中文名称为复杂可编程逻辑器件。

它是一种集成电路芯片,可以通过编程来实现逻辑功能。

CPLD由可编程逻辑器件(PLD)和可编程器件(PROM)组成,其中可编程逻辑器件包括可编程逻辑阵列(PLA)、可编程的中间级逻辑和可编程输入/输出(I/O)等组件。

CPLD的原理是通过编程来配置其逻辑功能。

首先,需要使用HDL (Hardware Description Language)来描述所需的逻辑功能。

常用的HDL语言包括VHDL和Verilog。

接着,使用逻辑综合工具将HDL代码转换成相应的逻辑门电路。

然后,将逻辑门电路映射到CPLD的可编程逻辑阵列中,通过PLA和中间级逻辑来实现复杂的逻辑功能。

最后,将输入/输出引脚与CPLD的可编程输入/输出连接,完成CPLD的配置。

CPLD的核心是可编程逻辑阵列(PLA),它由一系列可编程逻辑单元(PLU)组成。

每个PLU包含逻辑门电路和触发器,可以实现基本的逻辑功能和存储功能。

PLA中的PLU可以通过编程控制来连接或断开,从而实现不同的逻辑功能。

CPLD的可编程输入/输出可以用于与外部设备进行通信,如与其他芯片进行数据交换或与外部电路连接。

CPLD的优点之一是灵活性。

由于其可编程性,CPLD可以根据实际需求进行定制化设计。

它可以适应不同的应用场景,并实现不同的逻辑功能。

此外,CPLD还具有较高的集成度和可靠性,可以在小尺寸的芯片上实现复杂的逻辑功能。

CPLD在数字电路设计和嵌入式系统中起着重要的作用。

它可以用于实现各种逻辑功能,如控制逻辑、数据处理和通信接口等。

在数字电路设计中,CPLD可以替代离散逻辑电路,简化电路设计和布局。

在嵌入式系统中,CPLD可以与微处理器或微控制器配合使用,实现系统级的控制和接口功能。

除了CPLD,还有一种类似的器件称为FPGA(Field Programmable Gate Array),它与CPLD有一些相似之处,但也存在一些差异。

上海电机学院本科毕业设计(论文)选题汇总表概要

孙强

副教授

34

曹杰

基于PWM控制器的便携式DC-DC电源设计

√

朱一群

讲师

35

张游

PWM基带信号的产生与检测

√

胡之惠

讲师

36

黄盛

网络入侵异常检测新技术研究

√

贾铁军

教授

37

陆晓健

利用CDMA网络的轨道交通车辆检测系统

√

胡兰馨

副教授

38

张杰

利用Verilog设计和实现16位RISC CPU

√

王淮亭、陈智鹏

副教授

39

林华丞

基于工业总线的网络通讯系统研究

√

卢秋红、宋晓勇

工程师

14

李巧婷

智能机器人数据通讯系统的研究

√

卢秋红、宋晓勇

工程师

15

陈尧

社区视频监控系统之自动监控子系统的设计与实现

√

李健

讲师

16

徐梁

轨道交通Wi-Fi识别乘客支付系统

√

胡兰馨

副教授

17

余德明

轨道交通CDMA乘客支付系统

√

胡兰馨

副教授

18

邵晓慧

网络USB Key身份认证新技术及应用研究

√

贾铁军

教授

19

杨君轩

贾铁军

教授

9

吴豪俊

基于单片机的遥控小汽车的软件设计

√

王淮亭、陈智鹏

副教授

10

张孝萍

利用GSM网络的轨道交通列车区间冗塞控制系统

√

胡兰馨

副教授

11

沈王

多阶语音分离电路的设计研究

√

杨宇

CPLD结构与原理

CPLD结构与原理CPLD的结构和原理可以分为以下几个方面来介绍:1.可编程逻辑阵列(PAL):它是CPLD的主要部分,由多个逻辑单元组成。

每个逻辑单元由逻辑门和触发器构成。

逻辑门用于执行逻辑运算,如AND、OR、NOT等。

触发器用于存储和时序控制,保持和存储数据。

2.级联可编程逻辑单元(CPLD):它是CPLD的另一重要组成部分,由多个逻辑单元级联而成。

级联是通过内部的编程快速内部总线实现的,它可以连接多个逻辑单元以增强CPLD的能力。

3.输入/输出(I/O):CPLD具有多个输入和输出引脚,用于与外部设备进行通信。

I/O引脚可以配置为输入或输出,可以与其他数字电路连接。

CPLD的工作原理如下:1. 设计:首先,设计师使用HDL(Hardware Description Language)编写CPLD的逻辑设计。

HDL是一种用于描述硬件电路的语言,允许设计师按照所需的功能描述电路。

2.编译:设计师将HDL代码编译成器件可读的模式文件。

编译器将HDL代码解析并生成逻辑网表描述。

3.映射:逻辑网表被映射到CPLD的逻辑单元上。

这个过程将逻辑网表的逻辑块映射到CPLD的逻辑单元的布局上,确保逻辑网表能够正确地在CPLD上实现。

4.布局和布线:逻辑单元的布局确定了逻辑单元的位置和布线方案。

布线是将逻辑单元之间的连接线路化的过程。

这个过程确保逻辑单元之间的正确连接。

CPLD相对于其他可编程逻辑设备的优势在于它具有较高的灵活性、较低的功耗和较高的可靠性。

CPLD适用于多种应用,包括数字信号处理、通信、嵌入式系统等。

cpld的应用原理

CPLD的应用原理什么是CPLDCPLD(Complex Programmable Logic Device)是一种高度集成的可编程逻辑器件。

它由一系列可编程逻辑单元(PLD)和可编程电路连通网络(Interconnect Network)组成。

CPLD具有较高的逻辑密度和较低的功耗,适用于各种应用领域,如嵌入式系统、通信设备、工业控制等。

CPLD的工作原理CPLD的工作原理是基于可编程逻辑单元(PLD)和可编程电路连通网络(Interconnect Network)的组合。

PLD包括可编程逻辑阵列(PLA)和可编程输入输出(PIO)两部分,用于实现具体的逻辑功能。

而Interconnect Network则负责连接和配置PLD的内部单元。

在CPLD中,逻辑功能是通过编程来实现的。

用户可以使用硬件描述语言(如VHDL或Verilog)来描述所需的逻辑功能,并通过专门的编程软件将描述好的逻辑功能加载到CPLD中。

加载完成后,CPLD即可按照用户的要求进行逻辑运算和数据处理。

CPLD的应用CPLD在各种应用领域都有广泛的应用,下面是一些常见的应用示例:1.嵌入式系统:CPLD可以用于控制、处理和管理嵌入式系统中的各种外围设备,如键盘、显示器、存储器等。

它可以实现数据的输入输出、时序控制、状态切换等功能。

2.通信设备:CPLD可以用于实现通信设备中的各种协议和接口,如串行通信、以太网、USB等。

它可以提供高速数据传输和高质量的信号处理能力。

3.工业控制:CPLD可以用于工业控制系统中的逻辑控制和信号处理。

它可以实现各种输入输出的逻辑运算、信号转换和测量控制,提高系统的可靠性和稳定性。

4.汽车电子:CPLD可以应用于汽车电子控制单元(ECU)中,实现各种车载系统的控制和监测。

它可以处理传感器数据、驱动执行器、协调各个子系统之间的交互等。

5.航空航天:CPLD在航空航天领域有着广泛的应用。

它可以用于飞机系统和卫星系统中的控制和通信,提供高度可靠和高性能的功能实现。

用单片机实现流水灯的控制设计

用单片机实现流水灯的控制设计1.引言当今时代是一个新技术层出不穷的时代,在电子领域尤其是自动化智能控制领域,传统的分立元件或数字逻辑电路构成的控制系统,正以前所未见的速度被智能控制系统所取代。

单片机具有体积小、功能强、成本低、应用面广等优点,可以说,智能控制与自动控制的核心就是单片机。

目前,一个学习与应用单片机的高潮正在工厂、学校及企事业单位大规模地兴起。

学习单片机的最有效方法就是理论与实践并重,本设计课题是流水灯的控制设计,流水灯是一串按一定的规律像流水一样连续闪亮。

流水灯控制是可编程控制器的一个应用,其控制思想在工业控制技术领域也同样适用。

2.硬件组成2.1 总体方案设计分析要求用8255的A口和B口做为输出,接16个发光二极管,从而实现16位流水灯的显示效果,基本的界限可如下图A所示,在C口的地两位接两个开关,实现两个扩展功能的控制。

i:基本流水灯显示电路A口和B口两个端口不能同时复制,从而在试验中可以用BX进行需要复制的数据的存储,因为BX可以分从BH BL两个部分进行独立的操作,在本次试验中用BH对A口进行赋值,用BL对B口进行赋值,通过演示一段时间再对BH BL 进行移位和输出,实现流水灯的效果。

ii:正反方向选择把PC.0口接在开关上,编写程序对C端口的数据进行读取,并进行判断,使得当PC.0为高电平的时候则灯进行左移,同时B口与A口相反。

iii:快慢速度控制把PC.1口接在开关上,编写程序对C端口的数据进行读取,并进行判断,使得当PC.1为高电平的时候则延时的时间缩短,使得流水灯的流水速度加快,低电平的时候则进行延时的时间变长,使得流水灯的流水速度加快。

3硬件原理设计A该模块的WR.RD分别练到PC总线接口模块的XIOW和XIORB该模块的数据(AD0~AD7)、地址线(A0~A7)分别连到PC总线接口模块的数据(D0~D7)、地址线(A0~A7)C 8255模块选通线CA连到PC总线接口模块的IOY3D 8255的PA0~PA7连到发光二极管的L1~L8;8255的PB0~PB7连到发光二极管的L9~L16E 8255的PC0 PC1分别练到开关K0 K1F 软件流程框图及程序清单按照单片机系统扩展与系统配置状况,单片机应用系统可分为最小系统、最小功耗系统及典型系统等。

PLC控制的流水灯

目录第一章绪论 (2)1.1引言 (2)1.2采用流水灯的意义和目的 (2)1.3 本次设计的主要内容 (2)第二章主要硬件设备的介绍 (3)2.1可编程控制器的发展历史 (3)2.1.1 可编程控制器的定义 (4)2.1.2 可编程控制器的特点 (4)2.1.3 PLC的基本结构和工作原理 (5)2.2西门子S7-200的硬件组成 (8)第三章电路及软件设计 (10)3.1硬件电路设计 (10)3.1.1流水灯分布图 (10)3.1.2控制系统I/O点及地址分配 (10)3.2软件设计 (10)3.2.1梯形图 (10)3.2.2指令表 (19)第四章系统调试 (21)4.1 系统的连接与运行 (20)4.2 流水灯闪烁 (20)4.3 流水灯的调试 (22)总结 (22)第一章绪论1.1引言随着改革的不断深入,社会主义市场经济的不断繁荣和发展,各大中小城市都在进行亮化工程。

企业为宣传自己企业的形象和产品,均采用广告手法之一:流水灯广告屏来实现这一目的.当我们夜晚走在大街上,马路两旁各色各样的广告灯均可以见到,一种是采用流水灯管做成的各种形状和多中彩色的灯管,另一种为日光等管或白炽灯管作为光源,另配大型广告语或宣传画来达到宣传的效果。

这些灯的亮灭,闪烁时间及流动方向等均可以通过PLC 来达到控制的要求。

可编程控制器PLC:英文全称Programmable Logic Controller ,中文全称为可编程逻辑控制器,是一种数字运算操作的电子系统,专为在社会环境应用而设计的。

它采用一类可编程的存储器,用于其内部存储程序,执行逻辑运算,顺序控制,定时,计数与算术操作等面向用户的指令,并通过数字或模拟式输入/输出控制各种类型的机械或生产过程.作为自动控制装置的核心,它具有功能强,可靠性高等诸多优点。

该装置可以完成各种指令系统训练以及多种控制对象的程序设计训练。

1.2采用流水灯的意义和目的随着社会市场经济的不断发展,各种装饰流水灯,广告流水灯越来越多的出现在城市中。

cpld 实物图

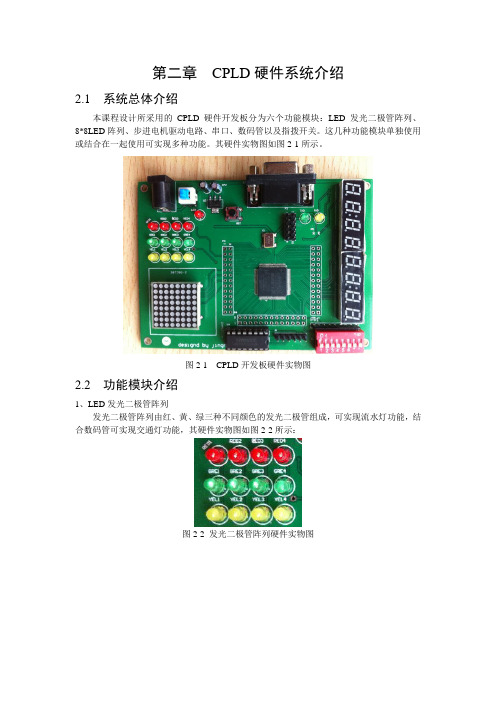

第二章CPLD硬件系统介绍

2.1 系统总体介绍

本课程设计所采用的CPLD硬件开发板分为六个功能模块:LED发光二极管阵列、8*8LED阵列、步进电机驱动电路、串口、数码管以及指拨开关。

这几种功能模块单独使用或结合在一起使用可实现多种功能。

其硬件实物图如图2-1所示。

图2-1 CPLD开发板硬件实物图

2.2 功能模块介绍

1、LED发光二极管阵列

发光二极管阵列由红、黄、绿三种不同颜色的发光二极管组成,可实现流水灯功能,结合数码管可实现交通灯功能,其硬件实物图如图2-2所示:

图2-2 发光二极管阵列硬件实物图。

流水灯电路设计

摘要:本次设计要求采用可编程逻辑器件实现一个流水灯控制电路,8个LED灯能连续发出三种不同的流水显示形式,先是8个LED灯从左到右依次点亮,左边亮四个,右边亮四个,最后从中间往两边亮、两边往中间亮,实现了灯光的移动和闪亮效果,特别是用于夜晚装饰,可以使我们的生活更为丰富多彩,同时也发挥出可编程器件的灵活性特点,可以改动电路实现多种效果。

流水灯是一串按一定的规律像流水一样连续闪亮,流水灯控制是可编程控制器的一个应用,其控制思想在工业控制技术领域也同样适用。

流水灯控制可用多种方法实现,但对现代可编程控制器而言,基于EDA技术的流水灯设计也是很普遍的。

关键字:EDA,CPLD,LED,状态机;Abstract:The design requirements by using the programmable logic device implements a water light control circuit, eight LED lights out for three different water display form, The first 8 LED lights lit up sequentially from left to right, the left four bright bright,right four, finally from the middle to both sides, both sides to the middle of the brightlight, realize the middle of mobile and ablaze effect, especially used for decoration, night can make our life more rich and colorful, also play a programmable device of flexibility, can change characteristics DuoZhong circuit implementation effect.Water lamp is a string of according to certain rules for shining, like water flowing water light control is a programmable controller, the control application in industrial control technology thought also applies. Water light control method can be used DuoZhong, but for modern programmable controller based on the technology for EDA water lamp design also is very common.Key word: EDA, CPLD, LED, state machine;目录1、前言 (1)1.1EDA技术介绍 (1)1.2 Verilog HDL简介 (1)2、总体方案设计 (2)2.2 设计方案比较 (2)2.3 方案论证 (2)2.4 方案选择 (3)3、单元模块设计 (4)3.1 CPLD系统电路 (4)3.1.1 时钟电路 (4)3.1.2 JTAG下载电路 (4)3.2 LED灯输出电路 (5)3.3 电源模块电路设计 (5)4、特殊器件的介绍 (7)4.1 CPLD器件介绍 (7)5、软件实现 (8)5.1 软件设计的程序 (8)6、系统仿真及调试 (9)6.1仿真 (9)6.2 调试 (11)7.1 设计小结 (12)7.2 设计收获 (13)7.3 致谢 (14)8、参考文献 (14)附录一:CPLD中顶层模块连接图 (16)1、前言1.1EDA技术介绍EDA是电子设计自动化(Electronic Design Automation)缩写,是90年代初从CAD(计算机辅助设计)、CAM(计算机辅助制造)、CAT(计算机辅助测试)和CAE(计算机辅助工程)的概念发展而来的。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

library ieee;

use ieee.std_logic_1164.all;

entity songlight is

port(en:in std_logic;

clk:in std_logic;

rst:in std_logic;

q:out std_logic_vector(11 to 0)); constant number1:integer:=2;

end songlight;

architecture func1 of songlight is begin

process(clk,rst)

variable temp1:integer range 0 to 2; variable temp2:integer range 0 to 11; begin

if(rst='0')then

q<="000000000000";

elsif(clk'event and clk='1')then

if(en='1')then

temp1:=temp1+1;

if(temp1=number1 and temp2=0)then

q<="000000000001";

temp2:=temp2+1;

temp1:=0;

elsif(temp1=number1 and temp2=1)then q<="000000000010";

temp2:=temp2+1;

temp1:=0;

elsif(temp1=number1 and temp2=2)then q<="000000000100";

temp2:=temp2+1;

temp1:=0;

elsif(temp1=number1 and temp2=3)then q<="000000001000";

temp2:=temp2+1;

temp1:=0;

elsif(temp1=number1 and temp2=4)then q<="000000010000";

temp2:=temp2+1;

temp1:=0;

elsif(temp1=number1 and temp2=5)then q<="000000100000";

temp2:=temp2+1;

temp1:=0;

elsif(temp1=number1 and temp2=6)then q<="000001000000";

temp2:=temp2+1;

temp1:=0;

elsif(temp1=number1 and temp2=7)then q<="000010000000";

temp2:=temp2+1;

temp1:=0;

elsif(temp1=number1 and temp2=8)then q<="000100000000";

temp2:=temp2+1;

temp1:=0;

elsif(temp1=number1 and temp2=9)then q<="001000000000";

temp2:=temp2+1;

temp1:=0;

elsif(temp1=number1 and temp2=10)then q<="010*********";

temp2:=temp2+1;

temp1:=0;

elsif(temp1=number1 and temp2=11)then q<="100000000000";

temp2:=temp2+1;

temp1:=0;

temp2:=0;

end if;

end if;

end if;

end process;

end func1; library ieee;

use ieee.std_logic_1164.all;

entity wang3 is

port(en:in std_logic;

clk:in std_logic;

rst:in std_logic;

q:out std_logic_vector(11 to 0)); constant number1:integer:=2;

end wang3;

architecture func1 of wang3 is

begin

process(clk,rst)

variable temp1:integer range 0 to 2; variable temp2:integer range 0 to 11; begin

if(rst='0')then

q<="000000000000";

elsif(clk'event and clk='1')then

if(en='1')then

temp1:=temp1+1;

if(temp1=number1 and temp2=0)then

q<="000000000001";

temp2:=temp2+1;

temp1:=0;

elsif(temp1=number1 and temp2=1)then q<="000000000010";

temp2:=temp2+1;

temp1:=0;

elsif(temp1=number1 and temp2=2)then q<="000000000100";

temp2:=temp2+1;

temp1:=0;

elsif(temp1=number1 and temp2=3)then q<="000000001000";

temp2:=temp2+1;

temp1:=0;

elsif(temp1=number1 and temp2=4)then q<="000000010000";

temp2:=temp2+1;

temp1:=0;

elsif(temp1=number1 and temp2=5)then q<="000000100000";

temp2:=temp2+1;

temp1:=0;

elsif(temp1=number1 and temp2=6)then q<="000001000000";

temp2:=temp2+1;

temp1:=0;

elsif(temp1=number1 and temp2=7)then q<="000010000000";

temp2:=temp2+1;

temp1:=0;

elsif(temp1=number1 and temp2=8)then q<="000100000000";

temp2:=temp2+1;

temp1:=0;

elsif(temp1=number1 and temp2=9)then q<="001000000000";

temp2:=temp2+1;

temp1:=0;

elsif(temp1=number1 and temp2=10)then q<="010*********";

temp2:=temp2+1;

temp1:=0;

elsif(temp1=number1 and temp2=11)then q<="100000000000";

temp2:=temp2+1;

temp1:=0;

temp2:=0;

end if;

end if;

end if;

end process;

end

func1;。