芯片设计工具及应用-54页PPT文档资料

集成电路设计中的工具与应用

集成电路设计中的工具与应用集成电路(IC)是现代电子设备的核心组成部分,其设计过程涉及到多种工具和方法。

本文将详细介绍集成电路设计中的工具与应用。

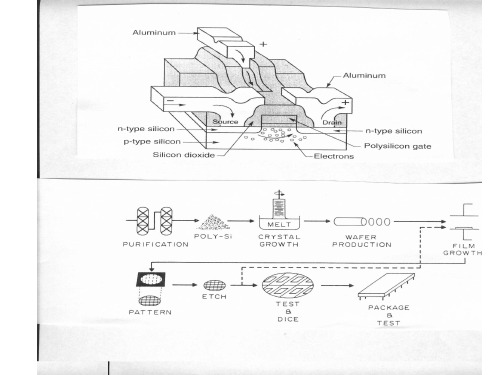

1. 集成电路设计流程集成电路设计是一个复杂的过程,主要包括以下几个阶段:1.需求分析与规划:确定IC的功能、性能、功耗等需求,并制定相应的设计计划。

2.前端设计:包括逻辑设计、架构设计、仿真验证等。

3.后端设计:包括物理设计、版图设计、工艺制造等。

4.测试与验证:对制造出的IC进行功能和性能测试,确保其满足设计要求。

2. 集成电路设计工具集成电路设计涉及多种工具,可以分为以下几类:2.1 硬件描述语言(HDL)工具硬件描述语言是用于描述IC逻辑结构和行为的语言,主要包括Verilog和VHDL。

这些语言可以方便地描述复杂的电路结构,并通过仿真验证其功能。

2.2 电路仿真工具电路仿真工具用于验证IC的性能和功能,如Cadence的 Spectre、Synopsys的Virtuoso等。

这些工具可以对电路进行详细的分析,包括时序、功耗、温度等。

2.3 版图绘制工具版图绘制工具用于将电路设计转换为实际的版图,如Cadence的Calibre、Mentor Graphics的AutoCAD等。

这些工具可以确保版图的精度和可靠性。

2.4 工艺制造工具工艺制造工具用于实现IC的制造过程,如光刻机、蚀刻机、离子注入机等。

这些工具决定了IC的制造成本和性能。

3. 集成电路设计应用集成电路设计应用广泛,涵盖了各个领域,如计算机、通信、消费电子、工业控制等。

下面以几个典型应用为例,介绍集成电路设计在实际中的应用。

3.1 中央处理器(CPU)CPU是计算机的核心部件,其设计涉及到复杂的逻辑结构和高性能要求。

集成电路设计工具和方法在CPU设计中起到了关键作用,如使用硬件描述语言进行逻辑设计、电路仿真工具进行性能验证等。

3.2 移动通信芯片移动通信芯片是现代手机的核心部件,其设计需要考虑到功耗、性能和尺寸等因素。

芯片制造流程ppt课件

芯片制作过程– 电路连接

The portions of a chip that conduct electricity form the chip’s interconnections. A conducting metal (usually a form of aluminum) is deposited on the entire wafer surface. Unwanted metal removed during lithography and etching leaves microscopically thin lines of metal interconnects. All the millions of individual conductive pathways must be connected in order for the chip to function. This includes vertical interconnections between the layers as well as horizontal Interconnections across each layer of the chip.

SMIC

0.13u

Cu

BEOL

Flow

1M L D D FL O W

C V D S IN D E P FSG D EP S IO N D E P V IA P H O T O V IA D R Y E T C H V IA C L E A N B A R C C O A T IN G PLUG ETCH BACK M TO X PH O TO M T DRY ETCH M T CLEAN STO P LA Y ER R EM O V E P O S T -S L R C L E A N T a N /T a & C u S E E D C U P L A T IN G M 2CU CM P

DSP芯片应用PPT课件

第8章 DSP芯片应用

int *data1 = 0x3000; /*内部存储器单元*/ int *data2= 0x8FFF; /*外部存储器单元*/ int func ( ) { ...

* data1 = 2000; * data2 = 0; ... }

第8章 DSP芯片应用

3.DSP I/O端口的访问 DSP I/O端口的访问通过ioport关键字实现。定义 的形式为

第8章 DSP芯片应用

ioport unsigned port10; /* 定义地址为10H的I/O端口变量*/

int func ( ) { ... port10 = 20; /* write a to port 10H */ ... b = port10; /* read port 10H into b */ ... }

... BRINT1: BD _ int_handler ; McBSP1接收中断

NOP NOP .end

第8章 DSP芯片应用

(2) C中断程序采用特殊的函数名,其格式为 c_intnn。其中,nn代表00~99之间的两位数,如 c_int01就是一个有效的中断函数名。下面是一个中断 函数的例子:

问,常常采用的方法是将DSP寄存器地址的列表定义 在头文件中(如reg.h)。DSP寄存器地址定义的形式为宏, 如下所示:

第8章 DSP芯片应用

#define IMR #define IFR #define ST0 #define ST1 #define AL #define AH #define AG #define BL #define BH #define BG

ioport type port hex_num 其中:ioport是关键字,表明变量是io变量;type 必 须 是 char 、 short 、 int 和 unsigned ; port 表 示 io 地 址 , hex_num是十六进制地址。 下例声明了一个io变量,地址为10H,并对I/O端口 做读/写操作。

芯片设计技术 ppt课件

前端设计流程—时序分析

确定芯片最高工作频率

通过时序分析可以控制工程的综合、映射、布局布线等环节,减 少延迟,从而尽可能提高工作频率

检查时序约束是否满足

可以通过时序分析来查看目标模块是否满足约束,如不满足,可 以定位到不满足约束的部分,并给出具体原因,进一步修改程序直 至满足时序要求

分析时钟质量

时钟存在抖动、偏移、占空比失真等不可避免的缺陷。通过时 序分析可以验证其对目标模块的影响

前端设计流程--验证平台

Modelsim

debussy

LINUX环境:VCS+debussy、 WINDOWS环境:modelsim

启动VCS验证

波形界面

仿真报告

前端设计流程

前端的基本设计流程,从输入需求到输出网表的过程。

主要步骤为:

1. RTL设计 2. 验证 3. 静态时序分析 4. 覆盖率 5. FPGA测试 6. ASIC综合

形式验证

前端设计流程--验证

前端设计流程--验证

前端设计流程--验证

功能验证的方法:

前端设计流程--验证

白盒法 黑盒法 灰盒法

前端设计流程--验证

芯片验证流程(以LINUX-VCS环境下为例):

建立工程、 设置验证环境

撰写仿真脚本、 配置工具路径、 设置快捷命令等

用汇编 或C编写 测试case

1.时序分析和验证时出现的错误可能需要反复重做前面几步才能解决 2.是一个迭代优化的过程。

结构说明和RTL编码 RTL仿真

逻辑综合、优化、扫描插入 形式验证(RTL和门级) 布局前STA 否 时序正确 是 布局、CT插入和全局布线

结束

前端设计流程—时序分析

转换时钟树到DC

集成电路版图设计与工具 PPT课件

问题讨论: (3)接触 版图设计中通常需要有多种接触,例如,金 属和P型扩散区接触、金属和N型扩散区接触、 金属和多晶硅的接触以及衬底接触等。根据工 艺不同,还有“隐埋”型多晶硅-扩散区接触和 拼合接触。 通常,制作芯片的衬底被划分成多个“阱” 区,每个孤立的阱必须利用衬底接触来接合适 的电源电压。将两个或多个金属和扩散区接触 用金属连通起来,称为合并接触。

问题讨论: (2)MOS管的规则

在多晶硅穿过有源区的地方,源和漏扩散区被多晶硅 区所掩蔽。因而,源、漏和沟道是自对准于栅极的。 重要的是,多晶硅必须完全穿过有源区,否则制成的 MOS管就会被源、漏之间的扩散通路所短路。为确保 这一条件得到满足,多晶硅必须超出扩散区边界,例 如该硅栅工艺中规则3.4中规定的1.5μm,这常常称 为“栅伸展”。同时,有源区也必须在多晶硅栅两边 扩 展,这样才能有扩散区存在,使载流子进入和流出沟 道,例如规则3.5规定的3.0μm就是保持源区和漏区 所必需的。

电学设计规则还为合理选择版图布线层提供了 依据。集成电路工艺为设计者提供了多层布线 的手段,最常用的布线有金属、多晶硅、硅化 物以及扩散区。但这些布线层的电学性能大不 相同。

随着器件尺寸的减小,线宽和线间距也在减小, 多层布线层之间的介质层也在变薄,这将大大 增加走线电阻和耦合电容,特别是发展到深亚 微米级和纳米之后,与门延迟相比,布线延迟 变得越来越不可忽略。因此,版图布线必须合 理选择布线层,尽可能地避免布线层电学参数 的影响。

为了工艺上按比例缩小或版图编辑的需要, 合并接触采用图4.9(a)所示的分离式接触结 构,而不采用图4.9(b)的合并长孔结构。

4.3 电学设计规则与布线

电学设计规则给出的是由具体工艺参数抽象 出的器件电学参数,是晶体管级集成电路模拟 的依据。与几何设计规则一样,对于不同的工 艺和不同的设计要求,电学设计规则将有所不 同。通常,特定工艺会给出电学参数的最小值、 典型值和最大值。上述N阱硅栅CMOS工艺的 部分电学设计规则的参数名称及其意义如表4.8 所示。

芯片制造基础知识PPT课件

• 光阻涂布的是否均 匀直接影响到将来 线宽的稳定性。

• 光阻分为两种:正 光阻和负光阻。

• 一般而言通常使用 正光阻。只有少数 层次采用负光阻。

第20页/共102页

• 曝光 • Exposure • 曝光动作的目的是将光罩上的图形传送到晶园上。 • 0.13um,0.18um就是这样做出来的。 • 曝光所采用的机台有两种:Stepper和Scanner。

第35页/共102页

• 采用铜导线的困难: • 当铜和硅接触的时候,会在硅中发生非常快速的扩散。 • 这种扩散还将改变制作在硅上面半导体三极管的电学特性,导致三极管 失效。

• IBM最终克服了这些困难(Damascene): • 采用先做绝缘层,再做铜导线层的方法解决扩散问题。 • 在制作铜导线层的时候,IBM采用一种铜的多晶体,进一步限制铜在硅 中的扩散。

第3页/共102页

• Poly Silicon Creation 2 • 采用一种叫做Trichlorosilane 的物质(SiHCl3)作为溶剂,氢气作为反应 环境,在钽(tantalum)电热探针指引下,经过初步提炼的硅形成晶体。 • 这种过程需要多次,中途还会用到氢氟酸(HF)这样剧毒的化学药品,硅的 纯度也随着这个过程而进一步被提高。 • 最后生成多晶硅的硅锭。

第29页/共102页

• 对于不同层次的光阻移除, 采用的等离子体是不一样的。

• 例如:硅、硅化物、金属导 线等等。

• 另外,在去除光阻止后,通 常还需要有一步清洗,以保 证晶园表面的洁净度。

第30页/共102页

2.7 金属蚀刻

• Metal Etch • 金属蚀刻用于制作芯片中的金属导线。 • 导线的形状由Photo制作出来。 • 这部分工作也使用等离子体完成。

芯片设计工具及应用PPT课件

03

CATALOGUE

芯片设计工具应用案例

数字IC设计流程

总结词

数字IC设计流程是芯片设计中的重要环节,包括逻辑设计、逻辑综合、布局布线等步骤。

详细描述

在数字IC设计流程中,设计师首先进行逻辑设计,将系统需求转化为逻辑电路图。然后进行逻辑综合,将逻辑电 路图转换为门级电路图,并优化电路性能。最后进行布局布线,将门级电路图映射到物理芯片上,完成物理设计 和验证。

高级封装与多芯片集成

小型化封装

01

随着芯片设计技术的发展,封装技术也在不断进步,实现更小

、更紧凑的封装形式。

多芯片集成

02

将多个芯片集成在一个封装内,实现更高的性能和更小的体积

。

异构集成

03

将不同类型的芯片集成在一起,如逻辑芯片、存储器、传感器

等,以实现更复杂的功能。

5G和物联网技术的影响

01

02

计师。

06

CATALOGUE

总结与展望

芯片设计工具的未来方向

智能化工具

随着人工智能和机器学习技术的 快速发展,芯片设计工具将更加 智能化,能够自动完成一些繁琐 和复杂的任务,提高设计效率。

协同设计工具

随着芯片设计的复杂度不断提高 ,需要更多的跨领域协同设计。 未来的芯片设计工具将更加注重 协同设计,支持多团队、多领域 的协同工作。

人工智能和机器学习技术在芯片设计中的应用将更加广泛,能够提 高设计效率、优化芯片性能,并推动芯片设计的创新。

绿色计算的需求

随着环保意识的提高,绿色计算的需求将不断增加。芯片设计将更 加注重能效比和环保,推动绿色计算的发展。

THANKS

感谢观看

详细描述

DFT和可测试性设计工具主 要包括自动测试向量生成、 测试压缩等,能够试性设计工具在 芯片设计的后期阶段起到至 关重要的作用,能够确保设 计的可测试性和可维修性。

芯片设计工具及应用54页PPT

2020/3/28

浙大微电子

10

模块2-3/5:设计实例--基准源、噪 声、开关电容及Monte-Carlo仿真

• 电压基准源设计 • 集成电路噪声分析及仿真 • 开关电容电路理论、设计举例及仿真 • Monte-Carlo仿真

2020/3/28

浙大微电子

18

模块3-4/4: 数字集成电路验证方法学

• 作业2-4 – 绘制一个电流控制振荡器,版图面积<0.05mm^2

• 作业2-5 – 通过DRC以及LVS,获得前仿、后仿结果

2020/3/28

浙大微电子

14

模块3:数字IC设计工具(4+1)

• 可综合Verilog语言及FPGA验证 • 逻辑综合与可测性设计 • 数字IC自动布局布线 • 数字集成电路验证方法学 • 实验课

2020/3/28

浙大微电子

11

模块2-4/5:模拟IC版图绘制及 Virtuoso工具软件

• 典型深亚微米工艺流程 • Design Rule的简介 • Virtuoso软件的简介及使用 • PDK简介 • 版图设计中的相关专题

2020/3/28

浙大微电子

12

模块2-5/5:版图验证与后仿真

• 概述 • DRC、LVS与后仿真介绍 • 验证工具介绍 • Calibre 使用方法 • Diva规则文件简介 • 实例分析

• 版图验证与后仿真 • 实验课

--随堂上机验收模拟IC设计5次作业

2020/3/28

浙大微电子

8

模块2-1/5: 系统级仿真与Matlab

IC设计工具原理讲义(PPT 45张)

EDA概述

CADENCE

• EDA发展概况:

(1)20世纪60、70年代出现计算机辅助设计(CAD) (2)随后出现CAE、CAM、CAT、CAQ。 (3)20世纪80年代,初级的具有自动化功能的EDA出现。 (4)20世纪90年代,EDA技术渗透到电子设计和集成电 路设计各个领域,形成了区别于传统设计的整套设计思 想和方法。 (5)当前,深亚微米工艺和SoC设计对EDA技术提出更 高更苛刻的要求。

12

EDA概述

CADENCE

• EDA主要供应商:

VHDL仿真 行为综合 逻辑综合 可测性设计 低功耗设计 布局布线 Cadence Vantage Synopsys

Synopsys Alta

Synopsys

Compass Mentor Graphics

Synopsys Sunrise Compass Synopsys Epic Cadence Avant! Mentor Graphics Synopsys Cadence Compass IKOS Vantage

37

Analog Simulation

CADENCE

• 选择信号输出

Select :Output-To Be Plotted-Select On Schematic

38

Analog Simulation

CADENCE

• 提取网表

39

Analog Simulation

CADENCE

• 运行仿真

Select Simulation-Run or Select the Run icon on the right side of the simulation window

20

[课件]第7讲 芯片设计与制造PPT

![[课件]第7讲 芯片设计与制造PPT](https://img.taocdn.com/s3/m/44430072f01dc281e53af0bb.png)

SoC定义的基本内容主要表现在两方面: 其一是它的构成,其二是它形成过程。 系统级芯片的构成可以是系统级芯片控制逻辑模块、微处理 器/微控制器CPU 内核模块、数字信号处理器DSP模块、嵌入的 存储器模块、和外部进行通讯的接口模块、含有ADC /DAC 的模 拟前端模块、电源提供和功耗管理模块,对于一个无线SoC还有 射频前端模块、用户定义逻辑(它可以由FPGA 或ASIC实现)以及 微电子机械模块,更重要的是一个SoC 芯片内嵌有基本软件 (RDOS或COS以及其他应用软件)模块或可载入的用户软件等。

2. SoC基系统,意 指它是一个产品,是一个有专用目标的集成电路,其中包含 完整系统并有嵌入软件的全部内容。同时它又是一种技术, 用以实现从确定系统功能开始,到软/硬件划分,并完成设计 的整个过程。 从狭义角度讲,它是信息系统核心的芯片集成,是将系 统关键部件集成在一块芯片上;从广义角度讲, SoC是一个 微小型系统。 20世纪90年代中期,因使用ASIC(一种为专门目的而 设计的集成电路 )实现芯片组受到启发,萌生应该将完整计 算机所有不同的功能块一次直接集成于一颗硅片上的想法。 这种芯片,初始起名叫System on a Chip(SoC),直译的中 文名是系统级芯片。

相对于其他逻辑系列,CMOS逻辑电路具有一下优点: (1)允许的电源电压范围宽,方便电源电路的设计 (2)逻辑摆幅大,使电路抗干扰能力强 (3)静态功耗低 (4)隔离栅结构使CMOS期间的输入电阻极大,从而使 CMOS期间驱动同类逻辑门的能力比其他系列强得多

三、芯片的封装技术

很多人对CPU内存以及芯片组封装并不了解。其实,所谓封装就 是指安装半导体集成电路芯片用的外壳,它不仅起着安放、固定、密 封、保持芯片和增强电热性能的作用,而且芯片上的接点用导线连接 到封装外壳的引脚上,这些引脚又通过印制板上的导线与其他器件建 立连接,从而实现内部芯片与外部电路的连接。因为芯片必须与外界 隔离,以防止空气中的杂质对芯片电路的腐蚀而造成电气性能下降。 另一方面,封装后的芯片也更便于安装和运输。 由于封装技术的好坏还直接影响到芯片自身性能的发挥和与之连 接的PCB(印制电路板)的设计和制造,因此它是至关重要的。 因此, 封装对CPU以及其他芯片都有着重要的作用。 封装时主要考虑的因素: (1)芯片面积与封装面积之比为提高封装效率,尽量接近1:1。 (2)引脚要尽量短以减少延迟,引脚间的距离尽量远,以保证互不 干扰,提高性能。 (3)基于散热的要求,封装越薄越好。

简洁科技芯片研发汇报ppt模板

单击此处添加文本单击此处添加文本单击此处添加文本单击此处添加文本单击此添加文本单击单击此处添加文本单击此处添加文本单击此处添加文本单击 此处添加文本单击此添加文本

图表标题

类别 4 类别 3 类别 2 类别 1

0

2

4

6

8

单击填加标题

您的内容打在这里,或者通过复制您的文本后,在此框中选择粘贴,并选择只保留 文字您的内容打在这里,或者通过复制您的文本后,在此框中选择粘贴,并选择只 保留文字

您的内容打在这里,或者通过复制您的文本后,在此框中选择粘贴,并选 择只保留文字

您的内容打在这里,或者通过复制您的文本后,在此框中选择粘贴,并选 择只保留文字

10

12

14

系列 1 系列 2 系列 3

图标以及图片均可根据您的个 人需要来进行一键替换。数据图表均可进行替换和编辑,根据 需要进行设置;祝你使用开心。

• 鼠标点击这里,输入您的文本文字,更改文 字的颜色或者大小属性。

• 调整文字文本的行间距。建议您使用文档源 文件中的原字体,效果会更好。

• 调整文字文本的行间距。建议您使用文档源 文件中的原字体,效果会更ቤተ መጻሕፍቲ ባይዱ。

标题添加

您的内容打在这里,或者通过复制您的文本后或者通过复制您 的文本后

标题添加

您的内容打在这里,或者通过复制您的文本后或者通过复制您 的文本后

标题添加

您的内容打在这里,或者通过复制您的文本后或者通过复制您 的文本后

PART 04

售后保障与服务

您的内容打在这里,或者通过复制您的文本后或者通过复制您的文本您的内容打在这里, 或者通过复制

图解芯片制作工艺流程图ppt课件

.

7

单晶硅锭:整体基本呈圆柱形,重

约100千克,硅纯度99.9999%。

.

8

.

9

处 理 晶 圆 的 机 器

.

10

• 硅锭切割:横向切割成圆形的单个硅片,也就是我们常说 的晶圆(Wafer)。顺便说,这下知道为什么晶圆都是圆形 的了吧?

.

11

• 晶圆:切割出的晶圆经过抛光后变得几乎完美无瑕,表面甚至可以当 镜子。事实上,Intel自己并不生产这种晶圆,而是从第三方半导体企 业那里直接购买成品,然后利用自己的生产线进一步加工,比如现在 主流的45nm HKMG(高K金属栅极)。值得一提的是,Intel公司创立之 初使用的晶圆尺寸只有2英寸/50毫米。

.

21

• 清除光刻胶:离子注入完成后,光刻胶也 被清除,而注入区域(绿色部分)也已掺杂, 注入了不同的原子。注意这时候的绿色和 之前已经有所不同。

.

22

• 晶体管就绪:至此,晶体管已经基本完成。 在绝缘材(品红色)上蚀刻出三个孔洞,并填 充铜,以便和其它晶体管互连。

.

23

• 电镀:在晶圆上电镀一层硫酸铜,将铜离子沉淀 到晶体管上。铜离子会从正极(阳极)走向负极(阴 极)。

.

1

.

2

INTEL 图解芯片制作工艺流程

共九个步骤

.

3

.

4

• 沙子:硅是地壳内第二丰富的元素,而脱氧后的沙子(尤 其是石英)最多包含25%的硅元素,以二氧化硅(SiO2)的 形式存在,这也是半导体制造产业的基础。

.

5

.

6

• 硅熔炼:12 英寸/300毫米 晶圆级,下同。 通过多步净化 得到可用于半 导体制造质量 的硅,学名电 子级硅(EGS), 平均每一百万 个硅原子中最 多只有一个杂 质原子。此图 展示了是如何 通过硅净化熔 炼得到大晶体 的,最后得到 的就是硅锭 (Ingot)。

芯片设计技术 ppt课件

前端设计流程—工艺选择

包括该工艺下的芯片 制造成本和设计成本

成本

Foundry可提供的第 三方IP,IP的功能、 性能和使用情况

芯片 工艺选择

工艺 成熟度

性能、功耗、面积、 温度、寿命、可实现 的频率、可支持的金 属层数等

前端设计流程—FPGA验证

验证主要针对了模块、系统的功能测试,而FPGA下载测试则 更接近芯片的实际应用环境进行功能和性能上的测试。

测试平台:FPGA开发板、外围电路

前端设计流程

前端的基本设计流程,从输入需求到输出网表的过程。

主要步骤为:

1. RTL设计 2. 验证 3. 静态时序分析 4. 覆盖率 5. FPGA测试 6. ASIC逻辑综合

前端设计流程

前端的基本设计流程,从输入需求到输出网表的过程。

主要步骤为:

1. RTL设计 2. 验证 3. 静态时序分析 4. 覆盖率 5. FPGA测试 6. ASIC综合

1.时序分析和验证时出现的错误可能需要反复重做前面几步才能解决 2.是一个迭代优化的过程。

验证的重要性

前端设计流程--验证

前端设计流程--覆盖率

从目标上分,可将覆盖率大体分为两类:

代码覆盖率: 作用:检查代码是否冗余,设计要点是否遍历。 被检测对象:RTL代码 检测方法:工具自动生成

功能覆盖率: 作用:检查功能是否遍历。 被检测对象:自定义容器 检测方法:自定义收集条件

前端设计流程--覆盖率

覆盖率的分类

代码覆盖率可分为: ➢ 行覆盖率 ➢ 分支覆盖率 ➢ 路径覆盖率 ➢ 条件覆盖率 ➢ 翻转覆盖率 ➢ 状态机覆盖率

芯片的基本原理图解和应用

芯片的基本原理图解和应用什么是芯片?芯片(Chip)也被称为集成电路(Integrated Circuit),是一种由块状材料上的面积很小的电子器件组成的集成电路板。

芯片的基本原理芯片是通过多道工序在硅片上制作出来的。

在芯片上,数以百万计的晶体管和其他电子器件进行了集成,它们相互连接形成电路,从而实现了电子设备的功能。

芯片的基本原理主要包括以下几个方面:1.光刻技术:通过光刻技术将芯片上的各个部分进行制作。

光刻技术是一种借助光斑进行图形转移的技术,利用紫外光照射光刻胶,然后进行衍射、显影等工艺步骤,最终形成芯片的图形。

2.扩散和离子注入:扩散技术是将杂质原子以定向方式引入芯片材料中,改变材料的导电性质。

离子注入是将离子束注入到芯片材料中,改变其电子特性。

这些技术对芯片电路中的不同部分进行区分,从而形成不同的功能区域。

3.电路连接和封装:芯片上的电子器件之间通过金属导线进行连接,形成完整的电路。

然后,芯片被封装在塑料或陶瓷芯片外壳中,以保护芯片并便于安装到电子设备中。

芯片的应用领域芯片在现代科技中得到广泛应用,几乎涵盖了各个领域。

以下是一些常见的芯片应用领域:1.计算机和通信设备:芯片是计算机和通信设备的核心组成部分。

在计算机中,芯片用于处理器、内存、图形卡等。

在通信设备中,芯片用于无线网络、蓝牙、移动芯片等。

2.消费电子产品:智能手机、平板电脑、音频设备等消费电子产品中都使用了芯片。

芯片的发展使得这些电子产品变得更加智能、高效。

3.汽车:现代汽车中大量使用了芯片技术。

例如,引擎控制单元(ECU)使用芯片来监测和控制发动机的性能。

汽车中的许多功能,如安全气囊、防抱死制动系统等,都依赖于芯片的控制。

4.医疗设备:医疗设备中广泛使用芯片。

例如,心脏起搏器、血糖仪、体温计等设备都是使用芯片来实现精准测量和控制。

5.工业控制:工业控制系统中也使用了大量的芯片技术。

例如,PLC(可编程控制器)使用芯片来进行自动化控制。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2019/10/7

浙大微电子

6

模块1-3/3:设计实例 --用TCAD设计ESD防护器件

• ESD及ISE-TCAD简介 • 工艺仿真(Dios) • 器件仿真(DESSIS)及模型的选取 • 热边界条件的设定 • ESD防护器件仿真中收敛性问题 • 一些对关键性能有影响的关键参数 • 二次击穿电流的仿真

--随堂上机验收数字IC设计4次作业

2019/10/7

浙大微电子

16

模块3-1/4: 可综合Verilog语言及FPGA验证

• 可综合Verilog • Testbench编写 • HDL的软件仿真 • FPGA简介及验证流程 • FPGA设计中的基本问题

2019/10/7

浙大微电子

17

模块3-2/4: 逻辑综合与可测性设计

2019/10/7

浙大微电子

5

模块1-2/3:新一代工艺及器件仿真 工具Sentaurus

• 工艺仿真系统 Sentaurus Process • 器件结构编辑工具Sentaurus Structure Editor • 器件仿真工具Sentaurus Device • 集成电路虚拟制造系统Sentaurus Workbench

2019/10/7

浙大微电子

14

模块2(5+1):实验课 --随堂上机验收模拟IC设计5次作业

• 作业2-1 – 利用Simulink 搭建一个4-16线译码器的仿真模型

• 作业2-2 – 对一个数模混合的FSK电路进行数模混合仿真

• 作业2-3 – 仿基准电压源的温度系数/工艺角/环路稳定性/电源抑制比

2019/10/7

浙大微电子

12

模块2-4/5:模拟IC版图绘制及 Virtuoso工具软件

• 典型深亚微米工艺流程 • Design Rule的简介 • Virtuoso软件的简介及使用 • PDK简介 • 版图设计中的相关专题

2019/10/7

浙大微电子

13

模块2-5/5:版图验证与后仿真

• 概述 • DRC、LVS与后仿真介绍 • 验证工具介绍 • Calibre 使用方法 • Diva规则文件简介 • 实例分析

常用选项:

- r 指示rm将参数中列出的全部目录和子目录均全部删除。 - i 进行交互式删除。

使用rm命令要小心。因为一旦文件被删除,它是不能被恢复的。为了防止这种情 况的发生,可以使用i选项来逐个确认要删除的文件。如果用户输入y,文件将被 删除。如果输入任何其他东西,文件则不会删除。

2019/10/7

• Spectre 模拟仿真 • Ultrasim 快速仿真 • Spectreverilog 数模混合仿真 • 演示

2019/10/7

浙大微电子

11

模块2-3/5:设计实例--基准源、噪 声、开关电容及Monte-Carlo仿真

• 电压基准源设计 • 集成电路噪声分析及仿真 • 开关电容电路理论、设计举例及仿真 • Monte-Carlo仿真

2019/10/7

浙大微电子

7

模块1(3+1):实验课

随堂上机验收工艺与器件设计3次作业

• 作业1-1

– 用T4做出一个NMOS管,再读入到MEDICI中,进 行栅特性仿真。

• 作业1-2

– 用Sentaurus工艺仿真软件跑出一个NMOS器件, 通过修改器件参数,使得耐压提高20% 。

• 作业1-3

-f 禁止交互操作。在mv操作要覆盖某已有的目标文件时不给任何指示,指 定此选项后,i选项将不再起作用。

2019/10/7

浙大微电子

32

rm命令

该命令的功能为删除一个目录中的一个或多个文 件或目录

语法: rm [选项] 文件

例如:

rm –r /home/lx/test 删除/home/lx目录下的test文件夹以及文件夹中的内容

– 将一个仿真不收敛的ESD防护器件,通过网格 调整而变得收敛。

2019/10/7

浙大微电子

8

模块2:模拟IC设计工具(5+1)

• 系统级仿真与Matlab • 模拟电路仿真工具+快速仿真+数模混合仿真 • 设计实例--基准源、噪声、开关电容及

Monte-Carlo仿真 • 模拟IC版图绘制及Virtuoso工具软件

•-f 删除已经存在的目标文件而不提示。 •-i 和f选项相反,在覆盖目标文件之前将给出提示要求用户确认。

回答y时目标文件将被覆盖 •-r 若给出的源文件是一目录文件,此时cp将递归复制该目录下所

有的子目录和文件。此时目标文件必须为一个目录名。

2019/10/7

浙大微电子

31

mv命令

用户可以使用mv命令来为文件或目录改名或将文 件由一个目录移入另一个目录中

2019/10/7

浙大微电子

23

1、基本操作

步骤一

下载安装putty软件 ( /ic/da

tas/news/0308/new_ 120213/putty-0.60-

installer.exe),在 Host name处填工 作站地址,端口默 认,协议 (protocol)选 SSH,如图所示, 在putty进行设置; 然后登录工作站。

浙大微电子

33

mkdir和rmdir命令

mkdir功能:创建一个目录 rmdir功能:删除一个空目录

语法:mkdir 文件名 rmdir 文件名

例如:

mkdir test 这是在当前目录下创建一个test目录 rmdir test 这是删除当前目录下的test空目录

2019/10/7

浙大微电子

34

浙大微电子

27

基本操作命令

LINUX文件名称

LINUX文件命名规则: • 大小写敏感(file1和File1表示两个不同的文

件); • 无专用扩展名(LINUX文件名可出现多个小

数点,并无特殊含义)。

2019/10/7

浙大微电子

28

LINUX文件名称

LINUX特殊字符 • / 表示根目录 • . 表示当前目录 • .. 表示当前目录的父目录 • .字符串 表示隐藏文件,如".profile"文件 • *任何字符,如"ab*10"表示以ab开头和以10

• 版图验证与后仿真 • 实验课

--随堂上机验收模拟IC设计5次作业

2019/10/7

浙大微电子

9

模块2-1/5: 系统级仿真与Matlab

• 集成电路设计的一般流程 • 系统级建模工具----Matlab • 设计实例--利用Matlab设计锁相环

2019/10/7

浙大微电子

10

模块2-2/5:模拟电路仿真工具 + 快速仿真 + 数模混合仿真

• 逻辑综合基本概念 • 逻辑综合工具--Design Compiler • 可测性基础 • 可测性设计工具 • 测试矢量生成软件TetraMAX

2019/10/7

浙大微电子

18

模块3-3/4: 数字IC自动布局布线

• 数字IC设计典型流程 • 自动布局布线基本概念 • 自动布局布线工具Astro介绍

• 上机操作 • Linix命令 • 上机实验作业布置

2019/10/7

浙大微电子

3

模块1: 半导体工艺与器件设计工具(3+1)

• 工艺仿真工具TSUPREM-4和 器件仿真工具MEDICI

• 新一代工艺及器件仿真工具Sentaurus • 设计实例--用TCAD设计ESD防护器件 • 实验课

随堂上机验收工艺与器件设计3次作业

2019/10/7

浙大微电子

24

2019/10/7

Putty 软件界面

用户名

VNC端口申请

输入密码(默认 密码edazueda)

VNC密码设置

端口号 putty密码修改

浙大微电子

25

步骤二

下载winvnc软件 /ic/datas/news/0308/new_120213/vncviewer. exe

cd命令和pwd命令

cd 命令(change directory) 功能:改变工作目录。

例:

cd .. 进入当前目录的上一层目录 cd ~ 进入用户的home目录,同cd cd /usr/bin 跳到/usr/bin目录

pwd 命令 (printing working directory)

说明:此命令显示出当前工作目录的绝对路径。

芯片设计工具及应用

韩雁 2019年9月

课程介绍

• 3学分,每周二上午三节课。分3个模块。 • 13次课堂教学,每堂布置1道作业,分3次验收:

– 模块1:3次课堂教学,3次作业,1次现场验收。 – 模块2:5次课堂教学,5次作业,1次现场验收。 – 模块3: 4次课堂教学,4次作业,1次现场验收。

• 教材:

2019/10/7

浙大微电子

19

模块3-4/4: 数字集成电路验证方法学

• 验证的必要性 • 验证方法学介绍 • 验证工具介绍 • 演示

2019/10/7

浙大微电子

20

模块3(4+1):实验课 --随堂上机验收数字IC设计4次作业

• 作业3-1

– 制作流水灯,完成前仿及FPGA布局布线后后仿

• 作业3-2

2019/10/7

浙大微电子

4

模块1-1/3:工艺仿真工具TSUPREM-4 和器件仿真工具MEDICI

• 工艺仿真工具TSUPREM-4介绍

– 模型介绍 – TSUPREM-4基本命令介绍 – 双极晶体管结构的一维仿真示例

• 器件仿真工具MEDICI介绍