TPS659113

2景阳公司模拟产品对应技术方案和芯

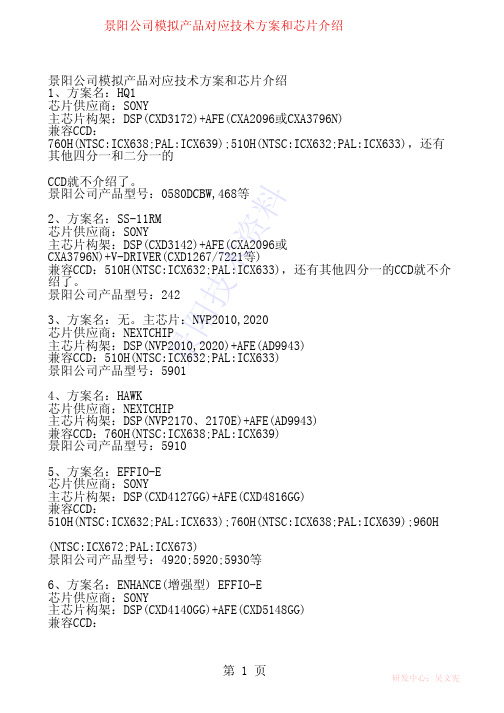

景阳公司模拟产品对应技术方案和芯片介绍景阳公司模拟产品对应技术方案和芯片介绍1、方案名:HQ1芯片供应商:SONY主芯片构架:DSP(CXD3172)+AFE(CXA2096或CXA3796N)兼容CCD :760H(NTSC:ICX638;PAL:ICX639);510H(NTSC:ICX632;PAL:ICX633),还有其他四分一和二分一的CCD 就不介绍了。

景阳公司产品型号:0580DCBW,468等2、方案名:SS-11RM 芯片供应商:SONY 主芯片构架:DSP(CXD3142)+AFE(CXA2096或CXA3796N)+V-DRIVER(CXD1267/7221等)兼容CCD :510H(NTSC:ICX632;PAL:ICX633),还有其他四分一的CCD 就不介绍了。

景阳公司产品型号:2423、方案名:无。

主芯片:NVP2010,2020芯片供应商:NEXTCHIP主芯片构架:DSP(NVP2010,2020)+AFE(AD9943)兼容CCD :510H(NTSC:ICX632;PAL:ICX633)景阳公司产品型号:59014、方案名:HAWK芯片供应商:NEXTCHIP主芯片构架:DSP(NVP2170、2170E)+AFE(AD9943)兼容CCD :760H(NTSC:ICX638;PAL:ICX639)景阳公司产品型号:59105、方案名:EFFIO-E芯片供应商:SONY主芯片构架:DSP(CXD4127GG)+AFE(CXD4816GG)兼容CCD :510H(NTSC:ICX632;PAL:ICX633);760H(NTSC:ICX638;PAL:ICX639);960H (NTSC:ICX672;PAL:ICX673)景阳公司产品型号:4920;5920;5930等6、方案名:ENHANCE(增强型) EFFIO-E 芯片供应商:SONY主芯片构架:DSP(CXD4140GG)+AFE(CXD5148GG)兼容CCD :第 1 页 景阳技术资料研发中心:吴文宪510H(NTSC:ICX632;PAL:ICX633);760H(NTSC:ICX638;PAL:ICX639);960H (NTSC:ICX672/810;PAL:ICX673/811)景阳公司产品型号:4920;5920;5930二代等7、方案名:EFFIO-S 芯片供应商:SONY 主芯片构架:DSP(CXD4130GG)+AFE(CXD5148GG)兼容CCD :510H(NTSC:ICX632;PAL:ICX633);760H(NTSC:ICX638;PAL:ICX639);960H (NTSC:ICX672/810;PAL:ICX673/811)景阳公司产品型号:目前搭配960H 的产品型号是5940系列等8、方案名:EFFIO-p 芯片供应商:SONY 主芯片构架:DSP(CXD4129GG)+AFE(CXD5148GG)兼容CCD :960H(NTSC:ICX662;PAL:ICX663)景阳公司产品型号:5950系列等9、方案名:seawolf芯片供应商:pixim主芯片构架:D8800C (含cmos sensor 和ISP )景阳公司产品型号:0586系列等10、方案名:无,主芯片mt9v136芯片供应商:Aptina(MICRON)主芯片构架:mt9v136(含cmos sensor 和ISP )10、方案名:无,主芯片OV7960芯片供应商:OV主芯片构架:OV7960(含cmos sensor 和ISP )第 2 页景阳技术资料研发中心:吴文宪。

TPS65910A3A1RSLR;TPS65910A3A1RSL;中文规格书,Datasheet资料

TPS65910,TPS65910A,TPS65910A3,TPS659101,TPS659102,TPS659103TPS659104,TPS659105,TPS659106,TPS659107,TPS659108,TPS659109 SWCS046O–MARCH2010–REVISED JULY2012 Integrated Power Management Unit Top SpecificationCheck forSamples:TPS65910,TPS65910A,TPS65910A3,TPS659101,TPS659102,TPS659103,TPS659104,TPS659105,TPS659106,TPS659107,TPS659108,TPS659109FEATURES APPLICATIONSThe purpose of the TPS65910device is to•Portable and handheld systemsprovide the following resources:•OMAP3power management•Embedded power controllerDESCRIPTION•Two efficient step-down dc-dc converters forThe TPS65910is an integrated power-management processor coresIC available in48-QFN package and dedicated to •One efficient step-down dc-dc converter for I/Oapplications powered by one Li-Ion or Li-Ion polymer powerbattery cell or3-series Ni-MH cells,or by a5-V input;•One efficient step-up5-V dc-dc converter it requires multiple power rails.The device providesthree step-down converters,one step-up converter,•SmartReflex™compliant dynamic voltageand eight LDOs and is designed to support the management for processor coresspecific power requirements of OMAP-based •8LDO voltage regulators and one RTC LDOapplications.(internal purpose)Two of the step-down converters provide power for •One high-speed I2C interface for general-dual processor cores and are controllable by a purpose control commands(CTL-I2C)dedicated class-3SmartReflex interface for optimum •One high-speed I2C interface for SmartReflex power savings.The third converter provides power for Class3control and command(SR-I2C)the I/Os and memory in the system.•Two enable signals multiplexed with SR-I2C,The device includes eight general-purpose LDOs configurable to control any supply state and providing a wide range of voltage and current processor cores supply voltage capabilities;they are fully controllable by the I2Cinterface.The use of the LDOs is flexible;they are •Thermal shutdown protection and hot-dieintended to be used as follows:Two LDOs are detectiondesignated to power the PLL and video DAC supply •A real-time clock(RTC)resource with:rails on the OMAP based processors,four general-–Oscillator for32.768-kHz crystal or32-kHz purpose auxiliary LDOs are available to provide built-in RC oscillator power to other devices in the system,and two LDOsare provided to power DDR memory supplies in –Date,time and calendarapplications requiring these memories.–Alarm capabilityIn addition to the power resources,the device •One configurable GPIOcontains an embedded power controller(EPC)to •DC-DC switching synchronization through manage the power sequencing requirements of the internal or external3-MHz clock OMAP systems and an(RTC).Figure1shows the top-level diagram of the device.Please be aware that an important notice concerning availability,standard warranty,and use in critical applications ofTexas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.PRODUCTION DATA information is current as of publication date.Copyright©2010–2012,Texas Instruments Incorporated Products conform to specifications per the terms of the TexasPSWCS046-001Ci Co Ci Ci Ci (VCCIO)Ci (VCC2)Ci (VCC1)TPS65910,TPS65910A,TPS65910A3,TPS659101,TPS659102,TPS659103TPS659104,TPS659105,TPS659106,TPS659107,TPS659108,TPS659109SWCS046O –MARCH 2010–REVISED JULY 2012Figure 1.48-QFN Top-Level Diagram2Submit Documentation Feedback Copyright ©2010–2012,Texas Instruments IncorporatedTPS65910,TPS65910A,TPS65910A3,TPS659101,TPS659102,TPS659103TPS659104,TPS659105,TPS659106,TPS659107,TPS659108,TPS659109 SWCS046O–MARCH2010–REVISED JULY2012 Table1.SUPPORTED PROCESSORS AND CORRESPONDING PART NUMBERSCompatible Processor(1)Part Number(1)TI processor-AM335x with DDR2TPS65910AA1RSLTI processor-AM335x with DDR3TPS65910A3A1RSL TI processors-AM1705/07,AM1806/08,AM3505/17,AM3703/15,DM3730/25,TPS65910A1RSL OMAP-L137/38,OMAP3503/15/25/30,TMS320C6742/6/8Samsung-S5PV210,S5PC110TPS659101A1RSLRockchip-RK29xx TPS659102A1RSLSamsung-S5PC100TPS659103A1RSLSamsung-S5P6440TPS659104A1RSLTI processors-DM643x,DM644x TPS659105A1RSLReserved TPS659106A1RSLFreescale-i.MX27,Freescale-i.MX35TPS659107A1RSLFreescale-i.MX508TPS659108A1RSLFreescale-i.MX51TPS659109A1RSL(1)The RSL package is available in tape and reel.See for details for corresponding part numbers,quantities and ordering information. ABSOLUTE MAXIMUM RATINGSover operating free-air temperature range(unless otherwise noted)Stresses beyond those listed under below may cause permanent damage to the device.These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated below are not implied.Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.The absolute maximum ratings for the TPS65910device are listed below:PARAMETER MIN MAX UNITVoltage range on pins/balls VCC1,VCC2,VCCIO,VCC3,VCC4,–0.37VVCC5,VCC6,VCC7Voltage range on pins/balls VDDIO–0.3 3.6VVoltage range on pins/balls OSC32KIN,OSC32KOUT,BOOT1,–0.3VRTC MAX+0.3VBOOT0Voltage range on pins/balls SDA_SDI,SCL_SCK,SDASR_EN2,–0.3VDDIO MAX+0.3VSCLSR_EN1,SLEEP,INT1,CLK32KOUT,NRESPWRONVoltage range on pins/balls PWRON–0.37VVoltage range on pins/balls PWRHOLD(1)GPIO_CKSYNC(2)–0.37V Functional junction temperature range–45150°CPeak output current on all other terminals than power resources–55mA(1)I/O supplied from VDDIO but which can be driven from to a VBAT voltage level(2)I/O supplied from VRTC but can be driven to a VBAT voltage levelTHERMAL CHARACTERISTICSover operating free-air temperature range(unless otherwise noted)DERATINGTA<25°C Power FACTOR ABOVE TA=70°C Power TA=85°C Power Package Rθja(°C/W)Rating(W)25°C(W)Rating(W)(mW/°C)RSL48-QFN37 2.637 1.481The thermal resistance RθJP junction-to-power PAD of the RSL package is1.1°C/WThe value of thermal resistance RθJA junction-to-ambient was measured on a high K.Copyright©2010–2012,Texas Instruments Incorporated Submit Documentation Feedback3TPS65910,TPS65910A,TPS65910A3,TPS659101,TPS659102,TPS659103TPS659104,TPS659105,TPS659106,TPS659107,TPS659108,TPS659109SWCS046O–MARCH2010–REVISED RECOMMENDED OPERATING CONDITIONSover operating free-air temperature range(unless otherwise noted)Lists of the recommended operating maximum ratings for the TPS65910device are given below.Note1:VCC7should be connected to the highest supply that is connected to the device VCCx pin.The exception is thatVCC2and VCC4can be higher than VCC7.Note2:VCC2and VCC4must be connected together(to the same voltage).Note3:If VDD3boost is used,VAUX33must be set to2.8V or higher and enabled before VDD3.PARAMETER TEST CONDITIONS MIN NOM MAX UNITV CC:Input voltage range on pins/balls VCC1,VCC2,VCCIO,VCC3,VCC4,VCC5,2.73.6 5.5VVCC7V CCP:Input voltage range on pins/balls VCC6 1.7 3.6 5.5VInput voltage range on pins/balls VDDIO 1.65 1.8/3.3 3.45VInput voltage range on pins/balls PWRON0 3.6 5.5VInput voltage range on pins/balls SDA_SDI,SCL_SCK,SDASR_EN2,SCLSR_EN1,1.65VDDIO 3.45V SLEEPInput voltage range on pins/balls PWRHOLD,GPIO_CKSYNC 1.65VDDIO 5.5VInput voltage range on balls BOOT1,BOOT0,OSC32KIN 1.65VRTC 1.95VOperating free-air temperature,T A–402785°CJunction temperature T J–4027125°CStorage temperature range–6527150°CLead temperature(soldering,10s)260°CPower ReferencesVREF filtering capacitor C O(VREF)Connected from VREF to REFGND100nFVDD1SMPSInput capacitor C I(VCC1)X5R or X7R dielectric10µFFilter capacitor C O(VDD1)X5R or X7R dielectric41012µFC O filter capacitor ESR f=3MHz10300mΩInductor L O(VDD1) 2.2µHL O inductor dc resistor DCR L125mΩVDD2SMPSInput capacitor C I(VCC2)X5R or X7R dielectric10µFFilter capacitor C O(VDD2)X5R or X7R dielectric41012µFC O filter capacitor ESR f=3MHz10300mΩInductor L O(VDD2) 2.2µHL O inductor dc resistor DCR L125mΩVIO SMPSInput capacitor C I(VIO)X5R or X7R dielectric10µFFilter capacitor C O(VIO)X5R or X7R dielectric41012µFC O filter capacitor ESR f=3MHz10300mΩInductor L O(VIO) 2.2µHL O inductor dc resistor DCR L125mΩVDIG1LDOInput capacitor C I(VCC6)X5R or X7R dielectric 4.7µFFiltering capacitor C O(VDIG1)0.8 2.2 2.64µFC O filtering capacitor ESR0500mΩVDIG2LDOFiltering capacitor C O(VDIG2)0.8 2.2 2.64µFC O filtering capacitor ESR0500mΩVPLL LDOInput capacitor C I(VCC5)X5R or X7R dielectric 4.7µFFiltering capacitor C O(VPLL)0.8 2.2 2.64µF4Submit Documentation Feedback Copyright©2010–2012,Texas Instruments IncorporatedTPS65910,TPS65910A,TPS65910A3,TPS659101,TPS659102,TPS659103TPS659104,TPS659105,TPS659106,TPS659107,TPS659108,TPS659109 SWCS046O–MARCH2010–REVISED JULY2012 RECOMMENDED OPERATING CONDITIONS(continued)over operating free-air temperature range(unless otherwise noted)Lists of the recommended operating maximum ratings for the TPS65910device are given below.Note1:VCC7should be connected to the highest supply that is connected to the device VCCx pin.The exception is thatVCC2and VCC4can be higher than VCC7.Note2:VCC2and VCC4must be connected together(to the same voltage).Note3:If VDD3boost is used,VAUX33must be set to2.8V or higher and enabled before VDD3.PARAMETER TEST CONDITIONS MIN NOM MAX UNITC O filtering capacitor ESR0500mΩVDAC LDOFiltering capacitor C O(VDAC)0.8 2.2 2.64µFC O filtering capacitor ESR0500mΩVMMC LDOInput capacitor C I(VCC4)X5R or X7R dielectric 4.7µFFiltering capacitor C O(VMMC)0.8 2.2 2.64µFC O filtering capacitor ESR0500mΩVAUX33LDOFiltering capacitor C O(VAUX33)0.8 2.2 2.64µFC O filtering capacitor ESR0500mΩVAUX1LDOInput capacitor C I(VCC3)X5R or X7R dielectric 4.7µFFiltering capacitor C O(VAUX1)0.8 2.2 2.64µFC O filtering capacitor ESR0500mΩVAUX2LDOFiltering capacitor C O(VAUX2)0.8 2.2 2.64µFC O filtering capacitor ESR0500mΩVRTC LDOInput capacitor C I(VCC7)X5R or X7R dielectric 4.7µFFiltering capacitor C O(VRTC)0.8 2.2 2.64µFC O filtering capacitor ESR0500mΩVDD3SMPSInput capacitor C I(VDD3)X5R or X7R dielectric 4.7µFFilter capacitor C O(VDD3)X5R or X7R dielectric41012µFC O filter capacitor ESR f=1MHz10300mΩInductor L O(VDD3) 2.8 4.7 6.6µHL O inductor DC resistor DCR L50500mΩBackup BatteryBattery or superCap supplying VBACKUP5102000mF Backup battery capacitor C BBCapacitor supplying VBACKUP140µF5to15mF101500Series resistorsΩ100to2000mF515I2C InterfacesSDA_SDI,SCL_SCK,SDASR_EN2,Connected to VDDIO 1.2kΩSCLSR_EN1external pull-up resistorCrystal Oscillator(connected from OSC32KIN to OSC32KOUT)Crystal frequency@specified load cap value32.768kHzCrystal tolerance@27°C–20020ppmOscillator contribution(not including crystalFrequency Temperature coefficient.–0.50.5ppm/°Cvariation)Secondary temperature coefficient–0.04–0.035–0.03ppm/°C2Voltage coefficient–22ppm/V Copyright©2010–2012,Texas Instruments Incorporated Submit Documentation Feedback5TPS65910,TPS65910A,TPS65910A3,TPS659101,TPS659102,TPS659103TPS659104,TPS659105,TPS659106,TPS659107,TPS659108,TPS659109SWCS046O–MARCH2010–REVISED RECOMMENDED OPERATING CONDITIONS(continued)over operating free-air temperature range(unless otherwise noted)Lists of the recommended operating maximum ratings for the TPS65910device are given below.Note1:VCC7should be connected to the highest supply that is connected to the device VCCx pin.The exception is thatVCC2and VCC4can be higher than VCC7.Note2:VCC2and VCC4must be connected together(to the same voltage).Note3:If VDD3boost is used,VAUX33must be set to2.8V or higher and enabled before VDD3.PARAMETER TEST CONDITIONS MIN NOM MAX UNIT Max crystal series resistor@Fundamental frequency90kΩCrystal load capacitor According to crystal data sheet612.5pFLoad crystal oscillator Coscinparallel mode Including parasitic PCB capacitor1225pF,CoscoutQuality factor800080000ESD SPECIFICATIONSover operating free-air temperature range(unless otherwise noted)TI STANDARD ESD METHOD STANDARD REFERENCE PERFORMANCEREQUIREMENTS Human body model(HBM)EIA/JESD22-A114D2000V2000VCharge device model(CDM)EIA/JESD22-C101C500V500V6Submit Documentation Feedback Copyright©2010–2012,Texas Instruments IncorporatedTPS65910,TPS65910A,TPS65910A3,TPS659101,TPS659102,TPS659103TPS659104,TPS659105,TPS659106,TPS659107,TPS659108,TPS659109 SWCS046O–MARCH2010–REVISED JULY2012 I/O PULLUP AND PULLDOWN CHARACTERISTICSover operating free-air temperature range(unless otherwise noted)(1)PARAMETER TEST CONDITIONS MIN TYP MAX UNITSDA_SDI,SCL_SCK,SDASR_EN2,SCLSR_EN1Programmable pullup(DFT,default Grounded,VDDIO=1.8V–45%8+45%kΩinactive)SLEEP programmable pulldown(default active)@1.8V,VRTC=1.8V2 4.510µA@1.8V,VRTC=1.8V,VCC7=2.72 4.510VPWRHOLD programmable pulldown(defaultµA active)@5.5V,VRTC=1.8V,VCC7=5.571430VBOOT0,BOOT1programmable pulldown(default@1.8V,VRTC=1.8V2 4.510µA active)NRESPWRON pulldown@1.8V,VCC7=5.5V,OFF state2 4.510µA32KCLKOUT pulldown(disabled in Active-sleep@1.8V,VRTC=1.8V,OFF state2 4.510µA state)PWRON programmable pullup(default active)Grounded,VCC7=5.5V–40–31–15µAGPIO_CKSYNC programmable pullup(defaultGrounded,VRTC=1.8V–27–18–9µA active)(1)The internal pullups on the CTL-I2C and SR-I2C balls are used for test purposes or when the SR-I2C interface is not used.Discretepullups to the VIO supply must be mounted on the board in order to use the I2C interfaces.The internal I2C pullups must not be used for functional applicationsCopyright©2010–2012,Texas Instruments Incorporated Submit Documentation Feedback7TPS65910,TPS65910A,TPS65910A3,TPS659101,TPS659102,TPS659103TPS659104,TPS659105,TPS659106,TPS659107,TPS659108,TPS659109SWCS046O–MARCH2010–REVISED DIGITAL I/O VOLTAGE ELECTRICAL CHARACTERISTICSover operating free-air temperature range(unless otherwise noted)PARAMETER MIN TYP MAX UNITRelated I/O:PWRONLow-level input voltage V IL0.3x VCC7V High-level input voltage V IH0.7x VCC7VRelated I/Os:PWRHOLD,GPIO_CKSYNCLow-level input voltage V IL0.45VVDDIO/VHigh-level input voltage V IH 1.3VCC7VCC7Related I/Os:BOOT0,BOOT1,OSC32KINLow-level input voltage V IL0.35x VRTC V High-level input voltage V IH0.65x VRTC VRelated I/Os:SLEEPLow-level input voltage V IL0.35x VDDIO V High-level input voltage V IH0.65x VDDIO VRelated I/Os:NRESPWRON,INT1,32KCLKOUTLow-level output voltage V OL I OL=100µA0.2VI OL=2mA0.45V High-level output voltage V OH I OH=100µA VDDIO–0.2VI OH=2mA VDDIO–0.45VRelated Open-Drain I/Os:GPIO0Low-level output voltage V OL I OL=100µA0.2VI OL=2mA0.45VI2C-Specific Related I/Os:SCL,SDA,SCLSR_EN1,SDASR_EN2Low-level input voltage V IL–0.50.3x VDDIO V High-level input voltage V IH0.7x VDDIO V Hysteresis0.1x VDDIO VLow-level output voltage V OL@3mA(sink current),VDDIO=1.8V0.2×VDDIO VLow-level output voltage V OL@3mA(sink current),VDDIO=3.3V0.4x VDDIO V8Submit Documentation Feedback Copyright©2010–2012,Texas Instruments IncorporatedTPS65910,TPS65910A,TPS65910A3,TPS659101,TPS659102,TPS659103TPS659104,TPS659105,TPS659106,TPS659107,TPS659108,TPS659109 SWCS046O–MARCH2010–REVISED JULY2012 I2C INTERFACE AND CONTROL SIGNALSover operating free-air temperature range(unless otherwise noted)NO.PARAMETER TEST CONDITIONS MIN TYP MAXINT1rise and fall times,C L=5to35pF510nsNRESPWRON rise and fall times,C L=5to35pF510nsSLAVE HIGH–SPEED MODESCL/SCLSR_EN1and SDA/SDASR_EN2rise and fall1080nstime,C L=10to100pFData rate 3.4MbpsI3t su(SDA-SCLH)Setup time,SDA valid to SCL high10nsI4t h(SCLL-SDA)Hold time,SDA valid from SCL low070nsI7t su(SCLH-SDAL)Setup time,SCL high to SDA low160nsI8t h(SDAL-SCLL)Hold time,SCL low from SDA low160nsI9t su(SDAH-SCLH)Setup time,SDA high to SCL high160nsSLAVE FAST MODESCL/SCLSR_EN1and SDA/SDASR_EN2rise and fall20+250nstime,C L=10to400pF0.1×C LData rate400KbpsI3t su(SDA-SCLH)Setup time,SDA valid to SCL high100nsI4t h(SCLL-SDA)Hold time,SDA valid from SCL low00.9µsI7t su(SCLH-SDAL)Setup time,SCL high to SDA low0.6µsI8t h(SDAL-SCLL)Hold time,SCL low from SDA low0.6µsI9t su(SDAH-SCLH)Setup time,SDA high to SCL high0.6µsSLAVE STANDARD MODESCL/SCLSR_EN1and SDA/SDASR_EN2rise and fall250nstime,C L=10to400pFData rate100KbpsI3t su(SDA-SCLH)Setup time,SDA valid to SCL high250nsI4t h(SCLL-SDA)Hold time,SDA valid from SCL low0µsI7t su(SCLH-SDAL)Setup time,SCL high to SDA low 4.7µsI8t h(SDAL-SCLL)Hold time,SCL low from SDA low4µsI9t su(SDAH-SCLH)Setup time,SDA high to SCL high4µsSWITCHING CHARACTERISTICSSLAVE HIGH–SPEED MODEI1t w(SCLL)Pulse duration,SCL low160nsI2t w(SCLH)Pulse duration,SCL high60nsSLAVE FAST MODEI1t w(SCLL)Pulse duration,SCL low 1.3µsI2t w(SCLH)Pulse duration,SCL high0.6µsSLAVE STANDARD MODEI1t w(SCLL)Pulse duration,SCL low 4.7µsI2t w(SCLH)Pulse duration,SCL high4µs Copyright©2010–2012,Texas Instruments Incorporated Submit Documentation Feedback9TPS65910,TPS65910A,TPS65910A3,TPS659101,TPS659102,TPS659103TPS659104,TPS659105,TPS659106,TPS659107,TPS659108,TPS659109SWCS046O–MARCH2010–REVISED POWER CONSUMPTIONover operating free-air temperature range(unless otherwise noted)All current consumption measurements are relative to the FULL chip,all VCC inputs set to VBAT voltage.PARAMETER TEST CONDITIONS MIN TYP MAX UNITDevice BACKUP state VBAT=2.4V,VBACKUP=0V,1116µA VBAT=0V,VBACKUP=3.2V69Device OFF state VBAT=3.6V,CK32K clock runningBOOT[1:0]=00:32-kHz RC oscillator16.523BOOT[1:0]=01:32-kHz quartz or bypass oscillator,BOOT0P1520=0µA BOOT[1:0]=01,Backup Battery Charger on,VBACKUP=3.23242VVBAT=5V,CK32K clock running:2028BOOT[1:0]=00:RC oscillatorDevice SLEEP state VBAT=3.6V,CK32K clock running,PWRHOLDP=0BOOT[1:0]=00,3DC-DCs on,5LDOs and VRTC on,no load295µA BOOT[1:0]=01,3DC-DCs on,3LDOs and VRTC on,no load,279BOOT0P=0Device ACTIVE state VBAT=3.6V,CK32K clock running,PWRHOLDP=0BOOT[1:0]=00,3DC-DCs on,5LDOs and VRTC on,no load1BOOT[1:0]=01,3DC-DCs on,3LDOs and VRTC on,no load,0.9mABOOT0P=0BOOT[1:0]=00,3DC-DCs on PWM mode(VDD1_PSKIP=VDD2_PSKIP=VIO_PSKIP=0),5LDOs and VRTC on,no21loadPOWER REFERENCES AND THRESHOLDSover operating free-air temperature range(unless otherwise noted)PARAMETER TEST CONDITIONS MIN TYP MAX UNITOutput reference voltage(VREFDevice in active or low-power mode–1%0.85+1%V terminal)Main battery charged Measured on VCC7terminalthreshold VMBCH(programmable)Triggering monitored through NRESPRWONVMBCH_VSEL=11,BOOT[1:0]=11or003VMBCH_VSEL=10 2.9VVMBCH_VSEL=01 2.8VMBCH_VSEL=00bypassedMain battery discharged Measured on VCC7terminal(MTL prg)VMBCH–V threshold VMBDCH(programmable)Triggering monitored through INT1100mVMain battery low threshold VMBLO Measured on VCC7terminal(Triggering2.5 2.6 2.7V (MB comparator)monitored on terminal NRESPWRON)VBACKUP=0V,measured on terminal VCC7Main battery high threshold VMBHI 2.6 2.753(MB comparator)VVBACKUP=3.2V,measured on terminal VCC7 2.5 2.553Main battery not present threshold Measured on terminal VCC71.92.1 2.2V VBNPR(Triggering monitored on terminal VRTC)V CC=3.6VGround current(analog references+comparators+backup battery Device in OFF state8µA switch)Device in ACTIVE or SLEEP state2010Submit Documentation Feedback Copyright©2010–2012,Texas Instruments Incorporated分销商库存信息:TITPS65910A3A1RSLR TPS65910A3A1RSL。

6N134中文资料

6N134中⽂资料FeaturesDual Marked with Device Part Number and DSCC Drawing NumberManufactured and Tested on a MIL-PRF-38534 Certified LineQML-38534, Class H and K Five Hermetically Sealed Package Configurations Performance Guaranteed over -55°C to +125°C ? High Speed: 10 M Bit/sCMR: > 10,000 V/µs Typical 1500 Vdc Withstand Test Voltage2500 Vdc Withstand Test Voltage for HCPL-565X High Radiation Immunity 6N137, HCPL-2601, HCPL-2630/-31 Function Compatibility ? Reliability DataTTL Circuit CompatibilityApplicationsMilitary and SpaceHigh Reliability SystemsTransportation, Medical, and Life Critical SystemsLine ReceiverVoltage Level ShiftingIsolated Input Line Receiver Isolated Output Line Driver Logic Ground Isolation Harsh Industrial EnvironmentsIsolation for Computer,Communication, and Test Equipment SystemsDescriptionThese units are single, dual and quad channel, hermetically sealed optocouplers. The products are capable of operation and storage over the full military temperature range and can be purchased as either standard product or with full MIL-PRF-38534 Class Level H or K testing or from the appropri-ate DSCC Drawing. All devices are manufactured and tested on a MIL-PRF-38534 certified line and are included in the DSCC Quali-fied Manufacturers List QML-38534 for Hybrid Microcircuits.Quad channel devices areavailable by special order in the 16 pin DIP through hole packages.Truth Table(Positive Logic)Multichannel DevicesInput Output On (H)L Off (L)HFunctional DiagramMultiple Channel Devices AvailableSingle Channel DIP Input Enable Output On (H)H L Off (L)H H On (H)L H Off (L)LH*See matrix for available extensions.Hermetically Sealed, High Speed,High CMR, Logic Gate Optocouplers Technical Data6N134*81028HCPL-563X HCPL-663X HCPL-565X 5962-98001HCPL-268K HCPL-665X 5962-90855HCPL-560XCAUTION: It is advised that normal static precautions be taken in handling and assembly of this component to prevent damage and/or degradation which may be induced by ESD.V CC V OUTV E GNDThe connection of a 0.1 µF bypass capacitor between V CC and GND is recommended.Selection Guide–Package Styles and Lead Configuration OptionsPackage16 Pin DIP 8 Pin DIP 8 Pin DIP 8 Pin DIP 16 Pin Flat Pack 20 Pad LCCC Lead Style Through Hole Through Hole Through Hole Through Hole Unformed Leads Surface MountChannels 212242Common Channel V CC , GND None V CC , GND V CC , GND V CC , GND None WiringWithstand Test Voltage 1500 Vdc 1500 Vdc 1500 Vdc 2500 Vdc 1500 Vdc 1500 Vdc Agilent Part # & Options Commercial6N134*HCPL-5600HCPL-5630HCPL-5650HCPL-6650HCPL-6630MIL-PRF-38534, Class H 6N134/883BHCPL-5601HCPL-5631HCPL-5651HCPL-6651HCPL-6631MIL-PRF-38534, Class K HCPL-268K HCPL-560K HCPL-563K HCPL-665K HCPL-663K Standard Lead Finish Gold Plate Gold Plate Gold Plate Gold Plate Gold PlateSolder PadsSolder Dipped Option #200Option #200Option #200Option #200Butt Cut/Gold Plate Option #100Option #100Option #100Gull Wing/Soldered Option #300Option #300Option #300Class H SMD Part #Prescript for all below None 5962-None None None None Either Gold or Solder 8102801EX 9085501HPX 8102802PX 8102805PX 8102804FX 81028032XGold Plate 8102801EC 9085501HPC 8102802PC 8102805PC 8102804FCSolder Dipped 8102801EA 9085501HPA 8102802PA 8102805PA81028032A Butt Cut/Gold Plate 8102801UC 9085501HYC 8102802YC Butt Cut/Soldered 8102801UA 9085501HYA 8102802YA Gull Wing/Soldered 8102801TA 9085501HXA8102802ZA Class K SMD Part #Prescript for all below 5962-5962-5962-5962-5962-Either Gold or Solder 9800101KEX 9085501KPX 9800102KPX 9800104KFX 9800103K2XGold Plate 9800101KEC 9085501KPC 9800102KPC 9800104KFCSolder Dipped 9800101KEA 9085501KPA 9800102KPA 9800103K2AButt Cut/Gold Plate 9800101KUC 9085501KYC 9800102KYC Butt Cut/Soldered 9800101KUA 9085501KYA 9800102KYA Gull Wing/Soldered9800101KTA 9085501KXA 9800102KZA*JEDEC registered part.Each channel contains a GaAsP light emitting diode which isoptically coupled to an integrated high speed photon detector. The output of the detector is an open collector Schottky clamped transistor. Internal shields provide a guaranteed common mode transient immunityspecification of 1000 V/µs. For Isolation Voltage applications requiring up to 2500 Vdc, the HCPL-5650 family is also available. Package styles for these parts are 8 and 16 pin DIP through hole (case outlines P andE respectively), and 16 pin surface mount DIP flat pack(case outline F), leadless ceramic chip carrier (case outline 2).Devices may be purchased with a variety of lead bend and plating options. See Selection Guide Table for details. Standard Microcircuit Drawing (SMD)parts are available for each package and lead style.Because the same electrical die (emitters and detectors) are used for each channel of each device listed in this data sheet, absolute maximum ratings, recommended operating conditions, electrical specifications, and performance characteristics shown in the figures are identical for all parts.Occasional exceptions exist due to package variations and limitations,and are as noted. Additionally, the same package assembly processes and materials are used in all devices. These similarities give justification for the use of data obtained from one part torepresent other parts’ performance for reliability and certain limited radiation test results.Outline Drawings16 Pin DIP Through Hole, 2 ChannelsFunctional DiagramsNote: All DIP and flat pack devices have common V CC and ground. Single channel DIP has an enable pin 7. LCCC (leadless ceramic chip carrier) package has isolated channels with separate VCC and ground connections. All diagrams are “top view.”Leaded Device MarkingLeadless Device MarkingNOTE: DIMENSIONS IN MILLIMETERS (INCHES).COMPLIANCE INDICATOR,*DATE CODE, SUFFIX (IF NEEDED)COUNTRY OF MFR.Agilent CAGE CODE*Agilent DESIGNATORDSCC SMD*PIN ONE/ ESD IDENTAgilent P/N DSCC SMD** QUALIFIED PARTS ONLYCOMPLIANCE INDICATOR,*DATE CODE, SUFFIX (IF NEEDED)DSCC SMD*Agilent CAGE CODE*Agilent DESIGNATORCOUNTRY OF MFR.Agilent P/N PIN ONE/ ESD IDENTDSCC SMD** QUALIFIED PARTS ONLYOutline Drawings (continued)16 Pin Flat Pack, 4 Channels8 Pin DIP Through Hole, 2 Channels 2500 Vdc Withstand Test Voltage20 Terminal LCCC Surface Mount,2Channels8 Pin DIP Through Hole, 1 and 2 Channels0.36 (0.014)NOTE: DIMENSIONS IN MILLIMETERS (INCHES).2.29 (0.090) 2.79 (0.110)NOTE: DIMENSIONS IN MILLIMETERS (INCHES).NOTE: DIMENSIONS IN MILLIMETERS (INCHES).NOTE: DIMENSIONS IN MILLIMETERS (INCHES). SOLDER THICKNESS 0.127 (0.005) MAX.Hermetic Optocoupler OptionsRecommended Operating ConditionsParameterSymbol Min.Max.Units Input Current, Low Level, Each Channel I FL 0250µA Input Current, High Level, Each Channel*I FH 1020mA Supply Voltage, OutputV CC 4.55.5VFan Out (TTL Load) Each ChannelN6*Meets or exceeds DSCC SMD and JEDEC requirements.Absolute Maximum Ratings(No derating required up to +125°C)Storage Temperature Range, T S ...................................-65°C to +150°C Operating Temperature, T A..........................................-55°C to +125°C Case Temperature, T C ................................................................+170°C Junction Temperature, T J ...........................................................+175°C Lead Solder Temperature ...............................................260°C for 10 s Peak Forward Input Current, I F PK , (each channel,≤1 ms duration)......................................................................40 mA Average Input Forward Current, I F AVG (each channel)................20 mA Input Power Dissipation (each channel).....................................35 mW Reverse Input Voltage, V R (each channel).........................................5 V Supply Voltage, V CC (1 minute maximum)........................................7 V Output Current, I O (each channel)...............................................25 mA Output Power Dissipation (each channel). (40)mW Output Voltage, V O (each channel)..................................................7 V*Package Power Dissipation, P D (each channel)........................200 mW*Selection for higher output voltages up to 20 V is available.Single Channel Product OnlyEmitter Input Voltage, V E ...............................................................5.5 VNote enable pin 7. An external 0.01 µF to 0.1 µF bypass capacitor must be connected between V CC and ground for each package type.8 Pin Ceramic DIP Single Channel SchematicESD Classification(MIL-STD-883, Method 3015)HCPL-5600/01/0K ...............................................................(?), Class 16N134, 6N134/883B, HCPL-5630/31/3K, HCPL-5650/51, HCPL-6630/31/3K and HCPL-6650/51/5K.......................(Dot), Class 3Electrical Characteristics (T= -55°C to +125°C, unless otherwise specified)*Identified test parameters for JEDEC registered parts.**All typical values are at V CC = 5 V , T A = 25°C. Recommended Operating Conditions (cont’d.)Single Channel Product Only [10]ParameterSymbol Min.Max.Units High Level Enable Voltage V EH 2.0V CC V Low Level Enable VoltageV EL0.8VElectrical Characteristics, (Contd.) T= -55°C to +125°C unless otherwise specifiedSingle Channel Product Only Low Level I EL V CC = 5.5 V,1, 2, 3-1.45-2.0mA Enable Current V E = 0.5 V High Level V EH 1, 2, 3 2.0V10Enable Voltage Low Level V EL 1, 2, 30.8VEnable Voltage*Identified test parameters for JEDEC registered part.**All typical values are at V CC = 5 V , T A = 25°C.Typical Characteristics, T = 25°C, V = 5 VDual and Quad Channel Product Only Input-Input I I-I 0.5nA Relative Humidity = 45%4Leakage CurrentV I-I = 500 V, t = 5 s Resistance (Input-Input)R I-I 1012V I-I = 500 V 4Capacitance (Input-Input)C I-I0.55pF f = 1 MHz4Notes:1. Each channel.2. All devices are considered two-terminal devices; I I-O is measured between all input leads or terminals shorted together and alloutput leads or terminals shorted together.3. Measured between each input pair shorted together and all output connections for that channel shorted together.4. Measured between adjacent input pairs shorted together for each multichannel device.5. t PHL propagation delay is measured from the 50% point on the leading edge of the input pulse to the 1.5 V point on the leadingedge of the output pulse. The t PLH propagation delay is measured from the 50% point on the trailing edge of the input pulse to the1.5 V point on the trailing edge of the output pulse.6. The HCPL-6630, HCPL-6631, and HCPL-663K dual channel parts function as two independent single channel units. Use the singlechannel parameter limits for each channel.7. CM L is the maximum rate of rise of the common mode voltage that can be sustained with the output voltage in the logic low state(V O < 0.8 V). CM H is the maximum rate of fall of the common mode voltage that can be sustained with the output voltage in the logic high state (V O > 2.0 V).8. This is a momentary withstand test, not an operating condition.9. It is essential that a bypass capacitor (0.01 to 0.1 µF, ceramic) be connected from V CC to ground. Total lead length between bothends of this external capacitor and the isolator connections should not exceed 20 mm.10. No external pull up is required for a high logic state on the enable input.11. The t ELH enable propagation delay is measured from the 1.5 V point on the trailing edge of the enable input pulse to the 1.5 Vpoint on the trailing edge of the output pulse.12. The t EHL enable propagation delay is measured from the 1.5 V point on the leading edge of the enable input pulse tothe 1.5 Vpoint on the leading edge of the output pulse.13. Standard parts receive 100% testing at 25°C (Subgroups 1 and 9). SMD and 883B parts receive 100% testing at 25, 125, and-55°C (Subgroups 1 and 9, 2 and 10, 3 and 11, respectively).14. Parameters are tested as part of device initial characterization and after design and process changes. Parameters are guaranteedto limits specified for all lots not specifically tested.15. Not required for 6N134, 6N134/883B, 8102801, HCPL-268K and 5962-9800101 types.16. Required for 6N134, 6N134/883B, 8102801, HCPL-268K and 5962-9800101 types.17. Not required for HCPL-5650, HCPL-5651 and 8102805 types.18. Required for HCPL-5650, HCPL-5651 and 8102805 types only.Figure 1. High Level Output Currentvs. Temperature.5 VV O * C L INCLUDES PROBE AND STRAY WIRING CAPACITANCE. Figure 4. Test Circuit for t PHL and t PLH .*I +5 V OUTPUT V O MONITORING NODEFigure 7. Test Circuit for Common Mode Transient Immunity and Typical Waveforms.11OUTPUT V OMONITORINGNODET A = +125 °C* ALL CHANNELS TESTED SIMULTANEOUSLY.V CCI O = 25 mAFigure 10. Operating Circuit for Burn-In and Steady State Life Tests. Figure 8. Test Circuit for t EHL and t ELH.Figure 9. Enable Propagation Delayvs. Temperature.MIL-PRF-38534 Class H,Class K, and DSCC SMDTest ProgramAgilent’s Hi-Rel Optocouplers arein compliance with MIL-PRF-38534 Classes H and K. Class Hand Class K devices are also incompliance with DSCC drawings81028, 5962-90855 and 5962-98001.Testing consists of 100% screen-ing and quality conformanceinspection to MIL-PRF-38534./doc/4e2d970a03d8ce2f006623a8.htmlData subject to change.Copyright ? 1999 Agilent TechnologiesObsoletes 5968-4743E5968-9407E (10/00)。

TPS65100中文资料

FB2 REF FB4 BASE

SW SW FB1 SUP

C2+ C2−/MODE

OUT3

FB3 VCOM PGND PGND

GND

R4

VO1

D1

Up to 15 V/350 mA

C5 R1

C4 22 µF

C2 0.22 µF R2

Vo3 up to 30 V/20 mA

R5

C7

0.22 µF

R6

C11 220 nF

Copyright © 2003–2004, Texas Instruments Incorporated

Байду номын сангаас

元器件交易网

TPS65100 TPS65105

SLVS496B – SEPTEMBER 2003 – REVISED MARCH 2004

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

Freescale i.MX6 Dual Quad TPS659114电源管理集成电路用户指南说明书

1SWCU181C–January 2016–Revised September 2016Submit Documentation FeedbackCopyright ©2016,Texas Instruments IncorporatedTPS659114for Freescale i.MX6Dual/Quad User's Guide User's GuideSWCU181C–January 2016–Revised September 2016TPS659114for Freescale i.MX6Dual/Quad User's Guide1IntroductionThis document is an application note describing the EEPROM configuration and the power-up sequence of the TPS659114power-management integrated circuit (PMIC).For details of the PMIC features and performance,refer to the full specification document TPS65911data manual (SWCS049).SWCU181-0012.7V < Vin <3.6V If LDO1 or LDO2usedPlatform Connection 2SWCU181C–January 2016–Revised September 2016Submit Documentation FeedbackCopyright ©2016,Texas Instruments IncorporatedTPS659114for Freescale i.MX6Dual/Quad User's Guide2Platform ConnectionFigure 1.Connecting TPS659114to Freescale i.MX6 EEPROM Setting3SWCU181C–January 2016–Revised September 2016Submit Documentation FeedbackCopyright ©2016,Texas Instruments IncorporatedTPS659114for Freescale i.MX6Dual/Quad User's Guide 3EEPROM SettingTable 1describes the EEPROM configuration for the TPS659114power-up sequence with BOOT1=1.When a resource is associated to time slot 0,it means that the resource is OFF at power up.Table 1.EEPROM Configuration for TPS659114REGISTERBITDESCRIPTIONOPTION SELECTEDVDD1_OP_REG/VDD1_SR_REG SEL VDD1voltage level selection for boot. 1.5V VDD1_REG VGAIN_SELVDD1gain selection,x1or x2x1EEPROM VDD1time slot selection 7DCDCCTRL_REG VDD1_PSKIP VDD1pulse skip mode enable Skip enabledVDD2_OP_REG/VDD2_SR_REG SEL VDD2voltage level selection for boot 1.1V VDD2_REG VGAIN_SEL VDD2gain selection,x1or x3x3EEPROM VDD2time slot selection 3DCDCCTRL_REG VDD2_PSKIP VDD2pulse skip mode enable Skip enabledVIO_REG SEL[3:9]VIO voltage selection 1.5V EEPROM VIO time slot selection 7DCDCCTRL_REG VIO_PSKIP VIO pulse skip mode enableSkip enabled VDDCtrl_OP_REG/VDDCtrl_SR_REG SELVDDCtrl voltage level selection for boot 1.35V EEPROM VDDCtrl time slot 6LDO1_REG SEL[7:2]LDO1voltage selection 1.8V EEPROM LDO1time slot 5LDO2_REG SEL[7:2]LDO2voltage selection 1.5V EEPROM LDO2time slot 4LDO3_REG SEL[6:2]LDO3voltage selection 2.5V EEPROM LDO3time slot 5LDO4_REG SEL[7:2]LDO4voltage selection 3.0V EEPROM LDO4time slot 1LDO5_REG SEL[6:2]LDO5voltage selection 2.8V EEPROM LDO5time slot 2LDO6_REG SEL[6:2]LDO6voltage selection 3.3V EEPROM LDO6time slot 4LDO7_REG SEL[6:2]LDO7voltage selection 3.3V EEPROM LDO7time slot 4LDO8_REG SEL[6:2]LDO8voltage selection 3.3V EEPROM LDO8time slot 5CLK32KOUT pinCLK32KOUT time slot 8NRESPWRON,NRESPWRON2pin NRESPWRON time slot 9GPIO0pin GPIO0time slot 1GPIO2pin GPIO2time slot 0GPIO6pin GPIO6time slot 0GPIO7pin GPIO7time slotVRTC_REGVRTC_OFFMASK 0=VRTC LDO will be in low-power mode during OFF state.1=VRC LDO will be in full-power mode during OFF state.Full-power modeDEVCTRL_REG CK32K_CTRL 0=Clock source is crystal/external clock.1=Clock source is internal RC oscillator.ExternalEEPROM Setting 4SWCU181C–January 2016–Revised September 2016Submit Documentation FeedbackCopyright ©2016,Texas Instruments IncorporatedTPS659114for Freescale i.MX6Dual/Quad User's GuideTable 1.EEPROM Configuration for TPS659114(continued)REGISTERBITDESCRIPTIONOPTION SELECTEDDEVCTRL_REGDEV_ON0=No impact1=Will maintain device on,in ACTIVE or SLEEP stateDEVCTRL2_REG TSLOT_LENGTH Boot sequence time slot duration:0=0.5ms 1=2ms2msDEVCTRL2_REG PWON_LP_OFF 0=Turn-off after PWRON long press not allowed.1=Turn-off after PWRON long press.1DEVCTRL2_REG PWON_LP_RST 0=No impact1=Reset digital core when device is OFF.0DEVCTRL2_REG IT_POL 0=INT1signal will be active low.1=INT1signal will be active high.Active lowINT_MSK_REGVMBHI_IT_MSK0=Device automatically switches on at NO SUPPLY-to-OFF or BACKUP-to-OFF transition.1=Start-up is reason required before switch-on.1=Start-up requires activity on PWRHOLDor PWRONINT_MSK3_REG GPIO5_F_IT_MSK0=GPIO5falling edge detection interrupt not masked.1=GPIO5falling edge detection interrupt masked.MaskedINT_MSK3_REG GPIO5_R_IT_MSK 0=GPIO5rising edge detection interrupt not masked.1=GPIO5rising edge detection interrupt masked.MaskedINT_MSK3_REG GPIO4_F_IT_MSK 0=GPIO4falling edge detection interrupt not masked.1=GPIO4falling edge detection interrupt masked.MaskedINT_MSK3_REG GPIO4_R_IT_MSK 0=GPIO4rising edge detection interrupt not masked.1=GPIO4rising edge detection interrupt masked.MaskedGPIO0_REG GPIO_ODEN 0=GPIO0configured as push-pull output.1=GPIO0configured as open-drain output.Push-pull WATCHDOG_REGWATCHDOG_EN0=Watchdog disabled1=Watchdog enabled,periodic operation with 100sDisabledVMBCH_REG VMBBUF_BYPASS 0=Enable input buffer for external resistive divider.1=In single-cell system,disable buffer for lower power consumption.Enable bufferVMBCH_REG VMBCH_SEL[5:1]Select threshold for boot gating comparator COMP1,2.5–3.5V.3.1VEEPROMAUTODEV_ON0=PWRHOLD pin is used as PWRHOLD feature.1=PWRHOLD pin is GPI.After power-on,DEV_ON is set high internally,no processor action needed to maintain supplies.PWRHOLD feature implementedEEPROM PWRDN_POL 0=PWRDN signal is active low.1=PWRDN signal is active high.Active low1PWRON button press falling edge 2Valid press after debounce3First step of power up sequence available for DCDC,LDO activation.Time slot (2ms between slots):Event DescriptionEvent:VIO,1.3-A limit LDO6, 300-mA limit LDO7, 300-mA limit VDD1,2-A limit LDO1, 320-mA limit LDO8, 300-mA limit VDDCTRL,6-A+limitCLK32KOUTLDO3, 200-mA limit PWRON buttonVDD_RTC/VRTCLDO4, 50-mA limit LDO5, 300-mA limit VDD2, 1.2-A limit LDO2, 320-mA limit GPIO0, push-pull NRESPWRONEEPROM Setting5SWCU181C–January 2016–Revised September 2016Submit Documentation FeedbackCopyright ©2016,Texas Instruments IncorporatedTPS659114for Freescale i.MX6Dual/Quad User's Guide Figure 2.Timing DiagramGetting Started With 6SWCU181C–January 2016–Revised September 2016Submit Documentation FeedbackCopyright ©2016,Texas Instruments IncorporatedTPS659114for Freescale i.MX6Dual/Quad User's Guide4Getting Started With TPS6591144.1First Initialization4.1.1DCDC Maximum Current CapabilityUpon reset,all buck converters initialize with ILMAX =0,which may not allow proper regulation across all expected loads.In VIO_REG,VDD1_REG,and VDD2_REG,set the ILMAX bit according to the required maximum current.4.1.2I/O Polarity/Muxing ConfigurationVoltage scaling for VDD1,VDD2,and VDDCtrl can be done either through the main I 2C interface orthrough dedicated interface EN1/EN2.Refer to the processor documentation for information on which one is supported.To enable the dedicated voltage scaling interface,set the SR_CTL_I2C_SEL bit to 0in the DEVCTRL_REG register.If sleep mode is supported,program the SLEEPSIG_POL bit in the DEVCTRL2_REG register according to the GPIO from the processor.This can be set to active-low or active-high for SLEEP transitions.Software can configure specific power resources to enter the LOW-POWER or OFF state in sleep mode.In the DEVCTRL_REG register,set the DEV_SLP bit to 1to allow the SLEEP transition when requested through the SLEEP pin.Update the GPIOx configuration (GPIOx_REG)based on the specification needs.4.1.3Define Wake Up/Interrupt Event (SLEEP or OFF)Select the appropriate bits in the INT_MSK_REG,INT_MSK2_REG,and INT_MSK3_REG registers to activate an interrupt to the processor on the INT1line.4.1.4Backup Battery ConfigurationBackup Battery charging is disabled by default.To enable,set the BBCHEN bit to 1in the BBCH_REG register.The maximum voltage can be set based on backup battery specifications by using the BBSEL bits in the BBCH_REG register.4.1.5Sleep Platform ConfigurationSleep mode is disabled by default.To use the sleep pin,sleep mode must first be enabled by setting DEV_SLP to 1in the DEVCTRL_REG.Configure the state of the DC-DCs and LDOs when the SLEEP signal is used.By default,in sleep mode all resources maintain their output voltage and load capability,but response to transients (load change)is reduced.GPIO0can follow sleep state.Resources that must provide full load capability must be set in the SLEEP_KEEP_LDO_ON_REG and SLEEP_KEEP_RES_ON_REG registers.Resources that can be set to off in the SLEEP state to optimize power consumption must be set in the SLEEP_SET_LDO_OFF_REG and SLEEP_SET_RES_OFF_REG registers.4.2Event Management Through InterruptsThis section describes the TPS659114interrupts.4.2.1INT_STS_REG.VMBHI_ITThe VMBHI_IT interrupt bit indicates that a supply (VBAT)is connected (PMIC leaving the BACKUP or NO SUPPLY state)and the system must be initialized (see Section 4.1,First Initialization ).4.2.2INT_STS_REG.PWRON_ITThe PWRON_IT interrupt bit is triggered by pressing the PWRON button.If the device is in the OFF or SLEEP state,then this acts as a wake-up event and resources are reinitialized. Ordering Information7SWCU181C–January 2016–Revised September 2016Submit Documentation FeedbackCopyright ©2016,Texas Instruments IncorporatedTPS659114for Freescale i.MX6Dual/Quad User's Guide 4.2.3INT_STS_REG.PWRON_LP_ITThe PWRON_LP_IT interrupt bit is the PWRON long-press interrupt.This interrupt is generated when the PWRON button is pressed for 4seconds.The application processor can make a decision to acknowledge the interrupt.If this interrupt is not acknowledged within the next second,the device interprets this as a power-down event.4.2.4INT_STS_REG.HOTDIE_ITThe HOTDIE_IT interrupt bit indicates that the temperature of the die is reaching the limit.The software must take action to decrease the power consumption before automatic shutdown.4.2.5INT_STS_REG.PWRHOLD_R/F_ITThe PWRHOLD_R/F_IT interrupt bit indicates a GPI interrupt event.4.2.6INT_STS_REG.RTC_ALARM_ITThe RTC_ALARM_IT interrupt bit is triggered when the RTC alarm set time is reached.4.2.7INT_STS2(3)_REG.GPIO_R/F_ITThe GPIOx_R/F_IT interrupt bit indicates a GPIO1,GPIO2or GPIO3interrupt event.It can be used to wake up the device from SLEEP state.This can be an interrupt coming from any peripheral device or alike.4.2.8INT_STS3_REG.PWRDN_ITThe PWRDN_IT interrupt bit is triggered when PWRDN reset is detected.4.2.9INT_STS3_REG.VMBDCH2_H/L_ITThe VMBDCH2_H_IT or VMBDCH2_L_IT interrupt bit is triggered when comparator 2input (VCCS)is above or below the threshold,respectively.4.2.10INT_STS3_REG.WATCHDOG_ITThe WATCHDOG_IT interrupt bit is triggered from the watchdog (periodic or interrupt mode).5Ordering InformationTable 2.Ordering InformationPART NUMBER ORDERING INFORMATIONPROCESSOR TPS659114TPS659114A2ZRC/RFreescale i.MX6Revision History 8SWCU181C–January 2016–Revised September 2016Submit Documentation FeedbackCopyright ©2016,Texas Instruments IncorporatedRevision HistoryRevision HistoryChanges from B Revision (August 2016)to C Revision Page •Changed document title from TPS659114User's Guide :to TPS659114for Freescale i.MX6Dual/Quad User's Guide..1Changes from A Revision (January 2016)to B Revision Page •Changed VMBHI_IT_MSK Bit OPTION SELECTED in Table 1 (4)Changes from Original (January 2016)to A Revision Page •Updated Figure 1 (2)IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,enhancements,improvements and other changes to its semiconductor products and services per JESD46,latest issue,and to discontinue any product or service per JESD48,latest issue.Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All semiconductor products(also referred to herein as“components”)are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its components to the specifications applicable at the time of sale,in accordance with the warranty in TI’s terms and conditions of sale of semiconductor products.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by applicable law,testing of all parameters of each component is not necessarily performed.TI assumes no liability for applications assistance or the design of Buyers’products.Buyers are responsible for their products and applications using TI components.To minimize the risks associated with Buyers’products and applications,Buyers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any patent right,copyright,mask work right,or other intellectual property right relating to any combination,machine,or process in which TI components or services are rmation published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Buyer acknowledges and agrees that it is solely responsible for compliance with all legal,regulatory and safety-related requirements concerning its products,and any use of TI components in its applications,notwithstanding any applications-related information or support that may be provided by TI.Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures,monitor failures and their consequences,lessen the likelihood of failures that might cause harm and take appropriate remedial actions.Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.In some cases,TI components may be promoted specifically to facilitate safety-related applications.With such components,TI’s goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements.Nonetheless,such components are subject to these terms.No TI components are authorized for use in FDA Class III(or similar life-critical medical equipment)unless authorized officers of the parties have executed a special agreement specifically governing such use.Only those TI components which TI has specifically designated as military grade or“enhanced plastic”are designed and intended for use in military/aerospace applications or environments.Buyer acknowledges and agrees that any military or aerospace use of TI components which have not been so designated is solely at the Buyer's risk,and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.TI has specifically designated certain components as meeting ISO/TS16949requirements,mainly for automotive use.In any case of use of non-designated products,TI will not be responsible for any failure to meet ISO/TS16949.Products ApplicationsAudio /audio Automotive and Transportation /automotiveAmplifiers Communications and Telecom /communicationsData Converters Computers and Peripherals /computersDLP®Products Consumer Electronics /consumer-appsDSP Energy and Lighting /energyClocks and Timers /clocks Industrial /industrialInterface Medical /medicalLogic Security /securityPower Mgmt Space,Avionics and Defense /space-avionics-defense Microcontrollers Video and Imaging /videoRFID OMAP Applications Processors /omap TI E2E Community Wireless Connectivity /wirelessconnectivityMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2016,Texas Instruments Incorporated。

DM8127平台入门教程

所以本人这里先把DM8127板子的启动过程先描述一下,让大家从硬件上和软件运行角度了解整个DM8127的工作过程,然后再去学习IPNC_RDK里面的开发包架构以及开发包的移植工作。

启动过程:上电——→DM8127内部片上的ROM CODE运行——→ROM CODE读取SYSBOOT PINS电平状态决定是从NAND FLASH BOOT还是UART0串口BOOT或者SD卡BOOT或者PCIe BOOT或者EMAC BOOT或者XIP BOOT ——→读取ubootmin并运行ubootmin(ubootmin取得ARM控制权)——→读取u-boot并运行u-boot(u-boot取得ARM控制权)——→读取linux 内核BIN并运行linux 内核(linux-2.6.37取得ARM控制权一直到板子复位或者断电)——→挂载文件系统(可以是存放在NAND FLASH的ubifs,squashfs,或者NFS)——→运行文件系统的脚本——→运行IPNC_RDK整个DEMO应用程序system_server,boa和live555等,启动VPSS M3核,启动VIDEO M3核,启动浮点DSP C674X核。

整个过程可以通过上图直观了解。

一、运行ubootmin一开始上电,DM8127主芯片内部有ROM CODE,这个是使用片上的内部RAM运行的,还没用片外的DDR3,如果新做的板子什么程序也没有,只要T PS659113电源管理芯片的供电时序正常,主晶振正常工作,那么ROM CODE 就会正常运行,先读取SYSBOOT PINS(就是BOOT MODE那几个外接上拉下拉电阻的管脚状态),如果对应的那些NAND FLASH或者SD 卡或者PCIe 等接口没有程序,那么DM8127这时会通过UART0 不断输出C C C C C C ……..的打印字符,试图通过UART0进行通讯下载UBOOT-OPTI BIN文件(这个UBOOT-OPTI后面介绍UBOOT移植的时候再分析)。

MEMORY存储芯片TPS65130RGER中文规格书

V V POSV NEGL1 TPS6513x Positive and Negative Output DC-DC Converter1Features• 2.7-V to 5.5-V Input Voltage Range•Dual Adjustable Output Voltages Up to 15V and Down to –15V•800-mA Typical Switch Current Limit at Boost and Inverter Main Switches at TPS65130•2-A Typical Switch Current Limit at Boost and Inverter Main Switches at TPS65131•Up to 89%Efficiency at Positive Output Voltage Rail•Up to 81%Efficiency at Negative Output Voltage Rail•Power-Save Mode for High Efficiency at Low Load Currents•Independent Enable Inputs for Power-Up and Power-Down Sequencing•Control Output for External PFET to Support Completely Disconnecting the Battery•Minimum 1.25-MHz Fixed Frequency PWM Operation•Thermal Shutdown•Overvoltage Protection on Both Outputs •1-µA Shutdown Current•Small 4-mm x 4-mm VQFN-24Package (RGE)2Applications•LCD and OLED Displays •Industrial Applications •Data Acquisition •Audio•General-Purpose Split-Rail Supplies3DescriptionThe TPS6513x is dual-output DC-DC converter generating a positive output voltage up to 15V and a negative output voltage down to –15V with output currents in a 200-mA range in typical applications,depending on input voltage to output voltage ratio.With a total efficiency up to 85%,the device is ideal for portable battery-powered equipment.The input voltage range of 2.7V to 5.5V allows the devices to be powered from batteries or from fixed 3.3-V or 5-V supplies.The TPS6513x comes in a small 4-mm ×4-mm VQFN-24package.Together with a minimum switching frequency of 1.25MHz,the device enables designing small power supply applications because it requires only a few small external components.The converter operates with a fixed frequency PWM control topology and,if power-save mode is enabled,it uses a pulse-skipping mode at light-load currents.It operates with only 500-µA device quiescent current.Independent enable pins allow power-up and power-down sequencing for both outputs.The device has an internal current limit overvoltage protection and a thermal shutdown for highest reliability under fault conditions.Device Information (1)PART NUMBER PACKAGE BODY SIZE (NOM)TPS65130VQFN (24) 4.00mm ×4.00mm TPS65131VQFN (24)4.00mm ×4.00mm(1)For all available packages,see the orderable addendum atthe end of the data sheet.Typical Application SchematicTPS65130,TPS65131SLVS493D–MARCH2004–REVISED JANUARY2016Typical Application(continued)8.2.1Design RequirementsFigure8uses the following parameters:Table1.Design ParametersDESIGN PARAMETER EXAMPLE VALUEInput voltage range 2.7V to5.5VBoost converter output voltage,V POS R1=1MΩR2=130kΩC9=6.8pF10.5VInverting converter output voltage,V NEGR3=1MΩR4=121.2kΩC10=7.5pF–10VTable2.List of ComponentsREFERENCE SETUP VALUE,DESCRIPTIONC1,C2—4.7µF,ceramic,6.3V,X5RC30.1µF,ceramic,10V,X5RC4,C54x4.7µF,ceramic,25V,X7R C610nF,ceramic,16V,X7RC7 4.7nF,50V,C0GC8220nF,ceramic,6.3V,X5RR1V POS=10.5V1MΩV POS=15V975kΩR2V POS=10.5V130kΩV POS=15V85.8kΩR3V NEG=–10V1MΩV NEG=–15V 1.3MΩR4V NEG=–10V121.2kΩV NEG=–15V104.8kΩR7—100ΩD1,D2Schottky,1A,20V,Onsemi MBRM120L1,L2Wurth Elektronik7447789004(TPS65130), EPCOS B82462-G4472(TPS65131)Q1MOSFET,P-channel,12V,4A,Vishay Si2323DS8.2.2Detailed Design ProcedureThe TPS6513x DC-DC converter is intended for systems typically powered by a single-cell Li-ion or Li-polymer battery with a terminal voltage from2.7V up to4.2V.Because the recommended input voltage goes up to5.5V, the device is also suitable for3-cell alkaline,NiCd,or NiMH batteries,as well as any regulated supply voltages from2.7V to5.5V.It provides two independent output voltage rails which are programmed as follows.8.2.2.1Programming the Output Voltage8.2.2.1.1Boost ConverterThe output voltage of the TPS6513x boost converter stage can be adjusted with an external resistor divider connected to the FBP pin.The typical value of the voltage at the FBP pin is the reference voltage,which is1.213 V.The maximum recommended output voltage at the boost converter is15V.To achieve appropriate accuracy, the current through the feedback divider should be about100times greater than the current into the FBP pin. Typical current into the FBP pin is0.05µA,and the voltage across R2is1.213V.Based on those values,the recommended value for R2should be lower than200kΩto set the divider current at5µA or greater.TPS65130,TPS65131SLVS493D–MARCH2004–REVISED JANUARY2016Product Folder Links:TPS65130TPS65131(ESR N)NEG (ESR C5)V I R 'u (ESR P)POS (ESR C4)V I R 'uNEG NEGNEG NEG I I V C5minf V V V u u 'uPOSPOS I POS POS I V V C4min f V V u u 'u TPS65130,TPS65131SLVS493D –MARCH 2004–REVISED JANUARY 2016Product Folder Links: TPS65130 TPS65131In typical applications,the recommendation is to choose a 4.7-μH inductor.The device is optimized to work with inductance values from 3.3μH to 6.8μH.Nevertheless,operation with greater inductance values may be possible in some applications.Perform detailed stability analysis in this case.Be aware of the possibility that load transients and losses in the circuit can lead to higher currents than estimated in Equation 3and Equation 4.Also,the losses caused by magnetic hysteresis and conductor resistance are a major parameter for total circuit efficiency.Table 3shows inductors from different suppliers used with the TPS6513x converter:Table 3.List of InductorsVENDORINDUCTOR SERIES EPCOS B8246284-G4Wurth Elektronik 7447789XXX 744031XXX TDKVLF3010VLF4012Cooper Electronics TechnologiesSD128.2.2.3Capacitor Selection8.2.2.3.1Input CapacitorAs a recommendation,choose an input capacitors of at least 4.7μF for the input of the boost converter (INP)and accordingly for the input of the inverting converter (INN).This improves transient behavior of the regulators and EMI behavior of the total power-supply circuit.Choose a ceramic capacitor or a tantalum capacitor.For the use of a tantalum capacitor,an additional,smaller ceramic capacitor (100nF)in parallel is required.Place the input capacitor(s)close to the input pins..8.2.2.3.2Output CapacitorsOne of the major parameters necessary to define the capacitance value of the output capacitor is the maximum allowed output voltage ripple of the converter.This ripple is determined by two parameters of the capacitor,the capacitance and the ESR.It is possible to calculate the minimum capacitance needed for the defined ripple,supposing that the ESR is e Equation 7for the boost converter output capacitor (C4min)and Equation 8for the inverting converter output capacitor (C5min).(7)(8)The parameter f is the switching frequency.ΔV POS and ΔV NEG are the maximum allowed ripple voltages for each converter.Choosing a ripple voltage in the range of 10mV requires a minimum capacitance of 12μF.The total ripple is larger due to the ESR of the output e Equation 9for he boost converter and Equation 10for the inverting converter to calculate this additional ripple component.(9)(10)In this example,an additional ripple of 2mV is the result of using a typical ceramic capacitor with an ESR in the 10-m Ωrange.The total ripple is the sum of the ripple caused by the capacitance and the ripple caused by the ESR of the capacitor.In this example,the total ripple is 10mV.Load transients can create additional ripple.When the load current increases rapidly,the output capacitor must provide the additional current until the inductor current increases by the control loop which sets a higher ON-time (duty cycle)of the main switch.The higher duty cycle results in longer inductor charging periods.The inductance itself also limits the rate of increase of the inductor current.When the load current decreases rapidly,the output capacitor must store the excess energy (stored in the inductor)until the regulator has decreased the inductor current by reducing the duty cycle.TI recommends using greater capacitance values,as the foregoing calculations show.7.5 V C10R36.8 V C9R1TPS65130,TPS65131SLVS493D –MARCH 2004–REVISED JANUARY 2016Product Folder Links:TPS65130TPS651318.2.2.4Rectifier Diode SelectionBoth converters (the boost and inverting converter)require rectifier diodes,D1and D2.As a recommendation,to reduce losses,use Schottky diodes.The forward current rating needed is equal to the maximum output current.Consider that the maximum currents,I POS max and I NEG max,might differ for V POS and V NEG when choosing the diodes.8.2.2.5External PMOS SelectionDuring shutdown,when connected to a power supply,a path from the power supply to the positive output conducts through the inductor and an external diode.Optionally,to fully disconnect the positive output V POS during shutdown,add an external PMOS (Q1).The BSW pin controls the gate of the PMOS.When choosing a proper PMOS,the V GS and V GD voltage ratings must cover the input voltage range,the drain current rating must not be lower than the maximum input current flowing into the application,and conditions of the PMOS operating area must fit.If there is no intention to use an external PMOS,leave the BSW pin floating.8.2.2.6Stabilizing the Control Loop8.2.2.6.1Feedforward CapacitorAs a recommendation,to speed up the control loop,place feedforward capacitors in the feedback divider,parallel to R1(boost converter)and R3(inverting converter).Equation 11shows how to calculate the appropriate value for the boost converter,and Equation 12for the inverting converter.(11)(12)To avoid coupling noise into the control loop from the feedforward capacitors,the feedforward effect can bebandwith-limited by adding a series resistor.Any value from 10k Ωto 100k Ωis suitable.The greater the resistance,the lower the noise coupled into the control loop system.8.2.2.6.2Compensation CapacitorsThe device features completely internally compensated control loops for both converters.The internal feedforward system has built-in error correction which requires external capacitors.As a recommendation,use a 10-nF capacitor at the CP pin of the boost converter and a 4.7-nF capacitor at the CN pin of the inverting converter.8.2.3Application Curves。

电源管理芯片TPS65910A3与开关按键控制器STM6601的嵌入式应用

应 用于便携式和手持系统 。

智 能 型开 关按 键控 制 器芯 片 S T M6 6 0 1 , 具备 更 简单 易用 的开机 、 关机 以及 解 冻/ 重 置功 能 , 可 避免 对终 端 产 品 造 成损

Abs t r ac t : A a ppl i c a t i on s o l ut i o n ba s e d o n i n t e l l i g e nt po we r ma na g e me nt c hi p TPS 65 91 0A 3 a nd i n t e l l i ge nt s wi t c h but t o n c ont r o l l )的 2 5 6 KB二 级 高 速 缓 存 。

1 T P S 6 5 9 1 0 A 3电 源 分 配 与 上 电 时 序

TP S 6 5 9 1 0 A3具 有 4路 DC—DC转 换 器 , 其 中 2路 高 效 DC—D C 降压 转 换 器 为 处理 器 提供 电 源 , 可通 过 德 州 仪

Bi n X i a n w e n, Ch e n We i , Wa n g S h o u f e n, Li n Qi n j i a n

( Hi — Ta r g e t S u r v e y I n s t r u me n t s C o mp a n y Lt d . ,Gu a n g z h o u 5 1 1 4 0 0, Ch i n a )

S TM 6 6 0 1 i s i n t r o d u c e d ,a n d a p p l i e d t o t h e e mb e d d e d s y s t e m t a k i n g TI AM 3 3 5 x p r o c e s s o r a s t h e c o r e . Th i s p a p e r p r e s e n t s t h e p o we r

一种低功耗频率稳定的CMOS环形振荡器设计

1引言

随着半导体行业发展,CMOS 工艺生产技术提 高,芯片面积越来越小。对芯片内部各模块的低功 耗、高稳定、高精度要求也越来越高[1]。振荡器模块作

. 24.微处理机源自2017 年被广泛应用于工业产品和学术设计中[3]。然而,COMS 环形振荡器在功耗和相位噪声及频率稳定性等方 面,仍需要更加深入的研究[4]。

2 传统环形振荡器介绍

环形振荡器由环路中若干振荡电路单元组成, 每个电路单元由有源器件构成。如果环形振荡器满 足“巴克豪森准则”将发生振荡,产生周期变化的电 压信号[5]。典型结构如图 1 所示。

第5期 2051期7 年 10 月

微处理机 MICROPROCESSORS

. . No. 5

Oct. ,2017

一种低功耗频率稳定的 CMOS 环形振荡器设计

张 可 1,代雪峰 2,张海涛 3

(1. 中国电子科技集团公司第四十七研究所,沈阳 110032;2. 东北大学理学院物理系,沈阳 110004; 3. 中国人民解放军 95979 部队,沈阳 110045)

摘 要:COMS 环形振荡器具有版图面积小,频率调谐范围大、线性度好等优点,可作为系统时钟

的关键部件,广泛应用于电子及通信系统中。对传统的环形振荡器及其频率稳定的改进方式进行介

绍,设计新的延时单元,搭建环形振荡器电路结构,实现了一种频率稳定的 CMOS 环形振荡器。该振

荡器电路结构简单,易于集成。通过 0.25滋m CMOS 工艺仿真对比分析,环形振荡器功耗降低了 40%,

汽车电路板上的TPS65917-Q1电源管理单元(PMU)为处理器1设备概述说明书

ProductFolderSample &BuyTechnical Documents Tools &SoftwareSupport &CommunityTPS65917-Q1SLVSD22–JULY 2015TPS65917-Q1Power Management Unit (PMU)for Processor1Device Overview1.1Features•Qualified for Automotive Applications•Five Low-Dropout (LDO)Linear Regulators:•AEC-Q100Qualified With the Following Results:–0.9-to 3.3-V Output Range in 50-mV steps –Device Temperature Grade 2:–40°C to +105°C –Two With 300-mA Capability and Bypass Mode Ambient Operating Temperature Range –One With 100-mA Capability and Capable of –Device HBM Classification Level 2Low-Noise Performance up to 50mA –Device CDM Classification Level C4B–Two Other LDOs With 200-mA Current Capability•System Voltage Range from 3.135V to 5.25V –Short-Circuit Protection•Low-Power Consumption •12-Bit Sigma-Delta General-Purpose ADC –20μA in Off Mode(GPADC)With 8Input Channels (2external)–90μA in Sleep Mode With Two SMPSs Active •Thermal Monitoring With High Temperature •Five Step-Down Switched-Mode Power Supply Warning and Thermal Shutdown (SMPS)Regulators:•Power Sequence Control:–0.7-to 3.3-V Output Range in 10-or 20-mV –Configurable Power-Up and Power-Down StepsSequences (OTP)–Two SMPS Regulators With 3.5-A Capability,–Configurable Sequences Between the SLEEP With the Ability to Combine into 7-A Output in and ACTIVE State Transition (OTP)Dual-Phase Configuration,With Differential Remote Sensing (Output and Ground)–Three Digital Output Signals that can be Included in the Startup Sequence –Three Other SMPS Regulators with 3-A,2-A,and 1.5-A Capabilities•Selectable Control Interface:–Dynamic Voltage Scaling (DVS)Control and –One SPI for Resource Configurations and DVS Output Current Measurement in 3.5-A and 3-A ControlSMPS Regulators–Two I 2C Interfaces.–Hardware and Software Controlled Eco-mode™•One Dedicated for DVS ControlSupplying up to 5mA •One General Purpose I 2C Interface for –Short-Circuit ProtectionResource Configuration and DVS Control–Power-Good Indication (Voltage and •OTP Bit-Integrity Error Detection With Options to Overcurrent Indication)Proceed or Hold Power-Up Sequence and –Internal Soft-Start for In-Rush Current Limitation RESET_OUT Release –Ability to Synchronize to External Clock between •Package Option:1.7MHz and2.7MHz–7-×7-mm 48-pin VQFN With 0.5-mm Pitch 1.2Applications•Automotive Infotainment •Automotive Advanced Driver Assistance System (ADAS)•Automotive Digital Cluster•Automotive Navigation Systems1.3DescriptionThe TPS65917-Q1device is an integrated PMIC with AEC-Q100qualification.The device provides 5configurable step-down converters with up to 3.5A of output current for memory,processor core,I/O,or preregulation of LDOs.These step-down converters can be synchronized to an external clock between 1.7MHz and 2.7MHz,or an internal fallback clock at 2.2MHz.Two of these configurable step-down converters can be combined together to allow up to 7A of output current.The device also contains 5LDO regulators for external use.These LDOs can be supplied from either the system supply or an external preregulated supply.An IMPORTANT NOTICE at the end of this data sheet addresses availability,warranty,changes,use in safety-critical applications,intellectual property matters and other important disclaimers.PRODUCTION DATA.TPS65917-Q1SLVSD22– The power-up and power-down controller is configurable and can support any power-up and power-down sequences(OTP based).As an additional safety feature,the OTP bit-integrity error-detection feature provides the option to stop the power-up sequence if an error is detected.The TPS65917-Q1device includes an internal32-kHz RC oscillator to sequence all resources during power up and power down.All LDOs and SMPS converters can be controlled by the SPI or I2C interface,or by power request signals.In addition,voltage scaling registers allow transition of the SMPS to different voltages by SPI,I2C,or roof-and-floor control.GPIO functionality is available and3GPIOs can be configured as part of the power-up sequence to control external resources.The fallback clock of the step-down converters can be output through the SYNCCLKOUT pin to provide synchronization clock to external resources.Power request signals enable power mode control for power optimization.The device includes a general-purpose sigma-delta analog-to-digital converter(ADC)with8channels(2with external access).The TPS65917-Q1device is available in a48-pin VQFN package with a0.5-mm pitch.Device Information(1)PART NUMBER PACKAGE BODY SIZE(NOM)TPS65917-Q1VQFN(48)7.00mm×7.00mm(1)For all available packages,see the orderable addendum at the end of the data sheet.2Device Overview Copyright©2015,Texas Instruments IncorporatedSubmit Documentation FeedbackProduct Folder Links:TPS65917-Q1TPS65917-Q1 SLVSD22–JULY20151.4Functional DiagramFigure1-1.Functional DiagramCopyright©2015,Texas Instruments Incorporated Device Overview3Submit Documentation FeedbackProduct Folder Links:TPS65917-Q1TPS65917-Q1SLVSD22– 2Device and Documentation Support2.1Documentation Support2.1.1Related DocumentationFor related documentation see the following:Guide to Using the GPADC in TPS65903x and TPS6591x Devices,SLIA0872.2Community ResourcesThe following links connect to TI community resources.Linked contents are provided"AS IS"by the respective contributors.They do not constitute TI specifications and do not necessarily reflect TI's views;see TI's Terms of Use.TI E2E™Online Community TI's Engineer-to-Engineer(E2E)Community.Created to foster collaboration among engineers.At ,you can ask questions,share knowledge,explore ideas and help solve problems with fellow engineers.Design Support TI's Design Support Quickly find helpful E2E forums along with design support tools and contact information for technical support.2.3TrademarksEco-mode,E2E are trademarks of Texas Instruments.All other trademarks are the property of their respective owners.2.4Electrostatic Discharge CautionThese devices have limited built-in ESD protection.The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.2.5GlossarySLYZ022—TI Glossary.This glossary lists and explains terms,acronyms,and definitions.3Mechanical,Packaging,and Orderable InformationThe following pages include mechanical,packaging,and orderable information.This information is the most current data available for the designated devices.This data is subject to change without notice and revision of this document.For browser-based versions of this data sheet,refer to the left-hand navigation.4Mechanical,Packaging,and Orderable Information Copyright©2015,Texas Instruments IncorporatedSubmit Documentation FeedbackProduct Folder Links:TPS65917-Q1IMPORTANT NOTICETexas Instruments Incorporated(TI)reserves the right to make corrections,enhancements,improvements and other changes to its semiconductor products and services per JESD46,latest issue,and to discontinue any product or service per JESD48,latest issue.Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.TI’s published terms of sale for semiconductor products(/sc/docs/stdterms.htm)apply to the sale of packaged integrated circuit products that TI has qualified and released to market.Additional terms may apply to the use or sale of other types of TI products and services.Reproduction of significant portions of TI information in TI data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.TI is not responsible or liable for such reproduced rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements. Buyers and others who are developing systems that incorporate TI products(collectively,“Designers”)understand and agree that Designers remain responsible for using their independent analysis,evaluation and judgment in designing their applications and that Designers have full and exclusive responsibility to assure the safety of Designers'applications and compliance of their applications(and of all TI products used in or for Designers’applications)with all applicable regulations,laws and other applicable requirements.Designer represents that,with respect to their applications,Designer has all the necessary expertise to create and implement safeguards that(1)anticipate dangerous consequences of failures,(2)monitor failures and their consequences,and(3)lessen the likelihood of failures that might cause harm and take appropriate actions.Designer agrees that prior to using or distributing any applications that include TI products,Designer will thoroughly test such applications and the functionality of such TI products as used in such applications.TI’s provision of technical,application or other design advice,quality characterization,reliability data or other services or information, including,but not limited to,reference designs and materials relating to evaluation modules,(collectively,“TI Resources”)are intended to assist designers who are developing applications that incorporate TI products;by downloading,accessing or using TI Resources in any way,Designer(individually or,if Designer is acting on behalf of a company,Designer’s company)agrees to use any particular TI Resource solely for this purpose and subject to the terms of this Notice.TI’s provision of TI Resources does not expand or otherwise alter TI’s applicable published warranties or warranty disclaimers for TI products,and no additional obligations or liabilities arise from TI providing such TI Resources.TI reserves the right to make corrections, enhancements,improvements and other changes to its TI Resources.TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.Designer is authorized to use,copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s)identified in such TI Resource.NO OTHER LICENSE,EXPRESS OR IMPLIED,BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT,AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN,including but not limited to any patent right,copyright,mask work right,or other intellectual property right relating to any combination,machine,or process in which TI products or services are rmation regarding or referencing third-party products or services does not constitute a license to use such products or services,or a warranty or endorsement e of TI Resources may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.TI RESOURCES ARE PROVIDED“AS IS”AND WITH ALL FAULTS.TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS,EXPRESS OR IMPLIED,REGARDING RESOURCES OR USE THEREOF,INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS,TITLE,ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY,FITNESS FOR A PARTICULAR PURPOSE,AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY DESIGNER AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE.IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT,SPECIAL,COLLATERAL,INDIRECT,PUNITIVE,INCIDENTAL,CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF,AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.Unless TI has explicitly designated an individual product as meeting the requirements of a particular industry standard(e.g.,ISO/TS16949 and ISO26262),TI is not responsible for any failure to meet such industry standard requirements.Where TI specifically promotes products as facilitating functional safety or as compliant with industry functional safety standards,such products are intended to help enable customers to design and create their own applications that meet applicable functional safety standards and ing products in an application does not by itself establish any safety features in the application.Designers must ensure compliance with safety-related requirements and standards applicable to their applications.Designer may not use any TI products in life-critical medical equipment unless authorized officers of the parties have executed a special contract specifically governing such use. Life-critical medical equipment is medical equipment where failure of such equipment would cause serious bodily injury or death(e.g.,life support,pacemakers,defibrillators,heart pumps,neurostimulators,and implantables).Such equipment includes,without limitation,all medical devices identified by the U.S.Food and Drug Administration as Class III devices and equivalent classifications outside the U.S.TI may expressly designate certain products as completing a particular qualification(e.g.,Q100,Military Grade,or Enhanced Product). Designers agree that it has the necessary expertise to select the product with the appropriate qualification designation for their applications and that proper product selection is at Designers’own risk.Designers are solely responsible for compliance with all legal and regulatory requirements in connection with such selection.Designer will fully indemnify TI and its representatives against any damages,costs,losses,and/or liabilities arising out of Designer’s non-compliance with the terms and provisions of this Notice.Mailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2017,Texas Instruments Incorporated。

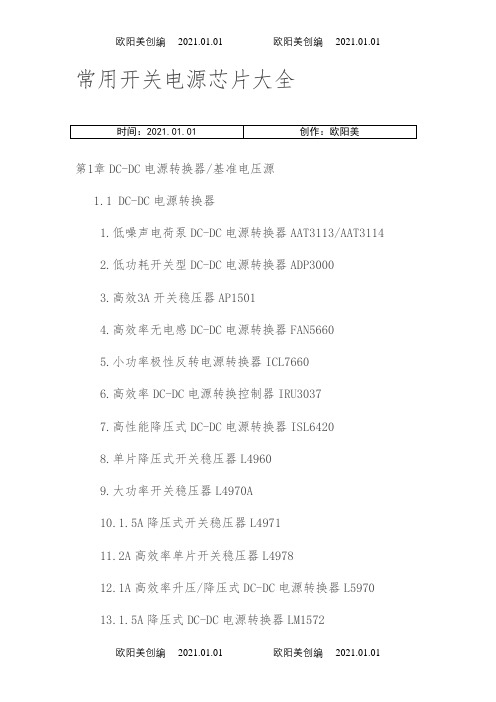

常用开关电源芯片大全之欧阳美创编