STA328中文资料

MEMORY存储芯片ATMEGA328P-AU中文规格书

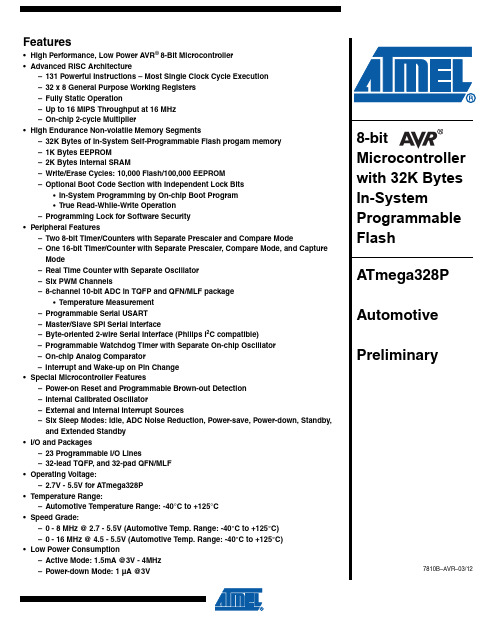

Features●High Performance, Low Power AVR ® 8-Bit Microcontroller Family ●Advanced RISC Architecture 131 Powerful Instructions – Most Single Clock Cycle Execution 32 x 8 General Purpose Working Registers Fully Static OperationUp to 20 MIPS Throughput at 20MHz On-chip 2-cycle Multiplier●High Endurance Non-volatile Memory Segments 4/8/16/32KBytes of In-System Self-Programmable Flash program memory 256/512/512/1KBytes EEPROM 512/1K/1K/2KBytes Internal SRAMWrite/Erase Cycles: 10,000 Flash/100,000 EEPROM Data retention: 20 years at 85°C/100 years at 25°C (1)Optional Boot Code Section with Independent Lock Bits●In-System Programming by On-chip Boot Program ●True Read-While-Write OperationProgramming Lock for Software Security●QTouch ® library support Capacitive touch buttons, sliders and wheels QTouch and QMatrix™ acquisition Up to 64 sense channels●Peripheral Features Two 8-bit Timer/Counters with Separate Prescaler and Compare ModeOne 16-bit Timer/Counter with Separate Prescaler, Compare Mode, and Capture ModemegaA VR ® Data SheetIntroductionThe ATmega48A/PA/88A/PA/168A/PA/328/P is a low power, CMOS 8-bit microcontrollers based on the AVR ® enhanced RISC architecture. By executing instructions in a single clock cycle, the devices achieve CPU throughput approaching one million instructions per second (MIPS) per megahertz, allowing the sys-tem designer to optimize power consumption versus processing speed.2.OverviewThe ATmega48A/PA/88A/PA/168A/PA/328/P is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, theATmega48A/PA/88A/PA/168A/PA/328/P achieves throughputs approaching 1 MIPS per MHz allowing thesystem designer to optimize power consumption versus processing speed.2.1Block DiagramFigure 2-1.Block DiagramThe AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.The ATmega48A/PA/88A/PA/168A/PA/328/P provides the following features: 4K/8Kbytes of In-SystemProgrammable Flash with Read-While-Write capabilities, 256/512/512/1Kbytes EEPROM, 512/1K/1K/2Kbytes SRAM, 23general purpose I/O lines, 32 general purpose working registers, three flexible Timer/Counters with compare modes, internal and external interrupts, a serial programmable USART, a byte-oriented 2-wire Serial Interface, an SPI serial port, a 6-channel 10-bit ADC (8 channels in TQFP and VQFN packages), aprogrammable Watchdog Timer with internal Oscillator, and five software selectable power saving modes. The Idle mode stops the CPU while allowing the SRAM, Timer/Counters, USART, 2-wire Serial Interface, SPI port, and interrupt system to continue functioning. The Power-down mode saves the register contents but freezes the Oscillator, disabling all other chip functions until the next interrupt or hardware reset. In Power-save mode, the asynchronous timer continues to run, allowing the user to maintain a timer base while the rest of the device is sleeping. The ADC Noise Reduction mode stops the CPU and all I/O modules except asynchronous timer and ADC, to minimize switching noise during ADC conversions. In Standby mode, the crystal/resonator Oscillator is running while the rest of the device is sleeping. This allows very fast start-up combined with low powerconsumption.Microchip offers the QTouch library for embedding capacitive touch buttons, sliders and wheels functionality into AVR® microcontrollers. The patented charge-transfer signal acquisition offers robust sensing and includes fully debounced reporting of touch keys and includes Adjacent Key Suppression™ (AKS™) technology forunambiguous detection of key events. The easy-to-use QTouch Suite toolchain allows you to explore, develop and debug your own touch applications.The device is manufactured using Microchip’s high density non-volatile memory technology. The On-chip ISP Flash allows the program memory to be reprogrammed In-System through an SPI serial interface, by aconventional non-volatile memory programmer, or by an On-chip Boot program running on the AVR core. The Boot program can use any interface to download the application program in the Application Flash memory.Software in the Boot Flash section will continue to run while the Application Flash section is updated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash ona monolithic chip, the ATmega48A/PA/88A/PA/168A/PA/328/P is a powerful microcontroller that provides ahighly flexible and cost effective solution to many embedded control applications.The ATmega48A/PA/88A/PA/168A/PA/328/P AVR is supported with a full suite of program and systemdevelopment tools including: C Compilers, Macro Assemblers, Program Debugger/Simulators, In-CircuitEmulators, and Evaluation kits.2.2Comparison Between ProcessorsThe ATmega48A/PA/88A/PA/168A/PA/328/P differ only in memory sizes, boot loader support, and interrupt vector sizes. Table 2-1 summarizes the different memory and interrupt vector sizes for the devices.Table 2-1.Memory Size SummaryATmega48A4KBytes256Bytes512Bytes 1 instruction word/vectorATmega48PA4KBytes256Bytes512Bytes 1 instruction word/vectorATmega88A8KBytes512Bytes1KBytes 1 instruction word/vectorATmega88PA8KBytes512Bytes1KBytes 1 instruction word/vectorATmega168A16KBytes512Bytes1KBytes 2 instruction words/vectorATmega168PA16KBytes512Bytes1KBytes 2 instruction words/vectorATmega32832KBytes1KBytes2KBytes 2 instruction words/vectorATmega328P32KBytes1KBytes2KBytes 2 instruction words/vector7.AVR CPU Core7.1OverviewThis section discusses the AVR core architecture in general. The main function of the CPU core is to ensure correct program execution. The CPU must therefore be able to access memories, perform calculations, control peripherals, and handle interrupts.Figure 7-1.Block Diagram of the AVR ArchitectureIn order to maximize performance and parallelism, the AVR uses a Harvard architecture – with separatememories and buses for program and data. Instructions in the program memory are executed with a single level pipelining. While one instruction is being executed, the next instruction is pre-fetched from the program memory.This concept enables instructions to be executed in every clock cycle. The program memory is In-SystemReprogrammable Flash memory.The fast-access Register File contains 32 x 8-bit general purpose working registers with a single clock cycle access time. This allows single-cycle Arithmetic Logic Unit (ALU) operation. In a typical ALU operation, two。

TMS320C28x系列DSP芯片结构及引脚功能

第1章芯片结构及性能概述TMS320C2000系列是美国TI公司推出的最佳测控应用的定点DSP芯片,其主流产品分为四个系列:C20x、C24x、C27x和C28x。

C20x可用于通信设备、数字相机、嵌入式家电设备等;C24x主要用于数字马达控制、电机控制、工业自动化、电力转换系统等。

近年来,TI公司又推出了具有更高性能的改进型C27x和C28x系列芯片,进一步增强了芯片的接口能力和嵌入功能,从而拓宽了数字信号处理器的应用领域。

TMS320C28x系列是TI公司最新推出的DSP芯片,是目前国际市场上最先进、功能最强大的32位定点DSP芯片。

它既具有数字信号处理能力,又具有强大的事件管理能力和嵌入式控制功能,特别适用于有大批量数据处理的测控场合,如工业自动化控制、电力电子技术应用、智能化仪器仪表及电机、马达伺服控制系统等。

本章将介绍TMS320C28x系列芯片的结构、性能及特点,并给出该系列芯片的引脚分布及引脚功能。

1.1 TMS320C28x系列芯片的结构及性能C28x系列的主要片种为TMS320F2810和TMS320F2812。

两种芯片的差别是:F2812内含128K×16位的片内Flash存储器,有外部存储器接口,而F2810仅有64K×16位的片内Flash存储器,且无外部存储器接口。

其硬件特征如表1-1所示。

表1-1 硬件特征请预览后下载!注:‡“S”是温度选择(-40℃ ~ +125℃)的特征化数据,仅对TMS是适用的。

‡‡产品预览(PP):在开发阶段的形成和设计中与产品有关的信息,特征数据和其他规格是设计的目标。

TI保留了正确的东西,更换或者终止了一些没有注意到的产品。

高级信息(AI):在开发阶段的取样和试制中与新产品有关的信息,特征数据和其他规格用以改变那些没有注意到的东西。

产品数据(PD):是当前公布的数据信息,产品遵守TI的每项标准保修规格,但产品加工不包括对所有参数的测试。

SiteMaster S331D S332D 传输线和天线分析仪 说明书

Site Master 是无线运营、承包以及安装商的传输线天溃线Snap-in Field 可替代的电池位置RS-232接口通过串口线将仪表或计算机存储的数据分别下载到计算机或仪表中,以便进一步分析。

也可以通过它进行自动控制和收集野外数据。

高分辨率大屏幕显示标准 VGA (640x480) 或彩色STN(可选640x480)对比度可调和背景灯能力,使得在各种光线条件下都很容易实现清晰可见。

坚固的外壳设计坚固、轻巧并高度紧凑的外壳,非常适合手持操作和环境恶劣的野外环境。

键盘特殊的橡胶膜设计能在潮湿和干旱的环境中使用。

功能键四个专用的功能键简化了测量任务。

外部直流电源接口多用户界面多语言界面:中文、英文、法文、德文、日文、西班牙文。

存储和调用显示多达200存储空间。

图文数据标记和自动时间/日期标签极大地简化了数据管理。

限制线可对测量设置简单通过/失败限制线或高、低标记线。

标记6个标记使得更多测量变得方便。

存储和调用设置设置快速可重复的测量S332D 型号 - 20S331D 型号 - 25T1/E1接收/发射接口(S331D 带选件50 )外部触发及参考输入 传输及天溃线分析接口频谱仪和功率计接口软键直接的软键和用户界面。

节约成本并且提高了质量无线市场激烈竞争要求运营商降低每个基站的维护开销。

Site Master的频域反射计(FDR)技术,使得您使用Site Master在重大故障发生前,就可以发现细小的、难于确认的问题,打破了传统的故障之后再修理的维护方法。

60-80%的基站典型故障都是由于有问题的电缆、连接头和天线引起的。

当电缆/天线被潮化或被损坏或放置不当,Site Master 能够及时地发现问题。

天线劣化将减少蜂窝覆盖甚至导致掉话。

Site Master 能够数秒钟之内在地面就能精确定位天线故障而不用爬到塔上去了。

密封条安装得不好的话将腐蚀连接头,如果没有被发现的话会逐渐损坏昂贵的同轴电缆。

328328甲全固态机载相控阵雷达

(内部资料)名称:328/328甲全固态机载相控阵雷达体制:全固态有源阵、单脉冲、脉冲压缩波段:X研制单位:中国科学院电子研究所、长风机器厂、航天部二院二十五所、上海电子物理研究所、中国雷华电子研究所等多家科研机构研制时间:1993年开始,1999年完成第一阶段计划:328全固态机载相控阵雷达研制目的:研究全固态机载有源相控阵雷达现状:2002年9月已发展到第二阶段:可装备试用阶段:328甲全固态机载相控阵雷达技术特点:328甲是我国多家科研部门为空军研制的第一部全固态有源相控阵雷达。

它的主要技术成果是:射频功率放大器、中放、混频器、倍频器、移相器以及开关等器件的集成化和批生产能力。

328甲全固态机载相控阵雷达系统具有地形跟随、地形回避、地面测绘和空地测距等功能。

该系统除天线阵列和共用电源外,还有六个密封部件。

天线阵列结构含数百个插入式射频微型组件,射频和直流综合装置以及冷却装置。

各微型组件安装在间隔为0.517λ的方形格栅上。

射频微型组件是一发射机/接收机复合单元,每一组件均能发射和接收9600兆赫能量。

发射机激励和本振功率从信号发生器通过公用馈电系统均匀地分配到每个组件。

信号发生器输出的S波段信号在组件中倍频到9600兆赫,2235兆赫本振信号在组件中倍频到9100兆赫,并与9600兆赫信号差频到510兆赫中频。

328甲全固态机载相控阵雷达系统采用脉冲压缩技术以得到足够的灵敏度的良好的分辨力。

发射机激励信号可以工作于脉冲压缩方式,也可将脉冲压缩发射与非脉冲压缩发射组合应用。

这就使得在地形回避、地形测绘和空地测距时,不论是近距离或远距离都有良好的分辨力。

微型组件的510兆赫中频输出按指定的加权分布在接收综合装置中组合起来,以获得良好的旁瓣特性。

微型组件共有六个单独的电路基片,中频放大器和调制器是分开制作的,分别结合在混频器/收发转换开关和脉冲功率放大器基片上。

各电路的互连采用金丝网焊接在微带线上来实现。

STA328 完美数字音频功放集成块

May 2008 Rev 41/57STA3282.1-channel high-efficiency digital audio systemFeatures!Wide supply voltage range (10 V - 36V)!Three power output configurations –2x 40W + 1x 80W –2x 80W –1x 160W !PowerSO-36 package ! 2.1 channels of 24-bit DDX ®!100-dB SNR and dynamic range !32kHz to 192kHz input sample rates !Digital gain/attenuation +48dB to -80dB in 0.5-dB steps!Four 28-bit user programmable biquads (EQ) per channel !I 2C control!2-channel I 2S input data interface!Individual channel and master gain/attenuation !Individual channel and master soft/hard mute !Individual channel volume and EQ bypass !Bass/treble tone control!Dual independent programmable limiters/compressors!AutoModes–32 preset EQ curves–15 preset crossover settings –Auto volume controlled loudness – 3 preset volume curves– 2 preset anti-clipping modes –Preset night-time listening mode –Preset TV AGC!Input and output channel mapping !AM noise-reduction and PWM frequency-shifting modes!Software volume update and muting !Auto zero detect and invalid input detect muting!Selectable DDX ® ternary or binary PWM output + variable PWM speeds !Selectable de-emphasis!Post-EQ user programmable mix with default 2.1 bass-management settings!Variable max power correction for lower full-power THD!Four output routing configurations !Selectable clock input ratio!96kHz internal processing sample rate, 24 to 28-bit precision!Video application supports 576 * fs input mode.Table 1.Device summaryOrder codePackagePackagingST A328PowerSO-36Tube ST A32813TRPowerSO-36Tape and reelContents STA328Contents1Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51.1Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51.2EQ processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61.3Output configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61.4Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72Pin out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82.1Package pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82.2Pin list . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82.3Pin description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93Electrical specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113.1General interface specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113.2DC electrical specifications (3.3V buffers) . . . . . . . . . . . . . . . . . . . . . . . . 123.3Power electrical specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 4Electrical characteristics curves . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145I2C bus specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165.1Communication protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165.2Device addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165.3Write operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175.4Read operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176Register description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196.1Configuration register A (addr 0x00) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 206.2Configuration register B (addr 0x01) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 236.3Configuration register C (addr 0x02) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 266.3.1DDX® power output mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 266.3.2DDX® variable compensating pulse size . . . . . . . . . . . . . . . . . . . . . . . . 266.4Configuration register D (addr 0x03) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 276.5Configuration register E (addr 0x04) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29 2/57STA328Contents6.6Configuration register F (addr 0x05) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 316.7Volume control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 336.7.1Master controls . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 336.7.2Channel controls . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 336.7.3Volume description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 336.8AutoMode registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 356.8.1AutoModes EQ, volume, GC (addr 0x0B) . . . . . . . . . . . . . . . . . . . . . . . 356.8.2AutoMode AM/pre-scale/bass management scale (addr 0x0C) . . . . . . 366.8.3Preset EQ settings (addr 0x0D) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 376.9Channel configuration registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 386.9.1Channel 1 configuration (addr 0x0E) . . . . . . . . . . . . . . . . . . . . . . . . . . . 386.9.2Channel 2 configuration (addr 0x0F) . . . . . . . . . . . . . . . . . . . . . . . . . . . 386.9.3Channel 3 configuration (addr 0x10) . . . . . . . . . . . . . . . . . . . . . . . . . . . 386.10Tone control (addr 0x11) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 406.11Dynamics control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 416.11.1Limiter 1 attack/release threshold (addr 0x12) . . . . . . . . . . . . . . . . . . . . 416.11.2Limiter 1 attack/release threshold (addr 0x13) . . . . . . . . . . . . . . . . . . . . 416.11.3Limiter 2 attack/release rate (addr 0x14) . . . . . . . . . . . . . . . . . . . . . . . . 416.11.4Limiter 2 attack/release threshold (addr 0x15) . . . . . . . . . . . . . . . . . . . . 416.11.5Dynamics control description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 416.11.6Anti-clipping mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 436.11.7Dynamic range compression mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . 447User programmable processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 457.1EQ - biquad equation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 457.2Pre-scale . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 457.3Post-scale . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 457.4Mix/bass management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 467.5Calculating 24-bit signed fractional numbers from a dB value . . . . . . . . . 477.6User defined coefficient RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 477.6.1Coefficient address register 1 (addr 0x16) . . . . . . . . . . . . . . . . . . . . . . . 477.6.2Coefficient b1data register bits 23:16 (addr 0x17) . . . . . . . . . . . . . . . . . 477.6.3Coefficient b1data register bits 15:8 (addr 0x18) . . . . . . . . . . . . . . . . . . 477.6.4Coefficient b1data register bits 7:0 (addr 0x19) . . . . . . . . . . . . . . . . . . . 477.6.5Coefficient b2 data register bits 23:16 (addr 0x1A) . . . . . . . . . . . . . . . . 477.6.6Coefficient b2 data register bits 15:8 (addr 0x1B) . . . . . . . . . . . . . . . . . 483/57Contents STA3284/577.6.7Coefficient b2 data register bits 7:0 (addr 0x1C) . . . . . . . . . . . . . . . . . . 487.6.8Coefficient a1 data register bits 23:16 (addr 0x1D) . . . . . . . . . . . . . . . . 487.6.9Coefficient a1 data register bits 15:8 (addr 0x1E) . . . . . . . . . . . . . . . . . 487.6.10Coefficient a1 data register bits 7:0 (addr 0x1F) . . . . . . . . . . . . . . . . . . 487.6.11Coefficient a2 data register bits 23:16 (addr 0x20) . . . . . . . . . . . . . . . . 487.6.12Coefficient a2 data register bits 15:8 (addr 0x21) . . . . . . . . . . . . . . . . . 487.6.13Coefficient a2 data register bits 7:0 (addr 0x22) . . . . . . . . . . . . . . . . . . 487.6.14Coefficient b0 data register bits 23:16 (addr 0x23) . . . . . . . . . . . . . . . . 497.6.15Coefficient b0 data register bits 15:8 (addr 0x24) . . . . . . . . . . . . . . . . . 497.6.16Coefficient b0 data register bits 7:0 (addr 0x25) . . . . . . . . . . . . . . . . . . 497.6.17Coefficient write control register (addr 0x26) . . . . . . . . . . . . . . . . . . . . . 49 7.7Reading a coefficient from RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50 7.8Reading a set of coefficients from RAM . . . . . . . . . . . . . . . . . . . . . . . . . . 50 7.9Writing a single coefficient to RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50 7.10Writing a set of coefficients to RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51 7.11Variable max power correction (addr 0x27, 0x28) . . . . . . . . . . . . . . . . . . 53 7.12Fault detect recovery (addr 0x2B, 0x2C) . . . . . . . . . . . . . . . . . . . . . . . . . 538Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54 9Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56STA328Description 1 Description1.1 OverviewThe STA328 comprises digital audio processing, digital amplifier control and DDX® poweroutput stage to create a high-power single-chip DDX® solution for high-quality,high-efficiency, all digital amplification.The STA328 power section consists of four independent half-bridges. These can beconfigured via digital control to operate in different modes. 2.1 channels can be provided bytwo half-bridges and a single full-bridge to give up to 2x40W plus 1x80 W of poweroutput. Two channels can be provided by two full-bridges to give up to 2x80W of power.The IC can also be configured as a single parallel full-bridge capable of high-currentoperation and 1x160W output.Also provided in the ST A328 is a full assortment of digital processing features. This includesup to four programmable 28-bit biquads (EQ) per channel and bass/treble tone control.AutoModes enable a time-to-market advantage by substantially reducing the amount ofsoftware development needed for certain functions. This includes auto volume loudness,preset volume curves, preset EQ settings. New advanced AM radio-interference reductionmodes.The serial audio data input interface accepts all possible formats, including the popular I2Sformat.Three channels of DDX® processing are provided. This high-quality conversion from PCMaudio to patented DDX® 3-state PWM switching provides over 100dB of SNR and dynamicrange.5/57Description STA3286/571.2 EQ processingTwo channels of input data (re-sampled if necessary) at 96kHz are provided to the EQprocessing block. In this block, up to four user-defined biquads can be applied to each of the two channels.Pre-scaling, DC-blocking, high-pass, de-emphasis, bass, and tone control filters can also be applied based on various configuration parameter settings.The entire EQ block can be bypassed for all channels simultaneously by setting the DSPB bit to 1. And the CxEQBP bits can be used to bypass the EQ function on a per channel basis. Figure 3 shows the internal signal flow through the EQ block.1.3 Output configurationsSTA328Description 1.4 Applications7/57Pin out STA3288/572 Pin out2.1 Package pinsFigure 6.Pin connections2.2 Pin listVCC_SIGNVSS VDD GND BICKI LRCKI SDI VDDA GNDA XTIPLL_FILTER RESERVEDSDA SCL RESET CONFIGVLVDD_REG SUB_GND N.C.OUT2B VCC2B N.C.GND2B GND2A VCC2A OUT2A OUT1B VCC1B GND1B GND1A N.C.VCC1A OUT1AGND_CLEAN GND_REG363534333231302928272625242322212019123456789101112131415161718Table 2.Pin listNumber TypeNameDescription1I/O SUB_GND Ground 2N.C.N.C.Not connected 3O OUT2B Output half bridge 2B 4I/O VCC2B Positive supply 5N.C.N.C.Not connected 6I/O GND2B Negative supply 7I/O GND2A Negative supply 8I/O VCC2A Positive supply 9O OUT2A Output half bridge 2A 10O OUT1B Output half bridge 1B 11I/O VCC1B Positive supply 12I/O GND1B Negative supply 13I/O.GND1A Negative supply 14N.C.N.C.Not connectedSTA328Pin out9/572.3 Pin descriptionOUT1A, 1B, 2A and 2B (pins 16, 10, 9 and 3)Output half bridge PWM outputs 1A, 1B, 2A and 2B provide the input signals to thespeakers.RESET (pin 22)Driving RESET low sets all outputs low and returns all register settings to their default (reset) values. The reset is asynchronous to the internal clock.15I/O VCC1A Positive supply 16O OUT1A Output half bridge 1A 17I/O GND_CLEAN Logical ground 18I/O GND_REG Substrate ground 19I/O VDD_REG Logic supply 20I/O VL Logic supply 21I CONFIG Logic levels 22I RESET Reset23I SCL I 2C serial clock 24I/O SDA I 2C serial data25-RESERVED This pin must be connected to GND 26I PLL_FILTER Connection to PLL filter 27I XTI PLL input clock 28I/O GNDA Analog ground29I/O VDDA Analog supply, nominally 3.3 V 30I SDI I 2S serial data channels 1 & 231I/O LRCKI I 2S left/right clock, 32I BICKI I 2S serial clock 33I/O GND Digital ground34I/O VDD Digital supply, nominally 3.3V 35I/O VSS 5V regulator referred to +V CC 36I/OVCC_SIGN5V regulator referred to groundTable 2.Pin listNumber TypeNameDescriptionPin out STA32810/57I2C signals (pins 23 and 24)The SDA (I2C Data) and SCL (I2C Clock) pins operate according to the I2C specification (Chapter5 on page16 gives more information). Fast-mode (400kB/s) I2C communication is supported.GNDA and VDDA (pins 28 and 29)This is the 3.3 V analog supply for the phase locked loop. It must be well decoupled and filtered for good noise immunity since the audio performance of the device depends upon the PLL circuit.CLK (pin 27)This is the master clock in used by the digital core. The master clock must be an integer multiple of the LR clock frequency. Typically, the master clock frequency is 12.288MHz (256*fs) for a 48kHz sample rate; it is the default setting at power-up. Care must be taken to provide the device with the nominal system clock frequency; over-clocking the device may result in anomalous operation, such as inability to communicate.FILTER_PLL (pin 26)This is the connection for external filter components for the PLL loop compensation. The schematic diagram in Figure5 on page7 shows the recommended circuit.BICKI (pin 32)The serial or bit clock input is for framing each data bit. The bit clock frequency is typically 64*fs using I2S serial format.SDI_12 (pin 30)This is the serial data input where PCM audio information enters the device. Six format choices are available including I2S, left or right justified, LSB or MSB first, with word widths of 16, 18, 20 and 24 bits.LRCKI (pin 31)The left/right clock input is for data word framing. The clock frequency is at the input sample rate, fs.11/573 Electrical specificationsTable 3.Absolute maximum ratingsTable 4.Thermal dataTable 5.Recommended operating conditions3.1 General interface specificationsOperating conditions V DD33 = 3.3V ±0.3V , T amb = 25°C unless otherwise specifiedSymbol ParameterValueUnit V DD33 3.3V I/O power supply (pins VDDA, VDD)-0.5 to 4V V i Voltage on input pins -0.5 to (V DD33+0.5)V V o Voltage on output pins -0.5 to (V DD33+0.5)V T stg Storage temperature-40 to +150°C T amb Ambient operating temperature-20 to +85°C V CC DC supply voltage (pins VCCnA, VCCnB)40V V MAXMaximum voltage on VL (pin 20)5.5VSymbol ParameterMinTypMax Unit R thj-case Thermal resistance junction to case (thermal pad) 2.5°C/W T j-SD Thermal shut-down junction temperature 150°C T WARN Thermal warning temperature 130°C T h-SDThermal shut-down hysteresis25°CSymbol ParameterValueUnit V DD33 I/O power supply3.0 to 3.6V T jOperating junction temperature-20 to +125°CTable 6.General interface electrical characteristicsSymbol ParameterTest Condition Min.Typ.Max.Unit I il Low level input no pull-up V i = 0V (1)1.The leakage currents are generally very small (< 1 nA). The values given here are the maximum valuesafter an electrostatic stress on the pin.1µA I ih High level input no pull-downV i = V DD33 (1)2µA I OZ 3-state output leakage withoutpull-up/downV i = V DD33 (1)2µA V esdElectrostatic protection (human-body model)Leakage current < 1µA2000V12/573.2 DC electrical specifications (3.3V buffers)Operating conditions V DD33 = 3.3V ±0.3V , T amb = 25°C unless otherwise specified3.3 Power electrical specificationsOperating conditions V DD33 = 3.3V ±0.3V , V L =3.3V , V CC =30V ,T amb = 25°C unless otherwise specified.Table 7.DC electrical specificationsSymbol ParameterTest conditionMin.Typ.Max.Unit V IL Low level input voltage 0.8V V IH High level input voltage 2.0V V hyst Schmitt trigger hysteresis 0.4V V ol Low level output IoI = 2mA 0.15V V ohHigh level outputIoh = -2mAV DD33- 0.15VTable 8.Power electrical characteristicsSymbol ParameterTest conditions Min.Typ.Max.Unit R dsON Power Pchannel/Nchannel MOSFET RdsON Id =1A 200270m Ω I dss Power Pchannel/Nchannel leakage IdssV CC = 35V 50µA g N Power Pchannel RdsON matchingId =1A 95%g P Power Nchannel RdsON matchingId =1A95%Dt_s Low current dead time (static)See test circuits, Figure 7 and Figure 81020ns t d ON Turn-on delay time Resistive load 100ns t d OFF Turn-off delay time Resistive load100ns t r Rise time Resistive load, Figure 7 and Figure 825ns t f Fall time Resistive load, Figure 7 and Figure 825ns V CC Supply voltage1036V V L Low logical state voltage VL V L = 3.3V 0.8V V H High logical state voltage VH V L = 3.3V 1.7V I VCC-PWRDNSupply current from V CC in PWRDNPin PWRDN = 0 V 3mA I VCC-hizSupply current from V CC in 3-stateV CC =30V , 3-state22mA13/57Figure 7.Test circuit 1I VCCSupply current from V CC in operation(both channel switching)Input pulse width = 50% duty,switchingfrequency =384kHz,no LC filters80mAI out-sh Overcurrent protectionthreshold (short circuit current limit)4.56AV UV Undervoltage protection threshold7V t pw-min Output minimum pulse width No load70150ns P oOutput power (refer to test circuitTHD = 10%R L = 4Ω, V CC = 21V R L = 8Ω, V CC = 36V 5080W W P oOutput power (refer to test circuitTHD = 1%R L = 4Ω, V CC = 21V R L = 8Ω, V CC = 36V4062W WTable 8.Power electrical characteristics (continued)SymbolParameterTest conditions Min.Typ.Max.UnitDT rDTfVcc (3/4)Vcc(1/2)Vcc (1/4)VcctOUTxYLow current dead time = MAX(DT r, DTf)+VccDuty cycle = 50%INxYM58M57OUTxYgndvdc = Vcc/2V67R 8W+-4 Electrical characteristics curves14/5715/57I 2C bus specificationSTA32816/575 I 2C bus specificationThe STA328 supports the I 2C protocol. This protocol defines any device that sends data on to the I 2C bus as a transmitter and any device that reads the data as a receiver. The device that controls the data transfer is known as the master and the other as the slave. The master always starts the transfer and provides the serial clock for synchronization. The STA328 is always a slave device in all of its communications.5.1 Communication protocolData transition or changeData changes on the SDA line must only occur when the SCL clock is low. SDA transitionwhile the clock is high is used to identify a START or STOP condition.Start conditionSTART is identified by a high to low transition of the data bus SDA signal while the clock signal SCL is stable in the high state. A START condition must precede any command for data transfer.Stop conditionSTOP is identified by a low to high transition of the data bus SDA signal while the clock signal SCL is stable in the high state. A STOP condition terminates communication between STA328 and the bus master.Data inputDuring the data input the STA328 samples the SDA signal on the rising edge of clock SCL. For correct device operation the SDA signal must be stable during the rising edge of the clock and the data can change only when the SCL line is low.5.2 Device addressingTo start communication between the master and the STA328, the master must initiate with astart condition. Following this, the master sends 8 bits (MSB first) onto the SDA line corresponding to the device select address and read or write mode.The 7 MSBs are the device address identifiers, corresponding to the I 2C bus definition. The STA328 device address is decimal 34 (binary 00100010).The 8th bit (LSB) identifies read or write operation, RW. This bit is set to 1 in read mode and 0 for write mode. After a START condition the STA328 identifies the device address on the bus. If a match is found, it acknowledges the identification on the SDA bus during the 9th bit time. The byte following the device identification byte is the internal space address.STA328I 2C bus specification17/575.3 Write operationFollowing the START condition the master sends a device select code with the RW bit setto 0. The ST A328 acknowledges this and then the master writes the internal address byte. After receiving the internal byte address the STA328 again responds with an acknowledgement.2Byte writeIn the byte write mode the master sends one data byte. This is acknowledged by the STA328. The master then terminates the transfer by generating a STOP condition.Multi-byte writeThe multi-byte write modes can start from any internal address. Sequential data byte writes will be written to sequential addresses within the STA328. The master generating a STOP condition terminates the transfer.5.4 Read operation2Current address byte readFollowing the START condition the master sends a device select code with the RW bit set to 1. The STA328 acknowledges this and then responds by sending one byte of data. The master then terminates the transfer by generating a STOP condition.I2C bus specification STA32818/57Current address multi-byte readThe multi-byte read modes can start from any internal address. Sequential data bytes will be read from sequential addresses within the STA328. The master acknowledges each data byte read and then generates a STOP condition terminating the transfer.Random address byte readFollowing the START condition the master sends a device select code with the RW bit set to0. The ST A328 acknowledges this and then the master writes the internal address byte. After receiving, the internal byte address the STA328 again responds with an acknowledgement. The master then initiates another ST ART condition and sends the device select code with the RW bit set to 1. The ST A328 acknowledges this and then responds by sending one byte of data. The master then terminates the transfer by generating a STOP condition.Random address multi-byte readThe multi-byte read modes could start from any internal address. Sequential data bytes will be read from sequential addresses within the ST A328. The master acknowledges each data byte read and then generates a STOP condition terminating the transfer.STA328Register description19/576 Register descriptionY ou must not reprogram the register bits marked “Reserved”. It is important that these bitskeep their default reset values.Table 9.Register summaryAddress Name D7D6D5D4D3D2D1D00x00ConfA FDRB TWAB TWRB IR1IR0MCS2MCS1MCS00x01ConfB C2IMC1IMDSCKE SAIFB SAI3SAI2SAI1SAI00x02ConfC Reserved CSZ4CSZ3CSZ2CSZ1CSZ0OM1OM00x03ConfD MME ZDE DRCBQLPSL DSPBDEMPHPB 0x04ConfE SVE ZCEReserved PWMS AMEReserved MPC MPCV 0x05ConfF E APDPWDN E CL E Reserved BCL EIDE OCFG1OCFG00x06Mmute Reserved Reserved Reserved Reserved Reserved Reserved Reserved MMute 0x07Mvol MV7MV6MV5MV4MV3MV2MV1MV00x08C1Vol C1V7C1V6C1V5C1V4C1V3C1V2C1V1C1V00x09C2Vol C2V7C2V6C2V5C2V4C2V3C2V2C2V1C2V00x0A C3Vol C3V7C3V6C3V5C3V4C3V3C3V2C3V1C3V00x0B Auto1AMPS Reserved AMGC1AMGC0AMV1AMV0AMEQ1AMEQ00x0C Auto2XO3XO2XO1XO1AMAM2AMAM1AMAM0AMAME 0x0D Auto3Reserved Reserved Reserved PEQ4PEQ3PEQ2PEQ1PEQ00x0E C1Cfg C1OM1C1OM0C1LS1C1LS0C1BO C1VBP C1EQBP C1TCB 0x1F C2Cfg C2OM1C2OM0C2LS1C2LS0C2BO C2VBP C2EQBP C2TCB 0x10C3Cfg C3OM1C3OM0C3LS1C3LS0C3BO C3VBP Reserved Reserved 0x11Tone TTC3TTC2TTC1TTC0BTC3BTC2BTC1BTC00x12L1ar L1A3L1A2L1A1L1A0L1R3L1R2L1R1L1R00x13L1atrt L1A T3L1A T2L1A T1L1A T0L1RT3L1RT2L1RT1L1RT00x14L2ar L2A3L2A2L2A1L2A0L2R3L2R2L2R1L2R00x15L2atrt L2A T3L2A T2L2A T1L2A T0L2RT3L2RT2L2RT1L2RT00x16Cfaddr2CFA7CFA6CFA5CFA4CFA3CFA2CFA1CFA00x17B1cf1C1B23C1B22C1B21C1B20C1B19C1B18C1B17C1B160x18B1cf2C1B15C1B14C1B13C1B12C1B11C1B10C1B9C1B80x19B1cf3C1B7C1B6C1B5C1B4C1B3C1B2C1B1C1B00x1A B2cf1C2B23C2B22C2B21C2B20C2B19C2B18C2B17C2B160x1B B2cf2C2B15C2B14C2B13C2B12C2B11C2B10C2B9C2B80x1C B2cf3C2B7C2B6C2B5C2B4C2B3C2B2C2B1C2B00x1DA1cf1C3B23C3B22C3B21C3B20C3B19C3B18C3B17C3B16Register description STA32820/576.1 Configuration register A (addr 0x00)The STA328 will support sample rates of 32kHz, 44.1kHz, 48kHz, 88.2kHz, and 96kHz. Therefore the internal clock will be:"32.768MHz for 32kHz"45.1584MHz for 44.1kHz, 88.2kHz, and 176.4kHz "49.152MHz for 48kHz, 96kHz, and 192kHzThe external clock frequency provided to the XTI pin must be a multiple of the input sample frequency (fs). The correlation between the input clock and the input sample rate isdetermined by the status of the MCSx bits and the IR (input rate) register bits. The MCSx0x1E A1cf2C3B15C3B14C3B13C3B12C3B11C3B10C3B9C3B80x1F A1cf3C3B7C3B6C3B5C3B4C3B3C3B2C3B1C3B00x20A2cf1C4B23C4B22C4B21C4B20C4B19C4B18C4B17C4B160x21A2cf2C4B15C4B14C4B13C4B12C4B11C4B10C4B9C4B80x22A2cf3C4B7C4B6C4B5C4B4C4B3C4B2C4B1C4B00x23B0cf1C5B23C5B22C5B21C5B20C5B19C5B18C5B17C5B160x24B0cf2C5B15C5B14C5B13C5B12C5B11C5B10C5B9C5B80x25B0cf3C5B7C5B6C5B5C5B4C5B3C5B2C5B1C5B00x26Cfud Reserved Reserved Reserved Reserved RA R1WAW10x27MPCC1MPCC15MPCC14MPCC13MPCC12MPCC11MPCC10MPCC9MPCC80x28MPCC2MPCC7MPCC6MPCC5MPCC4MPCC3MPCC2MPCC1MPCC00x29Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved 0x2A Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved 0x2B FDRC1FDRC15FDRC14FDRC13FDRC12FDRC11FDRC10FDRC9FDRC80x2C FDRC2FDRC7FDRC6FDRC5FDRC4FDRC3FDRC2FDRC1FDRC00x2DReserved Reserved Reserved Reserved Reserved Reserved Reserved ReservedReservedD7D6D5D4D3D2D1D0FDRB TWAB TWRB IR1IR0MCS2MCS1MCS001111Table 9.Register summaryAddress Name D7D6D5D4D3D2D1D0Table 10.Master clock selectBit R/W RST Name Description0RW 1MCS0Master clock select: Selects the ratio between the input I 2S sample frequency and the input clock.1RW 1MCS12RWMCS2。

atmega328p单片机原理

atmega328p单片机原理

ATmega328P是一款常用的8位单片机微控制器,在嵌入式系统

设计和开发领域广泛应用。

它由Atmel公司设计,具有高性能、低功耗、易于编程和扩展性强等优点,被广泛应用于各种电子设备中,如智能家居、智能穿戴、迷你机器人等。

ATmega328P单片机是基于Harvard架构的微处理器,具有32KB

的闪存程序存储器和2KB的SRAM数据存储器,以及1KB的EEPROM存储器,支持SPI、I2C、USART等多种通信协议。

它具有23个可编程

输入/输出引脚,包括14个数字输入/输出引脚和6个模拟输入引脚,还有一个复合输入/输出引脚。

ATmega328P单片机可以通过使用Arduino IDE等软件进行编程,以实现各种功能和应用。

它支持C语言和汇编语言编程,并且拥有丰富的编程库和示例代码,在编写程序时,可以直接调用库函数,简化开发流程。

除此之外,ATmega328P单片机还集成了许多硬件模块,如定时器、PWM、ADC、SPI、I2C、USART等,这些模块可以大大增强单片机的功能和性能,使得开发者可以快速构建各种电子设备。

总之,ATmega328P单片机是一款高性能、低功耗、易于编程和

扩展性强的微控制器,被广泛应用于各种嵌入式系统设计和开发领域。

有了它,开发者可以轻松地实现各种电子设备的功能和应用,为人们的生活带来更多的便利和舒适。

- 1 -。

ATmega328P中文翻译资料详解

- -40℃至85℃

•速度等级:

- 0 - 20 MHz的@1.8 - 5.5V

•低功耗在1 MHz,1.8V,25℃ATMEGA48PA/88PA/168PA/328P:

-主动模式:0.2毫安

-掉电模式:0.1μA

-省电模式:0.75μA(包括32千赫,RTC)

8位

微控制器

具有4/8/16/32K

字节的系统

可编程

闪光

ATMEGA48PA

ATMEGA88PA

ATMEGA168PA

ATMEGA328P

牧师8161D-AVR-10月9日

2

8161D-AVR-10月9日

ATMEGA48PA/88PA/168PA/328P

1引脚配置

图1-1。引出线ATMEGA48PA/88PA/168PA/328P

1

1.1.9 ADC7:6(TQFP和QFN/ MLF封装)

在TQFP和QFN/ MLF封装,ADC7:6作为模拟输入到A / D转换器。

这些引脚的模拟电源供电,并作为10位ADC通道。

5

8161D-AVR-10月9日

ATMEGA48PA/88PA/168PA/328P

二,产品简介

该ATMEGA48PA/88PA/168PA/328P是一款基于低功耗8位CMOS微控制器

端口D输出缓冲器具有同时具有高汇和源对称的驱动特性

能力。作为输入,端口D引脚被外部电路拉低时将输出电流,如果上拉

电阻器被激活。端口D引脚为三态时,复位过程中,

即使系统时钟没有运行。

4

8161D-AVR-10月9日

ATMEGA48PA/88PA/168PA/328P

不同的特殊功能端口D都页阐述了“备用端口D的功能”

2SC3281中文资料

MIN.

– – 200 55 35 – – – –

TYP.

– – – – 60 0.40 1.0 30 270

MAX.

5.0 5.0 – 160V

V V MHz pF

Note: hFE (1) Classification R : 0: 55 ~ 110, 0 : 80 ~ 160

CHARACTERISTIC

Collector-Base Voltage Collector-Emitter Voltage Emitter-Base Voltage Collector Current Base Current Collector PowerDissipation (Tc = 25°C) Junction Temperature Storage Temperature Range

SYMBOL

VCBO VCEO VEBO IC IB PC Tj Tstg

RATING

200 200 5 15 1.5 150 150 -55 ~ 150

UNIT

V V V A A W °C °C

Electrical Characteristics (Ta = 25°C)

CHARACTERISTIC

元器件交易网

TOSHIBA

Discrete Semiconductors

2SC3281

Transistor

Unit in mm

Silicon NPN Triple Diffused Type Power Amplifier Applications

Features • Complementary to 2SA1302 • Recommended for 100W High Fidelity Audio Frequency Amplifier Output Stage Absolute Maximum Ratings (Ta = 25°C)

A3283资料

The A3280--, A3281--, and A3283-- Hall-effect latches are ex-tremely temperature-stable and stress-resistant sensors especially suited for operation over extended temperature ranges to +150°C. Superior high-temperature performance is made possible through dynamic offset cancellation, which reduces the residual offset voltage normally caused by device overmolding, temperature dependencies, and thermal stress.The three devices are identical except for magnetic switch points.Each device includes on a single silicon chip a voltage regulator,Hall-voltage generator, small-signal amplifier, chopper stabilization,Schmitt trigger, and a short-circuit protected open-collector output to sink up to 25 mA. A south pole of sufficient strength will turn theoutput on. A north pole is necessary to turn the output off. An on-board regulator permits operation with supply voltages of 4.2 to 24 volts.The first character of the part number suffix determines the device operating temperature range; suffix ‘E–’ is for -40°C to +85°C and ‘L–’ is -40°C to +150°C. Three package styles provide a magnetically optimized package for most applications. Suffix ‘–LH’ is a miniature low-profile surface-mount package, ‘–LT’ is a miniature SOT-89/TO-243AA transistor package for surface-mount applications; while suffix ‘–UA’ is a three-lead ultra-mini-SIP for through-hole mounting.Data Sheet 27609.20FEATURESI Symmetrical Switch Points I Resistant to Physical Stress I Superior Temperature Stability I Output Short-Circuit ProtectionI Operation From Unregulated Supply I Reverse Battery Protection I Solid-State Reliability I Small Size3280, 3281,AND 3283Always order by complete part number: the prefix ‘A’ + the basic four-digit part number + a suffix to indicate operating temperature range +a suffix to indicate package style, e.g., A3281ELH .CHOPPER-STABILIZED, PRECISIONHALL-EFFECT LATCHES3280, 3281, AND 3283CHOPPER-STABILIZED,PRECISIONHALL-EFFECT LATCHES115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-50002Copyright © 2000 Allegro MicroSystems, Inc.Suffix ‘–LH’ PinningDwg. PH-003-4S U P P L YG R O U N DO U T P U T60040020020601001400AMBIENT TEMPERATURE in °CA L L O W AB L E P AC K A G E P O W E RD I S S I P A T I O N i n M I L L I W A T T SDwg. GH-046-2C40801201807005003001001603280, 3281, AND 3283CHOPPER-STABILIZED,PRECISIONHALL-EFFECT LATCHES3Part Numbers 1A3280A3281A3283Characteristic Test ConditionsMin.Typ.Max.Min.Typ.Max.Min.Typ.Max.Units Operate Point, B OPat T A = +25°C and T A = max. 5.02240155090100150180G at T A = -40°C5.0–4015–90100–200G Release Point, B RPat T A = +25°C and T A = max.-40-23-5.0-90-50-15-180-150-100G at T A = -40°C-40–-5.0-90–-15-200–-100G Hysteresis, B hysat T A = +25°C and T A = max.10458030100180–300360G (B OP - B RP )at T A = -40°C––80––180––400GNOTES:1. Complete part number includes a suffix to identify operating temperature range (E or L) andpackage type (LH, LT, or UA).2. As used here, negative flux densities are defined as less than zero (algebraic convention) and -50 G is less than +10 G.3. Typical Data is at T A = +25°C and V CC = 12 V and is for design information only.LimitsCharacteristic Symbol Test Conditions Min.Typ.Max.Units Supply Voltage Range V CC Operating, T J < 170°C 1 4.2–24V Output Leakage Current I OFF V OUT = 24 V, B < B RP ––10µA Output Saturation Voltage V OUT(SAT)I OUT = 20 mA, B > B OP –185500mV Output Current Limit I OM B > B OP 30–60mA Power-On Time t po V CC > 4.2 V––50µs Chopping Frequency f C –340–kHz Output Rise Time t r R L = 820 Ω, C L = 20 pF –0.2 2.0µs Output Fall Time t f R L = 820 Ω, C L = 20 pF –0.1 2.0µs Supply CurrentI CCB < B RP , V CC = 12 V – 3.08.0mA B > B OP , V CC = 12 V– 4.08.0mA Reverse Battery Current I CC V RCC = -30 V––-5.0mA Zener Voltage V Z + V D I CC = 15 mA, T A = 25°C 283237V Zener Impedancez z + z DI CC = 15 mA, T A = 25°C –50–ΩNOTES:1.Maximum voltage must be adjusted for power dissipation and junction temperature.2. B OP = operate point (output turns on); B RP = release point (output turns off).3. Typical Data is at T A = +25°C and V CC = 12 V and is for design information only.ELECTRICAL CHARACTERISTICS over operating temperature range.MAGNETIC CHARACTERISTICS over operating supply voltage range.3280, 3281, AND 3283CHOPPER-STABILIZED,PRECISIONHALL-EFFECT LATCHES115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-50004TYPICAL OPERATING CHARACTERISTICSas a function of temperature050100AMBIENT TEMPERATURE IN °C-50Dwg. GH-026-3S W I T C H P O I N T S I N G A U S S010150-25257512520304050-50-40-30-20-10050100AMBIENT TEMPERATURE IN °C-50Dwg. GH-026-4S W I T C H P O I N T S I N G A US S020150-252575125406080100-100-80-60-40-20* Complete part number includes a suffix denoting operating temperature range (E or L) and package type (LH, LT, or UA).A3283* SWITCH POINTSA3280* SWITCH POINTSA3281* SWITCH POINTS050100AMBIENT TEMPERATURE IN °C-50Dwg. GH-026-6S W I T C H P O I N T S I N G A U S S040150-25257512580120160200-200-160-120-80-403280, 3281, AND 3283CHOPPER-STABILIZED,PRECISIONHALL-EFFECT LATCHES5* Complete part number includes a suffix denoting operating temperature range (E or L) and package type (LH, LT, or UA).4.0 4.55.0SUPPLY VOLTAGE IN VOLTS3.0Dwg. GH-021-13.5S W I T C H P O I N T I N G A U S S4.0 4.55.0SUPPLY VOLTAGE IN VOLTS 3.0Dwg. GH-021-33.5S W I T C H P O I N T I N G A U S S24TYPICAL OPERATING CHARACTERISTICS as a function of temperature (cont'd)0255075100AMBIENT TEMPERATURE IN °C200-50Dwg. GH-029-4S A T U R A T I O N V O L T A G E I N m V150-25125 6.0SU P P L Y C U R R E N T I N m A5.04.03.02.00255075100AMBIENT TEMPERATURE IN °C-50Dwg. GH-028-5125-25150SUPPLY CURRENTOUTPUT SATURATION VOLTAGEA3280* SWITCH POINTSA3281* SWITCH POINTSTYPICAL OPERATING CHARACTERISTICSas a function of supply voltage3280, 3281, AND 3283CHOPPER-STABILIZED,PRECISIONHALL-EFFECT LATCHES115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-50006SENSOR LOCATIONS(±0.005" [0.13 mm] die placement)Package Designator ‘LH’Package Designators ‘UA’ and ‘UA-TL’0.011"0.28 mm NOMPackage Designator ‘LT’Although sensor location is accurate to three sigma for a particular design, product improvements may result in small changes to sensor location.TYPICAL OPERATING CHARACTERISTICS as a function of supply voltage (cont’d)4.0 4.55.0SUPPLY VOLTAGE IN VOLTS3.0Dwg. GH-055-13.5250S A T U R A T I O N V O L T A G E I N m V2002251754.0 6.09.0SUPPLY VOLTAGE IN VOLTS3.0Dwg. GH-058-45.0121.0S U P P L Y C U R R E N T I N m A10118.07.0SUPPLY CURRENTOUTPUT SATURATION VOLTAGEDwg. MH-008-80.030"0.76 mm NOMDwg. MH-011-9A3280, 3281, AND 3283CHOPPER-STABILIZED,PRECISIONHALL-EFFECT LATCHES7All Allegro sensors are subjected to stringent qualification requirements prior to being released to production.To become qualified, except for the destructive ESD tests, no failures are permitted.CRITERIA FOR DEVICE QUALIFICATIONQualification Test Test Method and Test Conditions Test Length SamplesComments Biased Humidity (HAST)T A = 130°C, RH = 85%50 hrs 77V CC = V OUT = 5 V High-Temperature JESD22-A108,408 hrs77V CC = 24 V,Operating Life (HTOL)T A = 150°C, T J ≤ 170°C V OUT = 20 V Accelerated HTOLT A = 175°C, T J ≤ 190°C 504 hrs 77V CC = 24 V,V OUT = 20 VAutoclave, Unbiased JESD22-A102, Condition C,96 hrs 77T A = 121°C, 15 psig High-Temperature MIL-STD-883, Method 1008,1000 hrs 77(Bake) Storage Life T A = 170°CTemperature CycleMIL-STD-883, Method 1010,500 cycles 77-65°C to +150°C Latch-Up—Pre/Post 6Reading Electro-Thermally—Pre/Post 6Induced Gate Leakage Reading ESD,CDF-AEC-Q100-002Pre/Post 3 per Test to failure,Human Body Model Reading test All leads > 1500 V ESD,JESD22-A115Pre/Post 3 per Test to failure,Macine Model Reading test All leads > 200 VElectrical DistributionsPer Specification—303280, 3281, AND 3283CHOPPER-STABILIZED,PRECISIONHALL-EFFECT LATCHES115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-50008FUNCTIONAL DESCRIPTIONChopper-Stabilized Technique. The Hall element can be considered as a resistor array similar to a Wheatstone bridge. A large portion of the offset is a result of the mismatching of these resistors. These devices use a proprietary dynamic offsetcancellation technique, with an internal high-frequency clock to reduce the residual offset voltage of the Hall element that is normally caused by device overmolding, temperature dependen-cies, and thermal stress. The chopper-stabilizing technique cancels the mismatching of the resistor circuit by changing the direction of the current flowing through the Hall plate using CMOS switches and Hall voltage measurement taps, whilemaintaing the Hall-voltage signal that is induced by the external magnetic flux. The signal is then captured by a sample-and-hold circuit and further processed using low-offset bipolar circuitry. This technique produces devices that have anextremely stable quiescent Hall output voltage, are immune to thermal stress, and have precise recoverability after temperature cycling. This technique will also slightly degrade the device output repeatability. A relatively high sampling frequency is used in order that faster signals can be processed.More detailed descriptions of the circuit operation can be found in: Technical Paper STP 97-10, Monolithic Magnetic Hall Sensor Using Dynamic Quadrature Offset Cancellation and Technical Paper STP 99-1, Chopper-Stabilized Amplifiers With A Track-and-Hold Signal Demodulator .Operation. The output of these devices switches low (turns on) when a magnetic field perpendicular to the Hall sensor exceeds the operate point threshold (B OP ). After turn-on, the output is capable of sinking 25 mA and the output voltage is V OUT(SAT). Note that the device latches; that is, a south pole of sufficient strength towards the branded surface of the device will turn the device on; removal of the south pole will leave the device on. When the magnetic field is reduced below therelease point (B RP ), the device output goes high (turns off). The difference in the magnetic operate and release points is the hysteresis (B hys ) of the device. This built-in hysteresis allows clean switching of the output even in the presence of external mechanical vibration and electrical noise.Applications. It is strongly recommended that an external bypass capacitor be connected (in close proximity to the Hall sensor) between the supply and ground of the device to reduce both external noise and noise generated by the chopper-stabilization technique.The simplest form of magnet that will operate these devices is a ring magnet. Other methods of operation, such as linear magnets, are possible. Extensive applications information on magnets and Hall-effect sensors is also available in the Allegro Electronic Data Book AMS-702 or Application Note 27701, orDwg. AH-011-2O U T P U T V O L T A G EFLUX DENSITYDwg. GH-034-53280, 3281, AND 3283CHOPPER-STABILIZED,PRECISIONHALL-EFFECT LATCHES9PACKAGE DESIGNATOR ‘LH’(fits SC-74A solder-pad layout)NOTES: 1.Tolerances on package height and width represent allowable mold offsets. Dimensions given aremeasured at the widest point (parting line).2.Exact body and lead configuration at vendor’s option within limits shown.3.Height does not include mold gate flash.4.Where no tolerance is specified, dimension is nominal.5.Add "LT" to part number for tape and reel.Dimensions in Inches (for reference only)Dimensions in Millimeters (controlling dimensions)Dwg. MA-011-3 inDwg. MA-011-3 mmDwg. MA-010-3B in0° TO MINDwg. MA-010-3B mm0° TO MIN3280, 3281, AND 3283CHOPPER-STABILIZED,PRECISIONHALL-EFFECT LATCHES115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000100.440.35PACKAGE DESIGNATOR ‘LT’(SOT-89/TO-243AA)Dimensions in Inches (for reference only)Dimensions in Millimeters (controlling dimensions)NOTES: 1.Exact body and lead configuration at vendor’s option within limits shown.2.Supplied in bulk pack (500 pieces per bag) or add "TR" to part number for tape and reel.Dwg. MA-012-3 inPads 1, 2, 3, and B — Low-Stress VersionPads 1, 2, and 3 only — Lowest Stress, But Not Self AligningDwg. MA-012-3 mmPads 1, 2, 3, and B — Low-Stress VersionPads 1, 2, and 3 only — Lowest Stress, But Not Self Aligning3280, 3281, AND 3283CHOPPER-STABILIZED,PRECISIONHALL-EFFECT LATCHES11Surface-Mount Lead Form (order A328xxUA-TL)Dimensions in Inches (controlling dimensions)Dimensions in Millimeters(for reference only)PACKAGE DESIGNATOR ‘UA’NOTES: 1.Tolerances on package height and width represent allowable mold offsets. Dimensions given aremeasured at the widest point (parting line).2.Exact body and lead configuration at vendor’s option within limits shown.3.Height does not include mold gate flash.4.Recommended minimum PWB hole diameter to clear transition area is 0.035" (0.89 mm).5.Where no tolerance is specified, dimension is nominal.6.Supplied in bulk pack (500 pieces per bag).Dwg. MH-014E in0.050BSC°Dwg. MH-014E mm1.27BSC°0.480.363280, 3281, AND 3283CHOPPER-STABILIZED,PRECISIONHALL-EFFECT LATCHES115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-500012The products described herein are manufactured under one or more of the following U.S. patents: 5,045,920; 5,264,783; 5,442,283;5,389,889; 5,581,179; 5,517,112; 5,619,137; 5,621,319; 5,650,719;5,686,894; 5,694,038; 5,729,130; 5,917,320; and other patents pending.Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, ormanufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.Allegro products are not authorized for use as critical components in life-support appliances, devices, or systems without express written approval.The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsi-bility for its use; nor for any infringements of patents or other rights of third parties that may result from its use.。

DM74LS283中文资料

DM74LS283中⽂资料2000 Fairchild Semiconductor Corporation DS006421/doc/4b10212517.htmlAugust 1986Revised March 2000DM74LS283 4-Bit Binary Adder with Fast CarryDM74LS2834-Bit Binary Adder with Fast CarryGeneral DescriptionThese full adders perform the addition of two 4-bit binary numbers. The sum (∑) outputs are provided for each bit and the resultant carry (C4) is obtained from the fourth bit.These adders feature full internal look ahead across all four bits. This provides the system designer with partial look-ahead performance at the economy and reduced package count of a ripple-carry implementation.The adder logic, including the carry, is implemented in its true form meaning that the end-around carry can be accomplished without the need for logic or level inversion.Featuress Full-carry look-ahead across the four bitss Systems achieve partial look-ahead performance with the economy of ripple carry s Typical add timesTwo 8-bit words25 nsTwo 16-bit words 45 nss Typical power dissipation per 4-bit adder 95 mWOrdering Code:Devices also available in T ape and Reel. Specify by appending the suffix letter “X” to the ordering code.Connection DiagramOrder Number Package NumberPackage DescriptionDM74LS283M M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow DM74LS283NN16E16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide/doc/4b10212517.html2D M 74L S 283Function TableH= HIGH Level, L = LOW LevelInput conditions at A1, B1, A2, B2, and C0 are used to determine outputs ∑1 and ∑2 and the value of the internal carry C2. The values at C2, A3, B3, A4, and B4 are then used to determine outputs ∑3, ∑4, and C4.Logic Diagram/doc/4b10212517.htmlDM74LS283Absolute Maximum Ratings (Note 1)Note 1: The “Absolute Maximum Ratings” are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings.The “Recommended Operating Conditions” table will define the conditions for actual device operation.Recommended Operating ConditionsElectrical Characteristicsover recommended operating free air temperature range (unless otherwise noted)Note 2: All typicals are at V CC = 5V, T A = 25°C.Note 3: Not more than one output should be shorted at a time, and the duration should not exceed one second.Note 4: I CC1 is measured with all outputs OPEN, all B inputs LOW and all other inputs at 4.5V, or all inputs at 4.5V.Note 5: I CC2 is measured with all outputs OPEN and all inputs GROUNDED.Supply Voltage 7V Input Voltage7VOperating Free Air Temperature Range 0°C to +70°C Storage Temperature Range65°C to +150°CSymbol ParameterMin Nom Max Units V CC Supply Voltage4.7555.25V V IH HIGH Level Input Voltage 2V V IL LOW Level Input Voltage 0.8V I OH HIGH Level Output Current ?0.4mA I OL LOW Level Output Current 8mA T A Free Air Operating Temperature70°CSymbol ParameterConditionsMinTyp Max Units (Note 2)V I Input Clamp Voltage V CC = Min, I I = ?18 mA ?1.5V V OH HIGH Level V CC = Min, I OH = Max 2.73.4VOutput Voltage V IL = Max, V IH = Min V OLLOW Level V CC = Min, I OL = Max0.350.5Output VoltageV IL = Max, V IH = Min VI OL = 4 mA, V CC = Min 0.250.4I I Input Current @ Max V CC = Max A, B 0.2mA Input Voltage V I = 7V C00.1I IH HIGH Level V CC = Max A, B 40µA Input Current V I = 2.7V C020I IL LOW Level V CC = MaxA, B ?0.8mA Input CurrentV I = 0.4V C00.4I OS Short Circuit Output Current V CC = Max 20100mA I CC1Supply Current V CC = Max (Note 4)1934mA I CC2Supply CurrentV CC = Max (Note 5)2239mA/doc/4b10212517.html4D M 74L S 283Switching Characteristicsat V CC = 5V and T A = 25°CFrom (Input)R L = 2 k ?Symbol ParameterTo (Output)C L = 15 pF C L = 50 pF UnitsMinMax MinMax t PLH Propagation Delay Time C0 to ∑1, ∑22428ns LOW-to-HIGH Level Output t PHL Propagation Delay Time C0 to ∑1, ∑22430ns HIGH-to-LOW Level Output t PLH Propagation Delay Time C0 to ∑32428ns LOW-to-HIGH Level Output t PHL Propagation Delay Time C0 to ∑32430ns HIGH-to-LOW Level Output t PLH Propagation Delay Time C0 to ∑42428ns LOW-to-HIGH Level Output t PHL Propagation Delay Time C0 to ∑42430ns HIGH-to-LOW Level Output t PLH Propagation Delay Time A i or B i to ∑i 2428ns LOW-to-HIGH Level Output t PHL Propagation Delay Time A i or B i to ∑i 2430ns HIGH-to-LOW Level Output t PLH Propagation Delay Time C0 to C41724ns LOW-to-HIGH Level Output t PHL Propagation Delay Time C0 to C41725ns HIGH-to-LOW Level Output t PLH Propagation Delay Time A i or B i to C41724ns LOW-to-HIGH Level Output t PHLPropagation Delay Time A i or B i to C41726ns HIGH-to-LOW Level Output/doc/4b10212517.htmlDM74LS283Physical Dimensions inches (millimeters) unless otherwise noted16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 NarrowPackage Number M16A/doc/4b10212517.html6D M 74L S 283 4-B i t B i n a r y A d d e r w i t h F a s t C a r r yPhysical Dimensions inches (millimeters) unless otherwise noted (Continued)16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 WidePackage Number N16EFairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.LIFE SUPPORT POLICY FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user. 2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness./doc/4b10212517.html。

布思安全系统D328A分析模块说明书

uDigital data communications and power provided over a two-wire circuitu Provides one Form C relay output u Two-color Status LEDuEEPROM addressing in module unitThe D328A is used to connect a fire alarm controlpanel (FACP) to other systems, controller inputs, door closures, fan controls, annunciators, indicators or other dry contact input devices. Normally-open (NO)or normally-closed (NC) contacts can indicate alarm,supervisory or trouble conditions.FunctionsBasic OperationAt a single address point on the FACP's polling circuit,this module provides a connection point for auxiliary system controls such as elevator recall systems or HVAC shutdown.Status LEDAn LED confirms polling response and activation status. The LED flashes green to indicate a normalpolling response and flashes red to indicate activation.Certifications and approvalsInstallation/configuration notesCompatibility InformationThe following products are compatible with the D328A Analog NAC Module:Category Product ID Product DescriptionControl Panels:D8024Analog fire alarm control panel (FACP) D10024A Analog FACP Modules:D9067Analog polling module Programmers :D5070Analog device programmerNoticeThe FACP's EPROM must be version 6.64 or higher.Installation ConsiderationsThere are three steps to installing the NAC module:1.Set the point address: Use the D5070 Analog Device Programmer to set the address by programming an EEPROM microchip.2.Connect the wiring: Wiring terminals are clearly marked and the module leaves ample room in the back box for wiring.3.Mount the module in the back box: The relay module mounts on a four-inch square back box. A wall plate (supplied) covers the module concealing the address pins but leaving the LED visible.Data Circuit LengthData (or polling) circuit length is the distance over the circuit wire from the connection at the D9067 module to the most distant device and back to the D9067module. The screw terminals can accept up to 14 AWG (ISO 2.5 mm2) wire, but this reduces the allowable length of the circuit. For specific wire instructions and specifications, see the D9067 Installation Guide ponent 1Relay module 1Wall plate 1Hardware pack 1Literature packElectricalCurrentVoltage (Operating)Electrical (Sensor Circuit Wiring 1)CapacitanceResistance1Data wire must be shielded cable.EnvironmentalMechanicalOutputsPolling Circuit Relay CircuitNoticeThe D328's relay contacts are not rated for AC voltage.2Inputs to both sets of Form C contacts must beeither power-limited or non-power-limited. Do not mix power-limited wiring and non-power-limited wiring on Terminal Block 2.Ordering informationD328A Analog Relay ModuleProvides one Form C relay output.Not Available.Order number D328ARepresented by:Americas:Europe, Middle East, Africa:Asia-Pacific:China:America Latina:Bosch Security Systems, Inc. 130 Perinton Parkway Fairport, New York, 14450, USA Phone: +1 800 289 0096 Fax: +1 585 223 9180***********************.com Bosch Security Systems B.V.P.O. Box 800025617 BA Eindhoven, The NetherlandsPhone: + 31 40 2577 284Fax: +31 40 2577 330******************************Robert Bosch (SEA) Pte Ltd, SecuritySystems11 Bishan Street 21Singapore 573943Phone: +65 6571 2808Fax: +65 6571 2699*****************************Bosch (Shanghai) Security Systems Ltd.201 Building, No. 333 Fuquan RoadNorth IBPChangning District, Shanghai200335 ChinaPhone +86 21 22181111Fax: +86 21 22182398Robert Bosch Ltda Security Systems DivisionVia Anhanguera, Km 98CEP 13065-900Campinas, Sao Paulo, BrazilPhone: +55 19 2103 2860Fax: +55 19 2103 2862*****************************© Bosch Security Systems 2014 | Data subject to change without notice 2738317707 | en, V4, 18. Aug 2014。

Staubli型号大全

史陶比尔集团(英文名:Staubli )创立于1892年(总部位于瑞士),创立于1892年,史陶比尔集团有着100多年的发展历史,是一家在纺织机械,工业快速接头和工业机器人三大领域顶尖地位的世界知名企业。

联系人:王凯文手机:135*52*86*5878Q Q:2*8*5*0*5*9*0*5*8*6座机:010-5243*0161邮箱:2850590586@中国市场常用型号:STAUBLI SENSORDISTRIBUTOR|B27595534STAUBLI union|RCS06??N01143299Staubli 85559752/10 B-30/854502staubli RMP49.06.7102/JVstaubli RBE11.1102/IA/JV/W/ODStaubli 18.564Staubli 18.565Staubli PH08.5103/IA/MA/JVSTAUBLI SPH08.2103/IA/MA/JVSTAUBLI SPH06.2102/IA/MA/JVSTAUBLI SPH06.5102/IA/MA/JVstaubli RMI 209-12-6000-LStaubli RMI 209-12-1000-0-2-03staubli RMI 09 5102 0001 3/8"STAUBLI SBA08.1103STAUBLI SBA08.7103Staubli RBE03.7150.ODStaubli RBE03.1150.ODStaubli SPH06.1103/VB/JV/SPStaubli n00618597Staubli N00618697Staubli RPL08.1252/KRStaubli RPL08.6812/RE/KRStaubli PL08.6812/KRSTAUBLI RBE06.1151 ??IA/HPGSTAUBLI RBE06.1908 ??IA/HPGSTAUBLI RBE06.1101 ??IA/HPGStaubli RBE08.6151Staubli RCS08.1810Staubli RBE06Staubli RCS06Staubli RBE08.6151Staubli RCS08.1810Staubli RMI206.20/ASStaubli AF153.13/ICStaubli ABA15/24Staubli AIRFLEX-S13;125mStaubli ABA15/24Staubli AF153.13/ICStaubli ??AIRFLEX-S13??;75mStaubli ABA15/24Staubli RCS11.8813Staubli HJP09M006/RBE116/ERS081Staubli RBE 08.6151Staubli RBE 08.6251Staubli RBE 08.6252Staubli RBE 11.6813Staubli HJP09M006/RBE116/ERS081STAUBLI QUICKCONNECTOR|CBI09.1102/IA/JVStaubli G1/2" part no.:HPX08.1103/JV/BMB/SP X6CrNiMoTi17-12-2 Staubli G1" part no.:N01221100 type:HPX20.1105/JV/BMR/SPX6CrNiMoTi17-12-2Staubli G3/8 part no.:RBE08.1102/IA/JV/OD/3/FBX6CrNiMoTi17-12-2/Staubli G3/8 partno.:RBE08.1102/IA/JV/OD/3/FB ??X6CrNiMoTi17-12-2/staubli 13184G046Pstaubli 13149G014Pstaubli 13150G014SStaubli RBE11.1153/IC/JE/ODStaubli STA06.1101/SILStaubli SCB04.7201/IC/JK/SPStaubli SCB04.1201/IC/JK/SPSTAUBLI G1/4 RCS08.1101/VDSTAUBLI G1/4 RBE08.6151STAUBLI G1/4 RCS06.1101/VDSTAUBLI G1/4 RBE06.6101Staubli SPC12.2000/IASTAUBLI STAUBLI RMI 200.30Staubli spt 10.7657/L/CGStaubli NYLFLEX12Staubli 108099 SPT10.7103/L/CGStaubli 173150 SPT 10.1657/L/CGStaubli 173156 CGO 05.2416/L/MD/JEStaubli 173157 CGO 05.5416/L/JEStaubli 173245 CGD 05.2416/L/JEStaubli 173247 CGD 05.5416/L/JESTAUBLI CT-E1-15/B;33.4022STAUBLI CT-E1-1.5;33.4023STAUBLI CT-BP1ET;33.0541STAUBLI CT-BP1ET/0.25-0.75AU;33.0143STAUBLI 33.4005STAUBLI CT-BEG;33.4057STAUBLI CS-BT;33.5606-64STAUBLI L1-BL;33.5623STAUBLI CT-AG5;33.1065STAUBLI 33.1021staubli RBE 03.1151/OD/JVstaubli RBE 03.7151/IA/JVstaubli RBE 03.6904staubli RBE 06 1152/OD/JVstaubli RMI 16.7104/JVstaubli RMI 16.1104/JVstaubli RMI 09.7102/JVstaubli RMI 09.1102/JVSTAUBLI B27586150STAUBLI B27586148STAUBLI B27586152STAUBLI B27586151STAUBLI B27586154Staubli PML06.11001/COTStaubli RBE 03.6150staubli R600000005 G4staubli RBE11.7102/45/JEstaubli RBE11.7102/3./JEStaubli CBI06.1101/IAStaubli RMI212.20.1103/JV(with 20st G1/2 connect) Staubli RMI09.512/JVStaubli RMI20049727Staubli RMI20049700Staubli RMF 152.102Staubli RMI 200.30Staubli RMI 09.5102/JVSTAUBLI RBE11.1103/IA/JV/HPLStaubli ADS11.1105/IAStaubli HPX33.7107/JVStaubli SPX08.7103/JVStaubli SPX/PP06.7102/JVStaubli HQ-A2-316??Staubli G1-1/2 STAUBLI?? 87?? Staubli G1/2 STAUBLI?? 89?? Staubli G3/8 STAUBLI?? 90?? Staubli 30.0020 EG-TS-PG36/150 Staubli SPC08.5000/IA/JVStaubli SPC08.2000/IA/JVStaubli SPC08.2000.IA.CDJV Staubli HEL030300STAUBLI HPX 08.1103+HPX 08.7103 STAUBLI HPX 12.1104 +HPX 12.7104 STAUBLI HPX 20.1105 +HPX 20.7105 Staubli K4N002181Staubli K4N001722Staubli K4N001726Staubli K4N001724Staubli K4N00450Staubli RCS08.1816Staubli RBE11.2103Staubli RBE11.1153/IH/JNStaubli N00624312Staubli R60000226Staubli R60111313staubli NGV1 NO01021995Staubli 30.0020 EG-TS-PG36/150 Staubli RMI209.12.1104/JVStaubli RMI09.5102/JVStaubli SPC08.2000.IA.CDJV STAUBLI B27595114STAUBLI B14826136STAUBLI K81556267STAUBLI B23585429STAUBLI B23585432STAUBLI B23586459STAUBLI B23587018STAUBLI B23587078STAUBLI B24582511STAUBLI B27585266STAUBLI B27585714STAUBLI B27595113STAUBLI K81450234STAUBLI K81450235STAUBLI K81556268STAUBLI K81615043STAUBLI K85535599STAUBLI K85536099STAUBLI K86300098STAUBLI 6MTW03-001STAUBLI 6MRW03-001Staubli 103586282staubli 358 0202 ABSTAUBLI RSI 08-1152STAUBLI tuyau HEL 03.03.00 + 2 raccords HEL 03.1150 STAUBLI RBE06.1151/IC/3/FB/VD/JC/ODSTAUBLI RBE06.1151/IC/45/FB/VD/JC/ODSTAUBLI RBE06.1151/IC/6/FB/VD/JC/ODSTAUBLI RBE06.7151/IC/3/JCSTAUBLI RBE06.7151/IC/45/JCSTAUBLI RBE06.7151/IC/6/JCSTAUBLI RSI 08-1152STAUBLI REA081600001STAUBLI SBA 08.1103STAUBLI SBA 08.7103STAUBLI RBE11.6103/45STAUBLI RBE11.6103/6STAUBLI RBE11.1103/ia/6/WSTAUBLI RBE11.1103/ia/45/WSTAUBLI RBE11.7103/IASTAUBLI RBE08.7102/IA/WSTAUBLI RBE08.1102/IA/0D/WSTAUBLI RBE11.1103/IA/0DSTAUBLI RBE11.7103/IA/JESTAUBLI RBE11.1103/IA/JE/0DSTAUBLI RCS-08.1153(G1/2")STAUBLI RCS-08.8103(G1/2")STAUBLI RBE08.6153(G1/2")STAUBLI RBE08.6103(G1/2")staubli SPC05.2000/IA/JVstaubli SPC08.2000/IA/JVstaubli SPC05.5000/IA/JVStaubli B27583359,REA03.2302STAUBLI dashuai2204STAUBLI NO11.198.03Staubli RM1061JVSTAUBLI tuyau HEL 03.03.00 + 2 raccords HEL 03.1150 Staubli RMI 12.1103/JVSTAUBLI S0*******STAUBLI S0*******STAUBLI S0*******STAUBLI RBE03.1100/IA/VD/HPG/JE/OSStaubli KTDEK11 STABU-1008;connector RBE 0.6101/IC Staubli RBE03.7150/IC/JEStaubli RBE03.1904/IC/JEStaubli RBE 11.1103staubli N00628610STAUBLI RBE03.2100/IA/15/HPG/JV/ODSTAUBLI RBE03.2100/IA/75/HPG/JV/ODSTAUBLI RBE03.7100/IA/75/HPG/JVSTAUBLI RBE03.6150/HPGStaubli RBE 03Staubli CBX 09.1102/JV/BF with plugStaubli CBX 09.7102/JV/BF with plugStaubli RMI 09.1102/JV with plugStaubli RMI 09.7102/JV with plugStaubli RBE 03.1251/HPLStaubli RBE 03.6200/HPLSTAUBLI K4N000299STAUBLI K4N000301STAUBLI N00237511STAUBLI N00418810STAUBLI N00428711STAUBLI N00634412STAUBLI N00719710STAUBLI N00728607STAUBLI N00816710STAUBLI N00833607STAUBLI N00919410STAUBLI N00920509Staubli N00642408Staubli N00642308Staubli AIRFLEX08 200MStaubli REE03.1100??JV/0DStaubli REE03.7151Staubli 18.9004 plug-SP1.5/0.5-1.5AGStaubli 18.8004 socket-BP1.5/0.5-1.5Staubli 18.4604 pin carrier-E3-24PE/SStaubli 18.4704 SOCKET CARRIER-E3-24PE/BStaubli 18.0308 socket housing-MGK3VB10-14+MGK3R-M32 Staubli 18.0310 PIN HOUSING-MGK3VS10-14+MGK3R-M32Staubli 18.5618 DST-RG GR.3/14 BUstaubli N00512808staubli N00260306Staubli SPH G1/4 04.5101/MA/IA/JVSTAUBLI NO1210411STAUBLI NO0624312STAUBLI RBE-03-M10X1-S9*******Staubli HPX12.1104 G3/4Staubli HPX20.1105 G1Staubli HPX25.1106 G1 1/4Staubli RBE06.6151/IC/HPISTAUBLI RCS06.1163Staubli AIRFLEX 08 200MStaubli RBE 06.2102/0/ICJTVD SF;QUICK CHANGE BUSHING\G3/8"i DN6 STAUBLI RMI12.1153/JVSTAUBLI RMI12.7152/JVStaubli unvalved plugs rbe03 6904 (no color)Staubli unvalved plugs rbe03 6904 (blue)Staubli plug type:CBI06.7151/IA/JV/REStaubli socket type:CBI06.1810/IA/CNStaubli pipe type:CALOREL-EC10/KBStaubli MCS/MA N-FIXED PLATEStaubli MCS/MA N-MOBILE PLATE。

THS3202中文资料

−50 −60 HD − Hormonic Distortion − dB −70 −80 −90 −100 3rd Harmonic −110 −120 0 2 4 6 8 10 12 VO − Output Voltage − Vpp G=5 RL = 500 Ω VCC = 15 V Rf = 420 Ω f = 10 MHz 50 48 46 44 OIP 3 − dBc 42 40 38 36 34 32 30 28 26 10 60

16.5 V ±VS ±3 V 175 mA

See Dissipation Rating Table

Continuous power dissipation TJ (3)

150°C 125°C −40°C to 85°C −65°C to 150°C 300°C 3000 V 1500 V 200 V

Copyright 2002 − 2004, Texas Instruments Incorporated

元器件交易网

THS3202

SLOS242D − SEPTEMBER 2002 − REVISED JANUARY 2004

ABSOLUTE MAXIMUM RATINGS

OIP3 vs FREQUENCY

Test Instrument Measurement Limit VCC = ±7.5 V VCC = ±7 V VCC = ±6 V

TEST CIRCUIT FOR IMD3 / OIP3

Output Power Spectrum Analyzer

2nd Harmonic

Maximum junction temperature, continuous operation, long term reliability TJ (4) Operating free-air temperature range, TA Storage temperature range, Tstg Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds

ATMEGA328P-15MZ;ATMEGA328P-15AZ;中文规格书,Datasheet资料