dsp优化心得

dsp学习心得体会 学习心得体会

dsp学习心得体会学习心得体会篇一:DSP学习总结DSP学习总结摘要:本总结介绍了数字信号技术(DSP)的基本结构,特点,发展及应用现状。

通过分析与观察,寄予了DSP美好发展前景的希望。

关键字:数字信号处理器,DSP,特点,应用1 DSP介绍数字信号处理简称DSP,是进行数字信号处理的专用芯片,是伴随着微电子学、数字信号处理技术、计算机技术的发展而产生的新器件,是对信号和图像实现实时处理的一类高性能的CPU。

所谓“实时实现”,是指一个实际的系统能在人们听觉、视觉或按要求所允许的时间范围内对输入信号进行处理,并输出处理结果。

数字信号是利用计算机或专用的处理设备,以数值计算的方式对信号进行采集、变换、综合、估计与识别等加工处理,从而达到提取信息和方便应用的目的。

数字信号处理的实现1是以数字信号处理理论和计算技术为基础的。

2 结构32位的C28xDSP整合了DSP和微控制器的最佳特性,能够在一个周期内完成32*32位的乘法累加运算。

所有的C28x芯片都含一个CPU、仿真逻辑以及内存和片内外设备的接口信号(具体结构图见有关书籍)。

CPU的主要组成部分有:程序和数据控制逻辑。

该逻辑用来从程序存储器取回的一串指令。

实时和可视性的仿真逻辑。

地址寄存器算数单元(ARAU)。

ARAU为从数据存储器取回的数据分配地址。

算术逻辑单元(ALU)。

32位的ALU执行二进制的补码布尔运算。

预取对列和指令译码。

为程序和数据而设的地址发生器。

定点MPY/ALU。

乘法器执行32位*32位的二进制补码乘法,并产生64位的计算结果。

中断处理。

3 特点采用哈佛结构。

传统的冯?诺曼结构的数据总线和指令总线是公用的,因此在高运算时在传输通道上会出拥堵现象。

而采用哈佛结构的DSP 芯片片内至少有4 套总线:程序的地址总线与数据总线,数据的地址总线与数据总线。

由于这种结构的数据总线和程序总线分离,从而在一个周期内同能2时获取程序存储器内的指令字和数据存储器内的操作数,提高了执行速度。

关于dsp心得体会

关于dsp心得体会篇一:dsp实验报告心得体会TMS320F2812x DSP原理及应用技术实验心得体会1. 设置环境时分为软件设置和硬件设置,根据实验的需要设置,这次实验只是软件仿真,可以不设置硬件,但是要为日后的实验做准备,还是要学习和熟悉硬件设置的过程。

2. 在设置硬件时,不是按实验书上的型号选择,而是应该按照实验设备上的型号去添加。

3. 不管是硬件还是软件的设置,都应该将之前设置好的删去,重新添加。

设置好的配置中只能有一项。

4. CCS可以工作在纯软件仿真环境中,就是由软件在PC机内存中构造一个虚拟的DSP环境,可以调试、运行程序。

但是一般无法构造DSP中的外设,所以软件仿真通常用于调试纯软件算法和进行效率分析等。

5. 这次实验采用软件仿真,不需要打开电源箱的电源。

6. 在软件仿真工作时,无需连接板卡和仿真器等硬件。

7. 执行write_buffer一行时。

如果按F10执行程序,则程序在mian主函数中运行,如果按F11,则程序进入write_buffe函数内部的程序运行。

8. 把str变量加到观察窗口中,点击变量左边的“+”,观察窗口可以展开结构变量,就可以看到结构体变量中的每个元素了。

9. 在实验时,显示图形出现问题,不能显示,后来在Graph Title 把Input的大写改为input,在对volume进行编译执行后,就可以看到显示的正弦波图形了。

10. 在修改了实验2-1的程序后,要重新编译、连接执行程序,并且必须对.OUT文件进行重新加载,因为此时.OUT文件已经改变了。

如果不重新加载,那么修改执行程序后,其结果将不会改变。

11. 再观察结果时,可将data和data1的窗口同时打开,这样可以便于比较,观察结果。

12. 通过这次实验,对TMS320F2812x DSP软件仿真及调试有了初步的了解与认识,因为做实验的时候都是按照实验指导书按部就班的,与真正的理解和掌握还是有些距离的。

dsp实习心得体会

dsp实习心得体会

作为一名实习生,在经历了一段时间的实习,我对DSP工作有了更深入的了解,并积累了一些心得体会。

首先,学习是实习中最重要的一部分。

在实习过程中,我主动向导师和同事请教问题,学习他们的经验和技巧。

同时,我也会主动在工作之余积极学习相关的书籍和资料,

不断提升自己的专业水平。

其次,沟通和合作能力至关重要。

在实习过程中,我意识到与同事和团队合作的重要性。

良好的沟通能力可以帮助我更好地理解任务需求,并与团队成员共同解决问题。

合作能力也是实现团队目标的关键,通过与团队成员的紧密合作,我们可以更高效地

完成任务。

另外,实习对于培养解决问题的能力也起到了重要的作用。

在实习过程中,我们经常

面临各种挑战和问题。

我逐渐养成了主动思考和分析问题的习惯,学会了寻找解决问

题的办法。

通过克服困难,我不仅增加了自信心,而且也锻炼了自己的解决问题的能力。

最后,实习也是一个提升自己综合素质的机会。

除了专业知识和技能外,我还懂得了

工作中的细节管理、时间管理,以及处理压力的能力。

通过实习,我不仅在专业方面

得到了提升,还全面提升了自己作为一名职业人士所必备的综合素质。

总之,通过这段实习经历,我深刻认识到了专业能力、沟通能力、问题解决能力以及

综合素质的重要性。

我将会继续学习和提升自己,不断成长,为将来的工作打下坚实

的基础。

dsp心得体会范文

dsp心得体会范文dsp心得体会篇一:DSP原理及应用的学习体会这个学期通过《对DSP芯片的原理与开发应用》课程的学习,对DSP芯片的概念、基本结构、开发工具、常用芯片的运用有了一定的了解和认识,下面分别谈谈自己的体会。

一,DSP芯片的概念数字信号处理(DigitalSignalProcessing)是利用计算机或专用处理设备,以数字形式对信号进行采集、变换、增强、滤波、估值、压缩、识别等处理,以得到符合人们需要的信号形式。

20世纪60年代以来,随着计算机和信息技术的飞速发展,数字信号处理技术应运而生并得到迅速的发展。

在通信、等诸多领域得到极为广泛的应用。

DSP(DigitalSignalProcess)芯片,即数字信号处理器,是一种特别适合于进行数字信号处理运算的微处理器,其应用主要是实时快速的实现各种数字信号处理算法。

该芯片一般具有以下主要特点:(1)在一个指令周期内可完成一次乘法和一次加法;(2)程序与数据空间分开,可以同时访问指令和数据;(3)片内具有快速RAM,通常可通过独立的数据总线在两块中同时访问;(4)具有低开销或无开销循环及跳转的硬件支持;(5)快速的中断处理和硬件支持;(6)具有在单周期内操作的多个硬件地址产生器;(7)可以并行执行多个操作;(8)支持流水线操作,使取值、译码和执行等操作可以同时进行。

世界上第一个单片DSP芯片应当是1978年AMI公司发布的S2811,1979年美国INTEL公司发布的商用可编程器件2920是DSP芯片的一个主要里程碑。

这两种芯片内部都没有现代DSP芯片所必须有的单周期乘法器。

1980年,日本NEC公司推出的uPD7720是第一个具有乘法器的商用DSP芯片。

当前,美国德州公司(TI),Motorola公司,模拟器件公司(AD),NEC公司,AT&T公司是DSP芯片主要生产商。

选择合适的DSP芯片,是设计DSP应用系统的一个非常重要的环节。

dsp实验心得体会范文3篇_dsp实习心得体会(2)

dsp实验心得体会范文3篇_dsp实习心得体会(2)dsp实习心得体会篇1如果说前几年DSP作为一个器件,一个处理器或一个事物是相对比较新的东西,那么现在DSP已经在我们电子设计开发中非常常见了。

首先我们从定义上简单理解一下DSP。

我们涉及到的DSP主要是只这里特指数字信号处理器芯片,这里我把我的一些学习经验和大家分享。

希望对大家有帮助了解DSP我个人认为学习一个东西首先是了解它,比如DSP到底是什么?用在什么地方?怎么用?和这里我们传统的单片机特点有那些相同与不同?开发需要注意什么?怎么样完成一个最小系统等。

我想了解清楚这些问题我们自然就清楚比较清楚的认识DSP了。

下面我们就来对上面的问题我们在很多地方都可以找到答案,我把其中比较重要的简单的回答一下。

DSP大家注意和传统的概念区分一下,传统我们经常说的DSP(Digital Signal Processing(数字信号处理))的缩写也就是说是一些功能算法,这里的DSP是指(Digital Signal Process(数字信号处理器))的缩写,也就是说他是一个集成一些外设的一个芯片,类似我们的单片机。

我们通过程序实现一些特定的功能。

和传统单片机比较的区别?DSP功能比普通单片机高出很多,当然价格也比较高。

所以直接用DSP和单片机比较是不合适的。

我们这里比较不是从他的应用领域来比较,我们是从开发的角度来比较,为了是使那些熟练使用单片机的朋友可以很快上手。

当然我的主要目的的大家可以比较学习,达到熟悉一种CPU其他就可以很快上手。

下面从几个方面比较一下1,硬件上比较从硬件上比较DSP和传统的单片机主要有几个方面不一样,很多DSP电源系统比传统的复杂,但是这个并不影响我们因为如TI的DSP 都提供相关的测试电路。

开始的时候大家可以完全按照他来设计。

调试方式上有很大不同,DSP一般通过JTAG来进行仿真和烧写的,而单片机是通过直接仿真器来仿真的(这里讲的单片机是比较早的,现在的单片机也有很多采用JTAG调试方式)。

dsp实验心得体会范文3篇_dsp实习心得体会

dsp实验心得体会范文3篇_dsp实习心得体会digital signal processor简称DSP,中文意思是数字信号处理,DSP就是用数值计算的方式对信号进行加工的理论和技术,现结合自身,谈谈一些心得体会。

本文是dsp实验的心得体会范文,仅供参考。

dsp实验心得体会范文篇一1. 设置环境时分为软件设置和硬件设置,根据实验的需要设置,这次实验只是软件仿真,可以不设置硬件,但是要为日后的实验做准备,还是要学习和熟悉硬件设置的过程。

2. 在设置硬件时,不是按实验书上的型号选择,而是应该按照实验设备上的型号去添加。

3. 不管是硬件还是软件的设置,都应该将之前设置好的删去,重新添加。

设置好的配置中只能有一项。

4. CCS可以工作在纯软件仿真环境中,就是由软件在PC机内存中构造一个虚拟的DSP环境,可以调试、运行程序。

但是一般无法构造DSP中的外设,所以软件仿真通常用于调试纯软件算法和进行效率分析等。

5. 这次实验采用软件仿真,不需要打开电源箱的电源。

6. 在软件仿真工作时,无需连接板卡和仿真器等硬件。

7. 执行write_buffer一行时。

如果按F10执行程序,则程序在mian主函数中运行,如果按F11,则程序进入write_buffe函数内部的程序运行。

8. 把str变量加到观察窗口中,点击变量左边的“+”,观察窗口可以展开结构变量,就可以看到结构体变量中的每个元素了。

9. 在实验时,显示图形出现问题,不能显示,后来在Graph Title 把Input的大写改为input,在对volume进行编译执行后,就可以看到显示的正弦波图形了。

10. 在修改了实验2-1的程序后,要重新编译、连接执行程序,并且必须对.OUT文件进行重新加载,因为此时.OUT文件已经改变了。

如果不重新加载,那么修改执行程序后,其结果将不会改变。

11. 再观察结果时,可将data和data1的窗口同时打开,这样可以便于比较,观察结果。

dsp实习心得体会7篇

dsp实习心得体会7篇dsp实习心得体会 (1) 很荣幸今年暑期能够通过赣州市青年英才“展翅计划”加入到南康区行政审批局进行为期一个月的暑期实习。

通过这一个月的实习,我了解到了南康区市民服务中心的工作运作情况和区行政审批局的单位文化,在实际的工作中提升了自己的职业技能,积累了一定的工作经验,收获颇丰。

在实习过程中,我了解到了市民服务中心为方便群众办理业务而设立的种种举措,双向开放服务中心努力为南康优化产业布局,做大做强南康家具产业集群提供强大助力。

在实际工作中,除了完成领导交代的任务外,引导群众到相应的窗口办理业务,解答群众的疑惑成为了我的主要工作。

刚开始虽然也会遇到不懂的问题,但是通过耐心地沟通解释最终也能够得以解决。

在这一个月中,国内疫情防控形式变得异常严峻,疫情防控措施逐渐加强。

按照上级要求,及时排查市民服务中心工作人员疫苗接种情况,详细询问未接种原因。

在市民服务中心一楼大厅入口值班,为来访的群众测量体温、查验赣通码、行程码,询问是否接种新冠疫苗成为了常态。

对于一些未正确佩戴口罩的人员,在我们的温馨提醒下,都能够自觉佩戴好口罩,为自己和他人的健康负责。

在经过这为期一个月的实习工作后,我感受到了单位工作人员的不易,帮助到了办事群众,也提升了自我,而我也将继续努力,在未来的学习、工作中积极参加各类社会实践活动,为社会奉献出自己的一份力量。

dsp实习心得体会 (2) 我的为期六个周的实习在昨天彻底的结束了,原以为我会很轻松很潇洒的离开,但是没有想到当我跟我们班的那些同学告别,收拾行李踏上返校的汽车的时候,心情竟然是如此的复杂。

有对我们班那些学生的不舍,刚开始的时候我觉得很难融入那个班集体,常常会觉得很失落,可是当我刚刚开始慢慢融入到那个集体,发现了那群学生的活泼可爱的时候,实习却要结束了。

发现现实真的是很残酷的,它总是能抓住人性的弱点,然后再给我们狠狠一击。

所以在这里我也衷心的祝愿我的那班学生们能够健康快乐的成长,虽然他们现在的学习不是很让人省心,但是我坚信他们最后都能找到适合自己的一条路,开创属于自己的一片天,因为他们都是聪明善良的孩子!也衷心的祝愿我的实习指导老师张老师能够健康快乐,生活幸福美满!也感谢她在这段时间给与我的帮助。

2024年dsp实习心得体会

2024年dsp实习心得体会(____字)一、实习前的准备作为一名计算机科学专业的学生,我对数字信号处理(DSP)有着浓厚的兴趣。

在大四年级,我有幸获得了一份DSP实习岗位,并且是在一家知名的科技公司进行实习。

为了充分准备实习,我提前学习了相关的基础知识,如信号处理理论、数字滤波器、频域分析等。

此外,我还系统地学习了Matlab和C语言的使用,以便更好地进行实习工作。

二、实习期间的学习和工作在实习的第一天,我被分配到一个DSP团队,该团队主要负责音频信号处理的相关项目。

在实习的初期,我主要进行了一些基础的工作,如编写测试脚本、调试硬件设备等。

这些工作虽然不是很有挑战性,但是对于我来说是一个很好的入门机会,让我熟悉了公司的工作流程和团队合作方式。

随着实习的深入,我逐渐接触到了一些更具挑战性的任务。

例如,我被要求设计一个实时音频滤波器,用于消除特定频率的噪音。

这个任务需要我运用已学的信号处理理论知识,并且结合Matlab和C语言进行算法设计和实现。

在完成任务的过程中,我遇到了一些困难和挫折,但是通过仔细研究文献资料和与导师的讨论,我最终成功地完成了这个任务。

通过这个项目,我不仅巩固了信号处理和编程的基础知识,也锻炼了我的问题解决能力和团队合作能力。

三、与团队的沟通和合作在实习期间,我与团队的沟通和合作起到了至关重要的作用。

首先,我与团队成员进行了充分的交流,让我更好地了解公司的工作流程和项目进展。

同时,我也与导师定期开展讨论,与他们分享我的想法和实习中遇到的问题。

在他们的指导下,我能够更好地理解项目的需求,并且提供相应的解决方案。

此外,我还积极参与团队的讨论和协作,与其他实习生和工程师们一起合作完成一些团队项目。

通过与团队的合作,我学会了如何与他人协作,如何有效地分配任务和管理时间。

团队的合作给我提供了很大的启发和帮助,让我更好地了解了工作中的团队协作和沟通的重要性。

四、个人成长和收获通过这次DSP实习经历,我在多个方面都得到了很大的成长和收获。

【心得体会】dsp实验心得体会

【心得体会】dsp实验心得体会

在进行dsp实验的过程中,我收获了很多。

首先,我学会了如

何运用数字信号处理的理论知识,将其应用到实际的实验中。

通过

实验,我深刻理解了滤波、频谱分析、信号重构等概念,加深了对

数字信号处理的理解。

其次,我学会了如何使用dsp工具进行数据处理和分析。

通过

使用MATLAB等工具,我能够对信号进行采样、滤波、变换等操作,

从而得到我们需要的结果。

这让我对数字信号处理的实际操作有了

更深入的认识。

另外,通过实验,我也体会到了团队合作的重要性。

在实验中,我和同学们一起讨论问题、分析数据、找出解决方案,共同完成了

实验任务。

这不仅提高了我的团队合作能力,也加深了我对数字信

号处理知识的理解。

最后,通过实验,我也发现了自己的不足之处。

在实验中遇到

了很多问题,有时候需要反复尝试才能找到解决方案。

这让我意识

到自己在理论知识和实际操作上还有很大的提升空间,需要不断学

习和实践。

总的来说,通过dsp实验,我不仅学到了很多知识,也提高了自己的实际操作能力和团队合作能力。

这对我的专业发展和个人成长都有着重要的意义。

希望在以后的学习和工作中能够继续努力,不断提升自己。

DSP学习心得

数字信号处理—DSP课程学习的认识今年学习了DSP这门课程后,有了一些自己的认识和见解,并且体会到了它强大的功能和作用,它不但在高端的技术领域有很重要的地位,如通信、雷达、声纳、语音合成和识别、图像处理、高速控制等;而且在生活中有它不小的作用,如,影视、仪器仪表、医疗设备、家用电器等众多领域。

但是,由于DSP技术发展很快,生产DSP芯片的厂家又多,这既是它的优点同时又是缺点,因为这样会导致产品更新换代的周期越来越短,还有,每一种芯片,都有其独特的硬件结构和一套专门的指令系统与开发工具,这更加的带来了学习DSP技术的困难。

在我自己的学习体系里,有自己的一点经验可以用来辅助的学习这门课程。

古时候的一个习语说的是“窥一斑而知全豹”这个同时可以用来指导学习DSP,尽管它的更新换代很快,但也只是为了完善它而更好用和借助其它的技术为它添加一些别的功能而使其更强大,其实质的理论还没有变话,所以,我们可以就其某一个芯片的知识来指导其它的芯片的学习和利用。

这里,以TMS320系列DSP芯片为例来进行知识的梳理。

x(t)→抗混叠滤波器→A/D→数字信号处理器→D/A→低通滤波器→y(t)数字信号处理系统简化框图这个作为基本的理论模型,然后开始主要内容:1.1,TMS320系列DSP芯片的概述﹑分类及应用、平台;1.2,主要特性有①CPU,②存储器,③指令系统,④在片外围电路,⑤电源,⑥在片仿真接口,⑦速度、组成框图;1.3,总线结构;1.4,存储器空间分配、存储器(程序存储器、数据存储器);1.5,中央处理单元中,算术逻辑运算单元①ALU的输入,②ALU的输出,③溢出处理,④进位位,⑤双16位算术运算,累加器A和B(保存累加器的内容、累加器移位和循环移位、专用指令),桶形移位器乘法器/加法器单元,比较、选择和存储单元,指数编码器,CPU状态和控制寄存器;1.6,数据寻址方式①立即寻址,②绝对寻址,③累加器寻址,④直接寻址,⑤间接寻址;⑥存储器映像寄存器寻址,⑦堆栈寻址;1.7程序存储器地址生成方式,程序计数器,分支转移,调用与返回,条件操作,重复操作(重复执行单条指令、程序块重复操作),复位操作,中断(中断类型、中断标志寄存器和中断屏蔽寄存器、中断处理过程),省电方式;1.8,流水线①流水线操作,②延迟分支转移,③条件执行,④双寻址存储器与流水线,⑤单寻址存储器与流水线,⑥流水线冲突和插入等待周期(流水线冲突、等待周期表);1.9,在片围电路①并行I/O口及通用I/O引脚,②定时器,③时钟发生器(硬件配置的PLL软件可编程PLL),④主机接口;1.10,串行口;串行口概述(标准串行口、缓冲串行口、时分多路串行口、多通道缓冲串行口);1.11,DMA控制器①DMA控制器的基本特征,②子地址寻址方式,③DMA通道优先级和使能控制寄存器,④DMA通道现场寄存器,⑤DMA编程举例;1.12,外部总线①外部总线接口,②外部总线操作的优先级别,③等待状态发生器,④分区切换逻辑,⑤外部总线接口定时器(存储器寻址定时图、I/O寻址定时图);⑥复位和IDLE3省电工作方式(外部总线复位定时图、“唤醒”IDLE3省电方式的定时图);1.13,TMS320C54x引脚信号说明。

DSP调试我自己的一些经验

DSP调试我自己的一些经验1)不要贪快,俗话说得好:欲速则不达。

毕竟硬件的编程和软件的编程还是有很大的不同,否则一旦出错,无从下手2)做到一定程度,要存档,要总结。

(备份)3)要看你所开发的DSP的文档,并且要详细反复的看,这一点尤为重要。

4)多参考示例代码,毕竟创造要有基础作保证。

还望大家多多指教!我推荐大家选购下面的2812开发板,对大家的学习应该有所帮助,祝大家能从中学到乐趣。

系统资源DSP 处理器TMS320F2812 ,最高工作频率150MHz;SHX-DSP2812开发板DSP 芯片内置18K X 16 位SRAM, 4K X 16 位BOOT ROM , 1K X 16 位OPT ROM ;DSP 芯片内置128K X 16 位FLASH;外扩32k×16bit 的程序RAM,32k×16bit 的数据RAM;监视用LED 发光管一个;DSP 所有功能引脚引出,176pin;4MB 程序、数据寻址空间;I/O 输入输出模块――8 个LED;SCI模块――RS232 通讯接口电路;SPI_DA模块――4 路8位串行D/A输出;A/D转换模块――2 路12位A/D 采样(可扩展到16 路);CAN 模块――CAN 总线收发器;PWM 模块――PWM 控制微型直流电机正反转(选配);步进电机支持(选配)。

扩展接口IEEE 1149.1 标准JTAG 接口;176pin 全部功能引脚引出,用户可以扩展使用;RS232 标准DB9 接口插座;4路D/A输出接口插座;2路A/D输出接口插座;CAN 总线接口插座;电机接口:支持直流电机、步进电机(选配)。

实例及代码实验1.外部RAM测试程序实验;实验2.定时器控制LED程序实验;实验3.LED走马灯程序实验;实验4. 数码管显示实验;实验5. 数码管按键实验;实验6. SCIA 串口通讯实验;实验7. SCIB 串口通讯实验;实验8. SPI接口的D/A实验;实验9. A/D采样实验;实验10. CAN 总线通信实验;实验11. PWM电机控制实验(选配);实验12. 步进电机控制实验(选配)。

dsp学习心得

dsp学习心得最近,我开始学习DSP技术,这是一项专业的数字信号处理技术。

虽然这项技术对于许多人来说可能还相对陌生,但我认为它具有巨大的潜力和前途。

在学习过程中,我克服了许多挑战,但我也获得了很多宝贵的经验。

下面是我个人的DSP学习心得与大家分享,希望对大家有所帮助。

一、DSP技术概述DSP技术是一种专业的数字信号处理技术,它主要应用于音频、视频、雷达、通信、医疗、军事等领域。

该技术基于数学算法,通过数字计算对采集到的模拟信号进行处理,提取出所需的信息。

DSP技术的优点包括处理速度快、精度高、可靠性强等。

二、DSP学习要点1.数学基础学习DSP技术需要较好的数学基础,特别是离散数学和信号与系统的相关知识。

需要了解傅里叶级数、离散傅里叶变换、卷积等概念和应用。

同时,也需要掌握线性代数和微积分等数学基础知识。

2.编程语言DSP技术的应用离不开编程语言,如C语言、MATLAB等。

其中,C语言是最常用的编程语言,掌握好C语言对于学习DSP 非常重要,能够帮助我们深入了解DSP技术的实现原理。

3.实践经验学习DSP技术需要有实践经验。

通过实际操作,能够更好地理解理论知识,并加深对DSP技术的认识。

需要有耐心和恒心,多进行实践操作,多总结不同的处理方法和技巧。

三、常见DSP应用场景1.音频处理DSP技术在音频处理中具有广泛应用,其主要任务是对音频信号进行数字处理,以提高音频品质或减少噪声等。

2.图像处理DSP技术在图像处理中也具有广泛应用,例如对图像进行滤波、检测等操作,可以提高图像的质量和清晰度,应用在运动目标识别、人脸识别等方面。

3.通信处理通信领域是DSP技术的重要应用领域之一。

DSP技术可以对电话、移动通信等进行数字信号处理,可以实现音频压缩、语音识别等功用。

四、学习中的关键困难点1.数学知识的差距DSP技术需要掌握较高级别的数学知识,这也是学习中的一个关键困难点。

如果数学基础比较弱,需要花费更多的时间来学习相关知识。

DSP学习总结(共5则)

DSP学习总结(共5则)第一篇:DSP学习总结DSP学习总结根据一学期以来对DSP这门课程的学习,学到了很多DSP相关的知识。

了解了如何根据实际需求选择DSP芯片,也知道了C54x的汇编和链接过程,还掌握了C54x的寻址方式。

对于老师的授课方法也有一定的见解。

开始学DSP的时候比较着急,因为也感觉什么都不会,不知道从哪里下手。

手上的资料只有书,后来去图书馆看了两本,一本是《DSP原理与开发》,除了有详细的理论说明之外,还会在每个章节之后配上一个例程,缺点就是错误也不少,估计时间太仓促,校对没做好。

另一本书是清华大学出版社的《TMS320C28X系列DSP的CPU与外设》,是从TI的英文的技术手册翻译过来的,分上、下两册,可以作为工具书,很实用,缺点是没有例子。

书看了一两遍,觉得还是一头雾水。

后来有相应的实验开课,慢慢对DSP有点了解了,刚开始都不知道怎么建PROJECT,后来问了同学,然后再看TI的例程,仿照它的程序框架,边看例程,边对着实验指导书,看得主要是如何初始化,需要对每个外设进行哪些寄存器的初始化,寄存器为什么这样设置,程序如何进中断,如何出中断等等。

边看书边做实验,效率会高很多,也就能慢慢理解了。

对于刚学DSP的新手我觉得掌握一些初级知识就差不多了。

第一步:硬件入门。

1.先学习DSP的硬件基础:了解CPU结构、中断、EMIF、HPI、GPIO、SPI、Timer、供电方式、时钟;2.了解DSP互连的存储器:SDRAM、FLASH、FIFO、双口RAM、SDSRAM 等不需深入研究;3.了解CPLD/FPGA的硬件结构、连接原理、VerilogHDL编程语言需深入研究;4.了解DSP Bootloader不需深入研究;5.了解DSP和外部通信的接口:PCI、USB、LAN、UART等,有时间可以看看DM642的VideoPort第二步:工具入门。

1.学习数字电路、模拟电路、电路分析的知识;2.学好一种PCB绘制软件如Protel DXP2006;3.学习信号完整性、学习传输线理论,特性阻抗知识;关于老师上课的方式我认为:1.太多的理论知识枯燥乏味,因为有实验课,我觉得老师可以根据实验要做的内容在课堂上深入讲解,这样在讲述的同时能让同学们认真听,认真记以便于实验课程的顺利完成,比纯理论效果会好点。

DSP程序优化总结

DSP程序优化总结随着计算机应用的日益广泛,对于程序优化的需求也越来越迫切。

在数字信号处理(DSP)领域,程序优化是提高计算速度和减少资源占用的重要手段。

本文将对DSP程序优化进行总结,包括优化的目标、常用的优化技术以及实施优化的步骤等方面。

首先,我们需要明确DSP程序优化的目标。

通常,DSP程序的优化目标可以概括为提高程序的执行速度、减少资源占用和降低功耗。

在实际的优化过程中,需要根据具体的应用场景和需求来确定优化的重点。

例如,对于实时音频处理应用,优化的重点可能是降低延迟和减少功耗;而对于图像处理应用,优化的重点可能是提高处理速度和减少资源占用。

其次,我们需要了解常用的DSP程序优化技术。

下面列举了一些常见的优化技术:1.算法优化:选择合适的算法和数据结构可以显著提高程序的执行速度和资源利用率。

例如,使用FFT算法代替DFT算法可以加速频域信号处理;使用滑动窗口技术可以减少不必要的计算;使用稀疏矩阵表示可以减少存储空间占用等。

2.并行计算:利用并行计算的能力可以加速程序的执行速度。

可以通过使用多线程、多核、GPU等方式来实现并行计算。

需要注意的是,合理的任务划分和数据分配是并行计算的关键。

3. 数据对齐和访存优化:对于DSP程序来说,访存是一个重要的性能瓶颈。

通过调整数据结构和内存布局,使得数据可以以连续和对齐的方式访问,可以提高DRAM访问效率。

另外,合理使用高速缓存(Cache)和预取机制也可以加速程序的执行。

4.编译器优化:编译器的优化功能可以自动地对程序进行优化,例如实施循环展开、代码重排、指令调度等。

在进行编译器优化时,需要根据具体的硬件平台和编译器选项做相应的调整。

最后,我们需要了解实施DSP程序优化的步骤。

一般来说,可以按照以下几个步骤来进行优化:1.分析和测量:首先需要对程序进行分析和测量,找出存在的性能瓶颈和资源占用问题。

可以通过使用性能分析工具、调试工具、模拟器等来获取运行时信息和性能指标。

DSP实验心得体会范文

DSP实验心得体会范文篇一:dp实验报告心得体会1.设置环境时分为软件设置和硬件设置,根据实验的需要设置,这次实验只是软件仿真,可以不设置硬件,但是要为日后的实验做准备,还是要学习和熟悉硬件设置的过程。

2.在设置硬件时,不是按实验书上的型号选择,而是应该按照实验设备上的型号去添加。

3.不管是硬件还是软件的设置,都应该将之前设置好的删去,重新添加。

设置好的配置中只能有一项。

可以工作在纯软件仿真环境中,就是由软件在pc 机内存中构造一个虚拟的dp环境,可以调试、运行程序。

但是一般无法构造dp中的外设,所以软件仿真通常用于调试纯软件算法和进行效率分析等。

5.这次实验采用软件仿真,不需要打开电源箱的电源。

6.在软件仿真工作时,无需连接板卡和仿真器等硬件。

7.执行write_buffer一行时。

如果按f10执行程序,则程序在mian 主函数中运行,如果按f11,则程序进入write_buffe函数内部的程序运行。

8.把tr变量加到观察窗口中,点击变量左边的“+”,观察窗口可以展开结构变量,就可以看到结构体变量中的每个元素了。

9.在实验时,显示图形出现问题,不能显示,后来在graphtitle把input的大写改为input,在对volume进行编译执行后,就可以看到显示的正弦波图形了。

10.在修改了实验2-1的程序后,要重新编译、连接执行程序,并且必须对.out文件进行重新加载,因为此时.out文件已经改变了。

如果不重新加载,那么修改执行程序后,其结果将不会改变。

11.再观察结果时,可将data和data1的窗口同时打开,这样可以便于比较,观察结果。

12.通过这次实验,对tm320f2812某dp软件仿真及调试有了初步的了解与认识,因为做实验的时候都是按照实验指导书按部就班的,与真正的理解和掌握还是有些距离的。

但是这也为我们日后运用这些知识打下了基础,我觉得实验中遇到的问题,不要急于问老师或者同学,先自己想办法分析原因,想办法解决,这样对自身的提高更多吧。

【推荐】dsp实验心得体会word版本 (8页)

本文部分内容来自网络整理,本司不为其真实性负责,如有异议或侵权请及时联系,本司将立即删除!== 本文为word格式,下载后可方便编辑和修改! ==dsp实验心得体会篇一:dsp 实验报告心得体会TMS320F2812x DSP原理及应用技术实验心得体会1. 设置环境时分为软件设置和硬件设置,根据实验的需要设置,这次实验只是软件仿真,可以不设置硬件,但是要为日后的实验做准备,还是要学习和熟悉硬件设置的过程。

2. 在设置硬件时,不是按实验书上的型号选择,而是应该按照实验设备上的型号去添加。

3. 不管是硬件还是软件的设置,都应该将之前设置好的删去,重新添加。

设置好的配置中只能有一项。

4. CCS可以工作在纯软件仿真环境中,就是由软件在PC机内存中构造一个虚拟的DSP环境,可以调试、运行程序。

但是一般无法构造DSP中的外设,所以软件仿真通常用于调试纯软件算法和进行效率分析等。

5. 这次实验采用软件仿真,不需要打开电源箱的电源。

6. 在软件仿真工作时,无需连接板卡和仿真器等硬件。

7. 执行write_buffer一行时。

如果按F10执行程序,则程序在mian主函数中运行,如果按F11,则程序进入write_buffe函数内部的程序运行。

8. 把str变量加到观察窗口中,点击变量左边的“+”,观察窗口可以展开结构变量,就可以看到结构体变量中的每个元素了。

9. 在实验时,显示图形出现问题,不能显示,后来在Graph Title 把Input 的大写改为input,在对volume进行编译执行后,就可以看到显示的正弦波图形了。

10. 在修改了实验2-1的程序后,要重新编译、连接执行程序,并且必须对.OUT文件进行重新加载,因为此时.OUT文件已经改变了。

如果不重新加载,那么修改执行程序后,其结果将不会改变。

11. 再观察结果时,可将data和data1的窗口同时打开,这样可以便于比较,观察结果。

12. 通过这次实验,对TMS320F2812x DSP软件仿真及调试有了初步的了解与认识,因为做实验的时候都是按照实验指导书按部就班的,与真正的理解和掌握还是有些距离的。

dsp优化心得

iPone的一句大家都耳熟能详的广告词:“一直被模仿,从未被超越”。

笔者认为主要是因为他们掌握着核心的算法和机器的优化策略。

因为一般的硬件我们都买的回来,但是能否将该硬件发挥到极致,就会公司之间的差别,因为同样的硬件,如果软件执行的速度不同,那结果就会有很大的差别,所以说:真正的技术是买不来的。

所以,我们进行嵌入式开发的时候,一旦选定了DSP6000系列的芯片,就不能把它当成单片机来用,必须发挥dsp与众不同,独一无二的性能。

也就是说如何调整c语言才能够适应这么强悍的硬件就是我们考虑的重点内容,即我们应该按照哪种既定的原则去编写C代码才能够让dsp真正作为dsp在工作,发挥到dsp 的优势。

dsp的优势在于:速度!所以,dsp的优化成为一门专业。

所以,我们一定要使自己在dsp上编写的c代码高效运行。

因为制约运行速度的因素是硬件和软件。

因为dsp一旦选定,硬件也就确定了。

所以,我们首先要注意如何提升软件的效率。

对于软件来说,一般情况下有3个优化等级。

第一:算法上优化。

第二:程序结构上的优化。

第三:汇编级的优化。

我们需要的是研究前两个等级的优化。

所以,在这篇文章中,我们需要研究的重点有两个:dsp的硬件结构和在dsp上如何优化c代码。

1.1 dsp的硬件结构关于dsp硬件结构的特色有几个:哈佛结构,流水线结构,带宽和运算方式的高效等。

1.1.1 哈佛结构哈佛结构的本质属性是数据存储器(RAM:存储数据的存储器)和程序存储器(存储指令)分开。

Cpu可以一边取指令,一边取数据。

这样会极大的提高处理的速度,因为以前是冯诺依曼结构,总线是分时复用的,这样会降低处理的速度。

而且,dsp6000系列是基于VLIW结构的,具体来讲就说CPU可以提取通过程序从程序存储器中一次提取256bit的指令,即CPU可以一次取8条指令放在处理中。

加上和8级流水线的配合,相当于8个传统的CPU一起工作。

1.1.2 流水线结构流水线结构涉及的CPU单元包括取指令单元(fetch),分配指令单元(dispatch)和执行指令单元(executive)。

dsp优化心得

dsp优化心得iPone的一句大家都耳熟能详的广告词:“一直被模仿,从未被超越”。

笔者认为主要是因为他们掌握着核心的算法和机器的优化策略。

因为一般的硬件我们都买的回来,但是能否将该硬件发挥到极致,就会公司之间的差别,因为同样的硬件,如果软件执行的速度不同,那结果就会有很大的差别,所以说:真正的技术是买不来的。

所以,我们进行嵌入式开发的时候,一旦选定了DSP6000系列的芯片,就不能把它当成单片机来用,必须发挥dp与众不同,独一无二的性能。

也就是说如何调整c语言才能够适应这么强悍的硬件就是我们考虑的重点内容,即我们应该按照哪种既定的原则去编写C代码才能够让dp真正作为dp在工作,发挥到dp的优势。

dp的优势在于:速度!所以,dp的优化成为一门专业。

所以,我们一定要使自己在dp上编写的c代码高效运行。

因为制约运行速度的因素是硬件和软件。

因为dp一旦选定,硬件也就确定了。

所以,我们首先要注意如何提升软件的效率。

对于软件来说,一般情况下有3个优化等级。

第一:算法上优化。

第二:程序结构上的优化。

第三:汇编级的优化。

我们需要的是研究前两个等级的优化。

所以,在这篇文章中,我们需要研究的重点有两个:dp的硬件结构和在dp上如何优化c代码。

1.1dp的硬件结构关于dp硬件结构的特色有几个:哈佛结构,流水线结构,带宽和运算方式的高效等。

1.1.1哈佛结构哈佛结构的本质属性是数据存储器(RAM:存储数据的存储器)和程序存储器(存储指令)分开。

Cpu可以一边取指令,一边取数据。

这样会极大的提高处理的速度,因为以前是冯诺依曼结构,总线是分时复用的,这样会降低处理的速度。

而且,dp6000系列是基于VLIW结构的,具体来讲就说CPU可以提取通过程序从程序存储器中一次提取256bit的指令,即CPU可以一次取8条指令放在处理中。

加上和8级流水线的配合,相当于8个传统的CPU一起工作。

1.1.2流水线结构流水线结构涉及的CPU单元包括取指令单元(fetch),分配指令单元(dipatch)和执行指令单元(e某ecutive)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

iPone 的一句大家都耳熟能详的广告词:“一直被模仿,从未被超越” 。

笔者认为主要是因为他们掌握着核心的算法和机器的优化策略。

因为一般的硬件我们都买的回来,但是能否将该硬件发挥到极致,就会公司之间的差别,因为同样的硬件,如果软件执行的速度不同,那结果就会有很大的差别,所以说:真正的技术是买不来的。

所以,我们进行嵌入式开发的时候,一旦选定了DSP6000系列的芯片,就不能把它当成单片机来用,必须发挥dsp 与众不同,独一无二的性能。

也就是说如何调整c 语言才能够适应这么强悍的硬件就是我们考虑的重点内容,即我们应该按照哪种既定的原则去编写C 代码才能够让dsp 真正作为dsp 在工作,发挥到dsp 的优势。

dsp 的优势在于:速度!所以,dsp 的优化成为一门专业。

所以,我们一定要使自己在dsp 上编写的c 代码高效运行。

因为制约运行速度的因素是硬件和软件。

因为dsp 一旦选定,硬件也就确定了。

所以,我们首先要注意如何提升软件的效率。

对于软件来说,一般情况下有3 个优化等级。

第一:算法上优化。

第二:程序结构上的优化。

第三:汇编级的优化。

我们需要的是研究前两个等级的优化。

所以,在这篇文章中,我们需要研究的重点有两个:dsp 的硬件结构和在dsp 上如何优化c 代码。

dsp 的硬件结构关于dsp 硬件结构的特色有几个:哈佛结构,流水线结构,带宽和运算方式的高效等。

1.1.1 哈佛结构哈佛结构的本质属性是数据存储器(RAM存储数据的存储器)和程序存储器(存储指令)分开。

Cpu可以一边取指令,一边取数据。

这样会极大的提高处理的速度,因为以前是冯诺依曼结构,总线是分时复用的,这样会降低处理的速度。

而且,dsp6000系列是基于VLIW结构的,具体来讲就说CPU可以提取通过程序从程序存储器中一次提取256bit的指令,即CPU可以一次取8条指令放在处理中。

加上和8级流水线的配合,相当于8个传统的CPU一起工作。

1.1.2 流水线结构流水线结构涉及的CPU 单元包括取指令单元(fetch ),分配指令单元(dispatch )和执行指令单元(executive )。

这3 个单元都是和程序存储器相关的,是处理指令的几个单元。

首先,程序总线可以一次从ROM中取到8条32位的指令,通俗点说,就说一次取了8条汇编语句。

然后经过取指令单元(4 个步骤,不详述),分配指令单元(2 个步骤),第一个为分配单元,作用是根据指令之间的相关性将这8 条指令再次分成不同大小的执行包,如果两条指令是没有相关的,就可以同时执行,不分先后顺序。

第二个为译码单元,即翻译成可以被执行单元处理的码。

执行指令单元(根据不同的指令分为5 个步骤)。

但8 条指令通过不是一次这4+2+5个步骤,而是在这9 个步骤中都有指令在同时工作。

例如第1个取值包在第1 个步骤,第2 个取值包就在第2 个步骤,第3 个取值包就在第3 个步骤,等等。

剩下要讨论的就说最关键的部分:执行指令单元。

执行指令单元有两个处理指令的通路,每个通路都有4个运算单元:L,S,D,M。

所以指令运算单元就有8个。

我们所说的8级流水线作业也就是因为执行单元有8 个运算单元。

以上就是软件流水线的硬件结构。

这就是最基础最最本质的硬件结构。

我们之后要做的所有的软件优化工作都将作用在这些硬件结构上。

但对于我们做优化来讲,我们不需要对硬件了解太深,但一定要了解软件流水线工作的硬件是如何工作的。

1.1.3 带宽优势和运算方式优势1.1.3.1 带宽优势DSP6000系列能够极大突破速度瓶颈的一个原因就是带宽和运算方式。

所谓带宽就是cpu 一次可以访问的数据量。

我们前面提过,指令就是操作码,和指令相关的单元就说取指令单元,分配指令单元和执行指令单元。

即这些单元就说和程序存储器ROM丁交道的单元。

我们在上面介绍了执行单元的8 个执行指令的运算单元。

但还有32数据通路,即在一个时钟周期内可以从数据存储器RAM中读取32bit的数据。

还有32个通用寄存器(也可以是16 个寄存器对)用来暂时存储操作数。

这些寄存器就是和数据存储器RAM 可接打交道的硬件结构。

这里所说的带宽就是我们在从RAM中读取数据的时候,要尽量利用数据通路的宽度,即我们在编写c代码的时候,一定要“想办法”使CPU^次可以读取32位数据到通用寄存器里面(c64 一次可以读取64 位数据到通用寄存器对里面),因为我们一般情况下处理的原始数据都不是很大,尤其是在图像处理的时候,我们一般情况下使用的是0-255(灰度图像)或0-1(二值图像)。

即使对这些数据做加减乘除运算,得到的结果也不会超过216。

所以,我们一般情况下可以用LDW从数据存储器RAM中读取两个16位的数据(即用short声明的数据)。

所以,一般情况下,我们用short来声明一个数组,然后用LDW来一次读取32位的数据到寄存器中。

这样,我们就可以尽量利用数据通路的宽度,这就是所谓的带宽优势。

1.1.3.2 运算方式优势所谓的运算就说8 个单元可以进行的操作码。

再说具体些就是:加法,减法,乘法,除法,移位,跳转,读取,存储等等。

一般情况下,我们在发挥DSP600C芯片带宽优势的同时要注意运算上的优势。

例如,我们一次可以读取两个16 位的数据放在一个32 位的通用寄存器里。

然后可以用一个双16*16 运算来处理这两个16 位的数据,即我们可以仅仅通过做一次运算就可以进行两个通用寄存器相乘(每个寄存器中的高16 位和低16 位存放的是独立的16 位数据,即两个通用寄存器中有4 个16 位数据),得到的结果就放在一个寄存器对里面。

(如A0:A1 组成的寄存器对,总长64 位,即第1 个结果放在A0里面,第2个结果放在A1里面)。

由于我们是在c 语言层次来讨论dsp 的优化,所以我们要在发挥带宽优势的时候使用内联函数。

因为我们一旦使用了字存取方式来处理数据,就必然会用到相关的内联函数,这两者是联系起来的。

这就是运算方式上的优势。

我们用数据相加来说明运算方式。

传统计算方式上,我们可以一次提取一个16 位数据(放在一个32 位的通用寄存器里),两次就提取两个16 位数据,然后使用一个加法运算,使两个寄存器相加,结果放在放在一个通用寄存器里。

这样一次运算可以使两个16 位的数相加。

如果我们在传统计算方式上进行优化的话,我们可以这样进行,首先使两个数组进行字对齐。

然后使用一个字读取的内联函数读取数据,这样可以一次读取两个16 位的数据放在一个寄存器里,两次就可以读取4 个16 位的数据,之后再使用一个可以进行双16 位数据加16 位数据的内联函数来处理这两个通用寄存器。

这样的话,我们就可以一次处理两个16 位数据和16 位数据的相加。

下面用汇编指令来说明,MPY酣以一次执行双16bit*16bit 的运算。

The following code:MPY A0, A1, A2MPYH A0, A1, A3may be replaced by:MPY2 A0, A1, A3:A2这就是所谓的运算方式上的优势。

一定要记得:带宽优势和运算方式优势是同时发挥的。

dsp 上如何优化 c 代码在C代码基础上进行优化的主要目的就是提高代码执行的速度。

主要策略就是向dsp6000系列的编译器传递一些优化的信息。

这些优化的信息被优化器理解后,就会使编译器将c 代码编译成这些优化信息对应的高效汇编指令,如使用LDW,MYPY等字读取,双16位*16位指令,字对齐,使指令并行执行等。

我们在实际工程应用中,主要针对的就说循环的优化,因为循环是影响执行指令速度的最关键因素。

我们只要优化了循环,就完成了dsp 的优化。

优化循环最大的效果就是使循环的每次迭代参加到流水线中。

下面我们来讨论优化循环的因素。

1.2.1 最重要的因素:循环次数对于一个循环而言,循环次数是最重要的因素,如果能在保证循环功能的情况下减少循环的话(如将16 位读取,16 位相加改称双16 位读取,双16 位相加),那么将极大的优化代码。

减少循环次数将最大限度的减少该循环的指令。

因为从本质上来说,循环次数越多,跳转的次数越多,这样的话CPI处理这些跳转指令的次数越多,负担肯定越大。

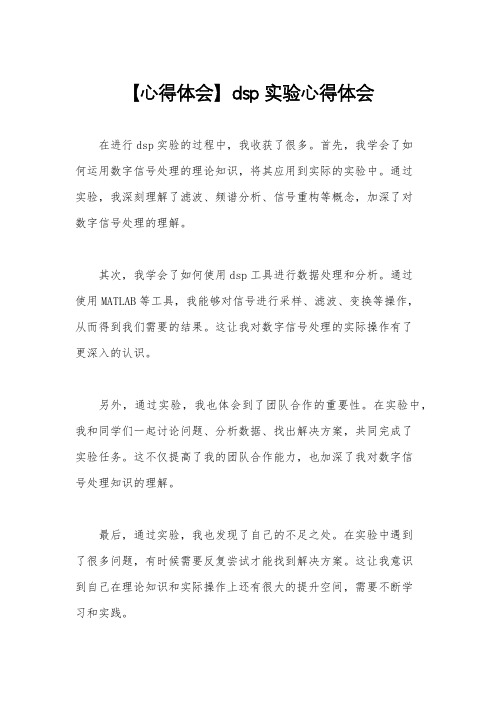

循环的汇编指令必须有下面两个指令(红色标记):LOOP:…循环体SUB BO,1,BOfor (i = 0: i < 40; i++){for (j = 0; j < 16;j++)sum += coefs[|] * inputfi + 15 - j];out[i] = (sum » 15);1.2.2}for (i = 0; i < 40; i+中){sum = coefsfO] * input[i -+ 1 5]; sum += coefs[1 ] * input[i + 14]; sum+= coefs[2] * input[i + 13]; sum += coefs[3] * inputfi + 12]; sum +=coefs[4] * input[i +11]; sum += coefs[5] * inputfi + 10];sum += coefs[6] * inpuifl + 9]:sum += coefs[7] “ input[i + 8];sum += coefs[8] * input[i + 7];sum += coefs[9] * inputfi + 6]; sum += ccets[10] * input[i + 5J; sum +=coefs[11 ] * input[i + 4]; sum += coefs[12] * inputfi + 3];sum += coefs[13] * i nput[i + 2];sum += coefs[14] * inputfi + 1];sum 十二coefs[1 5] * input[i + 0];out[i] = (sum >> 15); }units 00・*.S units2* 1・*.D units2* 2*・*.M units2* 2*・*.X cross paths11・*.T address paths2*2*・*Long read paths11・*Long write paths00・*Logical ops (.LS)11(.L or .S unit)・*Additi on ops (.LSD)01(丄 or .S or .Dunit)・*Bound(.L .S 丄S)2*1・*Bound(.L .S .D .LS LSD)2*2*以上是一个循环的资源分配表。

从上面可以看出:一个循环内D单元和M单元都用了两次,平衡了资源的分配。