DSP学习之前应该弄懂的问题

DSP学习笔记

一、如何开始DSP的学习以下为各网友学习DSP的一些经验fxw451:大家先大体上看一遍书,把大体的知识了解一下。

其次就是看例子了,例子是关键,例子里有你学的所有的东西,这次你再拿出一本书来看,这次是有针对性的看,比如你做的spi的,你就直接看spi那张,一边看例子一边看书,这样你就可以把一些重要的寄存器给记住了。

对于初学者来说,一直好奇的就是ccs的使用,拿我第一次使用ccs来说,当我把ccs 和板子连载一起时,我相当高兴,成功感油然升起,接下来就是用ccs里的看自带的例子了,看完后你就会发现,这些是什么东东哦,什么都不会,这就对了,你要是看一开始看会了你就是神仙了,dsp不像单片机那么容易上手,所以你要花费点功夫吃透它,好东西不是那么容易就可以搞定的。

到了自己编程的时候了,这个时候不要要求自己能编一个什么样的程序,你要仿着例子里的东西全部搞定就可以了,这就是你编程的第一步,当然也是成功的一步,在这成功下,我相信你的积极性肯定被调到起来,对dsp越来越热爱了。

suary:1)把存储器映射结构搞清楚----说的具体点就是dsp内到底有那些存储器(ram,rom,flash,etc),这些存储器到底是如何分配的,这个可以参考相关的.cmd文件的写法,它定义了存储器映射和输入输出段的位置2)编译器的堆栈操作---有关这点我还是没有具体弄清楚,就是中断或是子程序调用时,系统自己的堆栈操作。

2407有一个8级硬件堆栈,而2812没有,这个区别比较大,所以在编一边针对堆栈操作的程序(eg. rtos)时就要特别注意了。

3) 中断系统----每个mcu的中断系统搞清楚了,会给编程带来很大的便利,所以一定要对所用的mcu的中断过程了解的清清楚楚。

4)数据结构---设计好的,适合的数据结构会使自己的程序编写变得结构清楚而且“容易”。

dsp31:我的经验是:DSP不管是软件和硬件开发一定要多思考,多比较。

软件人员一定要会调试和定位硬件电路的问题点。

dsp知识点总结

dsp知识点总结一、DSP基础知识1. 信号的概念信号是指用来传输信息的载体,它可以是声音、图像、视频、数据等各种形式。

信号可以分为模拟信号和数字信号两种形式。

在DSP中,我们主要研究数字信号的处理方法。

2. 采样和量化采样是指将连续的模拟信号转换为离散的数字信号的过程。

量化是指将信号的幅度离散化为一系列离散的取值。

采样和量化是数字信号处理的基础,它们决定了数字信号的质量和准确度。

3. 傅里叶变换傅里叶变换是一种将时域信号转换为频域信号的方法,它可以将信号的频率分量分解出来,从而可以对信号进行频域分析和处理。

傅里叶变换在DSP中有着广泛的应用,比如滤波器设计、频谱分析等。

4. 信号处理系统信号处理系统是指用来处理信号的系统,它包括信号采集、滤波、变换、编解码、存储等各种功能。

DSP技术主要用于设计和实现各种类型的信号处理系统。

二、数字滤波技术1. FIR滤波器FIR滤波器是一种具有有限长冲激响应的滤波器,它的特点是结构简单、稳定性好、易于设计。

FIR滤波器在数字信号处理中有着广泛的应用,比如音频处理、图像处理等。

2. IIR滤波器IIR滤波器是一种具有无限长冲激响应的滤波器,它的特点是频率选择性好、相位延迟小。

IIR滤波器在数字信号处理中也有着重要的应用,比如通信系统、控制系统等。

3. 数字滤波器设计数字滤波器的设计是数字信号处理的重要内容之一,它包括频域设计、时域设计、优化设计等各种方法。

数字滤波器设计的目标是满足给定的频率响应要求,并且具有良好的稳定性和性能。

4. 自适应滤波自适应滤波是指根据输入信号的特性自动调整滤波器参数的一种方法,它可以有效地抑制噪声、增强信号等。

自适应滤波在通信系统、雷达系统等领域有着重要的应用。

三、数字信号处理技术1. 数字信号处理器数字信号处理器(DSP)是一种专门用于数字信号处理的特定硬件,它具有高速运算、低功耗、灵活性好等特点。

DSP广泛应用于通信、音频、图像等领域,是数字信号处理技术的核心。

dsp学习心得

dsp学习心得在过去的一段时间里,我深入研究了数字信号处理(DSP)的相关知识,并在实践中不断探索和应用。

通过这段学习过程,我不仅对DSP的概念有了更深刻的理解,而且积累了丰富的实际经验。

下面将分享我在学习DSP过程中的心得和体会。

一、了解DSP的基本概念在开始学习DSP之前,我首先对其基本概念进行了了解。

DSP,即数字信号处理,是一种通过对数字信号进行一系列算法处理来实现信号的转换、压缩、增强等目的的技术。

它在音频处理、图像处理、通信系统等领域起着重要的作用。

二、学习DSP的基础知识为了更好地掌握DSP技术,我系统地学习了相关的基础知识。

首先,我学习了数字信号的采样和量化原理,了解了数字信号与模拟信号的转换过程。

接着,我学习了常用的数字滤波器设计方法,包括FIR滤波器和IIR滤波器。

同时,我还学习了离散傅里叶变换(DFT)和快速傅里叶变换(FFT)等频域分析方法。

通过这些基础知识的学习,我对DSP的核心技术有了较为清晰的认识。

三、利用MATLAB进行DSP仿真实验为了更好地理解和应用DSP技术,我利用MATLAB进行了一系列的仿真实验。

我首先学习了MATLAB的基本语法和函数的使用方法,然后通过编写代码实现了常见的DSP算法。

例如,我通过MATLAB实现了数字滤波器的设计和应用,包括低通滤波器、高通滤波器和带通滤波器等。

此外,我还利用MATLAB进行了音频信号的压缩和解压缩实验,通过对信号的编码和解码,实现了对声音质量的有效控制。

四、应用DSP技术解决实际问题除了理论学习和仿真实验,我还将所学的DSP技术应用到了实际问题的解决中。

例如,在图像处理方面,我利用DSP技术实现了数字图像的去噪和增强。

通过选择合适的滤波器和处理算法,我成功地提高了图像的清晰度和质量。

在音频处理方面,我利用DSP技术对语音信号进行分析和识别,实现了自动语音识别的功能。

通过这些实际问题的解决,我深刻地体验到了DSP技术的强大和应用的广泛性。

DSP_入门教程

DSP_入门教程DSP(Digital Signal Processing)是数字信号处理的缩写,它是利用数字技术对信号进行处理的一种方法。

在现代工程中,DSP技术广泛应用于各种领域,如音频处理、图像处理、通信系统等。

下面将为大家介绍DSP的基本概念和入门教程。

首先,我们来了解一下什么是数字信号处理(DSP)。

数字信号是指连续信号经过采样和量化处理后得到的离散数值序列,而数字信号处理就是在这个离散序列上进行一系列数学运算和算法处理的过程。

DSP可以通过数字滤波、傅里叶变换、时域分析等方法对信号进行处理,使其具备滤波、降噪、压缩等功能。

要学习DSP,首先需要了解一些基本概念。

首先是采样和量化。

采样是指将连续信号在时间上进行离散化,即以一定的时间间隔对信号进行观测,得到一系列的采样值。

量化是指将采样得到的连续幅度值转换为离散幅度值的过程。

采样和量化是将连续信号转换为离散信号的关键步骤。

接下来是数字滤波。

数字滤波是指在离散时域或频域上进行滤波操作。

常见的数字滤波器有低通滤波器、高通滤波器、带通滤波器等。

数字滤波可以用于信号去噪、提取感兴趣的频率成分、改善信号质量等。

另外,我们还需要了解一些基本的数学运算和算法。

傅里叶变换是一种重要的信号处理方法,可以将时域信号转换为频域信号,从而分析信号的频谱特性。

在DSP中,快速傅里叶变换(FFT)是一种常用的算法,可用于高效计算傅里叶变换。

此外,数字信号处理还涉及到一些常见的算法,如卷积、相关、自相关、互相关等。

这些算法可以用于信号的滤波、特征提取、模式识别等任务。

要学习DSP,可以首先通过学习相关的数学知识打好基础。

掌握离散数学、线性代数、复变函数等基本概念,对于理解和应用DSP技术非常重要。

其次,可以学习一些基本的DSP算法和工具。

如学习使用MATLAB软件进行信号处理,掌握常用的DSP函数和工具箱,进行信号的滤波、频谱分析等操作。

另外,可以学习一些经典的DSP案例和应用。

DSP入门前的背景知识重点

DSP入门前的背景知识数字信号处理(DigitalSignal Processing,简称DSP)是一门涉及许多学科而又广泛应用于许多领域的新兴学科。

20世纪60年代以来,随着计算机和信息技术的飞速发展,数字信号处理技术应运而生并得到迅速的发展。

在过去的二十多年时间里,数字信号处理已经在通信等领域得到极为广泛的应用。

数字信号处理是利用计算机或专用处理设备,以数字形式对信号进行采集、变换、滤波、估值、增强、压缩、识别等处理,以得到符合人们需要的信号形式。

数字信号处理是围绕着数字信号处理的理论、实现和应用等几个方面发展起来的。

数字信号处理在理论上的发展推动了数字信号处理应用的发展。

反过来,数字信号处理的应用又促进了数字信号处理理论的提高。

而数字信号处理的实现则是理论和应用之间的桥梁。

数字信号处理是以众多学科为理论基础的,它所涉及的范围极其广泛。

例如,在数学领域,微积分、概率统计、随机过程、数值分析等都是数字信号处理的基本工具,与网络理论、信号与系统、控制论、通信理论、故障诊断等也密切相关。

近来新兴的一些学科,如人工智能、模式识别、神经网络等,都与数字信号处理密不可分。

可以说,数字信号处理是把许多经典的理论体系作为自己的理论基础,同时又使自己成为一系列新兴学科的理论基础。

数字信号处理的实现方法一般有以下几种:(1) 在通用的计算机(如PC机)上用软件(如Fortran、C语言)实现;(2) 在通用计算机系统中加上专用的加速处理机实现;(3) 用通用的单片机(如MCS-51、96系列等)实现,这种方法可用于一些不太复杂的数字信号处理,如数字控制等;(4) 用通用的可编程DSP芯片实现。

与单片机相比,DSP芯片具有更加适合于数字信号处理的软件和硬件资源,可用于复杂的数字信号处理算法;(5) 用专用的DSP芯片实现。

在一些特殊的场合,要求的信号处理速度极高,用通用DSP芯片很难实现,例如专用于 FFT、数字滤波、卷积、相关等算法的DSP芯片,这种芯片将相应的信号处理算法在芯片内部用硬件实现,无需进行编程。

DSP(知识点+思考题)

DSP复习要点第一章绪论1、数的定标:Qn表示。

例如:16进制数2000H=8192,用Q0表示16进制数2000H=0.25,用Q15表示2、‟C54x小数的表示方法:采用2的补码小数;.word 32768 *707/10003、定点算术运算:乘法:解决冗余符号位的办法是在程序中设定状态寄存器STl中的FRCT位为1,让相乘的结果自动左移1位。

第二章CPU结构和存储器设置一、思考题:1、C54x DSP的总线结构有哪些特点?答:TMS320C54x的结构是围绕8组16bit总线建立的。

(1)、一组程序总线(PB):传送从程序存储器的指令代码和立即数。

(2)、三组数据总线(CB,DB和EB):连接各种元器件,(3)、四组地址总线(PAB,CAB,DAB和EAB)传送执行指令所需要的地址。

2、C54x DSP的CPU包括哪些单元?答:'C54X 芯片的CPU包括:(1)、40bit的算术逻辑单元(2)、累加器A和B(3)、桶形移位寄存器(4)、乘法器/加法器单元(5)、比较选择和存储单元(6)、指数编码器(7)、CPU状态和控制寄存器(8)、寻址单元。

1)、累加器A和B分为三部分:保护位、高位字、地位字。

保护位保存多余高位,防止溢出。

2)、桶形移位寄存器:将输入数据进行0~31bits的左移(正值)和0~15bits的右移(负值)3)、乘法器/加法器单元:能够在一个周期内完成一次17*17bit的乘法和一次40位的加法4)、比较选择和存储单元:用维比特算法设计的进行加法/比较/选择运算。

5)、CPU状态和控制寄存器:状态寄存器ST0和ST1,由置位指令SSBX和复位指令RSBX控制、处理器模式状态寄存器PMST2-3、简述’C54x DSP的ST1,ST0,PMST的主要功能。

答:’C54x DSP的ST1,ST0,PMST的主要功能是用于设置和查看CPU的工作状态。

•ST0主要反映处理器的寻址要求和计算机的运行状态。

dsp入门需要注意的事项

dsp入门需要注意的事项在作硬件之前,需要看的资料有:1.芯片数据手册,描述该器件的引脚信号、片上资源、电气指标和机械特性(如封装等),在做硬件前必看(TMS320F281x数据手册SPRS174J)2.某一系列DSP的CPU和指令集用户指南,描述该系列DSP的CPU结构、内部寄存器、寻址方式等(TMS320F28x系列DSP的CPU和指令集用户指南SPRU430D)3.某一系列DSP片上外设用户指南,一般有很多本,用什么外设看相应的用户指南即可。

在作软件之前,需要看的资料有:1. 汇编语言工具(TMS320F28x Assembly Language Tools User’s Guide,SPRU513),描述汇编语言的基本格式、汇编器伪指令、汇编器参数、链接器和其他实用程序等,在做汇编程序开发前,首先看明白该书的第二章(描述Coff 格式,是汇编语言的基础),该书的其他内容,可以在使用中再来查阅。

2.汇编指令集(TMS320F28x DSP CPU and Instruction Set Reference Guide (Rev.D),SPRU430D),在做汇编程序前,首先要看明白寻址方式(第5章,C28xAddressing Modes),具体的指令(第6章,C28x Assembly LanguageInstructions)在编程时查阅。

3.优化C编译器(TMS320F28x Optimizing C/C++ Compiler User’s Guide,SPRU514),在做C程序前,首先要看明白C的运行环境(第7章,run-time environment),其他内容编程时查阅。

4.更高级的编程方法,还有很多资料,如DSP/BIOS、函数库等,均有相应的优化指南,用到时再去查看。

调试时,需要看的资料有:1.Code Composer Studio Getting Started Guide (Rev. D)2.Code Composer Studio User's Guide (Rev. B)转载请注明出自DSP交流网 DSP学习第一论坛 DSP技术应用与推广平台 DSP开发服务平台 /bbs/,本贴地址:/bbs /viewthread.php?tid=82111.关闭DSP--blog's Blog高速数字信号处理器是当前信息产业的热点技术之一,采用最先进的DSP无疑会使所开发的产品具有更强的市场竞争力。

DSP入门必看(非常好的DSP扫盲文章)

DSP入门必看(非常好的DSP扫盲文章)(ZZ)(7)如何设置硬件断点?在profiler ->profile point -> break pointc54x的外部中断是电平响应还是沿响应?是沿响应,准确的说,它要检测到100(一个clk的高和两个clk的低)的变化才可以。

参考程序,里面好象都要dISAble wachdog,不知道为什么?watchdog是一个计数器,溢出时会复位你的DSP,不dISAble的话,你的系统会动不动就reset。

时钟电路选择原则1,系统中要求多个不同频率的时钟信号时,首选可编程时钟芯片;2,单一时钟信号时,选择晶体时钟电路;3,多个同频时钟信号时,选择晶振;4,尽量使用DSP片内的PLL,降低片外时钟频率,提高系统的稳定性;5,C6000、C5510、C5409A、C5416、C5420、C5421和C5441等DSP片内无振荡电路,不能用晶体时钟电路;6,VC5401、VC5402、VC5409和F281x等DSP时钟信号的电平为1.8V,建议采用晶体时钟电路C程序的代码和数据如何定位1,系统定义:.cinit 存放C程序中的变量初值和常量;.const 存放C程序中的字符常量、浮点常量和用const声明的常量;.switch 存放C程序中switch语句的跳针表;.text 存放C程序的代码;.bss 为C程序中的全局和静态变量保留存储空间;.far 为C程序中用far声明的全局和静态变量保留空间;.stack 为C程序系统堆栈保留存储空间,用于保存返回地址、函数间的参数传递、存储局部变量和保存中间结果;.sysmem 用于C程序中malloc、calloc和realloc函数动态分配存储空间2,用户定义:#pragma CODE_SECTION (symbol, "section name");#pragma DATA_SECTION (symbol, "section name")cmd文件由3部分组成:1)输入/输出定义:.obj文件:链接器要链接的目标文件;.lib文件:链接器要链接的库文件;.map文件:链接器生成的交叉索引文件;.out文件:链接器生成的可执行代码;链接器选项2)MEMORY命令:描述系统实际的硬件资源3)SECTIONS命令:描述“段”如何定位为什么要设计CSL?1,DSP片上外设种类及其应用日趋复杂2,提供一组标准的方法用于访问和控制片上外设3,免除用户编写配置和控制片上外设所必需的定义和代码什么是CSL?1,用于配置、控制和管理DSP数字信号处理片上外设2,已为C6000和C5000系列DSP设计了各自的CSL库3,CSL库函数大多数是用C语言编写的,并已对代码的大小和速度进行了优化4,CSL库是可裁剪的:即只有被使用的CSL模块才会包含进应用程序中5,CSL库是可扩展的:每个片上外设的API相互独立,增加新的API,对其他片上外设没有影响CSL的特点1,片上外设编程的标准协议:定义一组标准的APIs:函数、数据类型、宏;2,对硬件进行抽象,提取符号化的片上外设描述:定义一组宏,用于访问和建立寄存器及其域值3,基本的资源管理:对多资源的片上外设进行管理;4,已集成到DSP/BIOS中:通过图形用户接口GUI对CSL进行配置;5,使片上外设容易使用:缩短开发时间,增加可移植.为什么需要电平变换?1) DSP系统中难免存在5V/3.3V混合供电现象;2)I/O为3.3V供电的DSP,其输入信号电平不允许超过电源电压3.3V;3)5V器件输出信号高电平可达4.4V;4)长时间超常工作会损坏DSP器件;5)输出信号电平一般无需变换电平变换的方法1,总线收发器(Bus Transceiver):常用器件:SN74LVTH245A(8位)、SN74LVTH16245A(16位)特点:3.3V供电,需进行方向控制,延迟:3.5ns,驱动:-32/64mA,输入容限:5V应用:数据、地址和控制总线的驱动2,总线开关(Bus Switch)常用器件:SN74CBTD3384(10位)、SN74CBTD16210(20位)特点:5V供电,无需方向控制延迟:0.25ns,驱动能力不增加应用:适用于信号方向灵活、且负载单一的应用,如McBSP等外设信号的电平变换3,2选1切换器(1 of 2 Multiplexer)常用器件:SN74CBT3257(4位)、SN74CBT16292(12位)特点:实现2选1,5V供电,无需方向控制延迟:0.25ns,驱动能力不增加应用:适用于多路切换信号、且要进行电平变换的应用,如双路复用的McBSP4,CPLD3.3V供电,但输入容限为5V,并且延迟较大:>7ns,适用于少量的对延迟要求不高的输入信号5,电阻分压10KΩ和20KΩ串联分压,5V×20÷(10+20)≈3.3V未用的输入/输出引脚的处理1,未用的输入引脚不能悬空不接,而应将它们上拉活下拉为固定的电平1)关键的控制输入引脚,如Ready、Hold等,应固定接为适当的状态,Ready引脚应固定接为有效状态,Hold引脚应固定接为无效状态2)无连接(NC)和保留(RSV)引脚,NC 引脚:除非特殊说明,这些引脚悬空不接,RSV引脚:应根据数据手册具体决定接还是不接3)非关键的输入引脚,将它们上拉或下拉为固定的电平,以降低功耗2,未用的输出引脚可以悬空不接3,未用的I/O引脚:如果确省状态为输入引脚,则作为非关键的输入引脚处理,上拉或下拉为固定的电平;如果确省状态为输出引脚,则可以悬空不接。

做DSP之前我们该弄明白那些基本问题

做DSP之前我们该弄明白那些基本问题1一、时钟和电源问:DSP的电源设计和时钟设计应该特别注意哪些方面?外接晶振选用有源的好还是无源的好?答:时钟一般使用晶体,电源可用TI的配套电源。

外接晶振用无源的好。

问:TMS320LF2407的A/D转换精度保证措施。

答:参考电源和模拟电源要求干净。

问:系统调试时发现纹波太大,主要是哪方面的问题?答:如果是电源纹波大,加大电容滤波。

问:请问我用5V供电的有源晶振为DSP提供时钟,是否可以将其用两个电阻进行分压后再接到DSP 的时钟输入端,这样做的话,时钟工作是否稳定?答:这样做不好,建议使用晶体。

问:一个多DSP电路板的时钟,如何选择比较好?DSP电路板的硬件设计和系统调试时的时序问题?答:建议使用时钟芯片,以保证同步。

硬件设计要根据DSP芯片的时序,选择外围芯片,根据时序设定等待和硬件逻辑。

二.干扰与板的布局问:器件布局应重点考虑哪些因素?例如在集中抄表系统中?答:可用TMS320VC5402,成本不是很高。

器件布局重点应是存贮器与DSP的接口。

问:在设计DSP的PCB板时应注意哪些问题?答:1.电源的布置;2.时钟的布置;3.电容的布置;4.终端电路;5.数字同模拟的布置。

问:请问DSP在与前向通道(比如说AD)接口的时候,布线过程中要注意哪些问题,以保证AD采样的稳定性?答:模拟地和数字地分开,但在一点接地。

问:DSP主板设计的一般步骤是什么?需要特别注意的问题有哪些?答:1.选择芯片;2.设计时序;3.设计PCB。

最重要的是时序和布线。

问:在硬件设计阶段如何消除信号干扰(包括模拟信号及高频信号)?应该从那些方面着手?答:1.模拟和数字分开;2.多层板;3.电容滤波。

问:在电路板的设计上,如何很好的解决静电干扰问题。

答:一般情况下,机壳接大地,即能满足要求。

特殊情况下,电源输入、数字量输入串接专用的防静电器件。

问:DSP板的电磁兼容(EMC)设计应特别注意哪些问题?答:正确处理电源、地平面,高速的、关键的信号在源端串接端接电阻,避免信号反射。

DSP开发入门基础知识

DSP开发入门基础知识发布日期:2009-3-6 11:12:07 文章来源:搜电浏览次数:111DSP是Digital Signal Processing(数字信号处理)或Digital Signal Processor(数字信号处理器)的缩写。

这一章中我们要讲的内容是,如何开始采用一个或多个数字信号处理芯片对输入信号(数字信号)进行分析、处理。

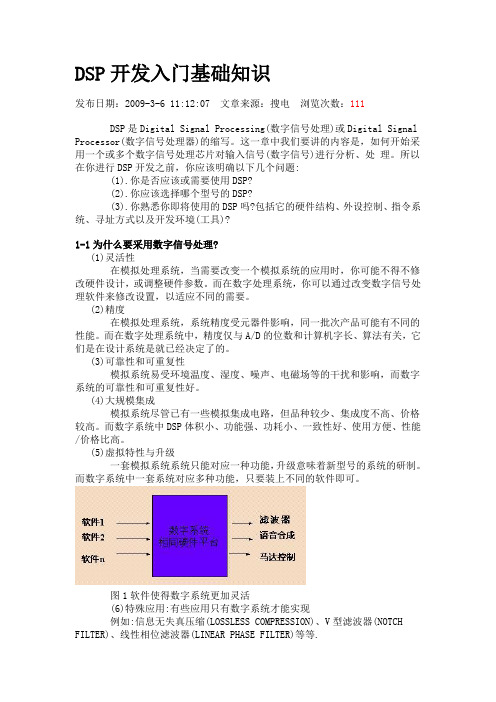

所以在你进行DSP开发之前,你应该明确以下几个问题:(1).你是否应该或需要使用DSP?(2).你应该选择哪个型号的DSP?(3).你熟悉你即将使用的DSP吗?包括它的硬件结构、外设控制、指令系统、寻址方式以及开发环境(工具)?1-1为什么要采用数字信号处理?(1)灵活性在模拟处理系统,当需要改变一个模拟系统的应用时,你可能不得不修改硬件设计,或调整硬件参数。

而在数字处理系统,你可以通过改变数字信号处理软件来修改设置,以适应不同的需要。

(2)精度在模拟处理系统,系统精度受元器件影响,同一批次产品可能有不同的性能。

而在数字处理系统中,精度仅与A/D的位数和计算机字长、算法有关,它们是在设计系统是就已经决定了的。

(3)可靠性和可重复性模拟系统易受环境温度、湿度、噪声、电磁场等的干扰和影响,而数字系统的可靠性和可重复性好。

(4)大规模集成模拟系统尽管已有一些模拟集成电路,但品种较少、集成度不高、价格较高。

而数字系统中DSP体积小、功能强、功耗小、一致性好、使用方便、性能/价格比高。

(5)虚拟特性与升级一套模拟系统系统只能对应一种功能,升级意味着新型号的系统的研制。

而数字系统中一套系统对应多种功能,只要装上不同的软件即可。

图1软件使得数字系统更加灵活(6)特殊应用:有些应用只有数字系统才能实现例如:信息无失真压缩(LOSSLESS COMPRESSION)、V型滤波器(NOTCH FILTER)、线性相位滤波器(LINEAR PHASE FILTER)等等.但数字信号处理也有局限性:(1) 实时性模拟系统中除开电路引入的延时外,处理是实时的。

DSP开发100问

DSP开发100问(转)一、时钟和电源问:DSP的电源设计和时钟设计应该特别注意哪些方面?外接晶振选用有源的好还是无源的好?答:时钟一般使用晶体,电源可用TI的配套电源。

外接晶振用无源的好。

问:TMS320LF2407的A/D转换精度保证措施。

答:参考电源和模拟电源要求干净。

问:系统调试时发现纹波太大,主要是哪方面的问题?答:如果是电源纹波大,加大电容滤波。

问:请问我用5V供电的有源晶振为DSP提供时钟,是否可以将其用两个电阻进行分压后再接到DSP的时钟输入端,这样做的话,时钟工作是否稳定?答:这样做不好,建议使用晶体。

问:一个多DSP电路板的时钟,如何选择比较好?DSP电路板的硬件设计和系统调试时的时序问题?答:建议使用时钟芯片,以保证同步。

硬件设计要根据DSP芯片的时序,选择外围芯片,根据时序设定等待和硬件逻辑。

二.干扰与板的布局问:器件布局应重点考虑哪些因素?例如在集中抄表系统中?答:可用TMS320VC5402,成本不是很高。

器件布局重点应是存贮器与DSP的接口。

问:在设计DSP的PCB板时应注意哪些问题?答:1.电源的布置;2.时钟的布置;3.电容的布置;4.终端电路;5.数字同模拟的布置。

问:请问DSP在与前向通道(比如说AD)接口的时候,布线过程中要注意哪些问题,以保证AD采样的稳定性?答:模拟地和数字地分开,但在一点接地。

问:DSP主板设计的一般步骤是什么?需要特别注意的问题有哪些?答:1.选择芯片;2.设计时序;3.设计PCB。

最重要的是时序和布线。

问:在硬件设计阶段如何消除信号干扰(包括模拟信号及高频信号)?应该从那些方面着手?答:1.模拟和数字分开;2.多层板;3.电容滤波。

问:在电路板的设计上,如何很好的解决静电干扰问题。

答:一般情况下,机壳接大地,即能满足要求。

特殊情况下,电源输入、数字量输入串接专用的防静电器件。

问:DSP板的电磁兼容(EMC)设计应特别注意哪些问题?答:正确处理电源、地平面,高速的、关键的信号在源端串接端接电阻,避免信号反射。

初学DSP,你得知道的那些事儿

初学DSP,你得知道的那些事儿DSP是嵌入式开发处理器的三大巨头之一,很多刚刚接触DSP的朋友大都会有这些疑问,为什么要用DSP?DSP是什么、能干嘛?有没有前途,或者有没有“钱途”?好不好学?该怎么学?今天就和大家聊下学习DSP得知道的那些事儿。

一、为什么要用DSP?3G通信技术的发展,要求处理器的速度越来越高,体积越来越小,MCU的速度较慢;CPU体积大、功耗高;嵌入CPU的成本较高。

DSP的发展正好能满足这一发展的要求,使其在许多速度要求较高、算法较复杂的场合取代MCU或其它处理器,而且综合成本有可能更低。

二、DSP是什么、能干嘛?想了解这些,就得一个概念讲起,DSP首先是Digital Signal Processing(数字信号处理),然后才是Digital Singnal Processor(数字信号处理器)。

具体关于DSP的介绍,请参考小弟的《三国杀之FPGA与ASIC、DSP全面大比拼!》,你能找到你想要的知识,也能找到学习DSP的动力。

三、DSP有没有前途(“钱途”)?很多人都觉得做技术就是苦逼,哪来的什么前途,一定要转做技术管理或销售。

以前我也这般认为,但现在越来越多的事实证明,这就是一个谬论,DSP相当有钱途!举两个例子:其一,某位DSP的资深AE,可以算是中国区该领域的专家,年薪不菲(60万以上),走遍世界,工作也很轻松;其二,某知名电信公司晋升年限一样的技术专家比同级的经理薪酬要高,如Expert(专家级)与管理大概50个人的经理相比,前者的薪酬要更高。

肯定有人说哪这么多高端人士,大家都是正常人类。

好吧,那来个正常的数据,京沪深的DSP工程师起薪基本上是10K/月,就是1万现大洋,满意了吧。

四、DSP好不好学?不管你喜不喜欢,学习DSP就必须得面对她:算法。

算法是DSP 的精华,可以说摆平了算法就搞定了80%,如果你又懂单片机编程,那么恭喜你有成为DSP专家的潜力。

肯定有童鞋问算法到底好不好学呢?算法,听上去是很高深的东西,但其原理也不过就是一些加减乘而已,连除都很少。

DSP系统设计100问

一、时钟和电源问:DSP的电源设计和时钟设计应该特别注意哪些方面?外接晶振选用有源的好还是无源的好?答:时钟一般使用晶体,电源可用TI的配套电源。外接晶振用无源的好。问:TMS320LF2407的A/D转换精度保证措施。答:参考电源和模拟电源要求干净。问:系统调试时发现纹波太大,主要是哪方面的问题?答:如果是电源纹波大,加大电容滤波。问:请问我用5V供电的有源晶振为DSP提供时钟,是否可以将其用两个电阻进行分压后再接到DSP的时钟输入端,这样做的话,时钟工作是否稳定?答:这样做不好,建议使用晶体。问:一个多DSP电路板的时钟,如何选择比较好?DSP电路板的硬件设计和系统调试时的时序问题?答:建议使用时钟芯片,以保证同步。硬件设计要根据DSP芯片的时序,选择外围芯片,根据时序设定等待和硬件逻辑。二.干扰与板的布局问:器件布局应重点考虑哪些因素?例如在集中抄表系统中?答:可用TMS320VC5402,成本不是很高。器件布局重点应是存贮器与DSP的接口。问:在设计DSP的PCB板时应注意哪些问题?答:1.电源的布置;2.时钟的布置;3.电容的布置;4.终端电路;5.数字同模拟的布置。问:请问DSP在与前向通道(比如说AD)接口的时候,布线过程中要注意哪些问题,以保证AD采样的稳定性?答:模拟地和数字地分开,但在一点接地。问:DSP主板设计的一般步骤是什么?需要特别注意的问题有哪些?答:1.选择芯片;2.设计时序;3.设计PCB。最重要的是时序和布线。问:在硬件设计阶段如何消除信号干扰(包括模拟信号及高频信号)?应该从那些方面着手?答:1.模拟和数字分开;2.多层板;3.电容滤波。问:在电路板的设计上,如何很好的解决静电干扰问题。答:一般情况下,机壳接大地,即能满足要求。特殊情况下,电源输入、数字量输入串接专用的防静器件。问:DSP板的电磁兼容(EMC)设计应特别注意哪些问题?答:正确处理电源、地平面,高速的、关键的信号在源端串接端接电阻,避免信号反射。问:用电感来隔离模拟电源和数字电源,其电感量如何决定?是由供电电流或噪音要求来决定吗?有没有计算公式?答:电感或磁珠相当于一个低通滤波器,直流电源可以通过,而高频噪声被滤除。所以电感的选择主要决定于电源中高频噪声的成分。问:讲座上的材料多是电源干扰问题,能否介绍板上高频信号布局(Layout)时要注意的问题以及数字信号对模拟信号的影响问题?答:数字信号对模拟信号的干扰主要是串扰,在布局时模拟器件应尽量远离高速数字器件,高速数字信号尽量远离模拟部分,并且应保证它们不穿越模拟地平面。问:能否介绍PCB布线对模拟信号失真和串音的影响,如何降低和克服?答:有2个方面,1. 模拟信号与模拟信号之间的干扰:布线时模拟信号尽量走粗一些,如果有条件,2个模拟信号之间用地线间隔。2. 数字信号对模拟信号的干扰:数字信号尽量远离模拟信号,数字信号不能穿越模拟地。

DSP重点知识点总结

DSP重点知识点总结DSP(数字信号处理)是一门涉及数字信号获取、处理和分析的学科。

DSP技术被广泛应用于通信、音频和视频处理、雷达和图像处理等领域。

下面是DSP的重点知识点总结。

1.信号与系统理论:信号可以理解为一种函数或者波形,可以用数学模型表示。

系统是根据输入信号产生输出信号的过程。

信号与系统理论研究信号和系统之间的关系,如卷积、频谱分析等。

2.时域和频域分析:时域分析是指对信号在时间上的特征进行分析,如幅度、相位、周期等。

频域分析则是将信号在频率上进行分析,如频谱、谐波成分等。

3.Z变换和离散时间系统:Z变换是一种离散信号处理的分析工具,它可以将离散时间信号转换成复变量的函数。

离散时间系统是一种对离散时间信号进行处理的系统,可以用系统函数来描述其输入输出关系。

4.数字滤波器设计:数字滤波器是一种对数字信号进行滤波处理的系统。

低通滤波器可以通过去除高频成分来平滑信号,高通滤波器则可以去除低频成分,带通滤波器可以只保留一些频段的信号。

5.快速傅里叶变换(FFT):FFT是一种将时域信号转换成频域信号的算法,它可以高效地计算信号的频谱。

FFT广泛应用于频谱分析、滤波器设计、信号压缩等领域。

6.语音信号处理:语音信号处理是DSP的一个重要应用领域。

它包括语音信号的获取、去噪、压缩、识别等技术。

常用的算法包括线性预测编码(LPC)、梅尔倒谱系数(MFCC)等。

7.图像处理:图像处理是DSP的另一个重要应用领域。

它包括图像的获取、增强、压缩、分割、识别等技术。

常用的算法包括离散余弦变换(DCT)、小波变换等。

8.数字信号处理芯片:数字信号处理芯片是一种集成了数字信号处理功能的专用芯片。

它可以高效地进行信号处理和计算,并广泛应用于通信设备、音频设备等领域。

9.数字信号处理应用:DSP技术在通信、音频、视频、雷达、图像等领域有广泛的应用。

例如,DSP可以用于音频信号的压缩、通信系统的调制解调、雷达信号的处理等。

DSP问答汇总

DSP问答汇总DSP问答汇总一、仿真器问题1、TI公司的仿真器同SEED仿真器的区别?1)SEED-XDS同TI的XDS-510完全兼容,可以完全替代XDS-510。

2)SEED-XDSPP同TI的XDS-510PP完全兼容,可以完全替代XDS-510PP。

3)SEED-XDSUSB和SEED-XDSPCI是合众达独创的产品,它们具有SEED-XDS的全部功能,更加便于使用。

4)SEED仿真器的JTAG/MPSD仿真电缆不同于TI,无需另外投资,可以方便更换。

5)SEED的仿真器同TI的仿真器一样,可以仿真所有TI的DSP和ARM。

2、DSP仿真器为什么必须连接目标系统(Target)?DSP的仿真器同单片机的不同,仿真器中没有DSP,提供IEEE标准的JTAG口对DSP进行仿真调试,所以仿真器必须有仿真对象,及目标系统。

目标系统就是你的产品,上面必须有DSP。

仿真器提供JTAG 同目标系统的DSP相接,通过DSP实现对整个目标系统的调试。

3、SEED-XDS仿真器安装的常见问题?请认真阅读“安装手册”。

常见问题是硬件的I/O口地址同主机的声卡或网卡有冲突,你可以改变仿真器的I/O口地址,也可以改变声卡或网卡的I/O口地址仿真工作正常对于DSP的基本要求1)DSP电源和地连接正确。

2)DSP时钟正确。

3)DSP的主要控制信号,如RS和HOLD信号接高电平。

4)C2000的watchdog关掉。

5)不可屏蔽中断NMI上拉高电平。

4、CCS或Emurst运行时提示“Can't Initialize Target DSP”1)仿真器连接是否正常?2)仿真器的I/O设置是否正确?3)XDSPP仿真器的电源是否正确?4)目标系统是否正确?5)仿真器是否正常?6)DSP工作的基本条件是否具备。

建议使用目标板测试。

5、为什么CCS需要安装Driver?CCS是开放的软件平台,它可以支持不同的硬件接口,因此不同的硬件接口必须通过标准的Driver 同CCS连接。

dsp最应弄懂的57个问题

dsp最应弄懂的57个问题二十.什么是boot loader?DSP的速度尽快,EPROM或flash的速度较慢,而DSP片内的RAM很快,片外的RAM也较快。

为了使DSP充分发挥它的能力,必须将程序代码放在RAM中运行。

为了方便的将代码从ROM中搬到RAM中,在不带flash的DSP中,TI在出厂时固化了一段程序,在上电后完成从ROM或外设将代码搬到用户指定的RAM中。

此段程序称为"boot loader"。

二十一.TMS320C3x如何boot?在MC/MP管脚为高时,C3x进入boot状态。

C3x的boot loader在reset时,判断外部中断管脚的电平。

根据中断配置决定boot的方式为存储器加载还是串口加载,其中ROM的地址可以为三个中的一个,ROM可以为8位。

二十二.Boot有问题如何解决?1)仔细检查boot的控制字是否正确。

2)仔细检查外部管脚设置是否正确。

3)仔细检查hex文件是否转换正确。

4)用仿真器跟踪boot过程,分析错误原因。

三十三.对于C5000,大于48K的程序如何BOOT?对于C5000,片内的BOOT程序在上电后将数据区的内容,搬移到程序区的RAM中,因此FLASH必须在RESET后放在数据区。

由于C5000,数据区的空间有限,一次BOOT的程序不能对于48K。

解决的方法如下:1.在RESET后,将FLASH译码在数据区,RAM放在程序区,片内BOOT程序将程序BOOT 到RAM中。

2.用户初试化程序发出一个I/O命令(如XF),将FLASH译码到程序区的高地址。

开放数据区用于其它的RAM。

3.用户初试化程序中包括第二次BOOT程序(此程序必须用户自己编写),将FLASH中没有BOOT的其它代码搬移到RAM中。

二.DSP的C语言同主机C语言的主要区别?1)DSP的C语言是标准的ANSI C,它不包括同外设联系的扩展部分,如屏幕绘图等。

但在CCS中,为了方便调试,可以将数据通过prinf命令虚拟输出到主机的屏幕上。

做DSP最应该懂的57个问题

几个DSP高手的经验介绍,编写基于DSP程序的注意事项[zt]一. 我是已经从事DSP开发有几年了,看到许多朋友对DSP的开发非常感兴取,我结合这几年对DSP 的开发写一写自己的感受,一家之言,欢迎指教。

我上研究生的第一天起根据老板的安排就开始接触DSP,那时DSP开发在国内高校刚刚开始,一台DSP开发器接近一万还是ISA总线的,我从206开始240、2407A都作过产品,对5402、2812、5471在产品方案规划制定和论证时也研究过。

由于方向所限对6X、8X系列没有接触。

我发现在国内无论在公司或高校许多地方为了加快开发周期往往把一个产品开发分为硬件和软件两个相对独立部分,由不同的人完成。

这在具有一定技术和管理基础的公司,由总设计师统一规划协调,分任务并行完成的情况下是可行的,也是符合现代产品开发规律的。

但是在高校人员的流动很大,研究生的有效科研时间很短、基础差(许多研究生起步时对电熔、电阻、三极管的分类和选型都很困难,我也是这样过来的)更不用说系统规划设计了,况且许多老板自己也不太懂,师兄有自己的任务,他们搞明白时也毕业了。

在许多高校做DSP就是找一个算法加到自己的主程序里,在板子上跑一下,基本达到效果就可以了,至于可靠性是次要的,产业化无从谈起,这已经算不错的了。

其实我觉得一个系统的完成,系统的规划是最重要的,在规划时对硬件设计的知识和认识是决定性的,它可以让你知道什么是可行的,什么是不可行的,当你同时具有软件设计能力时,就可以合理的分配系统功能,完成使用VHDL进行系统行为描述-—系统功能划分——系统子结构设计这样的自顶向下的设计规划流程,成为系统设计专家、项目经理,否则只是硬件工程师、软件工程师。

无论作51、196、还是DSP 都是这样。

下面分别谈谈我对硬件和软件设计的感受硬件设计是系统设计的关键,国内和国外产品的差距往往是硬件设计水平高低决定的,任何软件设计思想没有可靠的物理载体都是空中楼阁,纸上谈兵。

DSP入门

学习日志:1、看电路图,把整体结构看懂,然后找出对应的芯片的用的功能。

2、看实验箱上面的电路图,知道DSP每个脚所连接的线的作用。

3、把实验箱玩转,就是怎么接线的。

4、会根据已知的程序写进去,此处应该用到USB仿真器,此处要对相应的ccs学习。

5、ccs的学习,首先要学会配置,即先要进入Setup CCS 2 ('C2000)进行配置,此时最好亲自装一下ccs学会怎么配置,不然实验箱不会正常工作的,此处是在仿真模式下进行的。

配置之前先要clear,然后选择ICETEK-5100 EMULATOR for,也就是最后一个,这种模式下,是在外设相连的情况下的仿真,如果选择F2812 Device Simulator是纯仿真模式,不与外设相连接,在此情况下,一般只会用到这两种情况下的仿真。

6、对ccs的学习,在编写程序时,只需要编写.c程序和.cmd程序,其它的全部都从别的地方调进来的,不用编写,但是要理解相应程序的功能。

7、事件管理器的学习:GpioMuxRegs.GPAMUX.all=0x0000 GPIOA的I/O模式和第二功能模式0时I/O模式1时第二功能模式。

GpioMuxRegs.GPADIR.all=0x00bf GPIOA I/O模式的输入输出。

0输入1输出(p110 *p95)。

GpioMuxRegs.GPADIR.all此东东暂时没有什么用,编程时可以带上,令其=0x0000即可。

事件管理器分为EV A(起始地址7400H)和EVB(起始地址7500H),功能基本相同,只是模块的外部接口和信号有所不同。

(*p14) 8、通用定时器的比较器用作比较功能时可以产生PWM波形。

GP1为比较器和PWM电路提供基准时钟,GP2为捕获单元和正交脉冲计数操作提供基准时钟。

定时器包括:增减寄存器TxCNT比较寄存器TxCMPR周期寄存器TxPR控制寄存器TxCON通用定时器比较输出引脚TxCMP全局控制寄存器GPCONA/B定时器的四种模式:停止保持模式、连续增计数模式、定向的增减计数模式、连续的增减计数模式。

DSP知识整理

一、简答题1.什么是定点DSP芯片和浮点DSP芯片?各自有什么优缺点a)按数据的定点格式工作的DSP芯片成为定点DSP;b)按数据的浮点格式工作的DSP芯片成为浮点DSP;c)定点DSP的价格便宜,功耗低,但运算精度低;d)浮点DSP的价格较高,C语言编程调试方便,运算精度高。

2.流水线操作的基本原理流水线操作是各指令以机器周期为单位相差一个时钟周期,连续并行工作的情况。

其本质是DSP多条总线彼此独立地同时工作,使得同一指令在不同机器周期内占用不同的总线资源。

同时,不同指令在同一机器周期内占用不同的总线资源。

3.‘C54x DSP有哪些重复操作?各有什么优点?有单条指令重复执行和程序块重复执行两种重复操作。

单条指令重复操作功能,可以使乘法/累加和数据块传送那样的多周期指令在执行一次之后变成单周期指令,大大提高了这些指令的执行速度。

而利用块重复操作进行循环,是一种零开销循环。

4.软件可编程等待状态发生器的功能是什么?软件可编程等待状态产生器可以将外部总线周期扩展到7个机器周期(C5402、C5410、C5420为14个机器周期),这样‘C54x DSP可以方便的与慢速的片内存储器和I/O器件接口。

5.‘C54x DSP的串行口有哪些类型?各有什么特点?有标准同步串口SP、缓冲同步串口BSP、多路缓冲串口McBSP、时分多路同步串口TMD 四种。

缓冲串口(BSP)是一个增强型的标准串口,它由一个全双工双缓冲串口和一个自动缓冲单元(ABU)组成。

在标准模式下,缓冲串口的操作与标准串口的工作方式是一样的。

不过无论是标准模式还是自动缓冲模式,BSP都提供了一些增强功能。

主要包括了可编程控制的串口时钟、可选择时钟和帧同步信号的正负极性,能够以每帧8位、10位、12位和16位传输数据。

通过配置BSP的控制寄存器,BSP还能实现忽略帧同步信号的数据传输。

时分复用串行口TDM采用时分复用技术,将多个外部器件复用与’C54x进行串行通信,每一个时隙对应于其中的1路通信。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DSP学习之前应该弄懂的问题一、时钟和电源问:DSP的电源设计和时钟设计应该特别注意哪些方面?外接晶振选用有源的好还是无源的好?答:时钟一般使用晶体,电源可用TI的配套电源。

外接晶振用无源的好。

问:TMS320LF2407的A/D转换精度保证措施。

答:参考电源和模拟电源要求干净。

问:系统调试时发现纹波太大,主要是哪方面的问题?答:如果是电源纹波大,加大电容滤波。

问:请问我用5V供电的有源晶振为DSP提供时钟,是否可以将其用两个电阻进行分压后再接到DSP的时钟输是否稳定?答:这样做不好,建议使用晶体。

问:一个多DSP电路板的时钟,如何选择比较好?DSP电路板的硬件设计和系统调试时的时序问题?答:建议使用时钟芯片,以保证同步。

硬件设计要根据DSP芯片的时序,选择外围芯片,根据时序设定等待和二.干扰与板的布局问:器件布局应重点考虑哪些因素?例如在集中抄表系统中?答:可用TMS320VC5402,成本不是很高。

器件布局重点应是存贮器与DSP的接口。

问:在设计DSP的PCB板时应注意哪些问题?答:1.电源的布置;2.时钟的布置;3.电容的布置;4.终端电路;5.数字同模拟的布置。

问:请问DSP在与前向通道(比如说AD)接口的时候,布线过程中要注意哪些问题,以保证AD采样的稳定性?答:模拟地和数字地分开,但在一点接地。

问:DSP主板设计的一般步骤是什么?需要特别注意的问题有哪些?答:1.选择芯片;2.设计时序;3.设计PCB。

最重要的是时序和布线问:在硬件设计阶段如何消除信号干扰(包括模拟信号及高频信号)?应该从那些方面着手?答:1.模拟和数字分开;2.多层板;3.电容滤波。

问:在电路板的设计上,如何很好的解决静电干扰问题。

答:一般情况下,机壳接大地,即能满足要求。

特殊情况下,电源输入、数字量输入串接专用的防静电器件。

问:DSP板的电磁兼容(EMC)设计应特别注意哪些问题?答:正确处理电源、地平面,高速的、关键的信号在源端串接端接电阻,避免信号反射。

问:用电感来隔离模拟电源和数字电源,其电感量如何决定?是由供电电流或噪音要求来决定吗?有没有计算公答:电感或磁珠相当于一个低通滤波器,直流电源可以通过,而高频噪声被滤除。

所以电感的选择主要决定于电问:讲座上的材料多是电源干扰问题,能否介绍板上高频信号布局(Layout)时要注意的问题以及数字信号对模答:数字信号对模拟信号的干扰主要是串扰,在布局时模拟器件应尽量远离高速数字器件,高速数字信号尽量远们不穿越模拟地平面。

问:能否介绍PCB布线对模拟信号失真和串音的影响,如何降低和克服?答:有2个方面,1. 模拟信号与模拟信号之间的干扰:布线时模拟信号尽量走粗一些,如果有条件,2个模拟字信号对模拟信号的干扰:数字信号尽量远离模拟信号,数字信号不能穿越模拟地。

三.DSP性能问:1.我要设计生物图像处理系统,选用那种型号较好(高性能和低价格)?2.如果选定TI DSP,需要什么开发答:1.你可采用C54x 或C55x平台,如果你需要更高性能的,可采用C6x系列。

2.需要EVMs和XDS510仿真问:请介绍一种专门用于快速富利叶变换(FFT),数字滤波,卷积,相关等算法的DSP,最好集成12bit以上答:如果你的系统是马达/能量控制的,我建议你用TMS320LF240x。

详情请参阅DSP选择指南:http://www.d问:有些资料说DSP比单片机好,但单片机用的比DSP广。

请问这两个在使用上有何区别?答:单片机一般用于要求低的场合,如4/8位的单片机。

DSP适合于要求较高的场合。

问:我想了解在信号处理方面DSP比FPGA的优点。

答:DSP是通用的信号处理器,用软件实现数据处理;FPGA用硬件实现数据处理。

DSP的成本便宜,算法灵活好,成本较高。

问:请问减小电路功耗的主要途径有哪些?答:1.选择低功耗的芯片;2.减少芯片的数量;3.尽量使用IDLE。

问:用C55设计一个低功耗图像压缩/解压和无线传输的产品,同时双向传输遥控指令和其他信息,要求图像3 320*240,不知道能否实现?若能,怎样确定性能?选择周边元器件?确定最小的传输速率?能否提供开发的解答:1.有可能,要看你的算法。

2.建议先在模拟器上模拟。

问:用DSP开发MP3,比较专用MP3解码芯片如何,比如成本、难度、周期?谢谢。

答:1.DSP的功能强,可以实现附加的功能,如ebook等;2.DSP的性能价格比高;3.难度较大,需要算法,因方案。

问:用DSP开发的系统跟用普通单片机开发的系统相比,有何优势?DSP一般适用于开发什么样的系统?其开如何?与DSP的接口电路是否还得用专门的芯片?答:1.性能高;2.适合于速度要求高的场合;3.开发周期一般6个月,投入一般要一万元左右;4.不一定,但需问:DSP会对原来的模拟电路产生什么样的影响?答:一方面DSP用数字处理的方法可以代替原来用模拟电路实现的一些功能;另一方面,DSP的高速性对模拟应尽量使DSP远离模拟电路部分。

问:请问支持MPEG-4芯片型号是什么?答:C55x或C6000 或DSC2x问:DSP内的计算速度是快的,但是它的I/O口的交换速度有多快呢?答:主频的1/4左右。

四.技术性问题问:我有二个关于C2000的问题:1、C240或C2407的RS复位引脚既可输入,也可输出,直接用CMOS门电合适,还是应该用OC门(集电极开路)驱动?2、大程序有时运行异常,但加一两条空指令就正常,是何原因答:1、OC门(集电极开路)驱动。

2、是流水线的问题。

问:1.DSP芯片内是否有单个的随机函数指令?2.DSP内的计算速度是快的,但是它的I/O口的交换速度有多FPGA工作呢?答:1.没有。

2.取决于你所用的I/O。

对于HPI,传输速率(字节)大约为CPU的1/4,对McBSP,位速率(kb 你可以级联仿真接口和一个EPLD/FPGA在一起。

请参考下面的应用手册:/sc/docs/psheets/abstract/apps/spra439a.htm问:设计DSP系统时,我用C6000系列。

DSP引脚的要上拉,或者下拉的原则是怎样的?我经常在设计时为某阻而犹豫不定。

答:C6000系列的输入引脚内部一般都有弱的上拉或者下拉电阻,一般不需要考虑外部加上拉或者下拉电阻,问:我正在使用TMS320VC5402,通过HPI下载代码,但C5402的内部只提供16K字的存储区,请问我能通过扩展存储区运行吗?答:不行,只能下载到片内。

问:电路中用到DSP,有时当复位信号为低时,电压也属于正常范围,但DSP加载程序不成功。

电流也偏大,么?答:复位时无法加载程序。

问:DSP和单片机相连组成主从系统时,需要注意哪些问题?答:建议使用HPI接口,或者通过DPRAM连接。

问:原来的DSP的程序需放在EPROM中,但EPROM的速度难以和DSP匹配。

现在是如何解决此问题的?答:用BootLoad方法解决。

问:我在使用5402DSK时,一上电,不接MIC,只接耳机,不运行任何程序,耳机中有比较明显的一定频率的出现,但接MIC,运行范例中的CODEC程序时,又会出现这种噪声。

上述情况通常都在DSK工作一段时间后自现别人用DSK时也碰到过这种情况,我自己参照5402DSK做了一块板,所用器件基本一样,也是这现象,请问答:开始时没有有效的程序代码,所以上电后是随机状态,出现这种情况是正常的。

问:我使用的是TMS320LF2407,但是仿真时不能保证每次都能GO MAIN。

我想详细咨询一下,CMD文件的设义。

答:可能看门狗有问题,关掉看门狗。

有关CMD文件配置请参考《汇编语言工具》第二章。

问:我设计的TMS320VC5402板子在调试软件时会经常出现存储器错误报告,排除是映射的问题,是不是板子作不正常的问题?如何判别?答:你可以利用Memoryfill功能,填入一些数值,然后刷新一下,看是不是在变,如果是在变化,则Memory问:如何解决Flash编程的问题:可不可以先用仿真器下载到外程序存储RAM中,然后程序代码将程序代码自己F240的内部Flash ROM中,如何写?答:如果你用F240,你可以用下载TI做的工具。

其它的可以这样做。

问:C5510芯片如何接入E1信号?在接入时有什么需要注意的地方?答:通过McBSP同步串口接入。

注意信号电平必须满足要求。

问:请问如何通过仿真器把.HEX程序直接烧到FLASH中去?所用DSP为5402是否需要自己另外编写一个烧写答:直接写.OUT。

是DSP中写一段程序,把主程序写到FLASH中。

问:DSP的硬件设计和其他的电路板有什么不同的地方?答:1.要考虑时序要求;2.要考虑EMI的要求;3.要考虑高速的要求;4.要考虑电源的要求。

问:ADS7811,ADS7815,ADS8320,ADS8325,ADS8341,ADS8343,ADS8344,ADS8345中,哪个可以较10个模拟信号的AD转换(要求16bit,1毫秒内完成10个信号的采样,当然也要考虑价格)?答:作选择有下列几点需要考虑1. 总的采样率:1ms、10个通道,总采样率为100K ,所有A/D均能满足要求型:并行、串行。

前2种A/D为并行接口,后几种均为串行接口。

3. 接口电平的匹配。

前2种A/D为5V电平均可为3.3V电平,可与VC33直接接口。

问:DSP的电路板有时调试成功率低于50%,连接和底板均无问题,如何解决?有时DSP同CPLD产生不明原答:看来你的硬件设计可能有问题,不应该这么小的成功率。

我们的板的成功率为95%以上。

问:我们的工程有两人参与开发,由于事先没有考虑周全,一人使用的是助记符方式编写汇编代码,另一人使用代码,请问CCS5000中这二种编写方式如何嵌在一起调试?答:我没有这样用过,我想可以用下面的办法解决:将一种方式的程序先单独编译为.obj文件,在创建工程时,式的程序一起加进工程中,二者即可一起编译调试了。

问:DSP数据缓冲,能否用SDRAM代替FIFO?答:不行问:ADC或DAC和DSP相连接时,要注意什么问题?比如匹配问题,以保证A/D采样稳定或D/A码不丢失。

答:1. 接口方式:并行/串行;2. 接口电平,必须保证二者一致。

问:用F240经常发生外部中断丢失现象,甚至在实际环境中只有在程序刚开始时能产生中断,几分钟后就不能询的方式,请问有何有效的解决方法?改为F2407是不是要好些?答:应该同DSP无关。

建议你将中断服务程序简化看一下。

五、为什么要片内RAM大的DSP效率高?目前DSP发展的片内存储器RAM越来越大,要设计高效的DSP系统,就应该选择片内RAM较大的DSP。

片内R 优点:1)片内RAM的速度较快,可以保证DSP无等待运行。