F28335存储器以及地址分配

F28335BOOTROM引导模式和程序

28335使用串口烧写程序串口烧写是一种相对较方便的烧写方式,相对于仿真器或是CAN烧写,相对于仿真器或是USB转CAN的设备,串口是一种非常廉价的烧写方式,而且也不需要安装专业的集成开发环境CCS等,但是不能实现在线调试,因此也只适用于程序基本不用再调整或大批量的场合。

F28335的存储器映射图如下:BOOTROM 是一块8K X 16的只读存储器,位于地址空间0x3FE000~0x3FFFFF,片内BOOTROM在出厂时固化了引导加载程序以的存储映射如下图所示:及定点和浮点数据表,片上BOOTROM1.内BOOT ROM数学表:在BOOT ROM中保留了4K X 16位空间,用以存放浮点和IQ数据公式表,这些数据公式表有助于改善性能和节省SARAM空间。

向量表:CPU向量表位于ROM存储器0x3FE000~0x3FFFFF段内,如下图所示。

复位后,当VMAP=1,ENPIE=0(PIE向量表禁止)时,该向量表激活。

在内部BOOT ROM引导区中能够调用的唯一向量就是位于0x3FFFC0的复位向量。

复位向量在出厂时被烧录为直接指向存储在BOOT ROM 空间中的InitBoot函数,该函数用于开启引导过程。

然后通过通用I/O引脚上的检验判断,决定具体引导模式。

引导模式与控制引脚之间的关系如下图所示:Bootloader特性:Bootloader是位于片上引导ROM中的在复位后执行的程序,用于在上电复位后,将程序代码从外部源转移到内部存储器。

这允许代码暂时存储在掉电不丢失数据的外部存储器内,然后被转移到高速存储器中执行。

引导ROM中的复位向量将程序执行重定向至InitBoot函数。

执行器件初始化之后,bootloader将检查GPIO引脚的状态以确定您需要执行哪种引导模式。

这些选项包括:跳转至闪存、跳转至SARAM、跳转至OTP或调用其中一个片上引导加载例程。

完成选择进程后,如果已完成所需的引导加载,处理器将在所选引导模式确定的应用起点继续执行。

DSP2-F28335的结构原理

这些状态位在ST0寄存器中。

15

4、堆栈指针--SP

16位,寻址低64K字数据空间。 生长方向:低地址 高地址; 总指向下一个空位; 复位后,SP指向 0400H; 32位数入栈:低对低,高对高(小端模式); 32位数读写,约定偶地址访问: 例:SP为0083H,32位数读从0082H开始。 SP溢出时: 例:上溢,加到FFFFH后复位为0000H,重加。 下溢,减少SP低于0000H后,会从FFFFH继续减。

16

5、数据页指针--DP

每页64个字

17

6、辅助寄存器--XAR0~XAR7

8个:

操作数地址指针; 32位通用寄存器; 16位通用寄存器(AR0~AR7),可作循环控制。

(注意:高16位可能受影响)

注意:高16位不能单独访问。

18

7、程序计数器--PC

F1: Instruction Address F2: Instruction Content D1: Decode Instruction D2: Resolve Operand Addr R1: Operand Address R2: Get Operand E: CPU doing “real” work W: store content to memory

2017/3/1 Wednesday

7

一、F28335的乘法器

程序总线

32

数据总线

16 32

XT (32) or T/TL

16/32

1、32位乘法

•经XT(32)×另一个32位数 •积, P(高32位或低32位)

8/16/32 32

MULTIPLIER

Shift R/L (0-16)

TMS320F28335外部中断总结

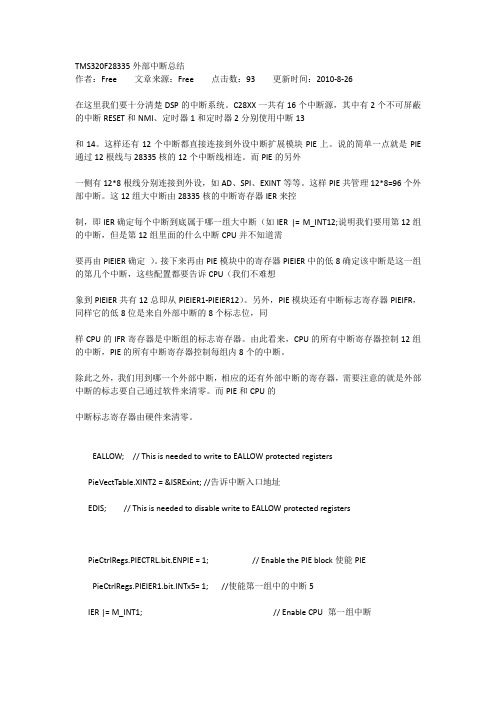

TMS320F28335外部中断总结作者:Free 文章来源:Free 点击数:93 更新时间:2010-8-26在这里我们要十分清楚DSP的中断系统。

C28XX一共有16个中断源,其中有2个不可屏蔽的中断RESET和NMI、定时器1和定时器2分别使用中断13和14。

这样还有12个中断都直接连接到外设中断扩展模块PIE上。

说的简单一点就是PIE 通过12根线与28335核的12个中断线相连。

而PIE的另外一侧有12*8根线分别连接到外设,如AD、SPI、EXINT等等。

这样PIE共管理12*8=96个外部中断。

这12组大中断由28335核的中断寄存器IER来控制,即IER确定每个中断到底属于哪一组大中断(如IER |= M_INT12;说明我们要用第12组的中断,但是第12组里面的什么中断CPU并不知道需要再由PIEIER确定)。

接下来再由PIE模块中的寄存器PIEIER中的低8确定该中断是这一组的第几个中断,这些配置都要告诉CPU(我们不难想象到PIEIER共有12总即从PIEIER1-PIEIER12)。

另外,PIE模块还有中断标志寄存器PIEIFR,同样它的低8位是来自外部中断的8个标志位,同样CPU的IFR寄存器是中断组的标志寄存器。

由此看来,CPU的所有中断寄存器控制12组的中断,PIE的所有中断寄存器控制每组内8个的中断。

除此之外,我们用到哪一个外部中断,相应的还有外部中断的寄存器,需要注意的就是外部中断的标志要自己通过软件来清零。

而PIE和CPU的中断标志寄存器由硬件来清零。

EALLOW; // This is needed to write to EALLOW protected registersPieVectTable.XINT2 = &ISRExint; //告诉中断入口地址EDIS; // This is needed to disable write to EALLOW protected registersPieCtrlRegs.PIECTRL.bit.ENPIE = 1; // Enable the PIE block使能PIE PieCtrlRegs.PIEIER1.bit.INTx5= 1; //使能第一组中的中断5IER |= M_INT1; // Enable CPU 第一组中断EINT; // Enable Global interrupt INTMERTM; // Enable Global realtime interrupt DBGM也就是说,12组中的每个中断都要完成上面的相同配置,剩下的才是去配置自己的中断。

Tms320F28335中AD采样存储地址问题记录

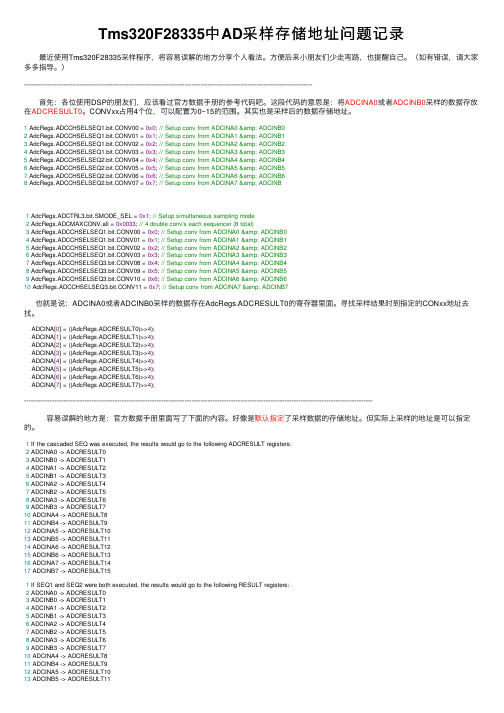

Tms320F28335中AD采样存储地址问题记录最近使⽤Tms320F28335采样程序,将容易误解的地⽅分享个⼈看法。

⽅便后来⼩朋友们少⾛弯路,也提醒⾃⼰。

(如有错误,请⼤家多多指导。

)----------------------------------------------------------------------------------------------------------------------------⾸先:各位使⽤DSP的朋友们,应该看过官⽅数据⼿册的参考代码吧。

这段代码的意思是:将ADCINA0或者ADCINB0采样的数据存放在ADCRESULT0。

CONVxx占⽤4个位,可以配置为0~15的范围。

其实也是采样后的数据存储地址。

1 AdcRegs.ADCCHSELSEQ1.bit.CONV00 = 0x0; // Setup conv from ADCINA0 & ADCINB02 AdcRegs.ADCCHSELSEQ1.bit.CONV01 = 0x1; // Setup conv from ADCINA1 & ADCINB13 AdcRegs.ADCCHSELSEQ1.bit.CONV02 = 0x2; // Setup conv from ADCINA2 & ADCINB24 AdcRegs.ADCCHSELSEQ1.bit.CONV03 = 0x3; // Setup conv from ADCINA3 & ADCINB35 AdcRegs.ADCCHSELSEQ2.bit.CONV04 = 0x4; // Setup conv from ADCINA4 & ADCINB46 AdcRegs.ADCCHSELSEQ2.bit.CONV05 = 0x5; // Setup conv from ADCINA5 & ADCINB57 AdcRegs.ADCCHSELSEQ2.bit.CONV06 = 0x6; // Setup conv from ADCINA6 & ADCINB68 AdcRegs.ADCCHSELSEQ2.bit.CONV07 = 0x7; // Setup conv from ADCINA7 & ADCINB1 AdcRegs.ADCTRL3.bit.SMODE_SEL = 0x1; // Setup simultaneous sampling mode2 AdcRegs.ADCMAXCONV.all = 0x0033; // 4 double conv's each sequencer (8 total)3 AdcRegs.ADCCHSELSEQ1.bit.CONV00 = 0x0; // Setup conv from ADCINA0 & ADCINB04 AdcRegs.ADCCHSELSEQ1.bit.CONV01 = 0x1; // Setup conv from ADCINA1 & ADCINB15 AdcRegs.ADCCHSELSEQ1.bit.CONV02 = 0x2; // Setup conv from ADCINA2 & ADCINB26 AdcRegs.ADCCHSELSEQ1.bit.CONV03 = 0x3; // Setup conv from ADCINA3 & ADCINB37 AdcRegs.ADCCHSELSEQ3.bit.CONV08 = 0x4; // Setup conv from ADCINA4 & ADCINB48 AdcRegs.ADCCHSELSEQ3.bit.CONV09 = 0x5; // Setup conv from ADCINA5 & ADCINB59 AdcRegs.ADCCHSELSEQ3.bit.CONV10 = 0x6; // Setup conv from ADCINA6 & ADCINB610 AdcRegs.ADCCHSELSEQ3.bit.CONV11 = 0x7; // Setup conv from ADCINA7 & ADCINB7也就是说:ADCINA0或者ADCINB0采样的数据存在AdcRegs.ADCRESULT0的寄存器⾥⾯。

5、F28335存储器以及地址分配全解

片外扩展存储器

程序空间

F28335对数据空间和程序空间进行了统 一编址,图5.1的映射表就像是各个空间的地

保留

M0向量 RAM(32 X 32)

图一样,有些空间既可以作为数据空间也可 以作为程序空间,有些空间只能作为数据空

0x00 到密码模块保护,有些空 间地址是作为保留的,具体内容就要仔细对 照这个地图来进行查阅了。

一种全为0,另一种全为1,一个新的FLASH或FLASH被擦除后,就变为全1了,这样只要读一下密码区,

就能破解了,还一种情况,就是全为0,这时候器件是被加密了,但是不管密钥寄存器的内容是什么, 器件都处在加密状态,即该器件无法解锁了,这时候芯片就被完全锁住了。因此不要用全0作为密码。 如果在擦除FLASH的期间,芯片复位了,那这个芯片的密码就不确定了,也不能解锁。

TMS320F28335内存保护特点

地址范围 片上存储器 数据空间 0x00 0000 0x00 0040 0x00 0400 0x00 0800 0x00 0D00 M0 SRAM(1k X16) M1 SRAM(1k X16) PF0 PIE 中断 向量表 0x00 0E00 0x00 2000 0x00 5000 0x00 6000 0x00 7000 0x00 8000 0x00 9000 0x00 A000 0x00 B000 0x00 C000 0x00 D000 0x00 E000 0x00 F000 0x01 0000 0x30 0000 0x33 FFF8 0x34 0000 0x38 0000 0x38 0400 0x38 0800 0x3F 8000 0x3F 9000 0x3F A000 0x3F B000 0x3F C000 0x3F E000 0x3F FFFC PF0 保留 PF3 DMA PF1 PF2

EPWMTMSF28335所需配置的EPWM寄存器

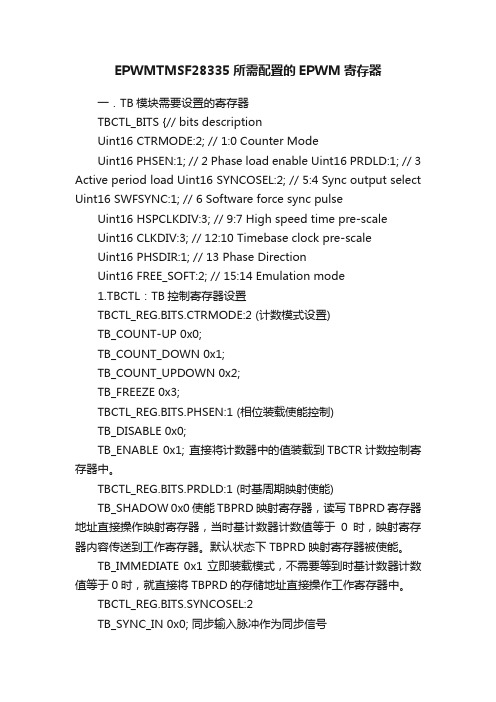

EPWMTMSF28335所需配置的EPWM寄存器一.TB模块需要设置的寄存器TBCTL_BITS {// bits descriptionUint16 CTRMODE:2; // 1:0 Counter ModeUint16 PHSEN:1; // 2 Phase load enable Uint16 PRDLD:1; // 3 Active period load Uint16 SYNCOSEL:2; // 5:4 Sync output select Uint16 SWFSYNC:1; // 6 Software force sync pulseUint16 HSPCLKDIV:3; // 9:7 High speed time pre-scaleUint16 CLKDIV:3; // 12:10 Timebase clock pre-scaleUint16 PHSDIR:1; // 13 Phase DirectionUint16 FREE_SOFT:2; // 15:14 Emulation mode1.TBCTL:TB控制寄存器设置TBCTL_REG.BITS.CTRMODE:2 (计数模式设置)TB_COUNT-UP 0x0;TB_COUNT_DOWN 0x1;TB_COUNT_UPDOWN 0x2;TB_FREEZE 0x3;TBCTL_REG.BITS.PHSEN:1 (相位装载使能控制)TB_DISABLE 0x0;TB_ENABLE 0x1; 直接将计数器中的值装载到TBCTR计数控制寄存器中。

TBCTL_REG.BITS.PRDLD:1 (时基周期映射使能)TB_SHADOW 0x0 使能TBPRD映射寄存器,读写TBPRD寄存器地址直接操作映射寄存器,当时基计数器计数值等于0时,映射寄存器内容传送到工作寄存器。

默认状态下TBPRD映射寄存器被使能。

TB_IMMEDIATE 0x1 立即装载模式,不需要等到时基计数器计数值等于0时,就直接将TBPRD的存储地址直接操作工作寄存器中。

dspf28335启动过程

dspf28335启动过程1.DSP reset后运行的起始地址是多少?0x3FFFC02.仿真器烧写程序的步骤是?根据cmd文件把程序烧到指定位置,然后执行。

3.DSP的Flash启动过程是什么?首先硬件配置GPIO84~87上拉为1,即处于Flash启动过程。

当DSP复位后,会从复位向量0x3FFFC0处取得复位向量,并跳转到InitBoot处开始执行,InitBoot会读GPIO84~87的值发现全为1判断为Flash启动方式。

然后会跳到0x33FFF6处执行。

在CCS5.2工程的cmd文件中有如下代码:MEMORY{PAGE 0 :BEGIN : origin = 0x33FFF6, length = 0x000002 /* Boot to M0 will go here */...}SECTIONS{...codestart : > BEGIN PAGE = 0...}即表示把codestart段放到0x33FFF6位置处,文件“DSP2833x_CodeStartBranch.asm”中有codestart段的定义,实际上codestart段只是包含了一个跳转指令,是程序跳转到_c_int00处,_c_int00在boot.asm in RTS library中有定义,_c_int00的代码最终会调用c的main 函数,之后就是main函数的执行。

总的就是:Reset(0x3fffc0)—>initBoot()—>判断启动方式—>codestart(0x33fff6)—>_c_int00—>main函数4.F28335如何烧写代码到flash中并运行?首先使用添加C:\ti\controlSUITE\device_support\f2833x\v133\DSP2833x_com mon\cmd\F28335.cmd。

此文件即为配置代码到flash中的TI官方配置文件。

【精品】:F28335寄存器

Table 1. Flash/OTP Configuration RegistersName (1) (2) Address Size (x16) Description Bit D escriptionFOP T 0x0A80 1 Flash Option Register Figure 4Reserved 0x0A81 1 ReservedFP WR 0x0A82 1 Flash P ow er Modes Register Figure 5FSTATUS 0x0A83 1 Status Register Figure 6FSTDBYWAIT (3) 0x0A84 1 Flash Sleep To Standby Wait Register Figure 7FACTIVE WAIT (3) 0x0A85 1 Flash Standby To Acti v e Wait Register Figure 8 FBANKWAIT 0x0A86 1 Flash Read Access Wait State Register Figure 9FOTPWAIT 0x0A87 1 OTP Read Access Wait State Register Figure 10Table 14. PLL, Clocking, Watchdog, and Low-Power Mode Registers Name Address Size Description (1) Bit Description(x16)P LLSTS (2) 0x7011 1 P LL Status Register Figure 24HISPCP 0x701A 1 High-Speed P eripheral Clock (HSPCLK) P rescaler Register Figure 17 LOSPCP 0x701B 1 Low-Speed P eripheral Clock (LSPCLK) P rescaler Register Figure 18 PCLKCR0 0x701C 1 P eripheral Clock Control Register 0 Figure 14PCLKCR1 0x701D 1 P eripheral Clock Control Register 1 Figure 15LPMCR0 0x701E 1 Low P ow er Mode Control Register 0 Figure 18PCLKCR3 0x7020 1 P eripheral Clock Control Register 3 Figure 16P LLCR (2) 0x7021 1 P LL Control Register Figure 23SCSR 0x7022 1 System Control & Status Register Figure 27WDCNTR 0x7023 1 Watchdog Counter Register. Figure 28WDKE Y 0x7025 1 Watchdog Reset Key Register Figure 29WDCR 0x7029 1 Watchdog Control Register Figure 30Table 31. CPU Timers 0, 1, 2 Configuration and Control RegistersName Address Size (x16) Description Bit DescriptionTIMER0TIM 0x0C00 1 CPU-Timer 0, Counter Register Figure 33TIMER0TIMH 0x0C01 1 CPU-Timer 0, Counter Register High Figure 34 TIMER0PRD 0x0C02 1 CPU-Timer 0, Period Register Figure 35TIMER0PRDH 0x0C03 1 CPU-Timer 0, Period Register High Figure 36 TIMER0TCR 0x0C04 1 CPU-Timer 0, Control Register Figure 37Reserved 0x0C05 1TIMER0TPR 0x0C06 1 CPU-Timer 0, Prescale Register Figure 38TIMER0TPRH 0x0C07 1 CPU-Timer 0, Prescale Register High Figure 39 TIMER1TIM 0x0C08 1 CPU-Timer 1, Counter Register Figure 33TIMER1TIMH 0x0C09 1 CPU-Timer 1, Counter Register High Figure 34 TIMER1PRD 0x0C0A 1 CPU-Timer 1, Period Register Figure 35TIMER1PRDH 0x0C0B 1 CPU-Timer 1, Period Register High Figure 36 TIMER1TCR 0x0C0C 1 CPU-Timer 1, Control Register Figure 37Reserved 0x0C0D 1TIMER1TPR 0x0C0E 1 CPU-Timer 1, Prescale Register Figure 38TIMER1TPRH 0x0C0F 1 CPU-Timer 1, Prescale Register High Figure 39TIMER2TIM 0x0C10 1 CPU-Timer 2, Counter Register Figure 33TIMER2TIMH 0x0C11 1 CPU-Timer 2, Counter Register High Figure 34TIMER2PRD 0x0C12 1 CPU-Timer 2, Period Register Figure 35TIMER2PRDH 0x0C13 1 CPU-Timer 2, Period Register High Figure 36TIMER2TCR 0x0C14 1 CPU-Timer 2, Control Register Figure 37Reserved 0x0C15 1TIMER2TPR 0x0C16 1 CPU-Timer 2, Prescale Register Figure 38TIMER2TPRH 0x0C17 1 CPU-Timer 2, Prescale Register High Figure 39Table 39. GPIO Control RegistersName (1) Address Size (x16) Register Description Bit DescriptionGPACTRL 0x6F80 2 GPIO A Control Register (GPIO0-GPIO31) Figure 53GPAQSEL1 0x6F82 2 GPIO A Qualifier Select 1 Register (GPIO0-GPIO15) Figure 55 GPAQSEL2 0x6F84 2 GPIO A Qualifier Select 2 Register (GPIO16-GPIO31) Figure 56 GPAMUX1 0x6F86 2 GPIO A MUX 1 Register (GPIO0-GPIO15) Figure 47GPAMUX2 0x6F88 2 GPIO A MUX 2 Register (GPIO16-GPIO31) Figure 48GPADIR 0x6F8A 2 GPIO A Direction Register (GPIO0-GPIO31) Figure 59GPAPUD 0x6F8C 2 GPIO A Pull Up Disable Register (GPIO0-GPIO31) Figure 62GPBCTRL 0x6F90 2 GPIO B Control Register (GPIO32-GPIO63) Figure 54GPBQSEL1 0x6F92 2 GPIO B Qualifier Select 1 Register (GPIO32-GPIO47) Figure 57 GPBQSEL2 0x6F94 2 GPIO B Qualifier Select 2 Register (GPIO48 - GPIO63) Figure 58 GPBMUX1 0x6F96 2 GPIO B MUX 1 Register (GPIO32-GPIO47) Figure 49GPBMUX2 0x6F98 2 GPIO B MUX 2 Register (GPIO48-GPIO63) Figure 50GPBDIR 0x6F9A 2 GPIO B Direction Register (GPIO32-GPIO63) Figure 60GPBPUD 0x6F9C 2 GPIO B Pull Up Disable Register (GPIO32-GPIO63) Figure 63GPCMUX1 0x6FA6 2 GPIO C MUX 1 Register (GPIO64-GPIO79) Figure 51GPCMUX2 0x6FA8 2 GPIO C MUX 2 Register (GPIO80-GPIO87) Figure 52GPCDIR 0x6FAA 2 GPIO C Direction Register (GPIO64-GPIO87) Figure 61GPCPUD 0x6FAC 2 GPIO C Pull Up Disable Register (GPIO64-GPIO87) Figure 64(1)The registers in this table are EALLOW protected. See Section 7.2 for more information. Table 40. GPIO Interrupt and Low Power Mode Select RegistersName (1) Address Size Register Description Bit Description (x16)GPIOXINT1SEL 0x6FE0 1 XINT1 Source Select Register (GPIO0-GPIO31) Figure 71 GPIOXINT2SEL 0x6FE1 1 XINT2 Source Select Register (GPIO0-GPIO31) Figure 71 GPIOXNMISEL 0x6FE2 1 XNMI Source Select Register (GPIO0-GPIO31) Figure 71 GPIOXINT3SEL 0x6FE3 1 XINT3 Source Select Register (GPIO32 - GPIO63) Table 82 GPIOXINT4SEL 0x6FE4 1 XINT4 Source Select Register (GPIO32 - GPIO63) Table 82 GPIOXINT5SEL 0x6FE5 1 XINT5 Source Select Register (GPIO32 - GPIO63) Table 82 GPIOXINT6SEL 0x6FE6 1 XINT6 Source Select Register (GPIO32 - GPIO63) Table 82 GPIOXINT7SEL 0x6FE7 1 XINT7 Source Select Register (GPIO32 - GPIO63) Table 82GPIOLPMSEL 0x6FE8 1 LPM wakeup Source Select Register (GPIO0-GPIO31) Figure 72Table 41. GPIO Data RegistersName Address Size (x16) Register D escription Bit DescriptionGP ADAT 0x6FC0 2 GPIO A Data Register (GPIO0-GPIO31) Figure 65GP ASE T 0x6FC2 2 GPIO A Set Register (GPIO0-GPIO31) Figure 68GP ACLE AR 0x6FC4 2 GPIO A Clear Register (GPIO0-GPIO31) Figure 68GP ATOGGLE 0x6FC6 2 GPIO A Toggle Register (GPIO0-GPIO31) Figure 68GPBDAT 0x6FC8 2 GPIO B Data Register (GPIO32-GPIO63) Figure 66GPBSE T 0x6FCA 2 GPIO B Set Register (GPIO32-GPIO63) Figure 69GPBCLE AR 0x6FCC 2 GPIO B Clear Register (GPIO32-GPIO63) Figure 69GPBTOGGLE 0x6FCE 2 GPIO B Toggle Register (GP IO32-GP IO63) Figure 69Table 41. GPIO Data Registers (continued)Name Address Size (x16) Register D escription Bit DescriptionGPCDAT 0x6FD0 2 GPIO C Data Register (GPIO64 - GPIO87) Figure 67GPCSET 0x6FD2 2 GPIO C Set Register (GPIO64 - GPIO87) Figure 70GPCCLE AR 0x6FD4 2 GPIO C Clear Register (GP IO64 - GPIO87) Figure 70GPCTOGGLE 0x6FD6 2 GPIO C Toggle Register (GP IO64 - GPIO87) Figure 70Table 46. Default State of Peripheral InputPeripheral Input Description Default Input (1)TZ1-TZ6 Trip zone 1-6 1EP WMSYNCI eP WM Synch Input 0ECAP neCAP input 1E QEPnAeQEP input 1E QEPnIeQEP index 1E QEPnSeQEP strobe 1SPICLKx SPI clock 1SPISTE x SPI transmit enable 0SPISIMOx SPI Slave-in, master-out 1SPISOMIx SPI Slave-out, master-in 1SCIRXDx SCI receive 1CANRXx CAN receive 1SDAA I2C data 1SCLA1 I2C clock 1。

TMS320F28335的DSP实验指导书

语音单元

开关量输入输出单元

液晶显示单元

键盘单元

信号扩展单元

CPLD模块单元

模拟信号源

EL-NC2100电子创新设计平台扩展总线接口

直流电源单元

1、CPU板接口(Techv总线)

Techv总线接口是和TI公司DSK兼容的信号扩展接口,可连接我公司各种Techv总线的CPU板和扩展板如:图像处理、高速AD、DA、USB/以太网等扩展板,也可以连接TI公司的标准DSK扩展信号板,扩展到CPU的IO空间和数据空间。CPU接口用来扩展CPU模块,信号定义如下图:

+5V

+5V电源

23

A03|XA05

地址线

O

24

A02|XA04

地址线

O

25

A01|XA03

地址线

O

26

A00|XA02

地址线

O

27

A21|BE3

地址线

O

28A20ຫໍສະໝຸດ BE2地址线O29

NC|BE1

地址线

O

30

NC|BE0

地址线

O

31

GND

地

32

GND

地

33

D31

数据线

IO

34

D30

数据线

IO

35

D29

46

SYS

CPU信号

IO

47

AD1/USER

扩展板AD输入1

I

48

AD2/USER

扩展板AD输入2

I

49

AD3/USER

扩展板AD输入3

I

50

AD4/USER

dsp tms320f28335 在线升级资料2(参考论坛博客)

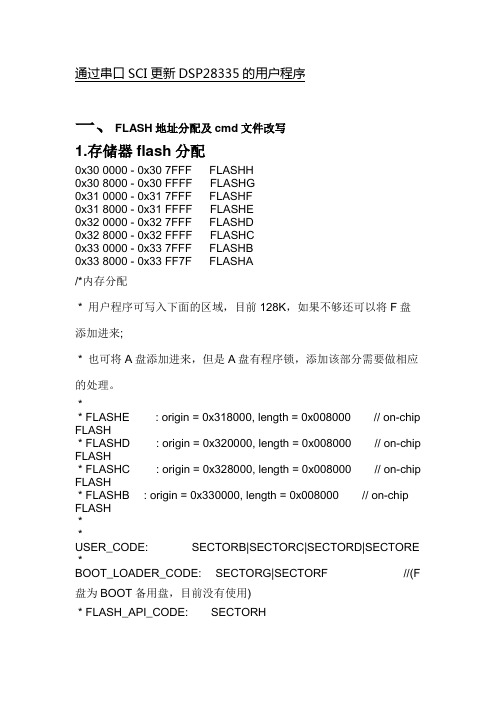

通过串口SCI更新DSP28335的用户程序一、FLASH地址分配及cmd文件改写1.存储器flash分配0x30 0000 - 0x30 7FFF FLASHH0x30 8000 - 0x30 FFFF FLASHG0x31 0000 - 0x31 7FFF FLASHF0x31 8000 - 0x31 FFFF FLASHE0x32 0000 - 0x32 7FFF FLASHD0x32 8000 - 0x32 FFFF FLASHC0x33 0000 - 0x33 7FFF FLASHB0x33 8000 - 0x33 FF7F FLASHA/*内存分配* 用户程序可写入下面的区域,目前128K,如果不够还可以将F盘添加进来;* 也可将A盘添加进来,但是A盘有程序锁,添加该部分需要做相应的处理。

** FLASHE : origin = 0x318000, length = 0x008000 // on-chip FLASH* FLASHD : origin = 0x320000, length = 0x008000 // on-chip FLASH* FLASHC : origin = 0x328000, length = 0x008000 // on-chip FLASH* FLASHB : origin = 0x330000, length = 0x008000 // on-chip FLASH**USER_CODE: SECTORB|SECTORC|SECTORD|SECTORE *BOOT_LOADER_CODE: SECTORG|SECTORF //(F 盘为BOOT备用盘,目前没有使用)* FLASH_API_CODE: SECTORH2.cmd文件其中用户程序中的cmd文件请注意:我把codestart写到了FLASHE的起始地址,这样当升级完程序后bootload程序应该接着运行USER_CODE段,此段正好在FLASHE中,所以程序就开始从更新的用户程序运行。

5、F28335存储器以及地址分配详解

一种全为0,另一种全为1,一个新的FLASH或FLASH被擦除后,就变为全1了,这样只要读一下密码区,

就能破解了,还一种情况,就是全为0,这时候器件是被加密了,但是不管密钥寄存器的内容是什么, 器件都处在加密状态,即该器件无法解锁了,这时候芯片就被完全锁住了。因此不要用全0作为密码。 如果在擦除FLASH的期间,芯片复位了,那这个芯片的密码就不确定了,也不能解锁。

需要与之匹配。当一开始调试FLASH区加密的芯片的时候,仿真器取得CPU的控制权需要

一定的时间,在此期间,CPU正在开始运行,并且会执行保护加密区的操作,这个操作会 引起仿真器断开连接,有两个方法可以解决这个问题。

1、采用Wait-in-Reset仿真模式,这种方法是让芯片保持在复位状态直到仿真器得到控

保留

存放的寄存器不可以随便配置,若要对存放

在Protected空间内的寄存器进行配置,要进 行EALLOW声明,以EDIS结束声明,起到保护 和警示作用。

TMS320F28335内存保护特点

用户用来解锁的寄存器为密钥寄存器,在存储空间映射地址为0x0000 0AE0~0x0000 0AE7,该区域受 EALLOW保护。当这个 128位的密钥位全 1时,密钥寄存器不

字的数据空间和4M字程序空代码安全模块(CSM)是F28335上程序安全性的主要手段,它禁止未授权的 用户访问片内存储器,禁止私有代码的复制或者逆向操作。 安全模块限制CPU去访问片内存储器。实际上,对各种存储器的读写访问都是通过JTAG端口或 外设来进行的,而CSM模块所谓的代码安全性主要是针对片内存储器的访问来定义的,用来禁止未经授 权去复制私人代码或数据。 通过一个128位的密码(相当于8个16位的字)来对安全区来进行加密或解密。这段密码保存 在FLASH的最后8个(0X33FFF8~0X33FFFF),也就是密码区中(PWL),通过密码匹配(PMF),可以解 锁器件。 如果密码保护区中的128位数都是同一个数,这个器件不受保护,全是同一个数有两种可能,

5、F28335存储器以与地址分配

TMS320F28335内存保护特点

代码安全模块CSM--代码安全模块(CSM)是F28335上程序安全性的主要手段,它禁止未授权的 用户访问片内存储器,禁止私有代码的复制或者逆向操作。

TMS320F28335内存保护特点

地址范围

0x00 Байду номын сангаас000

0x00 0040 0x00 0400 0x00 0800 0x00 0D00

0x00 0E00 0x00 2000

0x00 5000

0x00 6000 0x00 7000 0x00 8000 0x00 9000 0x00 A000 0x00 B000 0x00 C000 0x00 D000 0x00 E000 0x00 F000 0x01 0000

保留

FLASH(256K X16)

128位 密码

保留

TI OTP(1k X 16) 用户 OTP(1k X 16)

保留 L0 SARAM(4k X 16) L1 SARAM(4k X 16) L2 SARAM(4k X 16) L3 SARAM(4k X 16)

保留 Boot ROM(8k x 16)

安全模块限制CPU去访问片内存储器。实际上,对各种存储器的读写访问都是通过JTAG端口或 外设来进行的,而CSM模块所谓的代码安全性主要是针对片内存储器的访问来定义的,用来禁止未经授 权去复制私人代码或数据。

通过一个128位的密码(相当于8个16位的字)来对安全区来进行加密或解密。这段密码保存 在FLASH的最后8个(0X33FFF8~0X33FFFF),也就是密码区中(PWL),通过密码匹配(PMF),可以解 锁器件。

5、F28335存储器以及地址分配分析

BROM 向量表-ROM(32 X 32)

片外扩展存储器 保留

外部区域0扩展 4K X16 CS0

保留

外部区域6扩展 1M X16 CS6 外部区域7扩展 1M X16 CS7

保留

0x00 4000 0x00 5000

F28335对数据空间和程序空间进行了统 一编址,图5.1的映射表就像是各个空间的地 图一样,有些空间既可以作为数据空间也可 以作为程序空间,有些空间只能作为数据空 间,有些空间是受到密码模块保护,有些空 间地址是作为保留的,具体内容就要仔细对 照这个地图来进行查阅了。

如果密码保护区中的128位数都是同一个数,这个器件不受保护,全是同一个数有两种可能, 一种全为0,另一种全为1,一个新的FLASH或FLASH被擦除后,就变为全1了,这样只要读一下密码区, 就能破解了,还一种情况,就是全为0,这时候器件是被加密了,但是不管密钥寄存器的内容是什么, 器件都处在加密状态,即该器件无法解锁了,这时候芯片就被完全锁住了。因此不要用全0作为密码。 如果在擦除FLASH的期间,芯片复位了,那这个芯片的密码就不确定了,也不能解锁。

保留

FLASH(256K X16)

128位 密码

保留

TI OTP(1k X 16) 用户 OTP(1k X 16)

保留 L0 SARAM(4k X 16) L1 SARAM(4k X 16) L2 SARAM(4k X 16) L3 SARAM(4k X 16)

保留 Boot ROM(8k x 16)

0x30 0000 0x33 FFF8 0x34 0000 0x38 0000 0x38 0400 0x38 0800 0x3F 8000 0x3F 9000 0x3F A000 0x3F B000 0x3F C000 0x3F E000 0x3F FFFC

DSP2-F28335的结构基本知识

XINTF

D(31-0)

实时JTAG 仿真逻辑

Atomic ALU

(R-M-W)

乘法器

(32x32 bit)

辅助 寄存器组

(32 bit)

FPU

CPU

寄存器总线

Data Bus(数据总线)

系统控制

时钟管理 Watchdog 定时器*3

PIE

(96个中断)

2017/3/1 Wednesday

4

ePWM eCAP eQEP 12- bit ADC 片上外设 CAN2.0B

2017/3/1 Wednesday

8

二、F28335的ALU

1、ALU

•输入 •输出

程序总线 数据总线

32 16

2、ACC

•AH:AH.MSB,AH.LSB •AL:AL.MSB,AL.LSB

32

Shift R/L (0-16)

32 32

32

XT (32) or T/TL

MULTIPLIER

32 x 32 or Dual 16 x 16

(一)、 F28335的内部结构

一、F28335的基本组成 二、F28335的总线结构

一、F28335的基本组成

Program Bus(程序总线)

A(19-0)

Sectored Flash

(256KW)

SARAM

(34KW)

BootROM OTPROM

(8KW)

(1KW)

存储器

DMA

6 CH.

DMA总线

I 2C SCI SPI McBSP

88*GPIO

Program Bus(程序总线)

一、F28335的基本组成(续) Sectored Flash

DSP程序中寄存器如何分配地址

DSP程序中寄存器如何分配地址DSP中某个寄存器怎么分配地址?在数据⼿册中,我们常常看到说某个寄存器地址是多少,以TMS320F28335的时钟系统寄存器为例,在ti公司给出的⼿册我们看到如下信息我们看到HISPCP中的地址为0x701A;翻看ti公司给的⼀系列库我们发现其寄存器定义在结构体SYS_CTRL_REGS中,经过⼀系列查找,我们发现SYS_CTRL_REGS映射的是 DSP281x_Headers_nonBIOS.cmd⽂件中,其对应的地址映射是System:0我们发现其⾸地址是0x7010;⽽resvd1不代表任何含义,仅仅⽅便位置偏移设数,⽽结构体中HISPCP前⾯有10个16进制变量,HISPCP是第11个,在C语⾔中,下标是从0开始,所有HISPCP是第10个,也就是A,那么HISPCP地址是0x701A,查看芯⽚数据发现吻合,相关内容,可参考下⾯⼀⽚博客⽤过F2812的朋友⼀定会对cmd⽂件很熟悉,因为这个⽂件中为每个程序和数据分配了相应的地址。

我们常⽤的cmd⽂件包括连个:(1) DSP281x_Headers_nonBIOS.cmd(2) F2812_EzDSP_RAM_lnk.cmdDSP281x_Headers_nonBIOS.cmd上⾯第⼀个⽂件⽤于对DSP外设分配地址,⽽第⼆个⽂件是为系统的程序和数据分配地址。

当然,如果DSP的外设地址我们⽤C 语⾔已经⾃⼰定义,那第⼀个⽂件我们就可以不⽤了,笔者就是⾃⼰定义的,所以没有⽤到第⼀个⽂件。

对于为什么要⾃⼰定义外设寄存器以及中断地址,有这⼏个原因:(1) ⾃⼰定义外设寄存器地址可以很清楚的了解DSP的⼯作原理,虽然这样很耗费时间,但是会了解到DSP的中断等等是怎么⼯作的。

(2) 因为DSP外设寄存器地址的分配时采⽤寄存器形式分配到的。

举个例⼦,以sci串⼝通信为例,其他的外设以及中断都⼀样。

⽐如我们设置波特率,肯定是设置某个寄存器的相应位来实现。

F28335的位域和寄存器结构的学习

F28335的位域和寄存器结构的学习以前一直在使用C5000系列的DSP,具体型号为VC5509A。

不久前也接触了C2000系列的28335。

在学习这款DSP的过程中,感觉和C55X差别不少。

特别是在编程方面,两者对底层寄存器的操作方式有很大区别。

F28335拥有很丰富的外设资源,这也就说明了它必然有比较复杂的存储单元映射和中断管理体系。

关于存储单元映射,TI提供了C/C++ Header files文件来管理,这个和CSL有些类似,但和CSL并不完全相同。

首先在CSL使用最多的是宏伪指令,而在F28335中使用最多的是位域和寄存器文件结构体。

同CSL 相比,有利也有弊。

在下面会详细列出两者的优缺点。

这是我认为的最有用的一块,它为F28335提供了一个硬件抽象层,使得编程者无需去记忆大量寄存器名称。

而且它提供了一个很好的编程规范,是以后编程很好的参考。

所以花了一番功夫研究位域和寄存器文件结构体。

现将其中重要的部分描述如下:1、宏与位域和寄存器结构优缺点的对比传统的#define宏提供了地址编号或者是指向寄存器地址的指针。

这样做的优点是:1、简单,快,很容易通过键盘敲出。

2、变量名和寄存器名一致,容易记忆。

缺点是:1、具体位不容易获取,必须生成掩码来对某个位操作。

2、不能够在CCS的watch window中方便的显示某些位的值。

3、宏不能够利用CCS的自动完成功能。

4、宏不能对相同外设重复使用。

位域和寄存器结构体的优点如下:1、TI提供,无需自己编写,规范性好。

2、容易读、写、升级,效率高。

3、很好的利用了CCS的自动完成功能。

4、可以在CCS的观察窗口中查看具体位的值。

2、实现位域和寄存器文件结构体的具体步骤(以SCI外设为例)1)、定义一个寄存器文件结构体,SCI外设的寄存器在结构体中按实际的地址由低向高依次列出。

/******************************************************************** * SCI header file* Defines a register file structure for the SCI peripheral********************************************************************/ #define Uint16unsigned int#define Uint32unsigned longstruct SCI_REGS {Uint16 SCICCR_REG SCICCR;// Communications control register Uint16 SCICTL1_REG SCICTL1; // Control register 1Uint16 SCIHBAUD; // Baud rate (high) registerUint16 SCILBAUD; // Baud rate (low) registerUint16 SCICTL2_REG SCICTL2; // Control register 2Uint16SCIRXST_REG SCIRXST; // Receive status registerUint16SCIRXEMU; // Receive emulation buffer register Uint16SCIRXBUF_REG SCIRXBUF; // Receive data bufferUint16rsvd1; // reservedUint16SCITXBUF;// Transmit data bufferUint16SCIFFTX_REG SCIFFTX; // FIFO transmit registerUint16SCIFFRX_REG SCIFFRX; // FIFO receive registerUint16SCIFFCT_REG SCIFFCT; // FIFO control registerUint16rsvd2; // reservedUint16rsvd3; // reservedUint16SCIPRI_REG SCIPRI; // FIFO Priority control};2)、上面的定义本身并没有建立任何的变量,只是定义了一个结构体,而并没有实例化。

28335实用板硬件用户手册

研旭淘宝店铺:

MFSXA

63

MDXA

65

MCLKXA

67

SCIRXDB

69

CANRXA

71

SDA

73

GPIO60

75

DGND

77

DVDD3.3

79

CAN 引脚接口 CON1 如表 7-2 所示:

CANL1

1

64 66 68 70 72 74 76 78 80

8K ×16 位

OPT ROM

1K ×16 位

其中 FLASH、OPT ROM 受口令保护,可以保护用户程序。

片上外设

PWM

12 路

HRPWM

6路

QEP

2 通道

ADC

2×8 通道,12 位,80ns 转换时间,0—3V 输入量程

SCI

3 通道

MCBPS

2 通道

CAN

80ns)。 底板有两组电机控制接口,每组可以控制一台 3 相电机。 底板有 8 个发光二极管,可用于调试程序和监测等。 底板有一个 X1226 实时时钟和 1KB 的 I2C EEPROM。 底板有手动复位按钮,方便用户复位操作。 底板提供总线开放,数据线 16 位,地址线 20 位,特殊功能引脚,方便用户二次开

底板地址、数据以及特殊引脚接口(实用板 JP1)如表 7-1 所示:

D0

1

D2

3

D4

5

D6

7

D8

9

2Leabharlann D14D3

6

D5

8

D7

10

D9

10

D10 D12 D14 D16 D18 D20 D22 A00 A02 A04 A06 A08 A10 A12 A14 A16 A18 A20 A22 CS0 CS7 XHOLDA XWE XREADY SPISTATE SPISOMIA

5、F28335存储器以及地址分配分析

0x10 0000 0x20 0000 0x30 0000

图右半部分主要是通过XINTF外扩的存储 空间,当片内数据存储空间不够的时候,我 们可以外扩存储器。其中的保留区是为片内 存储器所占的地址。

有些空间是Protected,表示这三个空间 存放的寄存器不可以随便配置,若要对存放 在Protected空间内的寄存器进行配置,要进 行EALLOW声明,以EDIS结束声明,起到保护 和警示作用。

TMS320F28335存储器空间分配

F28335的CPU内核本身并不包含任何存储器,通过总线访问芯片内部集成的 或者外部扩展的存储器。其总线按照改进哈佛结构,分成了32位的数据读、数据写 数据总线,地址读、地址写总线,公用数据总线即程序总线,包括22位的程序地址 总线,用于传送程序空间的读/写地址,32位读数据程序总线,用于读取程序空间 的指令或者数据。

TMS320F28335内存保护特点

地址范围

0x00 0000

0x00 0040 0x00 0400 0x00 0800 0x00 0D00

0x00 0E00 0x00 2000

0x00 5000

0x00 6000 0x00 7000 0x00 8000 0x00 9000 0x00 A000 0x00 B000 0x00 C000 0x00 D000 0x00 E000 0x00 F000 0x01 0000

F28335BOOTROM引导模式和程序

F28335BOOTROM引导模式和程序28335使用串口烧写程序串口烧写是一种相对较方便的烧写方式,相对于仿真器或是CAN烧写,相对于仿真器或是USB转CAN的设备,串口是一种非常廉价的烧写方式,而且也不需要安装专业的集成开发环境CCS等,但是不能实现在线调试,因此也只适用于程序基本不用再调整或大批量的场合。

F28335的存储器映射图如下:BOOTROM 是一块8K X 16的只读存储器,位于地址空间0x3FE000~0x3FFFFF,片内BOOTROM在出厂时固化了引导加载程序以的存储映射如下图所示:及定点和浮点数据表,片上BOOTROM1.内BOOT ROM数学表:在BOOT ROM中保留了4K X 16位空间,用以存放浮点和IQ数据公式表,这些数据公式表有助于改善性能和节省SARAM空间。

向量表:CPU向量表位于ROM存储器0x3FE000~0x3FFFFF段内,如下图所示。

复位后,当VMAP=1,ENPIE=0(PIE向量表禁止)时,该向量表激活。

在内部BOOT ROM引导区中能够调用的唯一向量就是位于0x3FFFC0的复位向量。

复位向量在出厂时被烧录为直接指向存储在BOOT ROM 空间中的InitBoot函数,该函数用于开启引导过程。

然后通过通用I/O引脚上的检验判断,决定具体引导模式。

引导模式与控制引脚之间的关系如下图所示:Bootloader特性:Bootloader是位于片上引导ROM中的在复位后执行的程序,用于在上电复位后,将程序代码从外部源转移到内部存储器。

这允许代码暂时存储在掉电不丢失数据的外部存储器内,然后被转移到高速存储器中执行。

引导ROM中的复位向量将程序执行重定向至InitBoot函数。

执行器件初始化之后,bootloader将检查GPIO引脚的状态以确定您需要执行哪种引导模式。

这些选项包括:跳转至闪存、跳转至SARAM、跳转至OTP或调用其中一个片上引导加载例程。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

本课程是依照南京研旭电气科技有限公司推出的TMS320F28335至尊板来进 行详细讲解的,如果在学习过程中遇到任何疑问欢迎与我们进行联系沟通。

本教程是依照南京研旭电气科技有限公司推出的 TMS320F28335至尊板来进行详细讲解的。本书详细地阐 述了TMS320F28335 DSP处理器内部各功能模块的硬件结 构、工作原理、资源分配、功能特点以及应用等内容,同时 每个模块都配了实验教程,方便学生掌握提高。 本书配套资料包括:书中所有实例例程、烧写软件工具、 配套PPT、配套视频以及常用的调试工具软件,读者可以在 研旭电气提供的交流论坛(www.armdsp,net )相关版块或

第五讲:存储器以及地址分配

1、TMS320F28335存储器空间分配 2、TMS320F28335存储器保护特点 3、XINTF接口

4、相关寄存器介绍

XINTF接口

XINTF每个区域都有一个片选信号线,当对某个区域进行读写访问时,就要将信号 线置低,某些器件将两个区域的片选信号通过内部的与逻辑连接在一起,从而形成一个 共用的信号线,在这样的情况下,同一存储器可以与两个 XINTF 区域相连,要区分这两

TMS320F28335内存保护特点

地址范围 片上存储器 数据空间 0x00 0000 0x00 0040 0x00 0400 0x00 0800 0x00 0D00 M0 SRAM(1k X16) M1 SRAM(1k X16) PF0 PIE 中断 向量表 0x00 0E00 0x00 2000 0x00 5000 0x00 6000 0x00 7000 0x00 8000 0x00 9000 0x00 A000 0x00 B000 0x00 C000 0x00 D000 0x00 E000 0x00 F000 0x01 0000 0x30 0000 0x33 FFF8 0x34 0000 0x38 0000 0x38 0400 0x38 0800 0x3F 8000 0x3F 9000 0x3F A000 0x3F B000 0x3F C000 0x3F E000 0x3F FFFC PF0 保留 PF3 DMA PF1 PF2

FLASH的最后8个(0X33FFF8~0X33FFFF),也就是密码区中(PWL),通过密码匹配(PMF),

可以解锁器件。 如果密码保护区中的128位数都是同一个数,这个器件不受保护,全是同一个数有两种可能,一 种全为0,另一种全为1,一个新的FLASH或FLASH被擦除后,就变为全1了,这样只要读一下密码区, 就能破解了,还一种情况,就是全为0,这时候器件是被加密了,但是不管密钥寄存器的内容是什么, 器件都处在加密状态,即该器件无法解锁了,这时候芯片就被完全锁住了。因此不要用全0作为密码。 如果在擦除FLASH的期间,芯片复位了,那这个芯片的密码就不确定了,也不能解锁。

个区域就要与区分这两个区域的逻辑电路相连。

XINTF的存储器的三个区域中的任何一个都可通过编程设定独立的等待时间,选通 信号建立时间及保持时间,每个区域的读写操作都可以配置成不同的等待时间,另外可 以通过XREADY信号线延长等待时间,XINTF接口的这些特性允许其访问不同速率的外 部存储器设备。通过XTIMINGx寄存器可配置每个区域的等待时间及选通信号的建立于保 持时间。XINTF接口的访问时序是以内部时钟XTIMCLK位基准的,XTIMCLK信号频率可 配置为系统时钟SYSCLKOUT的频率或其一半。

保留

保留

图右半部分主要是通过XINTF外扩的存储 空间,当片内数据存储空间不够的时候,我 们可以外扩存储器。其中的保留区是为片内 存储器所占的地址。 有些空间是Protected,表示这三个空间 存放的寄存器不可以随便配置,若要对存放

保留

FLASH(256K X16) 128位 密码

外部区域6扩展 1M X16 CS6 外部区域7扩展 1M X16 CS7

保留

在Protected空间内的寄存器进行配置,要进

行EALLOW声明,以EDIS结束声明,起到保护 和警示作用。

TMS320F28335内存保护特点

用户用来解锁的寄存器为密钥寄存器,在存储空间映射地址为0x0000

0AE0~0x0000 0AE7,该区域受EALLOW保护。当这个128位的密钥位全1时,密钥寄

存器不需要与之匹配。当一开始调试FLASH区加密的芯片的时候,仿真器取得CPU 的控制权需要一定的时间,在此期间,CPU 正在开始运行,并且会执行保护加密区 的操作,这个操作会引起仿真器断开连接,有两个方法可以解决这个问题。 1、采用Wait-in-Reset仿真模式,这种方法是让芯片保持在复位状态直到仿真器得到 控制,这种方法要求仿真器要能支持这种模式。 2、采用“Branch to check boot mode”引导。这个方法会持续不停的让引导模式选 择引脚。可以选择这种引导模式,一旦仿真器通过重新映射PC到另外的地址或者改 变引导模式选择引脚以进入引导而进行连接。 如何杜绝由于程序原因导致FLASH加密?

南京研旭电气科技有限公司 F接口

XINTF接口

第五讲:存储器以及地址分配

1、TMS320F28335存储器空间分配 2、TMS320F28335存储器保护特点 3、XINTF接口

4、相关寄存器介绍

相关寄存器介绍

本讲到此结束 感谢大家的收看

学习、使用中如遇任何问题,可与我们联系 嵌嵌论坛: 研旭旗舰店(天猫):

F28335 DSP就是采用多级流水线的增强的哈佛总线结构,能够并行访问程

序和数据存储空间。在F28335芯片内部集成了大量的不同的存储介质,F28335片

上有256K×16位的FLASH,34K×16位的SARAM,8K×16位的BOOT ROM, 2K×16位的OPT ROM,采用统一寻址方式(程序、数据和I/O统一寻址),从而 提高了存储空间的利用率,方便程序的开发。除此之外,F28335 DSP还提供了外 部并行扩展接口XINTF,可进一步外扩存储空间。

《手把手教你学DSP——基于TMS320F28335》配套视频资料

第五讲

存储器以及地址分配

南京研旭电气科技有限公司

公司网站: 天猫旗舰店: 学习论坛: 交流邮箱:zqj518@

0x10 0000 0x20 0000 0x30 0000

保留

TI OTP(1k X 16) 用户 OTP(1k X 16) 保留 L0 SARAM(4k X 16) L1 SARAM(4k X 16) L2 SARAM(4k X 16) L3 SARAM(4k X 16) 保留 Boot ROM(8k x 16) BROM 向量表-ROM(32 X 32)

网站免费获取。

本书可作为DSP开发应用的入门级教材,也可作为其他 层次DSP开发应用人员的参考手册。

第五讲:存储器以及地址分配

1、TMS320F28335存储器空间分配 2、TMS320F28335存储器保护特点 3、XINTF接口

4、相关寄存器介绍

TMS320F28335存储器空间分配

TMS320F28335存储器空间分配

F28335的CPU内核本身并不包含任何存储器,通过总线访问芯片内部集成的或

者外部扩展的存储器。其总线按照改进哈佛结构,分成了32位的数据读、数据写数

据总线,地址读、地址写总线,公用数据总线即程序总线,包括22位的程序地址总 线,用于传送程序空间的读/写地址,32位读数据程序总线,用于读取程序空间的指 令或者数据。 改进的哈佛结构其实是综合了冯.诺依曼结构的简洁,哈佛结构的高效。F28335 应用32位数据地址和22位程序地址控制整个存储器以及外设,最大可寻址4M字的数

L0 SRAM (4k X 16) L1 L2 L3 L4 L5 L6 L7 SRAM SRAM SRAM SRAM SRAM SRAM SRAM (4k (4k (4k (4k (4k (4k (4k X X X X X X X 16) 16) 16) 16) 16) 16) 16) 外部区域0扩展 4K X16 CS0

据空间和4M字程序空间。

第五讲:存储器以及地址分配

1、TMS320F28335存储器空间分配 2、TMS320F28335存储器保护特点 3、XINTF接口

4、相关寄存器介绍

TMS320F28335内存保护特点

代码安全模块CSM--代码安全模块(CSM)是F28335上程序安全性的主要手段,它禁止未授权的 用户访问片内存储器,禁止私有代码的复制或者逆向操作。 安全模块限制CPU去访问片内存储器。实际上,对各种存储器的读写访问都是通过JTAG端口或 外设来进行的,而CSM模块所谓的代码安全性主要是针对片内存储器的访问来定义的,用来禁止未经 授权去复制私人代码或数据。 通过一个128位的密码(相当于8个16位的字)来对安全区来进行加密或解密。这段密码保存在

片外扩展存储器

程序空间

F28335对数据空间和程序空间进行了统 一编址,图5.1的映射表就像是各个空间的地

保留

M0向量 RAM(32 X 32)

图一样,有些空间既可以作为数据空间也可 以作为程序空间,有些空间只能作为数据空

0x00 4000 0x00 5000

保留

间,有些空间是受到密码模块保护,有些空 间地址是作为保留的,具体内容就要仔细对 照这个地图来进行查阅了。