Latch +

latch的工作原理

Latch的工作原理1. 引言Latch(锁存器)是一种用于存储和传输数据的电子元件,常被用于数字电路和计算机系统中。

它是一种时序电路,可以在特定的时刻将输入信号锁定并保持输出状态。

Latch的工作原理相对简单,但对于理解数字电路和计算机系统的基本原理非常重要。

2. Latch的基本结构和类型Latch通常由多个逻辑门(如与门、或门、非门)组成,其中包括存储器单元和控制电路。

根据存储器单元的不同,Latch可以分为SR Latch、D Latch、JK Latch 等多种类型。

2.1 SR LatchSR Latch是最简单的Latch类型之一。

它由两个交叉连接的NOR门组成。

其中一个门的输出连接到另一个门的输入,反之亦然。

SR Latch有两个输入端(S和R)和两个输出端(Q和Q’)。

2.2 D LatchD Latch是一种常用的Latch类型,它由一个与门和一个非门组成。

D Latch有一个数据输入端(D)、一个使能端(E)和一个输出端(Q)。

2.3 JK LatchJK Latch是一种更复杂的Latch类型,它由两个与门和两个非门组成。

JK Latch 有两个输入端(J和K)、一个使能端(E)和一个输出端(Q)。

3. SR Latch的工作原理下面将详细解释SR Latch的工作原理,以帮助理解Latch的基本原理。

3.1 输入和输出SR Latch有两个输入端(S和R)和两个输出端(Q和Q’)。

输入端的输入信号可以是高电平(1)或低电平(0),输出端的输出信号也可以是高电平(1)或低电平(0)。

3.2 真值表SR Latch的工作原理可以通过真值表来描述。

下面是SR Latch的真值表:S R Q Q’0 0 Q Q’0 1 0 11 0 1 01 1 X X根据真值表,可以得出以下结论: - 当S和R都为0时,Q和Q’的状态保持不变。

- 当S为0,R为1时,Q为0,Q’为1,表示Latch被复位(reset)。

锁存器Latch和触发器Flip-flop有何区别

锁存器Latch和触发器Flip-flop有何区别锁存器Latch概述锁存器(Latch)是一种对脉冲电平敏感的存储单元电路,它们可以在特定输入脉冲电平作用下改变状态。

锁存,就是把信号暂存以维持某种电平状态。

锁存器的最主要作用是缓存,其次完成高速的控制器与慢速的外设的不同步问题,再其次是解决驱动的问题,最后是解决一个I/O口既能输出也能输入的问题。

锁存器是利用电平控制数据的输入,它包括不带使能控制的锁存器和带使能控制的锁存器。

锁存器Latch结构latch:锁存器,是由电平触发,结构图如下:锁存器latch的优缺点优点:1、面积比ff小门电路是构建组合逻辑电路的基础,而锁存器和触发器是构建时序逻辑电路的基础。

门电路是由晶体管构成的,锁存器是由门电路构成的,而触发器是由锁存器构成的。

也就是晶体管-》门电路-》锁存器-》触发器,前一级是后一级的基础。

latch完成同一个功能所需要的门较触发器要少,所以在asic中用的较多。

2、速度比ff快用在地址锁存是很合适的,不过一定要保证所有的latch信号源的质量,锁存器在CPU设计中很常见,正是由于它的应用使得CPU的速度比外部IO部件逻辑快许多。

缺点:1、电平触发,非同步设计,受布线延迟影响较大,很难保证输出没有毛刺产生2、latch将静态时序分析变得极为复杂触发器Flip-flop结构lip-flop:触发器,是时钟边沿触发,可存储1bitdata,是register的基本组成单位,结构图如下:flip-flop的优缺点优点:1、边沿触发,同步设计,不容易受毛刺的印象2、时序分析简单缺点:1、面积比latch大,消耗的门电路比latch多锁存器Latch和触发器flipflop的区别1、锁存器Latch和触发器flipflop锁存器能根据输。

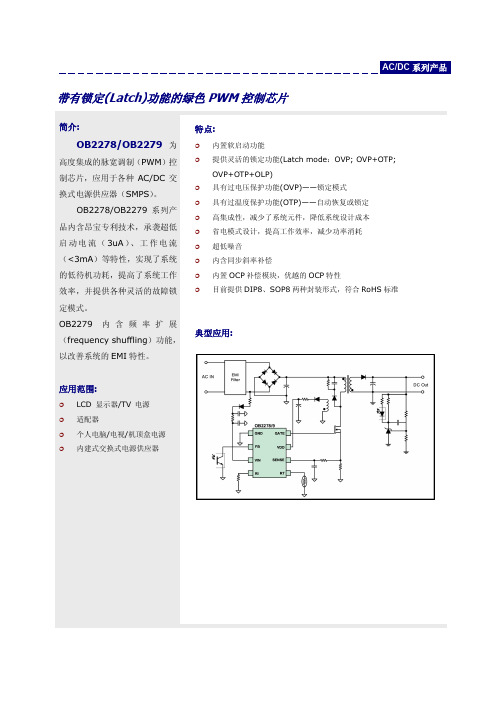

带有锁定 (Latch) 功能的绿色 PWM 控制芯片

带有锁定(Latch)功能的绿色 PWM 控制芯片

简介:

OB2278/OB2279 为

高度集成的脉宽调制(PWM)控 制芯片,应用于各种 AC/DC 交 换式电源供应器(SMPS)。

OB2278/OB2279 系列产 品内含昂宝专利技术,承袭超低 启 动 电 流 ( 3uA )、 工 作 电 流 (<3mA)等特性,实现了系统 的低待机功耗,提高了系统工作 效率,并提供各种灵活的故障锁 定模式。 OB2279 内 含 频 率 扩 展 (frequency shuffling)功能, 以改善系统的 EMI 特性。

典型应器/TV 电源 适配器 个人电脑/电视/机顶盒电源 内建式交换式电源供应器

特点:

内置软启动功能 提供灵活的锁定功能(Latch mode:OVP; OVP+OTP;

OVP+OTP+OLP) 具有过电压保护功能(OVP)——锁定模式 具有过温度保护功能(OTP)——自动恢复或锁定 高集成性,减少了系统元件,降低系统设计成本 省电模式设计,提高工作效率,减少功率消耗 超低噪音 内含同步斜率补偿 内置 OCP 补偿模块,优越的 OCP 特性 目前提供 DIP8、SOP8 两种封装形式,符合 RoHS 标准

latch工作原理

latch工作原理Latch(锁存器)是一种基本的数字电路元件,常用于存储和传输数据。

它的工作原理相对简单,但在数字系统中起着重要的作用。

一、什么是Latch?Latch是一种双稳态(bistable)电路,它可以在两个稳定状态之间切换。

这两个状态通常被称为“Set”和“Reset”。

Latch可以通过输入信号的变化来切换状态,并且可以保持其状态,即使输入信号不再存在。

二、Latch的基本结构Latch通常由两个互补的非门(NOR)或非门(NAND)构成。

这两个门的输出互相连接,形成一个反馈回路。

其中一个门被称为“Set”输入,另一个门被称为“Reset”输入。

当“Set”输入为高电平时,Latch进入“Set”状态;当“Reset”输入为高电平时,Latch进入“Reset”状态。

三、Latch的工作原理当Latch处于“Set”状态时,其输出为高电平。

这是因为“Set”输入信号将一个门的输入引脚拉低,导致该门的输出为高电平,从而使反馈回路中的另一个门的输入引脚也为高电平,进而保持输出为高电平。

当Latch处于“Reset”状态时,其输出为低电平。

这是因为“Reset”输入信号将一个门的输入引脚拉低,导致该门的输出为高电平,从而使反馈回路中的另一个门的输入引脚也为低电平,进而保持输出为低电平。

四、Latch的应用Latch在数字系统中有广泛的应用。

其中一个常见的应用是作为存储元件,用于存储数据。

通过控制“Set”和“Reset”输入信号,可以将数据写入Latch,并在需要时读取出来。

Latch还可以用于实现寄存器、计数器和其他复杂的数字逻辑电路。

Latch还可以用于时序电路中的状态保持。

在时序电路中,Latch可以用来存储和传输状态信息,以确保正确的时序操作。

五、总结Latch是一种重要的数字电路元件,具有存储和传输数据的功能。

它的工作原理基于两个稳定状态之间的切换,通过控制输入信号来改变状态。

科鲁兹LATCH接口安全座椅安装指南

LATCH/ISOFIX接口儿童安全座椅安装作业早就想给宝宝买一个儿童安全座椅,方便以后我一个人送他到去幼儿园。

科鲁兹车上带LATCH/ISOFIX接口,于是就想找一个同样带这种接口的座椅!网上查了一下LATCH和ISOFIX的区别!如下:欧美各国在交通安全防护上的观念似乎总是领先国内许多,儿童应使用儿童安全座椅早就是理所当然的事儿,且除了儿童安全座椅本身的检测标准之外,这几年欧美纷纷订定了儿童安全座椅在汽车上固定方式的标准-在美国叫做,在欧洲叫做-要求所有汽车都必须提供符合规定的扣件和拴带,能够让驾驶人快速、稳固、正确地固定儿童安全座椅。

从2002年9月1日开始,美国便规定几乎所有种类的小客车必须提供LATCH系统的儿童安全座椅固定方式。

什么是LATCH系统?LATCH是“Lower Anchors and Tethers for CHildren”的简称,中文翻译起来很生硬,叫做「儿童使用的下扣件和拴带」,简称合在一起“LATCH”这个字也是扣拴的意思。

在汽车内完整的LATCH系统包括位在座位下方两侧,座垫和椅背交接处有两个固定在座椅上的下扣件(Lower Anchors),后座椅背上方则有一条固定在车上的拴带(Tether)。

下扣件和拴带的接头都有标准化规格,符合LATCH系统的儿童安全座椅,在座椅两侧和椅背上方同样位置也有三个拴带和兼容的接头,父母只要把儿童安全座椅放在汽车座椅上,喀、喀、喀三声就稳稳地装好了,而且几乎没有装错的可能性。

根据美国一项调查数据显示,旧式使用汽车安全带固定的儿童安全座椅,至少有67%没有被正确地使用,反而让坐在安全座椅上的儿童承受更大受伤的风险。

这主要是因为汽车安全带本来的目的就不是用来固定儿童安全座椅,安全带的形式、扣合方式也各不相同,儿童安全座椅本身的扣合方式设计更是五花八门,组合起来就有非常多可能性,父母常常得先要搞清楚其车上的安全带应该用哪种方式固定儿童安全座椅,需不需要什么特别的技巧或工具。

latch电路原理

latch电路原理Latch电路原理引言:Latch电路是一种重要的数字电路组件,广泛应用于计算机、通信设备、数字电子仪器等领域。

本文将介绍Latch电路的原理、工作方式以及应用。

一、Latch电路的定义和作用Latch电路是一种存储器件,用于存储和保持数字信号的状态。

它具有两个稳定的输出状态,分别为“置位”和“复位”状态。

当输入信号满足特定条件时,Latch电路保持输出状态不变,直到另一个条件满足,才会发生状态变化。

因此,Latch电路可以用来存储信息、实现状态保持和信号传输等功能。

二、SR Latch电路SR Latch电路是最简单的一种Latch电路。

它由两个交叉耦合的NAND门或NOR门组成。

其中,S端口(Set)用于置位,R端口(Reset)用于复位。

当S=1、R=0时,Latch电路处于置位状态;当S=0、R=1时,Latch电路处于复位状态;当S=0、R=0或S=1、R=1时,Latch电路保持原来的状态。

三、Gated SR Latch电路Gated SR Latch电路在SR Latch电路的基础上增加了一个使能端口(G)。

当G=1时,Gated SR Latch电路的输入才起作用,根据S和R的值来决定Latch电路的输出;当G=0时,无论S和R的值如何,Latch电路的输出都保持不变。

四、D Latch电路D Latch电路是一种常用的Latch电路,也被称为数据存储器。

它由两个交叉耦合的NAND门或NOR门组成。

D端口(Data)用于输入数据,使能端口(E)用于控制数据存储。

当E=1时,D Latch 电路的输入才起作用,D的值被存储在Latch电路中;当E=0时,无论D的值如何,Latch电路的输出都保持不变。

五、Latch电路的应用1. 存储器:Latch电路可以用来实现存储器的功能,如SRAM(静态随机存储器)中常用的6T SRAM单元就是由SR Latch电路构成的。

明白latch

设Process1 got resource_1 at level06 Process2 got resource_2 at level09

Page: 4

Latch <<Oracle 8i Internal Service >>读后手记

Process1 need resource_2 at level05 (so it is spin) so, It must wait for Process2 to release level09's latch

------------------------------------------------

|Level15 |

|

|

|

------------------------------------------------

|Level09 |

| Process2 |

|

------------------------------------------------

如果不是这样我们可以很简单的模拟一个deadlock

------------------------------------------------

|

| resource_1 | resouce_2 | resource_3 |

------------------------------------------------

|Level05 |

|

|

|

------------------------------------------------

|Level01 |

|

|

|

-----------------------------------------------Process1需要resouce_2的Level01到Level06的latch话,必须使用no-wait Latch

FPGA和Verilog设计中的latch锁存器的问题讲解

FPGA和Verilog设计中的latch锁存器的问题讲解FPGA和Verilog设计中的latch锁存器的问题⼀直都知道fpga中有latch这么⼀回事,但是⼀直都不太清楚到底什么是锁存器,它是怎么产⽣的,它到底和寄存器有多少区别,它怎么消除。

为什么说他不好?⼀,是什么锁存器是⼀种在异步时序电路系统中,对输⼊信号电平敏感的单元,⽤来存储信息。

⼀个锁存器可以存储1bit的信息,通常,锁存器会多个⼀起出现,如4位锁存器,8位锁存器。

锁存器在数据未锁存时,输出端的信号随输⼊信号变化,就像信号通过⼀个缓冲器,⼀旦锁存信号有效,则数据被锁存,输⼊信号不起作⽤。

因此,锁存器也被称为透明锁存器,指的是不锁存时输出对于输⼊是透明的。

⼆锁存器与寄存器的区别:两者都是基本存储单元,单锁存器是电平触发的存储器,触发器是边沿触发的存储器。

本质是,两者的基本功能是⼀样的,都可以存储数据。

意思是说⼀个是组合逻辑的,⼀个是在时序电路中⽤的,时钟出发的。

三,锁存器的危害:对⽑刺敏感,不能异步复位,所以上电以后处于不确定的状态;Latch会使静态时序分析变得⾮常复杂;在PLD芯⽚中,基本的单元是由查找表和触发器组成的,若⽣成锁存器反⽽需要更多的资源。

第三条也是最基本的原因。

四,产⽣的原因********ps重重之重上⾯说了那没多只是觉得⽹上的没把锁存器说明⽩。

下⾯的才是重点。

1,case2,if-------else if3,always@(敏感信号表)五解决1.case——————加default:关于defalut的情况:⼀是可以default:data=1‘bx;这个x表⽰未知,在综合时可以避免产⽣锁存器。

在仿真时是红线表⽰。

⼆是default:data=0;这样产⽣⼀个默认的情况。

2.if-----------------------⼀定要有else语句。

3.always---------如是说道:在赋值表达式右边参与赋值的信号都必须在always@(敏感电平列表)中列出。

latch(latch)写法

latch(latch)是一种流行的编程技术,它可以在特定条件下触发或执行一些操作。

它通常用于控制流程,实现任务的串行执行或并行执行。

本文将从以下几个方面介绍latch写法的基本原理、使用场景和实际应用。

一、latch写法的基本原理1.1 latch的概念latch是一种同步工具,用于通知其他线程在一组线程等待完成后继续执行。

它类似于一个门闩,当条件满足时,门闩打开,允许其他线程通过。

1.2 latch的实现latch的实现通常具有两个主要方法:countDown()和aw本人t()。

countDown()用于减少计数器的值,而aw本人t()用于等待计数器达到零。

当计数器值为零时,等待的线程将继续执行。

1.3 latch的特点latch具有以下特点:一次性,即一旦打开,就不能关闭;非阻塞,即countDown()和aw本人t()方法不会阻塞线程的执行;可重用,即计数器可以多次减少和等待。

二、latch写法的使用场景2.1 多线程任务协调在多线程编程中,经常需要协调多个任务的执行顺序。

latch可以很好地实现这一目的,例如在主线程等待所有子线程执行完毕后再继续执行。

2.2 并发流程控制在并发编程中,latch可以用于控制并发流程,保证一组任务的顺序执行或并行执行。

2.3 等待事件触发latch还可以用于等待外部事件的触发,例如等待一组异步任务完成后再执行后续操作。

三、latch写法的实际应用3.1 并行计算在并行计算中,latch可以用于等待所有计算节点完成后汇总结果,提高计算效率。

3.2 服务启动和关闭在服务启动和关闭过程中,latch可以用于等待所有必要的资源初始化或销毁完成后再继续执行。

3.3 网络通信在网络通信中,latch可以用于等待数据接收完毕后再进行处理,保证数据的完整性和一致性。

latch写法是一种灵活、高效的编程技术,适用于多种场景和应用。

通过灵活运用latch,可以简化并发编程的复杂性,提高代码的可读性和可维护性。

latch的工作原理

latch的工作原理

latch的工作原理

1)内存Q里的锁标志位,要读写内存内容,必须先拿到钥匙,用来保证串行。

同时为了提高效率,用多个atch对应内存的多个区域(高效的设计)。

启发:设计时,并发控制只有一个程序,但可以分多个区域,这样既保证串行也保证并发。

如从号码池取号,可以分成8个号段,保证不重复取号,也有一定的并发性。

2)无队列的、轻量级锁。

一般过程是请求->spin->再请求

3)通过设置变量为0或非0,来表示Latch是否已经被取得

4)具体过程:获取latch->如果以占用,则spinCPU(独占)->再次获取->达到spin次数上线->休眠,释放CPU(释放cpu会进行上下文切换,cpu工作线程相关信息切换,属高耗操作)。

如果spin的次数过多,则cpu独占的过多,导致cpu使用率高。

5)结构

latch:bufferi读写标志位,拥有lath才可以读写ouffer;

bucket:桶,fileld+blockld的hash结果分组,相同的hash分到一个桶里。

buffer cache chain:bucketx对应的ouffer们的链表。

关系:

一个latch可以控制多个bucket

一个buckety对应一个ouffer cache chain。

latch

感谢观看

及物动词

vt. 1.用闩把...闩上;用碰锁把...锁上 Don't forget to latch the door before you go to bed. 睡觉前别忘了闩门。

不及物动词

vi. 1.闩上;用碰锁锁上 This door won'tlatchproperly. 这门闩不牢。 2.抓住;占有;理解;缠住[(+onto/upon)] John was very lucky to have latched onto the office with a river view. 约翰非常幸运,占了一间能看到河的办公室。 He alwayslatchedon to me when he saw me at a party. 他在聚会上一看见我就总是缠着我。

latch

英语单词

01 英英释义

03 及物动词

目录

02 名词 04 不及物动词

英 [læ tʃ]美 [læ tʃ] n.门闩;碰锁;弹簧锁v.上闩;缠着;明白

英英释义

Noun: Verb:Fra bibliotek名词n. [C] 1.闩;门闩;窗闩 The repairman installed an iron latch on the door. 修理工在门上安了铁门闩。 Please leave the doorlatchshut. 请把门闩上。 The sound of thelatchroused him. 门闩的声音惊醒了他。 Position thelatchon the hood inner panel. 把锁闩定位在引擎罩内板上。 2.碰锁,弹簧锁

fpga latch case语句

在FPGA设计中,latch通常是由于不完整的条件覆盖在case语句或if-else语句中产生的。

latch是一种存储元件,它有两个稳定的状态,但在没有明确的输入时,它会保持其当前状态。

这与触发器(flip-flop)不同,触发器总是在时钟边沿改变其状态。

当你编写case语句时,如果不覆盖所有的可能情况,那么编译器可能会推断出一个latch来保持那个未明确的状态。

但在FPGA设计中,这通常是不希望的,因为latch会消耗额外的资源,并可能导致不可预测的行为。

例如,考虑以下VHDL代码:vhdl复制代码process (sel)begincase sel iswhen"00" => out_sig <= '0';when"01" => out_sig <= '1';-- when "10" => ... -- 这里缺失了一个情况when"11" => out_sig <= '0';when others => null; -- 这不会阻止latch的生成end case;end process;在上述代码中,sel为"10"的情况没有被明确处理,因此编译器可能会生成一个latch来处理这种情况。

为了避免生成latch,你应该:1. 确保case语句覆盖所有的可能情况。

2. 如果你不关心某些输入值,明确地将它们设置为一个默认值。

3. 使用when others来处理所有未明确列出的情况,并为输出分配一个明确的值。

修复后的代码可能如下:vhdl复制代码process (sel)begincase sel iswhen"00" => out_sig <= '0';when"01" => out_sig <= '1';when"10" => out_sig <= '0'; -- 添加了缺失的情况when"11" => out_sig <= '0';when others => out_sig <= 'X'; -- 对于不可能的情况,设置为'X'或其他值end case;end process;但请注意,即使你使用了when others,如果在其他情况中你没有明确地覆盖所有的输入,那么仍然可能会生成latch。

锁存器与触发器(D类)

锁存器Latch概述锁存器(Latch)是一种对脉冲电平敏感的存储单元电路,它们可以在特定输入脉冲电平作用下改变状态。

锁存,就是把信号暂存以维持某种电平状态。

锁存器的最主要作用是缓存,其次完成高速的控制器与慢速的外设的不同步问题,再其次是解决驱动的问题,最后是解决一个I/O口既能输出也能输入的问题。

锁存器是利用电平控制数据的输入,它包括不带使能控制的锁存器和带使能控制的锁存器。

锁存器Latch结构latch:锁存器,是由电平触发,结构图如下:锁存器latch的优缺点优点:1、面积比ff小门电路是构建组合逻辑电路的基础,而锁存器和触发器是构建时序逻辑电路的基础。

门电路是由晶体管构成的,锁存器是由门电路构成的,而触发器是由锁存器构成的。

也就是晶体管-》门电路-》锁存器-》触发器,前一级是后一级的基础。

latch完成同一个功能所需要的门较触发器要少,所以在asic中用的较多。

2、速度比ff快用在地址锁存是很合适的,不过一定要保证所有的latch信号源的质量,锁存器在CPU设计中很常见,正是由于它的应用使得CPU的速度比外部IO部件逻辑快许多。

缺点:1、电平触发,非同步设计,受布线延迟影响较大,很难保证输出没有毛刺产生2、latch将静态时序分析变得极为复杂触发器Flip-flop结构lip-flop:触发器,是时钟边沿触发,可存储1bitdata,是register的基本组成单位,结构图如下:flip-flop的优缺点优点:1、边沿触发,同步设计,不容易受毛刺的印象2、时序分析简单缺点:1、面积比latch大,消耗的门电路比latch多锁存器Latch和触发器flipflop的区别1、锁存器Latch和触发器flipflop锁存器能根据输入端把结果自行保持;触发器是指由时钟边沿触发的存储器单元;由敏感信号(电平,边沿)控制的锁存器就是触发器;2、写电路时,产生锁存器的原因if语句中,没有写else,默认保持原值,产生锁存器,可能不是想要的结果;case语句中,没有写完整default项,也容易产生锁存器;例子:always@(aorb)beginif(a)q=b;end产生了锁存器,如下:没有锁存器的情况always@(aorb)beginif(a)q=b;elseq=0;end3、避免使用D锁存器,尽量使用D触发器D锁存器moduletest_latch(y,a,b); outputy;inputa;inputb;regy; always@(aorb)beginif(a==1’b1)y=b;endendmoduleD触发器moduletest_d(y,clk,a,b); outputy;inputclk;inputa;inputb;regy; always@(posedgeclk)beginif(a==1‘b1)y=b;endendmodule从图8可知,例10对应的电路是D触发器。

标准设计说明(Latch)

结构部标准设计说明——(Latch)1.概述本文件描述了结构部员工在设计中需要大家遵守的规范。

2.目的设计产品时有相应的依据,保证项目开发设计过程中数据的统一性,互换性,高效性。

提高工作效率。

3.具体内容Latch的分类:1)按组装形式分,可分为:A、装在Base_rear_hsg上,常应用于外置电池中。

B、组装在Batt_front_hsg上,常应用于内置电池中,具体如下图:Latch组装在Base_rear_hsg上Latch组装在Batt_front_hsg上2)按性能分:弹性式、滑移式。

3-1 功能描述:Latch在手机结构中起连接主机后壳和电池,保证电池装入后配合到位,前后、左右、上下没有自由活动的空间,防止在落下实验中Latch断裂。

3-2 与周边器件的装配关系:如以下图一、二所示图一:主机后壳、弹簧、锁扣、电池装配结构示意图(Explode)图二:主机后壳、弹簧、锁扣、电池装配结构示意图(Dorado)3-3(在整机中的定位方式):a、Latch弹性臂定位,大部分机型采用这种定位方式,优点是有利于拆装,如下图三:b、Latch顶部卡钩定位,优点是节省空间。

3-4 “标准化(理想)模型”的设计指导:关键尺寸、公差,与其他器件的配合间隙尺寸参考a. 尺寸(A)建议采用0.15mm,尺寸(B)建议采用0.05mm;b. LATCH属于运动件,设计时要将运动的各个位置考虑进去,计算好它的行程,防止LATCH已经运动到终点,而电池还不能弹出的情形。

LATCH装配尺寸图LATCH装配尺寸图3-6典型材料应用:Latch的注塑材料通常采用POM(DOPONT500),下面为POM 500T 美国杜邦技术指数表:。

flip-flop与latch的区别

flip-flop 与latch的区别《数字设计--原理和实践》(John )书中的定义:All digital designers use the name flip-flop for a sequential device that noramlly samples its inputs and changes its outputs only at times determined by a clocking signal. On the other hand, most digital designers use the name latch for a sequential device that watches all of its inputs continuously and changes its outputs at any time, independent of a clocking signal. Some text books and digital designers may (incorrectly) use the name “flip-flop” for a device that we call a “latch”.结论-- 寄存器(register):一般是指边沿触发的触发器,概念有点模糊。

-- 锁存器(latch):电平触发。

-- 触发器(flip-flop):边沿触发-- 在fpga中一般避免用latch,因为在FPGA中触发器资源丰富,不用白不用,latch由于是电平触发的,相对触发器来说容易产生毛刺,电路不稳定。

latch的优点是完成同一个功能所需要的门较触发器要少,所以在asic中用的较多。

关于flip-flop,网上辞典的解释:(1)An electronic circuit that alternates between two states. When current is applied, it changes to its opposite state (0 to 1 or 1 to 0). Made of several transistors, it is used in the design of static memories and hardware registers.(2)A digital logic circuit that can be in one of two states which it switches (or “toggles”) between under control of its inputs. It can thus be considered as a one bit memory. Three types of flip-flop are common: the SR flip-flop, the JK flip-flop and the D-type flip-flop (or latch).Early literature refers to the “Eccles-Jordan circuit” and the “Eccles-Jordan binary counter”, using two vacuum tubes as the active (amplifying) elements for each bit of information storage. Later implementations using bipolar transistors could operate at up to 20 million state transitions per second as early as 1963.。

数字电路中latch的优缺点

网络错误421请刷新页面重试持续报错请尝试更换浏览器或网络环境

数字电路中latch的优缺点

缺点: latch是电平触发,无法实现同步操作,与我们正常的时序逻辑电路设计思路不符。 latch会对输入电平敏感,受布线延迟影响较大,比较容易导致输出有毛刺产生。 latch会导致静态时序分析和DFT会很复杂。 在ASIC中使用latch的集成度比DFF高,但在FPGA中正好相反,因为FPGA中没有标准的latch单元,但有DFF单元,一个LATCH需要多个 LE才能实现。

latch电路原理

latch电路原理Latch电路是一种经典的数字电路,其原理是通过电子元件的开关状态来存储和保持信息。

它通常由两个交叉连接的反馈电路组成,其中一个电路被用作输入,另一个电路用于存储输出。

Latch电路在数字计算机和其他电子设备中被广泛应用,它们提供了一种便捷的方式来存储和传输数据。

在Latch电路中,通常使用两个互补的开关来控制输入和输出。

这两个开关可以是传统的开关,也可以是晶体管等电子元件。

在正常情况下,当输入开关打开时,输出开关关闭,反之亦然。

当输入开关发生变化时,如果输入开关关闭,输出开关会保持关闭状态,不受输入开关的影响。

这种状态的保持使得Latch电路可以存储和传输信息。

Latch电路的一个重要特点是它的稳定性。

一旦输入开关发生变化,输出开关的状态会立即改变,并保持在新的状态上。

这种稳定性使得Latch电路可以用作存储器件,将输入信息保持在输出端口上,直到下一次输入变化。

这种稳定性也使得Latch电路在数字电路中具有重要的应用,例如在时序电路和存储器中。

另一个重要的特点是Latch电路的可逆性。

当输入开关再次发生变化时,输出开关将返回到之前的状态。

这种可逆性使得Latch电路可以用于反转信号的状态,从而实现逻辑门电路的功能。

通过适当的连接和控制,Latch电路可以实现与门、或门、非门等逻辑门电路的功能,从而实现复杂的数字逻辑运算。

除了稳定性和可逆性,Latch电路还具有高速和低功耗的特点。

由于它是由电子元件构成的,Latch电路的响应速度非常快,可以达到纳秒级的级别。

同时,由于Latch电路只在输入变化时才会消耗能量,因此它的功耗非常低,非常适合用于电池供电或需要节能的应用中。

在实际应用中,Latch电路有许多不同的实现方式。

最常见的是SR Latch和D Latch两种类型。

SR Latch使用两个交叉连接的反馈电路来实现稳定性和可逆性。

它具有两个输入端口(Set和Reset)和两个输出端口(Q和Q')。

Latch的使用

Latch的使用详解Latch是Oracle为了保护内存结构而发明的一种资源。

常应用于并发的用户从磁盘中读取或写入数据。

最常见的latch争用有:共享池中latch的争用和数据缓冲池中latch的争用。

1、共享池中latch的争用:共享池中如果存在大量的SQL语句被反复分析,就很可能造成latch争用和长时间等待,常见的现象是由于没有绑定变量造成的。

SQL> select * from v$latchname where name like 'library cache%'在分析系统性能时,如果有library cache这样的latch争用,基本可以断定是共享池中出现的问题,这种问题是由SQL语句导致的,比如没有绑定变量或者一些存储过程被反复分析。

2、数据缓冲池中latch的争用:当很多用户一起去访问某几个数据块时,就会导致数据缓冲池的latch争用,主要有两种:buffer busy waits 和cache buffer chain。

访问频率高的数据块被称为热块(hot block),当很多用户同时访问相同的数据块就会导致热块问题,造成热块的原因可能是数据库设置导致或者重复执行的SQL频繁的访问一些相同的数据块导致的。

2.1查询当前数据库最繁忙的Buffer:TCH(Touch)表示访问次数越高,热点块竞争问题就存在select *from (select addr,ts#,file#,dbarfil,dbablk,tchfrom x$bhorder by tch desc)where rownum<11;2.2结合dba_extents查询得到这些热点Buffer来自哪些对象select e.owner, e.segment_name, e.segment_typefrom dba_extents e,(select *from (select addr, ts#, file#, dbarfil, dbablk, tchfrom x$bhorder by tch desc)where rownum<11)bwhere e.relative_fno=b.dbarfiland e.block_id<=b.dbablkand e.block_id+e.blocks>b.dbablk;2.3结合SQL视图可以找到操作这些对象的相关SQL,然后通过优化SQL减少数据的访问,或者优化某些容易引起争用的操作(如connect by等操作)来减少热点块竞争break on hash_value skip 1select /*+ rule */ hash_value,sql_textfrom v$sqltextwhere (hash_value, address)in (select a.hash_value, a.addressfrom v$sqltext a,(select distinct a.owner, a.segment_name, a.segment_typefrom dba_extents a,(select dbarfil, dbablkfrom (select dbarfil, dbablkfrom x$bhorder by tch desc)where rownum<11)bwhere a.relative_fno = b.dbarfiland a.block_id <= b.dbablkand a.block_id + a.blocks > b.dbablk) bwhere a.sql_text like ‘%’ || b.segment_name || ‘%’and b.segment_type = ‘TABLE’)order by hash_value, address, piece;。

数字电路中应避免产生不必要的锁存器Latch

数字电路中应避免产⽣不必要的锁存器Latch锁存器(Latch)是数字逻辑电路中很重要的⼀种基本电路,常见的锁存器包括三个端⼝:数据输⼊⼝、数据输出⼝、使能端。

当使能端为⾼电平时,输⼊⼝的数据直接送到输出⼝,此时输⼊输出⼝可以看成是直接连通的;当使能端为低电平时,输出⼝的数据保持之前的数据不变,⽆论输⼊⼝的数据怎么变化,输出都保持不变,就是把原来的状态锁存下来了(所以才叫锁存器)。

锁存器与触发器的区别在于:锁存器是电平触发,⽽触发器是边沿触发。

锁存器在不锁存数据时,输出随输⼊变化;但⼀旦数据锁存时,输⼊对输出不产⽣任何影响。

在FPGA电路设计中,不规范的描述语⾔可能会产⽣意想不到的锁存器,⽽设计者往往并没有注意到⾃⼰的设计会被综合出锁存器,导致综合出的电路出现逻辑错误。

在数字电路中,产⽣意外的锁存器的情况⼀般有以下两种:1. if……else……结构中缺少else先看⼀个实际的例⼦:⽤quartus综合⼀下这两个电路,看看产⽣的RTL图是怎样的:左边的电路:右边的电路:由RTL视图可以直观的看出,左边的电路没有⽣成锁存器,⽽右边的电路⽣成了⼀个我们不想要的锁存器(q1$latch)。

左边的电路是时序逻辑,⽣成触发器,⽽触发器是有使能端(en)的,使能端⽆效时就可以保存数据,⽆需锁存器。

右边的电路是组合逻辑,在en为低电平时,输出q1要保持不变,⽽组合逻辑没有存储元件,只能⽣成锁存器来保持数据。

所以在时序逻辑中,不完整的 if…else… 结构并不会⽣成锁存器,⽽组合逻辑中不完整的 if…else… 结构就会⽣成锁存器。

为了避免我们设计的组合逻辑中出现不想要的锁存器,在使⽤ if…else…结构时⼀定要写完整。

把刚才例⼦中右边的电路写完整,并查看其RTL视图如下:写完整后,就没有⽣成锁存器,⽽是⽣成了⼀个⼆选⼀的选择器,这正是我们想要设计的。

2. case结构中的分⽀没有包含所有情况且没有default语句case结构中⼀般要加上default语句,以保证出现意外情况也可以作出相应的反应。

latch写法

6 ball latch 碰球 7 blade latch 开关保险销 ; 闸刀保险梢 8 bobbin case latch 梭匣柄 9 door latch 排料启闭器 ; 门闩 【例句】 1 She listened for his key in the latch. 她留神听着他把钥匙插入门锁。 2 He lifted the latch and opened the door. 他拉起门闩开了门。 3 You left the latch off the gate and tan you leave the door on the latch so I can get in? 你别锁门好不好?我好进来。 5 Foley followed Albert through the gate, taking care to close the latch. 福利随着艾伯特进了大门,留心地把门闩上。 6 "Lift the latch," called out the grandmother, "I am too weak, and cannot get up." “把门闩拉开,”奶奶喊道,“我太虚弱了,起不来。” 7 Astronaut Pierre Thuot tried to latch the 15-foot robotic arm onto the satellite. 宇航员皮埃尔·索特想要把这个长 15 英尺的机械手安到人造卫星上。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Implementation of Gabor-type Filters on Field Programmable Gate Arrays Ocean Y.H.Cheung1,Philip H.W.Leong1,Eric K.C.Tsang2and Bertram E.Shi2 1The Chinese University of Hong Kong,Shatin,New Territory,Hong Kong,2University of Science and Technology,Clear Water Bay,Kowloon,{yhcheung,phwl}@.hk,{eeeric,eebert}@t.hkAbstractAlthough biological visual systems have been widelystudied at the physiological,psychophysical and functionallevels,our understanding of its signal processing mecha-nisms is still very rudimentary.One of the obstacles in thisprocess is the difficulty of dealing with the vast amounts ofprocessing necessary to test real-time temporal models ofthe visual system.In this paper,wefirst present a high per-formance FPGA-based cellular neural network which im-plements a Gabor-typefilter.This is a building block ele-ment which we intend to use with different parameters tomodel cells in V1.The application of the Gabor-typefil-ter in a neuromorphic system consisting of an analog VLSIretina chip interfaced to our Gabor chip is also presented.The retina chip serves as an imager and transmits its out-put to the FPGA via an address event representation(AER)transceiver[1].Using AER,multiple chips can be inter-connected in a modular network to form large networksof Gabor chips.By combining both analog VLSI chips anddigital chips(e.g.DSP chips,microprocessors,and FPGAchips),we hope to make real-time implementations of earlyvision models and visualize their temporal behaviour,whileachieving a level of performance,integration,power con-sumption,area andflexibility not possible using any tech-nology in isolation.1.ImplementationA Gaborfilter can be represented by thecomplex valued convolutional kernel g(x,y)=1 2πσ2e−x2+y22σ2e j(ωx x+ωy y)[4]whereσ,ωx,ωy are real con-stants.The even kernel is cosine modulated and the odd kernel is sine modulated and hence twofilers are90de-grees out of phase.Pollen and Ronner suggested that adjacent neurons in visual cortex have even and odd sym-metry[5]and therefore Gabor-filters can model receptive field profiles in the visual cortex[3].Cellular neural net-works(CNN)can be used to implement Gabor-typefil-ters[6].Figure1.Architecture of Euler core Let u ij,x ij and y ij represent the input,state and output pixels of an image respectively.The dynamics of the CNN are governed by the differential equationτdx ijdt=f ij=−x ij+kl∈N ra kl y kl+kl∈N rb kl u kl(1)where a kl represents the feedback template and b kl repre-sents the control template.By changing the values of the templates,the Gabor-typefilter can be tuned to respond to different orientations,bandwidth and spatial scales.The approach used in our FPGA implementation of the Gabor-typefilter was to develop a pipelined datapath which can perform the required complex multiply accumulate op-erations for the solution of Equation1using Euler’s method. Inputs,templates and outputs are stored in internal memo-ries of the FPGA so that the coefficients that control ori-entation and spatial scale are easily adjusted.A single core can process data in a time multiplexed manner with differ-ent parameters.Multiple cores can be also used to increase performance.Gabor-typefilters have a complex valued convolutional kernel,and a data format with complex values is used.As fixed-point arithmetic implementations require less area, two’s complement fractions are used.A core is built basedFigure2.Architecture of silicon retina system on16-bitfixed-point arithmetic and the Euler integration method.The data format consists of two16-bit words which are used for the even and odd kernels of equation1.The 16-bit words consist of a4-bit integer part and12-bit frac-tional part.For the VGA interface,image pixels are repre-sented by an8-bit number.Our Gabor-typefilter is used as the processing unit in a silicon retina system as shown infigure2.In the system,a silicon retina,leaky integrators,Gabor-typefilter core,and spike generator are integrated.The silicon retina is a cus-tom designed analog VLSI chip[7]and the other compo-nents are implemented on an FPGA.2.ResultsIn[2],Choi et.al.presented an analog VLSI retina system with a Gabor-typefilter VLSI chip.Our FPGA-based Gabor-typefilters are fully compatible with this sys-tem since both chips use the same AER input/output for-mat.The Euler core was implemented using VHDL on a Celoxica RC200platform which is populated with a Xilinx XC2V1000-4.For1024pixel frames,our entire implemen-tation uses1962slices,operates at120MHz and achieves 23,000Euler iterations over one frame per second.The power consumption of the analog Gabor chip (0.25µm technology at2.5−3V)and its peripher-als as described in[2]is44.1mW.The power consump-tion of the FPGA chip(0.12µm technology at1.5V) and all the peripherals on the RC200platform in the re-set state is1.929W.This increases to1.946W when the Euler core is processing.A ring pattern in black with a white background is dis-played on a LCD monitor and captured using the silicon retina.The image is processed by the FPGA-based Gabor-typefilter processor using templates corresponding to dif-ferent orientations.Results are shown infigure33.ConclusionAn implementation of Gabor-type Filters onfield pro-grammable gate arrays using cellular neural network(CNN) architecture is pared to other analog VLSI10203051015202530102030510152025301020305101520253010203051015202530Figure3.Odd(upper)and even(bottom)out-put for ring pattern input with vertical(left)and45degree(right)orientations.implementations of Gabor-typefilters,our implementation has advantages of shorter design time,scalability andflex-ibility.The design can accommodate different array sizes, as well as simultaneous computation of multiplefilter out-puts tuned to different orientations and bandwidths.References[1]K.Boahen.Point-to-point connectivity between neuromor-phic chips using address events.IEEE Trans.Circuits Syst.II, 47:416–434,May2000.[2]T.Y.W.Choi,B.E.Shi,and K.Boahen.An on-off orienta-tion selective address event representation image transceiver chip.IEEE Transactions on Circuits and Systems-I:Regular Papers,51:342–353,2004.[3]J.Daugman.Two-dimensional spectral analysis of cortical re-ceiptivefield profiles.Vision Research,20:847–856,1980. [4] D.Gabor.Theory of communication.J.Inst.Elect.Eng.Lon-don,93:429–457,1946.[5] D.A.Pollen and S.Ronner.Phase relationship between ad-jacent simple cells in the visual cortex.Science,212:1409–1411,1981.[6] B.Shi.Gabor-typefiltering in space and time with cellularneural networks.IEEE Trans.Circuits Syst.I,45:121–132, Feb1998.[7]K.A.Zaghloul.A silicon implementation of a novel modelfor retinal processing.PhD thesis,University of Pennsylva-nia,2001.。