latch up分析

芯片上电时序latch up大电流

芯片上电时序latch up大电流一、概述在现代社会中,芯片技术被广泛应用于各个领域,如通信、计算机、电子设备等。

而芯片在运行过程中可能会出现一些问题,比如Latch-up现象。

Latch-up是指芯片在工作时由于某些原因导致出现异常电流,这种异常电流可能对芯片造成严重损坏。

芯片上电时序Latch-up 大电流成为了一个重要的研究课题。

二、芯片上电时序Latch-up大电流的原因1.器件自身结构缺陷芯片中的器件可能存在结构缺陷,比如P-N结区域不良、金属引线焊点不良等,这些缺陷会导致芯片在上电时出现Latch-up现象。

2.工作环境不良芯片在工作时受到电磁干扰、温度变化等环境因素的影响,这些因素可能会导致Latch-up现象的发生。

3.设计缺陷芯片的设计可能存在缺陷,比如电源线路不合理、过电压保护不足等,这些设计缺陷也会导致Latch-up现象的出现。

三、芯片上电时序Latch-up大电流的影响Latch-up现象会使芯片内部出现异常电流,导致芯片的正常工作受到干扰甚至损坏。

而且Latch-up现象还可能会引发芯片周围其他器件的Latch-up现象,进一步扩大了损害范围,因此芯片上电时序Latch-up大电流对芯片的影响是非常严重的。

四、应对策略1.优化芯片设计在设计芯片时应充分考虑芯片在工作时可能遇到的各种环境因素,保证芯片的电路布局合理、电源线路设计完善,避免因设计缺陷导致Latch-up现象的发生。

2.加强工艺控制在制造芯片时应加强工艺控制,保证芯片中器件的质量,避免器件结构缺陷导致Latch-up现象的出现。

3.优化工作环境对芯片的工作环境进行优化,保证芯片在工作时受到最小的电磁干扰、温度变化等环境因素的影响,降低Latch-up现象发生的可能性。

五、结论芯片上电时序Latch-up大电流是一个复杂的问题,它涉及到芯片本身的结构、工作环境、设计等多个方面。

只有综合考虑这些因素,并在芯片设计、制造、工作过程中采取有效的措施,才能有效地避免Latch-up现象的发生,保障芯片的正常工作和稳定运行。

latch up 原理 -回复

latch up 原理-回复latch up 原理,是指在集成电路中由于不恰当的设计或操作而导致的一个临时的、不可逆转的电气现象。

当发生latch up时,集成电路往往会损坏甚至失效。

因此,了解latch up原理对于集成电路的设计和安全非常重要。

本文将逐步解析latch up原理,帮助读者深入了解这一现象。

首先,我们需要了解latch up的定义。

latch up是指在CMOS集成电路中,当正负输入端的电压超过一个特定的阈值时,导致PNPN结构内部失去控制,集成电路形成一个自维持的失控状态。

这个状态将持续下去,直到外部干扰因素消除或集成电路损坏。

那么,为什么会发生latch up呢?这是因为CMOS集成电路中的PNP 和NPN结构之间的正反馈效应。

当PNP结构的发射极上的电流增加时,会导致NPN结构的基极电流增加,反之亦然。

这种相互关联的正反馈效应可以引起latch up。

接下来,我们来看latch up发生的条件。

latch up需要满足以下两个条件:1. 存在一个PNPN结构,即CMOS集成电路中的PNP和NPN结构。

2. 正反馈效应,即PNP结构上的电流增加会导致NPN结构上的电流增加,反之亦然。

那么,如何避免latch up呢?以下是几个避免latch up的方法:1. 使用良好的电源设计。

电源抗扰度越高,latch up的可能性越小。

例如,可以添加阻抗较高的滤波电容和电感来降低电源的功率噪声。

2. 正确选择工艺和材料。

合理选择工艺和材料,可以减少PNP和NPN 结构之间的正反馈效应。

例如,使用低掺杂的基底可以减小PNPN结构的电流增益。

3. 使用良好的布局设计。

合理规划电路布局,减少PNP和NPN结构之间的相互影响。

例如,将PNP和NPN结构放置在尽可能远的位置,或者采用屏蔽层隔离电路。

4. 使用保护设计。

添加保护电路,当电路出现latch up时能够及时切断电源,以防止电路损坏。

例如,可以添加过电流保护电路或过压保护电路。

LATCH UP 测试分析

LATCH UP 测试LATCH UP 测试。

但是,以前我没做过类似的工作,因为以前的公司的芯片LATCH UP测试都是找宜硕这样的公司进行测试。

LATCH UP测试主要分为VSUPPLY OVER VOLTAGE TEST ,I TEST.I test又分为PIT(POSITIVE I TEST)和NIT(NEGATIVE I TEST)。

不过我们公司还增加了PVT(positive voltage test)和NVT(negative voltage test).在JESD78D规范(这个可以从JEDEC 网站上下到)上提到latch up 的测试流程。

首先待测试的IC 需要经过ATE测试,保证功能是正常的。

然后首先进行I—TEST,如果I—TEST FAIL,那这颗芯片就没PASS,如果通过了I-TEST,然后再进行OVER VOLTAGE TEST; 如果此时IC FAIL,那么这颗芯片就没有通过LATCH UP TEST,这些通过I—TEST 和OVER VOLTAGE TEST的芯片还要再进行ATE测试来确认芯片的功能是否正常.但是好多公司最后的ATE测试都省了。

VSUPPLY OVER VOLTAGE TEST,主要是对芯片的电源引脚进行过压测试,如果芯片有多个电源引脚,每个电源引脚都要进行测试.测试条件:一般是对电压引脚进行一个1。

5X MAX VSUPPLY 的TRIGGER 测试,1)其他引脚接LOGIC HIGH, 2)其他引脚接LOGIC LOW。

这两种情况都要进行测试。

PIT 测试是对除电源和地外的其他I/O引脚进行测试。

电源接VCC,1)所有引脚接LOGIC HIGH, 然后给待测试引脚来一个POSITIVE TRIGGER CURRENT PULSE。

2)所有引脚接LOGIC LOW,然后给待测试引脚来一个POSITIVE TRIGGER CURRENT PULSE。

latch up测试标准

latch up测试标准Latch up是指集成电路中的一种失效现象,当一个晶体管或器件被误用时,或由于外界干扰等原因导致,会出现电流过大的现象,从而导致电路失效或损坏。

Latch up测试是为了验证电路的稳定性和可靠性,以确保电路能够正常工作并长期稳定运行。

Latch up是一种瞬态故障,通常发生在集成电路中存在PNPN结构的电路,例如CMOS电路或双极性晶体管。

这种结构使得电路在特定条件下会形成一个自反馈回路,导致电流大幅度增加,进而导致电路失效。

Latch up测试通常包括以下步骤:1.设计电路:首先,在设计电路时需要充分考虑到避免触发Latch up现象的条件。

例如,采用合适的工艺参数和结构设计,选择适当的尺寸和电流容限,并避免形成PNPN结构的电路。

2.模拟仿真:使用电路仿真软件进行模拟分析,验证设计电路的稳定性和可靠性。

通过模拟仿真,可以观察电路在边界条件下是否可能出现Latch up现象。

3.制造过程控制:在芯片制造过程中,需要严格控制工艺参数和制造流程,以确保电路的稳定性。

例如,控制晶体管制造的掺杂浓度、尺寸和位置,避免PNPN结构的形成。

4.电流注入测试:进行电流注入测试是验证电路是否存在Latchup现象的重要步骤。

通常,将高电压施加到电路的输入、输出端口,然后测量电路中的电流变化。

如果电流显著增加,就说明电路存在Latch up现象。

5.温度测试:温度是影响电路稳定性的重要因素,因此进行温度测试可以验证电路在不同温度条件下的工作情况。

在温度测试中,可以观察电路在不同温度下的电流变化和稳定性。

6.电压应力测试:电压应力测试是在电路上施加不同的电压,并监测电流的变化。

通过电压应力测试,可以验证电路在不同电压条件下的稳定性和可靠性。

7.压耐测试:压耐测试是对电路进行高电压的耐受能力测试。

在压耐测试中,会施加高于设计电压的电压,并观察电路的稳定性和可靠性。

如果电路能够正常工作且没有失效,说明电路具有良好的压耐性能。

latch up原理

latch up原理Latch-Up原理。

Latch-Up是指在CMOS电路中由于PNP和NPN晶体管的基极和集电极之间的相互耦合而导致的一种电路失效现象。

当CMOS电路中的某些条件满足时,会导致PNP和NPN晶体管同时导通,形成一个正反馈回路,导致电路失效。

在本文中,我们将详细介绍Latch-Up原理及其防护措施。

Latch-Up的原理是由于CMOS电路中的PNP和NPN晶体管之间的相互耦合。

当CMOS电路中的两个晶体管之间的电压差超过一定阈值时,会导致PNP晶体管和NPN晶体管同时导通,形成一个正反馈回路。

由于这个正反馈回路的存在,一旦触发Latch-Up现象,电路将失去控制,导致电路失效。

Latch-Up现象会导致CMOS电路的性能下降甚至损坏,因此需要采取一定的防护措施。

首先,可以通过合理设计电路结构来减小PNP和NPN晶体管之间的耦合,减小Latch-Up的可能性。

其次,可以在电路中引入Latch-Up保护电路,如在电路中加入Latch-Up保护二极管来限制PNP和NPN晶体管之间的电压差,从而防止Latch-Up现象的发生。

此外,合理选择工艺和材料也可以减小Latch-Up的发生概率,如采用深亚微米工艺和抗辐射材料。

总之,Latch-Up是CMOS电路中常见的一种失效现象,其原理是由于PNP和NPN晶体管之间的相互耦合导致的。

为了防止Latch-Up现象的发生,我们可以通过合理设计电路结构、引入Latch-Up保护电路以及选择合适的工艺和材料来减小Latch-Up的可能性。

希望本文能够对Latch-Up原理有所了解,并为电路设计和应用提供一定的参考价值。

latch up原理

latch up原理

Latch up原理也被称为“瞬间自锁”,是电路设计和测试中需要特别

注意的一种现象。

简单地说,Latch up是指由于某些原因,一个双极

晶体管(BJT)或MOSFET绝缘体(MOSFET),在其电路中形成一

个临时短路,从而导致器件失效或被损坏。

Latch up现象通常在集成电路中出现,尤其在高密度集成电路中更为

常见。

在模拟电路中,Latch up现象可能会导致噪音增加,失真增加,甚至一些器件被完全烧毁。

因此,Latch up问题对于电路设计师和测

试人员来说是一种常见的故障。

Latch up的原因是多方面的。

通常情况下,它是由于IC中存在两个或多个PN结,以及多种原因所引起的。

例如,设备的工作情况和晶体

管中的电源电压和电流都会影响此现象的出现概率。

超过器件设计的

最大电流和电压也会导致Latch up,此时晶体管就会像一个快速的电

子开关而不是一个灵敏的控制器。

为了避免Latch up的问题发生,电路设计师需要在设计中考虑PN结的位置和数量,并使用合适的工艺方法来降低PN结的电压容限。

此外,还建议通过在PCB上放置解决这一问题的集成电路,使用具有专业化的工具来测试电路,并遵循厂商发布的规定修订。

</p

总之,Latch up是电路设计中需要特别注意和避免的问题。

在设计和测试过程中,通过精确计算和适当的方法来避免Latch up可能发生的影响,可以降低电路故障和失效的概率,从而提高设备的稳定性和可靠性。

latch up原理

latch up原理

latch up是指在集成电路中出现的一种不可逆转的失效状态,

该状态可能会导致电路的损坏。

当一个电路被连入一个能够提供电流的电源时,如果发生latch up,电路中的二极管或晶体

管将失去对输入电压的控制,从而导致电路中的电流迅速增大,最终可能会引起电压降和电流增加,从而损坏电路。

latch up的发生通常涉及到PN结中的电流增益效应。

PN结是

半导体器件中的一个常见结构,在正向偏置下,电子会从n区域注入到p区域中,形成电流。

而在反向偏置下,接近PN结

的区域的电子会移动到p区域中,同时空穴会移动到n区域中,这会导致电流增大。

正常情况下,这种电流增益效应不会引起严重的问题。

然而,当一些特殊条件下,这种电流增益效应可能会被放大,导致latch up的发生。

当输入电压超过某个边界值时,可能会

触发PN结中的电流增益效应,进而引发latch up。

一旦latch up发生,电路中的电流将极大增加,超过了正常工作范围,

可能会导致电路元件的烧毁。

为了预防latch up的发生,可以采取一系列措施。

例如,可以

通过设计时避免过高的功率和过大的电流,采用合适的材料和工艺以降低PN结的电流增益效应,或者使用特殊的结构设计

来防止latch up的发生。

总结来说,latch up是一种集成电路中的失效状态,它可能导

致电路损坏。

它的发生与PN结中的电流增益效应有关,通过合适的设计措施可以预防latch up的发生。

latch-up版图

latch-up原理分析

I n Out N+ P+ P+ Q1 Q2 N+ N+ P+

R w ell N w ell P- e p i

R su b P+s u b

华侨大学厦门专用集成电路系统重点实验室

Copyright by Huang Weiwei

latch-up原理分析

I n Out N+ P+ P+ Q1 Q1 Q2 OUT R su b P+s u b R su b Q2 OUT N+ N+ P+ R w ell

R su b

Q2

华侨大学厦门专用集成电路系统重点实验室

Copyright by Huang Weiwei

latch-up原理分析

I n Out N+ P+ P+ Q1 Q2 N+ N+ P+ R w ell N w ell P- e p i R su b P+s u b

Latch up的具体原因5 5 产生Latch up

OUT Q1

R w ell

R su b

Q2

华侨大学厦门专用集成电路系统重点实验室

Copyright by Huang Weiwei

latch-up原理分析

I n Out N+ P+ P+ Q1 Q2 N+ N+ P+ R w ell N w ell P- e p i R su b P+ s u b

华侨大学厦门专用集成电路系统重点实验室

Copyright by Huang Weiwei

latch-up保护方法

latch up 原理

latch up 原理latch up是一种常见的电路现象,特别是在模拟电路中,它会导致电路性能的恶化,甚至可能导致电路的崩溃。

本文将介绍latch up 的原理、现象、危害以及预防措施。

latch up是由于电路中的晶体管或其他电子元件在特定电压下导通,形成了一个或多个连续的电子通道,导致电路中的其他元件无法正常工作。

通常,latch up的产生需要两个条件:一是电路中存在连续的电流通路;二是电路中的电压达到特定值,使得电子在通道中的传输速度超过信号的传播速度。

latch up发生后,电路的性能会受到严重影响。

首先,latch up 会导致电路的延迟增加,从而影响电路的工作频率。

其次,latch up 还会导致电路的噪声容限降低,使得电路对噪声的敏感度增加。

此外,latch up还会导致电路的功耗增加,从而影响电路的散热性能。

latch up不仅会影响电路的性能,还可能导致电路的崩溃。

当latch up持续存在时,它会不断消耗电路中的电源和地电平,导致电源和地之间的电压波动,从而影响电路中的其他元件。

此外,latch up 还可能导致电路中的其他电子元件过热,从而引发火灾等安全问题。

四、预防措施为了防止latch up的发生,我们可以采取以下措施:1. 优化电路设计:在电路设计中,应避免使用连续的电流通路,避免使用高电压和高电流的工作模式。

同时,应合理分配电源和地的位置,以减少电源和地之间的干扰。

2. 使用抗latch up材料:在选择电子元件时,应选择具有抗latch up特性的材料,如低导通电压、低导通电阻的晶体管等。

3. 增加去耦电容:在电路中增加去耦电容可以减少电源和地之间的干扰,从而减少latch up的发生。

4. 调试和测试:在电路调试和测试过程中,应使用示波器等工具监测电路中的电压和电流变化,及时发现和处理latch up问题。

总之,latch up是一种常见的电路现象,它会导致电路性能的恶化,甚至可能导致电路的崩溃。

latch_up分析

闩锁效应(latch up)闩锁效应(latch up)是CMOS必须注意的现象,latch我认为解释为回路更合适,大家以后看到latch up就联想到在NMOS与PMOS里面的回路,其实你就懂了一半了.为什么它这么重要因为它会导致整个芯片的失效,所以latch up是QUAL测试的一种,并且与ESD(静电防护)紧密相关。

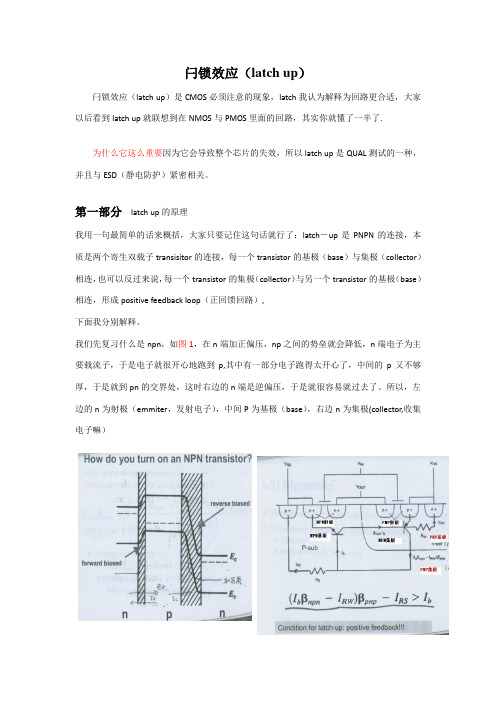

第一部分latch up的原理我用一句最简单的话来概括,大家只要记住这句话就行了:latch-up是PNPN的连接,本质是两个寄生双载子transisitor的连接,每一个transistor的基极(base)与集极(collector)相连,也可以反过来说,每一个transistor的集极(collector)与另一个transistor的基极(base)相连,形成positive feedback loop(正回馈回路),下面我分别解释。

我们先复习什么是npn,如图1,在n端加正偏压,np之间的势垒就会降低,n端电子为主要载流子,于是电子就很开心地跑到p,其中有一部分电子跑得太开心了,中间的p又不够厚,于是就到pn的交界处,这时右边的n端是逆偏压,于是就很容易就过去了。

所以,左边的n为射极(emmiter,发射电子),中间P为基极(base),右边n为集极(collector,收集电子嘛)理解了npn,那么pnp就好办,如图2。

图2清楚的表示了latch up的回路。

左边是npn,右边是pnp图3是电路示意图。

大家可以看出,P-sub既是npn的基极,又是pnp的集极;n-well既是既是pnp的基极,又是npn的集极,所以说,每一个transistor的集极(collector)与另一个transistor的基极(base)相连。

那么电流怎么走呢比如在P+加5V-->电洞被从P+推到N well-->越过n well再到p sub-->这个时候,大家注意,电洞有两条路可走,一是跑到NMOS的N+,二是跑到旁边的Nwell,nwell比n+深,当然更好去,所以电洞又回去了。

latch up标准

latch up标准Latch-up是一个电路问题,可能会导致芯片失效,因此在芯片的可靠性测试中是一个很重要的问题。

带有负反馈的集成电路在不适当的使用下可能引起电路中的正反馈回路,使其失去控制,这种情况称为Latch-up。

Latch-up出现在芯片设计不合理或者工艺制备工艺不合理的情况下,Latch-up会导致芯片销毁。

因此,研究Latch-up现象并提高集成电路的可靠性,是集成电路工业和学术界都十分关注的问题。

Latch-up的现象和成因Latch-up的发生表现为电路的电压和电流异常增大,导致芯片工作不正常,性能下降,甚至烧毁芯片。

Latch-up的形成主要是由于CMOS工艺兼容性等方面的原因,导致PNP及NPN晶体管集成电路中的短路问题。

CMOS技术在很大程度上取代了传统的NMOS技术,CMOS电路中经常使用P-型场效应晶体管,使得Latch-up问题变得更加复杂。

CMOS集成电路中,源漏极之间有一个隔离电阻,若该电阻失效或范围不够大,定向之间的反馈回路就会让某一个晶体管变成双极晶体管,当该点电流过大时就会导致芯片失效。

还有一些因素也能触发Latch-up现象,如操作温度、操作电源电压的大小、进入和退出Latch-up的时间等等,这些因素都有可能导致Latch-up的发生。

测试方法与标准Latch-up研究需要精细的实验手段和测试方法。

为了保证实验可重复性,需要遵循ISO 7637、IEC 61000-4-2等标准在电路板中注入不同强度的电源干扰,然后测试芯片的响应情况。

使用器件特征活检,必须采用复杂的特性打印和曲线分析技术进行测试,以识别和量化特定器件的Latch-up行为。

国家实验室的研究人员利用美国无分类信息法最高机密产生的独特电信号,对各种电路进行了Latch-up分析测试。

在这个过程中,研究人员考虑了多种因素,例如工艺、设计、芯片面积和材料。

在实验结果中,他们观察到Latch-up电流可以达到几个安培特级,芯片温度可能会上升到数百摄氏度。

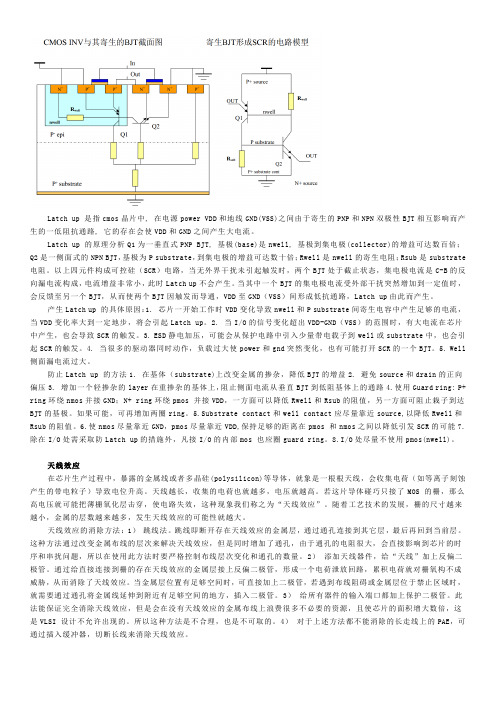

ch7_latch-up_和_GuardRing

Rwell Nwell P- epi

Q2

Rsub P+sub

LOGO

latch-up原理分析

In Out N+ P+ P+ Q1 N+ N+ P+ OUT Q1 Q2 OUT Rsub P+sub Rsub Q2 Rwell

Rwell Nwell P- epi

LOGO

latch-up原理分析

OUT Q1 Rwell CB结反 向电流

Q2的基区注入电流

IB2

Q2

I CE 2

2

则Q1的CE电流等于Q2的基区电流,则Q1的基区电流

Rsub

I B1

2 1

I CE 2

I漏

2 1

R well

则Q1的BE结电压

VBE1

I漏

1 2

所以漏电流大过大,会导致寄生PNP管导通,产生闩锁效应。

LOGO

本章主要内容

Latch-up原理分析

LOGO

OUT Q1

Rwell

4. Latch up产生原因4 当许多驱动器同时动作, 负载过大使VDD或GND突然变化, 也有可能打开SCR的一个BJT。

Rsub

Q2

LOGO

latch-up原理分析

In Out N+ P+ P+ Q1 N+ N+ P+ Rwell Nwell P- epi Rsub P+sub

Rsub

Q2

LOGO

latch-up保护方法

In Out N+ P+ P+ Q1 N+ N+ P+ Rwell Nwell P- epi Rsub P+sub

latch up闩锁效应原理及形成的原因

latch up闩锁效应原理及形成的原因

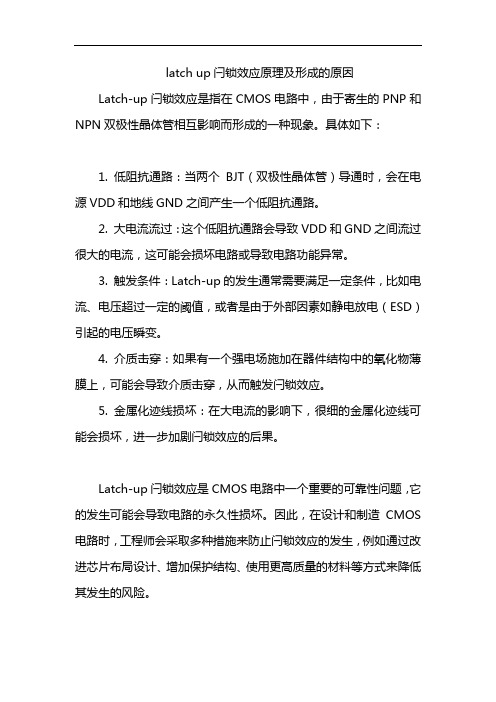

Latch-up闩锁效应是指在CMOS电路中,由于寄生的PNP和NPN双极性晶体管相互影响而形成的一种现象。

具体如下:

1. 低阻抗通路:当两个BJT(双极性晶体管)导通时,会在电源VDD和地线GND之间产生一个低阻抗通路。

2. 大电流流过:这个低阻抗通路会导致VDD和GND之间流过很大的电流,这可能会损坏电路或导致电路功能异常。

3. 触发条件:Latch-up的发生通常需要满足一定条件,比如电流、电压超过一定的阈值,或者是由于外部因素如静电放电(ESD)引起的电压瞬变。

4. 介质击穿:如果有一个强电场施加在器件结构中的氧化物薄膜上,可能会导致介质击穿,从而触发闩锁效应。

5. 金属化迹线损坏:在大电流的影响下,很细的金属化迹线可能会损坏,进一步加剧闩锁效应的后果。

Latch-up闩锁效应是CMOS电路中一个重要的可靠性问题,它的发生可能会导致电路的永久性损坏。

因此,在设计和制造CMOS 电路时,工程师会采取多种措施来防止闩锁效应的发生,例如通过改进芯片布局设计、增加保护结构、使用更高质量的材料等方式来降低其发生的风险。

latch up闩锁效应及解决方法

Latch Up(闩锁)效应及解决方法1. 什么是Latch Up效应?Latch Up效应是一种电子器件中的不可逆转的故障现象,当器件中的电流和电压超过其设计范围时,会导致器件处于一种持续的高电流状态,无法恢复正常工作。

这种效应通常发生在集成电路(IC)中,特别是CMOS(互补金属氧化物半导体)技术的IC中。

Latch Up效应是由于CMOS结构中的PNPN四层结构产生的。

当PNPN结构中的正向电流和反向电流同时大于一定的阈值时,就会导致PNPN结构中的PNP晶体管和NPN晶体管同时进入饱和状态,形成一个正反馈回路。

这个回路会导致电流无限增大,从而造成器件的失效。

2. Latch Up效应的原因Latch Up效应的主要原因有两个:2.1 器件内部结构CMOS器件中的PNPN结构是Latch Up效应的主要原因之一。

当器件内部的PNP晶体管和NPN晶体管同时进入饱和状态时,就会形成一个正反馈回路,导致电流无限增大。

2.2 外部环境因素外部环境因素也可以引起Latch Up效应。

例如,电压过大、电流过大、辐射、温度过高等都可能导致器件发生Latch Up效应。

3. Latch Up效应的影响Latch Up效应会导致器件失效,严重影响器件的性能和可靠性。

具体影响如下:3.1 功耗增加Latch Up效应会使器件处于高电流状态,导致功耗大大增加。

这不仅会浪费能源,还会导致器件发热严重,影响器件的工作温度范围。

3.2 逻辑错误Latch Up效应会改变器件的逻辑状态,导致器件输出错误的逻辑信号。

这会严重影响系统的正常工作。

3.3 器件损坏持续的高电流会导致器件损坏,甚至烧毁。

这不仅会造成经济损失,还会影响系统的可靠性和稳定性。

4. Latch Up效应的解决方法为了避免Latch Up效应对器件造成的影响,可以采取以下解决方法:4.1 增加阻抗通过增加器件内部的阻抗,可以限制电流的流动,从而减轻Latch Up效应的影响。

latch-up描述

Latch up:即闩锁效应,又称自锁效应、闸流效应,它是由寄生晶体管引起的,属于CMOS电路的缺点。

通常在电路设计和工艺制作中加以防止和限制。

该效应会在低电压下导致大电流,这不仅能造成电路功能的混乱,而且还会使电源和地线间短路,引起芯片的永久性损坏。

防止:在集成电路工艺中采用足够多的衬底接触。

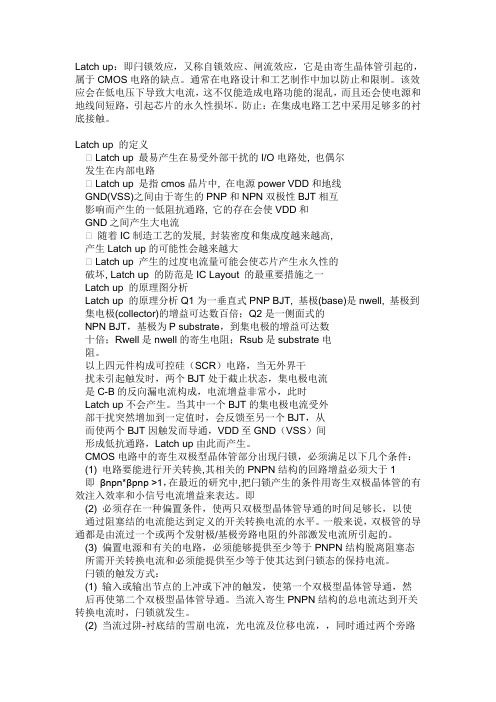

Latch up 的定义Latch up 最易产生在易受外部干扰的I/O电路处, 也偶尔发生在内部电路Latch up 是指cmos晶片中, 在电源power VDD和地线GND(VSS)之间由于寄生的PNP和NPN双极性BJT相互影响而产生的一低阻抗通路, 它的存在会使VDD和GND之间产生大电流随着IC制造工艺的发展, 封装密度和集成度越来越高,产生Latch up的可能性会越来越大Latch up 产生的过度电流量可能会使芯片产生永久性的破坏, Latch up 的防范是IC Layout 的最重要措施之一Latch up 的原理图分析Latch up 的原理分析Q1为一垂直式PNP BJT, 基极(base)是nwell, 基极到集电极(collector)的增益可达数百倍;Q2是一侧面式的NPN BJT,基极为P substrate,到集电极的增益可达数十倍;Rwell是nwell的寄生电阻;Rsub是substrate电阻。

以上四元件构成可控硅(SCR)电路,当无外界干扰未引起触发时,两个BJT处于截止状态,集电极电流是C-B的反向漏电流构成,电流增益非常小,此时Latch up不会产生。

当其中一个BJT的集电极电流受外部干扰突然增加到一定值时,会反馈至另一个BJT,从而使两个BJT因触发而导通,VDD至GND(VSS)间形成低抗通路,Latch up由此而产生。

CMOS电路中的寄生双极型晶体管部分出现闩锁,必须满足以下几个条件:(1) 电路要能进行开关转换,其相关的PNPN结构的回路增益必须大于1即βnpn*βpnp >1,在最近的研究中,把闩锁产生的条件用寄生双极晶体管的有效注入效率和小信号电流增益来表达。

latch up及天线效应

Latch up 是指cmos晶片中, 在电源power VDD和地线GND(VSS)之间由于寄生的PNP和NPN双极性BJT相互影响而产生的一低阻抗通路, 它的存在会使VDD和GND之间产生大电流。

Latch up 的原理分析Q1为一垂直式PNP BJT, 基极(base)是nwell, 基极到集电极(collector)的增益可达数百倍;Q2是一侧面式的NPN BJT,基极为P substrate,到集电极的增益可达数十倍;Rwell是nwell的寄生电阻;Rsub是substrate 电阻。

以上四元件构成可控硅(SCR)电路,当无外界干扰未引起触发时,两个BJT处于截止状态,集电极电流是C-B的反向漏电流构成,电流增益非常小,此时Latch up不会产生。

当其中一个BJT的集电极电流受外部干扰突然增加到一定值时,会反馈至另一个BJT,从而使两个BJT因触发而导通,VDD至GND(VSS)间形成低抗通路,Latch up由此而产生。

产生Latch up 的具体原因:1. 芯片一开始工作时VDD变化导致nwell和P substrate间寄生电容中产生足够的电流,当VDD变化率大到一定地步,将会引起Latch up。

2. 当I/O的信号变化超出VDD-GND(VSS)的范围时,有大电流在芯片中产生,也会导致SCR的触发。

3. ESD静电加压,可能会从保护电路中引入少量带电载子到well或substrate中,也会引起SCR的触发。

4. 当很多的驱动器同时动作,负载过大使power和gnd突然变化,也有可能打开SCR的一个BJT。

5. Well 侧面漏电流过大。

防止Latch up 的方法1. 在基体(substrate)上改变金属的掺杂,降低BJT的增益2. 避免source和drain的正向偏压3. 增加一个轻掺杂的layer在重掺杂的基体上,阻止侧面电流从垂直BJT到低阻基体上的通路4.使用Guard ring: P+ ring环绕nmos并接GND;N+ ring环绕pmos 并接VDD,一方面可以降低Rwell和Rsub的阻值,另一方面可阻止栽子到达BJT的基极。

hbm latchup mm cdm指标

HBM (Human Body Model)、Latchup、MM (Machine Model)和CDM (Charged Device Model)是集成电路领域中常见的指标,它们分别代表着集成电路在不同环境下对静电放电和瞬态电压的抗干扰能力。

本文将从这四个指标的定义、测试方法和应用领域等方面进行详细介绍。

一、HBM指标的定义和测试方法HBM是指人体模型,是用来模拟人体接触集成电路时产生的静电放电现象。

HBM测试是集成电路静电放电抗干扰能力的一项重要测试指标,它通过对集成电路引脚施加不同的静电电压脉冲,来测试集成电路对静电放电的承受能力。

HBM指标是以电压等级和脉冲波形来定义的,常见的HBM等级包括:1.5kV、2kV、4kV等,而脉冲波形包括:100ns、200ns等。

二、Latchup指标的定义和测试方法Latchup是指集成电路在工作过程中由于外部干扰或内部原因产生的永久性失控,导致集成电路无法正常工作的现象。

Latchup测试是用来评估集成电路在不同工作条件下对于外部干扰的抗干扰能力。

Latchup测试主要通过施加不同的电压或电流脉冲来模拟集成电路在工作过程中的外部干扰,从而评估其对Latchup现象的抵抗能力。

三、MM指标的定义和测试方法MM是指机器模型,是用来模拟集成电路在工作环境中对于瞬态电压的抗干扰能力的一项重要指标。

MM测试主要是通过对集成电路引脚施加不同的瞬态电压脉冲,来评估集成电路对瞬态电压的抵抗能力。

MM指标通常包括了电压等级和脉冲波形,如:100V、200V等电压等级,10ns、100ns等脉冲波形。

四、CDM指标的定义和测试方法CDM是指带电器件模型,是用来模拟集成电路在处理、运输、安装等过程中对于静电放电的抵抗能力的指标。

CDM测试是通过对集成电路设备进行特定的静电放电测试,来评估其对静电放电的抵抗能力。

CDM测试通常包括了不同的放电等级和测试条件,如:100V、200V 等放电等级,不同的测试方法和测试设备。

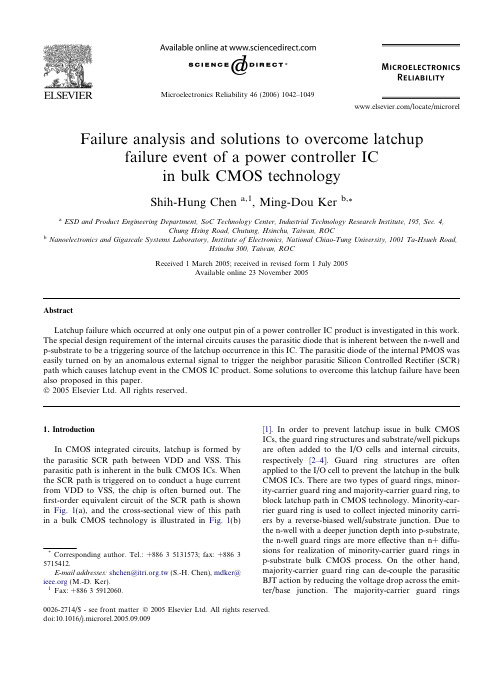

Latchup 失效分析(by Ming-Dou Ker 2006)

Failure analysis and solutions to overcome latchupfailure event of a power controller ICin bulk CMOS technologyShih-Hung Chena,1,Ming-Dou Kerb,*aESD and Product Engineering Department,SoC Technology Center,Industrial Technology Research Institute,195,Sec.4,Chung Hsing Road,Chutung,Hsinchu,Taiwan,ROCbNanoelectronics and Gigascale Systems Laboratory,Institute of Electronics,National Chiao-Tung University,1001Ta-Hsueh Road,Hsinchu 300,Taiwan,ROCReceived 1March 2005;received in revised form 1July 2005Available online 23November 2005AbstractLatchup failure which occurred at only one output pin of a power controller IC product is investigated in this work.The special design requirement of the internal circuits causes the parasitic diode that is inherent between the n-well and p-substrate to be a triggering source of the latchup occurrence in this IC.The parasitic diode of the internal PMOS was easily turned on by an anomalous external signal to trigger the neighbor parasitic Silicon Controlled Rectifier (SCR)path which causes latchup event in the CMOS IC product.Some solutions to overcome this latchup failure have been also proposed in this paper.Ó2005Elsevier Ltd.All rights reserved.1.IntroductionIn CMOS integrated circuits,latchup is formed by the parasitic SCR path between VDD and VSS.This parasitic path is inherent in the bulk CMOS ICs.When the SCR path is triggered on to conduct a huge current from VDD to VSS,the chip is often burned out.The first-order equivalent circuit of the SCR path is shown in Fig.1(a),and the cross-sectional view of this path in a bulk CMOS technology is illustrated in Fig.1(b)[1].In order to prevent latchup issue in bulk CMOS ICs,the guard ring structures and substrate/well pickups are often added to the I/O cells and internal circuits,respectively [2–4].Guard ring structures are often applied to the I/O cell to prevent the latchup in the bulk CMOS ICs.There are two types of guard rings,minor-ity-carrier guard ring and majority-carrier guard ring,to block latchup path in CMOS technology.Minority-car-rier guard ring is used to collect injected minority carri-ers by a reverse-biased well/substrate junction.Due to the n-well with a deeper junction depth into p-substrate,the n-well guard rings are more effective than n+diffu-sions for realization of minority-carrier guard rings in p-substrate bulk CMOS process.On the other hand,majority-carrier guard ring can de-couple the parasitic BJT action by reducing the voltage drop across the emit-ter/base junction.The majority-carrier guard rings0026-2714/$-see front matter Ó2005Elsevier Ltd.All rights reserved.doi:10.1016/j.microrel.2005.09.009*Corresponding author.Tel.:+88635131573;fax:+88635715412.E-mail addresses:shchen@.tw (S.-H.Chen),mdker@ (M.-D.Ker).1Fax:+88635912060.locally reduce the well/substrate resistance by forming the ohmic contact to reduce the voltage drop for a given trigger current.The guard ring structures are rarely applied to internal circuits due to the silicon area con-cerns.But,the substrate/well pickups are used in the internal circuits to reduce latchup susceptibility instead. The substrate/well pickups in internal circuits can decrease the voltage across the emitter/base junctions of the parasitic BJTs to efficiently improve latchup immunity.However,the wider double guard rings in I/ O cells and more pickups in the internal circuits often occupy more layout area in the bulk CMOS ICs[5,6].Although the guard rings and substrate/well pickups could efficiently overcome the latchup failure in CMOS ICs,the latchup failure phenomenon are still existed in many special application circuits.The‘‘signal latchup’’occurrence in voltage tolerant I/O circuits had been reported[7],where the parasitic SCR path existed between I/O pad and VSS.In addition,the power-on latchup phenomenon on DRAM modules was also investigated when the power supply is initially turned on[8].The‘‘anomalous latchup’’failure in ESD protec-tion circuits had also been studied[9,10],where the lat-chup failure was induced by the large N-well resistor associated with the RC-triggered active clamp circuit for on-chip ESD protection between VDD and VSS.In this paper,the latchup failure phenomenon of a power controller IC is presented.Only one output pin showed latchup failure under negative current-mode lat-chup test.In order tofind out the latchup failure spots, some failure analysis(FA)procedures,including de-cap of the IC package,EMission MIcroscope(EMMI),and Focused Ion Beam(FIB)were applied to this power controller IC.The reasons of latchup failure are ana-lyzed and discussed by comparing with the results of failure analyses,layout patterns,and equivalent circuits.tchup test2.1.Trigger current on the I/O pinTo verify the latchup immunity of a CMOS IC,the overshooting(positive)and undershooting(negative) currents are applied to each I/O pin of a CMOS IC to investigate whether the latchup occurs or not.The detailed latchup test procedure and specifications have been clearly specified in the EIA/JEDEC Standard No. 78[11].The schematic diagram to show a latchup trigger current applied to an output pin is illustrated in Fig.2(a).The overshooting/undershooting trigger cur-rent on the pad is applied into the drain regions of out-put devices,as shown in Fig.2(a).While the overshooting(undershooting)current is applied to I/O pin,the P+drain/n-well(N+drain/p-substrate)junc-tion of output PMOS(NMOS)is forward biased to fur-ther generate the trigger current into the substrate.The injecting substrate current can trigger parasitic SCR paths in the I/O cell or in the internal circuits.If the device under test(DUT)is triggered into latchup state by the trigger current applied on an I/O pin,the current flowing from VDD to VSS has an obvious increase.To avoid latchup induced by the trigger current on the I/O pins,the double guard rings are often used to block the latchup path between PMOS and NMOS in I/O cells.To avoid the latchup occurrence in the internal circuits induced by the trigger current on the I/O pins,the addi-tional guard rings have been suggested to be added between the I/O cells and the internal circuits[5,6]. 2.2.Over-voltage on the power pinThe latchup in CMOS ICs is also sensitive to voltage transition on VDD supply[8,12].In order to verify lat-chup immunity of CMOS ICs under a power-transient trigger,the test circuits is configured in Fig.2(b).The trigger voltage is applied on the VDD pin,and the VDD-to-VSS current is monitored to judge if lat-chup occur.The power-transition trigger voltage oftenS.-H.Chen,M.-D.Ker/Microelectronics Reliability46(2006)1042–10491043generates transient current through the parasitic junc-tion capacitance into the n-well or p-substrate to initiate latchup path in CMOS ICs.In general,the consumer CMOS ICs should not be triggered into latchup by a trigger current of±100mA on the I/O pins or a trigger voltage of1.5·VDD on the VDD pin[11].tchup failure in a power controller ICtchup phenomenon and failure analysisTable1gives the latchup testing results for input/out-put pins and power pins under current trigger test and over-voltage trigger test,respectively.This power con-troller IC shows a lower latchup immunity level under negative current trigger test.In Fig.3,the I–V character-istic of the inherent parasitic SCR in this chip shows a higher immunity level against the over-voltage trigger test.The trigger-on voltage(V t1)is about10V which is higher than the over-voltage test requirement of 1.5·VDD(7.5V).However,this chip still has the latchup risk because the inherent parasitic SCR shows a holding voltage(V h,$1.5V)lower than normal oper-Table1The latchup immunity levels of this IC productI-Test applied to I/O pins:>200mA/À50mAV supply Over-voltage test applied to power pin:>7.5VThe latchup immunity level is onlyÀ50mA under negative current trigger test.1044S.-H.Chen,M.-D.Ker/Microelectronics Reliability46(2006)1042–1049ation supply voltage of 5V.The parasitic SCR path could be induced into latchup state by the external trig-ger source during current-mode latchup test.According to the test results in Table 1,an output pin (Pin A)presents a lowest latchup immunity level throughout the entire test pins.The chip failed under the negative current trigger test when Pin A was trig-gered by a negative current pulse of 100mA.The mea-sured voltage waveforms between VDD and VSS are shown in Fig.4,when the Pin A was triggered by differ-ent negative trigger current pulses.The power pin VDD was applied with a normal operation voltage of 5V with respect to VSS.In addition,the negative trigger current was applied on Pin A as a trigger source of latchup event.The voltage waveforms between VDD and VSS were measured and used to judge if latchup occur or not during the current mode latchup test.When a nega-tive trigger current of 60mA was applied on Pin A,the VDD voltage is dropped down to 4V but it returns to 5V again after the current trigger.But,it was held on 2.3V and the chip entered latchup state after a negative trigger current of 80mA is applied to the Pin A.Never-theless,the other input and output pins in the same chip can sustain the positive and negative current trigger test up to a level over 200mA.However,all the input and output cells have the same ESD protection structure,including a gate-grounded NMOS (GGNMOS)and a gate-VDD PMOS (GDPMOS)as shown in Fig.5(a).The corresponding layout view of such ESD protection structure for I/O cell is shown in Fig.5(b).The GGN-MOS and GDPMOS devices were enclosed with double guard rings to prevent latchup in the I/O cells.To investigate the latchup phenomena between Pin A and the other output pins,different parameters (such as the rise time and the pulse width)of the negative trigger current sources were applied to the Pin A,Pin B,and Pin C which have the same I/O cell in the chip.The latchupimmunity levels in Pin A,Pin B,and Pin C under differ-ent test conditions are listed in Table 2.In Pin A,the lat-chup immunity level was found to be related the rise time and pulse width of the triggering current.The lat-chup immunity level is degraded by decreasing the rise time or increasing the pulse width of the triggering cur-rent source.On the contrary,the phenomena were not observed in the Pin B and the Pin C.The results of the latchup immunity levels among these pins with the same I/O cell have identified that the latchup occurrence was not related to the I/O cell with ESD protection devices (GGNMOS and GDPMOS).In order to find out the root cause of latchup,EMis-sion MIcroscope (EMMI)is used to locate the hotspotsFig.4.The measured voltage waveforms on VDD node under different trigger currents applied on the PinA.Fig.5.(a)The schematic circuit diagram,and (b)the layout top view,of the I/O cell with ESD protection devices.The double guard rings are used to block the latchup path in the I/O cell.S.-H.Chen,M.-D.Ker /Microelectronics Reliability 46(2006)1042–10491045and the latchup occurrence path.The measurement setup is illustrated in Fig.6(a).The latchup condition is pre-sented by a negative triggered current pulse of À100mA applied to Pin A,and the chip is powered with 5-V VDD.The parasitic SCR path at internal core cir-cuits was obviously observed by the Emission Micro-scopic photograph as shown in Fig.6(b).The metal line that connects to internal circuits of Pin A was cut offby Focused Ion Beam(FIB)to prove the latchup occurrence at the internal circuits.After FIB treatment,the results of current trigger latchup test on Pin A can pass the level of overÀ200mA.This has verified that the latchup occur-rence is located at the internal circuits,not the I/O cell.tchup failure mechanismAs comparing with the layout patterns and the hot-spot image of the EMMI photograph,Pin A was found to be directly connected to a PMOS transistor close to the internal latchup location.The equivalent circuit and the device cross-sectional view of the PMOS device in the internal circuits are shown in Fig.7(a)and(b), respectively.According to the schematics and layout patterns,the root cause of this anomalous latchup is identified to the n-well pickups of the PMOS.The n-well of this PMOS is directly connected to the output pad (Pin A),therefore the potential of n-well was related to the signal presenting on the pad.During the current-mode latchup test,a negative triggering current pulse drops down the potential of n-well.Consequently,the parasitic diode between the p-substrate and n-well turns on by a forward bias.The parasitic diode injects the sub-strate current to trigger the neighbor parasitic SCR path in the internal circuits,as illustrated in Fig.8.The loca-tions of the latchup path and the triggering source in the layout patterns are shown in Fig.9(a).The zoomed-in layout to show the relationship between the PMOS and latchup location is illustrated in Fig.9(b).The par-asitic diode between the n-well and p-substrate will be turned on by the negative I/V injection source on the pad(Pin A).Then,this forward biased diode will inject a huge substrate current to trigger on the parasitic SCR path in its neighborhood.Even if there are some guard rings to surround the PMOS(triggering source),the injecting substrate current is still large enough to induce latchup occurrence in the neighbor circuits to cause this latchup failure event.3.3.Solutions and discussions to overcome latchup failureAccording to the measurement results in Figs.3and 4,the latchup failure would not occur in the lack of enough substrate trigger current.Therefore,the latchup failure can be solved by eliminating or reducing the substrate trigger current which initiates the latchup occurrence during current trigger latchup test.Several solutions were proposed to improve the latchup immu-Table2The latchup immunity levels at Pin A,Pin B,and Pin C of a power controller IC under different pulse widths and rise times of the triggered sourcesPulse width Rise time5l s50l s500l s5msPin A10l s>±200mA>±200mA>±200mA>±200mA 1msÀ50mAÀ50mAÀ50mA>±200mA 1sÀ50mAÀ50mAÀ50mAÀ50mA Pin B10l s>±200mA>±200mA>±200mA>±200mA 1ms>±200mA>±200mA>±200mA>±200mA 1s>±200mA>±200mA>±200mA>±200mA Pin C10l s>±200mA>±200mA>±200mA>±200mA 1ms>±200mA>±200mA>±200mA>±200mA 1s>±200mA>±200mA>±200mA>±200mAFig.6.(a)The measurement setup of latchup test.(b)Thelatchup path in the internal circuits was identified by the EMMIphotograph.1046S.-H.Chen,M.-D.Ker/Microelectronics Reliability46(2006)1042–1049nity level in this chip.Firstly,the parasitic diode can be held on reverse status to thoroughly eliminate the sub-strate current injection during the negative current trig-ger latchup test.The potential of n-well (N+guard ring)of the PMOS should be connected to VDD or held on a high potential level,where only a few mask layers need to be modified for achieving high latchup immunity level in this IC product.When the n-well pickup is connectedto a high potential level to keep the parasitic diode in reverse biased,there is no substrate current injecting to trigger the latchup path in this CMOS IC product.How-ever,the original design for the n-well pickup of the PMOS tied to pad is used to reduce the threshold volt-age (V th )of the PMOS in this application.If the n-wellFig.9.(a)The relationship between the PMOS and latchup path in the layout pattern.(b)The zoomed-in layout pattern to show the latchup location at the neighbor circuits.S.-H.Chen,M.-D.Ker /Microelectronics Reliability 46(2006)1042–10491047pickup was tied to VDD,the threshold voltage of the PMOS will be increased due to the body effect.Then, the performance of this IC could be slightly degraded by the n-well pickup being tied to VDD.Secondly,the distributions of the trigger currents between the parasitic N+/p-well junction diode of the GGNMOS in I/O ESD cell and the n-well/p-substrate junction diode of the PMOS in the internal circuits under the negative trigger current stress are shown in Fig.10(a).These two forward-biased diodes conduct the latchup trigger current,I1and I2,during the negative current trigger latchup test.The I1current is supported by the guard ring of GGNMOS in the I/O ESD cell, and the I/O ESD cell is far away from the internal cir-cuits.So,the I1current did not cause latchup event in this Pin A.But,the transient current I2induces a large enough substrate current to initiate the latchup failure in the neighboring SCR path.If a resistor R with a resis-tance of several ohms is added between the pad and the output PMOS of Pin A,the transient current I2under the negative current trigger latchup test can be signifi-cantly reduced.While the turned-on resistance of the N+/p-well diode is about4X,the transient current I2 could be decreased about33–60%to reduce the sub-strate current injecting to the internal circuits by adding a resistor of4–12X,as shown in Fig.10(b).The latchup immunity level of this IC can be significantly improved by reducing the trigger current injecting into internal cir-cuits.However,the inserted resistor would induce the voltage drop to degrade the circuit performance.There-fore,the inserted resistance should be suitably chosen to achieve the optimal value for effectively improving the latchup immunity level without seriously degrading cir-cuit performance.1048S.-H.Chen,M.-D.Ker/Microelectronics Reliability46(2006)1042–1049Thirdly,a wider guard ring to surround the special PMOS is recommended to increase the latchup immu-nity of this IC product.The wider grounded P+guard ring can efficiently capture the major carriers(holes)to reduce the trigger substrate current injecting towards the internal circuits.In addition,the minority carrier (electrons)would also be caught by the N+/n-well guard ring to further eliminate the substrate current to prevent the latchup occurrence.The latchup would not occur under the lack of trigger current,therefore the wider double rings which surround thefloating n-well of PMOS can efficiently eliminate the trigger current to improve latchup immunity of the IC products.4.ConclusionFrom the detailed analyses,the latchup failure was attributed to the potential of n-well pickup in the PMOS of the internal circuits in CMOS IC.Due to the special design concern in the PMOS,the parasitic diode between the n-well and p-substrate was turned on to induce a substrate current to trigger the neighbor SCR path,when a negative latchup voltage/current trigger source is applied to the pad.To solve this latchup occur-rence,the potential of n-well in the PMOS should be connected to a higher potential.However,the perfor-mance will be slightly degraded when the n-well pickup is tied to VDD.On the other hand,the trigger current can be significantly restrained by adding a resistor between the I/O cell and the output PMOS in internal circuits.To re-draw the chip layout with a wider spacing from the PMOS and its neighborhood,as well as a wider P+guard ring to surround the PMOS,is sug-gested to overcome such latchup failure in this IC product.AcknowledgementsThis work was supported by ESD and Product Engi-neering Department,SoC Technology Center,Industrial Technology Research Institute,Hsinchu,Taiwan.The authors gratefully acknowledge Ms.C.-P.Weng,Mr.C.-C.Chiang,Mr.C.-H.Chuang,and Dr.K.-H.Lin for kind support and encouragement.The authors also thank to Editor,Prof.J.-J.Liou,for his encouragement to revise this manuscript for publication.References[1]Hargrove MJ,Voldman S,Gauthier R,Brown J,DuncanK,Craig tchup in CMOS technology.In:Proceed-ings of IEEE international reliability physics symposium, 1998.p.269–78.[2]Chen JY.CMOS devices and technology for VLSI.Pren-tice-Hall International;1990.[3]Troutman tchup in CMOS technology.KluwerAcademic Publishers;1986.[4]Aoki T.A practical high-latchup immunity design meth-odology for internal circuits in the standard cell-based CMOS/BiCMOS LSIs.IEEE Trans Electron Dev1993;40: 1432–6.[5]Ker M-D,Lo W-Y,Chen pact layout ruleextraction for latchup prevention in a0.25-l m shallow-trench-isolation silicided bulk CMOS process.In:Proceed-ings of international quality electronic design,2001.p.267–72.[6]Ker M-D,Lo W-Y.Methodology on extracting compactlayout rules for latchup prevention in deep-submicron bulk CMOS technology.IEEE Trans Semicond Manufact2003;16:319–34.[7]Suner JS,Cline R,Duvvury C,Hernandez AC,Ting L,Schichl J.A new I/O signal latchup phenomenon in voltage tolerant ESD protection circuits.In:Proceed-ings of international reliability physics symposium,2003.p.85–91.[8]Kim Y-H et al.Analysis and prevention of DRAMlatchup during power-on.IEEE Solid-State Circ1997;32: 79–85.[9]Lin I-C,Huang C-Y,Ker M-D,Chuan S-Y,Leu L-Y,Chiu F-C,et al.Anomalous latchup failure induced by on-chip ESD protection circuit in a high-voltage CMOS IC product.Microelectron Reliab2003;43:1295–301.[10]Tong C-F,Chen W-S,Jiang H-C,Hui J,Xu P-P,Liu Z-Q.Active ESD shunt with transistor feedback to reduce latchup susceptibility or false triggering.In:Proceedings of international physics and failure analysis symposium, 2004.p.89–92.[11]IC latch-up test,EIA/JEDEC,EIA/JESD78,1997.[12]Weiss GH,Young DE.Transient-induced latchup testingof CMOS integrated circuits.In:Proceedings of EOS/ESD Symposium,1995.p.194–8.S.-H.Chen,M.-D.Ker/Microelectronics Reliability46(2006)1042–10491049。

latch up测试标准

latch up测试标准Latchup测试是电路设计中非常重要的一部分,用于确保电路在各种情况下都能正常工作。

本测试标准旨在为电路设计人员提供一套清晰、准确、可操作的测试方法,以确保Latchup现象不会对电路性能产生不良影响。

一、测试目的1.确保Latchup不会在电路中发生;2.验证Latchup防护措施的有效性;3.确保电路在不同工作条件下都能正常工作。

二、测试范围1.电源电路;2.信号传输线路;3.数字和模拟电路;4.芯片接口电路;5.其他可能发生Latchup的区域。

三、测试方法1.静态测试:a.使用示波器、电压表和电流表测量电路各部分的工作电压、电流及信号波形;b.检查电路中的电感和电容元件,确保其性能正常;c.对比设计图纸和实际电路,确保元件布局、布线符合设计要求。

2.动态测试:a.模拟不同的工作环境,如电压波动、温度变化等;b.引入干扰信号,模拟Latchup条件;c.使用测试仪器观察电路各部分的工作状态,如电压、电流、信号质量等;d.观察Latchup发生时的现象,如电压下降、电流增大、信号畸变等。

3.防护措施测试:a.对电路中的Latchup防护措施(如箝位二极管、磁珠等)进行测试;b.验证这些防护措施在Latchup发生时的反应时间、抑制效果等性能指标;c.检查防护措施对电路其他部分的影响。

四、测试标准tchup现象未在电路中发生;2.电路在各种工作条件下都能正常工作,无异常现象;3.保护措施在Latchup发生时能迅速起作用,抑制效果良好;4.干扰信号对其他电路部分的影响在可接受范围内。

五、测试周期与记录1.每次设计变更后都应进行Latchup测试;2.测试结果应记录在案,便于日后查阅;3.对于多次出现问题的区域,应进行深入分析,找出根本原因。

通过遵循本测试标准,电路设计人员可以更准确地评估电路的安全性和可靠性,为产品的质量和性能提供有力保障。

闩锁效应原理及避免的方法

Latch up 的定义?? Latch up 最易产生在易受外部干扰的I/O电路处, 也偶尔发生在内部电路?? Latch up 是指cmos晶片中, 在电源power VDD和地线GND(VSS)之间由于寄生的PNP和NPN双极性BJT相互影响而产生的一低阻抗通路, 它的存在会使VDD和GND之间产生大电流?? 随着IC制造工艺的发展, 封装密度和集成度越来越高,产生Latch up的可能性会越来越大?? Latch up 产生的过度电流量可能会使芯片产生永久性的破坏, Latch up 的防范是IC Layout 的最重要措施之一Latch up 的原理分析?Q1为一垂直式PNP BJT, 基极(base)是nwell, 基极到集电极(collector)的增益可达数百倍;Q2是一侧面式的NPN BJT,基极为P substrate,到集电极的增益可达数十倍;Rwell是nwell的寄生电阻;Rsub是substrate电阻。

以上四元件构成可控硅(SCR)电路,当无外界干扰未引起触发时,两个BJT处于截止状态,集电极电流是C-B的反向漏电流构成,电流增益非常小,此时Latch up不会产生。

当其中一个BJT的集电极电流受外部干扰突然增加到一定值时,会反馈至另一个BJT,从而使两个BJT因触发而导通,VDD至GND(VSS)间形成低抗通路,Latch up由此而产生。

产生Latch up 的具体原因? 芯片一开始工作时VDD变化导致nwell和P substrate间寄生电容中产生足够的电流,当VDD变化率大到一定地步,将会引起Latch up。

? 当I/O的信号变化超出VDD-GND(VSS)的范围时,有大电流在芯片中产生,也会导致SCR的触发。

? ESD静电加压,可能会从保护电路中引入少量带电载子到well或substrate中,也会引起SCR的触发。

? 当很多的驱动器同时动作,负载过大使power和gnd突然变化,也有可能打开SCR的一个BJT。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

闩锁效应(latch up)闩锁效应(latch up)是CMOS必须注意的现象,latch我认为解释为回路更合适,大家以后看到latch up就联想到在NMOS与PMOS里面的回路,其实你就懂了一半了.为什么它这么重要?因为它会导致整个芯片的失效,所以latch up是QUAL 测试的一种,并且与ESD(静电防护)紧密相关。

第一部分 latch up的原理我用一句最简单的话来概括,大家只要记住这句话就行了:latch-up是PNPN的连接,本质是两个寄生双载子transisitor的连接,每一个transistor的基极(base)与集极(collector)相连,也可以反过来说,每一个transistor的集极(collector)与另一个transistor的基极(base)相连,形成positive feedback loop(正回馈回路),下面我分别解释。

我们先复习什么是npn,如图1,在n端加正偏压,np之间的势垒就会降低,n端电子为主要载流子,于是电子就很开心地跑到p,其中有一部分电子跑得太开心了,中间的p又不够厚,于是就到pn的交界处,这时右边的n端是逆偏压,于是就很容易就过去了。

所以,左边的n为射极(emmiter,发射电子),中间P为基极(base),右边n为集极(collector,收集电子嘛)理解了npn,那么pnp就好办,如图2。

图2清楚的表示了latch up的回路。

左边是npn,右边是pnp图3是电路示意图。

大家可以看出,P-sub既是npn的基极,又是pnp的集极;n-well既是既是pnp的基极,又是npn的集极,所以说,每一个transistor的集极(collector)与另一个transistor的基极(base)相连。

那么电流怎么走呢?比如在P+加5V-->电洞被从P+推到N well-->越过n well再到p sub-->这个时候,大家注意,电洞有两条路可走,一是跑到NMOS的N+,二是跑到旁边的Nwell,nwell比n+深,当然更好去,所以电洞又回去了。

这样就形成回路,而且会循环下去,gate基本上就成了摆设,完全控制不了电子或电洞的走向,所以CMOS就失效了。

图4是一个公式,我也不知道是什么意思,反正2个β变小,latch up就不容易发生。

图5是首位发现latch up的达人做出的解释:latch up是由于field inversion(反转电场),值得记住,但我不懂。

第二部分如何解决latch up?大家只要记住一句话,电子和电洞,都是单纯的家伙,哪里容易去,他们就去哪里,就像他们本来想去看朋友,走到半路看到一个美女在对他们打招呼,于是就很自然的跑到美女那边去了,不去本来该去的地方。

所以,下面所有的解决方法,要么是阻止电子或电洞去看美女,或者找个更漂亮的美女吸引他们过去。

解决方法目前为止,我总结出7个,如下:1.加大N+,P+距离,这是最容易想到的办法,虽然前面有美女,但是太远,所以还是不去了。

电子或电洞也是这样。

但是,这样的,必然会导致芯片的集成度下降,所以这是很傻的办法,没人用。

2.加深isolation.就是在NMOS和PMOS之间加隔离,比如STI(0.25um以下)和Field OX(0.35um以上)。

但是,隔离深度总是有限的,电子或电洞总有办法绕过去。

3.SOI。

Silicon on Insulator,在Si的表面加一层SiO2,使well或者N+无法直接与P-sub连接,这样电子或电洞就到不了下面。

4.Retrograded well,倒阱,用高能离子注入将杂质打入阱底部,这种阱不像常规的阱表面浓度最高,阱底部浓度最低,而是正相反,所以叫做倒阱。

这个概念极为重要!下面的浓度很大,那么电子或电洞到了基极以后,高浓深井可以有效的增加复合,就不想到集极去了,降低bipolar的放大系数,使没有backbias偏置的晶体管免于latch-up。

5.EPI wafer。

这也是一个重要的概念,在heavy doped substrate上面,加上一层轻微掺杂的EPI layer,这就是EPI wafer (即外延片,晶圆是wafer,在wafer基础上做EPI工艺出来的wafer就是EPI wafer)。

当这层EPI layer够薄的时候,pnp的载流子就不想去npn了,而是跑到更舒服的heavy doped substrate,因为heavy doped底材的浓度比P-sub的掺杂浓度高多了。

如图6很明显,EPI layer越薄越好,如图7,3um的EPI layer,trigger current(引发latch up的电流)最大,最不容易发生latch up但是不能太薄,不然底材的离子就扩散到EPI layer里面,造成离子浓度改变。

这是用EPI wafer的原因,EPI wafer缺点只有一个:贵!外延(Epitaxy, 简称Epi)工艺是指在单晶衬底上生长一层跟衬底具有相同晶格排列的单晶材料,外延层可以是同质外延层(Si/Si),也可以是异质外延层(SiGe/Si 或SiC/Si等);6.Guard ring。

在N+和P+的旁边加一个guard band,相当于保险,如图8。

大家看图9,应该会明白为什么Guard ring能防止latch up,与EPI是类似的道理。

7.Design rule。

这个很简单,在design的时候,会规定P+,N+的距离,guard ring离P+,N+的距离等等。

最后一个问题是,这么多解决方法,到底用哪一个?答案还是很简单,只要你有钱,能一起用就一起用。

latch up(闩锁反应)我们无可逃避,只能坚强应对。

首先来看一下latch up时拍到的照片放大后的照片红点部分就是发生latch up的位置,latch up可谓芯片杀手,通过循环放大最终将芯片烧毁。

我不想告诉大家latch up有多可怕,但有一点是应该知道的这种现象损害了芯片。

图片附件: latch01.jpg (2007-1-30 16:38, 11.73 K)图片附件: latch02.jpg (2007-1-30 16:38, 10.62 K)在CMOS制程里,这种情况就是由于npn或pnp结构形成的放大电路造成的。

所以要了解latch up现象,就必然首先了解放大电路是如何构成的,而最根本的就归结到npn或pnp晶体管是如何工作的。

了解晶体管的工作原理是研究latch up的重点。

而解决这一问题的关键又在于了解放大电路是如何构成的,这是两个方面,以下着重讨论。

一、晶体管的工作原理半导体工艺中,由高纯度的本征半导体进行掺杂,从而形成不同的形态。

如果掺杂5价原子因电子数大于空穴数即称为n型半导体,若掺杂3价原子因电子数小于空穴数即称为p型半导体。

空穴和电子都能搬运电荷,因而称载流子。

将两种形态的半导体相邻结合到一起,由于彼此所含电子和空穴数浓度不同,因而相互扩散,由浓度高的向浓度低的地方移动,电子和空穴会在一定时间内相互结合而消失,以保持中性,这样形成一段没有载流子的空间,称为耗尽层。

耗尽层存在电位差,有电场的存在,称之为内电场。

在电场的作用下载流子发生定向移动,称之为漂移。

扩散使电场增加,空间电荷范围加大,而漂移则在减弱空间电荷范围。

这种将pn 相邻结合到一起制成的晶体结构,称之为pn结。

pn结在没有外力的情况下,处于热平衡状态,这种平衡状态是处于动态之中的,即扩散运动与漂移运行达成的平衡状态。

pn结的外加电压,如果p端的电位高于n端的电位,这样的外电电场削弱了内电场,有利于多数载流子的扩散,形成从p流向n的电流,称为正向偏置,反之,载流子则几乎不发生移动,称为反向偏置。

反向电压大于某一值时,会有导致pn结击穿,称为齐纳击穿或隧道击穿。

另一种情况,是pn结两侧的杂质浓度过小,在高的反向电压作用下,引起价键的断裂,从而使电流成倍增加,称为电子雪崩现象或雪崩击穿。

pn结制作成元器件使用就是二极管。

pn结,p区空穴向n区扩散,n区电子向p区扩散,在相遇处复合。

p区空穴扩散后留下负离子,而n 区电子扩散后留下正离子,形成由n指向p的内电场。

正向偏置时,p区不断提供复合留下的负离子,n 区则复合留下的正离子,使得内电场范围缩小,扩散运动大于漂移运动,平衡状态发生破坏,因而有电流的产生。

反向偏置,少数载流子的漂移处于优势,但因少数载流子浓度太低,引起的反向电流远小于正向电流。

所以问题关键在于扩散与漂移运动是否平衡。

图片附件: psbias.gif (2007-1-30 16:38, 2.26 K)半导体三极管,存在两个pn结,了解半导体三极管的工作原理就是要了解这两个pn结的平衡状态,在发生什么变化。

这是三极管的符号,B(base)代表基电极,C(collector)代表集电极,E(emitter)代表发射极。

晶体管的制作要求,从浓度大小来看,发射区最大,集电区最小。

从尺寸看,集电区最大,基区最小。

如果条件不能满足,晶体管将无法工作。

以下以基极接地(共基极)为例进行分析:图片附件: pnpsymbl.gif (2007-1-30 16:38, 1.87 K)如上图所示,在E-B之间加正向偏置,在B-C之间加反向偏置。

此时发射区的电子浓度上升,在正向偏置的情况下,大部分电子都扩散到基区因为基区很薄,有少部分电子流出,但大部分在电场的作用下,漂移到集电区。

其中有些情况,比如基区向发射区的漂移(发射区很高的杂质浓度),集电区向基区的扩散等微乎其微(反向偏置),所以可以忽略。

所示npn的能够工作,除了发射区浓度很高,基区很薄,还有保证E-B正向偏置,B-C反向偏置。

相应电流关系如下:Ie=Ib+Ic 假设Ie占Ic的比例为a,即Ic=aIe,Ib=(1-a)Ie称为电流传输率。

Ic/Ib=(Iea)/[(1-a)Ie]=a/(1-a)设定a/(1-a)为ß,称为电流放大倍数。

通过比例关系可知,如果电流传输率为90%,电流放大9倍如果电流传输率为99%,电流将放大99倍。

90%到99%,放大倍数的骤增,可以想像Ib只要有小的变动,电流放大倍数就有大的变化。

如此可见,晶体管是电流控制器件。

二、放大电路是如何构成及触发条件现在进行实际操作,为了分析方便,以如图所示的电路具体进行分析。

对应CMOS的简单版图如下:图片附件: latchupfg02.gif (2007-1-30 16:38, 12.4 K)图画得不好,还请谅解。

以下来看一下对应的剖面图。

图片附件: latchupfg03.gif (2007-1-30 16:38, 10.2 K)任何相邻的pnp或npn都可以构成晶体管,所以考虑起来似乎比例麻烦!!从晶体管偏置来看,npn的基区p+与p-sub成反向偏置,发射区为衬底上的任一n+型区域,集电区为nwell及nwell上的n+。