TP30-180中文资料

744230181;中文规格书,Datasheet资料

2.1 2.0 1.02012-07-172012-07-172010-09-30SStSStSBaSStSBaWürth Elektronik eiSos GmbH & Co. KGEMC & Inductive SolutionsMax-Eyth-Str. 174638 WaldenburgGermanyTel. +49 (0) 79 42 945 - 0A Dimensions: [mm]F Typical Impedance Characteristics:H1: Classification Reflow Profile for SMT components:H2: Classification Reflow ProfilesProfile FeaturePreheat- Temperature Min (T smin ) - Temperature Max (T smax ) - Time (t s ) from (T smin to T smax )Ramp-up rate (T L to T P )Liquidous temperature (T L )Time (t L ) maintained above T L Peak package body temperature (T p )Time within 5°C of actual peak temperature (t p )Ramp-down rate (T P to T L )Time 25°C to peak temperature Pb-Free Assembly 150°C 200°C60-180 seconds 3°C/ second max.217°C60-150 seconds See Table H320-30 seconds 6°C/ second max.8 minutes max.refer to IPC/JEDEC J-STD-020DH3: Package Classification Reflow TemperaturePB-Free Assembly PB-Free Assembly PB-Free Assembly Package Thickness< 1.6 mm 1.6 - 2.5 mm ≥ 2.5 mmVolume mm³<350260°C 260°C 250°CVolume mm³350 - 2000260°C 250°C 245°CVolume mm³>2000260°C 245°C 245°Crefer to IPC/JEDEC J-STD-020DH Soldering Specifications:I Cautions and Warnings:The following conditions apply to all goods within the product series of WE-CNSWof Würth Elektronik eiSos GmbH & Co. KG:General:All recommendations according to the general technical specifications of the data sheet have to be complied with.The disposal and operation of the product within ambient conditions which probably alloy or harm the wire isolation has to be avoided.If the product is potted in customer applications, the potting material might shrink during and after hardening. Accordingly to this the product is exposed to the pressure of the potting material with the effect that the core, wire and termination is possibly damaged by this pressure and so the electrical as well as the mechanical characteristics are endanger to be affected. After the potting material is cured, the core, wire and termination of the product have to be checked if any reduced electrical or mechanical functions or destructions have occurred.The responsibility for the applicability of customer specific products and use in a particular customer design is always within the authority of the customer. All technical specifications for standard products do also apply for customer specific products.Cleaning solvents which are used to clean the application might damage or change the characteristics of the component.Direct mechanical impact to the product shall be prevented as the ferrite material of the core could flake or in the worst case it could break. Product specific:Follow all instructions mentioned in the datasheet, especially:•The soldering profile has to be complied with according to the technical reflow soldering specification, otherwise no warranty will be su-stained.•All products are supposed to be used before the end of the period of 12 months based on the transfer of title, if not a 100% solderability can´t be warranted.•Violation of the technical product specifications such as exceeding the nominal rated current will result in the loss of warranty.1. General Customer ResponsibilitySome goods within the product range of Würth Elektronik eiSos GmbH & Co. KG contain statements regarding general suitability for certain application areas. These statements about suitability are based on our knowledge and experience of typical requirements concerning the are-as, serve as general guidance and cannot be estimated as binding statements about the suitability for a customer application. The responsibi-lity for the applicability and use in a particular customer design is always solely within the authority of the customer. Due to this fact it is up to the customer to evaluate, where appropriate to investigate and decide whether the device with the specific product characteristics described in the product specification is valid and suitable for the respective customer application or not.2. Customer Responsibility related to Specific, in particular Safety-Relevant ApplicationsIt has to be clearly pointed out that the possibility of a malfunction of electronic components or failure before the end of the usual lifetime can-not be completely eliminated in the current state of the art, even if the products are operated within the range of the specifications.In certain customer applications requiring a very high level of safety and especially in customer applications in which the malfunction or failure of an electronic component could endanger human life or health it must be ensured by most advanced technological aid of suitable design of the customer application that no injury or damage is caused to third parties in the event of malfunction or failure of an electronic component.3. Best Care and AttentionAny product-specific notes, warnings and cautions must be strictly observed.4. Customer Support for Product SpecificationsSome products within the product range may contain substances which are subject to restrictions in certain jurisdictions in order to serve spe-cific technical requirements. Necessary information is available on request. In this case the field sales engineer or the internal sales person in charge should be contacted who will be happy to support in this matter.5. Product R&DDue to constant product improvement product specifications may change from time to time. As a standard reporting procedure of the Product Change Notification (PCN) according to the JEDEC-Standard inform about minor and major changes. In case of further queries regarding the PCN, the field sales engineer or the internal sales person in charge should be contacted. The basic responsibility of the customer as per Secti-on 1 and 2 remains unaffected.6. Product Life CycleDue to technical progress and economical evaluation we also reserve the right to discontinue production and delivery of products. As a stan-dard reporting procedure of the Product Termination Notification (PTN) according to the JEDEC-Standard we will inform at an early stage about inevitable product discontinuance. According to this we cannot guarantee that all products within our product range will always be available. Therefore it needs to be verified with the field sales engineer or the internal sales person in charge about the current product availability ex-pectancy before or when the product for application design-in disposal is considered.The approach named above does not apply in the case of individual agreements deviating from the foregoing for customer-specific products.7. Property RightsAll the rights for contractual products produced by Würth Elektronik eiSos GmbH & Co. KG on the basis of ideas, development contracts as well as models or templates that are subject to copyright, patent or commercial protection supplied to the customer will remain with Würth Elektronik eiSos GmbH & Co. KG.8. General Terms and ConditionsUnless otherwise agreed in individual contracts, all orders are subject to the current version of the “General Terms and Conditions of Würth Elektronik eiSos Group”, last version available at .J Important Notes:The following conditions apply to all goods within the product range of Würth Elektronik eiSos GmbH & Co. KG:分销商库存信息: WURTH-ELECTRONICS 744230181。

职称评定认可 期刊名录

复印报刊资料(中小学教育)

11-4299/G4

复印报刊资料(高等教育)

11-4309/G4

复印报刊资料(成人教育学刊)

11-4310/G2

复印报刊资料(幼儿教育导读)

11-4311/G4

复印报刊资料(职业技术教育)

11-4312/G4

复印报刊资料(家庭教育导读)

11-4348/G4

文种 汉文 汉文 汉文 汉文 汉文 汉文 汉文 汉文 汉文 汉文 汉文 汉文 汉文 汉文 汉文 汉文 汉文 汉文 汉文 汉文 汉文 汉文 汉文 汉文 汉文 汉文

85 河北教育

13-1036/G4

86 教育实践与研究

13-1259/G4

87 河北大学成人教育学院学报

13-1264/G4

88 河北农业大学学报(农林教育版)

13-1266/G4

89 河北师范大学学报(教育科学版)

13-1286/G

90 中国军事教育

13-1290/G4

91 学苑教育

13-1386/G4

11-1610/G4

学位与研究生教育

11-1736/G4

化学教育

11-1923/O6

中国健康教育

11-2513/R

中国音乐教育

11-2543/J

思想教育研究

11-2549/D

中国教育学刊

11-2606/G4

中-2688/G4

中国林业教育

11-2729/S

序号123456789101112131415161718192021222324252627282930313233343536373839404142434445期刊名称期刊cn号文种出版状态未来教育家101044g4汉文教育与职业111004g4汉文北京教育111129g4汉文艺术教育111188j汉文人民教育111199g4汉文中国高等教育111200g4汉文教育研究111281g4汉文中医教育111349r汉文学前教育111371g4汉文心理发展与教育111608b汉文清华大学教育研究111610g4汉文学位与研究生教育111736g4汉文化学教育111923o6汉文中国健康教育112513r汉文中国音乐教育112543j汉文思想教育研究112549d汉文中国教育学刊112606g4汉文中国基础教育研究115187g4汉文民族教育研究112688g4汉文中国林业教育112729s汉文中国民族教育112792g4汉文比较教育研究112878g4汉文公安教育112963d汉文中国职业技术教育113117g4汉文中国校外教育113173g4汉文中国职工教育113311g4汉文继续教育113315g4石油教育113322g4汉文中国冶金教育113775g4汉文中国电力教育113776g4汉文中国地质教育113777g4汉文环境教育113784g4汉文中国电化教育113792g4汉文中国特殊教育113826g4汉文思想理论教育导刊114062g4汉文中国远程教育114089g4汉文世界教育信息114123g4汉文复印报刊资料教育学114297g4汉文复印报刊资料思想政治教育114298g4汉文复印报刊资料中小学教育114299g4汉文复印报刊资料高等教育114309g4汉文复印报刊资料成人教育学刊114310g2汉文复印报刊资料幼儿教育导读114311g4汉文复印报刊资料职业技术教育114312g4汉文复印报刊资料家庭教育导读114348g4汉文职称评定认可教育类期刊名录4647484950515253545556575859606162636465666768697071727374757677787980818283848586878889909192复印报刊资料素质教育114350g4汉文报刊资料索引文化教育体育分册114364g汉文中国口腔医学继续教育杂志114430r汉文现代教育技术114525n汉文教

KK74HC125A资料

TECHNICAL DATAKK 74HC125AQuad 3-State Noninverting BuffersThe KK 74HC125A is identical in pinout to the LS/ALS125. The device inputs are compatible with standard CMOS outputs; with pullup resistors, they are compatible with LS/ALSTTL outputs.The KK 74HC125A noninverting buffers are designed to be used with 3-state memory address drivers, clock drivers, and other bus-oriented systems. The devices have four separate output enables that are active-low.• Outputs Directly Interface to CMOS, NMOS, and TTL• Operating Voltage Range: 2.0 to 6.0 V• Low Input Current: 1.0 µA • High Noise Immunity Characteristic of CMOS Devices LOGIC DIAGRAMPIN 14 =V CC PIN 7 = GNDPIN ASSIGNMENTFUNCTION TABLEInputs OutputA OE Y H L H L L L X H Z X = don’t careZ = high impedanceMAXIMUM RATINGS*Symbol Parameter ValueUnit V CC DC Supply Voltage (Referenced to GND) -0.5 to +7.0 VV IN DC Input Voltage (Referenced to GND) -1.5 to V CC +1.5 VV OUT DC Output Voltage (Referenced to GND) -0.5 to V CC +0.5 VI IN DC Input Current, per Pin ±20 mAI OUT DC Output Current, per Pin ±35 mAI CC DC Supply Current, V CC and GND Pins ±75 mAP D Power Dissipation in Still Air, Plastic DIP+ SOIC Package+ 750500mWTstg Storage Temperature -65 to +150 °CT L Lead Temperature, 1 mm from Case for 10 Seconds(Plastic DIP or SOIC Package)260 °C*Maximum Ratings are those values beyond which damage to the device may occur.Functional operation should be restricted to the Recommended Operating Conditions.+Derating - Plastic DIP: - 10 mW/°C from 65° to 125°CSOIC Package: : - 7 mW/°C from 65° to 125°CRECOMMENDED OPERATING CONDITIONSSymbol Parameter MinMaxUnit V CC DC Supply Voltage (Referenced to GND) 2.0 6.0 VV IN, V OUT DC Input Voltage, Output Voltage (Referenced to GND) 0 V CC VT A Operating Temperature, All Package Types -55 +125 °Ct r, t f Input Rise and Fall Time (Figure 1) V CC =2.0 VV CC =4.5 VV CC =6.0 V 01000500400nsThis device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high-impedance circuit. For proper operation, V IN and V OUT should be constrained to the range GND≤(V IN or V OUT)≤V CC.Unused inputs must always be tied to an appropriate logic voltage level (e.g., either GND or V CC). Unused outputs must be left open.DC ELECTRICAL CHARACTERISTICS (Voltages Referenced to GND)V CC Guaranteed LimitSymbol Parameter TestConditions V25 °Cto-55°C ≤85°C≤125°CUnitV IH Minimum High-Level Input Voltage V OUT= V CC-0.1 V⎢I OUT⎢≤ 20 µA2.04.56.01.53.154.21.53.154.21.53.154.2VV IL Maximum Low -Level Input Voltage V OUT=0.1 V⎢I OUT⎢≤ 20 µA2.04.56.00.51.351.80.51.351.80.51.351.8VV OH Minimum High-Level Output Voltage V IN=V IH⎢I OUT⎢≤ 20 µA2.04.56.01.94.45.91.94.45.91.94.45.9VV IN=V IH⎢I OUT⎢≤ 6.0 mA⎢I OUT⎢≤ 7.8 mA4.56.03.985.483.845.343.75.2V OL Maximum Low-Level Output Voltage V IN=V IL⎢I OUT⎢≤ 20 µA2.04.56.00.10.10.10.10.10.10.10.10.1VV IN=V IL⎢I OUT⎢≤ 6.0 mA⎢I OUT⎢≤ 7.8 mA4.56.00.260.260.330.330.40.4I IN Maximum InputLeakage CurrentV IN=V CC or GND 6.0±0.1±1.0 ±1.0 µAI OZ Maximum Three-State LeakageCurrent Output in High-ImpedanceStateV IN=V IL or V IHV IN=V CC or GND6.0±0.5±5.0 ±10 µAI CC Maximum QuiescentSupply Current(per Package) V IN=V CC or GNDI OUT=0µA6.0 4.0 40 160 µAAC ELECTRICAL CHARACTERISTICS (C L =50pF,Input t r =t f =6.0 ns)V CCGuaranteed LimitSymbol Parameter V 25 °C to -55°C ≤85°C ≤125°CUnitt PLH , t PHLMaximum Propagation Delay, Input A to Output Y (Figures 1 and 3)2.04.56.090 18 15 115 23 20 135 27 23 nst PLZ , t PHZ Maximum Propagation Delay, Output Enable toY (Figures 2 and 4)2.04.56.0120 24 20 150 30 26 180 36 31 nst PZL , t PZH Maximum Propagation Delay, Output Enable toY (Figures 2 and 4)2.04.56.090 18 15 115 23 20 135 27 23 nst TLH , t THL Maximum Output Transition Time, Any Output (Figures 1 and 3)2.04.56.060 12 10 75 15 13 90 18 15 nsC IN Maximum Input Capacitance-101010pFC OUT Maximum Three-State Output Capacitance (Output in High-Impedance State) - 15 15 15 pFPower Dissipation Capacitance (Per Buffer) Typical @25°C,V CC =5.0 VC PDUsed to determine the no-load dynamic power consumption:P D =C PD V CC 2f+I CC V CC45 pFFigure 1. Switching Waveforms Figure 2. Switching WaveformsFigure 3. Test Circuit Figure 4. Test CircuitEXPANDED LOGIC DIAGRAM(1/4 of the Device)。

HSMS-2810中文资料

HSMS-2810中⽂资料HSMS-281xSurface Mount RF Schottky Barrier DiodesData SheetDescription/ApplicationsThese Schottky diodes are specifically designed for both analog and digital applications. This series offers a wide range of specifications and package configurations to give the designer wide flexibility. The HSMS?281x series of diodes features very low flicker (1/f) noise.Note that Avago’s manufacturing techniques assure that dice found in pairs and quads are taken from adjacent sites on the wafer, assuring the highest degree of match.Package Lead Code Identification, SOT-23/SOT-143 (Top View)COMMON CATHODECOMMON ANODE SERIES SINGLEPackage Lead Code Identification, SOT-323(Top View)Package Lead Code Identification, SOT-363(Top View)UNCONNECTEDTRIOHIGH ISOLATIONUNCONNECTED PAIRNotes:1. Package marking provides orientation and identification.2. See “Electrical Specifications” for appropriate package marking.Pin Connections and Package MarkingFeaturesSurface Mount Packages Low Flicker NoiseLow FIT (Failure in Time) Rate* Sixsigma Quality Level Single, Dual and Quad Versions Tape and Reel Options Available ? Lead?free Option AvailableFor more information see the Surface Mount Schottky Reliability Data Sheet.123654Electrical Specifications T C = 25°C, Single Diode [3]Maximum MaximumMinimum Maximum Forward Reverse Typical Part Package Breakdown Forward Voltage Leakage Maximum Dynamic Number Marking Lead Voltage Voltage V F (V) @ I R (nA) @ Capacitance Resistance HSMS [4] Code Code Configuration V BR (V) V F (mV) I F (mA)V R (V) C T (pF) R D (?)[5]2810 B0 0 Single 204101.0 35200 151.2152812 B2 2 Series2813 B3 3 Common Anode 2814 B4 4 Common Cathode 2815 B5 5 Unconnected Pair 2817 B7 7 Ring Quad [4] 2818 B8 8 Bridge Quad [4] 281B B0 B Single 281C B2 C Series281E B3 E Common Anode 281F B4 F Common Cathode 281K BK K High IsolationUnconnected Pair 281LBLL Unconnected Trio Test ConditionsI R = 10 m AI F = 1 mAV F = 0 V I F = 5 mAf = 1 MHzAbsolute Maximum Ratings [1] T C = 25°CESD WARNING: Handling Precautions Should Be Taken To Avoid Static Discharge.SymbolParameterUnitSOT-23/SOT-143SOT-323/SOT-363I f Forward Current (1 µs Pulse) Amp 11P IV Peak Inverse Voltage V Same as V BR Same as V BR T j Junction Temperature °C 150 150 T stg Storage Temperature °C ?65 to 150 ?65 to 150 θjcThermal Resistance [2]°C/W500150Notes:1. Operation in excess of any one of these conditions may result in permanent damage to the device.2. T C = +25°C, where T C is defined to be the temperature at the package pins where contact is made to the circuit board.Notes:1. ?V F for diodes in pairs and quads in 15 mV maximum at 1 mA.2. ?C TO for diodes in pairs and quads is 0.2 pF maximum.3. Effective Carrier Lifetime (τ) for all these diodes is 100 ps maximum measured with Krakauer method at 5 mA.4. See section titled “Quad Capacitance.”5. R D = R S + 5.2Ω at 25°C and I f = 5 mA.Quad CapacitanceCapacitance of Schottky diode quads is measured using an HP4271 LCR meter. This instrument effectively isolates individual diode branches from the others, allowing ac?curate capacitance measurement of each branch or each diode. The conditions are: 20 mV R.M.S. voltage at 1 MHz. Avago defines this measurement as “CM”, and it is equiva?lent to the capacitance of the diode by itself. The equiva?lent diagonal and adjacent capaci?tances can then be cal?culated by the formulas given below.In a quad, the diagonal capacitance is the capacitance be?tween points A and B as shown in the figure below. The diagonal capacitance is calculated using the following formulaC 1 x C 2 C 3 x C 4C DIAGONAL = _______ + _______C 1 + C 2 C 3 + C 41C ADJACENT = C 1 + ____________ 1 1 1–– + –– + ––C 2 C3C 4R j = 8.33 X 10-5 nTI b+ I sThe equivalent adjacent capacitance is the capacitance between points A and C in the figure below. This capaci?tance is calculated using the following formula 1 x C 2 C 3 x C 4C DIAGONAL = _______ + _______C 1 + C 2 C 3 + C 41C ADJACENT = C 1 + ____________1 1 1–– + –– + –– C2 C 3C 4R j =8.33 X 10-5 nT I b + I sThis information does not apply to cross?over quad di?odes.jR j =8.33 X 10-5 nTI b + I swhereI b = externally applied bias current in ampsI s = saturation current (see table of SPICE parameters)T = temperature, °Kn = ideality factor (see table of SPICE parameters)Note:To effectively model the packaged HSMS-281x product, please refer to Application Note AN1124.R S = series resistance (see Table of SPICE parameters)C j = junction capacitance (see Table of SPICE parameters)Linear Equivalent Circuit Model Diode ChipESD WARNING:Handling Precautions Should Be Taken To Avoid Static Discharge.SPICE ParametersParameterUnitsHSMS-281xB V V 25C J0 pF 1.1 E G eV 0.69 I BV A E?5 I S A 4.8E?9 N 1.08 R S Ω 10 P B V 0.65 P T 2M0.5Typical Performance, T C = 25°C (unless otherwise noted), Single DiodeFigure 1. Forward Current vs. Forward Voltage at Temperatures.I F – F O R W A R D C U R R E N T (m A )V F – FORWARD VOLTAGE (V)Figure 2. Reverse Current vs. Reverse Voltage at Temperatures.I R – R E V E R S E C U R R E N T (n A )V R – REVERSE VOLTAGE (V)1100010010100,00010,000Figure 3. Dynamic Resistance vs. Forward Current.0.11100R D – D Y N A M I C R E S I S T A N C E ()I F – FORWARD CURRENT (mA)101101000100Figure 4. Total Capacitance vs. Reverse Voltage.***********14C T – C A P A C I T A N C E (p F )V R – REVERSE VOLTAGE (V)00.750.500.251.251V F - FORWARD VOLTAGE (V)Figure 5. Typical V f Match, Pairs and Quads.301010.3I F - F O R W A R D C U R R E N T (m A )V F - F O R W A R D V O L T A G E D I F F E R E N C E (m V )Applications InformationIntroduction— Product SelectionAvago’s family of Schottky products provides unique solu?tions to many design problems.The first step in choosing the right product is to select the diode type. All of the products in the HSMS?282x fam?ily use the same diode chip, and the same is true of the HSMS?281x and HSMS?280x families. Each family has a dif?ferent set of characteristics which can be compared most easily by consulting the SPICE parameters in Table 1.A review of these data shows that the HSMS?280x family has the highest breakdown voltage, but at the expense of a high value of series resistance (R s). In applications which do not require high voltage the HSMS?282x family, with a lower value of series resistance, will offer higher current carrying capacity and better performance. The HSMS?281x family is a hybrid Schottky (as is the HSMS?280x), offering lower 1/f or flicker noise than the HSMS?282x family.In general, the HSMS?282x family should be the designer’s first choice, with the ?280x family reserved for high volt?age applications and the HSMS?281x family for low flicker noise applications.Assembly InstructionsSOT-323 PCB FootprintA recommended PCB pad layout for the miniature SOT?323 (SC?70) package is shown in Figure 6 (dimensions are in inches). This layout provides ample allowance for pack?age placement by automated assembly equipment with?out adding parasitics that could impair the performance.Dimensions in inchesFigure 6. Recommended PCB Pad Layout for Avago’s SC70 3L/SOT-323 Products. Assembly InstructionsSOT-363 PCB FootprintA recommended PCB pad layout for the miniature SOT?363 (SC?70, 6 lead) package is shown in Figure 7 (dimen?sions are in inches). This layout provides ample allowance for package placement by automated assembly equip?ment without adding parasitics that could impair the per?formance.Dimensions in inchesFigure 7. Recommended PCB Pad Layout for Avago’s SC70 6L/SOT-363 Products.Table 1. Typical SPICE Parameters.Parameter Units HSMS-280x HSMS-281x HSMS-282xB V V 75 25 15C J0pF 1.6 1.1 0.7E G eV 0.69 0.69 0.69I BV A 1 E?5 1 E?5 1 E?4I S A 3 E?8 4.8 E?9 2.2 E?8N 1.08 1.08 1.08R S? 30 10 6.0P B (V J) V 0.65 0.65 0.65P T (XTI) 2 2 2M 0.5 0.5 0.5Figure 8. Surface Mount Assembly Profile.SMT AssemblyReliable assembly of surface mount components is a com?plex process that involves many material, process, and equipment factors, including: method of heating (e.g., IR or vapor phase reflow, wave soldering, etc.) circuit board material, conductor thickness and pattern, type of solder alloy, and the thermal conductivity and thermal mass of components. Components with a low mass, such as the SOT package, will reach solder reflow temperatures faster than those with a greater mass.Avago’s SOT diodes have been qualified to the time?tem?perature profile shown in Figure 8. This profile is repre?sentative of an IR reflow type of surface mount assembly process.After ramping up from room temperature, the circuit board with components attached to it (held in place with solder paste) passes through one or more preheat zones.The preheat zones increase the temperature of the board and components to prevent thermal shock and begin evaporating solvents from the solder paste. The reflow zone briefly elevates the temperature sufficiently to pro?duce a reflow of the solder.The rates of change of temperature for the ramp?up and cool?down zones are chosen to be low enough to not cause deformation of the board or damage to compo?nents due to thermal shock. The maximum temperature in the reflow zone (T MAX ) should not exceed 260°C. These parameters are typical for a surface mount assem?bly process for Avago diodes. As a general guideline, the circuit board and components should be exposed only to the minimum temperatures and times necessary to achieve a uniform reflow of solder.25T e m p e r a t u r eTpT Lead-Free Reflow Profile Recommendation (IPC/JEDEC J-STD-020C)Reflow ParameterLead-Free AssemblyAverage ramp?up rate (Liquidus Temperature (T S(max) to Peak)3°C/ second max Preheat Temperature Min (T S(min))150°C Temperature Max (T S(max))200°CTime (min to max) (t S )60?180 seconds Ts(max) to TL Ramp?up Rate 3°C/second maxTime maintained above:Temperature (T L )217°CTime (t L )60?150 seconds Peak Temperature (T P )260 +0/?5°C Time within 5 °C of actual Peak temperature (t P )20?40 seconds Ramp?down Rate 6°C/second max Time 25 °C to Peak Temperature8 minutes maxNote 1: All temperatures refer to topside of the package, measured on the package body surface Package DimensionsOutline 23 (SOT-23)A1Notes:XXX-package marking Drawings are not to scale DIMENSIONS (mm)MIN.0.790.0000.370.0862.731.150.891.780.452.100.45MAX.1.200.1000.540.1523.131.501.022.040.602.700.69 SYMBOL A A1B CD E1e e1e2E LOutline SOT-323 (SC-70 3 Lead)A1Notes:XXX-package marking Drawin g s are not to scaleDIMENSIONS (mm)MIN.0.800.000.15 0.101.801.101.80MAX.1.000.100.400.202.251.402.40SYMBOL A A1B C D E1e e1E L 1.30 typical 0.65 typical 0.425 typicalPart Number Ordering InformationNo. ofPart NumberDevicesContainerHSMS?281x?TR2G 10000 13" Reel HSMS?281x?TR1G 3000 7" ReelHSMS?281x?BLKG100antistatic bagx = 0, 2, 3, 4, 5, 7, 8, B, C, E, F, K, LDevice OrientationFor Outline SOT-143Note: "AB" represents package marking code. "C" re p resents date code.END VIE WTOP VIEW For Outlines SOT-23, -323For Outline SOT-363USER FEEDNote: "AB" represents package marking code. "C" represents date code.END VIEWTOP VIEW END VIEWTOP VIEW Note: "AB" represents package marking code."C" represents date code.Outline 143 (SOT-143)A1Notes:XXX-package marking Drawings are not to scale DIMENSIONS (mm)MIN.0.790.0130.360.760.0862.801.200.891.780.452.100.45 MAX.1.0970.100.540.920.1523.061.401.022.040.602.650.69SYMBOLA A1B B1CD E1e e1e2E LOutline SOT-363 (SC-70 6 Lead)For Outline SOT-23For Outline SOT-143DESCRIPTIONSYMBOL SIZE (mm)SIZE (INCHES)LENGTH WIDTH DEPTH PITCHBOTTOM HOLE DIAMETER A 0B 0K 0P D 1 3.15± 0.102.77± 0.101.22± 0.104.00± 0.101.00 + 0.050.124± 0.0040.109±0.0040.048± 0.0040.157± 0.0040.039± 0.002CAVITYDIAMETER PITCH POSITION D P 0E 1.50 + 0.104.00± 0.101.75± 0.100.059 + 0.0040.157± 0.0040.069±0.004PERFORATIONWIDTHTHICKNESSW t18.00 + 0.30 – 0.100.229± 0.0130.315 + 0.012 – 0.0040.009± 0.0005CARRIER TAPE CAVITY TO PERFORATION (WIDTH DIRECTION)CAVITY TO PERFORATION (LENGTH DIRECTION)F P 23.50± 0.052.00± 0.050.138± 0.0020.079± 0.002DISTANCE BETWEEN CENTERLINE1DESCRIPTIONSYMBOL SIZE (mm)SIZE (INCHES)LENGTH WIDTH DEPTH PITCHBOTTOM HOLE DIAMETER A 0B 0K 0P D 1 3.19± 0.102.80± 0.101.31± 0.104.00± 0.101.00 + 0.250.126± 0.0040.110±0.0040.052± 0.0040.157± 0.0040.039 + 0.010CAVITYDIAMETER PITCH POSITION D P 0E 1.50 + 0.104.00± 0.101.75± 0.100.059 + 0.0040.157± 0.0040.069±0.004PERFORATIONWIDTHTHICKNESSW t18.00 + 0.30 – 0.100.254± 0.0130.315+ 0.012 – 0.0040.0100± 0.0005CARRIER TAPE CAVITY TO PERFORATION (WIDTH DIRECTION)CAVITY TO PERFORATION (LENGTH DIRECTION)F P 23.50± 0.052.00± 0.050.138± 0.0020.079± 0.002DISTANCEXFor Outlines SOT-323, -363(CARRIER TAPE THICKNESS)(COVER TAPE THICKNESS)DESCRIPTIONSYMBOL SIZE (mm)SIZE (INCHES)LENGTH WIDTH DEPTH PITCHBOTTOM HOLE DIAMETER A 0B 0K 0P D 1 2.40± 0.102.40± 0.101.20± 0.104.00± 0.101.00 + 0.250.094± 0.0040.094±0.0040.047± 0.0040.157± 0.0040.039 + 0.010CAVITYDIAMETER PITCH POSITION D P 0E 1.55± 0.054.00± 0.101.75± 0.100.061± 0.0020.157± 0.0040.069±0.004PERFORATIONWIDTHTHICKNESS W t 18.00± 0.300.254± 0.020.315± 0.0120.0100± 0.0008CARRIER TAPE CAVITY TO PERFORATION (WIDTH DIRECTION)CAVITY TO PERFORATION (LENGTH DIRECTION)F P 2 3.50± 0.052.00± 0.050.138± 0.0020.079± 0.002DISTANCEFOR SOT-323 (SC70-3 LEAD)An8°C MAX FOR SOT-363 (SC70-6 LEAD)10°C MAXANGLEWIDTHTAPE THICKNESS C T t 5.4± 0.100.062± 0.0010.205± 0.0040.0025± 0.00004COVER TAPE For product information and a complete list of distributors, please go to our web site: /doc/a9472ff3770bf78a6529546e.html Avago, Avago Technologies, and the A logo are trademarks of Avago Technologies Limited in the United States and other countries.Data subject to change. Copyright ? 2005-2008 Avago Technologies Limited. All rights reserved. Obsoletes 5989-4021EN AV02-1367EN - June 23, 2008。

Z0109NN,135中文资料(nxp)中文数据手册「EasyDatasheet - 矽搜」

Z0103MA/MN/NA/NN

Z0107MA/MN/NA/NN

Z0109MA/MN/NA/NN

IH

防护持电流

Z0103MA/MN/NA/NN

Z0107MA/MN/NA/NN

Z0109MA/MN/NA/NN

VT

通态电压

VGT

门极触发电压

ID

动态特性

dV D/dt

dV com/dt

断态泄漏电流

崛起临界率 断态电压

Min Max 单元

-

600 V

-

800 V

-

600 V

-

800 V

-

8

A

-

8.5

A

-

1

A

-

1

A

-

0.35 A2s

-

20

A/µs

-

1.0

A

-

2.0

W

-

0.1

W

40 +150 °C

40 +125 °C

芯片中文手册,看全文,戳 飞利浦半导体

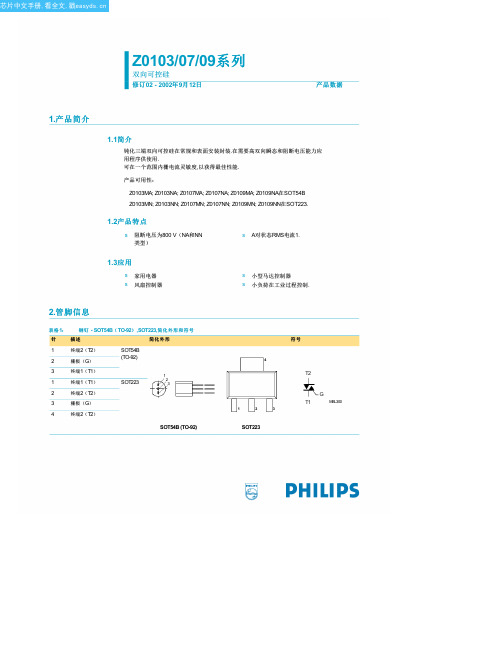

Z0103/07/09系列

双向可控硅

1.6

Ptot

1.2产品特点

s 阻断电压为800 V(NA和NN

类型)

s A对状态RMS电流1.

1.3应用

s 家用电器 s 风扇控制器

s 小型马达控制器 s 小负荷在工业过程控制.

2.管脚信息

表格 1: 钢钉 - SOT54B( TO-92) ,SOT223,简化外形和符号

针

描述

简化外形

1

终端2(T2)

2

栅极(G)

点SOT223

从交界处领导热电阻

SEN-R-956-003中文资料

TECHNICAL DATA SHEET 4200…SURFACE MOUNT DIE WITH HEAT ABSORBING STANDOFF TERMINAL STRIPS TRANSIENT VOLTAGE SUPPRESSOR 500 WATT SERIES Glass Passivated Die Plus Dual Heat StripsFeatures:• Low Profile• Broad Voltage Range Available - - 6.8 to 200 Volts • Broad Spectrum Transient Suppression• Rapid Response - - 4 nanoseconds typical• Built-in Heat Absorbing Terminations• Electrically Similar to Mil-Prf-19500/516 Applications:• Connector I/O Surge Suppression• Data Line Protection Description: This is a bipolar transient voltage suppressor series extending from 6.8 volts to 200 volts intended for surface mount applications.Each device comes as a “Cell” with its own heat absorbing terminals pre-bonded at high temperature. This permits mounting on printed circuit boards that cannot provide their own heat sinking. Each terminal is silver plated and is solderable permitting solder down attachment with a very small footprint. Each unit is bi-symmetrical so any orientation can be used.ELECTRICAL CHARACTERISTICSPARAMETER SYMBOL Test Conditions Min TYP Max.Units Response Turn-on Time ton 2 5 nsTransient Energy Pulse (Cell) Ep 1 10uS rise, I= 0.5Ip at t=100us (exponentialdecay)1500 WTransient Energy Pulse (Cell) Ep 2 10uS rise, I= 0.5Ip at t=1.0mS (exponentialdecay)500 WTransient Energy Pulse (Cell) Ep 3 10uS rise, I= 0.5Ip at t=10mS (exponentialdecay)150 WTransient Energy Pulse (Cell) Ep 4 10uS rise, I= 0.5Ip at t=50mS (exponentialdecay)70 WTransient Energy Pulse(Cell)Ep 5 10uS rise, I= 0.5Ip at t=50mS (step pulse) 50 W Electrical Parameters See TableMaximum SolderTemperatureTmax 10 second exposure 300 ºC Thermal Resistance (J-C) ΤJC Assume heat sink on terminal strip ends 18 30 ºC/WNote 1: “Die Only” configuration requires user to provide adequate energy absorption. Note 2: Terminal strips are 0.009” to 0.011” thick copper with nickel and silver plate.0.034"0.039"Typ0.052"0.056"0.0115"0.0155"Bipolar Die OnlySEN-R-956-XXX 500Watt TVS SeriesNominal Vz min Vz max TC (nom) Ir max Part Vz Iz @ Iz @ Iz of Vz Vr @ Vr Vcc Ip Number (V) (mA) (V) (V) (%.°C) (V) (uA) (V) (A) SEN-R-956-001 6.8 10 6.40 7.25 0.050 5.0 1600 9.2 54.3 SEN-R-956-002 7.2 10 6.67 7.67 0.060 6.0 1600 10.3 48.5 SEN-R-956-003 7.8 10 7.22 8.30 0.060 6.5 1000 11.2 44.6 SEN-R-956-004 8.4 10 7.78 8.95 0.060 7.0 400 12.0 41.7 SEN-R-956-005 9.0 1 8.33 9.58 0.070 7.5 200 12.9 38.8 SEN-R-956-006 9.6 1 8.89 10.23 0.070 8.0 100 13.6 36.8 SEN-R-956-007 10 1 9.44 10.82 0.070 8.5 20 14.4 34.7 SEN-R-956-008 11 1 10.00 11.50 0.080 9.0 10 15.4 32.5 SEN-R-956-009 12 1 11.10 12.80 0.080 10.0 5 17.0 29.4 SEN-R-956-010 13 1 12.20 14.00 0.080 11.0 5 18.2 27.5 SEN-R-956-011 14 1 13.30 15.50 0.085 12.0 5 19.9 25.1 SEN-R-956-012 15 1 14.40 16.50 0.085 13.0 5 21.5 23.3 SEN-R-956-013 17 1 15.60 17.90 0.085 14.0 5 23.2 21.6 SEN-R-956-014 18 1 16.70 19.20 0.090 15.0 5 24.4 20.5 SEN-R-956-015 19 1 17.80 20.50 0.090 16.0 5 26.0 19.2 SEN-R-956-016 20 1 18.90 21.70 0.090 17.0 5 27.6 18.1 SEN-R-956-017 22 1 20.00 23.30 0.095 18.0 5 29.2 17.1 SEN-R-956-018 24 1 22.20 25.50 0.095 20.0 5 32.4 15.4 SEN-R-956-019 26 1 24.40 28.00 0.095 22.0 5 35.5 14.1 SEN-R-956-020 29 1 26.70 30.70 0.095 24.0 5 38.9 12.9 SEN-R-956-021 31 1 28.90 33.20 0.095 26.0 5 42.1 11.9 SEN-R-956-022 33 1 31.10 35.80 0.095 28.0 5 45.4 11.0 SEN-R-956-023 36 1 33.30 38.30 0.095 30.0 5 48.4 10.3 SEN-R-956-024 39 1 36.70 42.20 0.100 33.0 5 53.3 9.4 SEN-R-956-025 43 1 40.00 46.00 0.100 36.0 5 58.1 8.6 SEN-R-956-026 48 1 44.40 51.10 0.100 40.0 5 64.5 7.8 SEN-R-956-027 51 1 47.80 54.90 0.100 43.0 5 69.4 7.2 SEN-R-956-028 54 1 50.00 57.50 0.100 45.0 5 72.7 6.9 SEN-R-956-029 57 1 53.30 61.30 0.100 48.0 5 77.4 6.5 SEN-R-956-030 61 1 56.7 65.2 0.100 51.0 5 82.4 6.1 SEN-R-956-031 65 1 60.0 69.0 0.100 54.0 5 87.1 5.7 SEN-R-956-032 69 1 64.4 74.1 0.105 58.0 5 93.6 5.3 SEN-R-956-033 72 1 66.7 76.7 0.105 60.0 5 96.8 5.2 SEN-R-956-034 76 1 71.1 81.8 0.105 64.0 5 103.0 4.9 SEN-R-956-035 84 1 77.8 89.5 0.110 70.0 5 113.0 4.4 SEN-R-956-036 90 1 83.3 95.8 0.110 75.0 5 121.0 4.1 SEN-R-956-037 93 1 86.7 99.7 0.110 78.0 5 126.0 4.0 SEN-R-956-038 101 1 94.4 108.2 0.110 85.0 5 137.0 3.6 SEN-R-956-039 108 1 100.0 115.5 0.110 90.0 5 146.0 3.4 SEN-R-956-040 120 1 111.0 128.0 0.110 100.0 5 162.0 3.1 SEN-R-956-041 131 1 122.0 140.5 0.110 110.0 5 177.0 2.8 SEN-R-956-042 143 1 133.0 153.0 0.110 120.0 5 193.0 2.6 SEN-R-956-043 155 1 144.0 165.5 0.110 130.0 5 209.0 2.4 SEN-R-956-044 180 1 167.0 192.5 0.110 150.0 5 243.0 2.1 SEN-R-956-045 192 1 178.0 205.0 0.110 160.0 5 259.0 1.9 SEN-R-956-046 203 1 189.0 217.5 0.110 170.0 5 275.0 1.81Time (s)Clamp Power vs Time for Sensitron 500W TVS SeriesTime (mS)Exponential Decay Pulse WaveformRated Vz of Device (V)Reverse Junction Capacitance for Sensitron 500W TVSSENSITRONSEMICONDUCTORTECHNICAL DATADISCLAIMER:1- The information given herein, including the specifications and dimensions, is subject to change without prior notice to improve product characteristics. Before ordering, purchasers are advised to contact the Sensitron Semiconductor sales department for the latest version of the datasheet(s).2- In cases where extremely high reliability is required (such as use in nuclear power control, aerospace and aviation, traffic equipment, medical equipment, and safety equipment), safety should be ensured by using semiconductor devices that feature assured safety or by means of users’ fail-safe precautions or other arrangement.3- In no event shall Sensitron Semiconductor be liable for any damages that may result from an accident or any other cause during operation of the user’s units according to the datasheet(s). Sensitron Semiconductor assumes no responsibility for any intellectual property claims or any other problems that may result from applications of information, products or circuits described in the datasheets.4- In no event shall Sensitron Semiconductor be liable for any failure in a semiconductor device or any secondary damage resulting from use at a value exceeding the absolute maximum rating.5- No license is granted by the datasheet(s) under any patents or other rights of any third party or Sensitron Semiconductor.6- The datasheet(s) may not be reproduced or duplicated, in any form, in whole or part, without the expressed written permission of Sensitron Semiconductor.7- The products (technologies) described in the datasheet(s) are not to be provided to any party whose purpose in their application will hinder maintenance of international peace and safety nor are they to be applied to that purpose by their direct purchasers or any third party. When exporting these products (technologies), the necessary procedures are to be taken in accordance with related laws and regulations.。

数控加工-数控技术培训学习教程 142页 精品

数控技术培训学习教程随着现代工业设备自动化,越来越多的工厂设备将采用PLC、变频器、人机介面等自动化器件来控制,因此设备自动化程度越来越高。

对设备的维护人员的技术要求越来越严格。

作为一名合格的技术员,需要掌握的技能也越来越多,越来越全面性,以此来满足自动化的发展及要求,因此设备相关的资料及软件,对我们技术员来说是必需具备的,为了满足大家的要求。

经过多年的积累,整理出四种最常用的三菱、OMRON 、AB、及西门子公司的相关资料及软件,特价向大家提供,详细软件资料清单见下面。

A盘:包含:西门子新版LOGOV4.0控制器编程软件,LOGO新版使用手册大全。

新版S7-200PLC中文版编程软件,s7_200_sim模拟软件汉化版,S7-200的中文系统手册大全。

S7-200上位机软件PC_Access_V10。

OP、TP系列中文版编程软件及编程手册大全,WINCC中文版编程手册,Protool中文手册,西门子STEP5教程中文版(NEW),PG702编程器操作手册,所有西门子公司自动化设备相关的中文资料,S7-200与S7-300的应用论文集,S7-200的应用实例中文注释,S7-400.S7-300梯形图(LAD) 中文版编程手册等。

(共650M,详细清单见A 盘说明)B盘:包含:三菱FX、A、Q系列GX-Developer V7.08中文版PLC编程软件及中文使用手册。

三菱FX20GM位置控制器编程软件、三菱PLC程序调试离线仿真软件GX-Simulator6中文版、三菱PLCFX最新FXGPWINV330(中文版),三菱FX系列仿真软件LTT-C简体中文版、三菱PLC可编程控制器教材、FX2N、FX2NC、FX1N、FXNS、FX0N、FX0S系列中文编程手册大全,FX随机手册及模块手册大全,FX-10P、20P编程器中文使用说明,三菱FR系列变频器使用手册大全。

(共650M,详细清单见B盘说明)C盘:包含:OMRON-SSS中文版PLC编程软件,OMRON全系列中文版编程软件CX-P V3.2、Cx-simulator离线仿真软件,人机介面NT系列设计软件,SysWin34OMRON最新开发的智能控制器的编程仿真软件,最新CS1-CJ1-CJ1M 系列PLC中文版操作手册、指令参考手册、编程手册大全、高速计数器、操位置控制、通信单元、温度控制等模块中文手册大全,CX-P中文版软件手册,OMRON PLC培训教材(编程器 SSS使用、CPMIA基础及CPMIA系统)。

SI2302-TP;中文规格书,Datasheet资料

Revision: A

/

3 of 5

2011/01/01

VGS, Gate to Source Voltage (V) ID, Drain Current (A)

VTH, Normalized Gate-Source Threshold Voltage

RDS(ON), Normalized RDS(ON), On-Resistance(Ohms)

IS, Source-drain current (A)

ID, Drain Current (A)

SI2302

10 25 C

Maximum Ratings @ 25OC Unless Otherwise Specified

Symbol VDS ID IDM VGS

PD R©JA

TJ

TSTG

Parameter Drain-source Voltage Drain Current-Continuous Drain Current-Pulsed a Gate-source Voltage

MCC

TM

Micro Commercial Components

5 VDS=10V ID=3.6A

4

3

2

1

0

0

2

4

6

Qg, Total Gate Charge (nC)

Figure 7. Gate Charge

VDD

RL VIN

D

VOUT

VGS

RGEN G

S

Figure 9. Switching Test Circuit

SA210A中文资料

DO-15

Dim

Min

Max

A

25.4

—

B

5.50

7.62

C

0.71

0.864

D

2.60

3.60

All Dimensions in mm

“C” Suffix Designates Bi-directional Devices “A” Suffix Designates 5% Tolerance Devices No Suffix Designates 10% Tolerance Devices

BREAKDOWN VOLTAGE

VBR (V) MAX. @IT

SA180 SA180A SA190 SA190A

180.00 180.00 190.00 190.00

198.00 198.00 209.00 209.00

253.80 230.40 267.90 243.20

SA200 SA200A SA210 SA210A

200.00 200.00 210.00 210.00

220.00 220.00 231.00 231.00

282.00 256.00 296.10 268.80

SA220 SA220A

220.00 220.00

242.00 242.00

310.20 281.60

TEST CURRENT

IT (mA)

200.00 200.00 210.00 210.00

220.00 220.00 231.00 231.00

282.00 256.00 296.10 268.80

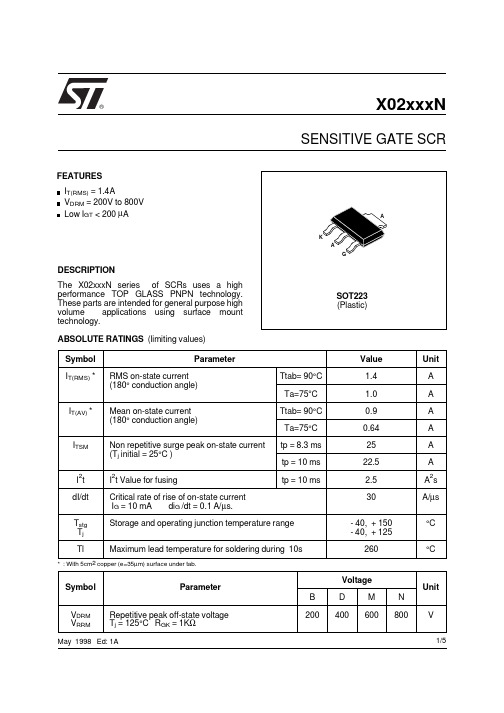

X02xxxN中文资料

Sensitivity

02

03

05

20

20

200

200

50

0.8

0.1

8 0.5

5

6

1.5

5

200

15

20

15

100

Fig.8 : On-state characteristics (maximum values).

I TSM (A). I2 t (A2 s) 100

ITSM 10

I2 t

1 1

Tj initial = 25oC

tp(ms) 10

I TM (A) 100

Tj initial 25oC

10

Tj max

The ST logo is a trademark of STMicroelectronics

VD=67%VDRM RGK = 1 KΩ

ITM= 3 x IT(AV) VR=35V dI/dt=10A/µs tp=100µs dV/dt=2V/µs VD= 67%VDRM RGK = 1 KΩ

Tj= 25°C MIN MAX

Tj= 25°C MAX Tj= 125°C MIN

Tj= 25°C MIN Tj= 25°C TYP

0.8

= 180o

0.6

0.4

0.2 0.0

0

Ttab (oC) 10 20 30 40 50 60 70 80 90 100 110 120 130

Fig.4 : Relative variation of thermal impedance junction to ambient versus pulse duration.

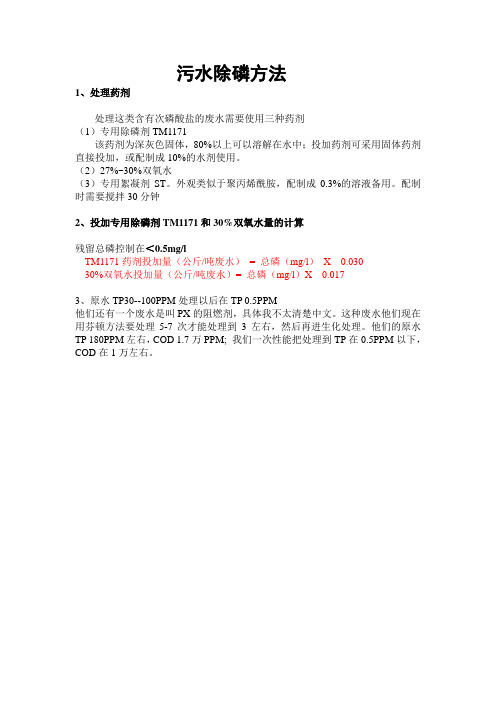

污水除磷方法

污水除磷方法

1、处理药剂

处理这类含有次磷酸盐的废水需要使用三种药剂

(1)专用除磷剂TM1171

该药剂为深灰色固体,80%以上可以溶解在水中;投加药剂可采用固体药剂直接投加,或配制成10%的水剂使用。

(2)27%~30%双氧水

(3)专用絮凝剂ST。

外观类似于聚丙烯酰胺,配制成0.3%的溶液备用。

配制时需要搅拌30分钟

2、投加专用除磷剂TM1171和30%双氧水量的计算

残留总磷控制在<0.5mg/l

TM1171药剂投加量(公斤/吨废水)= 总磷(mg/l)X 0.030

30%双氧水投加量(公斤/吨废水)= 总磷(mg/l)X 0.017

3、原水TP30--100PPM处理以后在TP 0.5PPM

他们还有一个废水是叫PX的阻燃剂,具体我不太清楚中文。

这种废水他们现在用芬顿方法要处理5-7次才能处理到3左右,然后再进生化处理。

他们的原水TP 180PPM左右,COD 1.7万PPM; 我们一次性能把处理到TP在0.5PPM以下,COD在1万左右。

IPP05N03L中文资料

IPB05N03LOpti MOS ® Buck converter seriesProduct Summary V DS30V R DS(on) max. SMD version 4.9m ΩID80AFeature• N-Channel• Logic Level• Very low on-resistance R DS(on)• Excellent Gate Charge x R DS(on) product (FOM)• Superior thermal resistance• 175°C operating temperature • Avalanche rated • d v /d t rated• Ideal for fast switching buck convertersP- TO263 -3-2P- TO220 -3-1Marking 05N03L 05N03LType Package Ordering Code IPP05N03L P- TO220 -3-1Q67042-S4038IPB05N03L P- TO263 -3-2Q67040-S4343Maximum Ratings , at T j = 25 °C, unless otherwise specifiedParameterSymbol Value Unit Continuous drain current 1)T C = 25 °C 1)I D8080APulsed drain currentT C =25°CI D puls 320Avalanche energy, single pulseI D =55A, V DD =25V, R GS =25ΩE AS 60mJRepetitive avalanche energy, limited by T jmax 2)E AR 16Reverse diode d v /d tI S =80A, V DS =24V, d i /d t =200A/µs, T jmax =175°Cd v /d t 6kV/µs Gate source voltage V GS ±20V Power dissipationT C =25°CP tot 167W Operating and storage temperature T j , T stg-55... +175°C IEC climatic category; DIN IEC 68-155/175/56IPB05N03LThermal Characteristics Parameter SymbolValues Unitmin.typ.max.CharacteristicsThermal resistance, junction - case R thJC -0.60.9K/WSMD version, device on PCB:@ min. footprint @ 6 cm 2 cooling area 3)R thJA---- 6240Electrical Characteristics , at T j = 25 °C, unless otherwise specified ParameterSymbolValues Unitmin.typ.max.Static CharacteristicsDrain-source breakdown voltageV GS =0V, I D =1mAV (BR)DSS 30--VGate threshold voltage, V GS = V DSI D =100µAV GS(th) 1.2 1.62Zero gate voltage drain currentV DS =30V, V GS =0V, T j =25°C V DS =30V, V GS =0V, T j =125°CI DSS-- 0.0110 1100µAGate-source leakage currentV GS =20V, V DS =0VI GSS -1100nA Drain-source on-state resistanceV GS =4.5V, I D =55AV GS =4.5V, I D =55A, SMD versionR DS(on)-- 5.65.2 7.57.2m ΩDrain-source on-state resistance 4)V GS =10V, I D =55AV GS =10V, I D =55A, SMD versionR DS(on)--43.75.24.91Current limited by bondwire ; with an RthJC = 0.9K/W the chip is able to carry I D = 145A at 25°C, for detailed information see app.-note ANPS071E available at /optimos 2Defined by design. Not subject to production test.3Device on 40mm*40mm*1.5mm epoxy PCB FR4 with 6cm² (one layer, 70 µm thick) copper area for drain connection. PCB is vertical without blown air.4Diagrams are related to straight lead versionsIPB05N03LElectrical Characteristics ParameterSymbol ConditionsValues Unitmin.typ.max.Dynamic Characteristics Transconductance g fs V DS ≥2*I D *R DS(on)max , I D =80A55110-SInput capacitance C iss V GS =0V, V DS =25V, f =1MHz-25003320pF Output capacitanceC oss -9751300Reverse transfer capacitance C rss -215325Gate resistance R G -1.75-ΩTurn-on delay time t d(on)V DD =15V, V GS =10V, I D =20A, R G =2.7Ω-1015nsRise timet r -1827Turn-off delay time t d(off)-4466Fall timet f -2030Gate Charge Characteristics Gate to source charge Q gs V DD =15V, I D =40A-7.910.5nC Gate to drain charge Q gd -18.523.1Gate charge total Q g V DD =15V, I D =40A, V GS =0 to 5V -3645Output charge Q ossV DS =15V, I D =40A, V GS =0V-34.843.5nC Gate plateau voltage V (plateau)V DD =15V, I D =40A -3.2-VReverse DiodeInverse diode continuous forward currentI ST C =25°C--80AInv. diode direct current, pulsed I SM --320Inverse diode forward voltage V SD V GS =0V, I F =80A -0.95 1.26V Reverse recovery time t rr V R =15V, I F =l S , d i F /d t =100A/µs-46.558.1ns Reverse recovery chargeQ rr-55.569.4nCIPB05N03L1 Power dissipation P tot = f (T C )IPP05N03LP t o t2 Drain current I D = f (T C )parameter: V≥ 10 VI D4 Max. transient thermal impedance Z thJC = f (t p )parameter : D = t/T10 10 10 10 10 10 K/WZ t h JC3 Safe operating area I D = f ( V DS )parameter : D = 0 , T = 25 °C2I DIPB05N03L5 Typ. output characteristic I D = f (V DS ); T j =25°C parameter: t= 80 µsI D6 Typ. drain-source on resistance R DS(on) = f (I D )parameter: V m ΩR D S (o n )7 Typ. transfer characteristics I D = f ( V GS ); V DS ≥ 2 x I D x R DS(on)max parameter: t p = 80 µsI D8 Typ. forward transconductance g fs = f(I D ); T j =25°C parameter: g fsg f sIPB05N03L9 Drain-source on-state resistance R DS(on) = f (T j )parameter : I D = 55 A, VGS = 10 Vm Ω14IPP05N03LR D S (o n)10 Typ. gate threshold voltage V GS(th) = f (T j )parameter: V GS = V DSV GS (t h )11 Typ. capacitances C = f (V DS )parameter: V GS =0V, f =1 MHzC12 Forward character. of reverse diode I F = f (V SD )parameter: T, t p = 80 µsI FIPB05N03L13 Typ. avalanche energy E AS = f (T j )par.: I D = 55 A, V DD = 25 V, R GS = 25 Ω14 Typ. gate charge V GS = f (QGate )parameter: I = 40 A pulsedV GS15 Drain-source breakdown voltage V (BR)DSS = f (T j )parameter: I =10 mAV (B R )D S SIPB05N03L Published byInfineon Technologies AG,Bereichs KommunikationSt.-Martin-Strasse 53,D-81541 München© Infineon Technologies AG 1999All Rights Reserved.Attention please!The information herein is given to describe certain components and shall not be considered as warranted characteristics.Terms of delivery and rights to technical change reserved.We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement,regarding circuits, descriptions and charts stated herein.Infineon Technologies is an approved CECC manufacturer.InformationFor further information on technology, delivery terms and conditions and prices please contact your nearestInfineon Technologies Office in Germany or our Infineon Technologies Reprensatives worldwide (see address list). WarningsDue to technical requirements components may contain dangerous substances.For information on the types in question please contact your nearest Infineon Technologies Office.Infineon Technologies Components may only be used in life-support devices or systems with the expresswritten approval of Infineon Technologies, if a failure of such components can reasonably be expected tocause the failure of that life-support device or system, or to affect the safety or effectiveness of that deviceor system Life support devices or systems are intended to be implanted in the human body, or to supportand/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the healthof the user or other persons may be endangered.。

TPA62中文资料

TPA SERIESBIDIRECTIONAL CROWBAR PROTECTION.VOLTAGERANGE:FROM 62V TO 270V.HOLDING CURRENT :I H =150mA min.REPETITIVE PEAK PULSE CURRENT :I PP =50A,10/1000µs.FEATURESF126The TPA series are TRISIL devices especially de-signed for protecting sensitive telecommunication equipment against lightning and transient voltages induced by AC power lines.They are available in the F126axial package.TRISIL devices provide bidirectional protection by crowbar action.Their characteristic response to transient overvoltages makes them particularly suited to protect voltage sensitive telecommuni-cation equipment.DESCRIPTIONSCHEMATIC DIAGRAMTRISIL ™COMPLIES WITH THE FOLLOWING STANDARDS:Peak Surge Voltage (V)Voltage Waveform (µs)Current Waveform (µs)AdmissibleIpp (A)Necessary Resistor (Ω)(CCITT)ITU-K20100010/7005/31025-(CCITT)ITU-K17150010/7005/31038-VDE0433200010/7005/31050-VDE08782000 1.2/501/2050-IEC-1000-4-5level 3level 410/7001.2/505/3108/2050100--FCC Part 68,lightning surge type A150080010/16010/56010/16010/560755512.56.5FCC Part 68,lightning surge type B10009/7205/32025-BELLCORE TR-NWT-001089First level250010002/1010/10002/1010/10001505011.510BELLCORE TR-NWT-001089Second level 50002/102/1015011.5CNET l31-2410000.5/7000.8/31025-®October 1998-Ed:9A1/5Symbol ParameterV RM Stand-off voltageI RM Leakage current at stand-off voltage V R Continuous Reverse voltage V BR Breakdown voltage V BO Breakover voltage I H Holding current I BO Breakover current I PP Peak pulse current C CapacitanceELECTRICAL CHARACTERISTICS (T amb =25°C)Symbol ParameterValue Unit R th (j-l)Junction to leads (L lead =10mm)60°C/W R th (j-a)Junction to ambient on printed circuit (L lead =10mm)100°C/WTHERMAL RESISTANCES Note 1:I R measured at V R guarantee V BRmin ≥V R Note 2:Measured at 50Hz (1cycle)-See test circuit 1.Note 3:See test circuit 2.Note 4:V R =1V,F =1MHz.Refer to fig.3for C versus V R .TypeI RM @V RM I R @V R V BO @I BO I H C max.max.note 1max.note 2min.note 3max.note 4µAVµAVVmAmApFTPA62TPA68TPA100TPA120TPA130TPA180TPA200TPA220TPA240TPA27022222222225661901081171621801982162435050505050505050505062681001201301802002202402708290133160173240267293320360800800800800800800800800800800150150150150150150150150150150150150100100100100100100100100Symbol ParameterValue Unit P Power dissipation on infinite heatsink T amb =50 °C 1.7W I PP Peak pulse current10/1000µs 8/20µs 50100A I TSM Non repetitive surge peak on-state current tp =20ms 30A I 2t I 2t value for fusingtp =20ms 9A 2s dV/dt Critical rate of rise of off-state voltage V RM5kV/µs T stg T j Storage temperature range Maximum junction temperature-55to +150150°C °C T LMaximum lead temperatureforsolderingduring 10sat 5mmfrom case230°CABSOLUTE MAXIMUM RATINGS (T amb =25°C)TPA SERIES2/5TEST CIRCUIT 1FOR I BO and V BO parameters:220Vstatic relay.R1R2240140D.U.TV BO measureI BO measuretp =20msKTransformer 220V/800V5AAutoTransformer 220V/2AV outTEST PROCEDURE :Pulse Test duration (tp =20ms):-For Bidirectional devices =SwitchK is closed -For Unidirectional devices =Switch K is open.V OUT Selection-Device with V BO <200Volt-V OUT =250V RMS ,R 1=140Ω.-Device with V BO ≥ 200Volt-V OUT =480V RMS ,R 2=240Ω.TEST CIRCUIT 2for I H parameter.R-V PV BAT =-48VSurge generatorD.U.T .This is a GO-NOGO Test which allows to confirm the holding current (I H )level in a functional test circuit.TEST PROCEDURE :1)Adjust the current level at the I H value by short circuiting the AK of the D.U.T.2)Fire the D.U.T with a surge Current :Ipp =10A ,10/1000µs.3)The D.U.T will come back off-state within 50ms max.TPA SERIES3/5TSM (A)Fig.1:Non repetitive surge peak on-state current versus overload duration (Tj initial=25°C).Fig.2:Relative variation of holding current versus junction temperature.tp(s)Fig.5:Transient thermal impedance junction to ambient versus pulse duration (for FR4PC Board with T lead =10mm).V (V)R Fig.3:Relative variation of junction capacitance versus reverse applied voltage (typical values).Note:For V RM upper than 56V,the curve is extrapolated(dotted line).I (A)T V (V)T Fig.4:On-state current versus on-state voltage (typical values).TPA SERIES4/5ORDER CODETPA 100RLVOLTAGEPACKAGING:RL =tape and reel.=Ammopack.TRISIL PROTECTION 50APackaging :Standard packaging is in tape and reel.MARKING :Logo,Date Code,Part rmation furnished is believed to be accurate and reliable.However,STMicroelectronics assumes no responsIbility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use.No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics.Specifications mentioned in this publication are subject to change without notice.This publication supersedes and replaces all information previously supplied.STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written ap-proval of STMicroelectronics.The ST logo is a registered trademark of STMicroelectronics ©1998STMicroelectronics -Printed in Italy -All rights reserved.STMicroelectronics GROUP OF COMPANIESAustralia -Brazil -Canada -China -France -Germany -Italy -Japan -Korea -Malaysia -Malta -Mexico -Morocco -The Netherlands -Singapore -Spain -Sweden -Switzerland -Taiwan -Thailand -United Kingdom -U.S.A.Weight:0.40gPACKAGE MECHANICAL DATA F126PlasticACCDDBREF.DIMENSIONSMillimeters Inches Min.Typ.Max.Min.Typ.Max.A 6.05 6.20 6.350.2380.2440.250B2.953.003.050.1160.1180.120C 26311.0241.220D0.760.810.860.0300.0320.034TPA SERIES5/5。

Z9951AA中文资料

3.3V, 180MHz, Multi-Output Zero Delay BufferProduct Features• 180MHz Clock Support• Supports PowerPC TM, Intel and RISC Processors • 9 Clock Outputs: Frequency Configurable• Two Reference Clock Inputs for Dynamic Toggling • Oscillator or PECL Reference Input • Output Disable Control• Spread Spectrum Compatible • 3.3V Power Supply• Pin Compatible with MPC951• Industrial Temp. Range: -40°C to +85°C • 32-Pin TQFP PackageBlock DiagramFigure 1Frequency TableSEL (A:D)QA QB QC (0,1)QD (0:4)0000VCO/2VCO/4VCO/4VCO/40001VCO/2VCO/4VCO/4VCO/80010VCO/2VCO/4VCO/8VCO/40011VCO/2VCO/4VCO/8VCO/80100VCO/2VCO/8VCO/4VCO/40101VCO/2VCO/8VCO/4VCO/80110VCO/2VCO/8VCO/8VCO/40111VCO/2VCO/8VCO/8VCO/81000VCO/4VCO/4VCO/4VCO/41001VCO/4VCO/4VCO/4VCO/81010VCO/4VCO/4VCO/8VCO/41011VCO/4VCO/4VCO/8VCO/81100VCO/4VCO/8VCO/4VCO/41101VCO/4VCO/8VCO/4VCO/81110VCO/4VCO/8VCO/8VCO/41111VCO/4VCO/8VCO/8VCO/8Table 1Pin ConfigurationR E F _S E LP L L _E NT C L KV S SQ AV D D C Q BV S SP E C L _C L K #M R /O E #V D D CQ D 4V S SQ D 3V D D CQ D 2QC0VDDC QC1VSS QD0VDDC QD1VSSVDD FB_IN SELA SELB SELC SELD VSSPECL_CLK3.3V, 180MHz, Multi-Output Zero Delay Buffer Pin DescriptionPIN NAME PWR I/O TYPE Description8PECL_CLK I PU PECL Input Clock.9PECL_CLK#I PECL Input Clock.30TCLK I External Test Clock Input.28QA VDDC O Clock Output. See Frequency Table.26QB VDDC O Clock Output. See Frequency Table.22, 24QC(1,0)VDDC O Clock Outputs. See Frequency Table.12, 14, 16,QD(4:0)VDDC O Clock Outputs. See Frequency Table.18, 202FB_IN I PD Feedback Clock Input. Connect to an output for normal operation.10MR/OE#I Master Reset/Output Enable Input. When asserted high, resetsall of the internal flip-flops and also disables all of the outputs.When pulled low, releases the internal flip-flops from reset andenables all of the outputs.31PLL_EN I PLL Enable Input. When asserted high, PLL is enabled. Andwhen set low, PLL is bypassed.32REF_SEL I Reference Select Input. When high, TCLK is the reference clockand when low, PECL clock is selected.3, 4, 5, 6SEL(A:D)I Frequency Select Inputs. See Frequency Table.If SEL_ = 1, then QA divider = ÷4, QB:D divider = ÷8If SEL_ = 0, then QA divider = ÷2, QB:D divider = ÷411, 15, 19,VDDC 3.3V Power Supply for Output Clock Buffers.23, 271VDD 3.3V Power Supply for PLL7, 13, 17, 21,VSS Common Ground25, 29PD = Internal Pull-Down, PU = Internal Pull-Up.3.3V, 180MHz, Multi-Output Zero Delay BufferMaximum Ratings¹Maximum Input Voltage Relative to VSS: VSS - 0.3V Maximum Input Voltage Relative to VDD:VDD + 0.3V Storage Temperature:-65°C to + 150°C Operating Temperature:-40°C to +85°CMaximum ESD protection 2KV Maximum Power Supply: 5.5V Maximum Input Current:±20mAThis device contains circuitry to protect the inputs against damage due to high static voltages or electric field; however, precautions should be taken to avoid application of any voltage higher than the maximum rated voltages to this circuit. For proper operation, Vin and Vout should be constrained to the range:VSS<(Vin or Vout)<VDDUnused inputs must always be tied to an appropriate logic voltage level (either VSS or VDD).DC ParametersCharacteristicSymbol Min Typ Max Units ConditionsInput Low Voltage VIL VSS -0.8V Input High VoltageVIH 2.0-VDD V Input Low Current (@VIL = VSS)IIL -120µA Input High Current (@VIL =VDD)IIH 120µA Note 2Peak-to-Peak Input Voltage PECL_CLKVPP 3001000mV Note 3Common Mode Range PECL_CLK VCMR VDD-2.0-VDD-0.6V Output Low Voltage VOL 0.5V IOL = 40mA, Note 4Output High Voltage VOH 2.4V IOH = -40mA, Note 4Quiescent Supply Current IDDC -1520mA All VDDC and VDDPLL Supply Current IDD -1520mA VDD only Input CapacitanceCin--4pFVDD = VDDC = 3.3V ±5%, TA = -40°C to +85°CNote 1: The voltage on any input or I/O pin cannot exceed the power pin during power-up. Power supply sequencing is NOT required.Note 2: Inputs have pull-up, pull-down resistors that affect input current.Note 3: The VCMR is the difference from the most positive side of the differential input signal. Normal operation is obtained when the “High” input is within the VCMR range and the input lies within the VPP specification.Note 4: Driving series or parallel terminated 50Ω (or 50Ω to VDD/2) transmission lines. Output buffers are dual staged to control drive strength in order to reduce over / under shoot.3.3V, 180MHz, Multi-Output Zero Delay BufferAC Parameters 1SYMBOLPARAMETERMINTYP MAXUNITSCONDITIONSTr / Tf TCLK Input Rise / Fall 3.0ns Fref Reference Input Frequency Note 2Note 2MHz FrefDC Reference Input Duty Cycle 2575%Fvco PLL VCO Lock Range 200480MHz Tlock Maximum PLL lock Time 10ms Tr / Tf Output Clocks Rise / Fall Time4,50.10 1.0ns 0.8V to 2.0V -180QA = (÷2)120QA/QB = (÷4)FoutMaximum Output Frequency60MHzQB = (÷8)FoutDC Output Duty Cycle4,5TCYCLE/2 –1TCYCLE/2 + 1ns tpZL, tpZH Output enable time (all outputs)6ns tpLZ, tpHZ Output disable time (all outputs)7ns TCCJ Cycle to Cycle Jitter (peak to peak)4,5+/- 100ps TCLK to FB_IN Delay350250400ps Tpd PECL_CLK to FB_IN Delay3-950-770-600ps Fref = 50MHz,Feedback = VCO/8TSKEW0Any Output to Any Output Skew4,5-200350psVDD = VDDC = 3.3V +/- 5%, TA = -40°C to +85°CNote 1:Parameters are guaranteed by design and characterization. Not 100% tested in production.Note 2:Maximum and minimum input reference is limited by the VCO lock range.Note 3: The Tpd window is specified for a 50MHz input reference clock. The window will enlarge/reduce proportionally from the minimum limits with an increase/decrease of the input reference clock period.Note 4: Driving series or parallel terminator 50Ω (or 50Ω to VDD/2) transmission lines.Note 5: Outputs loaded with 30pF each3.3V, 180MHz, Multi-Output Zero Delay BufferDescriptionThe Z9951 has an integrated PLL that provides low skew and low jitter clock outputs for high performance microprocessors. The PLL is ensured stable operation given that the VCO is configured to run between 200 MHz to 480 MHz. This allows a wide range of output frequencies from 25MHz to 180MHz.The phase detector compares the input reference clock to the external feedback input. For normal operation, the external feedback input, FB_IN, is connected to one of the outputs. The internal VCO is running at multiples of the input reference clock set by SEL(A:D) select inputs, see Table 2. The VCO frequency is then divided down to provide the required output frequencies. The use of even dividers ensures that the output duty cycle remains at 50%.SELA QA SELB QB SELC QC SELD QD0÷20÷40÷40÷41÷41÷81÷81÷8Table 2Zero Delay BufferWhen used as a zero delay buffer the Z9951 will likely be in a nested clock tree application. For these applications the Z9951 offers a low voltage PECL clock input as a PLL reference. This allows the user to use LVPECL as the primary clock distribution device to take advantage of its far superior skew performance. The Z9951 then can lock onto the LVPECL reference and translate with near zero delay to low skew outputs.By using one of the outputs as a feedback to the PLL the propagation delay through the device is eliminated. The PLL works to align the output edge with the input reference edge thus producing a near zero delay. The reference frequency affects the static phase offset of the PLL and thus the relative delay between the inputs and outputs. Because the staticphase offset is a function of the reference clock the Tpd of the Z9951 is a function of the configuration used.3.3V, 180MHz, Multi-Output Zero Delay BufferPackage Drawing and Dimensions32 Pin TQFP Outline DimensionsINCHESMILLIMETERSSYMBOLMIN NOM MAX MIN NOM MAX A--0.047-- 1.20A 10.002-0.0060.05-0.15A20.037-0.0410.95- 1.05D -0.354--9.00-D 1-0.276--7.00-b0.012-0.0180.30-0.45e 0.031 BSC0.80 BSCL0.018-0.0300.45-0.753.3V, 180MHz, Multi-Output Zero Delay Buffer Ordering InformationPart Number Package Type Production FlowZ9951AA32 PIN TQFP Industrial, -40°C to +85°CNote:The ordering part number is formed by a combination of device number, device revision, package style, and screening as shown below.Marking:Example:CypressZ9951AADate Code, Lot #Z9951AAPackageA = TQFPRevisionDevice Number3.3V, 180MHz, Multi-Output Zero Delay BufferNoticeCypress Semiconductor Corp. reserves the right to make changes to its products in order to improve design, performance or reliability. Cypress Semiconductor Corp.assumes no responsibility for the use of its products in life supporting and medical applications where the failure or malfunction of the product could cause failure of the life supporting and medical systems. Products are not authorized for use in such applications unless a written approval is requested by the manufacturer and an approval is given in writing by Cypress Semiconductor Corp. for the use of itsproducts in the life supporting and medical applications.3.3V, 180MHz, Multi-Output Zero Delay Buffer Document Title: Z9951 3.3V, 180 MHz, Multi-Output Zero Delay BufferDocument Number: 38-07084Rev.ECNNo.IssueDateOrig. ofChangeDescription of Change**10712006/12/01IKA Convert from IMI to Cypress*A10806307/03/01NDP Changed Commercial to Industrial (See page 7)Delete Pull down in pin 9,10,30& 32; Delete Pull up in pin3,4,5,6, & 31 (See page 2)*B12276912/22/02RBI Add power up requirements to maximum ratingsinformation。

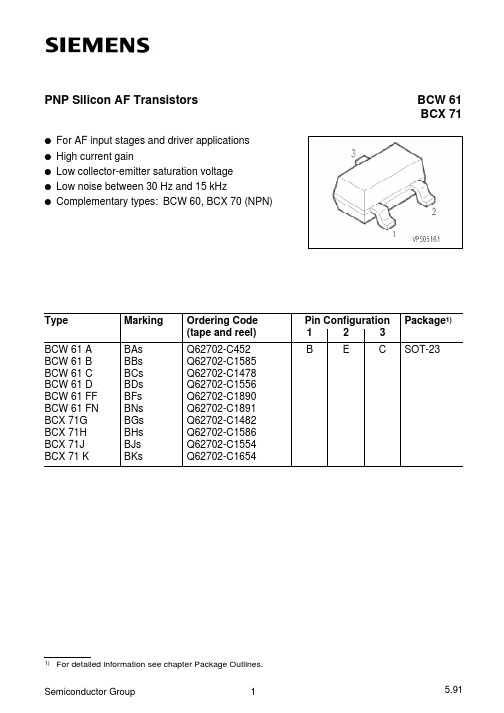

BCW61FF中文资料

PNP Silicon AF TransistorsBCW 61BCX 71Type Ordering Code (tape and reel)Marking Package 1)Pin Configuration BCW 61 A BCW 61 B BCW 61 C BCW 61 D BCW 61 FF BCW 61 FN BCX 71G BCX 71H BCX 71J BCX 71 KQ62702-C452Q62702-C1585Q62702-C1478Q62702-C1556Q62702-C1890Q62702-C1891Q62702-C1482Q62702-C1586Q62702-C1554Q62702-C1654BAs BBs BCs BDs BFs BNs BGs BHs BJs BKsSOT-23BEC123q For AF input stages and driver applications q High current gainq Low collector-emitter saturation voltage q Low noise between 30Hz and 15kHzqComplementary types:BCW 60, BCX 70 (NPN)Maximum Ratings ParameterSymbolValuesUnit Collector-emitter voltage V CE0VPeak collector current I CM Collector current I C mAJunction temperature T j ˚CTotal power dissipation,T S = 71˚C P tot mW Storage temperature range T stgCollector-base voltage V CB0Thermal Resistance 32100200330150– 65 … + 150Emitter-base voltage V EB0Peak base currentI BM 2003245323245BCW 61FF BCW 61BCX 715Junction - ambient 1)R th JA K/WJunction - soldering pointR th JS≤ 310≤ 240Electrical Characteristicsat T A = 25 ˚C, unless otherwise specified.VCollector-emitter breakdown voltage I C = 10mA BCW 61, BCW 61 FFBCX 71V (BR)CE03245––––nA nA µA µA Collector cutoff current V CB = 32V BCW 61, BCW 61 FF V CB = 45VBCX 71V CB = 32V,T A = 150˚C BCW 61, BCW 61 FF V CB = 45V,T A = 150˚C BCX 71I CB0––––––––20202020UnitValues ParameterSymbolmin.typ.max.DC characteristicsCollector-base breakdown voltage I C = 10µA BCW 61, BCW 61 FFBCX 71V (BR)CB03245––––Emitter-base breakdown voltage I E = 1µAV (BR)EB05–––DC current gain 1)I C = 10µA,V CE = 5VBCW 61 A, BCX 71 G BCW 61 B, BCX 71 HBCW 61 FF, BCW 61 C, BCX 71 J BCW 61 FN, BCW 61 D, BCX 71 KI C = 2mA,V CE = 5VBCW 61 A, BCX 71 G BCW 61 B, BCX 71 HBCW 61 FF, BCW 61 C, BCX 71 J BCW 61 FN, BCW 61 D, BCX 71 KI C = 50mA,V CE = 1VBCW 61 A, BCX 71 G BCW 61 B, BCX 71 HBCW 61 FF, BCW 61 C, BCX 71 J BCW 61 FN, BCW 61 D, BCX 71 Kh FE2030401001201802503806080100110140200300460170250350500––––––––220310460630––––nA Emitter cutoff current V EB = 4VI EB0––20Electrical Characteristicsat T A = 25 ˚C, unless otherwise specified.UnitValues ParameterSymbolmin.typ.max.VCollector-emitter saturation voltage 1)I C = 10mA,I B = 0.25mA I C = 50mA,I B = 1.25mA V CEsat––0.120.200.250.55Base-emitter saturation voltage 1)I C = 10mA,I B = 0.25mA I C = 50mA,I B = 1.25mA V BEsat––0.700.830.851.05Base-emitter voltage 1)I C = 10µA,V CE = 5V I C = 2mA,V CE = 5V I C = 50mA,V CE = 1V V BE (on)–0.55–0.520.650.78–0.75–DC characteristicsMHz Transition frequencyI C = 20mA,V CE = 5V,f = 100MHz f T –250–AC characteristicspFOutput capacitance V CB = 10V,f = 1MHz C obo –3–Input capacitance V CB = 0.5V,f = 1MHzC ibo –8–k ΩShort-circuit input impedance I C = 2mA,V CE = 5V,f = 1kHzBCW 61 A, BCX 71 G BCW 61 B, BCX 71 HBCW 61 FF, BCW 61 C, BCX 71 J BCW 61 FN, BCW 61 D, BCX 71 K h 11e––––2.73.64.57.5––––10–4Open-circuit reverse voltage transfer ratio I C = 2mA,V CE = 5V,f = 1kHzBCW 61 A, BCX 71 G BCW 61 B, BCX 71 HBCW 61 FF, BCW 61 C, BCX 71 J BCW 61 FN, BCW 61 D, BCX 71 Kh 12e–––1.52.02.03.0–––Electrical Characteristicsat T A = 25 ˚C, unless otherwise specified.dBNoise figureI C = 0.2mA,V CE = 5V,R S = 2k Ωf = 1kHz,∆f = 200HzBCW 61 A to BCX 71 K BCW 61 FF, BCW 61 FN F––21–2UnitValues ParameterSymbolmin.typ.max.AC characteristics–Short-circuit forward current transfer ratio I C = 2mA,V CE = 5V,f = 1kHzBCW 61 A, BCX 71 G BCW 61 B, BCX 71 HBCW 61 FF, BCW 61 C, BCX 71 J BCW 61 FN, BCW 61 D, BCX 71 K h 21e––––200260330520––––µsOpen-circuit output admittance I C = 2mA,V CE = 5V,f = 1kHzBCW 61 A, BCX 71 G BCW 61 B, BCX 71 HBCW 61 FF, BCW 61 C, BCX 71 J BCW 61 FN, BCW 61 D, BCX 71 K h 22e––––18243050––––µVEquivalent noise voltageI C = 0.2mA,V CE = 5V,R S = 2k Ωf = 10Hz … 50 HzBCW 61 FF, BCW 61 FNV n––0.11Total power dissipation P tot=f(T A*;T S) *Package mounted on epoxyPermissible pulse load P tot max/P tot DC =f (t p)Collector-base capacitance C CB0 =f (V CB0)Emitter-base capacitance C EB0 =f (V EB0)Transition frequency f T=f(I C)V CE = 5VBase-emitter saturation voltage I C =f (V BEsat )hFE = 40Collector current I C =f (V BE )V CE = 5V Collector-emitter saturation voltage I C =f (V CEsat )h FE= 40DC current gain h FE =f (I C )V CE = 5VCollector cutoff current I CB0=f (T A )h parameter h e =f (V CE )I C = 2mA h parameter h e =f (I C )V CE = 5VNoise figure F =f (V CE )I C = 0.2mA,R S = 2k Ω,f = 1kHzNoise figure F =f (f )I C = 0.2mA,R S = 2k Ω,V CE = 5V Noise figure F =f (I C )V CE = 5V,f= 1kHz Noise figure F =f (I C )V CE = 5V,f = 120HzNoise figure F =f (I C )V CE = 5V,f = 10kHz。

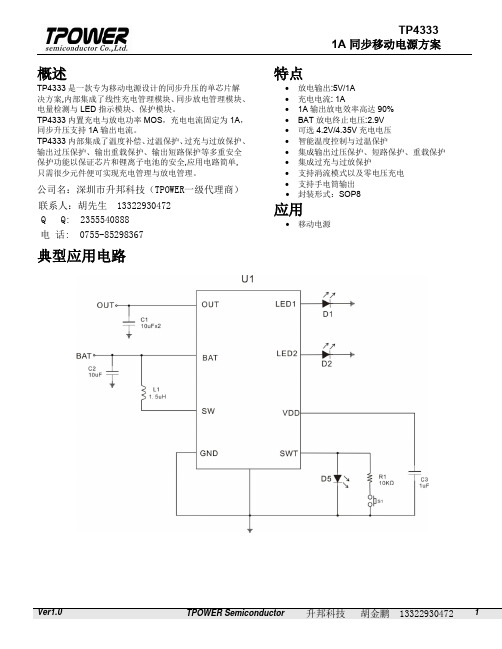

TP4333中文资料_TP4333规格书_TP4333 PDF

元件选择

1、输出电容 C1 选择质量较好的低 ESR 的贴片电容,否 则会影响输出纹波; 2、电感 L1 的饱和电流需大于 3A,否则因电感饱和可能 会导致芯片工作不正常;

PCB 设计参考

1、IC 下面敷铜接 GND,地线铺开面积要尽量大,其它 不重要的线都可以绕开以满足地线需要; 2、 建议电感旁边放置 10uF 而靠近芯片 BAT 脚放置 1uF 电容;如果只放一个 BAT 电容,必须保证电容位置既要 靠近芯片又要靠近电感;电容的地线尽量接在大面积地 线上,不要经过较小的地线再到芯片和大面积地; 3、输出电容 C1 尽量靠近芯片,其地线尽量接在大面积 地线上,不要经过较小的地线再到芯片和大面积地; 4、电感需靠近 BAT 电容,电感和 BAT 电容 C2 以及芯 片尽量在同一层而不要过过孔,电感到 SW 的走线尽量 短而粗;

保护功能

TP4333 集成了过充保护、过放保护、充电温度补偿、过 温保护、输出过压保护、输出重载保护、输出短路保护 等多重保护机制,也可以额外再加一颗 DW01 对系统进 行双重保护。 Ver1.0 TPOWER Semiconductor 4

TP4333 1A 同步移动电源方案

封装外形尺寸

SOP8L

注 1:最大极限值是指超出该工作范围芯片可能会损坏。推荐工作范围是指在该范围内芯片工作正常,但不完全保证满足 个别性能指标。 电气参数定义了器件在工作范围内并且在保证特定性能指标的测试条件下的直流和交流电气参数规范。 对 于未给定的上下限参数,该规范不予保证其精度,但其典型值合理反映了器件性能。

Ver1.0

TPOWER Semiconductor

2

TP4333 1A 同步移动电源方案

电气参数

无特殊说明, VDD=5V,Ta=25℃ 符号 参数 VDD 充电输入电压 VBAT IBAT ITRK VTRK VTRK_HYS TST TZERO VUV_BAT VWN_BAT VBAT_END ISD_BAT VSD VOUT ILEDx FLED1_C FLED2_WN RON_CHRG RON_NMOS RON_PMOS FOSC 预设充电电压 BAT 恒流充电电流 BAT 涓流充电电流 涓流充电阈值电压 涓流充电滞回电压 充电温度补偿阈值 充电零电流温度 BAT 欠压锁定阈值电 压 BAT 低压报警电压 BAT 放电终止电压 BAT 待机电流 VDD-VBAT 锁定阈值 升压输出电压 LEDx 驱动电流 LED1 充电闪烁频率 LED2 低电报警频率 充电 PMOS 导通电阻 放电 NMOS 导通电阻 放电 PMOS 导通电阻 升压电路工作频率 测试条件 针对 4.2V 规格 针对 4.35V 规格 恒流充电模式 涓流充电模式 VBAT 上升 最小值 4.3 4.15 4.30 典型值 5 4.2 4.35 1 100 2.9 100 120 135 3.2 3.0 2.85 50 180 80 5V 2 1 1 300 65 65 1 最大值 5.5 4.25 4.4 单位 V V V A mA V mV ℃ ℃ V V V uA mV mV V mA Hz Hz mΩ mΩ mΩ MHz

BYV38中文资料

Electrical Characteristics

Tj = 25_C Parameter Forward voltage Reverse current Reverse recovery time Diode Capacitance Test Conditions IF=1A Tj=150°C IF=0.5A, IR=1A, iR=0.25A VR=4V, f=1MHz Type Symbol VF IR IR trr CD Min Typ 1.0 Max 1.1 5 150 300 Unit V mA mA ns pF

Figure 6. Typ. Diode Capacitance vs. Reverse Voltage

www.vishay.de • FaxBack +1-408-970-5600 2 (4)

Document Number 86045 Rev. 2, 24-Jun-98

元器件交易网

l

RthJA=100K/W PCB: d=25mm

94 9552

l – Lead Length ( mm )

Figure 1. Max. Thermal Resistance vs. Lead Length

Figure 4. Max. Average Forward Current vs. Ambient Temperature

10

500 PR – Reverse Power Dissipation ( mW ) 450 400 350 300 250 200 150 100 50 0 25

15774

VR = VRRM IF – Forward Current ( A ) RthJA= 45K/W 100K/W 160K/W Tj = 175°C 1 Tj = 25°C 0.1 0.01

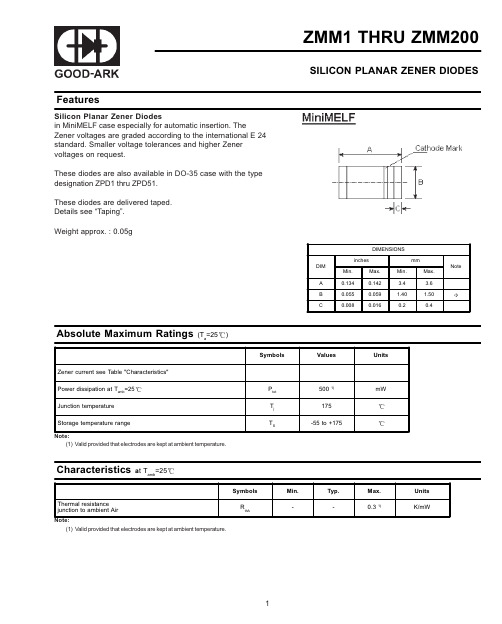

ZMM180资料

Note:(1) Valid provided that electrodes are kept at ambient temperature.FeaturesZMM1 THRU ZMM200SILICON PLANAR ZENER DIODESSilicon Planar Zener Diodesin MiniMELF case especially for automatic insertion. TheZener voltages are graded according to the international E 24standard. Smaller voltage tolerances and higher Zener voltages on request.These diodes are also available in DO-35 case with the type designation ZPD1 thru ZPD51.These diodes are delivered taped.Details see Taping .Weight approx. : 0.05gAbsolute Maximum Ratings (T a=25P tot500 1)mWJunction temperatureT j175Note:(1) Valid provided that electrodes are kept at ambient temperature.Characteristics a t Tamb=25C 0.0080.0160.20.4Notes:(1) T ested with pulses tp=20ms.(2) Valid provided that electrodes are kept at ambient temperature.(3) The ZMM1 is a silicon diode with operation in forward direction. Hence, the index of all parameters should be F instead of Z .TypeZener voltage range 1)D ynam ic resistanceR everse leakage currentTem p. coefficient of Zener VoltageV znom I Z T for V Z T 2)r zjT and r zjk at I Z KI R and I R 2) at V RTK V Z Vm A V m AAV %/K Z M M 13)0.7550.7 ... 0.8<8<501----0.26 ... -0.23Z M M 2.0 2.05 1.9 ... 2.1<85<6001<100<2001-0.09 ... -0.06Z M M 2.4 2.45 2.28 ... 2.56<85<6001<50<1001-0.09 ... -0.06Z M M 2.7 2.75 2.5 ... 2.9<85<6001<10<501-0.09 ... -0.06Z M M 3.0 3.05 2.8 ... 3.2<85<6001<4<401-0.08 ... -0.05Z M M 3.3 3.35 3.1 ... 3.5<85<6001<2<401-0.08 ... -0.05Z M M 3.6 3.65 3.4 ... 3.8<85<6001<2<401-0.08 ... -0.05Z M M 3.9 3.95 3.7 ... 4.1<85<6001<2<401-0.08 ... -0.05Z M M 4.3 4.35 4.0 ... 4.6<75<6001<1<201-0.06 ... -0.03Z M M 4.7 4.75 4.4 ... 5.0<60<6001<0.5<101-0.05 ... +0.02Z M M 5.1 5.15 4.8 ... 5.4<35<5501<0.1<21-0.02 ... +0.02Z M M 5.6 5.65 5.2 ... 6.0<25<4501<0.1<21-0.05 ... +0.05Z M M 6.2 6.25 5.8 ... 6.6<10<2001<0.1<220.03 ... 0.06Z M M 6.8 6.85 6.4 ... 7.2<8<1501<0.1<230.03 ... 0.07Z M M 7.57.557.0 ... 7.9<7<501<0.1<250.03 ... 0.07Z M M 8.28.257.7 ... 8.7<7<501<0.1<2 6.20.03 ... 0.08Z M M 9.19.158.5 ... 9.6<10<501<0.1<2 6.80.03 ... 0.09Z M M 101059.4 ... 10.6<15<701<0.1<27.50.03 ... 0.1Z M M 1111510.4 ... 11.6<20<701<0.1<28.20.03 ... 0.11Z M M 1212511.4 ... 12.7<20<901<0.1<29.10.03 ... 0.11Z M M 1313512.4 ... 14.1<26<1101<0.1<2100.03 ... 0.11Z M M 1515513.8 ... 15.6<30<1101<0.1<2110.03 ... 0.11Z M M 1616515.3 ... 17.1<40<1701<0.1<2120.03 ... 0.11Z M M 1818516.8 ... 19.1<50<1701<0.1<2130.03 ... 0.11Z M M 2020518.8 ... 21.2<55<2201<0.1<2150.03 ... 0.11Z M M 2222520.8 ... 23.3<55<2201<0.1<2160.04 ... 0.12Z M M 2424522.8 ... 25.6<80<2201<0.1<2180.04 ... 0.12Z M M 2727525.1 ... 28.9<80<2201<0.1<2200.04 ... 0.12Z M M 3030528 ... 32<80<2201<0.1<2220.04 ... 0.12Z M M 3333531 ... 35<80<2201<0.1<2240.04 ... 0.12Z M M 3636534 ... 38<80<2201<0.1<2270.04 ... 0.12Z M M 3939 2.537 ... 41<90<5000.5<0.1<5300.04 ... 0.12Z M M 4343 2.540 ... 46<90<5000.5<0.1<5330.04 ... 0.12Z M M 4747 2.544 ... 50<110<6000.5<0.1<5360.04 ... 0.12Z M M 5151 2.548 ... 54<125<7000.5<0.1<10390.04 ... 0.12Z M M 5656 2.552 ... 60<135<7000.5<0.1<10430.04 ... 0.12Z M M 6262 2.558 ... 66<150<10000.5<0.1<10470.04 ... 0.12Z M M 6868 2.564 ... 72<200<10000.5<0.1<10510.04 ... 0.12Z M M 7575 2.570 ... 79<250<10000.5<0.1<10560.04 ... 0.12Z M M 8282 2.577 ... 87<300<15000.25<0.1<10620.05 ... 0.12Z M M 9191185 ... 96<450<20000.1<0.1<10680.05 ... 0.12Z M M 100100194 ... 106<450<50000.1<0.1<10750.05 ... 0.12Z M M 1101101104 ... 116<600<50000.1<0.1<10820.05 ... 0.12Z M M 1201201114 ... 127<800<55000.1<0.1<10910.05 ... 0.12Z M M 1301301124 ... 141<950<60000.1<0.1<101000.05 ... 0.12Z M M 1501501138 ... 156<1250<65000.1<0.1<101100.05 ... 0.12Z M M 1601601153 ... 171<1400<70000.1<0.1<101200.05 ... 0.12Z M M 1801801168 ... 191<1700<85000.1<0.1<101300.05 ... 0.12Z M M 2002001188 (212)<2000<100000.1<0.1<101500.05 ... 0.12RATINGS AND CHARACTERISTIC CURVESRATINGS AND CHARACTERISTIC CURVESRATINGS AND CHARACTERISTIC CURVESRATINGS AND CHARACTERISTIC CURVESRATINGS AND CHARACTERISTIC CURVESRATINGS AND CHARACTERISTIC CURVES。

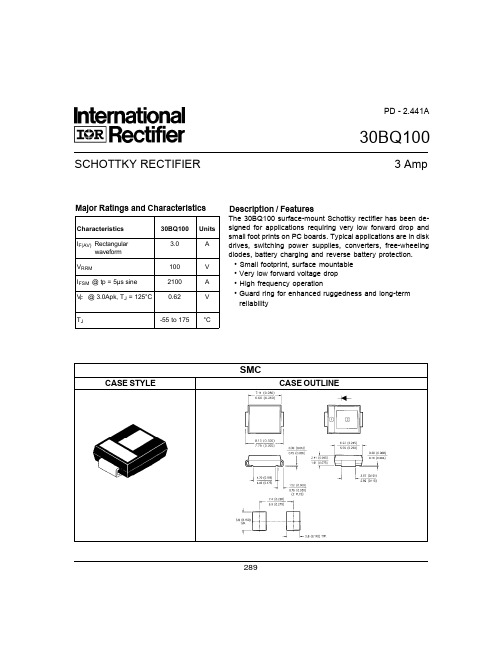

30BQ100资料

TJ T STG Max.Junction Temperature Range Max. Storage Temperature Range to Ambient RthJL wt Max. Thermal Resistance, Junction to Lead Approximate Weight Case Style Pulse Width < 300µs, Duty Cycle < 2%

Fig.7 Max. Non-Repetitive Surge Current

Fig. 8 Unclamped Inductive Test Circuit

Refer to the Appendix Section for the following: Appendix D: Tape and Reel Information — See page 339. 292

T J = 25°C, IAS = 2.8A, L = 10mH Current decaying linearly to zero in 1µsec Frequency limited by TJ max. VA = 1.5 X VR typical

Electrical Specifications

100 2100 0.62

V A V

-55 to 175

°C

SMC

CASE STYLE CASE OUTLINE

289

元器件交易网

30BQ100

Voltage Ratings

Part number

VR Max. DC Reverse Voltage (V) VRWM Max. Working Peak Reverse Voltage (V)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3/6

元器件交易网

TP30-xxx Series

TEST CIRCUIT 2 for IH parameter.

R D.U.T. VBAT = - 48 V Surge generator - VP

This is a GO-NOGO Test which allows to confirm the holding current (IH) level in a functional test circuit. TEST PROCEDURE : 1) Adjust the current level at the IH value by short circuiting the AK of the D.U.T. 2) Fire the D.U.T with a surge Current : Ipp = 10A , 10/1000 µs. 3) The D.U.T will come back off-state within 50 ms max.

Zth(j-a)(°CW) 1E+2

Fig. 6: Relative variation of VBO voltage versus junction temperature.

Vbo[Tj]/Vbo[Tj=25°C] 1.10 1.05

1E+1 1.00 1E+0 0.95 1E-1 1E-3

62 V 270 V

THERMAL RESISTANCES Symbol Rth (j-l) Rth (j-a) Junction to leads Junction to ambient on printed circuit with standard footprint dimension Parameter Value 60 100 Unit °C/W °C/W

50 50 40 40 35 35 30 30 30 30

IR measured at VR guarantee VBRmin ≥ VR Measured at 50 Hz (1 cycle) - See test circuit 1. See test circuit 2. VR = 1V, F = 1MHz. VR = 50V, F = 1MHz.

4/6

元器件交易网

TP30-xxx Series

Fig. 1: Non repetitive surge peak on-sate current versus overload duration (Tj initial = 25°C).

ITSM(A) 20

F = 50Hz

C A C

D

D

B

DIMENSIONS REF. Millimeters Min. A B C D 6.05 2.95 26 0.76 0.81 Typ. Max. Min. 6.20 3.00 Inches Typ. Max.

F = 1MHz

IT(A) 50

Tj = 25°C

0.5

20 10 5

0.2 2 0.1 1 10 VR(V) 100 300 1 0 1 2 3 4 5 6 VT(V) 7 8 9 10

Fig. 5: Variation of thermal impedance junction to ambient versus pulse duration.

Unit W A A A2s kV/µs °C °C °C

Critical rate of rise of off-state voltage VRM Storage temperature range Maximum junction temperature Maximumlead temperaturefor solderingduring 10s at 5mm forcase

TEST PROCEDURE : Pulse Test duration (tp = 20ms): - For Bidirectional devices = Switch K is closed - For Unidirectional devices = Switch K is open. VOUT Selection - Device with VBO < 250 Volt - VOUT = 250 VRMS, R1 = 140 Ω. - Device with VBO ≥ 250 Volt - VOUT = 480 VRMS, R2 = 240 Ω.

2

Parameter Power dissipation on infinite heatsink Peak pulse current Non repetitive surge peak on-state current I t value for fusing

2

Value Tamb = 50 °C 10/1000 µs 8/20 µs tp = 20 ms tp = 20 ms 3 30 60 15 1 5 - 55 to + 150 150 230

Fig. 2: Relative variation of holding current versus junction temperature.

IH[Tj] / IH[Tj=25 °C] 2.0 1.8 1.6 1.4 1.2 1.0 0.8 0.6 0.4 0.2 0.0 -40 -20 0 20

TP30-62 TP30-68 TP30-100 TP30-120 TP30-130 TP30-180 TP30-200 TP30-220 TP30-240 TP30-270

Note 1: Note 2: Note 3: Note 4: Note 5:

2 2 2 2 2 2 2 2 2 2

56 61 90 108 117 162 180 198 216 243

2/6

元器件交易网

TP30-xxx Series

Type IRM @ VRM max

µA V

IR @ V R max note 1

µA V

VBO @ IBO max note 2

V mA

IH min note 3

mA

C typ note 4

pF

typ note 5 20 20 16 16 14 14 12 12 12 12

50 50 50 50 50 50 50 50 50 50

62 68 100 120 130 180 200 220 240 270

82 90 133 160 173 240 267 293 320 360

800 800 800 800 800 800 800 800 800 800

150 150 150 150 150 150 150 150 150 150

15 10 0 t(s)

1E+1

1E+2

1E+3

40 Tj(°C)

60

80

100

120

Fig. 3: Relative variation of junction capacitance versus reverse applied voltage (typical values).

Note: For VRM upper than 56V, the curve is extrapolated (dotted line)

Fig. 4: On-state voltage versus on-state current (typical values).

C[VR]/C[VR=1V] 1.0

元器件交易网

®

TP30-xxx Series

TRISILTM

FEATURES BIDIRECTIONAL CROWBAR PROTECTION. VOLTAGE RANGE: FROM 62 V TO 270 V. HOLDING CURRENT : IH = 150 mA min. REPETITIVE PEAK PULSE CURRENT : IPP = 30 A, 10/1000 µs. JEDEC REGISTERED PACKAGE OUTLINE DESCRIPTION The TP30-xxx series has been designed to protect telecommunication equipment against lightning surges and overvoltages induced by AC power lines. F126 (JEDEC DO-204AC) SCHEMATIC DIAGRAM

Current Waveform (µs) 5/310 5/310 5/310 1/20 5/310 8/20 10/160 10/560 5/320 2/10 10/1000 2/10 0.8/310

Admissible Ipp (A) 25 38 40 50 25 50 65 50 25 125 30 125 25

Necessary Resistor (Ω) 10 15.5 8.0 15.0 23.3 15.0 1/6

元器件交易网

TP30-xxx Series

ABSOLUTE MAXIMUM RATINGS (Tamb = 25°C) Symbol P IPP ITSM I t dV/dt Tstg Tj TL

ELECTRICAL CHARACTERISTICS (Tamb = 25°C) Symbol VRM IRM VR VBR VBO IH IBO IPP C Parameter Stand-off voltage Leakage current at stand-off voltage Continuous Reverse voltage Breakdown voltage Breakover voltage Holding current Breakover current Peak pulse current Capacitance