W3EG7235S-JD3中文资料

三星3400系列洗衣机和干衣机产品指南说明书

3400 Series LaundryWA45T3400AV – WasherDVE45T3400V – Electric Dryer DVG45T3400V – Gas DryerProduct GuideTable of ContentsProduct Overview Product Overview 4Carousel Image Order 5Product Messaging Features and Benefits 7Product Specs Related Products 11Spec Sheet12Energy Guide and User Manual 13Feature Icons15WA45T3400AV – Top Load WasherProduct OverviewProduct Overview 17Carousel Image Order 18Product MessagingFeatures and Benefits 20Product SpecsRelated Products 24Spec Sheet 25User Manual 26Feature Icons28DVE45T3400V – Top Load Electric Dryer DVG45T3400V – Top Load Gas DryerProduct OverviewWA45T3400AV – 4.5 cu. ft. Capacity Top Load Washer with Active WaterJetProduct OverviewProduct Long Description (275 Characters)Samsung’s Large 4.5 cu. ft. Capacity Top Load washer fits more in every load and cuts down on laundry time. It is equipped with Active WaterJet that lets you pretreat heavily soiled and stained clothes and Vibration Reduction Technology+ that reduces noise for quiet washing.Product Short Description (136 Characters)Samsung’s Top Load washer is equipped with Active WaterJet to help pretreat clothes and Vibration Reduction Technology+ to reduce noise.Product Title4.5 cu. ft. Capacity Top Load Washer with Active WaterJetAvailable ColorBrushed BlackModel Number: WA45T3400AV UPC: 887276433431Carousel Image Order213636054789101112Easy Ads links :https:///p/z0c3461/external?q=tags.strict%3A%22pr659326033%22 :https:///p/z0c3461/external?q=tags.strict%3A%22pr659326034%22360 Spin: https:///s/69853n7kkbq88v7swhm5nhqProduct MessagingWA45T3400AV – 4.5 cu. ft. Capacity Top Load Washerwith Active WaterJet3400 Washer and Dryer Product Guide10 ProductSpecsWA45T3400AV – 4.5 cu. ft. Capacity Top Load Washerwith Active WaterJetRelated ProductsSpec SheetEasy Ads link https:///p/z0c3461/external?o=AND&q=WA45T3400AV%20Spec%20Sheet Features• Large 4.5 cu. ft. Capacity • Active WaterJet • Vibration Reduction Technology+• Self Clean • Smart Care*• Diamond Drum Interior • Soft-Close Lid • 700 RPM Maximum Spin Speed • A C Motor • 10 Preset Washing Cycles • 6 Additional Washing Options • 5 Temperature Levels • L ED Display: Ice Blue Convenience • Child Lock • D ispenser Trays: Main Wash, Softener, Bleach Large 4.5 cu. ft. Capacity Active WaterJet * R equires Samsung Smart Washer/Dryer App. The Samsung Smart Washer/Dryer App supports Android OS 2.3.6 or later and iOS 3 or later for iPhone models. Samsung Smart Washer/Dryer App available in App Store and Play Store.Rating IMEF = 1.57IWF = 6.5240 kWh/yr Electrical Requirements 120V / 60Hz 15 Amps Available Color Brushed Black Washer Spec Sheet - frontEnergy Guide and User ManualEasy Ads linkWasherUser manualWA45T3400** Energy GuideFeature IconsWA45T3400AV – 4.5 cu. ft. Capacity Top Load Washer with Active WaterJetFeature IconsSmart Care Large 4.5 cu. ft.CapacityVibration ReductionTechnology+Self CleanActive WaterJet Extra HighWater LevelProduct OverviewDVE45T3400V & DVG45T3400V - Large 7.4 cu. ft. Capacity Top Load Dryer with Sensor DryProduct OverviewProduct Long Description (248 Characters)Samsung’s Large 7.4 cu. ft. Capacity Top Load dryer fits more in every load, cutting down on laundry time. It features Sensor Dry that helps prevent overdrying for optimal fabric care, and has 10 Preset Drying Cycles to best suit your drying needs.Product Short Description (126 Characters)Samsung’s 7.4 cu. ft. capacity dryers feature Sensor Dry and 10 Preset Drying Cycles, so you can do fewer loads in less time.Product TitleLarge 7.4 cu. ft. Capacity Top Load Dryer with Sensor DryAvailable ColorBrushed Black Model Number: DVE45T3400V UPC: 887276430614Model Number: DVG45T3400V UPC: 887276430621Carousel Image Order2136360547891011Easy Ads links :https:///p/z0c3461/external?q=tags.strict%3A%22pr659326181%22 :https:///p/z0c3461/external?q=tags.strict%3A%22pr659326184%22 360 Spin: DVE45T3400V https:///s/5wr3sps3pw4gzk9r2g7qc 360 Spin: DVG45T3400V https:///s/vg9mqtpkhf4bk6jr4r2tww6gProduct MessagingDVE45T3400V & DVG45T3400V - Large 7.4 cu. ft. Capacity Top Load Dryer with Sensor Dry| 3400 Dryer Easy Ads link: https:///p/z0c3461/external?q=tags.strict%3A%22pr659340016%223400 Washer and Dryer Product Guide20Product SpecsDVE45T3400V & DVG45T3400V - Large 7.4 cu. ft. Capacity Top Load Dryer with Sensor DryRelated ProductsFeatures• Sensor Dry• Large 7.4 cu. ft. Capacity • 10 Preset Drying Cycles • Reversible Dryer Door • Smart Care*• 7 Additional Drying Options • 4 Temperature Levels • Wrinkle Prevent • 4-Way Venting• Powder Coat Interior • LED Display: Ice BlueConvenience• Child Lock• Filter Check IndicatorSensor Dry Large 7.4 cu. ft. CapacityRating644 kWh/yrElectrical Requirements120V/ 240V / 60Hz 30 AmpsAvailable ColorBrushed Black* R equires Samsung Smart Washer/Dryer App. The Samsung Smart Washer/Dryer App supports Android OS 2.3.6 or later and iOS 3 or later for iPhone models. Samsung Smart Washer/Dryer App available in App Store and Play Store.Features• Sensor Dry• Large 7.4 cu. ft. Capacity • 10 Preset Drying Cycles • Reversible Dryer Door • Smart Care*• 7 Additional Drying Options • 4 Temperature Levels • Wrinkle Prevent • 3-Way Venting• Powder Coat Interior • LED Display: Ice BlueConvenience• Child Lock• Filter Check IndicatorElectrical Requirements120V / 60Hz 15 AmpsAvailable ColorBrushed Black* R equires Samsung Smart Washer/Dryer App. The Samsung Smart Washer/Dryer App supports Android OS 2.3.6 or later and iOS 3 or later for iPhone models. Samsung Smart Washer/Dryer App available in App Store and Play Store.Sensor Dry Large 7.4 cu. ft. CapacitySpec SheetsGas Dryer Spec Sheet - front Gas Dryer Spec Sheet - backElectric Dryer Spec Sheet - front Electric Dryer Spec Sheet - backEasy Ads linkhttps:///p/z0c3461/external?o=AND&q=DV*45T3400V%20Spec%20SheetUser Manual Easy Ads linkDryerUser manualDVE(G)45T3400*Feature IconsDVE45T3400V & DVG45T3400V - Large 7.4 cu. ft. Capacity Top Load Dryer with Sensor DryFeature IconsSmart CareLarge 7.4 cu. ft.Capacity10 Preset Drying CyclesSensor Dry Lint FilterIndicatorReversible Dryer Door。

W3EG7234S265JD3资料

White Electronic DesignsW3EG7234S-D3-JD3-AJD3PRELIMINARY*256MB - 32Mx72 DDR SDRAM REGISTERED, w/PLLDESCRIPTIONThe W3EG7234S is a 32Mx72 Double Data Rate SDRAM memory module based on 128Mb DDRSDRAM component. The module consists of eighteen 32Mx4 DDR SDRAMs in 66 pin TSOP package mounted on a 184 Pin FR4 substrate.Synchronous design allows precise cycle control with the use of system clock. Data I/O transactions are possible on both edges and Burst Lenths allow thesame device to be useful for a variety of high bandwidth, high performance memory system applications.* T his product is under development, is not qualifi ed or characterized and is subject to change without notice.FEATURESDouble-data-rate architecture Clock speeds: 100MHz and 133MHz Bi-directional data strobes (DQS) Differential clock inputs (CK & CK#) Programmable Read Latency 2,2,5 (clock) Programmable Burst Length (2,4,8)Programmable Burst type (sequential & interleave) Edge aligned data output, center aligned data input Auto and self refresh Serial presence detect Power Supply: 2.5V ± 0.20VJEDEC standard 184 pin DIMM package•Package height options: JD3: 30.48mm (1.20") AJD3: 28.70mm (1.13")OPERATING FREQUENCIESDDR266 @CL=2DDR266 @CL=2.5DDR200 @CL=2Clock Speed 133MHz 133MHz 100MHz CL-t RCD -t RP2-2-22.5-3-32-2-2White Electronic DesignsW3EG7234S-D3-JD3-AJD3PRELIMINARYPIN CONFIGURATIONSPIN NAMESA0 – A12Address input (Multiplexed)BA0-BA1Bank Select Address DQ0-DQ63 Data Input/Output CB0-CB7Check bitsDQS0-DQS17Data Strobe Input/Output CK0Clock Input CK0#Clock InputCKE0Clock Enable Input CS0#Chip select Input RAS#Row Address Strobe CAS#Column Address Strobe WE#Write Enable V CC Power SupplyV CCQ Power Supply for DQS V SS GroundV REF Power Supply for Reference V CCSPD Serial EEPROM Power Supply SDA Serial data I/O SCL Serial clockSA0-SA2Address in EEPROM V CCID V CC Identifi cation Flag NCNo Connect RESET#Reset EnablePIN SYMBOL PIN SYMBOL PIN SYMBOL PIN SYMBOL 1V REF 47DQS893V SS 139V SS 2DQ048A094DQ4140DQS173V SS 49CB295DQ5141A104DQ150V SS 96V CCQ 142CB65DQS051CB397DQS9143V CCQ 6DQ252BA198DQ6144CB77V CC 53DQ3299DQ7145V SS 8DQ354V CCQ 100V SS 146DQ369NC 55DQ33101NC 147DQ3710RESET#56DQS4102NC 148V CC 11V SS 57DQ34103NC 149DQS1312DQ858V SS 104V CCQ 150DQ3813DQ959BA0105DQ12151DQ3914DQS160DQ35106DQ13152V SS 15V CCQ 61DQ40107DQS10153DQ4416*CK162V CCQ 108V CC 154RAS#17*CK1#63WE#109DQ14155DQ4518V SS 64DQ41110DQ15156V CCQ 19DQ1065CAS#111*CKE1157CS0#20DQ1166V SS 112V CCQ 158*CS1#21CKE067DQS5113*BA2159DQS1422V CCQ 68DQ42114DQ20160V SS 23DQ1669DQ43115A12161DQ4624DQ1770V CC 116V SS 162DQ4725DQS271*CK2#117DQ21163*CS3#26V SS 72DQ48118A11164V CCQ 27A973DQ49119DQS11165DQ5228DQ1874V SS 120V CC 166DQ5329A775*CK2#121DQ22167A13*30V CCQ 76*CK2122A8168V CC 31DQ1977V CCQ 123DQ23169DQS1532A578DQS6124V SS 170DQ5433DQ2479DQ50125A6171DQ5534V SS 80DQ51126DQ28172V CCQ 35DQ2581V SS 127DQ29173NC 36DQS382V CCID 128V CCQ 174DQ6037A483DQ56129DQS12175DQ6138V CC 84DQ57130A3176V SS 39DQ2685V CC 131DQ30177DQS1640DQ2786DQS7132V SS 178DQ6241A287DQ58133DQ31179DQ6342V SS 88DQ59134CB4180V CCQ 43A189V SS 135CB5181SA044CB090NC 136V CCQ 182SA145CB191SDA 137CK0183SA246V CC92SCL138CK0#184V CCSPD* Not UsedWhite Electronic Designs W3EG7234S-D3-JD3-AJD3PRELIMINARY FUNCTIONAL BLOCK DIAGRAMWhite Electronic Designs W3EG7234S-D3-JD3-AJD3PRELIMINARYABSOLUTE MAXIMUM RATINGSParameter Symbol Value UnitsVoltage on any pin relative to V SS V IN, V OUT-0.5 to 3.6VVoltage on V CC supply relative to V SS V CC, V CCQ-1.0 to 3.6VStorage Temperature T STG-55 to +150°CPower Dissipation P D27WShort Circuit Current I OS50mANote: Permanent device damage may occur if ‘ABSOLUTE MAXIMUM RATINGS’ are exceeded.Functional operation should be restricted to recommended operating condition.Exposure to higher than recommended voltage for extended periods of time could affect device reliabilityDC CHARACTERISTICS0°C ≤ T A≤ 70°C, V CC = 2.5V ± 0.2VParameter Symbol Min Max Unit Supply Voltage V CC 2.3 2.7V Supply Voltage V CCQ 2.3 2.7V Reference Voltage V REF 1.15 1.35V Termination Voltage V TT 1.15 1.35VInput High Voltage V IH V REF + 0.15V CCQ + 0.3VInput Low Voltage V IL-0.3V REF -0.15V Output High Voltage V OH V TT + 0.76—V Output Low Voltage V OL—V TT-0.76VCAPACITANCET A = 25°C. f = 1MHz, V CC = 2.5VParameter Symbol Max UnitInput Capacitance (A0-A12)C IN1 6.25pFInput Capacitance (RAS#,CAS#,WE#)C IN2 6.25pFInput Capacitance (CKE0)C IN3 6.25pFInput Capacitance (CK0#,CK0)C IN4 5.5pFInput Capacitance (CS0#)C IN5 6.25pFInput Capacitance (DQS0-DQS17)C IN613pFInput Capacitance (BA0-BA1)C IN7 6.25pFData input/output capacitance (DQ0-DQ63)(DQS)C OUT13pFData input/output capacitance (CB0-CB7)C OUT13pFWhite Electronic Designs W3EG7234S-D3-JD3-AJD3PRELIMINARYI DD SPECIFICATIONS AND TEST CONDITIONS0°C ≤ T A≤ 70°C, V CCQ = 2.5V ± 0.2V, V CC = 2.5V ± 0.2VIncludes PLL and Register PowerParameter Symbol Rank 1ConditionsDDR266@CL=2MaxDDR266@CL=2.5MaxDDR200@CL=2Max UnitsOperating Current I DD0One device bank; Active - Precharge; t RC= t RC (MIN); t CK = t CK (MIN); DQ,DM andDQS inputs changing once per clock cycle;Address and control inputs changing onceevery two cycles.252023852385mAOperating Current I DD1One device bank; Active-Read-PrechargeBurst = 2; t RC = t RC (MIN); t CK = t CK (MIN);l OUT = 0mA; Address and control inputschanging once per clock cycle.270025202520mAPrecharge Power-Down Standby Current I DD2P All device banks idle; Power-down mode;t CK = t CK (MIN); CKE = (low)545454mAIdle Standby Current I DD2F CS# = High; All device banks idle;t CK = t CK (MIN); CKE = High; Addressand other control inputs changing onceper clock cycle. V IN = V REF for DQ, DQSand DM.112010301030mAActive Power-Down Standby Current I DD3P One device bank active; Power-Downmode; t CK (MIN); CKE = (low)450360360mAActive Standby Current I DD3N CS# = High; CKE = High; One devicebank; Active-Precharge;t RC = t RAS (MAX);t CK = t CK (MIN); DQ, DM and DQS inputschanging twice per clock cycle; Addressand other control inputs changing once perclock cycle.121011201120mAOperating Current I DD4R Burst = 2; Reads; Continuous burst; Onedevice bank active; Address and controlinputs changing once per clock cycle; t CK =t CK (MIN); l OUT = 0mA.274526102610mAOperating Current I DD4W Burst = 2; Writes; Continuous burst; Onedevice bank active; Address and controlinputs changing once per clock cycle;t CK = t CK (MIN); DQ,DM and DQS inputschanging once per clock cycle.270025652565mAAuto Refresh Current I DD5t RC = t RC (MIN)377036803645mA Self Refresh Current I DD6CKE ≤ 0.2V329311346mA Operating Current I DD7A Four bank interleaving Reads (BL=4)with auto precharge with t RC=t RC (MIN);t CK=t CK(MIN); Address and control inputschange only during Active Read or Writecommands.486047704770mAWhite Electronic Designs W3EG7234S-D3-JD3-AJD3PRELIMINARYI DD SPECIFICATIONS AND TEST CONDITIONS0°C ≤ T A≤ 70°C, V CCQ = 2.5V ± 0.2V, V CC = 2.5V ± 0.2VIncludes DDR SDRAM components onlyParameter Symbol Rank 1ConditionsDDR266@CL=2MaxDDR266@CL=2.5MaxDDR200@CL=2Max UnitsOperating Current I DD0One device bank; Active - Precharge; t RC= t RC (MIN); t CK = t CK (MIN); DQ,DM andDQS inputs changing once per clock cycle;Address and control inputs changing onceevery two cycles.193518001800mAOperating Current I DD1One device bank; Active-Read-PrechargeBurst = 2; t RC = t RC (MIN); t CK = t CK (MIN);l OUT = 0mA; Address and control inputschanging once per clock cycle.211519351935mAPrecharge Power-Down Standby Current I DD2P All device banks idle; Power-down mode;t CK = t CK (MIN); CKE = (low)545454mAIdle Standby Current I DD2F CS# = High; All device banks idle;t CK = t CK (MIN); CKE = High; Addressand other control inputs changing onceper clock cycle. V IN = V REF for DQ, DQSand DM.810720720mAActive Power-Down Standby Current I DD3P One device bank active; Power-Downmode; t CK (MIN); CKE = (low)450360360mAActive Standby Current I DD3N CS# = High; CKE = High; One devicebank; Active-Precharge;t RC = t RAS (MAX);t CK = t CK (MIN); DQ, DM and DQS inputschanging twice per clock cycle; Addressand other control inputs changing once perclock cycle.900810810mAOperating Current I DD4R Burst = 2; Reads; Continuous burst; Onedevice bank active; Address and controlinputs changing once per clock cycle; t CK =t CK (MIN); l OUT = 0mA.216020252025mAOperating Current I DD4W Burst = 2; Writes; Continuous burst; Onedevice bank active; Address and controlinputs changing once per clock cycle;t CK = t CK (MIN); DQ,DM and DQS inputschanging once per clock cycle.211519801980mAAuto Refresh Current I DD5t RC = t RC (MIN)315030603060mA Self Refresh Current I DD6CKE ≤ 0.2V543636mA Operating Current I DD7A Four bank interleaving Reads (BL=4)with auto precharge with t RC=t RC (MIN);t CK=t CK(MIN); Address and control inputschange only during Active Read or Writecommands.427541854185mAWhite Electronic Designs W3EG7234S-D3-JD3-AJD3PRELIMINARYI DD1 : OPERATING CURRENT: ONE BANK1. Typical Case: V CC =2.5V, T = 25°C2. Worst Case: V CC = 2.7V, T = 10°C3. Only one bank is accessed with t RC (min), Burst Mode, Address and Control inputs on NOP edge are changing once per clock cycle. l OUT = 0mA4. Timing patterns• DDR200 (100MHz, CL = 2) : t CK = 10ns, CL2, BL =4, t RCD = 2*t CK, t RAg = 5*t CKRead: A0 N R0 N N P0 N A0 N - repeat the sametiming with random address changing; 50% of data changing at every burst• DDR266 (133MHz, CL = 2.5) : t CK = 7.5ns, CL =2.5, BL = 4, t RCD = 3*t CK, t RC = 9*t CK, t RAg = 5*t CKRead: A0 N N R0 N P0 N N N A0 N - repeat thesame timing with random address changing; 50% of data changing at every burst• DDR266 (133MHz, CL = 2) : t CK = 7.5ns, CL = 2, BL = 4, t RCD = 3*t CK, t RC = 9*t CK, t RAg = 5*t CKRead: A0 N N R0 N P0 N N N A0 N - repeat thesame timing with random address changing; 50% of data changing at every burst I DD7A: OPERATING CURRENT: FOUR BANKS1. Typical Case: V CC =2.5V, T = 25°C2. Worst Case: V CC = 2.7V, T = 10°C3. Four banks are being interleaved with t RC (min), Burst Mode, Address and Control inputs on NOP edge are not changing.lout = 0mA4. Timing patterns• DDR200 (100MHz, CL = 2) : t CK = 10ns, CL2,BL = 4, t RRD = 2*t CK, t RCD = 3*t CK, Read withautoprechargeRead: A0 N A1 R0 A2 R1 A3 R2 A0 R3 A1 R0- repeat the same timing with random addresschanging; 100% of data changing at every burst • DDR266 (133MHz, CL = 2.5) : t CK = 7.5ns, CL =2.5, BL = 4, t RRD = 3*t CK, t RCD = 3*t CK Read withautoprechargeRead: A0 N A1 R0 A2 R1 A3 R2 N R3 A0 N A1R0 - repeat the same timing with random addresschanging; 100% of data changing at every burst • DDR266 (133MHz, CL = 2): t CK = 7.5ns, CL2 = 2,BL = 4, t RRD = 2*t CK, t RCD = 3*t CKRead: A0 N A1 R0 A2 R1 A3 R2 N R3 A0 N A1R0 - repeat the same timing with random addresschanging; 100% of data changing at every burstDETAILED TEST CONDITIONS FOR DDR SDRAM I DD1 & I DD7A Legend: A = Activate, R = Read, W = Write, P = Precharge, N = NOPA (0-3) = Activate Bank 0-3R (0-3) = Read Bank 0-3White Electronic Designs W3EG7234S-D3-JD3-AJD3PRELIMINARYDDR SDRAM COMPONENT ELECTRICAL CHARACTERISTICS ANDRECOMMENDED AC OPERATING CONDITIONS0°C ≤ T A ≤ +70°C; V CC = +2.5V ±0.2V, V CCQ = +2.5V ±0.2VAC Characteristics262/265202Parameter Symbol Min Max Min Max Units Notes Access window of DQs from CK, CK#t AC-0.75+0.75-0.8+0.8nsCK high-level width t CH0.450.550.450.55t CK16CK low-level width t CL0.450.550.450.55t CK16 Clock cycle time CL=2.5t CK (2.5)7.513813ns22CL=2t CK (2)7.5/10131013ns22DQ and DM input hold time relative to DQS t DH0.50.6ns14,17 DQ and DM input setup time relative to DQS t DS0.50.6ns14,17 DQ and DM input pulse width (for each input)t DIPW 1.752ns17 Access window of DQS from CK, CK#t DQSCK-0.75+0.75-0.8+0.8nsDQS input high pulse width t DQSH0.350.35t CKDQS input low pulse width t DQSL0.350.35t CKDQS-DQ skew, DQS to last DQ valid, per group, per access t DQSQ0.50.6ns13,14 Write command to fi rst DQS latching transition t DQSS0.75 1.250.75 1.25t CKDQS falling edge to CK rising - setup time t DSS0.20.2t CKDQS falling edge from CK rising - hold time t DSH0.20.2t CKHalf clock period t HP t CH, t CL t CH, t CL ns18 Data-out high-impedance window from CK, CK#t HZ+0.75+0.8ns8,19 Data-out low-impedance window from CK, CK#t LZ-0.75-0.8ns8,20 Address and control input hold time (fast slew rate)t IHf0.90 1.1ns6 Address and control input set-up time (fast slew rate)t ISf0.90 1.1ns6 Address and control input hold time (slow slew rate)t IHs1 1.1ns6 Address and control input setup time (slow slew rate)t ISs1 1.1ns6 Address and control input pulse width (for each input)t IPW 2.2 2.2nsLOAD MODE REGISTER command cycle time t MRD1516nsDQ-DQS hold, DQS to fi rst DQ to go non-valid, per access t QH t HP-t QHS t HP-t QHS ns13,14 Data hold skew factor t QHS0.751nsACTIVE to PRECHARGE command t RAS40120,00040120,000ns15 ACTIVE to READ with Auto precharge command t RAP1520nsACTIVE to ACTIVE/AUTO REFRESH command period t RC6070nsAUTO REFRESH command period t RFC7580ns21White Electronic Designs W3EG7234S-D3-JD3-AJD3PRELIMINARYDDR SDRAM COMPONENT ELECTRICAL CHARACTERISTICS ANDRECOMMENDED AC OPERATING CONDITIONS (continued)0°C ≤ T A ≤ +70°C; V CC = +2.5V ±0.2V, V CCQ = +2.5V ±0.2VAC Characteristics262/265202Parameter Symbol Min Max Min Max Units Notes ACTIVE to READ or WRITE delay t RCD1520nsPRECHARGE command period t RP1520nsDQS read preamble t RPRE0.9 1.10.9 1.1t CK19 DQS read postamble t RPST0.40.60.40.6t CKACTIVE bank a to ACTIVE bank b command t RRD1215nsDQS write preamble t WPRE0.250.25t CKDQS write preamble setup time t WPRES00ns10,11 DQS write postamble t WPST0.40.60.40.6t CK9 Write recovery time t WR1515nsInternal WRITE to READ command delay t WTR11t CKData valid output window NA t QH-t DQSQ t QH-t DQSQ ns13 REFRESH to REFRESH command interval t REFC140.6140.6μs12 Average periodic refresh interval t REFI15.615.6μs12 Terminating voltage delay to V CC t VTD00nsExit SELF REFRESH to non-READ command t XSNR7580nsExit SELF REFRESH to READ command t XSRD200200t CKWhite Electronic DesignsW3EG7234S-D3-JD3-AJD3PRELIMINARY11. It is recommended that DQS be valid (HIGH or LOW) on or beforethe WRITE command. The case shown (DQS going from High-Z to logic LOW) applies when no WRITEs were previously in progress on the bus. If a previous WRITE was in progress, DQS could be high during this time, depending on t DQSS .12. The refresh period is 64ms. This equates to an average refreshrate of 15.625µs. However, an AUTO REFRESH command must be asserted at least once every 140.6µs; burst refreshing orposting by the DRAM controller greater than eight refresh cycles is not allowed.13. The valid data window is derived by achieving other specifi cations- t HP (t CK/2), t DQSQ , and t QH (t QH = t HP - t QHS ). The data valid window derates directly proportional with the clock duty cycle and a practical data valid window can be derived. The clock is allowed a maximum duty cycled variation of 45/55. Functionality is uncertain when operating beyond a 45/55 ratio. The data valid window derating curves are provided below for duty cycles ranging between 50/50 and 45/55.14. Referenced to each output group: x4 = DQS with DQ0-DQ3.15. READs and WRITEs with auto precharge are not allowed to beissued until t RAS (MIN) can be satisfi ed prior to the internal precharge command being issued.16. JEDEC specifi es CK and CK# input slew rate must be > 1V/ns(2V/ns differentially).17. DQ and DM input slew rates must not deviate from DQS by morethan 10%. If the DQ/DM/DQS slew rate is less than 0.5V/ns, timing must be derated: 50ps must be added to t DS and t DH for each 100mV/ns reduction in slew rate. If slew rates exceed 4V/ns, functionality is uncertain.18. t HP min is the lesser of t CL min and t CH min actually applied to thedevice CK and CK# inputs, collectively during bank active.19. t HZ (MAX) will prevail over the t DQSCK (MAX) + t RPST (MAX)condition. t LZ (MIN) will prevail over t DQSCK (MIN) + PRE (MAX) condition.20. For slew rates greater than 1V/ns the (LZ) transition will start about310ps earlier.21. CKE must be active (High) during the entire time a refreshcommand is executed. That is, from the time the AUTO REFRESH command is registered, CKE must be active at each rising clock edge, until t RFC has been satisfi ed.22. Whenever the operating frequency is altered, not including jitter, the DLL is required to be reset. This is followed by 200 clock cycles (before READ commands).Notes1.All voltages referenced to V SS2. Tests for AC timing, I DD , and electrical AC and DC characteristicsmay be conducted at normal reference / supply voltage levels, but the related specifi cations and device operations are guaranteed for the full voltage range specifi ed.3.Outputs are measured with equivalent load:Output (V OUT )4.AC timing and I DD tests may use a V IL -to-V IH swing of up to 1.5V in the test environment, but input timing is still referenced to V REF (or to the crossing point for CK/CK#), and parameter specifi cations are guaranteed for the specifi ed AC input levels under normal use conditions. The minimum slew rate for the input signals used to test the device is 1V/ns in the range between V IL (AC) and V IH (AC).5.The AC and DC input level specifi cations are defi ned in the SSTL_2 standard (i.e., the receiver will effectively switch as a result of the signal crossing the AC input level, and will remain in that state as long as the signal does not ring back above [below] the DC input LOW [high] level).6.For slew rates less than 1V/ns and greater than or equal to 0.5V/ns. If the slew rate is less than 0.5V/ns, timing must be derated: t IS has an additional 50ps per each 100mV/ns reduction in slew rate from the 500mV/ns. t IH has 0ps added, that is, it remains constant. If the slew rate exceeds 4.5V/ns, functionality is uncertain. For 403 and 335, slew rates must be greater than or equal to 0.5V/ns.7.Inputs are not recognized as valid until V REF stabilizes. Exception: during the period before V REF stabilizes, CKE ≤ 0.3 x V CCQ is recognized as LOW.8. t HZ and t LZ transitions occur in the same access time windows asvalid data transitions. These parameters are not referenced to a specifi c voltage level, but specify when the device output is no longer driving (HZ) and begins driving (LZ).9.The intent of the “Don’t Care” state after completion of thepostamble is the DQS-driven signal should either be HIGH, LOW, or high-Z, and that any signal transition within the input switching region must follow valid input requirements. That is, if DQS transitions HIGH (above V IHDC (MIN) then it must not transition LOW (below V IHDC ) prior to t DQSH (MIN).10. This is not a device limit. The device will operate with a negativevalue, but system performance could be degraded due to bus turnaround.White Electronic Designs W3EG7234S-D3-JD3-AJD3PRELIMINARYORDERING INFORMATION FOR JD3Part Number Speed CAS Latency t RCD t RP Height*W3EG7234S262JD3133MHz/266Mb/s22230.48 (1.20")W3EG7234S265JD3133MHz/266Mb/s 2.53330.48 (1.20")W3EG7234S202JD3100MHz/200Mb/s22230.48 (1.20")PACKAGE DIMENSIONS FOR JD3White Electronic DesignsW3EG7234S-D3-JD3-AJD3PRELIMINARYORDERING INFORMATION FOR AJD3Part Number Speed CAS Latencyt RCD t RP Height*W3EG7234S262AJD3133MHz/266Mb/s 22228.70 (1.13")W3EG7234S265AJD3133MHz/266Mb/s 2.53328.70 (1.13")W3EG7234S202AJD3100MHz/200Mb/s22228.70 (1.13")PACKAGE DIMENSIONS FOR AJD3* ALL DIMENSIONS ARE IN MILLIMETERS AND (INCHES).White Electronic DesignsW3EG7234S-D3-JD3-AJD3PRELIMINARYORDERING INFORMATION FOR D3Part Number Speed CAS Latencyt RCD t RP Height*W3EG7234S262D3133MHz/266Mb/s 22228.58 (1.125")W3EG7234S265D3133MHz/266Mb/s 2.53328.58 (1.125")W3EG7234S202D3100MHz/200Mb/s22228.58 (1.125")PACKAGE DIMENSIONS FOR D3* ALL DIMENSIONS ARE IN MILLIMETERS AND (INCHES).White Electronic Designs W3EG7234S-D3-JD3-AJD3PRELIMINARY Document Title256MB - 32Mx72 DDR SDRAM REGISTERED, w/PLLRevision HistoryRev #History Release Date StatusRev A Created5-21-02Advanced7-04Preliminary Rev 00.1 Updated CAP and I DD specs0.2 Removed "E D" from Part Marking0.3 Added JD3 and AJD3 Package Height Options0.4 Moved datasheet from Advanced to Preliminary0.5 Added new Document Title PageRev 1 1.1 Added AC specs11-04Preliminary Rev 2 2.1 Updated I DD specs12-04Preliminary。

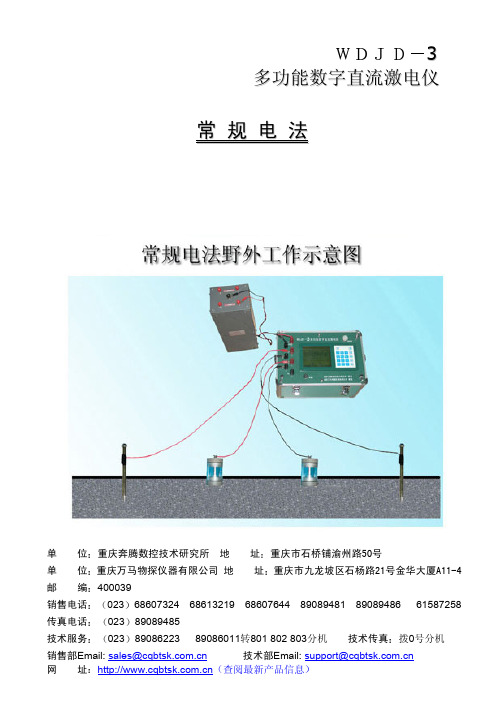

WDJD-3多功能数字直流激电仪说明书

WDJD-3多功能数字直流激电仪原理框

程控放大

电流

四

仪器结构 仪器的全部操作均在面板上完成 图4-1为面板示意图 显示器 160 128点阵图形大屏幕液晶 16个键的键盘 可进行各种操作和数据输入 键 用于输入数字和菜单选择 其中 键在显示曲线时 向 右或左移动曲线光标 键可将显示的曲线上 下移动 此外 键还用于开机时调节显示对比度 键 用于输入小数点 显示曲线时用于压缩曲线幅度 键 用于输入数字符号 显示曲线时用于放大曲线幅度 清除键 输入数据时 可用来清除已输入的数字 此外 还具有清除已 存贮数据的功能 功能/存贮键 双功能键 若屏幕右上角有测量数据未存标志时 则按下此键 将工作区的测量数据存贮到存贮器中 否则此键用于选择仪器 功能 确认键 用于确认输入或选择 退出键 用于退出当前菜单功能或结束数据输入 A 接A电极 B 接B电极 供电输出接线柱 信号输入接线柱 M 接M电极 N 接N电极 用于接高压供电电源 接电源正极 接电源负极 RS-232 为标准串行接口 将测量数据传送到微机 做进一步处理 开 关 仪器电源开关按键 按开则打开电源 按关则关闭仪器电源 R地 两芯电极接地电阻测试插座 报警 出错报警蜂鸣器

R地 超强干扰抑制器 程控放大 M N 加 法 器 2 3 2 S R 键盘 显示器 大容量 程序与数据 存储器 3 电池电压 D / A 多 路 转 换 开 关

接口

转换器

电流

键盘控制器

+ -

B

A

图3-1

P S 电桥控制 隔放滤波

补偿

中央处理模块 数字滤波模块 过流保护模块

显示控制器

高压电桥 电流取样

录

仪器主要特点与功能 ·············································································2 仪器主要技术指标 ·················································································2 仪器工作原理 ··························································································3 仪器结构 ···································································································4 操作说明 ···································································································5 5-1 开机与对比度调节 ···········································································5 5-2 菜单操作 ····························································································5 5-2.0 主菜单 ···························································································5 5-2.1 设置工作参数 ··············································································5 5-2.2 测量 ································································································7 5-2.3 测线表 ·························································································10 5-2.4 显示曲线 ····················································································11 5-2.5 显示数据 ····················································································11 5-2.6 RS-232C 通讯 ···········································································12 5-2.7 硬件测试 ····················································································12 5-3 存贮操作 ··························································································13 5-4 清除操作 ··························································································13 5-5 选择测量功能 ·················································································14 5-6 关机 ··································································································15 5-7 测量操作一般工作流程 ································································15 5-8 野外操实例 ·················································································16 5-9 操作注意事项 ·················································································21 六 故障诊断 ··································································································21 七 仪器保养 ··································································································22 八 仪器成套性 ································································································22 附录 A 附录 B 附录 C 附录 D 附录E 数据接收与格式转换软件 BTRC 使用说明 电极排列的说明 主要参数含义及计算方法 问题解答 无极差电极的制做

400NEDPV-3 3 孔终端装载洗衣机 萃取机规格说明书

103" [2616mm]

V

54" [1372mm]

F

L1 L 2-LL 2-CL 2-R

! DAN GER A m p u t a t i o n hazard. T u r n i n g c y linder can t w i s t o ff ar m s.

Nev er r ea ch i nt o or p ull l i n e n fr o m a turning c yl in de r .

weight imbalance.

Shipping Weight

12,780 lbs [5,797 kg]

Operating Weight

15,630 lbs. [7,090kg]

Static Base Plate Loading

1464.9 lbs/sq.ft. [7,152 kg/m2]

Dynamic Base Plate Loading

D1 & D2 D3

4" [108mm] 23" [597mm]

27" [679mm]

88" [2248mm]

ON

O F F

W1 W2 W3 W4

91" [2324mm]

47" [1194mm]

2" BORE x 4" STROKE 2" BORE x 4" STROKE 2" BORE x 4" STROKE

END-LOADER WASHER/EXTRACTOR SPECIFICATIONS

EL 400 – 3 POCKET (400NEDPV-3)

G.A. BRAUN, INC., P.O. BOX 3029, SYRACUSE, NY 13220, 315-475-3123

三汇示波器说明书(Ver1.0)

DST4000 和 DST1000 系列数字存储示波器用户手册

i

目录

5.1 显示区 ........................................................................................ 20 5.2 信息区域..................................................................................... 23 5.3 波形显示..................................................................................... 23

三汇系列产品

DST4000 和 DST1000 系列 数字存储示波器

Version 1.0

杭州三汇科技有限公司 www.

目录

目录

目 录 ...........................................................................................................i 版权申明 .......................................................................................................................................................................v 第 1 章 安全事项......................................................................................... 1

723数字控制说明书

合排油门限制和时间延迟的目的是防止合排时 冒烟。当将33闭合(螺旋桨脱排)和34断开(发 电机合排)时,增压空气和扭距限制不起作用, 转速将按转速斜率特性来控制(若不须转速斜率 控制,可将斜率设定为0)。

图1 系统原理图

723数字控制器内设有扭矩限制和增压空气压力 限制器,两条限制曲线由5个设定点组成。Slave机 使用自身的限制曲线,因此两台主机可有不同的 限制曲线。另外,Slave机也可由外部信号来限制。 如果Master机已被限制,则Slave机也被限制,因 为Slave机的油门始终跟随Master机处在同样位置。

2. 静电保护

注意:本系统中有些另部件对静电损害特别敏 感,必须采取一定措施消除或减少静电量,当 你接近或动作该控制器时必须注意以下几点:

2.1 当你需要对该电子控制设备进行维修时,必 须释放你身上所带的静电,办法是用手握住接 地的金属体(管子、箱体、设备等)

2.2 防止在你身上产生静电,尽量不要穿化纤衣 服,而穿棉制品,后者较前者储存静电较少。

723数字控制器有两组PID调节参数,可按不同的 合排状态选择,控制器的增益、稳定度和补偿率可 以选择成主机转速的函数关系。其增益量在转速偏 差大于一定值后自动增大。合排时,四个离合器不 能同时合排。

3.2 输入/输出结构 723有开关量输入/输出,和模拟量输入/输出两种

接口。

3.2.1 输入口内容说明 总共有8个开关量输入口,可以用编程来设定其

Woodward 723数字控制 器

说明书

上海驷博监控技术工程有限公司

W3EG72125S-D3中文资料

W3EG72125S-D3-JD3-AJD3PRELIMINARY*White Electronic Designs1GB – 2x64Mx72 DDR SDRAM REGISTERED ECC w/PLLThe W3E G72125S is a 2x64Mx72 Double Data Rate SDRAM memory module based on 256Mb DDR SDRAM components. The module consists of eighteen 2x64Mx4 stacked (36 components), in 66 pin TSOP package mounted on a 184 pin FR4 substrate.Synchronous design allows precise cycle control with the use of system clock. Data I/O transactions are possible on both edges and Burst Lengths allow the same device to be useful for a variety of high bandwidth, high performance memory system ap p li c a t ions.* T his product is under development, is not qualifi ed or characterized and is subject to change without notice.DESCRIPTIONFEATURESDouble-data-rate architectureClock Speeds of 100MHz, 133MHz and 166MHz Bi-directional data strobes (DQS) Differential clock inputs (CK & CK#) Programmable Read Latency 2,2.5 (clock) Programmable Burst Length (2,4,8)Programmable Burst type (sequential & interleave) Edge aligned data output, center aligned data input Auto and self refresh Serial presence detect Dual RankPower supply: V CC = 2.5V ± 0.2V JEDEC standard 184 pin DIMM package• Package height options:JD3: 30.48mm (1.20") and AJD3: 28.70mm (1.13")NOTE: C onsult factory for availability of:• RoHS compliant products • Vendor source control options • Industrial temperature optionOPERATING FREQUENCIESDDR333 @CL=2.5DDR266 @CL=2DDR266 @CL=2DDR266 @CL=2.5DDR200 @CL=2Clock Speed 166MHz 133MHz 133MHz 133MHz 100MHz CL-t RCD -t RP2.5-3-32-2-22-3-32.5-3-32-2-2W3EG72125S-D3-JD3-AJD3PRELIMINARYWhite Electronic DesignsPIN#SYMBOL PIN#SYMBOL PIN#SYMBOL PIN#SYMBOL 1V REF 47DQS893V SS 139V SS 2DQ048A094DQ4140DQS173V SS 49CB295DQ5141A104DQ150V SS 96V CCQ 142CB65DQS051CB397DQS9143V CCQ 6DQ252BA198DQ6144CB77V CC 53DQ3299DQ7145V SS 8DQ354V CCQ 100V SS 146DQ369NC 55DQ33101NC 147DQ3710RESET#56DQS4102NC 148V CC 11V SS 57DQ34103NC 149DQS1312DQ856V SS 104V CCQ 150DQ3813DQ959BA0105DQ12151DQ3914DQS160DQ35106DQ13152V SS 15V CCQ 61DQ40107DQS10153DQ4416NC 62V CCQ 108V CC 154RAS#17NC 63WE#109DQ14155DQ4518V SS 64DQ41110DQ15156V CCQ 19DQ1065CAS#111CKE1157CS0#20DQ1166V SS 112V CCQ 158CS1#21CKE067DQS5113NC 159DQS1422V CCQ 68DQ42114DQ20160V SS 23DQ1669DQ43115A12161DQ4624DQ1770V CC 116V SS 162DQ4725DQS271NC 117DQ21163NC 26V SS 72DQ48118A11164V CCQ 27A973DQ49119DQS11165DQ5228DQ1874V SS 120V CC 166DQ5329A775NC 121DQ22167NC 30V CCQ 76NC 122A8168V CC 31DQ1977V CCQ 123DQ23169DQS1532A578DQS6124V SS 170DQ5433DQ2479DQ50125A6171DQ5534V SS 80DQ51126DQ28172V CCQ 35DQ2581V SS 127DQ29173NC 36DQS382V CCID 128V CCQ 174DQ6037A483DQ56129DQS12175DQ6138V CC 84DQ57130A3176V SS 39DQ2685V CC 131DQ30177DQS1640DQ2786DQS7132V SS 178DQ6241A287DQ58133DQ31179DQ6342V SS 88DQ59134CB4180V CC Q 43A189V SS 135CB5181SA044CB090NC 136V CCQ 182SA145CB191SDA 137CK0183SA246V CC92SCL138CK0#184V CCSPDPIN CONFIGURATIONA0-A12Address input (Multiplexed)BA0-BA1Bank Select Address DQ0-DQ63Data Input/Output CB0-CB7Check bitsDQS0-DQS17Data Strobe Input/Output CK0Clock Input CK0#Clock inputCKE0, CKE1Clock Enable input CS0#, CS1#Chip Select Input RAS#Row Address Strobe CAS#Column Address Strobe WE#Write EnableV CC Power Supply (2.5V)V CCQ Power Supply for DQS (2.5V)V SS GroundV REF Power Supply for Reference V CCSPD Serial EEPROM Power Supply (2.3V to 3.6V)SDA Serial data I/O SCL Serial clockSA0-SA2Address in EEPROM V CCID V CC Indentifi cation Flag NCNo Connect RESET#Reset EnablePIN NAMESW3EG72125S-D3-JD3 White Electronic Designs-AJD3PRELIMINARY FUNCTIONAL BLOCK DIAGRAMW3EG72125S-D3-JD3-AJD3PRELIMINARYWhite Electronic DesignsABSOLUTE MAXIMUM RATINGSDC CHARACTERISTICS0°C ≤ T A ≤ 70°C, V CC = 2.5V ± 0.2VCAPACITANCET A = 25°C, f = 1MHz, V CC = 2.5VParameter Symbol Min Max Unit Supply Voltage V CC 2.3 2.7V Supply Voltage V CCQ 2.3 2.7V Reference Voltage V REF 1.15 1.35V Termination Voltage V TT 1.15 1.35V Input High Voltage V IH V REF + 0.15V CCQ + 0.3V Input Low Voltage V IL -0.3V REF - 0.15V Output High Voltage V OH V TT + 0.76—V Output Low VoltageV OL—V TT - 0.76VParameterSymbol Max Unit Input Capacitance (A0-A12)C IN1 6.5pF Input Capacitance (RAS#, CAS#, WE#)C IN2 6.5pF Input Capacitance (CKE0)C IN3 6.5pF Input Capacitance (CK0#, CK0)C IN4 5.5pF Input Capacitance (CS0#)C IN5 6.5pF Input Capacitance (DQM0-DQM8)C IN613pF Input Capacitance (BA0-BA1)C IN7 6.5pF Data input/output capacitance (DQ0-DQ63)(DQS)C OUT 13pF Data input/output capacitance (CB0-CB7)C OUT13pFParameterSymbol Value Units Voltage on any pin relative to V SS V IN , V OUT -0.5 to 3.6V Voltage on V CC supply relative to V SS V CC , V CCQ-1.0 to 3.6V Storage Temperature T STG -55 to +150°C Power Dissipation P D 9W Short Circuit CurrentI OS50mANote: Permanent device damage may occur if "ABSOLUTE MAXIMUM RATINGS" are exceeded. Functional operation should be restricted to recommended operating condition. Exposure to higher than recommended voltage for extended periods of time could affect device reliability.W3EG72125S-D3-JD3-AJD3PRELIMINARY White Electronic DesignsI DD SPECIFICATIONS AND TEST CONDITIONS0°C ≤ T A≤ +70°C, V CCQ = 2.5V ± 0.2V, V CC = 2.5V ± 0.2V.Includes DDR SDRAM components onlyParameter Symbol Rank 1ConditionsDDR333@CL=2.5MaxDDR266:@CL=2, 2.5MaxDDR200@CL=2Max UnitsRank 2StandbyStateOperating Current I DD0One device bank; Active - Precharge; t RC= t RC (MIN); t CK = t CK (MIN); DQ,DM andDQS inputs changing once per clock cycle;Address and control inputs changing onceevery two cycles.441039603960mA I DD3NOperating Current I DD1One device bank; Active-Read-PrechargeBurst = 2; t RC = t RC (MIN); t CK = t CK (MIN);l OUT = 0mA; Address and control inputschanging once per clock cycle.522045904590mA I DD3NPrecharge Power-Down Standby Current I DD2P All device banks idle; Power-down mode;t CK = t CK (MIN); CKE = (low)144144144rnA I DD2PIdle Standby Current I DD2F CS# = High; All device banks idle;t CK = t CK (MIN); CKE = High; Addressand other control inputs changing onceper clock cycle. V IN = V REF for DQ, DQSand DM.180016201620mA I DD2FActive Power-Down Standby Current I DD3P One device bank active; Power-Downmode; t CK (MIN); CKE = (low)108010801080mA I DD3PActive Standby Current I DD3N CS# = High; CKE = High; One devicebank; Active-Precharge;t RC = t RAS (MAX);t CK = t CK (MIN); DQ, DM and DQS inputschanging twice per clock cycle; Addressand other control inputs changing once perclock cycle.216018001800mA I DD3NOperating Current I DD4R Burst = 2; Reads; Continuous burst; Onedevice bank active; Address and controlinputs changing once per clock cycle; t CK =t CK (MIN); l OUT = 0mA.531049504950mA I DD3NOperating Current I DD4W Burst = 2; Writes; Continuous burst; Onedevice bank active; Address and controlinputs changing once per clock cycle;t CK = t CK (MIN); DQ,DM and DQS inputschanging once per clock cycle.504052205220rnA I DD3NAuto Refresh Current I DD5t RC = t RC (MIN)675062106210mA I DD3N Self Refresh Current I DD6CKE ≤ 0.2V144144144mA I DD6 Operating Current I DD7A Four bank interleaving Reads (BL=4)with auto precharge with t RC=t RC (MIN);t CK=t CK(MIN); Address and control inputschange only during Active Read or Writecommands.954083708370mA I DD3NW3EG72125S-D3-JD3-AJD3PRELIMINARY White Electronic DesignsI DD SPECIFICATIONS AND TEST CONDITIONS0°C ≤ T A≤ +70°C, V CCQ = 2.5V ± 0.2V, V CC = 2.5V ± 0.2V.Includes PLL and register powerParameter Symbol Rank 1ConditionsDDR333@CL=2.5MaxDDR266:@CL=2, 2.5MaxDDR200@CL=2Max UnitsRank 2StandbyStateOperating Current I DD0One device bank; Active - Precharge; t RC= t RC (MIN); t CK = t CK (MIN); DQ,DM andDQS inputs changing once per clock cycle;Address and control inputs changing onceevery two cycles.523047804780mA I DD3NOperating Current I DD1One device bank; Active-Read-PrechargeBurst = 2; t RC = t RC (MIN); t CK = t CK (MIN);l OUT = 0mA; Address and control inputschanging once per clock cycle.604054105410mA I DD3NPrecharge Power-Down Standby Current I DD2P All device banks idle; Power-down mode;t CK = t CK (MIN); CKE = (low)144144144rnA I DD2PIdle Standby Current I DD2F CS# = High; All device banks idle;t CK = t CK (MIN); CKE = High; Addressand other control inputs changing onceper clock cycle. V IN = V REF for DQ, DQSand DM.214519651965mA I DD2FActive Power-Down Standby Current I DD3P One device bank active; Power-Downmode; t CK (MIN); CKE = (low)108010801080mA I DD3PActive Standby Current I DD3N CS# = High; CKE = High; One devicebank; Active-Precharge;t RC = t RAS (MAX);t CK = t CK (MIN); DQ, DM and DQS inputschanging twice per clock cycle; Addressand other control inputs changing once perclock cycle.250521452145mA I DD3NOperating Current I DD4R Burst = 2; Reads; Continuous burst; Onedevice bank active; Address and controlinputs changing once per clock cycle; t CK =t CK (MIN); l OUT = 0mA.613057705770mA I DD3NOperating Current I DD4W Burst = 2; Writes; Continuous burst; Onedevice bank active; Address and controlinputs changing once per clock cycle;t CK = t CK (MIN); DQ,DM and DQS inputschanging once per clock cycle.586060406040rnA I DD3NAuto Refresh Current I DD5t RC = t RC (MIN)744069006900mA I DD3N Self Refresh Current I DD6CKE ≤ 0.2V619619619mA I DD6 Operating Current I DD7A Four bank interleaving Reads (BL=4)with auto precharge with t RC=t RC (MIN);t CK=t CK(MIN); Address and control inputschange only during Active Read or Writecommands.1036091909190mA I DD3NW3EG72125S-D3-JD3-AJD3PRELIMINARY White Electronic DesignsI DD1 : Operating Current : One Bank1. Typical Case : V CC =2.5V, T = 25°C2. Worst Case : V CC = 2.7V, T = 10°C3. Only one bank is accessed with t RC (min), BurstMode, Address and Control inputs on NOP edgeare changing once per clock cycle. I OUT = 0mA4. Timing Patterns :• DDR200 (100 MHz, CL = 2) : t CK = 10ns, CL2, BL=4, t RCD = 2*t CK, t RAS = 5*t CKRead : A0 N R0 N N P0 N A0 N - repeat thesame timing with random address changing;50% of data changing at every burst• DDR266 (133MHz, CL=2.5) : t CK = 7.5ns, CL = 2.5, BL = 4, t RCD = 3*tCK, t RC = 9*t CK,t RAS = 5*t CKRead : A0 N N R0 N P0 N N N A0 N - repeatthe same timing with random addresschanging; 50% of data changing at every burst • DDR266 (133MHz, CL = 2) : t CK = 7.5ns,CL = 2, BL = 4, t RCD = 3*t CK, t RC = 9*t CK,t RAS = 5*t CKRead : A0 N N R0 N P0 N N N A0 N - repeatthe same timing with random addresschanging; 50% of data changing at every burst • DDR333 (166MHz, CL = 2.5) : t CK = 6ns,BL = 4, t RCD = 10*t CK, t RAS = 7*t CKRead : A0 N N R0 N P0 N N N A0 N - repeatthe same timing with random addresschanging; 50% of data changing at every burst I DD7A : Operating Current: Four Banks1. Typical Case : V CC =2.5V, T = 25°C2. Worst Case : V CC = 2.7V, T = 10°C3. Four banks are being interleaved with t RC (min),Burst Mode, Address and Control inputs on NOPedge are not changing. I OUT=0mA4. Timing Patterns :• DDR200 (100 MHz, CL = 2) : t CK = 10ns, CL2, BL = 4, t RRD = 2*t CK, t RCD = 3*t CK, Read withAutoprechargeRead : A0 N A1 R0 A2 R1 A3 R2 A0 R3 A1 R0- repeat the same timing with random addresschanging; 100% of data changing at everyburst• DDR266 (133MHz, CL = 2.5) : t CK = 7.5ns, CL = 2.5, BL = 4, t RRD = 3*t CK, t RCD = 3*t CKRead with AutoprechargeRead : A0 N A1 R0 A2 R1 A3 R2 N R3 A0 NA1 R0 - repeat the same timing with randomaddress changing; 100% of data changing atevery burst• DDR266 (133MHz, CL = 2) : t CK = 7.5ns,CL2 = 2, BL = 4, t RRD = 2*t CK, t RCD = 2*t CKRead : A0 N A1 R0 A2 R1 A3 R2 N R3 A0 NA1 R0 - repeat the same timing with randomaddress changing; 100% of data changing atevery burst• DDR333 (166MHz, CL=2.5) : t CK=6ns,BL=4, t RRD=3*t CK, t RCD=3*t CK, Read withAutoprechargeRead : A0 N A1 R0 A2 R1 A3 R2 N R3 A0 NA1 R0 - repeat the same timing with randomaddress changing; 100% of data changing atevery burstDETAILED TEST CONDITIONS FOR DDR SDRAM I DD1 & I DD7ALegend : A = Activate, R = Read, W = Write, P = Precharge, N = NOPA (0-3) = Activate Bank 0-3R (0-3) = Read Bank 0-3W3EG72125S-D3-JD3 White Electronic Designs-AJD3PRELIMINARYDDR SDRAM COMPONENT ELECTRICAL CHARACTERISTICS ANDRECOMMENDED AC OPERATING CONDITIONS0°C ≤ T A ≤ +70°C; V CC = +2.5V ±0.2V, V CCQ = +2.5V ±0.2VAC Characteristics335262/263/265202Parameter Symbol Min Max Min Max Min Max Units Notes Access window of DQs from CK, CK#t AC-0.7+0.7-0.75+0.75-0.8+0.8nsCK high-level width t CH0.450.550.450.550.450.55t CK16 CK low-level width t CL0.450.550.450.550.450.55t CK16 Clock cycle time CL=2.5t CK (2.5)6137.513813ns22CL=2t CK (2)7.5137.5/10131013ns22 DQ and DM input hold time relative to DQS t DH0.450.50.6ns14,17 DQ and DM input setup time relative to DQS t DS0.450.50.6ns14,17 DQ and DM input pulse width (for each input)t DIPW 1.75 1.752ns17 Access window of DQS from CK, CK#t DQSCK-0.60+0.60-0.75+0.75-0.8+0.8nsDQS input high pulse width t DQSH0.350.350.35t CKDQS input low pulse width t DQSL0.350.350.35t CKDQS-DQ skew, DQS to last DQ valid, per group, per access t DQSQ0.350.50.6ns13,14 Write command to fi rst DQS latching transition t DQSS0.75 1.250.75 1.250.75 1.25t CKDQS falling edge to CK rising - setup time t DSS0.20.20.2t CKDQS falling edge from CK rising - hold time t DSH0.20.20.2t CKHalf clock period t HP t CH, t CL t CH, t CL t CH, t CL ns18 Data-out high-impedance window from CK, CK#t HZ+0.70+0.75+0.8ns8,19 Data-out low-impedance window from CK, CK#t LZ-0.70-0.75-0.8ns8,20 Address and control input hold time (fast slew rate)t IHf0.750.90 1.1ns6 Address and control input set-up time (fast slew rate)t ISf0.750.90 1.1ns6 Address and control input hold time (slow slew rate)t IHs0.801 1.1ns6 Address and control input setup time (slow slew rate)t ISs0.801 1.1ns6 Address and control input pulse width (for each input)t IPW 2.2 2.2 2.2nsLOAD MODE REGISTER command cycle time t MRD121516nsDQ-DQS hold, DQS to fi rst DQ to go non-valid, per access t QH t HP-t QHS t HP-t QHS t HP-t QHS ns13,14 Data hold skew factor t QHS0.500.751nsACTIVE to PRECHARGE command t RAS42120,00040120,00040120,000ns15 ACTIVE to READ with Auto precharge command t RAP182020nsACTIVE to ACTIVE/AUTO REFRESH command period t RC606570nsAUTO REFRESH command period t RFC727580ns21W3EG72125S-D3-JD3 White Electronic Designs-AJD3PRELIMINARYDDR SDRAM COMPONENT ELECTRICAL CHARACTERISTICS ANDRECOMMENDED AC OPERATING CONDITIONS (continued)0°C ≤ T A ≤ +70°C; V CC = +2.5V ±0.2V, V CCQ = +2.5V ±0.2VAC Characteristics335262/263/265202Parameter Symbol Min Max Min Max Min Max Units Notes ACTIVE to READ or WRITE delay t RCD182020ns PRECHARGE command period t RP182020nsDQS read preamble t RPRE0.9 1.10.9 1.10.9 1.1t CK19 DQS read postamble t RPST0.40.60.40.60.40.6t CKACTIVE bank a to ACTIVE bank b command t RRD121515nsDQS write preamble t WPRE0.250.250.25t CKDQS write preamble setup time t WPRES000ns10,11 DQS write postamble t WPST0.40.60.40.60.40.6t CK9 Write recovery time t WR151515nsInternal WRITE to READ command delay t WTR111t CKData valid output window NA t QH-t DQSQ t QH-t DQSQ t QH-t DQSQ ns13 REFRESH to REFRESH command interval t REFC70.370.370.3μs12 Average periodic refresh interval t REFI7.87.87.8μs12 Terminating voltage delay to V CC t VTD000nsExit SELF REFRESH to non-READ command t XSNR757580nsExit SELF REFRESH to READ command t XSRD200200200t CKW3EG72125S-D3-JD3-AJD3PRELIMINARY White Electronic DesignsNotes1. All voltages referenced to V SS2. Tests for AC timing, I DD, and electrical AC and DC characteristicsmay be conducted at normal reference / supply voltage levels, butthe related specifi cations and device operations are guaranteed forthe full voltage range specifi ed.3. Outputs are measured with equivalent load:Output (V OUT)Ω4. AC timing and I DD tests may use a V IL-to-V IH swing of up to 1.5Vin the test environment, but input timing is still referenced to V REF(or to the crossing point for CK/CK#), and parameter specifi cations are guaranteed for the specifi ed AC input levels under normal use conditions. The minimum slew rate for the input signals used totest the device is 1V/ns in the range between V IL(AC) and V IH(AC).5. The AC and DC input level specifi cations are defi ned in the SSTL_2 standard (i.e., the receiver will effectively switch as a result of thesignal crossing the AC input level, and will remain in that state aslong as the signal does not ring back above [below] the DC inputLOW [high] level).6. For slew rates less than 1V/ns and greater than or equal to 0.5V/ns. If the slew rate is less than 0.5V/ns, timing must be derated: t IS has an additional 50ps per each 100mV/ns reduction in slew ratefrom the 500mV/ns. t IH has 0ps added, that is, it remains constant.If the slew rate exceeds 4.5V/ns, functionality is uncertain. For 403 and 335, slew rates must be greater than or equal to 0.5V/ns.7. Inputs are not recognized as valid until V REF stabilizes. Exception:during the period before V REF stabilizes, CKE ≤ 0.3 x V CCQ isrecognized as LOW.8. t HZ and t LZ transitions occur in the same access time windows asvalid data transitions. These parameters are not referenced to aspecifi c voltage level, but specify when the device output is nolonger driving (HZ) and begins driving (LZ).9. The intent of the “Don’t Care” state after completion of thepostamble is the DQS-driven signal should either be HIGH, LOW, or high-Z, and that any signal transition within the input switchingregion must follow valid input requirements. That is, if DQStransitions HIGH (above V IHDC (MIN) then it must not transitionLOW (below V IHDC) prior to t DQSH (MIN).10. This is not a device limit. The device will operate with a negativevalue, but system performance could be degraded due to busturnaround.11. It is recommended that DQS be valid (HIGH or LOW) on or beforethe WRITE command. The case shown (DQS going from High-Z to logic LOW) applies when no WRITEs were previously in progresson the bus. If a previous WRITE was in progress, DQS could behigh during this time, depending on t DQSS.12. The refresh period is 64ms. This equates to an average refreshrate of 7.8125µs. However, an AUTO REFRESH command mustbe asserted at least once every 70.3µs; burst refreshing or posting by the DRAM controller greater than eight refresh cycles is notallowed.13. The valid data window is derived by achieving other specifi cations- t HP (t CK/2), t DQSQ, and t QH (t QH = t HP - t QHS). The data validwindow derates directly proportional with the clock duty cycleand a practical data valid window can be derived. The clock isallowed a maximum duty cycled variation of 45/55. Functionalityis uncertain when operating beyond a 45/55 ratio. The data validwindow derating curves are provided below for duty cycles ranging between 50/50 and 45/55.14. Referenced to each output group: x4 = DQS with DQ0-DQ4.15. READs and WRITEs with auto precharge are not allowed to beissued until t RAS (MIN) can be satisfi ed prior to the internal precharge command being issued.16. JEDEC specifi(2V/ns differentially).17. DQ and DM input slew rates must not deviate from DQS by morethan 10%. If the DQ/DM/DQS slew rate is less than 0.5V/ns,timing must be derated: 50ps must be added to t DS and t DH foreach 100mV/ns reduction in slew rate. If slew rates exceed 4V/ns, functionality is uncertain.18. t HP min is the lesser of t CL min and t CH min actually applied to thedevice CK and CK# inputs, collectively during bank active.19. t HZ (MAX) will prevail over the t DQSCK (MAX) + t RPST (MAX)condition. t LZ (MIN) will prevail over t DQSCK (MIN) + PRE (MAX)condition.20. For slew rates greater than 1V/ns the (LZ) transition will start about310ps earlier.21. CKE must be active (High) during the entire time a refreshcommand is executed. That is, from the time the AUTO REFRESH command is registered, CKE must be active at each rising clockedge, until t RFC has been satisfi ed.22. Whenever the operating frequency is altered, not including jitter,the DLL is required to be reset. This is followed by 200 clock cycles(before READ commands).W3EG72125S-D3-JD3-AJD3PRELIMINARYWhite Electronic DesignsPACKAGE DIMENSIONS FOR JD3ORDERING INFORMATION FOR JD3Part Number Speed CAS Latencyt RCD t RP Height*W3EG72125S335JD3166MHz/333Mb/s 2.53330.48 (1.20")W3EG72125S262JD3133MHz/266Mb/s 22230.48 (1.20")W3EG72125S263JD3133MHz/266Mb/s 23330.48 (1.20")W3EG72125S265JD3133MHz/266Mb/s 2.53330.48 (1.20")W3EG72125S202JD3100MHz/200Mb/s22230.48 (1.20")NOTES: • Consult Factory for availability of RoHS compliant products. (G = RoHS Compliant) • V endor specifi c part numbers are used to provide memory components source control. The place holder for this is shown as lower case “x” in the part numbers above and is tobe replaced with the respective vendors code. Consult factory for qualifi ed sourcing options. (M = Micron, S = Samsung & consult factory for others)• Consult factory for availability of industrial temperature (-40°C to 85°C) optionW3EG72125S-D3-JD3-AJD3PRELIMINARYWhite Electronic DesignsPACKAGE DIMENSIONS FOR AJD3ORDERING INFORMATION FOR AJD3Part NumberSpeed CAS Latencyt RCD t RP Height*W3EG72125S335AJD3166MHz/333Mb/s 2.53328.70 (1.13")W3EG72125S262AJD3133MHz/266Mb/s 22228.70 (1.13")W3EG72125S263AJD3133MHz/266Mb/s 23328.70 (1.13")W3EG72125S265AJD3133MHz/266Mb/s 2.53328.70 (1.13")W3EG72125S202AJD3100MHz/200Mb/s22228.70 (1.13")NOTES: • Consult Factory for availability of RoHS compliant products. (G = RoHS Compliant) • V endor specifi c part numbers are used to provide memory components source control. The place holder for this is shown as lower case “x” in the part numbers above and is tobe replaced with the respective vendors code. Consult factory for qualifi ed sourcing options. (M = Micron, S = Samsung & consult factory for others)• Consult factory for availability of industrial temperature (-40°C to 85°C) optionW3EG72125S-D3-JD3-AJD3PRELIMINARYWhite Electronic DesignsPACKAGE DIMENSIONS FOR D3ORDERING INFORMATION FOR D3Part Number Speed CAS Latencyt RCD t RP Height*W3EG72125S335D3166MHz/333Mb/s 2.53328.58 (1.125")W3EG72125S262D3133MHz/266Mb/s 22228.58 (1.125")W3EG72125S263D3133MHz/266Mb/s 23328.58 (1.125")W3EG72125S265D3133MHz/266Mb/s 2.53328.58 (1.125")W3EG72125S202D3100MHz/200Mb/s22228.58 (1.125")NOTES: • Consult Factory for availability of RoHS compliant products. (G = RoHS Compliant) • V endor specifi c part numbers are used to provide memory components source control. The place holder for this is shown as lower case “x” in the part numbers above and is tobe replaced with the respective vendors code. Consult factory for qualifi ed sourcing options. (M = Micron, S = Samsung & consult factory for others)• Consult factory for availability of industrial temperature (-40°C to 85°C) optionW3EG72125S-D3-JD3 White Electronic Designs-AJD3PRELIMINARY Document Title1GB – 2x64Mx72 DDR SDRAM REGISTERED ECC w/PLLRevision HistoryRev #History Release Date StatusRev 0Initial Release May 2002AdvancedFebruary 2003Preliminary Rev 1Changes (Pg. 1, 3, 4, 5, 6, 7, 8, 9, 10)1.1 Update module description to 2 Ranks 64Mb x 721.2 Correct block diagram1.3 D3 Module "Not Recommended for New Designs".1.4 JD3 Module dimension corrections1.5 AJD3 Module dimension correctionsRev 2 2.1 Added Lead-Free and RoHS note November 2004Preliminary。

3W3中文手册(通用)

U n i n t e r r u p t i b l eP o w e r S u p p l y用户手册U S E R′S M A N U A L10-40KVA三相输出Three-phase Outputpag. 2 / 29安全规范注意事项本手册包含安装与操作本产品的说明.。

请在安装前由经过专业训练的人员详细阅读本手册。

因为本手册包含基本的使用说明。

请妥善保存!安全规范■ 本产品安装时必须接地请确保地线牢固地索附在有右图标示的接地铜条上:■ 所有关于本产品内部的维修保养工作必须由经过专业训练的人员操作■ 在需要更换保险丝的情形时,请更换同样型式与规格的保险丝(请参阅”设置输出入配线”章节). ■ 在必须切断UPS 的输入市电时,请断开前面板内的所有开关,或者经由UPS 的控制面板选择”SYSTEM OFF”电瓶更换必须由专业人员执行.更换之后的废电瓶请交由专业的废电的处置,因为电池内 可能有对环境造成污染的物质!由于本产品不断的改良与研发,对于本手册内容有所修正时将不另行通知.欢迎您随时与我们联系以取得最新信息.电磁干扰要求本产品”不断电式电源供应器”(UPS),符合基本的电磁干扰要求:EMC 指令89/336e 92/31 a 93/68 ECC.使用说明警告:本产品属于A 等级的UPS.在居住的环境中,本产品可能会造成无线电干扰,此情况下,使用者可能必须采取适当的措施.例如:当电视或者收音机受到干扰时,可将本产品搬移到适当的距离以减少干扰情形.索引外观位置图 (5)储存 (5)安装环境 (6)前置作业 (6)安装环境 (6)安装位置 (6)设置输出入配线 (7)保护 (7)UPS内部 (7)UPS输入 (7)UPS 输出,短路与选择性 (7)差异 (8)配线与连接 (8)启动UPS前置作业 (8)市电与负载连接 (9)三相输出(输入:三相) (9)电瓶 (9)外接电瓶箱 (9)内接电瓶箱 (9)连接状况 (9)开机程序 (9)功能检查 (10)关机 (10)配置模式 (10)在线式(ON - LINE) (10)待机经济模式(STANDBY-ON operation) (10)操作模式 (11)电瓶操作模式(不属于稳压器配置模式) (11)旁路操作模式 (12)手动旁路维护模式 (12)维护 (13)UPS 部件 (13)输入 / 输出过滤器 (13)转换器 (13)pag. 3 / 29逆变器 (14)旁路 (14)SWMB (手动维护开关), SWIN, SWOUT (14)电瓶 (14)RS232 n.1 与 n. 2 介面 (14)讯号及指令面板 (14)EPO连接器 (15)规格 (16)系统 (16)转换器输入 (16)转换器输出 (17)电瓶 (17)输出逆变器 (17)旁路 (17)状态讯息显示 (18)概述 (18)警示灯号: LED (18)警告讯息 (19)控制面板 (20)基本选单 (20)Key menu 1, "?", HELP (20)Key menu 2 "测量" (20)Key menu 2, 2 : “输出测量” (21)Key menu 3 "KEY", 指令 (21)Key menu 3, 2: 电瓶测试 (21)Key menu 3, 5: 使用者自订 (22)Key menu 3, 5, 436215, 2: 工作模式和功率设定 (22)Key menu 3, 5, 436215,3:输出电压,旁路电压范围,旁路频率范围的设定 (22)Key menu 3, 5, 436215, 4:电池数量,电池浮充电压,电池容量设定 (22)Key menu 3, 5, 436215,5:电池定时自测试设定 (22)Key menu 3, 6: 逆变器关闭 / 切至旁路模式 (23)Key menu 3, 7: 系统完全关机设定 (23)Key menu 4:事件记录 (23)故障代码表 (25)附录 (27)尺寸 / 重量 (28)pag. 4 / 29pag. 5 / 29外观位置图1. 控制面板2. 上面板3. 前面板4. 滑轮5. 背面通风孔6. 散热孔7. 风扇网格 8. EPO 连接器9. REMOTE 连接器 10. RS232-2 通讯端口 11. RS232-1 通讯端口 12. 侧面板储存本产品的储存条件如下:温 度:0°- 40°C (32°- 104°F) 相对湿度:< 95%UPS 内含电瓶时:UPS 内部的电瓶会因为化学变化而自我放电.假如您并非要立即使用本产品,请注意外装箱上标示的再充电日期(此标示只有在UPS 内含电瓶时才会有),并在期限内再充电!再充电只要提供UPS输入电源并开机限内再充电,保持在”正常模式”下运作至少24小时安装环境三相输出额定容量 [kVA] 10 15 20 30 40 操作温度0 ± 40 °C最大相对湿度95 % (无冷凝)最大操作高度4000m尺寸 (长 x 宽 x 高) [mm] 505 x 720 x 1140 505 x825 x 1215 UPS 重量100 114 120 126 140在标称负载及电瓶充电时的能量损失.[kW / kcal /B.T.U.]0.760024001.0490036001.39120048002.1180071002.824009600允许通过的空气流速(室内装置)[立方公尺/小时] 370 557 742 1100 1400 最大漏电流 (mA) < 100 mA保护等级IP20配线箱体底部前置作业本产品出厂时附有:- 保证书- 使用手册·-Nr. 3输入电瓶保险丝,-Nr. 2 输入电瓶箱保险丝(假如内接电瓶存在时)安装环境· 避免灰尘量太大,或者空气内有其它粉尘类的物质.· 确认安装的地板可以承受UPS以及电瓶箱的重量(请参照”尺寸与重量”章节) · 请检查安装的地点有足够的空间,不会造成日后维修的困扰· UPS操作时的环境必须在0-40℃之间.本产品可以在0-40℃之间正常操作.建议最佳的UPS与电瓶操作温度是20-25℃之间.事实上,电瓶在20℃下的平均寿命是4年,而在30℃之下则寿命会减半.· 避免阳光直接照射及靠近热源.为了保持安装环境的温度如上所述,请装设适当的排热系统(请参照“规格”章节确认kcal/kW/B.T.U.参考值).你可以参考下列的做法:· 自然散热;· 强制散热:当外界温度(例如20℃比UPS的操作环境低(例如25℃);· 空调设备:当外界温度(例如30℃比UPS的操作环境高(例如25℃)安装位置对于安装位置请注意下列事项:• UPS 的前面板请留至少1公尺的空间以便日后维护方便.pag. 6 / 29• UPS后背板与墙壁间至少留下20公分的距离以保持散热风扇的排热效果;至少40公分以便维护.• 请勿放置任何物品于UPS的上方• 交流/直流输出入电源线可以从UPS的底部或者后方进入设置输出入配线保护UPS内部输出入的保护开关与保险丝如下所列(请查询方块图).更换保险丝时请依照下表所示的规格与型号.三相输出UPS开关及内部保护装置UPS型式开关保险丝[kVA] UPS输入UPS 输出 / 维护整流器输入保险丝电瓶保险丝旁路保险丝输入电流.输出电流.[A]SWIN SWOUT/SWMB FBAT FBY 最大值额定值10 32A(4P) 32A(4P) 25AgR(10x38)25A gR(10x38)25A gG(10x38) 18 14 15 32A(4P) 32A(4P) 32AgR(10x38)32A gR(10x38)32A gG(10x38) 26 2620 32A(4P) 32A(4P) 32AgR(10x38)32A gR(10x38)50A gR(14x51)32A gG(10x38) 35 3530 63A(4P) 63A(4P) 50AgR(14x51)50A gR(14x51)50A gG(14x51) 52 4440 80A(4P) 80A(4P) 63AgR(14x51)80A gR(14x51)63A gG(14x51) 70 61 UPS 输入.当安装输入保护装置时,请考量下列两种模式的最大可能电流:• 在"正常操作"模式, 由输入电源至整流器, “最大输入电流” 如上表所列.断路器在整流器输入位置, 如上表中的"SWIN".• 在"旁路操作"模式, 旁路的最大电流值由断路器"SWBY”保护.UPS 输出, 短路与选择性额定的输出入电流如上表所示.短路当 UPS的负载发生异常状况时,也就是短路,UPS将会经由限制供应的输出电流值做自我保护 (短路电流).视短路发生时的操作状况.可以分成两方面:• UPS 在正常模式下:UPS将马上切换到旁路模式,在保险丝动作前,电流值如同“旁路规格” 表所示.• UPS 在电瓶供电模式下:UPS 提供两倍的额定输出电流(0.1秒)选择性在正常操作模式下,选择性参照第二行。

ua723中文资料

元器件交易网IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinueany product or service without notice, and advise customers to obtain the latest version of relevant informationto verify, before placing orders, that information being relied on is current and complete. All products are soldsubject to the terms and conditions of sale supplied at the time of order acknowledgement, including thosepertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extentTI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarilyperformed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OFDEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICALAPPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, ORWARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHERCRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TOBE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operatingsafeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or representthat any license, either express or implied, is granted under any patent right, copyright, mask work right, or otherintellectual property right of TI covering or relating to any combination, machine, or process in which suchsemiconductor products or services might be or are used. TI’s publication of information regarding any thirdparty’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1999, Texas Instruments Incorporated。

3 x 2 3 GN 电子湿热转热炉产品说明书

4 Spare parts list

Lista ricambi

Brand/Marchio: Factory code:

All 9PDX

From sr. Nr/ Da Ser. Nr.: ***

From status level / Da scatto: **

Page: 1

Ed. 2015 09 Doc. Nr.: 875401M00

60 0282217501 057534 Guarnizione resistenza

Gasket, heating element

61 0682800000 054842 Motoventilatore forno

Fan motor, oven

62 0446578602 057937 Termostato

5 0855889602 054844 Guide Dx

6 0514846900 054868 Supporto anteriore guide

7 0805833900 054855 Cerniera superiore porta

8 0875854503 054849 Controporta

9 0543805500 054850 Guarnizione per vetro

Page: 3

Ed. 2015 09 Doc. Nr.: 875401M00

3 x 2/3 GN ELECTRIC HUMIDIFIED CONVECTION OVEN FORNO CONVEZIONE ELETTRICO UMIDIFICATO 3 x 2/3 GN

Pos

Factory Code

Ref. Group Page Notes

a

MKS DELTA III流量比例控制器说明书

Key Benefits•Accurately and repeatably control flow ratio providing for better process optimization•Digital control loop provides rapid response to channel set point independent of the gas mix•Uses standard web browser – no special software requiredFigure 2The DELTA III ratio controller provides control for three channels of flow. Above the device starts with flows of 25, 25 and 50% in channels Q1, Q2, and Q3, respectively. The flow then transitions to 33.3% in each channel followed by a transition to 10, 50 and 40% in each channel, respectively.PerformanceFull Scale Ranges (each channel nitrogen equivalent - Q)500, 1000, 2000, 3000, 5000 and 10000 sccmPercentage Accuracy (includes non-linearity, hysteresis,and non-repeatability)±2% set point (for flow ≥10% of channel Full Scale)Channel Flow Control Range0, 5 to 100% Full ScaleInput Ratio Range 0, 2 to 100% of total flow within flow channel control range Percentage Repeatability±0.3% of set pointResolution 0.02% of channel Full ScaleMaximum Operating Outlet Pressure 200 Torr at maximum flow rate through all channelsMaximum Allowable Outlet Pressure Differential(highest to lowest pressure channel)50 Torr with the same percentage flow through all channelsNormal Operating Pressure Differential <150 Torr @ 3K split 33.3%; Except, <450 Torr for 10K/10K Percentage Settling Time <3 seconds (typical dependent on downstream conductance matching) Maximum Inlet Pressure 150 psig (non-operational)Temperature CoefficientsZeroSpan • <0.05% Full Scale/°C (500 ppm)• <0.08% of Reading/°C (800 ppm)Warmup Time60 minutesNormal Operating Temperature10 to 60°CStorage Temperature-20 to 65°CStorage Humidity0 to 95% relative humidity, non-condensingTemperature Accuracy+2°CTemperature Resolution0.1°CCompliance CE (a n overall metal braided, shielded able, properly grounded at both ends, is required during use). MechanicalFittingsInletOutlet • Swagelok® 4 VCR®• Male (non-rotatable)• Male (non-rotatable)Leak IntegrityExternal (scc/sec He)Through Closed Valve • <1x10-10• <2% of Channel Full Scale at 500 Torr differential to <10 TorrWetted Materials316 S.S. VAR (equivalent to 316 S.S. SCQ for semiconductor quality);316 S.S., Inconel®, KM-45, PTFESurface Finish 5 microinch average RaWeight7.27 lbs (3300 g)Electrical Communications EtherCAT®Input Power Required+24 VDC ±10% (13 Watts)Connector 2 x RJ-45 (comm.) male, M8 male, 5 pin (power)Data Rate Switch/Selection No switchComm. Rate(s)100 MbpsMac ID Switches/Addresses 3 switches, 16 positionsNetwork Size Up to 4095 nodesVisual Indicators LED Power (green), LED Run (green), LED Error (red), LED Comm (green)The MKS DELTA III Flow Ratio Controller shall not be used with any gas mixture which will react with each other as gas reactions are likely to affect the device flow measurements and may damage the device.The MKS DELTA III Flow Ratio Controller uses thermal sensors which add heat energy to the gas (and gas mixture) which may cause the gas to decompose and a mixture to react. Please consult MKS Applications Engineering if this is a concern for the intended application of the device.For channels with "0%" set points, a downstream shut-off valve is required to assure no flow through the channel.MKS products provided subject to the US Export Regulations. Export, re-export, diversion or transfer contrary to US law (and local country law) is prohibited. DELTA ™ is a trademark of MKS Instruments, Inc. or a subsidiary of MKS Instruments, Inc. All other trademarks cited herein are the property of their respective owners.DELTA III EtherCAT - 08/23©2023 MKS Instruments, Inc.Specifications are subject to change without notice.Ordering Code: DLT3B0BBB8R11Code ConfigurationModelDELTA III 3-Channel Flow Ratio Controller DLT3B DLT3BReserved Reserved00Channel Full Scale Flow Ranges3 channel 500 sccm 1000 sccm 2000 sccm 3000 sccm 5000 sccm 10000 sccmAll channels must be the same and are N 2 equivalent.AAA BBB CCC DDD EEE FFFBBBInterface Electronics EtherCAT 88Fittings4 VCR male, non-rotatable on inlet and outlet R RFirmwareFirmware Revision1111Dimensional DrawingNote: Unless otherwise specified, dimensions are nominal values in inches (mm referenced).。

海哥尔德电子产品简介说明书

APRIL 2013Quick-Refere nce GuideLAPTOP, DESKTO P AND VIDEO STORAGE DRIVESSeagate Partner Program MembersVisit the Sales Tools section to access the latestproduct roadmap, end-of-life schedule and product information. DistributorsEMEA SPP Support00-800-6890-8282US Sales Support1-800-SEAGATE or 1-405-324-4700Visit for more information or call 1-800-SEAGATE (1-800-732-4283) © 2013 Seagate Technology LLC. All rights reserved. Printed in USA. Seagate, Seagate Technology and the Wave logo are registered trademarks of Seagate Technology LLC in the United States and/or other countries. Barracuda, G-Force Protection, Momentus, Pipeline HD, SmartAlign and SV35 Series are either trademarks or registered trademarks of Seagate Technology LLC or one of its affiliated companies in the United States and/or other countries. The FIPS logo is a certification mark of NIST, which does not imply product endorsement by NIST, the U.S., or Canadian governments. All other trademarks or registered trademarks are the property of their respective owners. When referring to drive capacity, one gigabyte, or GB, equals one billion bytes and one terabyte, or TB, equals one trillion bytes. Your computer’s operating system may use a different standard of measurement and report a lower capacity. In addition, some of the listed capacity is used for formatting and other functions, and thus will not be available for data storage. Actual data rates may vary depending on operating environment and other factors. The export or re-export of hardware or software containing encryption may be regulated by the US Department of Commerce, Bureau of Industry and Security (for more information go to ). Seagate reserves the right to change, without notice, product offerings or specifications. QR502.15-1304GB, April 2013APRIL 2013Quick-Reference GuideLAPTOP, DESKTOP AND VIDEO STORAGE DRIVESNew Seagate Model Number KeyDesktop, laptop and video storageST 500 DX 001BRANdCAPACiTySegMeNTATTRiBuTeS2 letters ST= Seagate MX= Maxtor2 to 4 digits 80 = 80GB 500 = 500GB 1500 = 1,500GB Capacities>9,999GB: 10 = 10TB 15 = 15TB2 lettersDX = Desktop Premium DM = Mainstream DL = Entry LevelLX = Laptop Premium LM = Laptop Mainstream LT = Laptop Thin VX = Surveillance VM = DVR VT = DVR Thin3 digits, non-intelligent Varies for:Z-height Form Factor RPM Cache Interface SED, FIPS Drop Sensor Interface SpeedView a brief training presentation on how our model numbering format has changed at /seagate/ModelNumber 1 One gigabyte, or GB, equals one billion bytes; and one terabyte, or TB, equals one trillion bytes when referring to drive capacity.2See FIPS 140-2 Level 2 Certificate at /groups/STM/cmvp/documents/140-1/1401vend.htm.37mm z-height expanded to 9.5mm enables compatibility with standard laptop chassis.4Advanced Format 4K sector drive with SmartAlign ™ technology resolves misalignment conditions.5Seagate makes this drive in both 4K and 512-byte sectors. SmartAlign technology is included on 4K sector drives. Both drives are functionally and physically equivalent.6Formerly Barracuda ®drive。

铸钢铁中外牌号对照

序号

国别

铸铁牌号

1

中国

—

HT350

HT300

HT250

HT200

HT150

HT100

2

日本

—

FC350

FC300

FC250

FC200

FC150

FC100

3

美国

NO.60

NO.50

NO.45

NO.35

NO.30

NO.20

—

4

前苏联

CЧ40

CЧ35

CЧ30

CЧ25

CЧ20

CЧ15

CЧ10

FNG38-17

FNG42-12

FNG50-7

FNG60-2

FNG70-2

FNG80-2

—

23

奥地利

SG38

SG42

SG50

SG60

SG70

—

—

碳素铸钢和合金铸钢牌号近似对照

序号

中国

(GB)

日本

(JIS)

美国

前苏联

(TOCT)

德国

意大利

(UNI)

法国

(NF)

英国

(BS)

瑞典

(SS14)

国际标准

(ISO)

316C16

—

—

CN-7M

—

—

—

SCS14

13

—

SCS5

SCS6

—

—

—

G-X5CrNi13 4

1.4313

—

Z4CND13.4-M

425C11

—

—

—

—

—

—

MWIII说明书

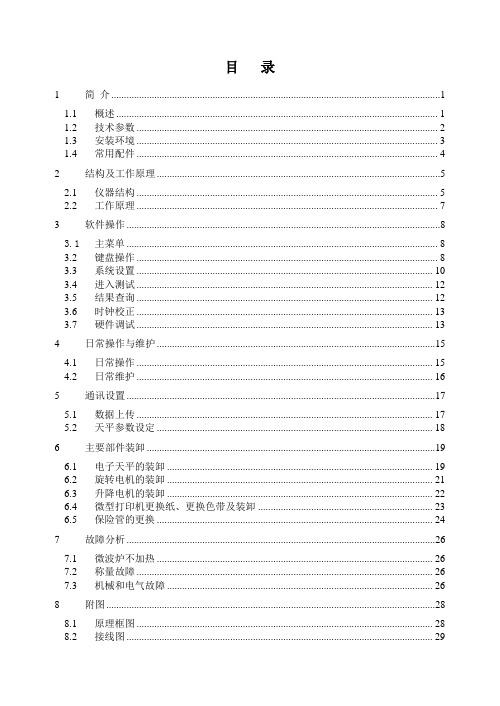

目录1 简介 (1)1.1 概述 (1)1.2 技术参数 (2)1.3 安装环境 (3)1.4 常用配件 (4)2 结构及工作原理 (5)2.1 仪器结构 (5)2.2 工作原理 (7)3 软件操作 (8)3.1主菜单 (8)3.2 键盘操作 (8)3.3 系统设置 (10)3.4 进入测试 (12)3.5 结果查询 (12)3.6 时钟校正 (13)3.7 硬件调试 (13)4 日常操作与维护 (15)4.1 日常操作 (15)4.2 日常维护 (16)5 通讯设置 (17)5.1 数据上传 (17)5.2 天平参数设定 (18)6 主要部件装卸 (19)6.1 电子天平的装卸 (19)6.2 旋转电机的装卸 (21)6.3 升降电机的装卸 (22)6.4 微型打印机更换纸、更换色带及装卸 (23)6.5 保险管的更换 (24)7 故障分析 (26)7.1 微波炉不加热 (26)7.2 称量故障 (26)7.3 机械和电气故障 (26)8 附图 (28)8.1 原理框图 (28)8.2 接线图 (29)长沙开元仪器有限公司 5E 微波水分测试仪11 简 介1.1 概述谢谢您购买我公司的5E 微波水分测试仪,为了确保您正确的操作和维护该仪器,请仔细阅读本说明书,若有疑问,请立即与我们的技术支持人员联系,我们会给您更详细的解答。

5E 微波水分测试仪用于测定煤和焦炭中的全水分和内水分。

该仪器具有微波和红外两种加热方式,用户可根据被测物质的性质选择适用的方法(见1.2)。

仪器内部集成了进口高精度电子天平,配合称量机构能自动完成测试过程,放样后再无需人工干预。

该仪器采用单片机控制和大屏幕液晶显示,能够存储1200个最新测试结果,能打印两种固定格式报告单,测试数据可上网。

该仪器与传统烘箱比较具有自动化程度高、测试速度快,功耗小等优点。

图1-1 仪器外形图本产品标准:Q/BABU014-2002本产品制造计量器具许可证号:湘制01000035-3号 本说明书版次:2006年5月第2版,本说明书的部分内容如“进入测试”菜单中选择坩埚编号,红外法中设定加热次数和加热时间,仅适用于单片机控制软件为V1.3以上版本的仪器。

三晶变频器S系列说明书大

1

S350系列

第一章 概 况

第一章 概 况电压范围:380V/220V±15% ◆输入频率范围:47~63Hz ◆输出电压范围:0~额定输入电压 ◆输出频率范围:0~600Hz ●外围接口特性 ◆可编程数字输入:6 路输入 ◆可编程模拟量输入:VI:0~10V输入,CI:0~20mA 输入 ◆开路集电极输出:1 路输出 ◆继电器输出:2 路输出(7.5kw以下 1 路输出,可扩展) ◆模拟量输出:2 路输出 FM 可选 0/4~20mA 或 0~10V,AM 0~10V(7.5kw以下只 有FM、AM需带扩展卡) ◆可编程高速脉冲HM1输入:1路输入0~50kHz ●技术性能特性 ◆控制方式:无 PG 矢量控制、V/F 控制、转矩控制 ◆过载能力:150% 额定电流 60s;180% 额定电流10s ◆启动转矩:无 PG 矢量控制:0.5Hz/%(SVC) ◆调速比:无 PG 矢量控制:1:100 ◆速度控制精度:无 PG 矢量控制:±0.5%最高速度 ◆载波频率:1.0k~15.0kHz ●功能特性 ◆频率设定方式:数字设定、模拟量设定、串行通讯设定、多段速、PID设定等。 ◆PID 控制功能 ◆多段速控制功能:16 段速控制 ◆摆频控制功能 ◆瞬时停电不停机功能 ◆自动电压调整功能:当电网电压变化时,能自动保持输出电压恒定 ◆提供多达 25 种故障保护功能:过流、过压、欠压、过温、缺相、过载等保护 功能。

在某些情况下,甚至在

中所述的内容也会导致重大的事故。所以在

任何情况下要遵守这些重要的注意事项。

★

为了确保正确的运行而采取的步骤。

警告标记呈现在变频器的 上。 使用变频器时要遵守这些指导。

WARNING

Read the user manual before operation. Risk of electrical shock.Wait 10 minutes after removing power before servicing. Do not connect AC power to output terminals U/T1,V/T2 and W/T3.

G3CN-DX03P-US中文资料

Solid-state Relay G3CN PCB-mounting SSR for FA EquipmentRequiring High Reliability Array Wide I/O voltage range: 3 to 28 VDC input and 75 to264 VAC output or 3 to 28 VDC input and 3 to52.8 VDC output.Two load currents available: 2 A and 3 AFlat and vertical models available for a variety ofapplications.Approved by UL and CSA.*V ertical models.**When ordering, specify the input voltage171RatingsInputNote:The input impedance is measured at the maximum value of the operating voltage. For example, with the model rated at 4 to 24 VDC, the input impedance is measured at 28 VDC.OutputCharacteristics172173Load Current vs. Ambient Temperature CharacteristicsG3CN-202P(1)/-202PL(1)/-DX02P(1)-USAmbient temperature (°C)L o a d c u r r e n t (A )G3CN-203P(1)/-203PL(1)/-DX03P(1)-USL o a d c u r r e n t (A )Ambient temperature (°C)G3CN-203P(1)/-203PL(1)-US G3CN-DX02P(1)-USI n r u s h c u r r e n t (A . P e a k )Energizing time (ms)I n r u s h c u r r e n t (A . P e a k )Energizing time (ms)Inrush Current ResistivityNon-repetitive (Keep the inrush current to half the rated value if it occurs repetitively .)G3CN-202P(1)/-202PL(1)-USG3CN-DX03P(1)-USI n r u s h c u r r e n t (A . P e a k )I n r u s h c u r r e n t (A . P e a k )Energizing time (ms)Energizing time (ms)174T erminal Arrangement/Internal Connections (Bottom View)Flat ModelG3CN-20j P/-20j PL/-DX0j PVertical ModelG3CN-20j P1/-20j PL1/-DX0j P1Note:Values in parentheses apply to the DC-load versions.Note:Values in parentheses apply to the DC-load versions.0.433 max.25 max.14.5max.20 max. 1.5 max.25±0.512.5±0.510±0.50.70.70.70.433 max.14 max.26.5 max.32 max.1.5 max.27.5±0.5(17.5)5±0.53±1Four 1.2-dia.holes2512.55(17.5)527.5Two, 2-dia.holesTwo, 4 dia.holesTwo, 2-dia.holesFour 1.2-dia.holesPatternPattern10Terminal Arrangement/Mounting Holes (Bottom View)T erminal Arrangement/Internal Connections (Bottom View)T erminal Arrangement/Mounting Holes (Bottom View)5±0.5175ConnectionWith the SSR for DC switching, the load can be connected to either positive or negative output terminal of the SSR.Protective ComponentSince the SSR does not incorporate an overvoltage absorption component, be sure to connect an overvoltage absorption compo -nent when using the SSR under an inductive load.ALL DIMENSIONS SHOWN ARE IN MILLIMETERS.To convert millimeters into inches, multiply by 0.03937. T o convert grams into ounces, multiply by 0.03527.Cat. No. K063-E1-2A。

三星电子 sirius 3RP25 时间间隔电子延迟时间电源控制器说明书

三星W3(S42AX-YD05)屏电源工作原理

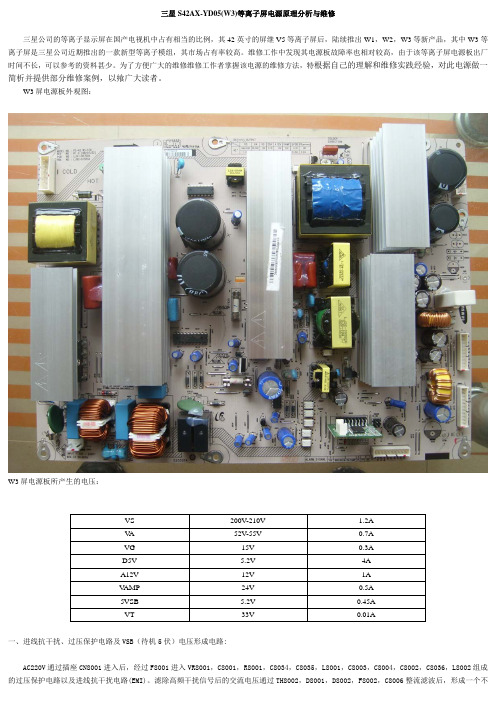

三星S42AX-YD05(W3)等离子屏电源原理分析与维修三星公司的等离子显示屏在国产电视机中占有相当的比例,其42英寸的屏继V5等离子屏后,陆续推出W1,W2,W3等新产品,其中W3等离子屏是三星公司近期推出的一款新型等离子模组,其市场占有率较高。

维修工作中发现其电源板故障率也相对较高,由于该等离子屏电源板出厂时间不长,可以参考的资料甚少。

为了方便广大的维修维修工作者掌握该电源的维修方法,特根据自己的理解和维修实践经验,对此电源做一简析并提供部分维修案例,以飨广大读者。

W3屏电源板外观图:W3屏电源板所产生的电压:VS 200V-210V 1.2AV A 52V-55V 0.7AVG 15V 0.3AD5V 5.2V 4AA12V 12V 1AV AMP 24V 0.5A5VSB 5.2V 0.45AVT 33V 0.01A 一、进线抗干扰、过压保护电路及VSB(待机5伏)电压形成电路:AC220V通过插座CN8001进入后,经过F8001进入VR8001,C8001,R8001,C8034,C8035,L8001,C8003,C8004,C8002,C8036,L8002组成的过压保护电路以及进线抗干扰电路(EMI)。

滤除高频干扰信号后的交流电压通过TH8002,D8001,D8002,F8002,C8006整流滤波后,形成一个不稳定的300V直流电压。

该电压经过T8001初级绕组加到U8001(VIPER22A)的第5,6,7,8脚。

U8001进入工作状态。

从T8001次级产生感生电压经过D8005,C8032整流滤波,ZD8001稳压后给U8001提供一个稳定的工作电压,该绕组同时经过D8008,C8021整流滤波后为Q8001(A1281)提供一个待命电压。

此时Q8001处于截止状态。

从T8001另一次级绕组产生的感生电压经过D8006,C8013,C8033整流滤波后形成5VSB电压。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。