103SR12A-7中文资料

SD103CW-7中文资料

SD103AW - SD103CWSCHOTTKY BARRIER DIODEFeatures• Low Forward Voltage Drop• Guard Ring Construction for Transient Protection• Lead, Halogen and Antimony Free, RoHSCompliant "Green" Device (Notes 3 and 4)Mechanical Data• Case: SOD-123• Case Material: Molded Plastic. UL FlammabilityClassification Rating 94V-0• Moisture Sensitivity: Level 1 per J-STD-020D• Leads: Solderable per MIL-STD-202, Method 208• Lead Free Plating (Matte Tin Finish annealed overAlloy 42 leadframe)• Polarity: Cathode Band• Marking: Date Code and Type Code, See Page 3• Type Codes: SD103AW S4SD103BW S5 or S4SD103CW S6 or S5 or S4• Ordering Information: See Page 3• Weight: 0.01 grams (approximate)Maximum Ratings@T A = 25°C unless otherwise specifiedCharacteristic Symbol SD103AW SD103BW SD103CW UnitPeak Repetitive Reverse Voltage Working Peak Reverse Voltage DC Blocking Voltage V RRMV RWMV R40 30 20 VRMS Reverse Voltage V R(RMS)28 21 14 V Forward Continuous Current (Note 1) I FM350 mA Non-Repetitive Peak Forward Surge Current @ t ≤ 1.0s I FSM 1.5 A Power Dissipation (Note 1) P D400 mW Thermal Resistance, Junction to Ambient Air (Note 1) RθJA300 °C/W Operating and Storage Temperature Range T J, T STG-65 to +125 °CElectrical Characteristics@T A = 25°C unless otherwise specifiedCharacteristic Symbol Min Typ Max Unit Test Condition Reverse Breakdown Voltage (Note 2) SD103AWSD103BW SD103CW V(BR)R403020⎯⎯V I R = 100μAForward Voltage Drop V FM⎯⎯0.370.60VI F = 20mAI F = 200mAPeak Reverse Current (Note 2) SD103AWSD103BW SD103CW I RM⎯⎯ 5.0 μAV R = 30VV R = 20VV R = 10VTotal Capacitance C T⎯28 ⎯pF V R = 0V, f = 1.0MHzReverse Recovery Time t rr⎯10 ⎯ns I F = I R = 200mA,I rr = 0.1 x I R, R L = 100ΩNotes: 1. Part mounted on FR-4 board with recommended pad layout, which can be found on our website at /datasheets/ap02001.pdf.2. Short duration test pulse used to minimize self-heating effect.3. No purposefully added lead. Halogen and Antimony Free.4. Product manufactured with Data Code V9 (week 33, 2008) and newer are built with Green Molding Compound. Product manufactured prior to Date CodeV9 are built with Non-Green Molding Compound and may contain Halogens or Sb2O3 Fire Retardants.Please click here to visit our online spice models database.0.010.110.0010.00018006004002001,000I ,I N S T A N T A N E O U S F O R W A R D C U R R E N T (A )F V , INSTANTANEOUS FORWARD VOLTAGE (mV)Fig. 2 Typical Forward Characteristics F0100200500255075125150P , P O W E R D I S S I P A T I O N (m W )d T , AMBIENT TEMPERATURE (°C)Fig.1 Power Derating CurveA 100300400PERCENT OF RATED PEAK REVERSE VOLTAGE (%)Fig. 4 Typ. Total Capacitance vs. Reverse Voltage C , TO T A L C A P A C I T A N C E (p F )T0.010.11101001,000257550PERCENT OF RATED PEAK REVERSE VOLTAGE (%)Fig. 3 Typical Reverse Characteristics 100Ordering Information (Note 5)Device Packaging ShippingSD103AW-7-F SOD-123 3000/Tape and Reel SD103BW-7-F SOD-123 3000/Tape and Reel SD103CW-7-F SOD-123 3000/Tape and Reel SD103CW-13-FSOD-12310,000/Tape and ReelNotes:5. For packaging details, go to our website at /datasheets/ap02007.pdf.Marking InformationXX = Product Type Marking Code, See Page 1YM = Date Code Marking Y = Year (ex: T = 2006)M = Month (ex: 9 = September)XXY MDate Code KeyYear 19981999 2000 2001 2002 2003 2004 2005 2006 2007 2008 2009 2010 2011 2012CodeJ K LM N P R ST U V W X Y ZMonth Jan Feb Mar Apr May Jun Jul Aug Sep Oct Nov Dec Code 123456789ONDIMPORTANT NOTICEDiodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to any product herein. Diodes Incorporated does not assume any liability arising out of the application or use of any product described herein; neither does it convey any license under its patent rights, nor the rights of others. The user of products in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on our website, harmless against all damages.LIFE SUPPORTDiodes Incorporated products are not authorized for use as critical components in life support devices or systems without the expressed written approval of the President of Diodes Incorporated.。

Converge SR 1212A数字矩阵混音器与四通道电源放大器数据资料说明书

Converge TM|SR 1212ADigital Matrix Mixer with Four Channel Power AmplifierConverge Pro DATA SHeeT <THE ULTIMATE IN AUDIO PROCESSING AND DIGITAL MATRIX MIXING APPLICATIonSBoardroomsTraining CentersMunicipal RoomsCourtroomsHouses of WorshipTelemedicinePresentation SystemsZoned PagingMasking SystemsADvAnTAgeSAdvanced Feature SetManagement Improvements+Integrated Ethernet and USB connections>SNMP and HTML remote management agents>Event scheduler>Diagnostic console>Simplified Configuration Software+Drag & drop A/V and channel objects>Selectable views -- unit, matrix, channel>Expanded serial command set+Superior Audio PerformanceDARE™ (Dynamic Automatic Resonance Elimination) for control of feedback+Unique automatic mixing process delivers optimum intelligibility+20 Hz-22 kHz bandwidth for full-range audio response+ALC & AGC keep participants’ audio balanced and consistent+Advanced Digital Processing on each amplifier channel+Configuration FlexibilityFour built-in 35 Watt amplifiers, 8Ω or 70V/100V+Up to 96 microphones+Link multiple Converge/Converge Pro units (Converge Pro 880, 880T, 880TA, 840T, 8i, TH20,+Converge SR 1212 and SR 1212A) for extensive microphone coverage and up to 16 phonelinesEnhanced expansion bus, featuring 18 mix-minus audio buses for routing between units+Ten mic gating groups (four internal & six global) allow separation of mics into individual+mixer gating groups for greater configuration flexibility32 presets can be executed on-the-fly without disturbing other ongoing preset operations+255 Macros for customized audio control/configuration with single command execution+No space required between rack mounted units+NEw!Audio PerformanceConditions: Unless otherwise specified,all measurements are performedfrom 20 Hz to 22 kHz Bw limit (no weighting)Frequency Response: 20 Hz to 22 kHz+/- 1 dBNoise (EIN): -126 dBu, 20 kHz Bw,max gainRs= 150ΩTHD+ Noise: <0.02%Dynamic Range: >105 dB (non A weighted)Crosstalk: <-91 dB re 20 dBu full band. Mic/Line Inputs 1-8Push-on mini-terminal block, balanced, bridgingImpedance: > 5 KΩNominal Level: adjustable -56 dBu to 0 dBu (7dB step coarse gain adjustment) Maximum Level: -65 to +20 dBu Phantom Power: 24V, selectableLine Inputs 9-12Push-on mini-terminal block, balanced, bridgingImpedance: > 5 KΩNominal Level: 0 dBuMaximum Level: 20 dBuoutput 1-8Push-on mini-terminal block, balanced, bridgingImpedance: < 50ΩNominal Level: 0 dBuMaximum Level: 20 dBuAuto Mixer ParametersNumber of Open Microphones (NOM)PA Adaptive ModeFirst Mic Priority ModeMaximum # of MicsAmbient LevelGate Threshold AdjustOff Attenuation AdjustHold TimeDecay RateChairman Override96 T otal Microphones per site6- Global Gating Groups4- Internal Gating Groups Matrix Mixing Parameters8- Microphone Analog Inputs4- Analog Line Inputs8- Analog Line Outputs4- Power Amplifier Outputs18- Expansion Bus in/out8- Assignable Processing Blocks in/outAssignable Processing BlocksFiltersAll PassLow PassHigh PassLow shelvingHigh shelvingPEQNotchCrossoversCD HornCompressorDelay: adjustable up to 250 msPower Amplifier output ProcessingFeedBack Elimination w/ring cancellation10-band EQ filter4-node filter bank for CrossoverDelay BlockCompressor/LimiterNoise Gate for Hiss ControlSound Masking Generator per channelAdaptive Volume ControlMulti Channel ControlMicrophone Processing4-node filter bankAGC/ALCPower AmplifiersChannels: 4Amplifier Output: 4x35 Watts into 8ΩImpedance: Selectable 8Ω, 70V, 100VTHD + Noise: <0.2% (1/3 Power)Crosstalk: <-68 dBexpansion BusConnection: CAT 5, RJ45Mix Minus Structure18 Audio Buses6 Gating Buses8 Reference Busesnetwork10/100 Auto Switching (PC andNetwork Port)HTTP ServerT elnet ClientSNMP AgentSMTP ClientDNSDHCPrS-232DB-99.6k – 115k baud8/1/0Hardware Flow ControlUSBVersion 2.0 compatibleT ype: B-connectorgPIoDB 25 female (A/B)Inputs: Active LowOutputs: Open Collector, 40Vdc, 40 mAPower100-240VAC; 50/60 Hz,300 watts (maximum)Idle: 139 BTU/hrFull Load: 779 BTU/hrEfficiency: >80%Humidity15 to 80%MechanicalDimensions: 2RU3.5” H x 17.25” w x 15.92” Dweight: < 30 lbs.environmentalOperating temperature:32-122 degrees FComplianceFCCIndustry CanadaCERoHSClass 2 wiring RequiredPart number910-151-901 Converge SR 1212ACONVERGE PRO SR 1212A DATA SHeeT <> Converge Pro Sr 1212A BACK PAneL > SPeCIFICATIonS> CLeArone LoCATIonSHeadquarters:Salt Lake City, UT USA 5225 wiley Post way Suite 500Salt Lake City, UT 84116 Tel: 801-975-7200T oll Free: 800-945-7730 Fax: 801-977-0087******************Latin AmericaTel: 801-974-3621*******************EMEATel: 44 (0) 1189 036 053*******************APACTel: 801-303-3388*******************Other product names may be registered trademarks of their respective owners who do not necessarily endorse ClearOne or ClearOne’s products. All rights reserved. Information in this document subject to change without notice.© ClearOne. 802-151-901-DS Revision 1.9。

STM8S103中文资料

10 电气特性 .................................................................................................................32

10.1 参数条件............................................................................................................................32 10.1.1 最小和最大值 .............................................................................................................32 10.1.2 典型数值 ....................................................................................................................32 10.1.3 典型曲线 ....................................................................................................................32 10.1.4 负载电容 ....................................................................................................................32 10.1.5 引脚输入电压 .............................................................................................................32

AD8130ARM-REEL7中文资料

Low Cost 270 MHzDifferential Receiver AmplifiersAD8129/AD8130Rev. CInformation furnished by Analog Devices is believed to be accurate and reliable. However , no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners.One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 781.329.4700 Fax: 781.461.3113 © 2005 Analog Devices, Inc. All rights reserved.FEATURESHigh speedAD8130: 270 MHz, 1090 V/μs @ G = +1 AD8129: 200 MHz, 1060 V/μs @ G = +10 High CMRR94 dB min, dc to 100 kHz 80 dB min @ 2 MHz 70 dB @ 10 MHzHigh input impedance: 1 MΩ differential Input common-mode range ±10.5 V Low noiseAD8130: 12.5 nV/√Hz AD8129: 4.5 nV/√HzLow distortion, 1 V p-p @ 5 MHzAD8130, −79 dBc worst harmonic @ 5 MHz AD8129, −74 dBc worst harmonic @ 5 MHz User-adjustable gainNo external components for G = +1 Power supply range +4.5 V to ±12.6 V Power-downAPPLICATIONSHigh speed differential line receivers Differential-to-single-ended converters High speed instrumentation amps Level shiftingCONNECTION DIAGRAM–IN +V S OUT FB02464-001Figure 1.The AD8129/AD8130 are differential-to-single-ended amplifiers with extremely high CMRR at high frequency. Therefore, they can also be effectively used as high speed instrumentation amps or for converting differential signals to single-ended signals. The AD8129 is a low noise, high gain (10 or greater) version intended for applications over very long cables, where signal attenuation is significant. The AD8130 is stable at a gain of 1 and can be used for applications where lower gains are required. Both have user-adjustable gain to help compensate for losses in the transmission line. The gain is set by the ratio of two resistor values. The AD8129/AD8130 have very high input impedance on both inputs, regardless of the gain setting.GENERAL DESCRIPTIONThe AD8129/AD8130 are designed as receivers for thetransmission of high speed signals over twisted-pair cables to work with the AD8131 or AD8132 drivers. Either can be used for analog or digital video signals and for high speed data transmission.1201101009080706050403010k100k1M10M100MFREQUENCY (Hz)C M R R (d B )02464-002Figure 2. AD8129 CMRR vs. FrequencyThe AD8129/AD8130 have excellent common-mode rejection (70 dB @ 10 MHz), allowing the use of low cost, unshielded twisted-pair cables without fear of corruption by external noise sources or crosstalk. The AD8129/AD8130 have a wide power supply range from single +5 V to ±12 V , allowing wide common-mode and differential-mode voltage ranges while maintaining signal integrity. The wide common-mode voltage range enables the driver-receiver pair to operate without isolation transformers in many systems where the ground potential difference between drive and receive locations is many volts. The AD8129/AD8130 have considerable cost and performance improvements over op amps and other multiamplifier receiving solutions.OUTV OUT =V IN [1+(R F /R G )]02464-003Figure 3. Typical Connection ConfigurationAD8129/AD8130Rev. C | Page 2 of 40TABLE OF CONTENTSFeatures..............................................................................................1 Applications.......................................................................................1 Connection Diagram.......................................................................1 General Description.........................................................................1 Revision History...............................................................................2 AD8129/AD8130 Specifications.....................................................3 5 V Specifications.........................................................................3 ±5 V Specifications.......................................................................5 ±12 V Specifications.....................................................................7 Absolute Maximum Ratings............................................................9 Thermal Resistance......................................................................9 ESD Caution..................................................................................9 Typical Performance Characteristics...........................................10 AD8130 Frequency Response Characteristics........................10 AD8129 Frequency Response Characteristics........................13 AD8130 Harmonic Distortion Characteristics......................16 AD8129 Harmonic Distortion Characteristics......................18 AD8130 Transient Response Characteristics..........................23 AD8129 Transient Response Characteristics..........................26 Theory of Operation......................................................................32 Op Amp Configuration.............................................................32 Applications.....................................................................................33 Basic Gain Circuits.....................................................................33 Twisted-Pair Cable, Composite Video Receiver withEqualization Using an AD8130...................................................33 Output Offset/Level Translator................................................34 Resistorless Gain of 2.................................................................35 Summer.......................................................................................35 Cable-Tap Amplifier..................................................................35 Power-Down...............................................................................36 Extreme Operating Conditions................................................36 Power Dissipation.......................................................................37 Layout, Grounding, and Bypassing..........................................38 Outline Dimensions.......................................................................39 Ordering Guide.. (40)REVISION HISTORY11/05—Rev. B to Rev. CChanges to 5 V Specifications.........................................................3 Changes to Table 4 and Maximum Power Dissipation Section..9 Changes to Figure 16......................................................................11 Changes to Figure 17. (12)9/05—Rev. A to Rev. BExtended Temperature Range...........................................Universal Deleted Figure 5................................................................................5 Added Thermal Resistance Section...............................................9 Updated Outline Dimensions.......................................................39 Changes to Ordering Guide..........................................................40 3/05—Rev. 0 to Rev. AChanges to Specifications.................................................................2 Replaced Figure 3..............................................................................5 Changes to Ordering Guide.............................................................6 Updated Outline Dimensions.......................................................27 Revision 0: Initial VersionAD8129/AD8130Rev. C | Page 3 of 40AD8129/AD8130 SPECIFICATIONS5 V SPECIFICATIONSAD8129 G = +10, AD8130 G = +1, T A = 25°C, +V S = 5 V , −V S = 0 V , REF = 2.5 V , PD ≥ V IH , R L = 1 kΩ, C L = 2 pF, unless otherwise noted. T MIN to T MAX = −40°C to +125°C, unless otherwise noted. Table 1.Model AD8129 AD8130 Parameter Conditions Min Typ Max Min Typ Max Unit DYNAMIC PERFORMANCE −3 dB Bandwidth V OUT ≤ 0.3 V p-p 160 185 220 250 MHz V OUT = 1 V p-p 160 185 180 205 MHzBandwidth for 0.1 dB Flatness V OUT ≤ 0.3 V p-p,SOIC/MSOP 25/40 25 MHz Slew Rate V OUT = 2 V p-p, 25%to 75%810 930 810 930 V/μs Settling Time V OUT = 2 V p-p, 0.1% 20 20 nsRise and Fall Times V OUT ≤ 1 V p-p, 10%to 90%1.8 1.5 ns Output Overdrive Recovery 20 30 ns NOISE/DISTORTIONSecond Harmonic/ThirdHarmonic V OUT = 1 V p-p, 5 MHz −68/−75 −72/−79 dBc V OUT = 2 V p-p, 5 MHz −62/−64 −65/−71 dBc V OUT = 1 V p-p, 10 MHz −63/−70 −60/−62 dBc V OUT = 2 V p-p, 10 MHz −56/−58 −68/−68 dBc IMD V OUT = 2 V p-p, 10 MHz −67 −70 dBc Output IP3 V OUT = 2 V p-p, 10 MHz 25 26 dBm Input Voltage Noise (RTI) f ≥ 10 kHz 4.5 12.3 nV/√Hz Input Current Noise (+IN, −IN) f ≥ 100 kHz 1 1 pA/√HzInput Current Noise(REF, FB)f ≥ 100 kHz 1.4 1.4 pA/√Hz Differential Gain Error AD8130, G = +2, NTSC 100 IRE, R L ≥ 150 Ω0.30.13 % Differential Phase Error AD8130, G = +2, NTSC 100 IRE, R L ≥ 150 Ω0.10.15 Degrees INPUT CHARACTERISTICSCommon-Mode Rejection Ratio DC to 100 kHz,V CM = 1.5 V to 3.5 V 86 96 86 96 dB V CM = 1 V p-p @ 1 MHz 80 80 dB V CM = 1 V p-p @ 10 MHz 70 70 dB CMRR with V OUT = 1 V p-p V CM = 1 V p-p @ 1 kHz, V OUT = ±0.5 V dc8072 dB Common-Mode Voltage Range V +IN − V −IN = 0 V 1.25 to 3.7 1.25 to3.8 V Differential Operating Range ±0.5 ±2.5 V Differential Clipping Level ±0.6 ±0.75 ±0.85 ±2.3 ±2.8 ±3.3 V Resistance Differential 1 6 MΩ Common mode 4 4 MΩ Capacitance Differential 3 3 pF Common mode 4 4 pFAD8129/AD8130Rev. C | Page 4 of 40AD8129/AD8130Rev. C | Page 5 of 40±5 V SPECIFICATIONSAD8129 G = +10, AD8130 G = +1, T A = 25°C, V S = ±5 V , REF = 0 V , PD ≥ V IH , R L = 1 kΩ, C L = 2 pF, unless otherwise noted. T MIN to T MAX = −40°C to +125°C, unless otherwise noted. Table 2.AD8129 AD8130 Parameter Conditions Min Typ Max Min Typ Max Unit DYNAMIC PERFORMANCE −3 dB Bandwidth V OUT ≤ 0.3 V p-p 175 200 240 270 MHz V OUT = 2 V p-p 170 190 140 155 MHzBandwidth for 0.1 dB Flatness V OUT ≤ 0.3 V p-p,SOIC/MSOP 30/50 45 MHz Slew Rate V OUT = 2 V p-p,25% to 75%925 1060 950 1090 V/μs Settling Time V OUT = 2 V p-p, 0.1% 20 20 nsRise and Fall Times V OUT ≤ 1 V p-p,10% to 90%1.7 1.4 ns Output Overdrive Recovery 30 40 ns NOISE/DISTORTIONSecond Harmonic/ThirdHarmonic V OUT = 1 V p-p, 5 MHz −74/−84 −79/−86 dBc V OUT = 2 V p-p, 5 MHz −68/−74 −74/−81 dBc V OUT = 1 V p-p, 10 MHz −67/−81 −74/−80 dBc V OUT = 1 V p-p, 10 MHz −61/−70 −74/−76 dBc IMD V OUT = 2 V p-p, 10 MHz −67 −70 dBc Output IP3 V OUT = 2 V p-p, 10 MHz 25 26 dBm Input Voltage Noise (RTI) f ≥ 10 kHz 4.5 12.5 nV/√HzInput Current Noise(+IN, −IN)f ≥ 100 kHz 1 1 pA/√Hz Input Current Noise(REF, FB)f ≥ 100 kHz 1.4 1.4 pA/√Hz Differential Gain Error AD8130, G = +2, NTSC200 IRE, R L ≥ 150 Ω0.3 0.13 % Differential Phase Error AD8130, G = +2, NTSC200 IRE, R L ≥ 150 Ω0.1 0.15 Degrees INPUT CHARACTERISTICSCommon-Mode Rejection Ratio DC to 100 kHz,V CM = −3 V to +3.5 V 94 110 90 110 dB V CM = 1 V p-p @ 2 MHz 80 80 dB V CM = 1 V p-p @ 10 MHz 70 70 dB CMRR with V OUT = 1 V p-p V CM = 2 V p-p @ 1 kHz,V OUT = ±0.5 V dc100 83 dB Common-Mode VoltageRangeV +IN − V −IN = 0 V ±3.5 ±3.8 V Differential OperatingRange±0.5 ±2.5 V Differential Clipping Level ±0.6 ±0.75 ±0.85 ±2.3 ±2.8 ±3.3 V Resistance Differential 1 6 MΩ Common mode 4 4 MΩ Capacitance Differential 3 3 pF Common mode 4 4 pFAD8129/AD8130Rev. C | Page 6 of 40AD8129/AD8130Rev. C | Page 7 of 40±12 V SPECIFICATIONSAD8129 G = +10, AD8130 G = +1, T A = 25°C, V S = ±12 V , REF = 0 V , PD ≥ V IH , R L = 1 kΩ, C L = 2 pF, unless otherwise noted. T MIN to T MAX = −40°C to +85°C, unless otherwise noted. Table 3.AD8129 AD8130 Parameter Conditions Min Typ Max Min Typ Max Unit DYNAMIC PERFORMANCE −3 dB Bandwidth V OUT ≤ 0.3 V p-p 175 200 250 290 MHz V OUT = 2 V p-p 170 195 150 175 MHz Bandwidth for 0.1 dB Flatness V OUT ≤ 0.3 V p-p, SOIC/MSOP50/70 110 MHzSlew Rate V OUT = 2 V p-p, 25%to 75%935 1070 960 1100 V/μs Settling Time V OUT = 2 V p-p, 0.1% 20 20 nsRise and Fall Times V OUT ≤ 1 V p-p, 10%to 90%1.7 1.4 ns Output Overdrive Recovery 40 40 ns NOISE/DISTORTIONSecond Harmonic/ThirdHarmonic V OUT = 1 V p-p, 5 MHz −71/−84 −79/−86 dBc V OUT = 2 V p-p, 5 MHz −65/−74 −74/−81 dBc V OUT = 1 V p-p, 10 MHz −65/−82 −74/−80 dBc V OUT = 2 V p-p, 10 MHz −59/−70 −74/−74 dBc IMD V OUT = 2 V p-p, 10 MHz −67 −70 dBc Output IP3 V OUT = 2 V p-p, 10 MHz 25 26 dBm Input Voltage Noise (RTI) f ≥ 10 kHz 4.6 13 nV/√HzInput Current Noise(+IN, −IN)f ≥ 100 kHz 1 1 pA/√Hz Input Current Noise(REF, FB)f ≥ 100 kHz 1.4 1.4 pA/√Hz Differential Gain Error AD8130, G = +2, NTSC 200 IRE, R L ≥ 150 Ω0.30.13 % Differential Phase Error AD8130, G = +2, NTSC 200 IRE, R L ≥ 150 Ω0.10.2 Degrees INPUT CHARACTERISTICSCommon-Mode Rejection Ratio DC to 100 kHz,V CM = ±10 V 92 105 88 105 dB V CM = 1 V p-p @ 2 MHz 80 80 dB V CM = 1 V p-p @ 10 MHz 70 70 dB CMRR with V OUT = 1 V p-p V CM = 4 V p-p @ 1 kHz,V OUT = ±0.5 V dc93 80 dB Common-Mode VoltageRangeV +IN − V –IN = 0 V ±10.3 ±10.5 V Differential Operating Range ±0.5 ±2.5 V Differential Clipping Level ±0.6 ±0.75 ±0.85 ±2.3 ±2.8 ±3.3 V Resistance Differential 1 6 MΩ Common mode 4 4 MΩ Capacitance Differential 3 3 pF Common mode 4 4 pFAD8129/AD8130Rev. C | Page 8 of 40AD8129/AD8130Rev. C | Page 9 of 40ABSOLUTE MAXIMUM RATINGSTable 4.Parameter Rating Supply Voltage 26.4 V Power Dissipation Refer to Figure 4Input Voltage (Any Input) −V S − 0.3 V to +V S + 0.3 V Differential Input Voltage (AD8129) V S ≥ ±11.5 V ±0.5 V Differential Input Voltage (AD8129) V S < ±11.5 V ±6.2 V Differential Input Voltage (AD8130) ±8.4 VStorage Temperature Range −65°C to +150°CLead Temperature (Soldering, 10 sec) 300°CJunction Temperature 150°CStresses above those listed under Absolute Maximum Ratingsmay cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operationalsection of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.THERMAL RESISTANCEθJA is specified for the worst-case conditions, that is, θJA isspecified for the device soldered in a circuit board in still air. Table 5. Thermal ResistancePackage TypeθJA Unit 8-Lead SOIC/4-Layer 121 °C/W 8-Lead MSOP/4-Layer142 °C/WMaximum Power DissipationThe maximum safe power dissipation in the AD8129/AD8130 packages is limited by the associated rise in junction temp-erature (T J ) on the die. At approximately 150°C, which is the glass transition temperature, the plastic changes its properties. Even temporarily exceeding this temperature limit can change the stresses that the package exerts on the die, permanently shifting the parametric performance of the AD8129/AD8130. Exceeding a junction temperature of 150°C for an extended period can result in changes in the silicon devices, potentially causing failure. The power dissipated in the package (P D ) is the sum of thequiescent power dissipation and the power dissipated in the package due to the load drive. The quiescent power is the voltage between the supply pins (V S ) times the quiescent current (I S ). The power dissipated due to the load drive depends upon the particular application. The power due to load drive is calculated by multiplying the load current by the associated voltage drop across the device. RMS voltages and currents must be used in these calculations. Airflow reduces θJA . In addition, more metal directly in contact with the package leads from metal traces through holes, ground, and power planes reduces the θJA . Figure 4 shows the maximum safe power dissipation in the package vs. the ambient temperature for the 8-lead SOIC(121°C/W) and MSOP (θJA = 142°C/W) packages on a JEDEC standard 4-layer board. θJA values are approximations.AMBIENT TEMPERATURE (°C)M A X I M U M P O W ER D I S S I P A T I O N (W )1.751.501.001.250.500.250.7502464-005Figure 4. Maximum Power Dissipation vs. TemperatureESD CAUTIONESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performancedegradation or loss of functionality.AD8129/AD8130Rev. C | Page 10 of 40TYPICAL PERFORMANCE CHARACTERISTICSAD8130 FREQUENCY RESPONSE CHARACTERISTICSG = +1, R L = 1 kΩ, C L = 2 pF, V OUT = 0.3 V p-p, T A = 25°C, unless otherwise noted.G A I N (d B )30–3–4–5–6–7–2–112FREQUENCY (MHz)11010040002464-006Figure 5. AD8130 Frequency Response vs. Supply, V OUT = 0.3 V p-pFREQUENCY (MHz)G A I N (d B )31–3–4–5–6–7–2–1121010030002464-007Figure 6. AD8130 Frequency Response vs. Supply, V OUT = 1 V p-pFREQUENCY (MHz)G A I N (d B )1–3–4–5–6–7–2–110100300301202464-008Figure 7. AD8130 Frequency Response vs. Supply, V OUT = 2 V p-pFREQUENCY (MHz)G A I N (d B )6130–1–2–3–412451010030002464-009Figure 8. AD8130 Frequency Response vs. Load CapacitanceFREQUENCY (MHz)G A I N (d B )0.710.40.10–0.1–0.2–0.30.20.30.50.610100300Figure 9. AD8130 Fine Scale Response vs. Supply, R L = 1 kΩFREQUENCY (MHz)G A I N (d B )0.510.2–0.1–0.2–0.3–0.4–0.500.10.30.41010030002464-011Figure 10. AD8130 Fine Scale Response vs. Supply, R L = 150 ΩAD8129/AD8130FREQUENCY (MHz)G A I N (d B )3–3–4–5–6–7–2–11202464-012Figure 11. AD8130 Frequency Response vs. Supply, R L = 150 ΩFREQUENCY (MHz)G A I N (d B )31–3–4–5–6–7–2–11210100300Figure 12. AD8130 Frequency Response vs. Supply,G = +2, V OUT = 0.3 V p-pFREQUENCY (MHz)G A I N (d B)31–3–4–5–6–7–2–1121010030002464-014Figure 13. AD8130 Frequency Response vs. Supply,G = +2, V OUT = 2 V p-p FREQUENCY (MHz)G A I N (d B )310–3–4–5–6–7–2–1121010030002464-015Figure 14. AD8130 Frequency Response for Various R F /R GFREQUENCY (MHz)G A I N (dB )0.31101000–0.3–0.4–0.5–0.6–0.7–0.2–0.10.10.2Figure 15. AD8130 Fine Scale Response vs. Supply,G = +2, R L = 1 kΩFREQUENCY (MHz)G A I N (d B )0.31100–0.3–0.4–0.5–0.6–0.7–0.2–0.10.10.210002464-017Figure 16. AD8130 Fine Scale Response vs. Supply,G = +2, R L = 150 ΩAD8129/AD8130FREQUENCY (MHz)G A I N (d B )3130010100–3–4–5–6–7–2–11202464-018FREQUENCY (MHz)G A I N (d B )31101000–3–4–5–6–7–2–1120.102464-021Figure 17. AD8130 Frequency Response vs. Supply,G = +2, R L = 150 ΩFigure 20. AD8130 Frequency Response vs. Supply,G = +5, G = +10, R L = 150 ΩFREQUENCY (MHz)G A I N (d B )0.30.1–0.3–0.4–0.5–0.6–0.7–0.2–0.10.10.2110FREQUENCY (MHz)O U T P U T V O L T A G E (dB V )121060–6–12–18–24–30–36–42–481004003002464-019Figure 18. AD8130 Fine Scale Response vs. Supply,G = +5, G = +10, V OUT = 2 V p-pFigure 21. AD8130 Frequency Response for Various Output LevelsFREQUENCY (MHz)G A I N (d B )31101000–3–4–5–6–7–2–1120.102464-02002464-023LG12510R F 0Ω499Ω8.06k Ω4.99k ΩR G –499Ω2k Ω549ΩFigure 19. AD8130 Frequency Response vs. Supply,G = +5, G = +10, V OUT = 2 V p-pFigure 22. AD8130 Basic Frequency Response Test CircuitAD8129/AD8130AD8129 FREQUENCY RESPONSE CHARACTERISTICSG = +10, R L = 1 kΩ, C L = 2 pF, V OUT = 0.3 V p-p, T A = 25°C, unless otherwise noted.FREQUENCY (MHz)G A I N (d B )31300101000–3–4–5–6–7–2–112Figure 23. AD8129 Frequency Response vs. Supply, V OUT = 0.3 V p-pFREQUENCY (MHz)G A I N (d B )3130010100–3–4–5–6–7–2–112Figure 24. AD8129 Frequency Response vs. Supply, V OUT = 1 V p-pFREQUENCY (MHz)G A I N (d B )–3–4–5–6–7–2–13012Figure 25. AD8129 Frequency Response vs. Supply, V OUT = 2 V p-pFREQUENCY (MHz)G A I N (d B )41–2–3–4–5–6–1023Figure 26. AD8129 Frequency Response vs. Load Capacitance02464-028FREQUENCY (MHz)G AI N (d B )0.50.2–0.1–0.2–0.3–0.4–0.50.30.41300101000.1Figure 27. AD8129 Fine Scale Response vs. Supply, R L = 1 kΩ02464-029FREQUENCY (MHz)G A I N (d B )300101000.30–0.3–0.4–0.5–0.6–0.7–0.2–0.10.10.21Figure 28. AD8129 Fine Scale Response vs. Supply, R L = 150 ΩAD8129/AD813002464-030FREQUENCY (MHz)G A I N (d B )300100103210–1–2–3–4–5–6–7Figure 29. AD8129 Frequency Response vs. Supply, R L = 150 Ω02464-031FREQUENCY (MHz)G A I N (d B )30010013210–1–2–3–4–5–6–710Figure 30. AD8129 Frequency Response vs. Supply,G = +20, V OUT = 0.3 V p-p02464-032FREQUENCY (MHz)G A I N (d B )30010013210–1–2–3–4–5–6–710Figure 31. AD8129 Frequency Response vs. Supply,G = +20, V OUT = 2 V p-pFREQUENCY (MHz)G A I N (d B )300100110Figure 32. AD8129 Fine Scale Response vs. SOIC and MSOPfor Various R F /R G02464-034FREQUENCY (MHz)G A I N (d B )301100.20.10–0.1–0.2–0.3–0.4–0.5–0.6–0.7–0.8Figure 33. AD8129 Fine Scale Response vs. SupplyFREQUENCY (MHz)G A I N (d B )301100.10.30–0.3–0.4–0.5–0.6–0.7–0.2–0.10.10.2Figure 34. AD8129 Fine Scale Response vs. SupplyAD8129/AD813002464-036FREQUENCY (MHz)G A I N (d B )13001010030–3–4–5–6–7–2–112Figure 35. AD8129 Frequency Response vs. Supply,G = +20, R L = 150 Ω02464-037FREQUENCY (MHz)G A I N (d B )0.11100.2–0.1–0.4–0.5–0.6–0.7–0.8–0.3–0.200.1Figure 36. AD8129 Fine Scale Response vs. Supply,G = +50, G = +100, V OUT = 2 V p-p02464-038FREQUENCY (MHz)G A I N (d B )30–3–4–5–6–7–2–112Figure 37. AD8129 Frequency Response vs. Supply,G = +50, G = +100, V OUT = 2 V p-p02464-039FREQUENCY (MHz)G A I N (d B )30–3–4–5–6–7–2–112Figure 38. AD8129 Frequency Response vs. Supply,G = +50, G = +100, R L = 150 Ω02464-040FREQUENCY (MHz)O U T P U T V O L T A G E (d B V )1260–6–12–18–24–30–36–42–4810100400Figure 39. AD8129 Frequency Response for Various Output Levels102050100R F G 2k Ω2k Ω2k Ω2k Ω221Ω105Ω41.2Ω20ΩC L02464-041R GFigure 40. AD8129 Basic Frequency Response Test CircuitAD8129/AD8130AD8130 HARMONIC DISTORTION CHARACTERISTICSR L = 1 kΩ, C L = 2 pF, T A = 25°C, unless otherwise noted.02464-042–90–84–78–72–66–60FREQUENCY (MHz)H D 2 (d B c )Figure 41. AD8130 Second Harmonic Distortion vs. Frequency02464-043FREQUENCY (MHz)H D 2 (d B c )Figure 42. AD8130 Second Harmonic Distortion vs. Frequency02464-0440.5–91–85–79–73–67–611V OUT (V p-p)H D 2 (d B c )10–55Figure 43. AD8130 Second Harmonic Distortion vs. Output Voltage 1–99–93–87–81–75–6910FREQUENCY (MHz)H D 3 (d B c )40–63–57–5102464-045Figure 44. AD8130 Third Harmonic Distortion vs. Frequency–93–87–81–75–69–63FREQUENCY (MHz)H D 3 (d B c )–57–51–45Figure 45. AD8130 Third Harmonic Distortion vs. Frequency02464-0470.5–94–88–82–76–70–641V OUT (V p-p)H D 3 (d B c )10–58–52–46Figure 46. AD8130 Third Harmonic Distortion vs. Output VoltageAD8129/AD813002464-0481–79–73–67–61–55–4910FREQUENCY (MHz)H D 2 (d B c )40–4302464-05000.5 1.0 1.5 2.0 2.5 3.0–94–88–82–76–70–64V OUT (V p-p)H D (d B c )–58–52–46Figure 49. AD8130 Harmonic Distortion vs. Output VoltageFigure 47. AD8130 Second Harmonic Distortion vs. Frequency02464-0491–96–90–84–78–72–6610FREQUENCY (MHz)H D 3 (d B c )40–60–54–48–42Figure 48. AD8130 Third Harmonic Distortion vs. FrequencyAD8129/AD8130AD8129 HARMONIC DISTORTION CHARACTERISTICSR L = 1 kΩ, C L = 2 pF, T A = 25°C, unless otherwise noted.FREQUENCY (MHz)H D 2 (d B c )–511–57–63–69–75–81–87104002464-051Figure 50. AD8129 Second Harmonic Distortion vs. FrequencyFREQUENCY (MHz)H D 2 (d B c )–421–48–54–60–66–72–781040–8402464-052Figure 51. AD8129 Second Harmonic Distortion vs. FrequencyV OUT (V p-p)H D 2 (d B c )–62–68–74–80–86–56–5002464-053Figure 52. AD8129 Second Harmonic Distortion vs. Output Voltage FREQUENCY (MHz)H D 3 (d B c )11040–96–66–72–78–84–90–60–5402464-054Figure 53. AD8129 Third Harmonic Distortion vs. FrequencyFREQUENCY (MHz)H D 3 (d B c )1104002464-055Figure 54. AD8129 Third Harmonic Distortion vs. FrequencyV OUT (V p-p)0.5110H D 3 (d B c )Figure 55. AD8129 Third Harmonic Distortion vs. Output VoltageAD8129/AD8130FREQUENCY (MHz)H D 2 (d B c )1–44–50–56–62–68–74–80104002464-057Figure 56. AD8129 Second Harmonic Distortion vs. FrequencyFREQUENCY (MHz)H D 3 (d B c )1104002464-058Figure 57. AD8129 Third Harmonic Distortion vs. FrequencyV OUT (V p-p)–50–56–62–68–74–80–86H D (d B c )02464-059Figure 58. AD8129 Harmonic Distortion vs. Output Voltage 02464-060–87–81–75–69–63–57V CM (V)D I S T O R T I O N (d B c )–51–45–39–5–4–3–2–1012345Figure 59. AD8130 Harmonic Distortion vs. Common-Mode Voltage02464-061–97–91–85–79–73–67R L (Ω)D I S T O R T I O N (d B c)–611001kFigure 60. AD8130 Harmonic Distortion vs. Load Resistance02464-062–86–80–74–68–62–56R L (Ω)D I S T O R T I O N(d B c )–501001kFigure 61. AD8130 Harmonic Distortion vs. Load ResistanceAD8129/AD813002464-063–78–72–66–60–54–48V CM (V)D I S T O R T I O N (d B c )–42–36–5–4–3–2–112345Figure 62. AD8129 Harmonic Distortion vs. Common-Mode Voltage02464-064–90–84–78–72–68–60R L (Ω)D I S T O R T I O N (d B c )–541001k–48Figure 63. AD8129 Harmonic Distortion vs. Load Resistance02464-065–80–74–68–62–56–50R L (Ω)D I S T O R T I O N (d B c )–441001kFigure 64. AD8129 Harmonic Distortion vs. Load Resistance02464-066VLFigure 65. AD8129/AD8130 Basic Distortion Test Circuit,V CM = 0 V, Unless Otherwise Noted02464-0670.11.010FREQUENCY (Hz)10010100k1001k10k 1M 10MC U R R E N T N O I S E (p A /√H z )Figure 66. AD8129/AD8130 Input Current Noise vs. Frequency110FREQUENCY (Hz)100C U R R E N T N O I S E (n V /√H z )10100k1001k10k 1M 10MFigure 67. AD8129/AD8130 Input Voltage Noise vs. Frequency。

AS-12系列产品性能参数

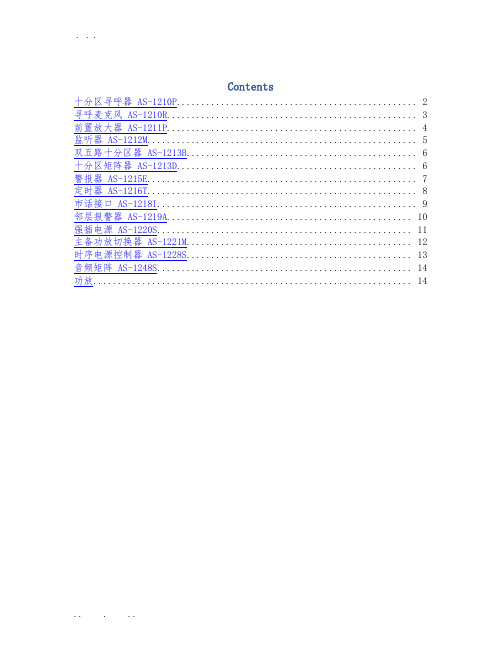

Contents十分区寻呼器 AS-1210P (2)寻呼麦克风 AS-1210R (3)前置放大器 AS-1211P (4)监听器 AS-1212M (5)双五路十分区器 AS-1213B (6)十分区矩阵器 AS-1213D (6)警报器 AS-1215E (7)定时器 AS-1216T (8)市话接口 AS-1218I (9)邻层报警器 AS-1219A (10)强插电源 AS-1220S (11)主备功放切换器 AS-1221M (12)时序电源控制器 AS-1228S (13)音频矩阵 AS-1248S (14)功放 (14)十分区寻呼器 AS-1210P性能特点(1)10分区寻呼报警功能(2)音频信号采用优质平衡传输连接技术(3)音频信号、控制信号采用双绞线同缆实时传输连接技术(4)采用专业级钟声提示音音效电路技术(5)具有四级优先权设计,分别为:本机MIC 1、钟声提示音为最高优先级,紧急音频信号(EMC)为第二级,寻呼麦克风1(MIC1)为第三级,寻呼麦克风2、3、4 (RMIC 2、3、4)和线路(AUX)为第四级(6)采用地址拨码,同时最多8台分区寻呼器相连接(7)15针电脑激活接口,低电平报警激活设备型号AS-1210P报警信号输入口EMC : 10K ohms(Ω) 330mV,不平衡线路输入口LINE :10K ohms(Ω) 330mV,不平衡话筒输入口MIC : 600 ohms(Ω) 5mV,不平衡寻呼话筒输入口四组RMIC1、RMIC2、RMIC3、RMIC4 10k ohms(Ω) 10V,平衡线路输出四组RMIC1、RMIC2、RMIC3、RMIC4 10k ohms(Ω) 10V,平衡非线性失真THD < 0.01% at 1k Hz信号噪声比S/N >70 dB可控制分区数十分区 "CH1~CH10"分区输出控制可手动选择或由警报信号激活任意分区警报激活输入口(0V) 短路信号 15针"ALARM IN (CH1~CH10) 一组警报激活输出口(0V) 短路信号 15针"ALARM OUT (CH1~CH10) 一组警报激活输出口(0V) 短路信号 "ALARM OUT" 二路默音抑制能力本机MIC、钟声提示音为最高优先级。

MICROMEGA 高精度过程控制器说明书

CN77000 R300和R500控制器,图片中含RHS-43孔锯, 易于钻圆孔。

有关订购信息, 请参见最后一页。

CN77333-A2 NEMA 12款方形开孔。

CN77533 NEMA 4方形开孔。

图片为实际尺寸。

1⁄16 DIN MICROMEGA ®自动调谐PID温度/过程控制器U 高精度:±0.5°C (0.9°F), 读数的0.03% U品质优秀, 还有5年保修支持 U 通用输入—过程电压/电流、热电偶、RTD U 双4位数字LED 显示屏和指示器, 用于显示输出和报警状态 U 可选RS232或RS485, OMEGA ® 协议U 继电器、SSR 、DC 脉冲、0 ~ 10 V, 以及 0 ~ 20 mA 输出类型 U 斜坡到设定值功能 U 通用电源, 90 ~ 250 Vac 或Vdc U 双输出和双报警功能U 隔离模拟输出或远程设定值可选将方形控制器放置于圆孔中!高精度、高品质MICROMEGA ®控制器在过程控制中提供无与伦比的灵活性。

每台设备均允许用户从10个热电偶类型(J 、K 、T 、E 、R 、S 、B 、C 、N 和JDIN )、Pt RTD (100、500或1000 Ω, 385或392曲线)或者模拟电压或电流输入中选择输入类型。

电压/电流输入可完全扩展到各工程单位,可选择小数点,是压力、流量或其他过程输入的理想之选。

MICROMEGA ®控制器具有大型双LED 显示屏,采用前面板配置,可选温度/过程输入,并接受90 ~ 250 Vac 或Vdc 通用电源。

提供单和双输入配置,CN77000系列适用于继电器、SSR 、DC 脉冲或模拟电压或电流输出。

单报警是标准配置。

可选项包括第二报警、 RS232、RS485、模拟输出以及远程设定值可选。

“300”系列控制器有许多特色,更大,紧凑型1⁄4 DIN 控制器,1⁄16 DIN 尺寸。

瑞纳捷 RJGT103 芯片数据手册说明书

瑞纳捷RJGT103芯片数据手册武汉瑞纳捷半导体有限公司Wuhan Runjet Semiconductor Co.,Ltd1.简介1.1.芯片功能介绍RJGT103是集成了256Byte的EEPROM(包含16Byte的密钥和8Byte的UID),执行RC4算法的加密芯片。

它与MCU可通过RSD单线串行接口通信,芯片支持计次功能。

1.2.产品特点●高性能防复制加密芯片;●RC4加密认证算法;●RSD单线总线协议,标准速率20Kbps;●用于写入用户自定义数据的EEPROM单元;●EEPROM存储大小256Byte,共16页,每页16Byte;●16Byte密钥,8Byte UID;●支持4Byte独立硬件真随机数;●支持计数功能,计数到阈值后,芯片功能指令全部失效;●正常工作功耗:<1mA;●工作电压范围2.2V~3.6V;●封装类型:SOT23-3、SOP8;1.3.系统框图图1-1RJGT103系统框图RJGT103包括模拟模块(OSC、EEPROM、复位模块)和数字逻辑模块。

FSM_CTRL 是整个系统的控制中心,根据RSD指令流程,进行RC4运算和EEPROM读写等操作。

1.4.芯片管脚功能SOT23-3封装管脚如下图:图1-5典型应用电路R0参考值:300Ω~2.2KΩ;C0参考值:1uF~4.7uF2.寄存器和数据存储2.1.内部寄存器描述表2-1RJGT103寄存器地址分配2.2.EEPROM存储描述表2-2EEPROM存储分配备注说明:(1)认证读写指的是从机认证读和从机认证写;(2)认证读写是针对用户数据存储区和功能控制区而言的,Key和UID不存在认证读写的说法;(3)写保护指的是正常功能模式下的写保护,初始化模式下不存在写保护的说法。

3.RSD接口RSD采用单根信号线,既传输时钟又传输数据,而且数据传输是双向的。

它具有结构简单、成本低廉、节省I/O资源、便于总线扩展和维护等众多优点。

英飞凌 FS100R12N2T7_B15 EconoPACK 2 模块 数据表

EconoPACK ™2 模块 采用第七代沟槽栅/场终止IGBT7和第七代发射极控制二极管带有温度检测NTC 特性•电气特性-V CES = 1200 V-I C nom = 100 A / I CRM = 200 A -沟槽栅IGBT7-低 V CEsat-过载操作达175°C•机械特性-高功率循环和温度循环能力-集成NTC 温度传感器-铜基板-低热阻的三氧化二铝 Al 2O 3 衬底-焊接技术可选应用•辅助逆变器•电机传动•伺服驱动器产品认证•根据 IEC 60747、60749 和 60068 标准的相关测试,符合工业应用的要求。

描述FS100R12N2T7_B15EconoPACK ™2 模块内容描述 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1特性 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1可选应用 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1产品认证 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1内容 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2 1封装 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3 2IGBT, 逆变器 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3 3二极管,逆变器 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5 4负温度系数热敏电阻 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6 5特征参数图表 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7 6电路拓扑图 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12 7封装尺寸 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12 8模块标签代码 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13修订历史 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14免责声明 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .151封装表 1绝缘参数特征参数代号标注或测试条件数值单位绝缘测试电压V ISOL RMS, f = 50 Hz, t = 1 min 2.5kV 模块基板材料Cu内部绝缘基本绝缘 (class 1, IEC 61140)Al2O3爬电距离d Creep端子至散热器10.0mm 电气间隙d Clear端子至散热器7.5mm 相对电痕指数CTI>200相对温度指数 (电)RTI封装140°C 表 2特征值特征参数代号标注或测试条件数值单位最小值典型值最大值杂散电感,模块L sCE26nH 模块引线电阻,端子-芯片R CC'+EE'T C=25°C, 每个开关 2.7mΩ储存温度T stg-40125°C 模块安装的安装扭距M根据相应的应用手册进行安装M5, 螺丝36Nm 重量G180g 注:The current under continuous operation is limited to 50 A rms per connector pin.2IGBT, 逆变器表 3最大标定值特征参数代号标注或测试条件数值单位集电极-发射极电压V CES T vj = 25 °C1200V 连续集电极直流电流I CDC T vj max = 175 °C T C = 95 °C100A 集电极重复峰值电流I CRM t P = 1 ms200A 栅极-发射极峰值电压V GES±20V表 4特征值特征参数代号标注或测试条件数值单位最小值典型值最大值集电极-发射极饱和电压V CE sat I C = 100 A, V GE = 15 V T vj = 25 °C 1.50 1.80VT vj = 125 °C 1.64T vj = 175 °C 1.72栅极阈值电压V GEth I C = 2.5 mA, V CE = V GE, T vj = 25 °C 5.15 5.80 6.45V 栅极电荷Q G V GE = ±15 V, V CE = 600 V 1.8µC 内部栅极电阻R Gint T vj = 25 °C 1.5Ω输入电容C ies f = 100 kHz, T vj = 25 °C, V CE = 25 V, V GE = 0 V21.7nF 反向传输电容C res f = 100 kHz, T vj = 25 °C, V CE = 25 V, V GE = 0 V0.076nF 集电极-发射极截止电流I CES V CE = 1200 V, V GE = 0 V T vj = 25 °C0.01mA 栅极-发射极漏电流I GES V CE = 0 V, V GE = 20 V, T vj = 25 °C100nA开通延迟时间(感性负载)t don I C = 100 A, V CE = 600 V,V GE = ±15 V, R Gon = 3.9 ΩT vj = 25 °C0.175µs T vj = 125 °C0.192T vj = 175 °C0.205上升时间(感性负载)t r I C = 100 A, V CE = 600 V,V GE = ±15 V, R Gon = 3.9 ΩT vj = 25 °C0.046µs T vj = 125 °C0.051T vj = 175 °C0.053关断延迟时间(感性负载)t doff I C = 100 A, V CE = 600 V,V GE = ±15 V, R Goff = 3.9 ΩT vj = 25 °C0.309µs T vj = 125 °C0.389T vj = 175 °C0.442下降时间(感性负载)t f I C = 100 A, V CE = 600 V,V GE = ±15 V, R Goff = 3.9 ΩT vj = 25 °C0.104µs T vj = 125 °C0.198T vj = 175 °C0.248开通损耗能量 (每脉冲)E on I C = 100 A, V CE = 600 V,Lσ = 35 nH, V GE = ±15 V,R Gon = 3.9 Ω, di/dt =1650 A/µs (T vj = 175 °C)T vj = 25 °C10.5mJ T vj = 125 °C14.7T vj = 175 °C16.8关断损耗能量 (每脉冲)E off I C = 100 A, V CE = 600 V,Lσ = 35 nH, V GE = ±15 V,R Goff = 3.9 Ω, dv/dt =3030 V/µs (T vj = 175 °C)T vj = 25 °C 6.68mJ T vj = 125 °C10.8T vj = 175 °C12.8(待续)表 4(续) 特征值特征参数代号标注或测试条件数值单位最小值典型值最大值短路数据I SC V GE≤ 15 V, V CC = 800 V,V CEmax=V CES-L sCE*di/dt t P≤ 8 µs,T vj=150 °C370At P≤ 7 µs,T vj=175 °C350结-外壳热阻R thJC每个 IGBT0.371K/W 外壳-散热器热阻R thCH每个 IGBT, λgrease= 1 W/(m*K)0.135K/W 允许开关的温度范围T vj op-40175°C注:T vj op > 150°C is allowed for operation at overload conditions. For detailed specifications, please refer to AN 2018-14.3二极管,逆变器表 5最大标定值特征参数代号标注或测试条件数值单位反向重复峰值电压V RRM T vj = 25 °C1200V 连续正向直流电流I F100A 正向重复峰值电流I FRM t P = 1 ms200A I2t-值I2t t P = 10 ms, V R = 0 V T vj = 125 °C1260A²sT vj = 175 °C1060表 6特征值特征参数代号标注或测试条件数值单位最小值典型值最大值正向电压V F I F = 100 A, V GE = 0 V T vj = 25 °C 1.72 2.10VT vj = 125 °C 1.59T vj = 175 °C 1.52反向恢复峰值电流I RM V R = 600 V, I F = 100 A,V GE = -15 V, -di F/dt =1650 A/µs (T vj = 175 °C)T vj = 25 °C57.7A T vj = 125 °C77.4T vj = 175 °C88.3(待续)表 6(续) 特征值特征参数代号标注或测试条件数值单位最小值典型值最大值恢复电荷Q r V R = 600 V, I F = 100 A,V GE = -15 V, -di F/dt =1650 A/µs (T vj = 175 °C)T vj = 25 °C 6.9µC T vj = 125 °C15.4T vj = 175 °C19.4反向恢复损耗(每脉冲)E rec V R = 600 V, I F = 100 A,V GE = -15 V, -di F/dt =1650 A/µs (T vj = 175 °C)T vj = 25 °C 2.04mJ T vj = 125 °C 4.61T vj = 175 °C 6.66结-外壳热阻R thJC每个二极管0.592K/W 外壳-散热器热阻R thCH每个二极管, λgrease= 1 W/(m*K)0.148K/W 允许开关的温度范围T vj op-40175°C注:T vj op > 150°C is allowed for operation at overload conditions. For detailed specifications, please refer to AN 2018-14.4负温度系数热敏电阻表 7特征值特征参数代号标注或测试条件数值单位最小值典型值最大值额定电阻值R25T NTC = 25 °C5kΩR100偏差ΔR/R T NTC = 100 °C, R100 = 493 Ω-55%耗散功率P25T NTC = 25 °C20mW B-值B25/50R2 = R25 exp[B25/50(1/T2-1/(298,15 K))]3375K B-值B25/80R2 = R25 exp[B25/80(1/T2-1/(298,15 K))]3411K B-值B25/100R2 = R25 exp[B25/100(1/T2-1/(298,15 K))]3433K 注:根据应用手册标定4 负温度系数热敏电阻6电路拓扑图图 17封装尺寸图 28模块标签代码图 3修订历史修订历史修订版本发布日期变更说明1.002021-11-19Initial version商标所有参照产品或服务名称和商标均为其各自所有者的财产。

贴片电容容量表

贴片电容容量表X7R贴片电容简述X7R贴片电容属于EIA规定的Class 2类材料的电容。

它的容量相对稳定。

X7R贴片电容特性具有较高的电容量稳定性,在-55℃~125℃工作温度范围内,温度特性为±15%。

层叠独石结构,具有高可靠性。

优良的焊接性和和耐焊性,适用于回流炉和波峰焊。

应用于隔直、耦合、旁路、鉴频等电路中。

X7R贴片电容容量范围厚度与符号对应表0201~1206 X7R贴片电容选型表1210~2225 X7R贴片电容选型表NPO COG 贴片电容容量规格表默认分类 2009-07-15 16:28 阅读354 评论1字号:大大中中小小NPO(COG)贴片电容属于Class 1温度补偿型电容。

它的容量稳定,几乎不随温度、电压、时间的变化而变化。

尤其适用于高频电子电路。

具有最高的电容量稳定性,在-55℃~125℃工作温度范围内,温度特性为:0±30ppm/℃(COG)、0±60ppm/℃(COH)。

层叠独石结构,具有高可靠性。

优良的焊接性和和耐焊性,适用于回流炉和波峰焊。

应用于各种高频电路,如:振荡、计时电路等。

我们把用来制造片式多层瓷介电容(MLCC)的陶瓷叫电容器瓷。

这里所说的瓷介就是用电容器瓷制成的陶瓷介质。

大家知道,陶瓷是一类质硬、性脆的无机烧结体。

就其显微结构而论,大都具有多晶多相结构。

其性能往往决定于其成份和结构。

当配方确定之后,能否达到预期的效果,关键取决于制造陶瓷粉料的工艺。

按其用途可以分为三类:①高频热补偿电容器瓷(UJ、SL);②高频热稳定电容器瓷(NPO);③低频高介电容器瓷(X7R、Y5V、Z5U)。

按温度系数分可以分为两类:①负温度系数电容器瓷(即高频热补偿电容器瓷);②正温度系数电容器瓷(即平时我们常说的COG、X7R、Y5V瓷料)。

按工作频率可以分为三类:低频、高频、微波介质。

高频热补偿、热稳定电容器瓷是专供Ⅰ类瓷介电容器作介质用,其瓷料主要成分是MgTiO3、CaTiO3、SrTiO3和TiO2再加入适量的稀土类氧化物等配制而成。

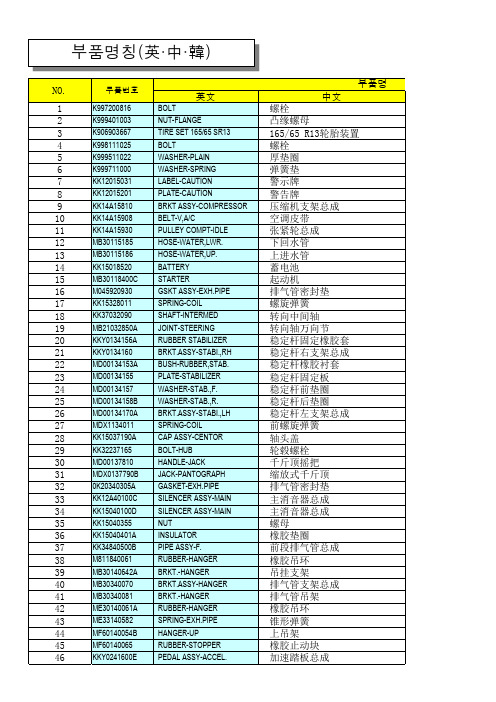

汽车部品名称

120

MDA0154395B HOOK-TIE DOWN,LH

121

MDA0154650A CROSSMEMBER NO.2,LH

122

KK1365572009 BEZEL ASSY-CLOCK

123

KK19055710A

AUTO CLOCK

124

0G03056784A

RUBBER-CUSHION

125

PLATE-CLOSING,RH

104

MD00153630A BRKT.-SEAT,B,,RH

105

MD00153640B BRKT-PARKING BRAKE

106

MDA0153250

BRKT-ENG.MTG.

107

MDA0153291

REINF.-WHL.APRON,R

108

MDA0153350B FRAME-F.LWR,RH

FLAP-R.,LH

左后挡泥板

79

KK10251660

MP

后雾灯支架

80

KK10751270

LAMP-LICENSE

后牌照灯

81

KK10Y51650

LAMP-RR.FOG.

后雾灯

82

KK11C51685

LAMP-BRKT,LH

左后雾灯支架

83

KK13551081

FASTENER

KK14A15930

PULLEY COMPT-IDLE

张紧轮总成

12

MB30115185

HOSE-WATER,LWR.

下回水管

13

MB30115186

HOSE-WATER,UP.

上进水管

SD103CW(丝印S6)二极管规格书(含样品申请表)

MARKING: SD103AW: S4 SD103BW: S5 SD103CW: S6

Maximum Ratings and Electrical Characteristics, Single Diode @Ta=25℃

Parameter

Symbol SD103AW SD103BW SD103CW Unit

CT trr

50 10

pF ns

VR=0V,f=1.0MHz IF=IR=200mA Irr=0.1XIR,RL=100Ω

B,Jul,2012

【领先的片式无源器件整合供应商—南京南山半导体有限公司】

联系资料

电话:

南京南山半导体有限公司-样品申请单

技术支持:

传真:

电邮:Service@

℃

Storage Temperature

TSTG

Electrical Ratings @Ta=25℃

-55~+150

℃

Parameter Reverse breakdown voltage

SD103AW SD103BW SD103CW

Symbol Min Typ 40

V (BR)R

30

20

Max Unit V

SOD-123

FEATURES z Low forward voltage drop z Guard ring construction for transient protection z Negligible reverse recovery time z Low reverse capacitance

回访记录

□已联系确认 日期:

□已建议执行 日期:

□未发送但已下单 日期:

STR7系列微控制器复习课程

S T R7系列微控制器第二章 STR7系列微控制器 (3)2.1STR71X系列微控制器 (3)2.1.1 特点 (4)2.1.2 总体结构 (6)2.1.3 引脚描述 (11)2.1.4 电气特性 (23)2.2STR73X系列微控制器 (29)2.2.1 特点 (30)2.2.2 总体结构 (32)2.2.3 引脚描述 (36)2.2.4 电气特性 (44)第二章 STR7系列微控制器意法半导体(ST)的STR7系列微控制器基于16/32位 ARM7TDMI RISC CPU,该系列种类齐全,用户可以根据不同的应用需求选择合适的芯片。

根据内核类型、片内Flash和片内RAM的容量,以及片上外设资源种类和数量的不同,STR7系列微控制器主要分成如下几类:STR71x系列、STR73x系列以及STR75x系列。

本章将对它们的硬件特性、结构和电气特性作一介绍,更详细的交、直流特性可参考ST的相关数据手册。

片内外设的详细描述可参考本书的第三章。

2.1 STR71x系列微控制器STR71x系列是片上集成Flash和RAM的微控制器系列。

它基于高性能的ARM7TDMI内核,拥有丰富的外设和增强的I/O功能。

该系列中的所有器件都包含片上高速单电压Flash存储器和高速RAM存储器。

由于内嵌ARM内核,所以STR71x与所有的ARM工具和软件兼容。

表2.1-1是STR71x系列微控制器器件型号总览,可作为选型参考。

表2.1-1 STR71x器件总表2.1.1 特点1.存储器✓片内集成最高达256+16k字节的flash存储器(代码FLASH可反复擦写10,000次,数据FLASH可反复擦写100,000次,存储信息最长可以保持20年),可加密保护;✓片内集成最高达64k字节的RAM存储器;✓拥有可以寻址4个存储器段的外部存储器接口(EMI),支持SRAM、Flash 以及ROM等存储器类型;✓支持多种启动方式。

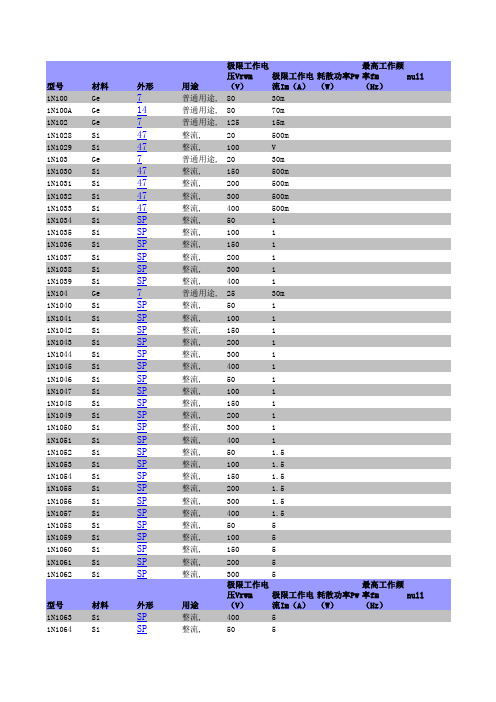

1N系列二极管手册

型号材料外形用途极限工作电压Vrwm(V)极限工作电流Im(A)耗散功率Pw(W)最高工作频率fm(H稳压)V稳压1N1313Si51稳压200μ150m8.75 1N1314Si51稳压200μ150m10.5 1N1315Si51稳压200μ150m12.71N1316Si51稳压200μ150m15.7 1N1317Si51稳压200μ150m18.5 1N1318Si51稳压200μ150m23.5 1N1319Si51稳压200μ150m28.5 1N1320Si51稳压200μ150m34.5 1N1321Si51稳压200μ150m41 1N1322Si51稳压200μ150m49.5 1N1323Si51稳压200μ150m58 1N1324Si51稳压200μ150m71 1N1325Si51稳压200μ150m87.5 1N1326Si51稳压200μ150m105 1N1327Si51稳压200μ150m127 1N1347Si SP整流,50061N1347A Si4整流,50061N1347B Si4整流,50061N1347C Si4整流,50061N1348Si SP整流,60061N1348A Si4整流,60061N1348B Si4整流,60061N1348C Si4整流,60061N135Ge7普通用途,755m1N1351Si4稳压500m10101N1351A Si4稳压500m1010 1N1351B Si SP稳压500m1010 1N1352Si4稳压500m10111N1352A Si4稳压500m1011 1N1352B Si SP稳压500m1011 1N1353Si4稳压500m1012 1N1353A Si4稳压500m1012 1N1353B Si稳压500m10121N1354Si4稳压500m10131N1354A Si4稳压500m1013 1N1354B Si SP稳压500m1013 1N1355Si4稳压500m10151N1355A Si4稳压500m1015 1N1355B Si SP稳压500m1015 1N1356Si4稳压500m1016 1N1356A Si4稳压500m1016 1N1356B Si SP稳压500m1016 1N1357Si4稳压500m1018 1N1357A Si4稳压500m1018 1N1357B Si SP稳压500m1018 1N1358Si4稳压150m1020 1N1358A Si4稳压150m1020 1N1358B Si SP稳压150m1020 1N1359Si4稳压150m1022 1N1359A Si4稳压150m1022 1N1359B Si SP稳压150m1022 1N1360Si4稳压150m1024 1N1360A Si4稳压150m1024 1N1360B Si SP稳压150m1024 1N1361Si4稳压150m1027 1N1361A Si4稳压150m1027 1N1361B Si SP稳压150m1027 1N1362Si4稳压150m1030 1N1362A Si4稳压150m1030 1N1362B Si SP稳压150m1030 1N1363Si4稳压150m1033 1N1363A Si4稳压150m1033 1N1363B Si SP稳压150m1033 1N1364Si4稳压150m1036 1N1364A Si4稳压150m1036 1N1364B Si SP稳压150m1036 1N1365Si4稳压150m1039 1N1365A Si4稳压150m1039 1N1365B Si SP稳压150m1039 1N1366Si4稳压150m1043 1N1366A Si4稳压150m1043 1N1366B Si SP稳压150m1043 1N1367Si4稳压150m1047 1N1367A Si4稳压150m1047 1N1367B Si SP稳压150m1047 1N1368Si4稳压150m1051 1N1368A Si4稳压150m1051 1N1368B Si稳压150m10511N1369Si4稳压150m1056 1N1369A Si4稳压150m1056 1N1369B Si SP稳压150m1056 1N1370Si4稳压50m1062 1N1370A Si4稳压50m1062 1N1370B Si SP稳压50m1062 1N1371Si4稳压50m1068 1N1371A Si4稳压50m1068 1N1371B Si SP稳压50m1068 1N1372Si4稳压50m1075 1N1372A Si4稳压50m1075 1N1372B Si SP稳压50m1075 1N1373Si4稳压50m1082 1N1373A Si4稳压50m1082 1N1373B Si SP稳压50m1082 1N1374Si4稳压50m1091 1N1374A Si4稳压50m1091 1N1374B Si SP稳压50m1091 1N1375Si4稳压50m10100 1N1375A Si4稳压50m10100 1N1376Si SP整流,502401N1377Si SP整流,1002401N1378Si SP整流,1502401N1379Si SP整流,2002401N137A Si51整流,3630m1N137B Si51整流,3675m1N1380Si SP整流,3002401N1381Si SP整流,4002401N1382Si SP整流,5002401N138A Si51整流,1850m1N138B Si51整流,189.0m1N139Ge7普通用途,4670m1N1396Si SP整流,5070 1N1397Si SP整流,10070 1N1398Si SP整流,15070 1N1399Si SP整流,200701N140Ge7普通用途,6085m1N1400Si整流,300701N1401Si SP整流,40070 1N1402Si SP整流,50070 1N1403Si SP整流,60070 1N1406Si45整流,600125m型号材料外形用途极限工作电压Vrwm(V)极限工作电流Im(A)耗散功率Pw(W)最高工作频率fm(Hz)Vz1N1911Si47整流,400 1.59页</< html>9a页</< html>12页</<。

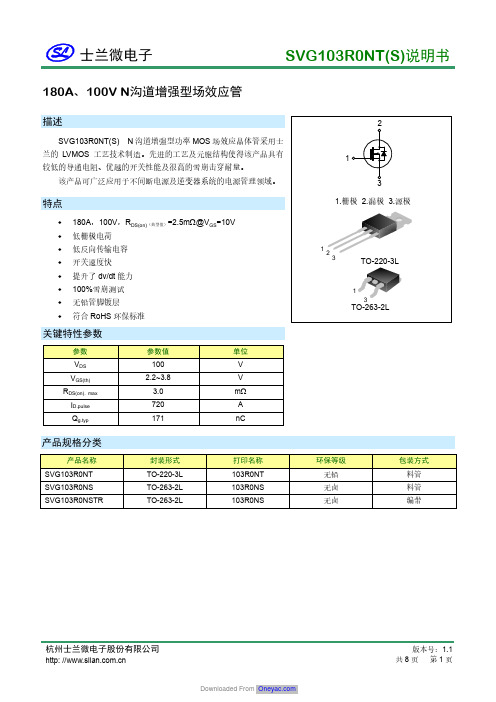

士兰微电子 SVG103R0NT(S)说明书

180A、100V N沟道增强型场效应管SVG103R0NT(S) N沟道增强型功率MOS场效应晶体管采用士兰的LVMOS 工艺技术制造。

先进的工艺及元胞结构使得该产品具有较低的导通电阻、优越的开关性能及很高的雪崩击穿耐量。

该产品可广泛应用于不间断电源及逆变器系统的电源管理领域。

特点♦180A,100V,R DS(on)(典型值)=2.5mΩ@V GS=10V♦低栅极电荷♦低反向传输电容♦开关速度快♦提升了dv/dt能力♦100%雪崩测试♦无铅管脚镀层♦符合RoHS环保标准关键特性参数产品规格分类极限参数(除非特殊说明,T=25︒C)A热特性电气参数(除非特殊说明,T=25︒C)j注:1. 脉冲时间5µs;2. 耗散功率值会随着温度变化而变化,当大于25︒C时耗散功率值随着温度每上升1度减少1.8W/︒C;3. 脉冲测试:脉冲宽度≤300μs,占空比≤2%;4. 基本上不受工作温度的影响。

典型特性曲线典型特性曲线(续)典型测试电路V DSV GS 10V栅极电荷量测试电路及波形图开关时间测试电路及波形图LDDV V E AS 测试电路及波形图V DDV LBV DSSI ASV DDtpTimeV DS(t)I D(t)E AS =12LI AS 2BV DSS BV DSS V DD封装外形图重要注意事项:1. 士兰保留说明书的更改权,恕不另行通知。

2. 客户在下单前应获取我司最新版本资料,并验证相关信息是否最新和完整。

产品应用前请仔细阅读说明书,包括其中的电路操作注意事项。

3. 我司产品属于消费类电子产品或其他民用类电子产品。

4. 在应用我司产品时请不要超过产品的最大额定值,否则会影响整机的可靠性。

任何半导体产品特定条件下都有一定的失效或发生故障的可能,买方有责任在使用我司产品进行系统设计、试样和整机制造时遵守安全标准并采取安全措施,以避免潜在失败风险可能造成人身伤害或财产损失情况的发生。

adv7123

修订版 BAnalog Devices 所提供的资料,相信是准确和可靠。

不过,没有责任假定模拟装置及其使用,也不为任何侵犯专利权或其他权利的第三方,可能会导致从其使用。

没有许可证是隐含批予或以其它方式根据模拟装置的任何专利或专利的权利。

一个adv7123一个技术途径,信箱 9106,norwood ma (,马 02062-9106,美国电话: 781/传真: 781/326-8703。

analog Devices,Inc.2002 CMOS,330 MHz三重10 位高速度视频数模转换器功能方框图r9–r0GNDSETIORIOR复合adv7123VREF电压参考电路g9–g0b9–b0IOGIOGIOBIOBPSAVE POWER 向下模式空白同步时钟V机场管理局数据10 DAC10 登记册数据10 DAC10 登记册数据10 DAC10 登记册兰科及SYNC逻辑功能330 MSPS 吞吐率三重 10 Bit D/A 转换器SFDR– 70 dB at f赤角= 50 MHz ; f OUT= 1 MHz– 53 dB at f赤角= 140 MHz ; f OUT= 40 MHzRS-343A/RS-170 兼容输出互补输出至二十六日 DAC 输出电流范围 2 mA mATTL 兼容的输入内部参考 (1.23 V)单电源 5 V/3.3 V 运行48-铅 LQFP 包低功耗 (30 毫瓦民 @ 3 V)低功率待机模式(6 mW 典型 @ 3 V)工业温度范围(– 40_C 至 + 85_C)应用程序数字视频系统 (1600年_1200 @ 100 Hz)高分辨率彩色图形数字无线电调制图像处理仪器仪表视频信号重构一般说明,ADV7123 (ADV®) 是一个三高速数字-模拟一个单片机芯片上的转换器。

it consists of 三高速与互补的10 位、视频D/A converters输出、 a standard TTL input 的interface 和一个高的阻抗模拟输出电流源。

AS-NZS 3112:2000-繁体中文版

Approval and test specification –Plugs and socket-outlets認可及測試規範-插頭和插座(AS/NZS 3112:2000和AS/NZS 3112/Amdt 1/2001)第一部份: 範圍及慨述1.1範圍本標準規定了家用及類似用途的額定電流不超過32A的超低電壓或低電壓的插頭和插座(如1.4條所定義的)的最基本的安全要求.(對於超低電壓插頭和插座見附錄E)本標準不適用於下列:(a) 電器耦合器(見AS/NZS 3109.1)(b) 裝置耦合器(見AS/NZS 3131:1995或暫標準AS/NZS 61535)(c) 工業用途的插頭, 插座和耦合器(見AS/NZS 3123)(d) 可移動電器用插頭和插座(見AS/NZS 3131)1.2應用1.2.1AS/NZS 3100標準的通用要求本標準應与AS/NZS 3100標準同時閱讀, AS/NZS 3100標準的相關條款應適用於插頭或插座的結構以及正常載流部件的絕緣和安全保護.1.2.2本標準的特殊要求插頭或插座如果符合本標準的所有相關要求並通過所規定的相關測試,則認為其符合本標準.注釋: (略)1.3參考文件本標準需參考下列文件:(略)1.4定義對本標準而言, AS/NZS 3100標準中的定義和如下的定義均適用:1.4.1完全凹入式插座具有符合3.6.4條的額外保護的插座.注釋: 這種額外保護應設計成可防止接觸插頭(符合圖2.1(e))的帶電端子.1.4.2絕緣插片式插頭所有帶電插片(N/L极插片----譯註)具有符合本標準的絕緣部份的插頭.1.4.3不可拆線式插頭插頭的結構應為插頭與其電源線形成一整體單元,以及;(a) 如果未使其永久破壞,電源線不可拆除;(b) 不可用手或普通工具更換電源線.1.4.4 插頭(略)1.4.5 具有螺紋連接裝置以及IP額定值的插頭(略)1.4.6 可拆線式插頭插頭的電源線可更換.1.4.7 插座(Socket-outlet)(略)1.4.8 具有螺紋連接裝置以及IP額定值的插座.(略)第二部份: 插頭2.1 端子及內部連接2.1.1 材料主要用於載流的端子及內部連接應為具有足夠硬度和剛度的耐腐蝕金屬材料.2.1.2 端子的結構端子應具有適當的大小和形狀,以配合相當於插頭額定電流的載流容量的電源線的導體. 應配有防止導體或絞合導體檜或拉伸的裝置.2.2 插片2.2.1 插片的材料插片的載流部份應為金屬,並具有足夠的機械強度,導電性和耐腐蝕性.符合性通過目視檢查,如有懷疑,則通過化學分析檢查.用於允許的溫度範圍和在正常化學污染的情況下,適當材料的實例如下:(a) 銅;(b) 銅合金,由冷軋薄板製作的部件含至少58%的銅,對於其它部件含至少50%的銅.(c) 不銹鋼,含至少13%鉻和小於0.09%碳.2.2.2 插片的組裝在組裝時,插片可能與插頭本體脫落但仍與電源線的導體連接,不允許插頭組裝時,任何插片不處於其預定的位置.用彈性絕緣材料製作的插頭,插片和端子應牢固定位.注釋: 參見2.8條關於扁平插片的呎寸.2.2.3 插片的形狀插片整體應具有適當的比例,鄰近連接處的部位其結構應不產生可導致插片斷裂的應力集中,同時應具有適當的開關以防止在正常使用時由於彎曲對絞合導體的擦傷或割傷. 插片的外露端應具有引入端,斜角或圓角以便於插入帶保護蓋的插座,同時無銳邊或毛邊.插片的接觸部位應光滑,無縫隙或缺口,但對於扁平插片而言,在一個面的接觸部份有0.3mm寬的縱向裂紋或縫隙是可以接受的.任何插片在裂紋處的厚度用如圖2.3所示的0.3mm厚的刀片測量.非絕緣插片的外露部份應無任何非金屬涂層.2.2.4 插片的絕緣絕緣插片的插頭的帶電部件應不外露,當插頭部份或全部插入插座時.如圖2.1所示的這種類型插頭的符合性按圖2.4測量檢查.對本條文而言,清漆,亮漆或噴涂的絕緣涂料不認為是絕緣材料.符合圖2.1(a), 2.1(c), 或2.1(f)(扁平帶電插片)至15A的插頭和絕緣插片式插頭不需符合圖2.1(e)中R20.0±1mm的要求.除如圖2.1(a2),(b)和(g)所示的插頭之外,低壓插頭的所有帶電插片應為絕緣插片,自本標準發佈之日后5年.2.3 絕緣材料2.3.1 慨述陶瓷除外,插頭的所有絕緣材料應符合2.13.11條.成型材料或包封材料應具有適當的性能並且其結構完全均勻,以保證具有適當的物理性能,它應無會明顯降低插頭的機械性能或電氣性能的空穴.2.3.2 插頭本體插頭本體的絕緣部份應為:(a) 性能不低於符合AS3121 (NZS/AS3121)的溫度種類為80℃的絕緣材料.(b) 陶瓷材料, 在水中浸泡48小時后並用潔凈布除去可見的水珠,其質量增加應不超過2%.2.3.3 插頭保護蓋插頭保護蓋的絕緣材料應具有不低於AS3121 (NZS/AS3121)中對溫度種類為60℃的絕緣材料所規定的性能.2.4 不可拆線插頭不可拆線插頭應符合如下要求:(a)每個導體應牢固並有效的連接到適當的插片上.每個插片(連接有導體)和鄰近連接處的導體的絕緣層應適當的支撐並固定在插頭中的位置.(b)導體應通過夾緊,壓著,碰焊或錫焊連接到插片.錫焊連接應符合AS/NZS 3100標準. 錫焊應僅用作夾緊或壓著連接的補充,除非插頭的結構為錫焊連接在插頭的正常使用中不會受到彎曲或承受機械應力.(c) 完整電源線(包括任何編織層,外被層)應包含在插頭本體中. 完整電源線應通過注塑,密封,封套或其它適當的方式牢固定位於插頭中,並能有效防止在正常使用中電源線的任何部份從插頭中移動出來.2.5 電源線進線口及固定措施2.5.1 慨述電源線進線口應能有效地固定電源線或打算配置的幾種電源線,以致在端子處的應力將顯著降低.對於可拆線插頭,應能有效固定表2.1中所列範圍的電源線,除非;(a) 有一特殊的開口,僅能配置一種規格的電源線,圓孔不認為限定直徑小於孔徑的電源線進入.(b) 製造商指定的電源線或電源線範圍按2.12.3(4)的規定進行標示.電源線的固定應符合AS/NZS 3100標準,除AS/NZS 3100標準的電源線拉力測試由本標準的2.13.4條的測試所代替.另外,除插頭僅使用平行二芯無外被電源線,如下應施加於彈性和熱塑性插頭(如圖2.1(a)和圖2.1(b)所示):應提供二種方式線夾: 一種是通過支柱,接線柱,夾具,曲折路徑或同等有效的方式固定每一條絕緣芯線;另一種是夾持電源線的外被.在一個裝置中可以使用二種方式.2.5.2 右角插頭( Side-entry plug)除需符合2.5.1條的通用要求之外,額定值至15A的低壓扁平插片右角插頭應符合圖2.1(d1)或圖2.1(d2)注釋: (略)圖2.1(d2)型的右角插頭的電源線的進入角度不作規定.但是,對於這種類型的插頭,電源線包括任何保護套或SR的邊緣距插頭面的距離不小於8.6mm.注釋: (略)表2.1電源線的範圍2.6 無線電干擾抑制裝置當電容加入插頭中用於無線電或電視干擾的抑制時,電容應符合IEC 60384-14標準.2.7 把手(Finger-grip)插頭應具有功能適當的把手,以便於容易插入插座或從插座中拔出.符合圖2.1(a1), (c), (d), (f)或(g)的插頭應容易插入或拔出符合圖3.5的完全凹入式插座.符合性通過目視檢查.2.8 低壓插頭的額定值和呎寸.2.8.1 慨述彽壓扁平插片插頭和具有一個圓形接地片及二個扁平帶電插片或二個圓形帶電片及一個扁平接地片的低壓插頭(額定值至20A)應符合圖2.1所示的適當呎寸.除圖2.1的呎寸之外,任何插頭的帶電片與插頭注塑邊緣之間的距離應不小於9mm.當懷疑符合此要求時,將附錄A的圖A1或附錄B的圖B1或附錄F的圖F1(a),F1(b)的適當治具置於插片上以接觸插頭面的最高點.使用寬度大於3mm的1.5mm厚薄規插入插頭和插頭治具之間(不用力),在9mm之內應不可接觸到帶電插片.插頭的前面應無任何一點凸出超過0.5mm.插片長度的測量應從插頭前面插片通過的最高點的平面到插片的末端.注釋: 凸出的實例是注塑的不平整和標示.2.8.2 整體注塑插頭和電源線二芯線可與3插片插頭整體注塑.2.8.3 具有非平行插片的二扁平插片插頭低壓,具有如圖2.1(c)排列二扁平插片插頭其電流額定值不超過連接的電線的額定值.這種插頭只允許10A最大額定電流並整體注塑.2.8.4 圖2.1的呎寸要求的相符性應通過任何適當的謶檢查的方式檢查低壓插頭與圖2.1所規定的呎寸的相符性,除涉及插片排列的標稱呎寸如距中心間距和角度方向應用符合附錄A,附錄B或附錄F的適當治具進行檢查.另外,額定電流至15A的低壓扁平插片或扁平插片和圓形插片組合的插頭(圖2.1(a1), 圖2.1(c), 圖2.1(d), 圖2.1(f)或圖2.1(g))應符合圖2.1(e)的呎寸要求.符合本標準具有絕緣插片的插頭不需符合圖2.1(e)中的R20±1.0mm的呎寸.(見圖2.1的注釋1)符合性用任何適當的方式進行檢查.2.8.5具有螺紋連接裝置以及IP額定值的插頭(略)2.9 內部連接配有接地連接的插頭的設計和結構應為當插頭正確接線和完整組裝時:(a) 松脫的端子螺絲或導電材料不能跨接任何帶電部件或接地部件;(b) 接地部件應有效的隔離,避免接觸可能松脫的帶電導體;(c) 帶電部件應有效的隔離,避免接觸可能松脫的接地導體.輔助裝置如無線電干擾抑制器或指示燈的任何連接需符合上述要求.2.10 接地連接的排列任何低壓,3插片插頭的接地插片應徑向於環繞插片的圓(見圖2.1(a1),圖2.1(f)和圖2.1(g)).2.11 保險絲加入插頭中並額定值不大於5A的保險絲應符合BS646標準.加入插頭中並額定值大於5A的保險絲應為符合AS 2005.30和AS 2005.10中相關要求的熔絲型.2.12 標示(Marking)2.12.1 要求的標示按照AS/NZS 3100標準, 插頭應標示如下資訊:(a) 製造商的名稱,商業名稱或標誌;(b) 額定電流,以安培表示;(c) 電壓;(d) 如果製造商標示的插頭不是唯一類型,則插頭還應標示產品號碼,型號或名稱與區分標示的任何其它插頭.(e) 宣稱的IP額定值.注釋: (略)2.12.2 標示的位置2.12.1條所要求的標示應位於如下:(a) (a)和(d)項—位於插頭的任何部位.(b) (b),(c)和(e)項—位於插頭的外部本體.2.12.3 對可拆線插頭的額外要求(略)2.12.4 接地連接(略)2.12.5 帶電連接(略)2.12.6 插頭的構型符合圖2.1(a),圖2.1(c),圖2.1(f)或圖2.1(g)的插頭當正確連接插片時,從插片視角,插片的構型應為E极,N极,L极處於順時針方向.當無接地插片時,帶電插片應符合這種構型.2.13.1 慨述插頭應按表2.2所述的順序進行測試並符合每項測試的要求.表2.2 插頭需進行的測試及順序插頭的耐絕緣應在500Vd.c.電壓下按如下進行:(a) 插頭的所有极之間(成對).(b) 插頭的帶電极與任何外部金屬之間, 插頭的所有帶電极連接在一起.(c) 插頭的帶電极與外露金屬的接地端子之間, 帶電极連接在一起.(d) 帶電极與施加到非導電部件(使用時正常握持)的軟電極之間, 所有帶電极連接在一起.(e) 對於絕緣插片插頭,帶電极與施加於每個帶電插片絕緣部位(距插頭面約4mm)的金屬箔之間, 所有帶電极連接在一起.測量的絕緣電阻應不小於5MΩ.2.13.3 高壓測試插頭應能經受表2.3所示的交流電壓,此電壓施加于2.13.2條的(a)和(c)項各1分鐘.插頭應能進一步經受3500Va.c.的電壓,此電壓施加于2.13.2條的(b)和(d)項各1分鐘. 絕緣插片的絕緣層應經受1250Va.c.電壓1分鐘(按2.13.2條的(e)項施加).表2.3 高壓測試的測試電壓2.13.4 電源線固定測試電源線測試時導體應連接於適當的端子.沿電源線進入插頭的方向施加表2.4中第4欄所規定值的直接拉力.超過10秒的時間,拉力均勻增加至適當的值,繼續保持10秒鐘,然後松開.此測試進行3次.彈性和熱塑性插頭的端子螺絲盡可能的松開(螺絲不脫落), 表2.4中第5欄規定值的直接拉力施加於電源線上. .超過10秒的時間,拉力均勻增加至適當的值,繼續保持10秒鐘,然後松開.此測試進行3次.電源線的芯線數應與插頭的插片數相適應.如果插頭設計只配置一種特定類型的電源線(按2.5條),則插頭僅需測試此種線材,但是,對應特定類型圓線直徑大小的進線口並不認為限定插頭只使用此種線材.如果電源線與端子分開;端子斷裂或損壞或當端子螺絲松開測試中電源線移動2mm.,則認為電線固定不適當.表2.4 電源線固定測試的負載2.13.5 外部螺帽或夾環的測試(略)2.13.6 保護蓋的連接(略)2.13.7 滾筒測試3個未進行測試的插頭按AS/NZS 3109.1標準所述在滾筒中進行測試.可拆線插頭配有表2.1中規定的最輕載荷,最小截面積的電線,長度約為100mm(從SR處或插頭處測量). 用等於AS/NZS 3100的螺紋和固定測試中規定力矩的2/3力矩將端子螺絲和組裝螺絲擰緊.不可拆線插頭按送測時所帶電線進行測試,電線保留約100mm自由長度(從SR處或插頭處測量).樣品從500mm高度跌落到3mm厚的鋼板上.每跌落100次后,目視插片並直接通過圖A1或F1的治具.總跌落次數為1000次.滾筒轉速為5轉/分鐘,每分鐘產生10次跌落.每次僅測試一個樣品.測試后,樣品應無本標準意義上的損壞.特別如下:(a) 帶電部件不外露於本標準的測試指.(b) 對於接地插片,仍需符合3.14.7條.(c) 任何其它影響安全性的功能將不減弱.(d) 無帶電部件鬆脫至產生危害情況的程度(參見2.9條).(e) 用正常視力或校正至正常的視力目測插頭.片如需要可除去絕緣層.插片應無破裂或顯示裂紋注釋: (略)2.13.8 溫升測試插頭的結構應使其符合如下溫升測試:(a) 不可拆線插頭按送測時樣品測試(用於溫度測試可接觸到端子的特制樣品).(b) 可拆線插頭配置製造商說明書中規定的導體截面積最小的PVC電線.用測試代號5中測試所規定的力矩的2/3,擰緊端子螺絲或螺帽.注釋: (略)測試插座為符合本標準的固定式插座.注釋: (略)固定式插座應安裝於適當的金屬壁箱子中,箱子置於自由通風之處,插座配置至少2.5m 長,如表3.4中所示的截面積的PVC絕緣的導體.插座的電線應在箱子線路接頭的1m距離封閉.插頭插入插座並通1.1倍額定電流的交流電1小時.電線接頭的溫度由熔化粒子,顏色變化指示劑或熱電偶方式確定,其選擇和放置應對需確定的溫度無影響.接頭的溫升應不超過45K.2.13.9 插片的牢固性2.13.9.1 插片的移動通過一剛性夾持塊夾持插片測試插片的移動, 夾持塊位於距插頭面5±0.5mm處,並施加18±1N的力於插片. 夾持塊的設計應為,測試時未測試的插片不會接觸到夾持塊.不可拆線插頭除外,測試時插頭不需連接電線,端子螺絲松開至可允許1mm2導體連接. 插頭和測試設備在40±1℃溫度下預處理1小時,不施加測試力.整個測試中,插頭和測試設備的所有部件都處於此溫度.對於所有插頭,施力點為沿著插片距插頭面14±0.5mm處,力的方向應為:(a) 沿著垂直於插片平面的線以及通過插片中心的二個方向.(b) 沿著一條線以右角達到(a)中的規定.在10秒的時間,以(a)和(b)所述方式將力逐漸施加至每個插片,並保持其最大力10秒,然後松開. 當施加力時,沿著相對於剛性夾持塊的力線測量插片的偏差.最大偏差應不超過2.0mm.依次測試符合圖2.1的插頭的所有的插片,在完成最後一個插片測試后5分鐘,其任何變形不應防止插頭插入附錄A,B,F中所示的適當的標準治具(不施加過分的力).對於其它類型的插頭,5分鐘后的任何變形不應防止插頭插入適當的插座(不施加過分的力).2.13.9.2 插片的固定另一個插頭樣品加熱至50±2℃1小時,並在整個測試包括除去測試負荷的5分鐘保持此溫度.插頭牢固地固定,其方式不會對插頭本體產生過分的擠壓或扭曲,而且不會使插片保持其原來的位置.在10秒的時間,每個插片依次平穩地施加力至60±0.6N,並保持10分鐘.每個插片進行2次測試,一次力的方向沿著插片長度朝向插頭本體的方向,另一次為相反方向.如果在測試中的任何時候,任何插片相對於本體材料移動大於2.4mm或在除去測試力的5分鐘內,任何插片不能回到圖2.1規定的標稱長度的0.8mm之內,則認為插片的連接是不恰當的.2.13.10 IP額定值確定插頭的IP額定值由製造商指定的插座和任何連接裝置進行確定,此組合物按AS 1939標準進行測試.當插頭測試AS 1939標準的第一個數字5(粉塵測試)時,測試應在AS 1939標準中規定的第2類條件下測試.2.13.11 防火性測試所有絕緣材料應進行AS/NZS 4695.2.11規定的灼熱絲測試,並符合相關的條款,施加650℃的灼熱絲30秒.2.13.12不可拆線插頭和電源線的額外測試2.13.12.1 慨述不可拆線插頭和電源線應通過2.13.12.2至2.13.12.6條的測試,除2.13.12.5條的測試僅用於具有錫箔導體的電線.每項測試在不同的樣品上進行.在這些測試時,室溫保持20±2℃.2.13.12.2 電源線的固定按如下步驟進行彎曲測試:(a) 將插頭固定至測試儀通過將插片固定於如圖2.2所示儀器的搖擺機構上而將插頭固定,搖擺機構處於運動中心,插頭出線口處電線的軸線垂直並通過搖擺的軸線.對此測試,任何SR認為是插頭的一部份.帶扁線的插頭其安裝應為截面的主軸平行於搖擺的軸線.插頭應置於測試儀上,以致當搖擺時,重塊和電線產生最小的側向運動.為了得到測試中重塊和電線具有最小側向運動的安裝位置,測試儀的結構應為,搖擺機構的不同支承物可通過螺紋軸(至少可移動範圍20至150mm)調節.一個裝置如條片應用於檢查重塊和電線產生最小側向運動.(b) 電線的負載電線應有如下負載:Ⅰ). 20±0.2N, 電線的截面積超過0.75 mm2Ⅱ). 10±0.1N, 電線的截面積未超過0.75 mm2重塊位於電線進線口至少300mm處(見圖2.2).(c) 測試方法搖擺機構擺動90°(每側45°), 彎曲次數為10000次,彎曲速度為60次/分鐘.注釋: 一次彎曲為向一個方向的一次運動.彎曲5000次后,圓線樣品在搖擺機構中轉動90°. 扁線樣品僅在垂直於含有線軸的平面方向彎曲.(d) 彎曲測試中的符合性在測試中,無銅絲刺破絕緣層,使其可接觸.(e) 彎曲測試后的符合性符合性指標如下:(Ⅰ). 樣品不顯示損壞.(Ⅱ). 保護套(如有)應不與插頭本體分開.(Ⅲ). 電線的絕緣層應不損壞.(Ⅳ). 每個導體的銅絲數不大於10%的破裂.2.13.12.3 芯線的連接通過夾持插片牢固地固定插頭.將沿電線出線口方向的直接拉力施於距進線口約600mm 處芯線(夾持在一起).,外被除去至插頭.在10秒的時間,拉力均勻增加至110±1N,並保持此最大值10秒鐘,然後鬆開.如果在測試中的任何時候,任何芯線從插頭上脫落或所有導體銅絲從插片上脫落,可認為芯線的連接不適當.2.13.12.4 外被的連接(帶外被電線)通過夾持插片牢固地固定插頭.將沿電線出線口方向的直接拉力施於距進線口約600mm 處外被,在距插頭約25mm處切斷芯線.在外被上做一軸向切口. 在10秒的時間,拉力均勻增加至130±1.3N,並保持此最大值10秒鐘,然後鬆開.如果在直接拉力達到所需值之前或在保持拉力期間,在進線口或SR處芯線外露,可認為外被的連接不適當.對於連接輕負載PVC電線或普通負載的彈性電線的插頭,如果在達到130N最大力之前,當外被破裂時,進線口處芯線不外露,則認為連接是恰當的.2.13.12.5 絕緣層的連接(無外被電線)通過夾持插片牢固地固定插頭.將沿電線出線口方向的直接拉力施於距進線口約600mm 處電線,每條線的絕緣層從距進線口約25mm處平行於導體切開一小段距離.導體的所有銅絲從切開部份切斷, 在10秒的時間,拉力均勻增加至65±0.7N,並保持此最大值10秒鐘,然後鬆開.如果在測試中的任何時候,絕緣層脫離插頭或進線口附近導體外露,則認為絕緣層的連接是不適當的.2.13.12.6 導體的連接插頭應切開,並且插片和適當長度的芯線從插頭上除去.另外,製造商可送交未注塑的樣品用於此項測試.鄰近插片約25mm的絕緣層從電線上剝開.每個插片依次固定,直接拉力施於距插片約600mm處的導體上,方向為導體連接到插片的方向.在10秒的時間,拉力逐漸增加至85±0.9N,並保持此最大值1分鐘,然後鬆開.如果在測試的任何時候,所有導體銅絲從插片上脫落,則認為導體的連接是不適當的.2.13.13具有絕緣插片的插頭的額外測試2.13.13.1 慨述插片的絕緣材料應能經受高溫和低溫應力.通過2.13.13.2至2.13.13.5條的測試進行檢查.2.13.13.2 高溫壓力測試一個絕緣插片樣品用如圖2.5所示的儀器進行如下測試.該儀器有一直徑為6mm,厚度為0.7mm的圓形壓片.如圖2.5所示放置樣品,通過壓片對樣品施加2.5N的力.放置樣品的儀器置於160±5℃的烘箱中2小時.從儀器中取出樣品,在10秒鐘內浸入冷水中冷卻.立即測量浸入處絕緣層的厚度,而且厚度的降低不超過50%.目視檢查絕緣材料應無裂紋,而且絕緣材料的呎寸應不低於圖2.4所示的最小呎寸.2.13.13.3 靜態阻尼加熱測試具有絕緣插片的插頭應按IEC 60068-2-30.Db (12+12 h cycle)進行2次阻尼加熱循環.相對溫度為95%,低溫為25±3℃,高溫為40℃.經過上述處理並恢復到室溫后,樣品應進行如下測試:(a) 耐絕緣測試(2.13.2(5)條)(b) 高壓測試(2.13.3條)(c) 耐磨測試(2.13.6條).注釋: (略)2.13.13.4 低溫測試具有絕緣插片的插頭應在-15±2℃保持至少24小時,然後回到室溫.樣品應進行如下測試:(a) 耐絕緣測試(2.13.2(5)條)(b) 高壓測試(2.13.3條)(c) 耐磨測試(2.13.6條).注釋: (略)2.13.13.5 低溫衝擊測試僅一個絕緣插片樣品進行衝擊測試,使用如圖2.6所示的儀器.下落重塊的質量為100±1g. 在40mm厚泡沫橡膠墊上的儀器與樣品置於-15±2℃保持至少24小時.在時間末期,樣品如圖2.6所示放置,下落重塊可從100mm高處下落.對同一樣品連續進行4次衝擊,在衝擊之間將其轉動90°.測試后,樣品回到室溫然後進行檢查.目視檢查樣品,絕緣材料應無裂紋.注釋: (略)2.13.13.6 耐磨測試具有絕緣插片的插頭應用如圖2.7所示的儀器進行如下測試.測試儀器包括一水平橫樑,它可圍繞其中心旋轉.一段直徑為1mm鋼絲線,彎成U形,其底部為平直的, 兩端牢固地連接於橫樑的一端,以致平直部份凸出橫樑之下,並平行橫樑旋轉軸.用適當的夾具夾持插頭,使鋼絲線平直部份靠在插片主軸面上.插頭處於與水平面成10°的斜面.對橫樑加載,使鋼絲線對插片施加4N的力.插頭在水平方向前後移動,使鋼絲線沿插片磨擦.插片被磨擦的長度約為9mm,其中約7mm為絕緣部份.移動的次數為20000次(每個方向10000次),速度為30次/分鐘.測試后,插片應無影響安全性或插頭使用的損壞,尤其是絕緣護套不被刺破或起皺.第三部份: 插座3.1 接頭和內部連接3.1.1 材料主要用於載流的接頭和內部連接應為具有足夠硬度和剛度的適當的耐腐蝕性金屬.3.1.2 接頭的結構插座的接頭應隱入插座的本體,以防止其偶爾接觸裸露的接地導體或其它外露金屬.除在額定電流為15A或以上的插座中,插座的帶電接頭應有適當的大小和形狀,以配合相當於插座額定值的至少二種規格的導體.對於所有的插座,接地接頭應有適當的大小和形狀,以配合相當於插座額定值的至少二種規格的接地導體.注釋: (略)3.2 禁止的配置低壓固定式插座或其面板不能並入通訊線路,電視或無線電天線線路或其它相似線路系統的連接裝置.3.3 插座彈夾3.3.1 材料彈夾應為對其用途具有足夠的剛性和耐久性的耐腐蝕性金屬.3.3.2 結構。

MEMORY存储芯片N25Q032A13ESE40F中文规格书

Table 33: 1.35V R TT Effective Impedance (Continued)ODT SensitivityIf either the temperature or voltage changes after I/O calibration, then the tolerancelimits listed in Table 32 and Table 33 can be expected to widen according to Table 34and Table 35.Table 34: ODT Sensitivity DefinitionNote: 1.˂T = T - T(@ calibration), ˂V = V DDQ - V DDQ(@ calibration) and V DD = V DDQ.Table 35: ODT Temperature and Voltage SensitivityNote: 1.˂T = T - T(@ calibration), ˂V = V DDQ - V DDQ(@ calibration) and V DD = V DDQ.ODT Timing DefinitionsODT loading differs from that used in AC timing measurements. The reference load forODT timings is shown in Figure 24. Two parameters define when ODT turns on or offsynchronously, two define when ODT turns on or off asynchronously, and another de-fines when ODT turns on or off dynamically. Table 36 and Table 37 (page 63) outlineand provide definition and measurement references settings for each parameter.ODT turn-on time begins when the output leaves High-Z and ODT resistance begins toturn on. ODT turn-off time begins when the output leaves Low-Z and ODT resistancebegins to turn off.4Gb: x4, x8, x16 DDR3L SDRAM Electrical Characteristics and AC Operating ConditionsCommand and Address Setup, Hold, and DeratingThe total t IS (setup time) and t IH (hold time) required is calculated by adding the data sheet t IS (base) and t IH (base) values (see Table 60; values come from the ElectricalCharacteristics and AC Operating Conditions table) to the ǻt IS and ǻt IH derating values (see Table 61 (page 104), Table 62 (page 104) or Table 63 (page 104)) respectively. Ex-ample: t IS (total setup time) = t IS (base) + ǻt IS. For a valid transition, the input signal has to remain above/below V IH(AC)/V IL(AC) for some time t VAC (see Table 64 (page 105)).Although the total setup time for slow slew rates might be negative (for example, a valid input signal will not have reached V IH(AC)/V IL(AC) at the time of the rising clock transi-tion), a valid input signal is still required to complete the transition and to reachV IH(AC)/V IL(AC) (see Figure 15 (page 53) for input signal requirements). For slew rates that fall between the values listed in Table 61 (page 104) and Table 63 (page 104), the derat-ing values may be obtained by linear interpolation.Setup (t IS) nominal slew rate for a rising signal is defined as the slew rate between the last crossing of V REF(DC) and the first crossing of V IH(AC)min . Setup (t IS) nominal slew rate for a falling signal is defined as the slew rate between the last crossing of V REF(DC) and the first crossing of V IL(AC)max . If the actual signal is always earlier than the nominal slew rate line between the shaded V REF(DC)-to-AC region, use the nominal slew rate for derat-ing value (see Figure 34 (page 106)). If the actual signal is later than the nominal slew rate line anywhere between the shaded V REF(DC)-to-AC region, the slew rate of a tangent line to the actual signal from the AC level to the DC level is used for derating value (see Figure 36 (page 108)).Hold (t IH) nominal slew rate for a rising signal is defined as the slew rate between the last crossing of V IL(DC)max and the first crossing of V REF(DC). Hold (t IH) nominal slew rate for a falling signal is defined as the slew rate between the last crossing of V IH(DC)min and the first crossing of V REF(DC). If the actual signal is always later than the nominal slew rate line between the shaded DC-to-V REF(DC) region, use the nominal slew rate for derat-ing value (see Figure 35 (page 107)). If the actual signal is earlier than the nominal slew rate line anywhere between the shaded DC-to-V REF(DC) region, the slew rate of a tangent line to the actual signal from the DC level to the V REF(DC) level is used for derating value (see Figure 37 (page 109)).Table 60: DDR3L Command and Address Setup and Hold Values 1 V/ns Referenced – AC/DC-Based4Gb: x4, x8, x16 DDR3L SDRAMCommand and Address Setup, Hold, and Derating。

布森南·SMD熔断器CC12H用户手册说明书

High I2t Chip fuse withstands high inrush currents in a 1206 (3216 metric) packageThe compact CC12H offers a significant space savings over other larger SMD devices with similar performance.Product description:Eaton’s Bussmann® seriesCC12H SMD fuses providesexcellent inrush withstandperformance coupled with thecycling advantages of a ceramicsolid matrix construction.The CC12H is a cost-effectivesolution for applications in whichhigh inrush currents and/oron-off cycling are present.The CC12H allows maximumprotection without oversizing ofthe fuse rating.Features and benefits:• High inrush withstandcapability.• AEC-Q200 Grade 1 qualified(750 mA to 20 A versions)• cURus recognized• Compact 1206 (3216 metric)design utilizes less boardspace.• RoHS compliant, lead free andhalogen free construction• Operating temperature of-55 °C to +125 °C [with derating](250 mA to 15 A versions)ensuring protection in harshclimates.• The high I2t values of allowsthe end user to avoidnuisance openings from highinrush currents and providesadditional protection againstuncertain current surges fromthe system.CC12H High I2t Chip Fuses BUSSMANNSERIESEaton is a registered trademark.All other trademarks are property of their respective owners.EatonElectronics Division 1000 Eaton Boulevard Cleveland, OH 44122United States/elx© 2016 EatonAll Rights Reserved Printed in USAPublication No. 4025 BU-MC16042July 2016Ratings:• Voltage rating DC: 32 V to 63 V • Current rating: 0.25 A to 30 A •Interrupting rating: 50 A to 200 AAgency information:•cURus recognition: File E19180, Guide JDYX2/JDYX8•AEC-Q200 qualified: (750 mA to 20 A versions)• RoHS compliant•REACH declaration available upon requestSpecificationsElectrical characteristics:Amp Rating % of Amp Rating Opening Time 250 mA – 30 A 100% 4 hours minimum 1 A – 3 A 200% 1 s – 60 s 25 A – 30 A 200% 120 s max 1 A – 5 A 250% 5 s max 1 A – 5 A300% 0.1 s – 3 s 250 mA – 750 mA 350% 5 s max 6 A – 20 A 350% 5 s max 250 mA – 500 mA 1000% 0.01 ms – 1 ms 750 mA – 30 A1000%0.2 ms – 20 msPackaging and ordering information:•-TR (3000 parts on a 7” reel, tape width 8 mm)Ordering Code Part Number-TR optionC 12H250mA C C 12H250mA-TR C 12H375mA C C 12H375mA-TR C 12H500mA C C 12H500mA-TR C 12H750mA C C 12H750mA-TR12H1A C C 12H1A-TR 12H1.5A C C 12H1-5A-TR 12H2A C C 12H2A-TR 12H2.5A C C 12H2-5A-TR 12H3A C C 12H3A-TR 12H3.5A C C 12H3-5A-TR 12H4A C C 12H4A-TR 12H4.5A C C 12H4-5A-TR 12H5A C C 12H5A-TR 12H6A C C 12H6A-TR 12H7A C C 12H7A-TR 12H8A C C 12H8A-TR 12H10A C C 12H10A-TR 12H12A C C 12H12A-TR 12H15A C C 12H15A-TR 12H20A C C 12H20A-TR 12H25A C C 12H25A-TR12H30A C C 12H30A-TRConstruction and dimensions mm (in):Alpha code marking (amp designation)Metal film fusible element0.6 +0.2, -0.15(0.024 + 0.008, -0.006)3.2 +/-0.2(0.126 +/-0.008)1.6 +/-0.2(0.063 +/-0.008)Green fused-glass coverSilver terminal padEnd termination (nickel underplate/tin overplate)White ceramic substrate。