EMCEMI_Analysis_in_Wireless_Communication_Networks

关于EMC、EMI、EMS之间的区别与联系浅析

关于EMC、EMI、EMS之间的区别与联系浅析什么是emi、ems和emc?在电气干扰领域有许多英文缩写。

emi(electro magnetic interference)直译是电磁干扰。

这是合成词,我们应该分别考虑"电磁"和"干扰"。

所谓"干扰",指设备受到干扰后性能降低以及对设备产生干扰的干扰源这二层意思。

第一层意思如雷电使收音机产生杂音,摩托车在附近行驶后电视画面出现雪花,拿起电话后听到无线电声音等,这些可以简称其为与"bci""tvi""teli",这些缩写中都有相同的"i"(干扰)(bc:广播)那么emi标准和emi检测是emi的哪部分呢?理所当然是第二层含义,即干扰源,也包括受到干扰之前的电磁能量。

其次是"电磁"。

电荷如果静止,称为静电。

当不同的电位向一致移动时,便发生了静电放电,产生电流,电流周围产生磁场。

如果电流的方向和大小持续不断变化就产生了电磁波。

电以各种状态存在,我们把这些所有状态统称为电磁。

所以emi标准和emi检测是确定所处理的电的状态,决定如何检测,如何评价。

ems(electro magneTIc suscepTIbility)直译是"电磁敏感度"。

其意是指由于电磁能量造成性能下降的容易程度。

为通俗易懂,我们将电子设备比喻为人,将电磁能量比做感冒病毒,敏感度就是是否易患感冒。

如果不易患感冒,说明免疫力强,也就是英语单词immunity,即抗电磁干扰性强。

emc(electro magneTIc compaTIbility)直译是"电磁兼容性"。

意指设备所产生的电磁能量既不对其它设备产生干扰,也不受其他设备的电磁能量干扰的能力。

emc这个术语有其非常广的含义。

如同盲人摸象,你摸到的与实际还有很大区别。

电磁兼容解决方案

电磁兼容解决方案一、背景介绍电磁兼容(Electromagnetic Compatibility,简称EMC)是指在电子设备和系统之间实现相互协调和无干扰的能力。

在现代社会中,电子设备的广泛应用使得电磁辐射和电磁干扰的问题日益突出。

为了保证电子设备的正常运行,确保设备之间不发生干扰,需要采取一系列的电磁兼容解决方案。

二、问题描述在电子设备和系统中,常常会出现以下问题:1. 电磁辐射:电子设备在工作过程中会产生电磁辐射,如果辐射强度过大,会对周围的设备和系统产生干扰。

2. 电磁干扰:电子设备之间的相互干扰会导致设备的正常工作受到影响,甚至造成设备损坏。

3. 电磁敏感性:某些电子设备对外界的电磁干扰非常敏感,容易受到干扰而无法正常工作。

三、解决方案为了解决上述问题,我们提出以下电磁兼容解决方案:1. 设计合理的电磁屏蔽结构通过在电子设备和系统中设计合理的电磁屏蔽结构,可以有效地阻挡电磁辐射的传播,减少对周围设备和系统的干扰。

常见的电磁屏蔽结构包括金属外壳、屏蔽罩、屏蔽隔板等。

通过合理的屏蔽结构设计,可以降低电磁辐射的强度,提高设备的电磁兼容性。

2. 优化电磁波传输路径在电子设备和系统的设计过程中,需要优化电磁波的传输路径,减少电磁波在传输过程中的能量损耗和干扰。

通过合理的布局设计、优化导线和电缆的走向,可以降低电磁波的传输损耗,提高设备的电磁兼容性。

3. 选择合适的滤波器和隔离器在电子设备和系统中,可以通过选择合适的滤波器和隔离器来降低电磁干扰的影响。

滤波器可以通过滤除特定频率的电磁波来减少干扰,隔离器可以将不同部分的电子设备和系统隔离开,减少相互干扰。

4. 合理设置接地系统接地系统是保证设备正常工作和提高电磁兼容性的关键。

通过合理设置接地系统,可以有效地降低电磁干扰的影响。

在接地系统设计中,需要考虑接地电阻、接地路径的选择等因素,确保设备的接地系统能够有效地排除干扰。

5. 进行电磁兼容测试和评估在电子设备和系统设计完成后,需要进行电磁兼容测试和评估,以验证设备的电磁兼容性。

电子设备的EMI与EMC问题解决方法

电子设备的EMI与EMC问题解决方法随着科技的快速发展,电子设备在我们的日常生活中扮演着越来越重要的角色。

然而,随之而来的问题就是电磁干扰(Electromagnetic Interference,简称EMI)与电磁兼容性(Electromagnetic Compatibility,简称EMC)。

这些问题会导致设备性能下降,甚至可能造成严重的故障。

下面将详细介绍电子设备EMI与EMC问题的解决方法。

一、了解EMI与EMC的原因和影响1. EMI的原因:电子设备中的各种信号电路会产生互相干扰的电磁场,从而产生电磁波辐射,导致EMI问题。

2. EMC的影响:EMI问题可能会导致信号传输的错误、数据丢失、仪器测量不准确等影响设备性能的问题。

二、采取措施减少EMI问题1. 采用屏蔽技术:在电子设备的关键部件或线路周围设置屏蔽罩,以减少电磁波的辐射和接受。

这可以通过使用屏蔽材料和接地技术来实现。

2. 优化线路布局:合理排布电路,避免信号线与电源线之间的互相干扰,减少EMI问题的发生。

同时,使用分离地面平面和分层布局也可以有效降低EMI问题。

3. 控制信号的频率和功率:降低电子设备内部信号线路的频率和功率,可减少电磁波辐射。

这可以通过电路设计和合理选择相关元件来实现。

三、提高设备的EMC性能1. 通过滤波器控制电磁波干扰:在设备中添加滤波器,可有效降低电磁波的干扰。

常见的滤波器包括电源滤波器、信号滤波器等。

2. 使用合适的接地设计:良好的接地系统设计可以有效地减少EMI问题。

通过使用大地板、接地导线等,可将设备的电磁辐射能量导入地面。

3. 注意设备的散热设计:过高的温度可能会导致电子设备内部电路的不稳定工作,进而影响EMC性能。

因此,设备的散热设计应得到重视。

四、进行EMC测试和认证1. 进行EMI测试:通过使用专业的EMI测试仪器,对电子设备进行辐射和传导测量。

这可以帮助确定问题所在,并采取相应的措施进行修正。

电子产品设计中的EMC和EMI问题分析

电子产品设计中的EMC和EMI问题分析电子产品设计中的EMC问题和EMI问题是非常重要的考虑因素,其影响着产品的性能和可靠性。

本文将详细分析EMC和EMI问题,并给出相应的解决步骤。

1. 什么是EMC和EMI问题:- EMC (Electromagnetic Compatibility) 是指电子设备在同一环境中能够共存并互不干扰。

- EMI (Electromagnetic Interference) 是指电子设备之间相互干扰,导致其性能下降或者失效。

2. EMC和EMI问题的原因:- 电子设备内部不同电路之间的高频信号干扰。

- 电子设备与外部环境的电磁辐射和电磁感应。

3. EMC和EMI问题的影响:- 降低产品性能和可靠性。

- 对其他设备产生干扰。

4. 解决EMC和EMI问题的步骤:- 设计阶段:a. 选择合适的电磁屏蔽材料,将电磁波传播限制在产品内部。

b. 使用合适的滤波器和降噪电路,减少干扰信号的传播。

c. 合理规划电路板布局,减少高频信号的串扰。

d. 使用地线和功率平面分层布局,减少地回流干扰。

- 材料选择:a. 选择低电阻和高导电性的材料,提高电磁波的屏蔽效果。

b. 选择低电磁散射率和高磁饱和磁导率的材料,减少电磁波的反射和传播。

c. 选择低介电常数和低介电损耗的绝缘材料,减少电磁波的衍射和能量损耗。

- 电路设计:a. 适当地使用滤波器和降噪电路,降低电磁干扰信号的传输。

b. 使用合适的屏蔽技术,将关键的高频信号线缠绕在金属盖板或电磁屏蔽罩中,避免干扰信号泄漏。

- PCB布局设计:a. 避免信号线和功率线平行布局,降低互相的干扰。

b. 合理规划地线和功率平面的布局,减少地回流干扰。

c. 使用地平面和功率平面进行分层布局,减少电磁辐射。

d. 对高频信号线进行合理的阻抗匹配,减少反射和串扰。

- 产品测试:a. 使用专业的EMI测试设备对产品进行测试,确保其符合相关的电磁兼容标准。

b. 测试产品在不同频率下的辐射和传导幅度,找出潜在的干扰源和敏感部件。

电磁兼容(EMC)和电磁干扰(EMI)的浅谈及改善策略 2

电磁兼容(EMC)和电磁干扰(EMI)的浅谈及改善策略摘要:本文介绍了电磁兼容(EMC)和电磁干扰(EMI)的概念及其对电子器件的工作、人体健康以及工业生产的影响,并简要说明了EMI的产生原理及其理论上的改善方法,最后,举出了几种工业生产上改善电磁兼容性的实例。

Abstract:This article describes the electromagnetic compatibility (EMC) and electromagnetic interference (EMI) The concept and its impact on the work of electronic devices, human health and the impact of industrial production, and a brief description of the EMI generation principle and theoretical ways of improvement, finally, cited a number of industrial production to improve the electromagnetic compatibility instance.关键词:电磁兼容(EMC);电磁干扰(EMI);改善策略目录:一、前言 (1)二、电磁兼容(EMC)和电磁干扰(EMI) (1)(一)电磁兼容(electromagnetic compatibility;EMC)的定义 (1)(二)电磁兼容(EMC)的设计目的 (2)(三)近年来电磁兼容(EMC)领域的发展概况 (2)三、电磁干扰(EMI)的原理及改善电磁兼容性的措施 (2)(一)EMI的产生原因 (2)(二)电磁干扰的传播途径 (2)(三)改善电磁兼容性的措施 (3)四、工程上一些改善电磁兼容(EMC)的设计思路 (3)五、展望 (4)参考文献: (4)一、前言电子技术的飞速发展给人们的生活和工作带来了巨大的帮助。

怎样提高电子产品的EMC、EMI

怎样提高电子产品的EMC、EMI在研制带处理器的电子产品时,如何提高抗干扰能力和电磁兼容性?1、下面的一些系统要特别注意抗电磁干扰:(1) 微控制器时钟频率特别高,总线周期特别快的系统。

(2) 系统含有大功率,大电流驱动电路,如产生火花的继电器,大电流开关等。

(3) 含微弱模拟信号电路以及高精度A/D变换电路的系统。

2、为增加系统的抗电磁干扰能力采取如下措施:(1) 选用频率低的微控制器:选用外时钟频率低的微控制器可以有效降低噪声和提高系统的抗干扰能力。

同样频率的方波和正弦波,方波中的高频成份比正弦波多得多。

虽然方波的高频成份的波的幅度,比基波小,但频率越高越容易发射出成为噪声源,微控制器产生的最有影响的高频噪声大约是时钟频率的3倍。

(2) 减小信号传输中的畸变微控制器主要采用高速CMOS技术制造。

信号输入端静态输入电流在1mA左右,输入电容10PF左右,输入阻抗相当高,高速CMOS电路的输出端都有相当的带载能力,即相当大的输出值,将一个门的输出端通过一段很长线引到输入阻抗相当高的输入端,反射问题就很严重,它会引起信号畸变,增加系统噪声。

当Tpd>Tr时,就成了一个传输线问题,必须考虑信号反射,阻抗匹配等问题。

信号在印制板上的延迟时间与引线的特性阻抗有关,即与印制线路板材料的介电常数有关。

可以粗略地认为,信号在印制板引线的传输速度,约为光速的1/3到1/2之间。

微控制器构成的系统中常用逻辑电话元件的Tr (标准延迟时间)为3到18ns之间。

在印制线路板上,信号通过一个7W的电阻和一段25cm长的引线,线上延迟时间大致在4~20ns之间。

也就是说,信号在印刷线路上的引线越短越好,最长不宜超过25cm。

而且过孔数目也应尽量少,最好不多于2个。

当信号的上升时间快于信号延迟时间,就要按照快电子学处理。

此时要考虑传输线的阻抗匹配,对于一块印刷线路板上的集成块之间的信号传输,要避免出现Td>Trd的情况,印刷线路板越大系统的速度就越不能太快。

emi emc 标准(二)

emi emc 标准(二)什么是EMI/EMC标准•EMI是指电磁干扰•EMC是指电磁兼容•标准是为了保证电子产品在操作时不会产生电磁辐射干扰其他设备,同时也不会受到其他设备的影响而出现故障EMI/EMC标准的重要性•EMI/EMC标准是电子产品生产和销售的必要条件•不符合标准的产品容易对其他设备产生电磁干扰,影响正常使用•不符合标准的产品也容易受到其他设备的电磁干扰,从而出现故障EMI/EMC标准的分类•国家标准:由政府机构制定的标准,如国家电子工业标准•行业标准:由行业协会或商会制定的标准,如机电产品电磁兼容标准•国际标准:由国际标准制定组织(ISO、IEC等)制定的标准,如ISO 9001EMI/EMC标准的测试•根据不同标准的要求,需要进行不同的测试,如辐射测试、共模抑制测试、抗干扰测试等•测试过程需要符合一定的规范和条件,如测试室需要符合一定的尺寸、地面、墙壁等条件•测试结果需要符合标准的要求,一般需要向相关机构提交测试报告进行认证EMI/EMC标准的应用•电子产品的生产和销售:电子产品需要符合国家和行业标准的要求,才能在市场上合法生产和销售•电磁辐射监测:电磁干扰对周围环境和人体健康有潜在的影响,需要进行监测和控制•标准的更新和演进:随着科技的发展,标准也需要不断更新和演进,以适应新的技术和需求EMI/EMC标准是保障电子产品正常运行和使用的重要手段,需要重视和遵守相关标准的要求。

如何满足EMI/EMC标准•电路设计:合理的电路设计可以有效减小电磁辐射和受干扰的风险,例如使用滤波电路、屏蔽电路等•PCB设计:合理的PCB设计也可以有效减小电磁辐射和受干扰的风险,例如合理布局、使用屏蔽层等•材料选择:选择合适的材料也可以有效减小电磁辐射和受干扰的风险,例如使用抗干扰材料、屏蔽材料等。

•测试认证:进行相应的测试认证可以验证产品是否符合EMI/EMC 标准的要求,如果不符合则需要进行改进和优化。

EMCEMI综合解决与方案与设计经验

EMC-EMI综合解决方案与设计经验分享随着电气电子技术的发展,家用电器产品日益普及和电子化,广播电视、邮电通讯和计算机及其网络的日益发达,电磁环境日益复杂和恶化,使我们逐渐关注设备的工作环境,日益关注电磁环境对电子设备的影响,电气电子产品的电磁干扰(EMI)和电磁兼容性(EMC)的问题越来越受到工程师和生产企业的重视。

电子元件技术网为帮助广大工程师朋友解决在产品设计和应用中遇到的EMC/EMI问题,已成功举办了七届电磁兼容技术研讨会,邀请在EMC/EMI领域的专家讲解其市场、技术趋势和前沿应用,更有现场提问环节,与专家讨论实际设计中遇到的EMC/EMI设计难题以及ESD防护。

本期半月谈将以往EMC/EMI研讨会的技术精华进行了汇总。

在4月8日于深圳会展中心举行的第七届电路保护和电磁兼容研讨会上,多家国内外领先的厂商发表了针对EMC/EMI的解决方案,下面是各位专家演讲内容实录和演讲资料的下载地址:苏州泰思特电子科技有限公司总工程师赵阳博士:《电磁兼容问题综合解决方案》(点击下载演讲PPT)著名专家,社区好老师陶显芳:《设计工程师EMC 经验分享》(点击下载演讲PPT)村田(中国)投资有限公司高级产品工程师范为俊:《改进手机灵敏度的EMC 解决方案》(点击下载演讲PPT)静电防护(ESD)找到被保护对象很重要“在设计电磁防护电路中,工程师要清楚的知道在系统里要保护什么?找到被保护的对象很重要,如何在10000个器件中找到哪些是核心的,哪些是容易受干扰的?当找到了被保护的电路,就要开始进行静电分析,是哪种静电让它失效的?是什么原因?分析完种种原因后就要进行静电防护措施,选用对应的器件。

” 赵阳博士在电磁兼容问题综合解决方案中提到。

传导性ESD防护:对静电电流在电路中防护主要使用一些保护器件,在敏感器件前端构成保护电路,引导或耗散电流。

此类保护器件有:陶瓷电容,压敏电阻,TVS管等。

辐射性ESD防护:对于静电产生的场对敏感电路产生影响,防护方法主要是尽量减少场的产生和能量,通过结构的改善增加防护能力,对敏感线路实施保护。

EMI电磁干扰与探讨防制.ppt

Reconfirm的重要

在許多EMI對策上會面臨Golden Sample可符合而量產品 卻無法符合的困擾,會有這現象最主要就是沒有逐一確 認所下的對策是否有效,故Reconfirm的觀念是很重要的 正確的步驟如下:

1.EMC和天線理論是密切而息息相關的,如何將天線理 論的觀念,應用到實際產品的設計修改對策是非常重 要的,能夠充分了解認識天線理論才能做好產品的 EMC的防制。

2.電磁波輻射是一個很抽象的現象,因為電波輻射在空中 看不見也摸不著,因此當發生電磁干擾現象時往往不 易解決。

3.整個天線的理論是相當複雜的,從EMC的角度而言其 實重點只有一個,那便是天線的長度。因為雜訊是經 由天線將能量輻射到空中,而不同的長度所共振的頻 率是不同的,所以只要避免或減低共振天線的效應, 則可有效控制產品的EMC。

(2)I/O Port (a)Bypass(20p-100p) (b)Bead(阻抗500 ohm以上) (c)Resister(22-47ohm)

(3)Vcc&Ground Bypsaa &Bead

四、Cable

(1)Inside (a)Short (b)Core(for below 300MHz noise) (c)Shielding(for above 300MHznoise)

Path

Antenna

什麼是EMC ???

當我們看電視或操作電腦時,如果旁邊有人使用電鬍 刀或吸塵器時,螢幕常會出現令人煩 躁的雪花條紋或 晃動現象。另外報章雜誌也時常報導有關行動電話干 擾心率調整器(pace- maker)或工廠之起重機而造成誤 動作的事故,基本上這些都是電磁干擾現象如果電磁 干擾信號妨礙了正使用中的醫療電子設備或飛行中的 飛機電子設備時,則可能會造成不堪設想的後果。

EMI问题解决策略

EMC/EMI问题解决策略引言EMC(Electromagnetic Compatibility,电磁兼容性)和EMI(Electromagnetic Interference,电磁干扰)是现代电子设备设计和生产中常见的问题。

EMC指的是不同电子设备之间,以及设备与电磁环境之间互不干扰的能力;而EMI指的是电子设备对其周围电磁环境的干扰。

在电子设备频繁使用的现代社会,解决EMC/EMI问题至关重要。

本文将介绍一些常见的EMC/EMI问题解决策略,以帮助电子设备设计者和制造商解决这些问题。

问题识别与分析在解决EMC/EMI问题之前,首先需要对问题进行识别和分析。

以下是识别和分析EMC/EMI问题的一些常见方法:1.测试和测量:通过使用专业的EMC测试设备和测量仪器,对电子设备进行测试和测量,以确定是否存在EMC/EMI问题。

例如,使用频谱分析仪、信号发生器和射频扫描仪等设备,可以对电磁辐射和传导干扰进行测量和分析。

2.频谱分析:通过频谱分析,可以识别电子设备发出的电磁辐射信号的频率和幅度。

这有助于确定是否存在干扰源,并确定其频段和强度。

3.电磁场模拟软件:使用专业的电磁场模拟软件,如ANSYS、CST等,可以对电子设备的辐射和接收情况进行模拟和仿真。

这些软件可以帮助电子设备设计者预测和处理EMC/EMI问题。

4.故障排除:当电子设备出现EMC/EMI问题时,通过排除法逐步确定问题的来源。

可以通过逐个关闭或断开电子设备的部件,以确定是否是某个特定部件引起的问题。

解决策略一旦识别和分析了EMC/EMI问题,下一步就是采取适当的解决策略来解决这些问题。

以下是一些常见的EMC/EMI问题解决策略:1.电磁屏蔽:电磁屏蔽是减少或消除电子设备之间和设备与环境之间电磁干扰的一种常用方法。

可以使用金属外壳、金属屏蔽罩等材料来包裹电子设备,以阻隔电磁干扰。

此外,还可以采用地线、屏蔽接地等技术手段,有效地抑制电磁干扰。

家用电器产品EMC&EMI测试讲解

共模辐射

共模辐射主要由接地杂讯组成,如图B所示。这个接地 杂讯可以是由接地反弹所引起。除此之外,任何两个 装置接线间因接地不良所形成的地端回路电流也会产 生接地杂讯。 接地反弹是数字系统的主要杂讯之一,常见的现象是 会造成系统的逻辑运作产生错误的动作。它主要是源 自于电源路径以及IC封装所造成的杂散电感

电磁干扰会发生作用,有三个要素必须同时存在, 包括一个电磁波的辐射源或传导源,和一个传播媒 介以及一个或一个以上的受干扰电子装置,如图A所 示。如果其中任何一个要素不存在,干扰就不会发 生,所以防止电磁干扰的方法有三个: A 设法降低电磁波辐射源或是传导源; B 中断传播媒介; C 增加受扰装置的抗扰能力。 电磁干扰源大致可以分为天然和人为两种,而EMI 的传播媒介也有两种:一种是以电流的形式由电源 线和I/O排线或电缆传导出去,另一种是以辐射电磁 波的形式由空气辐射出去。

BACK

干扰源

传播介

受扰装置

图A 电磁干扰环境的三大要素

辐射干扰的类型

对于高速数字系统而言,其辐射干扰的来源主 要是来自于印刷电路板的数字电路。数字电路 的辐射干扰有共模辐射和差模辐射,其中差模 辐射主要是发生在数字电路的磁场回路,而共 模辐射则是由于I/O排线或者控制线出现电双极 的情形。

电流回路的面积

常见的方法有采用较小尺寸的IC封装,也可以选用多层 板来替代单层或双层的印刷电路板。 对于高速数字系统而言,可以减少电流频率很高的时钟 信号回路与电流值很大的电源电流回路的面积,而电源 回路是另一个需要减少其面积的回路。

回路电流的高频谐波分量

对于时钟信号,假若时序规格允许的话,通常会利用一 个低通滤波器来减缓时钟信号的转换时间。

建立完善的EMC测试和EMI调试手段的报告

建立完善的EMC测试和EMI调试手段的报告前言未来的战争是信息的战争,这一点已经成为共识,信息的主要传送方式是电磁波。

军用产品的电磁干扰控制技术,不仅仅是国军标GJB-151A/152A所要求的,更是为了提高国防能力的需要,摆在各军品生产单位面前最迫切的任务就是控制产品的电磁辐射,提高产品的电磁隐蔽性能,提高产品对电磁干扰的抗干扰能力。

产品的电磁兼容特性,不仅仅是产品的一个最重要的质量指标,对军用产品,它更是一项安全指标。

西方发达国家,对产品的电磁兼容(EMC)/电磁干扰(EMI)的研究已经积累了几十年的经验,并拥有大量先进的测试和调试设备,美国最早的军用标准发布于1967年并在当年强制实施。

而我国的军用标准最早分布于1986年,强制执行GJB-151A/152A还是最近几年的事情。

我们的工程师对产品的EMC 设计技术和EMI抑制技术还很不熟悉;我们企业的EMC/EMI设备几乎是空白。

为使公司不断开发满足现代战争要求的产品,建立一套相对完善的EMC测试和EMI调试手段是非常必要的。

建立EMC测试手段的目的在于能在公司内部对产品的各个阶段实际测量产品的EMC特性,及时掌握产品的EMC性能,在研究、开发、生产的各个阶段控制产品的EMC指标。

建立EMI调试手段的目的则在于排除产品内部的EMI问题,提高产品质量;在电路设计上,从源头降低产品对外的电磁干扰;在电路设计上考虑产品的抗干扰性能,提高产品的电磁环境适应能力。

一、电子产品EMC设计对策1.传统的电磁兼容设计对策传统的电子产品设计流程是,硬件工程师对EMC的理论、EMI的产生机理和抑制手段概不清楚,他们在基于逻辑考虑,完成PCB设计和样机的调试后,就把样机交给专门的EMI工程师。

目前,大部分企业的EMI工程师,更熟悉结构设计,一般不熟悉PCB的设计技术。

传统的EMI对策方法,是将试制完成的产品(EUT)送到电磁兼容(EMC)认证测试中心的暗室,实测它所发出的电磁辐射;针对实测结果,采取相应对策。

3GPP 5G基站(BS)R16版本一致性测试英文原版(3GPP TS 38.141-1)

4.2.2

BS type 1-H.................................................................................................................................................. 26

4.3

Base station classes............................................................................................................................................27

1 Scope.......................................................................................................................................................13

All rights reserved. UMTS™ is a Trade Mark of ETSI registered for the benefit of its members 3GPP™ is a Trade Mark of ETSI registered for the benefit of its Members and of the 3GPP Organizational Partners LTE™ is a Trade Mark of ETSI registered for the benefit of its Members and of the 3GPP Organizational Partners GSM® and the GSM logo are registered and owned by the GSM Association

EMC-EMI之综合解决方案

EMC-EMI之综合解决方案引言概述:电磁兼容性(EMC)和电磁干扰(EMI)是现代电子设备设计和制造中的重要问题。

在一个复杂的电磁环境中,电子设备需要能够正常工作,而不会对其他设备或系统产生干扰。

为了解决这个问题,工程师们需要采取一系列综合的解决方案。

本文将介绍EMC-EMI综合解决方案的五个主要部分。

一、电磁兼容性设计1.1 电磁兼容性测试与分析:在设计阶段,工程师需要进行电磁兼容性测试和分析,以评估设备在电磁环境中的性能。

这包括测量设备的辐射和敏感性,以及分析设备的电磁兼容性问题。

1.2 电磁屏蔽设计:为了减少设备对外部电磁干扰的敏感性,工程师需要设计有效的电磁屏蔽。

这可以通过使用屏蔽材料、设计屏蔽结构和布线来实现。

1.3 地线和接地设计:良好的地线和接地设计是保证设备电磁兼容性的关键。

工程师需要注意地线的布线和连接,以减少电磁干扰的传导和辐射。

二、滤波器设计2.1 电源线滤波器:电源线滤波器可以有效地抑制电源线上的高频噪声和干扰。

工程师需要选择适当的滤波器类型和参数,以满足设备的EMI要求。

2.2 信号线滤波器:信号线滤波器可以减少信号线上的电磁干扰。

工程师需要根据信号频率和干扰源的特性选择合适的滤波器,并考虑滤波器对信号质量的影响。

2.3 模块化滤波器设计:对于大型系统或模块化设备,工程师可以设计模块化滤波器来简化滤波器的安装和维护。

这可以提高设备的可靠性和可维护性。

三、接地和屏蔽技术3.1 接地系统设计:良好的接地系统可以减少设备的地线回路干扰和地线回路噪声。

工程师需要设计合适的接地系统,包括接地电极的布置和连接。

3.2 屏蔽技术:除了电磁屏蔽设计外,工程师还需要考虑其他屏蔽技术,如屏蔽罩、屏蔽盒和屏蔽涂料。

这些技术可以进一步减少设备的辐射和敏感性。

3.3 防静电设计:静电会对电子设备的性能和可靠性产生负面影响。

工程师需要采取防静电设计措施,如使用防静电材料和接地技术,以减少静电干扰和损害。

EMC-EMI之综合解决方案

EMC-EMI之综合解决方案EMC(Electromagnetic Compatibility)和EMI(Electromagnetic Interference)是电磁兼容性和电磁干扰的两个重要概念。

在现代电子设备和系统中,EMC和EMI问题越来越受到重视,因为电磁干扰会影响设备的正常工作,甚至会导致设备损坏。

因此,为了解决EMC和EMI问题,需要综合的解决方案。

一、电磁兼容性(EMC)问题1.1 电磁兼容性测试:通过电磁兼容性测试可以评估设备在电磁环境中的性能,包括传导和辐射干扰。

1.2 电磁兼容性设计:在设计阶段考虑电磁兼容性可以减少后期干扰问题的发生,包括布线设计、地线设计等。

1.3 电磁兼容性标准:遵循国际和国内的电磁兼容性标准可以确保设备在市场上的合规性,如CISPR、IEC等标准。

二、电磁干扰(EMI)问题2.1 电磁干扰源:识别和消除电磁干扰源是解决EMI问题的第一步,包括电源、信号线、开关电源等。

2.2 电磁屏蔽:采用合适的电磁屏蔽材料和技术可以有效减少电磁干扰的影响,如金属外壳、铁氧体材料等。

2.3 滤波器设计:在电路设计中加入滤波器可以减少电磁噪声的传播,提高系统的抗干扰能力。

三、综合解决方案3.1 综合测试:通过综合的EMC测试可以全面评估设备的电磁兼容性和抗干扰能力,及时发现和解决问题。

3.2 专业咨询:寻求专业的EMC工程师的建议和咨询可以匡助解决复杂的EMC和EMI问题,提高设备的性能。

3.3 持续改进:定期对设备进行EMC测试和评估,并不断改进设计和技术可以确保设备在不断变化的电磁环境中保持稳定性。

四、应用案例4.1 工业控制设备:在工业控制设备中,EMC和EMI问题尤其重要,因为设备的稳定性直接影响生产效率。

4.2 医疗设备:医疗设备对电磁干扰的敏感度较高,需要采用专业的EMC解决方案确保设备的安全和可靠性。

4.3 通信设备:在通信设备中,EMC和EMI问题会影响信号传输的质量,需要采取合适的措施保证通信质量。

EMC-EMI之综合解决方案

EMC-EMI之综合解决方案引言概述:电磁兼容性(EMC)和电磁干扰(EMI)是现代电子设备设计中不可忽视的重要问题。

为了确保电子设备在电磁环境中的正常运行,需要采取综合的解决方案来解决EMC和EMI问题。

本文将介绍一种综合的解决方案,以确保电子设备在各种电磁环境下的正常工作。

一、电磁兼容性(EMC)问题1.1 电磁辐射- 电子设备在工作过程中会产生电磁辐射,可能会对周围设备和系统造成干扰。

- 采取屏蔽措施,如金属外壳和屏蔽罩,以减少电磁辐射。

1.2 电磁感应- 电子设备受到周围电磁场的感应,可能导致设备的正常工作受到干扰。

- 采取滤波措施,如滤波器和抑制器,以减少电磁感应。

1.3 电磁敏感性- 电子设备对外界电磁场的敏感性可能导致设备的正常工作受到干扰。

- 采取抗干扰措施,如增加设备的抗干扰能力和提高系统的抗干扰能力。

二、电磁干扰(EMI)问题2.1 电磁辐射源- 电子设备可能成为电磁辐射源,对周围设备和系统造成干扰。

- 采取屏蔽措施,如金属外壳和屏蔽罩,以减少电磁辐射。

2.2 电磁感应源- 电子设备可能成为电磁感应源,对周围设备的正常工作造成干扰。

- 采取滤波措施,如滤波器和抑制器,以减少电磁感应。

2.3 电磁敏感源- 电子设备可能成为电磁敏感源,对外界电磁场的敏感性可能导致设备的正常工作受到干扰。

- 采取抗干扰措施,如增加设备的抗干扰能力和提高系统的抗干扰能力。

三、综合解决方案3.1 设备设计- 采用合适的电磁屏蔽材料和结构设计,以减少电磁辐射和电磁感应。

- 优化电路布局和地线设计,以提高电磁兼容性。

3.2 电磁兼容性测试- 对电子设备进行电磁兼容性测试,以评估设备在电磁环境中的性能。

- 根据测试结果进行调整和优化,以提高设备的电磁兼容性。

3.3 抗干扰措施- 采用滤波器、抑制器和抗干扰电路等措施,以减少电磁干扰。

- 优化设备的抗干扰能力和提高系统的抗干扰能力。

四、效果评估和改进4.1 评估电磁兼容性- 对设备进行电磁兼容性评估,以检测设备在电磁环境中的性能。

设计电子产品中产生EMI和EMC问题原因分析及解决

高速电路传输线效应分析与处理随着系统设计复杂性和集成度的大规模提高,电子系统设计师们正在从事100MHZ以上的电路设计,总线的工作频率也已经达到或者超过50MHZ,有一大部分甚至超过100MHZ。

目前约80% 的设计的时钟频率超过50MHz,将近50% 以上的设计主频超过120MHz,有20%甚至超过500M。

当系统工作在50MHz时,将产生传输线效应和信号的完整性问题;而当系统时钟达到120MHz时,除非使用高速电路设计知识,否则基于传统方法设计的PCB将无法工作。

因此,高速电路信号质量仿真已经成为电子系统设计师必须采取的设计手段。

只有通过高速电路仿真和先进的物理设计软件,才能实现设计过程的可控性。

传输线效应基于上述定义的传输线模型,归纳起来,传输线会对整个电路设计带来以下效应。

· 反射信号Reflected signals· 延时和时序错误Delay & Timing errors· 过冲(上冲/下冲)Overshoot/Undershoot· 串扰Induced Noise (or crosstalk)· 电磁辐射EMI radiation1 反射信号在高速电路中,信号的传输如上图所示,如果一根走线没有被正确终结(终端匹配),那么来自于驱动端的信号脉冲在接收端被反射,从而引发不可预期效应,使信号轮廓失真。

当失真变形非常显著时可导致多种错误,引起设计失败。

同时,失真变形的信号对噪声的敏感性增加了,也会引起设计失败。

如果上述情况没有被足够考虑,EMI将显著增加,这就不单单影响自身设计结果,还会造成整个系统的失败。

反射信号产生的主要原因:过长的走线;未被匹配终结的传输线,过量电容或电感以及阻抗失配。

2 延时和时序错误信号延时和时序错误表现为:信号在逻辑电平的高与低门限之间变化时保持一段时间信号不跳变。

过多的信号延时可能导致时序错误和器件功能的混乱。

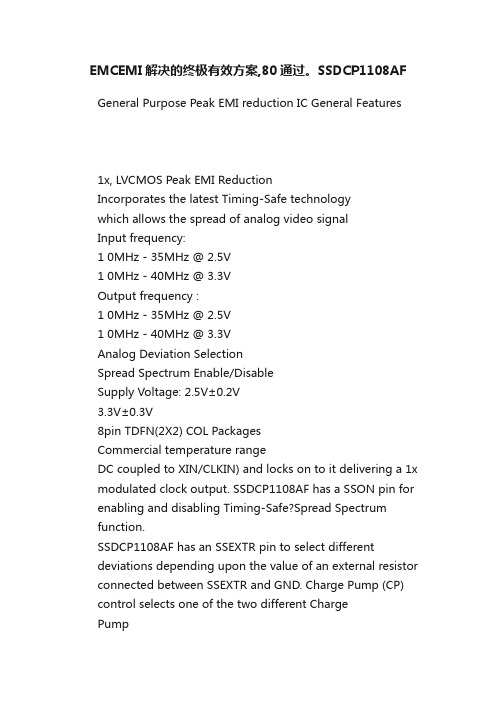

EMCEMI解决的终极有效方案,80通过。SSDCP1108AF

EMCEMI解决的终极有效方案,80通过。

SSDCP1108AF General Purpose Peak EMI reduction IC General Features1x, LVCMOS Peak EMI ReductionIncorporates the latest Timing-Safe technologywhich allows the spread of analog video signalInput frequency:********************************Output frequency :********************************Analog Deviation SelectionSpread Spectrum Enable/DisableSupply Voltage: 2.5V±0.2V3.3V±0.3V8pin TDFN(2X2) COL PackagesCommercial temperature rangeDC coupled to XIN/CLKIN) and locks on to it delivering a 1x modulated clock output. SSDCP1108AF has a SSON pin for enabling and disabling Timing-Safe?Spread Spectrum function.SSDCP1108AF has an SSEXTR pin to select different deviations depending upon the value of an external resistor connected between SSEXTR and GND. Charge Pump (CP) control selects one of the two different ChargePumpcurrent settings.SSDCP1108AF operates from a 3.3V/2.5V supply, and isavailable in an 8 pin TDFN(2X2) COLpackages, over Commercial temperature range.Functional DescriptionSSDCP1108AF is a versatile, 3.3V/2.5V Peak EMI reduction IC. SSDCP1108AF accepts an input clock either from a fundamental Crystal or from an external reference (AC or ?ApplicationSSDCP1108AF is targeted for consumer electronicsapplication such as MFP, STB, DSC, MID,HDMI,LCD panel Camcorder,and other timing sensitive analog video imaging applications ?Applications of HDMI, RJ45 port has good compatibilityBlock DiagramVDDSSON CPXIN/CLKINXOUTCrystalOscillatorPLL ModOUTSSEXTRGNDPin ConfigurationXIN / CLKIN 1XOUT 2SSON 38 VDDSSEXTRModOUT7 SSDCP1108AF SSDCP1108A6GND 4 5 Pin Description Pin #12345678 Pin NameXIN / CLKINXOUTSSONGNDModOUTCPSSEXTRVDDPin TypeIOIPOIPDescriptionCrystal connection or External reference clock input.Crystal connection. If using an external reference, this pin should be left open.Spread Spectrum ON/OFF. Spread Spectrum function enabled when HIGH, disabledwhen LOW. Has an internal pull-up resistor inside.GroundModulated clock outputCharge Pump current Select. When LOW selects Low CP current. Selects High CPcurrent when pulled HIGH. Has an internal pull-up resistor inside.Analog Deviation Selection through external resistor to GND.2.5V /3.3V supply Voltage.Frequency Selection tableVDD (V)2.53.3 Frequency (MHz)15-3515-40Operating ConditionsParameterVDDTACCINDescriptionSupply VoltageOperating Temperature (Ambient Temperature)Load CapacitanceInput CapacitanceMin2.3Max3.6+70107UnitV°CpFpFAbsolute Maximum RatingSymbolVDD, V INT STG T s T JT DVParameterVoltage on any input pin with respect to Ground Storage temperatureMax. Soldering Temperature (10 sec) Junction Temperature Static Discharge Voltage (As per JEDEC STD22- A114-B)Rating-0.5 to +4.6 -65 to +125260 150 2Unit V°C °C °C KVNote: These are stress ratings only and are not implied for functional use. Exposure to absolute maximum ratings for prolonged periods of time may affectdevice reliability.DC Electrical Characteristics for 2.5V ParameterVDD V IL V IH I IL I IH V OL V OH I CC I DDZ oDescriptionSupply Voltage Input LOW Voltage Input HIGH Voltage Input LOW Current Input HIGH Current Output LOW Voltage Output HIGH Voltage Static Supply Current Dynamic Supply Current Output ImpedanceTest Conditions Min2.3Typ2.5Max2.7 0.71.7V IN V INI OL I OH= 0V= V DD = 8mA = -8mA25 25 0.61.8XIN / CLKIN pulled low Unloaded Output50 1235UnitV V VμA μA V V μA mASwitching Characteristics for 2.5VParameterInput Frequency* / ModoUT 1, 2Duty CycleTest Conditions 1, 2 Output Rise Time 1,2Output Fall Time2Cycle-to-Cycle Jitter 2PLL Lock TimeMeasured at V DD /2Measured between 20% to 80% Measured between 80% to 20%Unloaded output with SSEXTR OPEN @ 27MHz Stable power supply, valid clock presented on XIN / CLKINMin1045Typ 50Max3555 2.2 2±1753Unit% nS nS pSmSNote: 1. All parameters are specified with 10pF loaded outputs.2. Parameter is guaranteed by design and characterization. Not 100% tested in production* Functionality with Crystal is guaranteed by design and characterization. Not 100% tested in production.DC Electrical Characteristics for 3.3V ParameterVDD V IL V IH I IL I IH V OL V OH I CC I DDZ oDescriptionSupply Voltage Input LOW Voltage Input HIGH Voltage Input LOW Current Input HIGH Current Output LOW Voltage Output HIGH Voltage Static Supply CurrentDynamic Supply CurrentOutput ImpedanceTest Conditions Min3.0Typ3.3Max3.6 0.82.0V IN V INI OL I OH= 0V= V DD= 8mA = -8mA 25 25 0.4XIN / CLKIN pulled lowUnloaded Output501630UnitV V VμA μA V VμAmASwitching Characteristics for 3.3VParameterInput Frequency* / ModOUT 3, 4Duty CycleTest Conditions 3, 4 Output Rise Time 3, 4Output Fall Time4Cycle-to-Cycle Jitter 4PLL Lock TimeMeasured at V DD /2Measured between 20% to 80% Measured between 80% to 20%Unloaded output with SSEXTR OPEN @ 27MHz Stable power supply, valid clock presented on XIN / CLKINMin1045Typ 50Max55 1.8 1.6±1503UnitMHz% nS nS pSmSNote: 3. All parameters are specified with10pF loaded outputs.4. Parameter is guaranteed by design and characterization. Not 100% tested in production.* Functionality with Crystal is guaranteed by design and characterization. Not 100% tested in production.Typical Crystal SpecificationsFundamental AT cut parallel resonant crystal Nominal frequency Frequency tolerance Operating temperature range Storage temperatureLoad capacitance(C P ) Shunt capacitance ESR27MHz± 50 ppm or better at 25°C 0°C to +70°C -40°C to +85°C 18pF7pF maximum 25Note: C L is the Load Capacitance and Rx is used to prevent oscillations at overtone frequency of the Fundamental frequency.Typical Crystal Interface CircuitSSDCP1108ARXIN/CLKINCrystalXOUTRxC LC LC L = 2*(C P - C S ),Where C P = Load capacitance of crystal from crystal vendor datasheetC S = Stray capacitance due to C IN, PCB, Trace etc.Switching WaveformsDuty Cycle Timingt 1t 2V DD /2V DD /2 V DD /2OUTPUTOutput Rise/Fall Time80%20%80%20%OUTPUTt 3t 4Application SchematicC L is the load capacitance for proper XTAL operation1 C LSSDCP1108AFXIN/CLKINVDD 8Noise Reduction FilterCVDDExternal Deviation ControlVDDR1XOUTVDD2 SSEXTR7Analog Deviation Control SSEXTR can be Pulled HIGH to turn OFF Deviation3 SSONCP 6SSON ControlCP Control4 GNDModOUT 5Note: SSON (Pin#3) CP (Pin#6): Connect to VDD or GNDRefer to Pin Description table for Functionality detailsNote: For AC Coupled Interface refer to Application Brief: CT100801Deviation Vs SSEXTR resistance Charts at 27MHzDeviation Vs SSEXTR Resistance @ 27MHz2.5CP=1MR=12.0 1.51.00.550 100 150 200 250 300 350 400 450 500 550 600 650Resistance(K _))% ± ( n o i t a i v e DDeviation Vs SSEXTR Resistance @ 27MHz2.5CP=0MR=0 2.01.51.00.50.00 50 100 150Resistance(K_) 200 250 300) %±( n o i t a i v e DTDFN COL 2x2 8L package Outline drawing Symbol InchesMin0.027 DimensionsMillimetersA A3 b D E e LMax0.0315Min0.700.008 BSC0.0080.0120.079 BSC0.078 BSC0.020 BSC0.0200.0240.200.50Max0.800.203 BSC0.302.00 BSC2.00 BSC0.50 BSC0.60SSDCP1108AF Spectrum DeviceOrdering CodePart Number SSDCP1108AF-08-CR Marking DAPackage8- pin 2-mm TDFN COL - TAPE & REEL, Green Temperature0 °C to +70 °CDevice Ordering InformationS S D C P 1 1 0 8 A F - 08 - CRR = Tape & Reel, T = Tube or TrayO = TSOT23S = SOICT = TSSOPA = SSOPV = TVSOPB = BGAQ = QFNU = MSOPE = TQFPL = LQFPU = MSOPP = PDIPD = QSOPX = SC-70J=TSOT26C=TDFN (2X2) COLDEVICE PIN COUNTF = LEAD FREE AND RoHS COMPLIANT PARTG = GREEN PACKAGE, LEAD FREE, and RoHS PART NUMBERI= Industrial(-40 °C to +85 °C )A = Clock GeneratorB = Non PLL basedC = EMI ReductionD = DDR support productsE = STD Zero Delay BufferP or n/c = Commercial(0 °C to +70 )°CF = Power ManagementG = Power ManagementH = Power ManagementIJ= Hi Performance= ReservedSpread Spectrum Device CO.,LTDCopyright All rights reserved by Spread Spectrum Device Part Number:SSDCP1108AFDocument Version:0.22。

电磁干扰[EMI]问题诊断步骤和电磁兼容[EMC]整改步骤

![电磁干扰[EMI]问题诊断步骤和电磁兼容[EMC]整改步骤](https://img.taocdn.com/s3/m/b019b9f5e2bd960591c677cb.png)

电磁干扰(EMI)问题诊断步骤|电磁兼容(EMC)整改步骤1.前言电磁干扰的观念及防制﹐在国内已逐渐受到重视。

虽然目前国内并无严格管制电子产品的电磁干扰(EMI)﹐但由于欧美各国多已实施电磁干扰的要求﹐加上数字产品的普遍使用﹐对电磁干扰的要求已是刻不容缓的事情。

笔者由于工作的关系﹐经常遇到许多产品已完成成品设计﹐因无法通过EMI测试﹐而使设计工程师花费许多时间和精力投入EMI的修改﹐由于属于事后的补救﹐往往投入许多时间及金钱﹐甚而影响了产品上市的时机2.正确的诊断要解决产品上的EMI问题﹐若能在产品设计之初便加以考虑﹐则可以节省事后再投入许多时间及金钱。

由于目前EMI Design-in的观念并不是十分普遍﹐而且由于事先的规划并不能保证其成品可以完全符合电磁干扰的测试在﹐所以如何正确的诊断EMI问题﹐对于设计工程师及EMI工程师是非常重要的。

事实上﹐我们如果把EMI当做一种疾病﹐当然平时的预防保养是很重要的﹐而一旦有疾病则正确的诊断﹐才能得到快速的痊愈﹐没有正确的诊断﹐找不到病症的源头﹐往往事倍功半而拖延费时。

故在EMI的问题上﹐常常看到一个EMI有问题的产品﹐由于未能找到造成EMI问题的关键﹐花了许多时间﹐下了许多对策﹐却始终无法解决﹐其中亦不乏专业的EMI工程师。

以往谈到EMI往往强调对策方法﹐甚而视许多对策秘决或绝招﹐然而没有正确的诊断﹐而在产品上加了一大堆EMI抑制组件﹐其结果往往只会使EMI情况更糟。

笔者起初接触产品EMI对策修改时﹐会听到资深EMI工程师说把所有EMI 对策拿掉﹐就可以通过测试。

初听以为是句玩笑话﹐如今回想这是很宝贵的经验谈。

而后亦听到许多EMI工程师谈到类似的经验。

本文中将举出实际的例子﹐让读者更加了解EMI的对策观念。

一般提到如何解决EMI问题﹐大多说是case by case,当然从对策上而言﹐每一个产品的特性及电路板布线(layout)情况不同﹐故无法用几套方法而解决所有EMI的问题﹐但是长久以来﹐我们一直想要把处理EMI问题并做适当的对策﹐另外也提供专业的EMI工程师一种参考方法。

什么是EMC?电磁兼容性基础知识

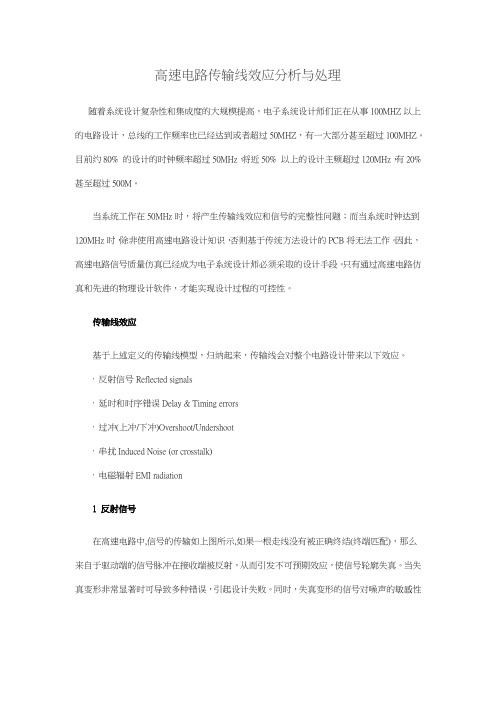

什么是EMC:一分钟了解电磁兼容性基础知识随着无线连接设备数量的增加,EMC的重要性日益增加,定义EMC是什么并理解这些概念可以从一开始就实现电磁兼容性,电磁兼容性,EMC是使不同电子设备在没有相互干扰的情况下运行的概念- 电磁干扰,EMI - 当它们彼此靠近操作时。

所有电子电路都有可能辐射拾取不需要的电干扰,这可能损害一个或另一个电路的操作。

电磁兼容性EMC /电磁干扰EMI概念1、什么是EMC - 定义EMC定义为设备和系统在其电磁环境中运行而不损害其功能且无故障的能力,反之亦然。

电磁兼容性,EMC确保操作不会影响电磁环境,以至于其他设备和系统的功能受到不利影响。

2、人们对EMC的认识历程:在电子产品的早期,相对较少的电子设备项目正在使用中。

然而今天,日常电子产品的数量已经大幅增加。

其中一些发射信号,而其他许多是敏感接收器。

其他人可能利用可能由瞬态信号错误触发的数字电子系统。

这些更多的例子可能是EMC电子设计的关键要素。

在电子系统的早期,收音机收到的流行音乐,刘海和一般噪音被视为收听收音机的“体验”的一部分- 即使它们是由其他本地电气设备制造的,电气干扰对电子系统影响的一些主要问题来自军事应用。

第二次世界大战后,随着核武器重要性的提高,爆炸产生的电子脉冲及其对设备的影响成为一个问题。

此外,高功率雷达系统对设备的影响也是一个问题。

后来,与ESD相关的电子设备面临的风险变得明显。

这些不仅损坏了电子设备,而且还可以设置错误的触发器。

在20世纪70年代,逻辑电路的使用迅速增长,并且随之增加了切换速度。

这些电路开启了EMI的影响,并且如果这些项目在现实世界中令人满意地工作,则需要将EMC预防措施纳入设计中。

由于这种日益增长的实现,许多国家开始意识到EMC是一个日益严重的问题,一些人开始向电子设备制造商发出指令,定义设备在出售设备之前应该满足的标准。

欧洲共同体是个实施EMC要求的地方,虽然许多人初都持怀疑态度,但EMC标准的引入提高了标准,使大多数类型的设备能够在不受干扰的情况下并排运行。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

S. Loyka

Department of Electrical Engineering Ecole de Technologie Superieure 1100, Notre-Dame St. West Montreal (Quebec), H3C 1K3, CANADA Email: sergey.loyka@ Abstract: Main challenges in EMCEMI modeling and simulation for modern and future wireless communication networks are addressed in this paper. It is emphasized that there exists a big difference between simulating analog and digital systems. A computationally-efficient approach for EMC/EMI analysis of wireless networks by behavioural-level numerical simulation is proposed. INTRODUCTION Wireless communication systems experience today unprecedented growth. The number of systems increases almost exponentially. In view of very limited spectrum available and large concentration of system over limited space (for example, in dense urban or indoor environments), the potential for mutual interference is tremendous. There are three potential wireless “candidates” for large EMC/EMI problems in the near future. First, the implementation of advanced smart antennas in 3G wireless systems, which allows to improve their performance substantially [l, 21, may cause additional EMC/EMI problems because a typical branch of antenna array, which is the main structure for smart antennas, contains active (nonlinear) stages. These stages can produce a considerable amount of RF EMI, especially in heavily-overcrowded spectrum [3, 41. Secondly, the large-scale introduction of broadband wireless systems [5, 61, which is foreseen for near future, will make these problems even more important and more difficult to solve since any bandwidth expansion increases the risk of getting interference problems. Thirdly, Bell Labs Layered Space-Time (BLAST) communication architecture, also known as MIMO (multiple-input multiple-output), is likely to be implemented in the near hture due to its unprecedented spectral efficiency [7, 81. This architecture uses multiple transmit and receive branches to launch and detect independent bit streams over the same wireless channel. Thus, its Tx and Rx branches operate at the same frequency, which can be a source of many EMC/EMI problems, especially in a complex electromagnetic environment [3]. The complexity of EMCEMI analysis in a future wireless network is very large due to the large number of systems in the network and due to the complexity of system (many Tx/Rx branches, complex structure of every branch) and of the electromagnetic environment. Generally speaking, the performance of wireless communication networks can be severe degraded by mutual interference between various radio systems sharing the same space and the same frequency band and, thus, must be carefully taken into account in the design and implementation (deployment) stages. The techniques proposed in the past [9111 are largely based on empirical or semi-empirical models developed for analog systems and are, in general, not accurate for modem digital systems. In this paper, we discuss main challenges in EMCEMI modeling and simulation for wireless communication networks, main differences between EMCEMI analyses for analog and digital systems and propose a computationallyefficient approach for systemlevel simulation of wireless systems at the physical layer (i.e., taking into account almost all the hardware imperfections) which can be efficiently combined with the existing methods of simulation at the signal processing level providing in this way a technique for the simulation of the entire communication link, starting for the source of information and up to the destination point. The computational efficiency of this approach is expected to be high enough to allow the simulation of real-world systems under real-world conditions in reasonable time and using reasonable computational resources.

E M INANALOG D I G ~ A L AND WIRELESS SYSTEMS

The mutual interference between wireless systems is presently taken into account mainly during the frequency planning stage and in an oversimplified way, i.e. no comprehensive Tx and Rx models are employed, only few basic parameters (carrier frequency, bandwidth, Tx power, Rx sensitivity and selectivity etc.) are accounted for. The main reason for this is that there is no accurate and computationally-efficienttechnique available for more %curate and comprehensive analysis. Thus, even carefully made frequency planning does not guarantee the absence of EM1 in any scenario. In general, all the interference effects may be divided into two large groups: (1) linear effect and (2) nonlinear effect. Modeling and simulation of linear effects in communication systems do not present a serious problem and can be carried out in a conventional way [ll]. On the contrary, accurate modeling and simulation of nonlinear effects in modem communication systems is a big challenge [12]. Thus, we